LTC6244による高速ピーク検出器

はじめに

ピーク検出器は、その入力における電圧信号の極値をキャプチャします。正ピーク検出器は入力信号の正のピーク値をキャプチャし、負ピーク検出器は入力信号の負のピーク値をキャプチャします。理想的には、ピーク検出回路の出力は極値に達するまで入力電圧をトラッキングし、入力が減少に転じるとその値をホールドします。理想的なピーク検出器は、入力信号の速度に関わらずこの機能を実行しますが、実際のピーク検出器の性能は、入力信号の帯域幅によって制限されます。本稿では、従来型アクティブ・ピーク検出回路の動作を検証して帯域幅の制約となるパラメーターと部品を明確にし、これらの制約を解消するための改善策を提案して、改善した回路の性能を比較したシミュレーション結果を示します。

従来型ピーク検出器

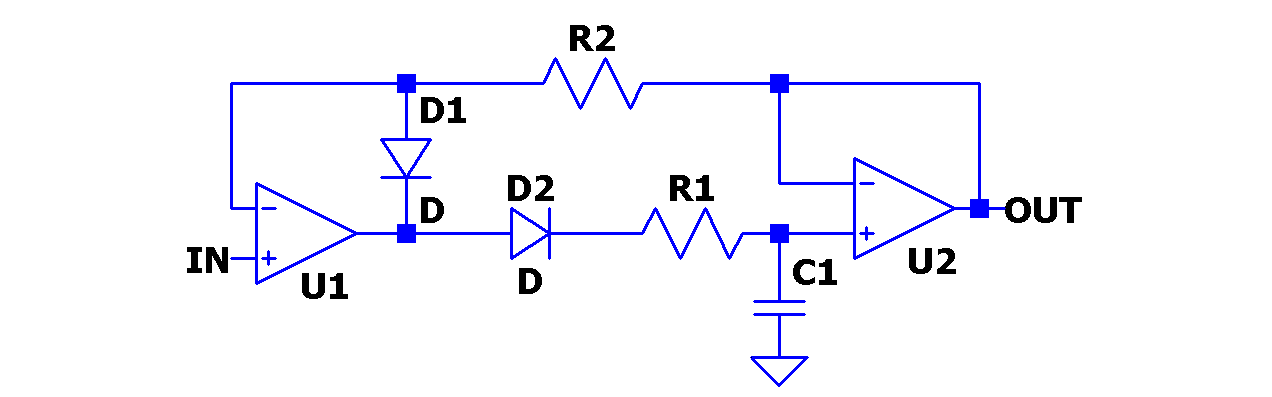

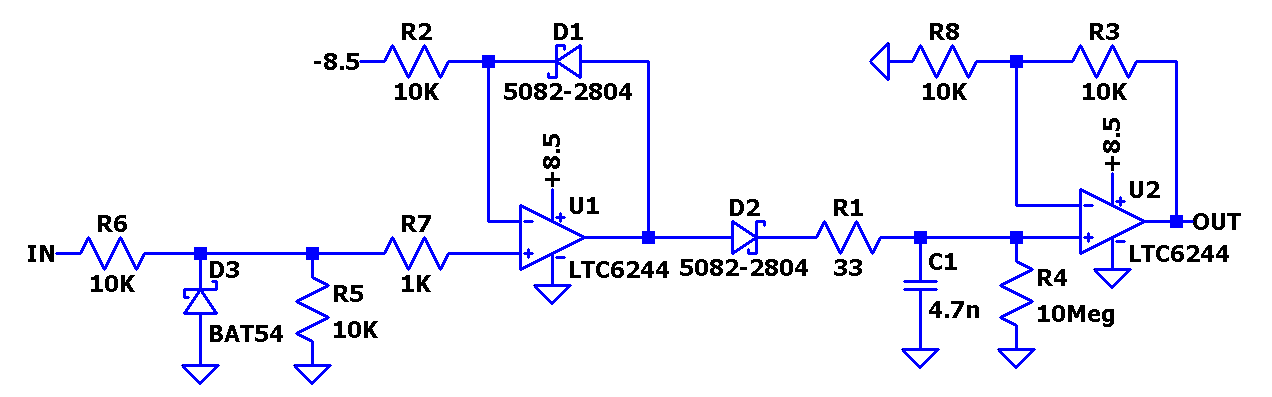

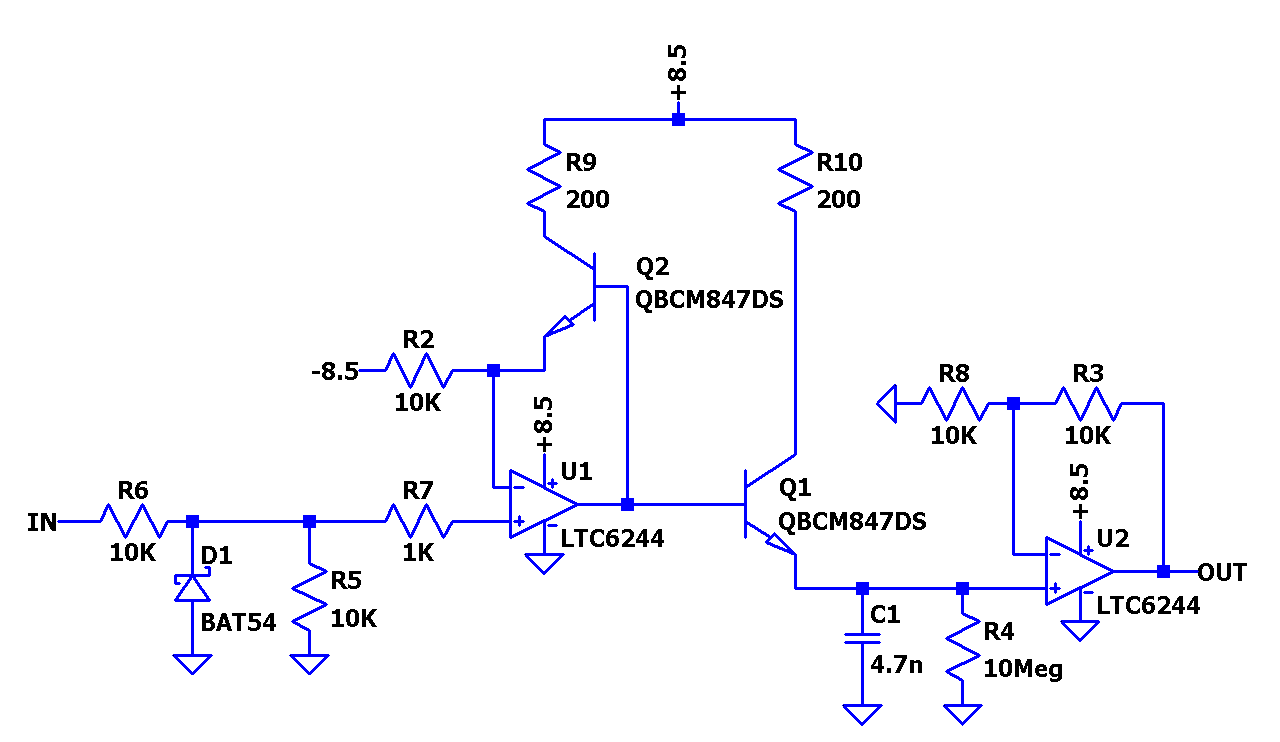

ピーク検出器の2とおりの実装例を図1と図2に示します。図1の回路は従来型のピーク検出器です。図2の回路は従来型ピーク検出器の制約に対処したものです。本稿では、従来型ピーク検出器の動作を検証してその回路の制約を明確にし、改善を加えた回路がこれらの制約にどのように対処しているのかを説明し、図3に示すように回路をさらに改善する方法を探ります。

図1.従来型ピーク検出器

図1の回路は、入力電圧(IN)のピーク値をキャプチャします。INが正の場合、D1には逆方向バイアス、D2には順方向バイアスがかかり、帰還抵抗R2には電流は流れません。従って、出力電圧(OUT)は入力電圧(IN)をトラッキングします。これは、外部帰還ループが、U1の入力を実質的な短絡状態(V+ = V–)にするからです。U2は電圧フォロワとして構成されているので、出力電圧はコンデンサC1の電圧をトラッキングします。C1は、U1の出力電流により、D2を介してこの電圧まで充電されます。R1は、U1がその短絡出力電流を超えないようにするとともに、U1をC1の容量から分離してリンギングや発振を防ぎます。この状態は、入力電圧が正で増加を続けている限り維持されます。

図1に示す回路は、入力電圧が減少すると状態が変化します。入力電圧が減少すると、U1の出力(D2の陽極)がD2の陰極電圧(C1に保存された、それ以前のピーク電圧に等しい電圧)未満に低下するので、D2に逆方向バイアスがかかります。この状態では外部帰還ループが失われ、U1の出力は負のレール電圧に合わせようとします。この状態ではD1に順方向バイアスがかかってU1へのローカル帰還が行われ、それによってD2の陽極が入力電圧より1ダイオード・ドロップ分だけ低い値にクランプされます。この状態は、入力電圧がコンデンサ電圧(出力電圧に等しい)を上回るまで維持されます。このD1クランプは、ホールド状態からトラッキング状態へ戻るまでの遷移時間を短縮します。

速度は、図1に示す従来型ピーク検出回路の主要な制約要素です。C1の充電より早く出力電圧を変えることはできません。C1の充電速度は、U1の短絡出力電流、D2の順方向電圧降下、D2の応答速度、およびR1とC1により形成される時定数に起因する指数関数的立上がりによって制限されます。

改良型ピーク検出器

図2に示す回路の速度と誤差は、図1に示す回路より向上しています。この向上は、従来型ピーク検出器のいくつかの制約に対処した結果です。整流ダイオードがショットキー・バリア・タイプに変更されている点に注目してください。この変更により順方向電圧降下が減少し、それによってC1に流れる初期充電電流が増大します。加えて、ショットキー・ダイオードは回復時間が短いので、トラッキング状態からホールド状態への遷移速度が向上します。さらに、ショットキー・ダイオードは逆回復電荷が小さいので、C1のペデスタル誤差が減少します。

ショットキー・ダイオードの電圧降下は比較的小さいものですが、図1に示す従来型回路とは異なり電圧降下を補償する外部帰還ループがないので、出力に直接反映されます。この回路では、U1のローカル帰還ループのマッチング・ショットキー・ダイオードを使って相殺することにより、このダイオード・ドロップを補償しています。マッチングさせたダイオードが同じようにバイアスされていれば、これら2つのダイオード・ドロップはほとんど打ち消されます。R2はD1のバイアス電流を設定し、これによりD1の電圧降下でD2の電圧降下を打ち消して、この誤差を最小限に抑えます。

R5とR6は抵抗分圧器を形成して、入力電圧のレベルを下げます。D3は、0Vよりダイオード・ドロップ分低い値に入力電圧をクランプして、負の電源レールのU1とU2に余裕を持たせます。

図2.改良型ピーク検出器

LTC6244は、ユニティ・ゲイン安定性を持った高速CMOSデュアル・オペアンプで、50MHzのゲイン帯域幅、40V/μsのスルー・レート、1pAの入力バイアス電流、低入力容量、レールtoレールの出力スイングを特長とします。0.1Hz~10Hzのノイズはわずか1.5μVP-Pで、1kHzのノイズは12nV/√Hz未満であることが確保されています。この優れたAC性能とノイズ性能に加えて、広い電源範囲での動作、100μV以下のオフセット電圧、わずか2.5μV/°Cのドリフトという特性から、LTC6244はこのようなアプリケーションに最適と言えます。

電流ブーストを追加した改良型ピーク検出器

図3の回路は、図2に示す改良型ピーク検出器の方法を利用して、C1充電電流を大きくするために電流ブースト機能を追加したものです。この電流ブースト型ピーク検出器では、マッチングしたダイオードを、マッチングしたNPNバイポーラ接合トランジスタ(BJT)に変更しています。この回路は図2の回路とまったく同じ動作をしますが、C1の充電速度が大幅に向上しています。

図3.電流ブーストを追加した改良型ピーク検出器

このトポロジには、ショットキー・ダイオードを使う方法以外にいくつかの改善策があります。C1の充電電流は、コモン・コレクタBJT構造の電流ゲインと同じ倍率で増加します。加えて、このトポロジではC1のソース・インピーダンスが小さくなります。エミッタ・フォロワはU2より大きい電流ソース能力を備えているのでR3は不要になり、結果として充電時定数はほぼゼロになります。図3の回路の速度は、U2の帯域幅、またはエミッタ・フォロワのユニティ・ゲイン周波数(fT)のいずれか小さい方によって制限されます。Q1のベース・エミッタ接合の電圧降下は、図2のD2およびD3の相殺と同じようにして、Q2のベース・エミッタ接合により打ち消すことができます。

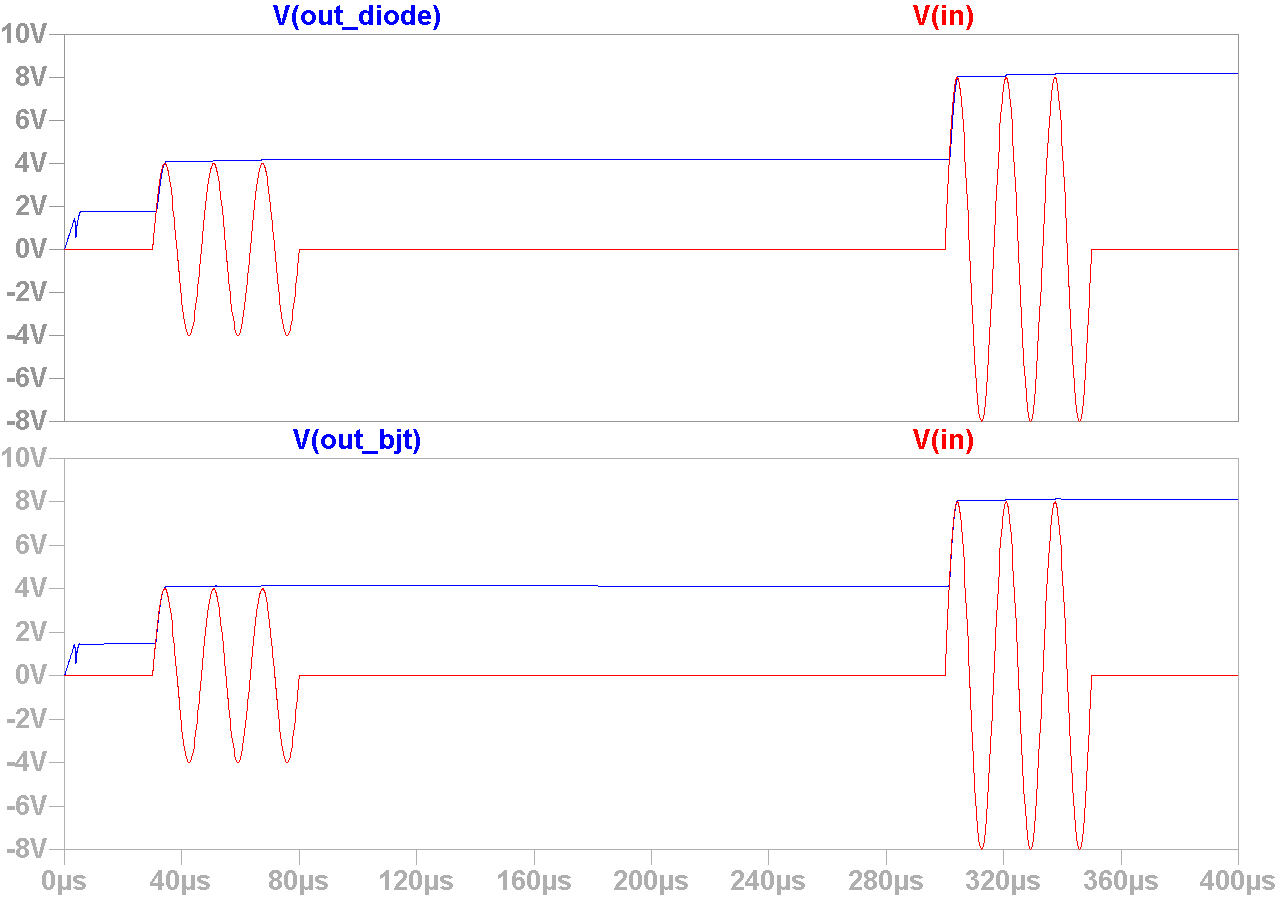

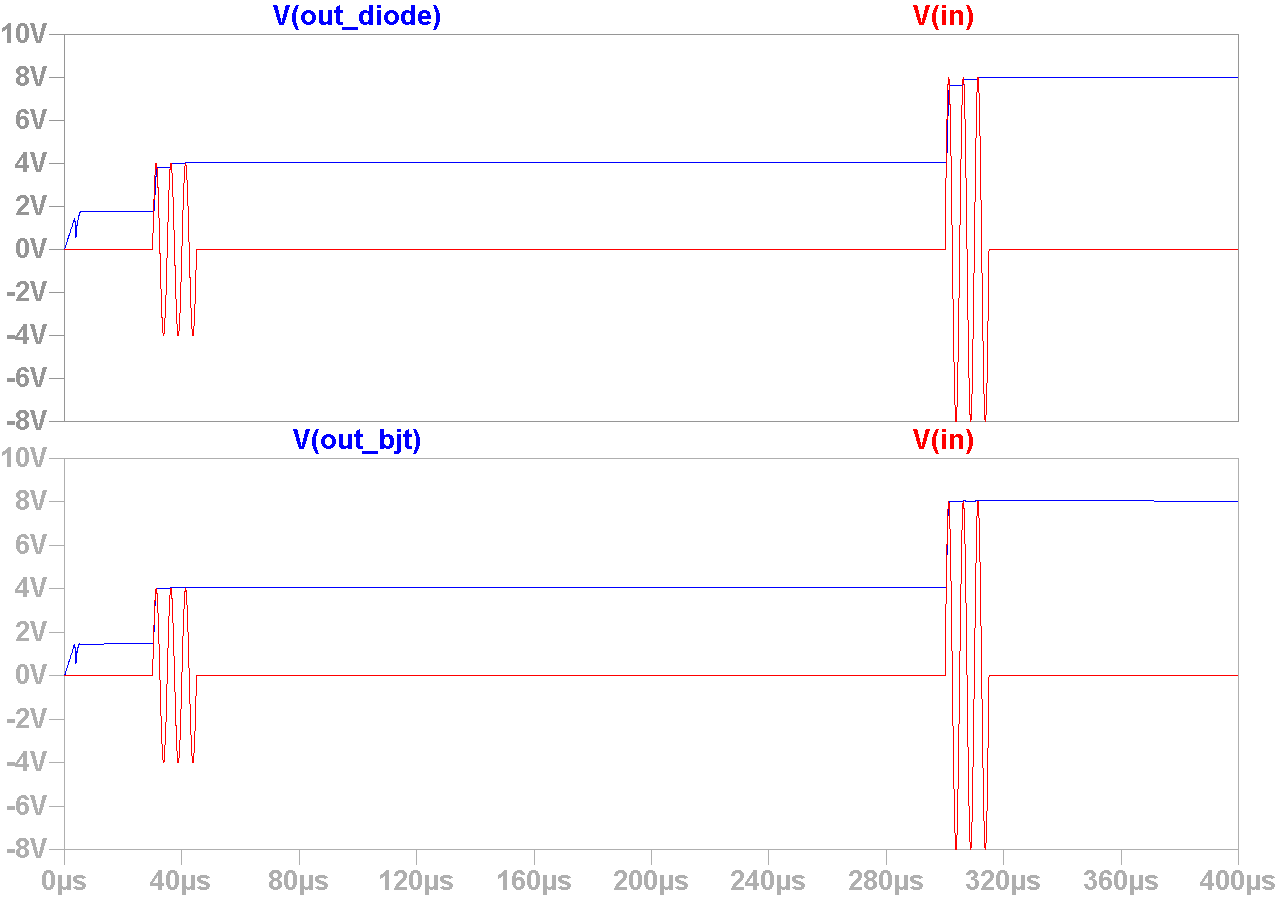

これら2つの高速ピーク検出器の性能を比較すると、図4は60kHzにおける回路の性能がどちらも同程度であることを示しており、図5は電流ブーストの改良で帯域幅が広くなったことを示しています。

図4.60kHzでの比較

図5.200kHzでの比較

まとめ

従来型ピーク検出器を、図3に示すような電流ブースト型ピーク検出器に改良するにはコストが伴います。しかし、速度と精度が重視されるアプリケーションの場合、このような回路の改善を施すことで、消費電力や部品点数の増大、ならびに複雑化といったデメリットを十分に埋め合わせすることができるでしょう。