概要

設計リソース

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-AD5504EBZ ($138.02) High Voltage 30 V DAC Powered from a Low Voltage 3 V Supply Generates Tuning Signals for Antennas and Filters

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- 最大4つの高電圧出力を制御

- 単電源3Vから30V出力を発生

参考資料

回路機能とその特長

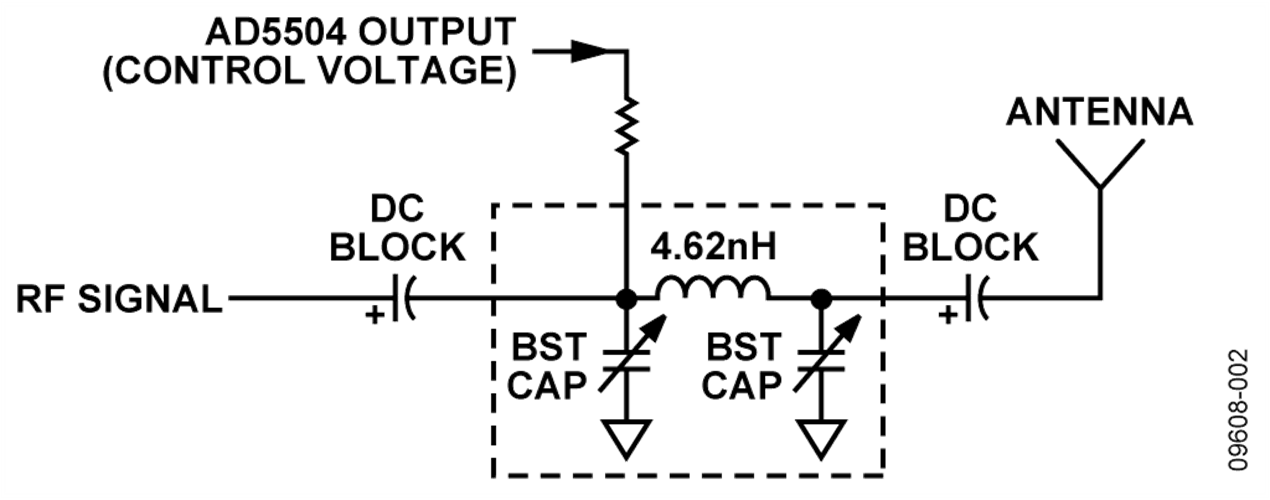

図1に示す回路は、高電圧信号を生成し、BST(バリウム・ストロンチウム・チタン酸塩)コンデンサの容量を制御することができます。BSTコンデンサの容量は、その端子に0V~30V間の電圧を印加することで可変できます。 これは誘電体の厚みを変化させることで、容量を変化させています。BSTコンデンサはアンテナ・アレイまたはチューナブル・フィルタ用としてよく用いられます。 以下のようなアプリケーションにおいて、チューニング動作させることが可能という、明らかな優位点があります。 例えば ・部品の許容誤差の補正 ・フィルタのカットオフ周波数の微調整 ・チューナブル・アンテナに関するネットワーク・インピーダンスのマッチング、 などが挙げられます。

このアプリケーションでは、高電圧電源を生成するにために、利便性、小型、低価格な回路が必要とされます、それは、このような機能だけのために、単に別電源を追加することが場合によっては実用的ではないためです。 図1の回路はADP1613 昇圧コンバータとAD5504、30V/60VDACを使うことで、これらの要求を満たすことが出来ます。昇圧レギュレータ回路の全体の基板面積は、わずか43mm2ですみます。 ADP1613は8ピンのMSOPパッケージで、AD5504は16ピンのTSSOP パッケージです。 この昇圧回路はLEDドランバのアプリケーションにも、またオプティカル通信システムにおける受信バイアス電圧供給にも使うことが出来ます。

回路説明

この回路は3V (VDD) 電源電圧で動作しますが、BSTコンデンサを完全に制御するためには、20Vを超える電圧が必要です。2つの回路ブロックは、ADP1613ステップアップ・スッチング・コンバータとAD5504高電圧DACから成り立っています。図1に回路図を示します。

ADP1613は、20Vもの高い電圧を出力する能力を持つ、パワー・スイッチを内蔵したステップアップDC/DCスイッチング・コンバータです。外部部品を追加することによって、更に高い電圧を発生することもできます。 ADP1613は調整可能なソフトスタート機能を備えており、デバイスがイネーブルになるときの突入電流を防ぐことができます。端子で設定可能なスイッチング周波数とPWM電流モード・アーキテクチャのため、ノイズのフィルタリングが容易で、優れたトランジェント応答が得られます。 ADP1613の周辺に接続された部品は、3V入力から32V出力を発生できます。

ADIsimPower™設計ツールにより、入力と出力要求に基づいて、適切な部品を容易に決定できます。 図1に示したADP1613の回路の設計は、入力電圧3V、出力電圧32V、負荷電流40mAで、ADIsimPowerの「最低価格」オプションを使用しました。この設計データは、www.analog.com/CN0193-PowerDesignからダウンロードすることができます。

ADIsimPowerの設計ファイルには、部品表(BOM)、詳細回路図、ボーデ線図、効率プロット、トランジエント応答、および推奨するボードのレイアウトが含まれています。

ADP1613からの32V出力は、AD5504の電源電圧として使われます。AD5504は、クワッド・チャンネルの最大出力電圧60Vの12ビットDACです。AD5504のフルスケール出力は、 R_SELピンによって設定されます。 ここでのアプリケーションでは、R_SEL はVDDに接続されており、30Vのフルスケール出力が選択されています。AD5504は3Vロジックに互換のシリアル・インターフェースで制御されます。DACの出力はシリアル・インターフェースを介して、適切なDACレジスタに書き込むことで変更されます。 4個のDACは、ロードDAC(LDAC)ピンをロー・レベルにすることによって、同時にアップデートされますので、4つのBSTコンデンサ全てを同時に変化させることができます。

図1に示した回路を用いることで、DAC出力電圧として最大30Vを生成することができます。この出力電圧は、BSTコンデンサのバイアス電圧を設定するために用いられ、これによりアンテナ応答を調整します。図2はチューナブル・マッチング・ネットワークとして使われるBSTコンデンサの等価回路です。 図3はバイアス電圧の関数としてのBSTコンデンサのグラフと、その結果として得られるアンテナ応答の伝達関数を示しています。BSTコンデンサについての更なる詳細は www.agilerf.comを参照してください。

高精度が重要になる回路では、ボード上の電源とグラウンド・リターンのレイアウトを注意深く行うことが重要です。この回路を実装するプリント基板(PCB)では、アナログ部とデジタル部を分離する必要があります。 AGNDとDGNDの接続が必要なデバイスがあるようなシステム内で使われる回路の場合には、この接続は1ヵ所で行う必要があります。グラウンド・ポイントはAD5504のできるだけ近くに配置する必要があります。 この回路は広い面積のグラウンド・プレーン層とパワー・プレーン層を持った、多層のプリント基板上に構築する必要があります。レイアウトとグラウンド設計の詳細については、チュートリアルMT-031を参照してください。

AD5504への電源は、10μFと0.1μFのコンデンサでバイパスする必要があります。コンデンサは物理的にデバイスのできるだけ近くに配置し、理想的には0.1μFのコンデンサはデバイスの真上に配置することが望まれます。 10μFコンデンサは、タンタルのビーズ型またはセラミック・タイプを使います。0.1μFコンデンサは、通常のセラミック型コンデンサのような、実効直列抵抗(ESR)が小さく、かつ実効直列インダクタンス(ESL)が小さいものを使う必要があります。 この0.1μFのコンデンサは、内部ロジックのスイッチングにより発生する、過渡電流に起因する高周波信号をグラウンドへ低インピーダンスで流す経路を実現できます。適切なデカップリング技術の詳細については、 チュートリアルMT-101を参照してください。

電源ラインはできるだけ太いパターンにしてインピーダンスを小さくし、電源ライン上のグリッチによる影響を軽減させるようにします。クロックとその他の高速スイッチング・デジタル信号は、デジタル・グラウンドを使ってボード上の他の部分からシールドする必要があります。 DIsimPowerによる設計ファイルには、この回路のADP1631部に関する推奨レイアウトが示されています。このファイルは、www.analog.com/CN0193-PowerDesignでダウンロードすることができます。 この回路ノートに関する完全な設計サポート・パッケージはhttps://www.analog.com/CN0193-DesignSupportで入手できます。

バリエーション回路

システムの必要に応じて、代替として他の昇圧レギュレータを使うことも出来ます。詳細については、設計ツールADIsimPower™を参照してください。

AD5501はAD5504のシングルチャネルバージョンです。

回路の評価とテスト

図1の回路は、VDDに3Vの電源電圧を与えてテストしました。このVDDからAD5504のための32V電圧が作りだされ(14番ピンで測定)、またAD5504のVLOGIC電圧にも供給されます。 マイクロコントローラ、DSPまたはFPGAを、AD5504へのデジタル・インターフェース信号を与えるために使います。

CLR は通常はハイ・レベルにする必要があります。 SYNC、SCLKとSDATAラインは、 AD5504のデータシートに記載されているように、AD5504の種々のレジスタにデータを書き込んで、動作させる必要があります。 LDACをロー・レベルにしたままでDACレジスタにデータを書き込むと、対応する出力は直ちにアップデートされます。 LDACをハイ・レベルにしたままでDACレジスタにデータを書き込むと、LDACがロー・レベルにされるまでは、DAC出力は従来の値を維持し続けます。