概要

設計リソース

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- Programmable window detector

- Single supply

- 4 seperate channels possible

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

CN-0182: 単電源、低消費電力、プログラマブル・ウィンドウ・ディテクタ2012/06/13PDF0

回路機能とその特長

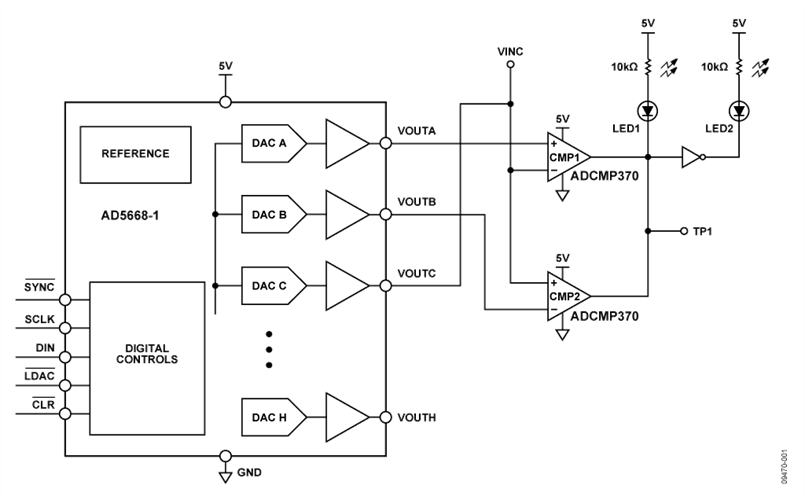

図 1に示す回路は上限、下限が設定可能な単電源、低消費電力、ウィンドウ・ディテクタ回路です。このタイプの回路は信号がプリセットした制限範囲から外れた時アラームを発生する回路に使用でき、検出や監視アプリケーションによく使われます。ウィンドウの制限値を設定するために、8チャンネル、低消費電力、16ビット、バッファ付き電圧出力DAC AD5668-1を使用します。AD5668-1は1.25 V、5 ppm/°C リファレンスを内蔵しているので出力範囲のフルスケールは0 V ~ 2.5 Vになります。内部リファレンスはソフトウェアで書き込む事によりイネーブルになります。AD5668-1と通信するためにはSPIインターフェースを使用します。

使用するコンパレータは入力オフセット電圧9 mVでオープン・ドレイン出力の汎用、低消費電力(20 μW typ@ 5 V)コンパレータ ADCMP370です。

回路説明

図 1の回路は上限電圧と下限電圧が設定可能なウィンドウ・ディテクタです。上限と下限はそれぞれ各DACレジスタにロードされます。回路の主なアプリケーションは外部信号が設定した制限値以内に入るかどうかテストする事です。

AD5668-1 は8チャンネルDACで、上限と下限はそれぞれチャンネルAの出力とチャンネルBの出力によって設定されます。

DAC Cはテスト用に信号入力を提供します。信号がDAC A とDAC Bによって設定された領域内に入った時、TP1の電圧はロジック1になって、LED1はオフになり、LED2はオンになります。信号が上限と下限によって設定されたウィンドウの外になった時、LED1はオンになりLED2はオフになります。

プルアップ・レジスタをADCMP370の出力に接続すれば、非反転入力が反転入力よりも大きい時その出力は5 Vになります;それ以外の場合には出力は0 Vになります。

ADCMP370はオープン・ドレイン出力なのでコンパレータC1とコンパレータC2の出力をワイアードAND接続できます。回路の真理値表を表1に示します。この例では、VOUTAが上限、VOUTBが下限で、VOUTA > VOUTBになります。

図 2に回路の動作が説明されています。DAC CはコンパレータのVINC(TP2/TESTC)入力を駆動する0 V ~ 2.5 Vの三角波を生成します。閾値はDAC A(VOUTA=2 V)とDAC B (VOUTB=1 V)によって設定されます。TP1の電圧はVINC電圧が2つの閾値の間にある時、ロジック1になります。

| VINC Level | Output CMP1 | Output CMP2 | Output CMP1 AND Output CMP2 | TP1 | LED1 | LED2 |

| VINC < VOUTB < VOUTA | 1 | 0 | 0 | 0 | On | Off |

| VINC > VOUTA > VOUTB | 0 | 1 | 0 | 0 | On | Off |

| VOUTB < VINC < VOUTA | 1 | 1 | 1 | 1 | Off | On |

回路の評価とテスト

必要な装置(同等の装置に変更可能)

- EVAL-SDP-CB1Z システム・デモ用プラットホーム

- CN-0182回路評価用ボード(EVAL-CN0182-SDZ)

- CN-0182 評価用ソフトウェア

- テクトロニクス TDS2024、4チャンネル・オシロスコープ

- HP-E3630A、0 V ~ 6 V、2.55 A;±20 V/0.5 A、トリプル出力DC電源

- PC(Windows® 32ビット又は64ビット)

始めてみよう

CN-0182評価用ソフトウェアCDをPCのCDドライブに入れて評価用ソフトウェアをロードしてください。マイコンピュータを使用して、評価用ソフトウェアのCDを含むドライブを見つけ、Readmeファイルを開いてください。

Readmeファイルに含まれているインストラクションに従って、評価用ソフトウェアをインストールし、使用してください。

機能ブロック図

図 3 はテスト・セットアップの機能ブロック図を示します。

セットアップ

EVAL-CN0182-SDZ回路ボードの120ピン・コネクタをEVAL-SDP-CB1Z評価用(SDP)ボードの「CON A」又は「CON B」コネクタに接続してください。120ピン・コネクタの末端にある穴を利用して2つのボードをしっかり固定するためにネジを使用してください。DC出力電源を正常に5 V、3.3 Vに設定した後、電源をオフにしてください。

電源オフの状態で、5V電源をJ1-1ピン(AVDD)に接続し、GNDをJ1-2 ピンとJ2-2ピン(それぞれAGND とDGND)に接続し、3.3 VをJ2-1ピン(VLOGIC)に接続してください。あるいは、SDPボードを介してUSBポートからデジタル回路に電源を供給するためにポジションBにLink 1を配置してください(デフォルト設定)。この場合は、VLOGICは必要ありません。

電源を投入した後にSDP基板のUSBケーブルをPCのUSBポートに接続してください。注意:EVAL-CN0182-SDZのDC電源を投入する前にUSBケーブルをSDPボード上のミニUSBコネクタに接続しないでください。

テスト

テスト装置をセットアップした後、オシロスコープのプローブをTP1、VOUTA、VOUTB、TP2/TESTCと記されたテスト・ポイントに接続してください。

ご提供するソフトウェアを使ってVOUTA とVOUTBの値を設定し、ウィンドウを設定する事ができます。デフォルト設定の状態であれば、図 2に示すようにVINCに三角波信号を形成するためにメインのソフトウェア・ウィンドウのtriangleを押してください。この信号の期間と振幅は変更できます。この信号はTP2/ TESTCテスト・ポイントで観察できます。1秒間が経ちVOUTA とVOUTBがそれぞれ2000 mV と1000 mVに安定すると、「回路の説明」セクションで説明したように、LEDはVINCの値が制限範囲内に出入りする時点滅します。AD5668-1 DACはVOUTA、VOUTB、VINCの最大値を2.5 Vに制限します。

リンク5をポジションAに配置する事によりVINピンに外部信号(VINC)を印加する事が可能になります。これはテスト・ポイントTP2で観察できます。さらに、出力はテスト・ポイントTP1で観察できます。

リンク1を挿入しない時、出力はVOUTAと比較したVINCの大きさによって変化します。

| ジャンパ | 記述 | 設定 | 機能 |

| LK1 | CコンパレータCMP1 とCMP2の出力の接続 | Inserted | CMP1出力とCMP2 出力はTP1で短絡されます。これはウィンドウ・コンパレータ回路です。 |

| Opened | 2つのCMP出力は短絡されません。CMP1はLEDのみに連結され、VINCはVOUTA(ハイレベル)とのみ比較されます。 | ||

| LK2 | デジタル電源の供給 | Position A | デジタル回路の電源はJ2-1ピン(VLOGIC)に接続した外部電源から供給されます。 |

| Position B | デジタル電源はSDPボードから供給されます;VLOGICピンに何も電圧を加える必要はありません。 | ||

| LK5 | VINC電圧の電圧源 | Position A | VINCはSDPによって設定され、TESTCテスト・ポイントで測定する事ができます。 |

| Position B | VINCはJ2-3ピン(VIN)を通じて外部電源(0V~5V)によって設定され、TP2テスト・ポイントで測定する事ができます。 |