概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- PADS Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CFTL-6V-PWRZ ($23.01) Wall Power Supply for Eval Board

- EVAL-CN0241-SDPZ ($79.98) High-Side Current Sensing with Input Overvoltage Protection

- EVAL-SDP-CB1Z ($134.00) EVAL Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- ±32 V 入力過電圧保護

- 5 V単電源で動作

- ハイサイド検出でグラウンドノイズを除去

- 低消費電力、一方向電流監視システム

参考資料

-

MT-068: Difference and Current Sense Amplifiers2016/05/13PDF244 kB

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-035: Op Amp Inputs, Outputs, Single-Supply, and Rail-to-Rail Issues2015/02/14PDF115 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

MT-036: Op Amp Output Phase-Reversal and Input Over-Voltage Protection2008/12/11PDF653 kB

-

CN-0241: 入力過電圧保護機能を備えたハイサイド電流検出2012/06/13PDF354 kB

-

AN-2571: 入力過電圧保護が施されたハイサイド電流検出2025/04/02

回路機能とその特長

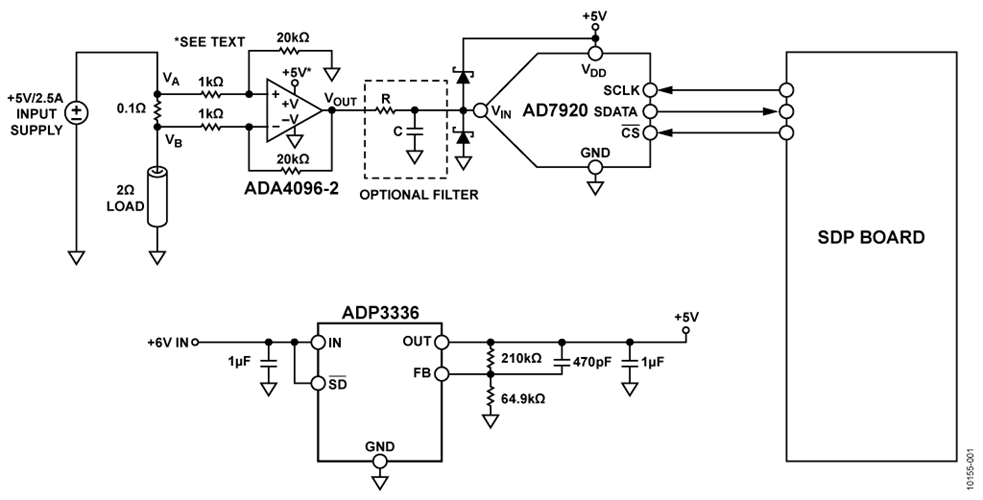

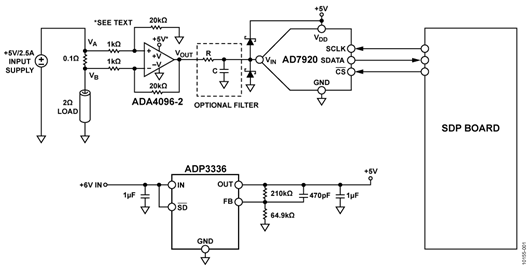

ハイサイド電流モニタには、トランジェントやモニタリング回路の接続、切断、パワーダウンによる過電圧状態が生じる可能性があります。図1に示す回路では、過電圧保護されたADA4096-2オペアンプがハイサイド電流をモニタするためのディファレンス・アンプとして接続されています。ADA4096-2は、電源レールの上下32Vの電圧に対して位相反転やラッチアップを起こさない入力過電圧保護機能を備えています。

この回路はADP3336可変低ドロップアウト500mAリニア電圧レギュレータから給電されます。また、このレギュレータは必要に応じてシステムの他のデバイスへの電力供給に使用することもできます。5V出力に設定されている場合、5.2V~12Vの入力電圧範囲が可能です。節電するため、ADP3336への電源を切り離すことによって電流検出回路をパワーダウンすることができますが、太陽電池パネルなどの電力源は引き続き動作する可能性があります。

これにより、電力が供給されないADA4096-2の入力に電圧が印加されますが、32Vまでの入力電圧でラッチアップや損傷が生じることはありません。遅いスループット・レートが必要な場合、サンプリングとサンプリングの間にAD7920をパワーダウンさせることもできます。AD7920の最大消費電力はパワーダウン時に5μW、パワーアップ時には15mWになります。ADA4096-2は動作状態で120μAしか必要としません。5Vで動作する場合、これはわずか0.6mWの消費電力です。シャットダウン・モード時、ADP3336に流れる電流はわずか1μAです。

図2. ADA4096-2の等価回路

この回路はADP3336可変低ドロップアウト500mAリニア電圧レギュレータから給電されます。また、このレギュレータは必要に応じてシステムの他のデバイスへの電力供給に使用することもできます。5V出力に設定されている場合、5.2V~12Vの入力電圧範囲が可能です。節電するため、ADP3336への電源を切り離すことによって電流検出回路をパワーダウンすることができますが、太陽電池パネルなどの電力源は引き続き動作する可能性があります。

図1. 入力過電圧保護機能を備えたハイサイド電流検出

(簡略回路図:全接続の一部およびデカップリングは省略されています)

これにより、電力が供給されないADA4096-2の入力に電圧が印加されますが、32Vまでの入力電圧でラッチアップや損傷が生じることはありません。遅いスループット・レートが必要な場合、サンプリングとサンプリングの間にAD7920をパワーダウンさせることもできます。AD7920の最大消費電力はパワーダウン時に5μW、パワーアップ時には15mWになります。ADA4096-2は動作状態で120μAしか必要としません。5Vで動作する場合、これはわずか0.6mWの消費電力です。シャットダウン・モード時、ADP3336に流れる電流はわずか1μAです。

図2. ADA4096-2の等価回路

回路説明

この回路は1本の検出抵抗を用いた従来型のハイサイド電流検出回路を構成しています。他の4本の抵抗(2組の1kΩと20kΩの分圧器)は、比率を一致させるために薄膜回路網に形成され、ディファレンス・アンプのゲインを設定するのに使用されます。このアンプは検出抵抗両端に生じる2つの電圧の差を増幅し、同相電圧を除去します。

ADA4096-2の等価回路を図2に示します。入力段は並列動作する2組の差動ペア(Q1~Q4とQ5~Q8)を構成しています。入力同相電圧がVCC − 1.5Vに近づくと、I1がその最小コンプライアンス電圧に達することによってQ1~Q4がシャットダウンします。逆に、入力同相電圧がVEE + 1.5Vに近づくと、I2がその最小コンプライアンス電圧に達することによってQ5~Q8がシャットダウンします。このトポロジーでは、アンプが室温時に電源レールから200mV外側の電圧の入力で作動することができるので、入力ダイナミック・レンジを最大にすることができます。

他のレールtoレール入力アンプと同様に、2組の入力ペア間のVOSの不整合によってアンプのCMRRが決まります。入力同相電圧の範囲が各電源レールの1.5V以内の場合、入力ペア間の遷移が回避されるので、CMRRが約10dBだけ改善されます。

ADA4096-2の入力は、各電源レールの32V外側までの入力電圧変動から保護されています。アンプへの電源が供給される前に信号源がアクティブになる可能性のある電源シーケンスの問題を抱えるアプリケーションでは、この機能は特に重要です。

ADA4096-2の低RDSON の内部直列FETによる入力電流制限能力(緑の線)と、5kΩの外付け直列抵抗と保護回路のないオペアンプを使った入力電流制限能力(赤の線)を比較したグラフを図3に示します。

図3. 入力電流の制限能力

図3は、ユニティ・ゲイン・バッファ構成のADA4096-2で、電源をGND(または±15V)に接続し、正側の入力を電源電圧を32V超える電圧まで掃引して得られたものです。通常、入力電流は正の過電圧状態で1mAに、負の低電圧状態では200μAに制限されます。たとえば、20Vの過電圧では、ADA4096-2の入力電流は1mAに制限され、20kΩの直列抵抗に相当する電流制限が行われます。

また、図3はアンプへの給電の有無に関係なく電流制限回路がアクティブであることも示しています。

図3は異常状態のときだけの入力保護を示しています。補正アンプの動作入力電圧範囲(IVR)は、ADA4096-2のデータシートの表2~表4で規定されています。

AD7920は12ビット、高速、低消費電力の逐次比較型A/Dコンバータです。このデバイスは、2.35V~5.25Vの単電源で動作し、最大250kSPSのスループット・レートを備えています。また、低ノイズ、広帯域幅のトラック&ホールド・アンプを内蔵しており、13MHzを超える入力周波数に対応可能です。

変換プロセスとデータ・アクイジションはCSとシリアル・クロック(SCLK)を使って制御されるため、このデバイスはマイクロプロセッサやDSPにインターフェースすることができます。入力信号は、CSの立下がりエッジでサンプリングされ、この時点で変換が開始されます。このデバイスに伴うパイプライン遅延はありません。

AD7920では高度な設計手法を使って、高いスループット・レートで非常に小さい消費電力を実現しています。

パワーダウン・モードにするには、SCLKの2番目の立下がりエッジの後から、SCLKの10番目の立下がりエッジの前までのどこかでCSをハイ・レベルにすることにより、変換プロセスを中断させる必要があります。SCLKのこの範囲内でCSがハイ・レベルになると、デバイスはパワーダウン・モードになり、CSの立下がりエッジで開始された変換は終了し、SDATAはスリー・ステートに戻ります。SCLKの2番目の立下がりエッジの前にCSがハイ・レベルになると、デバイスはノーマル・モードのままでパワーダウンしません。この機能により、CSラインのグリッチに起因する偶発的なパワーダウンを防止します。

この動作モードを終了してAD7920を再度パワーアップするために、ダミー変換を実行します。CSの立下がりエッジでデバイスはパワーアップを開始し、SCLKの10番目の立下がりエッジの後までCSがロー・レベルに保持されている限りパワーアップを続けます。16個のSCLKが経過するとデバイスは完全にパワーアップされ、次の変換から有効なデータが得られます。

SCLKの10番目の立下がりエッジの前にCSEAがハイ・レベルになると、AD7920は再度パワーダウン・モードに戻ります。これにより、CSEAライン上のグリッチや、CSEAがロー・レベルの間の8 SCLKサイクルの予期せぬバーストに起因する偶発的なパワーアップが防止されます。デバイスはCSEAの立下がりエッジでパワーアップを開始できますが、SCLKの10番目の立下がりエッジより前であれば、CSEAの立上がりエッジで再度パワーダウンします。

タイミングの詳細については、AD7920のデータシートを参照してください。

テスト結果

回路の性能を示す重要な指標は、最終出力電圧の測定値のノイズの大きさです。

10,000個の測定サンプルのヒストグラムを図4に示します。このデータは、 EVAL-SDP-CB1Z 評価ボードに接続されたCN-0241評価ボードを使って得られたものです。セットアップの詳細については「回路の評価とテスト」のセクションで説明します。

次に、ADP3336に接続されたSDシャットダウン・ピンをソフトウェアでロー・レベルにすることによってLDOの出力をオフにしました。約1分後にADP3336のシャットダウン・ピンをハイ・レベルにして出力をオンに戻すことで、同じ数のデータ・サンプルを収集しました。この収集結果を図5に示します。

図5は、入力がハイ・レベルに保たれていてパワーダウンしている間ADA4096-2の出力がラッチしなかったことを示しています。

この回路ノートに関する設計サポート・パッケージは、 www.analog.com/CN0241-DesignSupportで入手できます。

VOUT = (VA – VB) (20 kΩ/1 kΩ)

ADA4096-2の等価回路を図2に示します。入力段は並列動作する2組の差動ペア(Q1~Q4とQ5~Q8)を構成しています。入力同相電圧がVCC − 1.5Vに近づくと、I1がその最小コンプライアンス電圧に達することによってQ1~Q4がシャットダウンします。逆に、入力同相電圧がVEE + 1.5Vに近づくと、I2がその最小コンプライアンス電圧に達することによってQ5~Q8がシャットダウンします。このトポロジーでは、アンプが室温時に電源レールから200mV外側の電圧の入力で作動することができるので、入力ダイナミック・レンジを最大にすることができます。

他のレールtoレール入力アンプと同様に、2組の入力ペア間のVOSの不整合によってアンプのCMRRが決まります。入力同相電圧の範囲が各電源レールの1.5V以内の場合、入力ペア間の遷移が回避されるので、CMRRが約10dBだけ改善されます。

ADA4096-2の入力は、各電源レールの32V外側までの入力電圧変動から保護されています。アンプへの電源が供給される前に信号源がアクティブになる可能性のある電源シーケンスの問題を抱えるアプリケーションでは、この機能は特に重要です。

ADA4096-2の低RDSON の内部直列FETによる入力電流制限能力(緑の線)と、5kΩの外付け直列抵抗と保護回路のないオペアンプを使った入力電流制限能力(赤の線)を比較したグラフを図3に示します。

図3. 入力電流の制限能力

図3は、ユニティ・ゲイン・バッファ構成のADA4096-2で、電源をGND(または±15V)に接続し、正側の入力を電源電圧を32V超える電圧まで掃引して得られたものです。通常、入力電流は正の過電圧状態で1mAに、負の低電圧状態では200μAに制限されます。たとえば、20Vの過電圧では、ADA4096-2の入力電流は1mAに制限され、20kΩの直列抵抗に相当する電流制限が行われます。

また、図3はアンプへの給電の有無に関係なく電流制限回路がアクティブであることも示しています。

図3は異常状態のときだけの入力保護を示しています。補正アンプの動作入力電圧範囲(IVR)は、ADA4096-2のデータシートの表2~表4で規定されています。

AD7920は12ビット、高速、低消費電力の逐次比較型A/Dコンバータです。このデバイスは、2.35V~5.25Vの単電源で動作し、最大250kSPSのスループット・レートを備えています。また、低ノイズ、広帯域幅のトラック&ホールド・アンプを内蔵しており、13MHzを超える入力周波数に対応可能です。

変換プロセスとデータ・アクイジションはCSとシリアル・クロック(SCLK)を使って制御されるため、このデバイスはマイクロプロセッサやDSPにインターフェースすることができます。入力信号は、CSの立下がりエッジでサンプリングされ、この時点で変換が開始されます。このデバイスに伴うパイプライン遅延はありません。

AD7920では高度な設計手法を使って、高いスループット・レートで非常に小さい消費電力を実現しています。

パワーダウン・モードにするには、SCLKの2番目の立下がりエッジの後から、SCLKの10番目の立下がりエッジの前までのどこかでCSをハイ・レベルにすることにより、変換プロセスを中断させる必要があります。SCLKのこの範囲内でCSがハイ・レベルになると、デバイスはパワーダウン・モードになり、CSの立下がりエッジで開始された変換は終了し、SDATAはスリー・ステートに戻ります。SCLKの2番目の立下がりエッジの前にCSがハイ・レベルになると、デバイスはノーマル・モードのままでパワーダウンしません。この機能により、CSラインのグリッチに起因する偶発的なパワーダウンを防止します。

この動作モードを終了してAD7920を再度パワーアップするために、ダミー変換を実行します。CSの立下がりエッジでデバイスはパワーアップを開始し、SCLKの10番目の立下がりエッジの後までCSがロー・レベルに保持されている限りパワーアップを続けます。16個のSCLKが経過するとデバイスは完全にパワーアップされ、次の変換から有効なデータが得られます。

SCLKの10番目の立下がりエッジの前にCSEAがハイ・レベルになると、AD7920は再度パワーダウン・モードに戻ります。これにより、CSEAライン上のグリッチや、CSEAがロー・レベルの間の8 SCLKサイクルの予期せぬバーストに起因する偶発的なパワーアップが防止されます。デバイスはCSEAの立下がりエッジでパワーアップを開始できますが、SCLKの10番目の立下がりエッジより前であれば、CSEAの立上がりエッジで再度パワーダウンします。

タイミングの詳細については、AD7920のデータシートを参照してください。

テスト結果

回路の性能を示す重要な指標は、最終出力電圧の測定値のノイズの大きさです。

10,000個の測定サンプルのヒストグラムを図4に示します。このデータは、 EVAL-SDP-CB1Z 評価ボードに接続されたCN-0241評価ボードを使って得られたものです。セットアップの詳細については「回路の評価とテスト」のセクションで説明します。

電源を3.0Vに設定し、10,000個のデータ・サンプルをLDOの出力をオフすることなく、250kSPSの最大レートで収集しました。図4はこの収集結果を示しています。ピークtoピーク・ノイズは約2LSBで、約0.3LSB rmsに相当します。

図4. パワーダウン前の10,000サンプルに対するコードのヒストグラム

次に、ADP3336に接続されたSDシャットダウン・ピンをソフトウェアでロー・レベルにすることによってLDOの出力をオフにしました。約1分後にADP3336のシャットダウン・ピンをハイ・レベルにして出力をオンに戻すことで、同じ数のデータ・サンプルを収集しました。この収集結果を図5に示します。

図5. パワーダウン後の10,000サンプルに対するコードのヒストグラム

図5は、入力がハイ・レベルに保たれていてパワーダウンしている間ADA4096-2の出力がラッチしなかったことを示しています。

この回路ノートに関する設計サポート・パッケージは、 www.analog.com/CN0241-DesignSupportで入手できます。

バリエーション回路

この回路は、優れた安定性と精度で動作することが実証されています。このボードはSDP-Sコントローラ・ボード(EVAL-SDP-CS1Z)とも互換性があります。

図1の回路をわずかに変更することにより、30Vまでの入力電源電圧に対する電流のモニタリングが可能になります。ADA4096-2の+VピンをADP3336から得られる5Vに接続する代わりに、モニタ対象の入力電源に直接接続します。この構成の場合、ADA4096-2は入力電源から直接給電されます。

図1の回路をわずかに変更することにより、30Vまでの入力電源電圧に対する電流のモニタリングが可能になります。ADA4096-2の+VピンをADP3336から得られる5Vに接続する代わりに、モニタ対象の入力電源に直接接続します。この構成の場合、ADA4096-2は入力電源から直接給電されます。

回路の評価とテスト

この回路は、 EVAL-CN0241-SDPZ 回路ボードと EVAL-SDP-CB1Z-SDP-B コントローラ・ボードを使用します。2枚のボードは120ピンのコネクタ(Mating Connector) を備えているので、短時間で組み立てて回路の性能を評価することができます。EVAL-CN0241-SDPZボードにはこの回路ノートに示す評価対象回路が含まれており、SDP-Bコントローラ・ボードはCN0241評価用ソフトウェアとともに使用して、EVAL-CN0241-SDPZ回路ボードからのデータを取り込みます。

必要な装置

以下の装置が必要です。

評価開始にあたって

CN0241評価用ソフトウェアCDをPCのCDドライブにセットして評価用ソフトウェアをロードします。マイコンピュータから評価用ソフトウェアCDを挿入したドライブを探します。

機能ブロック図

回路ブロック図についてはこの回路ノートの図1を、回路図についてはファイルEVAL-CN0241-SDPZ-SCH-RevA.pdfをご覧ください。このファイルは、CN0241設計サポート・パッケージ( CN0241 Design Support Package)に含まれています。

セットアップ

テスト

EVAL-CN0241-SDPZ回路ボードに接続された6V電源(またはACアダプタ)をオンにします。評価用ソフトウェアを起動し、PCからのUSBケーブルをSDP-BボードのミニUSBコネクタに接続します。

USBによる通信が確立されると、SDP-Bボードを使ってEVAL-CN0241-SDPZボードとの間のシリアル・データの送受信およびキャプチャを行うことができます。

データ収集の準備ができたら5V/2.5AのDC電源をオンします。測定に必要な電流量の出力に応じて電圧出力を調整します。

CN0241 SDP評価用ソフトウェアのインターフェースのスクリーンショットを図6に、EVAL-CN0241-SDPZ評価ボードのスクリーンショットを図7に示します。SDP-Bボードについては、SDP-Bユーザー・ガイド SDP-B User Guide を参照してください。

必要な装置

以下の装置が必要です。

- USBポート付きPCおよびWindows® XP、Windows Vista® またはWindows® 7(32ビット)

- EVAL-CN0241-SDPZ回路評価ボード

- EVAL-SDP-CB1Z SDP-Bコントローラ・ボード

- CN0241 SDP評価用ソフトウェア

- 6V/1Aを駆動可能なDC電源

- 5V/2.5Aを駆動可能なDC電源

- 2Ω/12Wの負荷抵抗

評価開始にあたって

CN0241評価用ソフトウェアCDをPCのCDドライブにセットして評価用ソフトウェアをロードします。マイコンピュータから評価用ソフトウェアCDを挿入したドライブを探します。

機能ブロック図

回路ブロック図についてはこの回路ノートの図1を、回路図についてはファイルEVAL-CN0241-SDPZ-SCH-RevA.pdfをご覧ください。このファイルは、CN0241設計サポート・パッケージ( CN0241 Design Support Package)に含まれています。

セットアップ

EVAL-CN0241-SDPZ回路ボードの120ピン・コネクタをEVAL-SDP-CB1Zコントローラ(SDP-B)ボードのCON Aコネクタに接続します。120ピン・コネクタの両端にある穴を利用し、ナイロン製の固定用部品を使って2枚の基板をしっかりと固定します。電源をオフにして、6V電源をボードの+6VピンとGNDピンに接続します。6VのACアダプタがある場合は、ボード上のACアダプタ用ジャックに接続して、6V電源の代わりに使用することができます。SDP-Bボードに付属しているUSBケーブルをPCのUSBポートに接続します。このとき、USBケーブルをSDPボードのミニUSBコネクタに接続しないでください。

5V/2.5AのDC電源をEVAL-CN0241-SDPZボードのJ1コネクタの+VINとGNDに接続します。2Ω/12Wの負荷抵抗をEVAL-CN0241-SDPZボードのLOADとGNDに接続します。テスト

EVAL-CN0241-SDPZ回路ボードに接続された6V電源(またはACアダプタ)をオンにします。評価用ソフトウェアを起動し、PCからのUSBケーブルをSDP-BボードのミニUSBコネクタに接続します。

USBによる通信が確立されると、SDP-Bボードを使ってEVAL-CN0241-SDPZボードとの間のシリアル・データの送受信およびキャプチャを行うことができます。

データ収集の準備ができたら5V/2.5AのDC電源をオンします。測定に必要な電流量の出力に応じて電圧出力を調整します。

CN0241 SDP評価用ソフトウェアのインターフェースのスクリーンショットを図6に、EVAL-CN0241-SDPZ評価ボードのスクリーンショットを図7に示します。SDP-Bボードについては、SDP-Bユーザー・ガイド SDP-B User Guide を参照してください。

図6. CN-0241 SDP評価用ソフトウェアのインターフェース

図7. SDPボードに接続されたEVAL-CN0241-SDPZ評価ボード