高精度、超低消費電力のハイサイド電流検出

はじめに

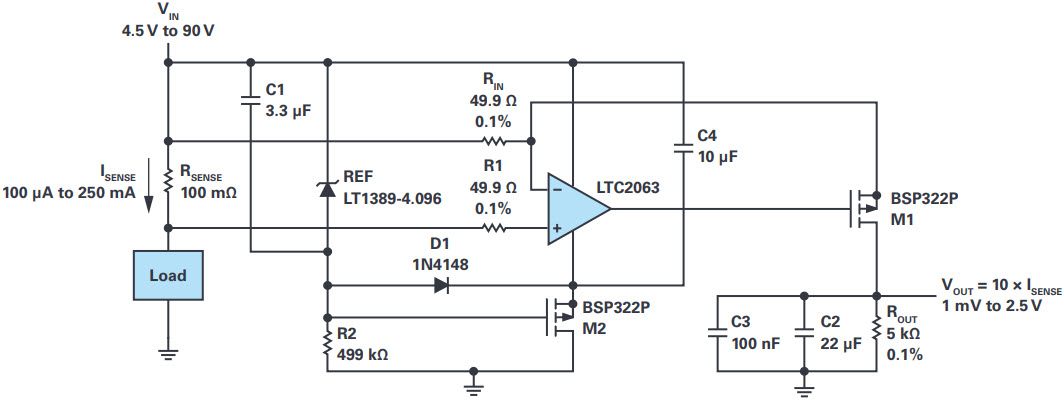

マイクロアンペア電流のハイサイド測定を高い精度で行うには、値の小さい検出抵抗と低オフセットの電圧アンプが必要です。LTC2063ゼロドリフト・アンプの最大入力オフセット電圧は5μV、消費電流は1.4µAです。これはいずれも非常に小さい値で、図1に示すような全機能内蔵型の超低消費電力、高精度のハイサイド電流検出回路の構成に最適です。

図1 LTC2063ゼロドリフト・アンプをベースとした高精度ハイサイド電流検出回路。

この回路が、100µA~250mAという広いダイナミック・レンジの電流検出に使用する電源電流は、2.3µA~280µAにすぎません。LTC2063はオフセットが極めて小さいため、わずか100mΩのシャント抵抗でこの回路を作動させることができ、最大シャント電圧は25mVという低い値に抑えられます。これによりシャント抵抗での電力損失が最小限に抑えられるので、最大限の電力を負荷に使用することができます。LTC2063のレールtoレール入力は、この回路を極めて小さい負荷電流で動作させることができますが、その際の入力同相電圧はレール電圧にほぼ一致します。内蔵のEMIフィルタは、ノイズの多い条件下でもRF干渉からデバイスを保護します。

所定の検出電流に対するこの回路の電圧出力は、次式で与えられます。

ゼロ・ポイント

電流検出ソリューションの重要な仕様の1つがゼロ・ポイント、つまり検出電流が存在しない場合の生成出力に対する入力時の等価誤差電流です。ゼロ・ポイントは、一般に、アンプの入力オフセット電圧をRSENSEで除した値によって決まります。LTC2063は、オフセット電圧が代表値で1µV、最大値で5µV、入力バイアス電流とオフセット電流が代表値で1pA~3pAと、いずれも非常に小さいので、ゼロ・ポイント入力換算誤差電流を代表値でわずか10µA(1µV/0.1Ω)、最大値で50µA(5µV/0.1Ω)に抑えることができます。このように誤差が小さいことから、図2に示すように、検出回路はその指定範囲の最小電流値(100µA)まで直線性を維持し、分解能の喪失によるプラトーが生じることはありません。入力電流と出力電圧の関係を示すプロットは、全電流検出範囲にわたって直線です。

図2 ISENSE = 100μAまでの下限部分にプラトーがありません。

ゼロ・ポイント誤差のもう1つの発生源が、出力PMOSのゼロ・ゲート電圧ドレイン電流(IDSS)です。これは、PMOSが見かけ上オフになっているときに(¦VGS¦ = 0)、ゼロ以外のVDSに対して発生する寄生電流です。MOSFETのリーク電流IDSSが大きい場合は、ISENSEが存在しない状態でもVOUTはゼロ以外の正の値を示します。

この設計に使われているトランジスタはInfineonのBSP322Pで、¦VDS¦ = 100VにおけるIDSSの上限値は1µAです。このアプリケーションにおいて、室温でVDS = –7.6Vという条件下で見込まれるBSP322PのIDSS(代表値)の値はわずか0.2nAであり、0Aの入力電流測定時の出力誤差は1µV、つまり入力電流誤差にして100nAにすぎません。

アーキテクチャ

LT1389-4.096リファレンスは、M2、R2、およびD1で構成されるブートストラップ回路と共に、超低消費電力の絶縁型3Vレール(4.096 V + M2のVTH、代表値–1V)を確立し、電圧が5.5Vの絶対最大電源電圧に達することがないようLTC2063を保護します。直列抵抗でも十分にバイアス電流を確立させることができますが、トランジスタM2を使用すると、全体としてはるかに高い電源電圧を使用しながら、電源範囲の上限で電流消費をわずか280µAに抑えることができます。

精度

LTC2063の入力オフセット電圧は、入力換算電流誤差を10µA(代表値)に固定する一助となっています。フルスケール入力が250mAの場合、このオフセットによる誤差は0.004%にすぎません。下限側では100µAに対し10µAで、10%の誤差となります。オフセットは一定なので補正できます。図3は、LTC2063、マッチングされていない寄生熱電対、およびあらゆる寄生直列入力抵抗による合計オフセットが2µVに止まることを示しています。

図3 ISENSE全範囲における最小電源4.5VでのVINからVOUTへの変換。出力オフセットが200.7µVであるということは、100.05V/V の電圧利得で割った場合のRTI入力オフセットが2µVであることを意味します。

図3に示す利得100.05V/Vは、回路構成時におけるROUTとRINの実測値から得られる予想利得(4.978kΩ/50.4Ω = 98.77V/V)より1.28V/V高い値になっています。この誤差は、LTC2063の入力とRSENSE間の約500mΩの寄生直列抵抗によるものと考えられます。

この回路の出力における不確実性の主な要因はノイズなので、ノイズ帯域幅を減らし、更にそれによって合計積分ノイズを減らすには、大きい並列コンデンサによるフィルタリングが極めて重要です。1.5Hzの出力フィルタを使用した場合、LTC2063には約2µVp-pの低周波入力換算ノイズが新たに発生します。ノイズに起因する誤差は、できるだけ長い時間を取って出力を平均することによって更に減らすことができます。

この電流検出回路におけるその他の誤差要因としては、LTC2063入力のRSENSEと直列の寄生基板抵抗、利得設定抵抗RINとROUTの抵抗値の許容誤差、利得設定抵抗の温度係数の不一致、および寄生熱電対によるオペアンプ入力の誤差電圧などがあります。上記のうちの最初の3つの誤差源は、ケルビン・センス型の4ピン検出抵抗をRSENSEに使用し、これと同等以下の温度係数を持つ0.1%抵抗をクリティカル利得設定経路であるRINとROUTに使用することによって、最小限に抑えることができます。オペアンプ入力における寄生熱電対を相殺するには、RINと同じ金属端子をR1に使用する必要があります。また、入力における温度勾配は、できるだけ非対称とならないようにしてください。

この項で検討したすべての誤差要因が全体に占める割合は、図4に示すように、2.5Vのフルスケール出力に対し最大で1.4%程度です。

図4 全指示範囲で1.4%未満の誤差率を維持。

電源電流

LT1389-4.096とLTC2063に必要な最小電源電流は、図5に示すように、最小VSUPPLY とISENSE(4.5Vと100µA)で2.3µA、最大VSUPPLY とISENSE(90Vと250mA)で最大280µAです。能動部品が消費する電流に加えて、M1に流れる出力電流IDRIVEもVSUPPLYから供給する必要があります。この電流は出力電圧に比例し、範囲は200nA(1.0mV出力時、ISENSE = 100µA)から500µA(2.5V出力時、ISENSE = 250mA)までです。したがって、ISENSEにこれらの値を加えた合計電源電流の範囲は2.5µA~780µAとなります。適切なA/Dコンバータ(ADC)駆動値が得られるよう、ROUTは5kΩに設定されます。

図5 電源電流は電源電圧と共に増加しますが、280μAを超えることはありません。

入力電圧範囲

このアーキテクチャにおける最大電源電圧は、PMOS出力が耐えることのできる最大¦VDS¦によって設定されます。BSP322Pの定格値は100Vなので、動作限界としては90Vが適切な値です。

出力範囲

この設計は5kΩの負荷を駆動できるため、多数のADCを駆動する段に適しています。出力電圧範囲は0V~2.5Vです。LTC2063の出力はレールtoレールなので、最大ゲート駆動能力を制限するものはLTC2063のヘッドルームだけです。この設計における最大ゲート駆動電圧は3V(代表値)で、これは、LT1389-4.096の4.096VにM2のVTHである–1V(代表値)を加えることによって設定されます。

この回路の出力は電圧ではなく電流なので、グラウンドまたはリードのオフセットが精度に影響することはありません。したがって、出力PMOS M1とROUTの間に長いリードを使用し、RSENSEを検出電流の近くに、ROUTをADCおよびそれに続くその他のシグナル・チェーン段の近くに置くことができます。長いリードの欠点は、EMIの影響を受けやすくなることです。ROUTと並列に配置した100nFのC3は、有害なEMIを分離して次段の入力に入り込むのを防ぎます。

速度制限

LTC2063の利得帯域幅積は20kHzなので、この回路は20Hz以下の信号の計測に使用することを推奨します。負荷と並列に配置された22µFのC2は、出力ノイズを1.5Hzにフィルタして精度を向上させ、後続段を突然の電流サージから保護します。このフィルタリングのトレードオフはセトリング時間が長くなることで、特に、入力電流範囲の下限付近ではその傾向が強くなります。

まとめ

LTC2063の極めて小さい入力オフセット電圧、小さいIOFFSETとIBIAS、そしてレールtoレール入力は、100μA~250mAの全範囲にわたって高精度の電流測定を可能にします。その最大電源電流は2µAであり、動作範囲のほとんどにおいて、最大値の280µAよりもはるかに少ない電流で回路を駆動することができます。LTC2063は電源電圧条件が低く、電源電流も小さいので、ヘッドルームに余裕のある電圧リファレンスから電源を供給することが可能です。