AN-2615: GMSL2 からGMSL3 へのアップグレード

概要

本稿では、既存のGMSL2™ 設計からGMSL3™ 設計へとアップグレードする際に必要な設計上の考慮事項を説明します。具体例として、GMSL2 センサー・ペアのMAX96717 とMAX96716A、およびピン互換のGMSL3 センサー・ペアであるMAX96793 とMAX96792A を使用します。ここでは、GMSL2 からGMSL3 にアップグレードするための設計上の考慮事項と共に、GMSL3 の利点についても説明します。

はじめに

GMSL™ 技術の主な利点の1 つが、世代が異なるデバイス間での互換性です。GMSL2 はGMSL1™ との、GMSL3 はGMSL2 との後方互換性を備えています。個々の製品の互換性についてはデータシートを確認してください。互換性のある部品に対して設計を再利用できるよう同じピン配置とパッケージを維持することで、この柔軟性は時間の節約にもつながります。

GMSL3 の概要

GMSL3 における主な相違点は、リンク上でのGMSL のデータ・レートが12Gbps まで倍増していることです。通常、ほとんどのアプリケーションに対してGMSL2 でも十分ですが、センサーやディスプレイの帯域幅は増え続けています。GMSL3 は、アダプティブ・イコライゼーション(AEQ)、ASIL-B の機能安全、堅牢なエラーの監視・診断機能といったGMSL の利点をすべて保持したままで、このような高データ・レートを達成することを目的としています。

GMSL2 は、非ゼロ復帰(NRZ)変調を使用しており、ナイキスト周波数は伝送データ・レートの半分になります。これは、6Gbps のリンクでは3GHz に相当します(3Gbps のリンクでは1.5GHz)。NRZ 変調を使用しながらデータ・レートが倍になると、12Gbps のリンクでは6GHz になります。しかし、このような高周波数を使用すると、ケーブル、コネクタ、PCB などにより大きな挿入損失が発生するため、アプリケーションの総ケーブル長を短くする必要がある、といった欠点があります。

データ・レートを倍増させても周波数が高くならないように、GMSL3 では4 値パルス振幅変調(PAM4)を活用し、GMSL2 と同じナイキスト周波数を維持しています。チャンネルの動作周波数を低くすると、システムは多くの利点が得られます。

- GMSL2とGMSL3が同じクロック・リンク・レートを使用することで、回路図とレイアウトを再利用し、FR-4のPCBで動作させることができます。

- ケーブルおよびコネクタ上の挿入損失が低くなります。

- 帯域幅を倍にして、同じリンク・レートを維持することにより、スペクトル効率を高めることができます。

GMSL3は、6GbpsのNRZと12GbpsのPAM4の両方をサポートしています。

設計上の考慮事項

例を示すため、MAX96793 をCSI-2 からGMSL3 へのシリアライザ、MAX96792A をGMSL3 からCSI-2 へのデシリアライザとします。一般的には、変更は最小限で済みますが、システムのアプリケーションごとに確認する必要があります。

ピン互換性

GMSL2 世代とGMSL3 世代のGMSL デバイスは、設計を再利用できるようにピンの互換性を備えた設計がなされています。シリアライザのパッケージは、5mm × 5mmのTQFN デバイスです。図1 にMAX96717 とMAX96793 のピン配置を示します。

これらのデバイスに搭載されたリファレンス・オーバー・リバース・クロッキング(RoR)機能を使用する場合、20nF±10%のコンデンサをVREFピン(ピン7)とグラウンドの間に接続します。RoR を使用する場合、逆方向リンクの適切なマージンを保つため、GMSL3 モードではこの接続が必要ですが、GMSL2 モードでは任意です。

GMSL3 でRoR を使用しない場合は、このコンデンサは不要です。

デシリアライザのパッケージは、7mm × 7mmのTQFN デバイスです。図2 にMAX96716A とMAX96792A のピン配置を示します。

消費電力

これらのデバイスの消費電力は、表1 のConfiguration 欄に記載されているように、物理層インターフェースの動作性能をフルに使用して特性評価されています。

| DEVICE | CONFIGURATION | IDD18 | IDD (VDD = 1.2V) | PTOTAL |

| MAX96717 | 6Gbps Forward Link Rate (GMSL2 Mode) RGB888 Color Bar Pattern 4-lane CSI-2 DPHY input 1.3Gbps per lane |

46mA (25°C) 53mA (105°C) |

98mA (25°C) 232mA (105°C) |

~210mW (25°C) ~393mW (105°C) |

| MAX96793 | 12Gbps Forward Link Rate (GMSL3 Mode) RGB888 Color Bar Pattern 4-lane CSI-2 DPHY input 2.5Gbps per lane |

46mA (25°C) 53mA (105°C) |

170mA (25°C) 340mA (105°C) |

~301mW (25°C) ~529mW (105°C) |

両デバイスは、電源トポロジに必要な条件を簡略化するため、同じ電源レール電圧を使用しています。VDD18 レールは、MAX96717 とMAX96793のGMSLデバイス・ファミリ両方で同じ電力を使用します。VDDコア・レールの最大電流には、約70mA(25ºC)または110mA(105ºC)のわずかな電流増加が生じます。電源ソースを調べ、この電流増加に対応できるだけのマージンがレールにあることを確認してください。

前述したように、これらのデバイスは物理層インターフェースの性能をフルに使用するよう設定することで特性評価されています。すなわち、デシリアライザはGMSL 入力の両方とMIPI-CSI2 出力の両方を使用することになります。両デバイスを単一のGMSL 入力や単一のMIPI-CSI2 出力と共に使用することで総消費電力を削減できます。

また、カメラのデシリアライザ・デバイスはMIPI-CSI2 PHY 用にMIPI-CSI2 電源レールVTERMを備えています。

| DEVICE | CONFIGURATION | IDD18 | IDD (VDD = 1.2V) | ITERM | PTOTAL |

| MAX96716A | 6Gbps Forward Link Rate (GMSL2 Mode) 2x 6Gbps inputs 2x 4-Lane CSI-2 DPHY inputs 1.3Gbps per lane |

196mA (25°C) 245mA (105°C) |

197mA (25°C) 460mA (105°C) |

27mA (25°C) 40mA (105°C) |

~654mW (25°C) ~1095mW (105°C) |

| MAX96792A | 12Gbps Forward Link Rate (GMSL3 Mode) 2x 12Gbps inputs 2x 4-Lane CSI-2 DPHY inputs 2.5Gbps per lane |

210mA (25°C) 250mA (105°C) |

365mA (25°C) 850mA (105°C) |

31mA (25°C) 40mA (105°C) |

~898mW (25°C) ~1596mW (105°C) |

両デバイスは、電源トポロジの条件を簡略化するため、同じ電源レール電圧を使用しています。VDD18 レールは、MAX96716A とMAX96792A のGMSL デバイス・ファミリ両方で同じ電力を使用します。VDD コア・レールの最大電流には、約160mA(25ºC)または約390mA(105ºC)の電流増加が生じます。電源ソースを調べ、この電流増加に対応できるだけのマージンがレールにあることを確認してください。

また、両ファミリに対して同じシステム条件を保つため、静止電流、および電源ノイズの最大許容値は両デバイスで同じです。

設定ピンの設定値

これらのデバイスの設定ピンにはわずかな違いしかありません。ブートアップされるたびに設定ピンの値によってデバイスの設定が決定されるため、設定値をデバイスのデータシートで確認することが重要です。

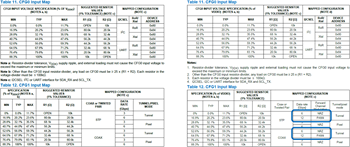

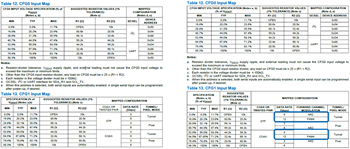

図3 と図4 に設定ピンの詳細を示します。説明のため、MAX96717 とMAX96793 について具体的に示します。すべての設定ピンの設定値はデバイスに固有のもので、詳細はそれぞれのデバイスのデータシートに記載されています。

設定0 ピン(CFG0)は、UART またはI2C の通信チャンネル・インターフェース選択、RoR または水晶発振器の選択、およびデバイス・アドレスの設定に使用します。

設定1 ピン(CFG1)は、STP または同軸のケーブル・タイプ選択、GMSL のデータ・レート、およびトンネル・モードかピクセル・モードかを設定します。GMSL データ・レートの設定値に関して、CFG1 にわずかな違いがあります。ピクセル・モードのデータ・レートは両デバイスで同じです。トンネル・モード動作に関しては、GMSL3 が6Gbps と12Gbps、GMSL2 が3Gbps と6Gbps をサポートしています。

PAM4 変調方式

PAM4 は、厳しいオートモーティブ環境用にGMSL が使用する既存の変調方式です。NRZ が2 つの電圧レベルを使用して1 ビット・シンボルを表すのに対して、PAM4 は4 つの電圧レベルで2 ビット・シンボルを表します。これにより、GMSL3 はGMSL2 と同じボー・レートで動作しながら、伝送されるデータのビット・レートを倍にできます。

ただし、データ・レートを倍増することによる影響が何もないということではありません。トレードオフとして、PAM4 のアイ開口部は、NRZ のアイ開口部の約1/3 という小さなものになります。

図5 で、「A」がNRZ のアイ開口部と定義されています。これは、NRZ が1 周期あたり1 ビット(1/T)をA のSN 比で伝送する場合、PAM4 は1 周期あたり2 ビット(2/T)をA/3 のSN 比で伝送することを意味します。

フォワード・エラー・コレクション

PAM4 が持つこのノイズに対する敏感さを解決するため、GMSL3 には、フォワード・エラー・コレクション(FEC)が採用されており、リンクにデータの冗長性とエラー訂正機能が追加されています。FEC はSN 比の条件を大きく軽減することができ、リンクのビット・エラー・レート(BER)をGMSL リンクの寿命期間に対して実質的に1 ビット・エラーまで減少させることができます。

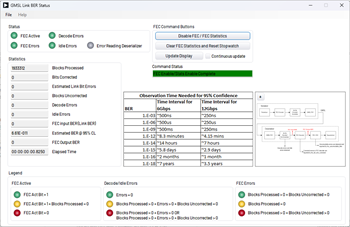

GMSL のFEC は、CD やQR コードの他、宇宙船ボイジャーにも採用された、リードソロモン・エンコーディングを使用しています[1]。また、このFEC 情報はレジスタによってリアルタイムでモニタできます。また、GMSL のGUI を使用しても容易にモニタできます。

FEC はGMSL3 の動作に必須のため、ユース・ケースが十分な帯域幅を持っていることを確認する場合には、帯域幅へのFEC の影響を考慮に入れる必要があります。FEC を使用してBER の堅牢性を強化する場合、GMSL リンク上ではFEC により6.67%(128/120)が追加で消費されます。GMSL GUI のGMSL 帯域幅計算機は、このオーバーヘッドを含めて計算します。このオーバーヘッドは、GMSL3 リンク上で使用可能な帯域幅の約9.7Gbps に相当します。

エラーのレポート

GMSL3 リンクでFEC を使用する場合、システムのモニタリング条件に基づいてエラー・モニタの考え方を変える必要があります。FECはリンク上で発生する可能性のあるエラーの検出と訂正が可能なため、デバイスが訂正をレポートすることによりFEC 訂正可能ビットがあることが分かります。FECで訂正不可能なビットは許容されません。これは、GMSL3 デバイスがリンクで既に発生したエラーを訂正できないことを示しています。

結果的に、エラー・モニタリングは、何をエラーと考えるかに合わせて対応する必要があります。GMSL2 モードでは、デコード・エラーとアイドル・エラーを使用してリンクでエラーが発生したことをレポートします。GMSL3 モードでは、FECで訂正不可能なエラーを使用して、リンクでエラーが発生したことをレポートします。また、FEC で訂正されたビットもレポートされます。

デフォルトでは、FEC エラー・フラグが、訂正可能なビットと訂正不可能なビットをチェックしてERRB ピンにレポートします。訂正可能なビットに対するFEC 閾値は、システム条件に合うよう調整する必要があります。エラー・モニタの変更点については、ソフトウェアの違いのセクションに詳細が記載されています。

チャンネルの仕様

GMSL2 とGMSL3 の間で大きく変更されたのは、GMSL のチャンネル仕様です。GMSL3 のチャンネル仕様は厳しいバジェットが設定されているため、GMSL2 準拠のシステムがGMSL3 のチャンネル仕様と互換性を有していると考えてはいけません。GMSL2 およびGMSL3 の最新のチャンネル仕様をanalog.com から入手して参照してください。

設計を再利用する場合には、PCB レイアウトと配線に必要な条件を再評価することが重要です。

GMSL3(12Gbps)とGMSL2(6Gbps)は両方ともリンクの基本周波数である3GHz で動作します。

GMSL3 では、長いチャンネル(高損失)と短いチャンネル(低損失)の両方に対して、挿入損失の要件が追加で仕様規定されています。短いチャンネルはより厳しい挿入損失(IL)が規定されていますが、リターン・ロス(RL)は緩和されています。

GMSL3 では、長いチャンネル(高損失)と短いチャンネル(低損失)の両方に対して、リターン損失の要件も追加で仕様規定されています。短いチャンネルはRL が緩和されていますが、IL が厳しくなっています。

S パラメータ・データは、GMSL3 IL およびRL の制限値と比較する前にフィルタリングする必要があります。100MHz のフィルタをS パラメータの全範囲に適用します。取得した最も低い周波数から50MHz まではフィルタリングされていないデータを使用し、50MHz 以降はフィルタリングされたデータを使用して制限値と比較します。

レジスタ設定値の違い

これらのデバイスの間には主に2 つのソフトウェア上の違いがあります。GMSL3 モードの動作とエラー・モニタリングです。

GMSL3 モードにするには、表3 と表4 に示すすべての変更をCFG ピンを通じて行います。これらのピンを使用することで、デバイスの送受信速度とPAM4 変調を正しく設定できます。CFG ピンをソフトウェアで設定、もしくは上書きする場合のために表3 と表4 にはレジスタも示していますが、通常、この方法は推奨しません。

注:CFG ピンを使用してGMSL モードを設定する場合には、表3 と表4 を用いた以下の変更は必要ありません。

設定手順は、決められた順番で行う必要があります。リモート・デバイスから始め、その後にローカル・デバイスを変更します。リモートかローカルかは、I2Cコントローラの位置を基準に定義しています。ローカル・デバイスの設定時には、リモート・デバイスとの通信ができなくなります。この例では、MAX96793 がリモート・デバイスでMAX96792A(I2C コントローラと接続されている)がローカル・デバイスです。

| STEP | LOCATION | DEVICE | DESCRIPTION | REGISTER | VALUE |

| 1 | Remote | MAX96793 | Change Tx rate to 12Gbps | 0x0001 | REG1[3:2] = 0b11 |

| 2 | Remote | MAX96793 | Enable FEC | 0x0028 | TX0[1] = 0b1 |

| 3 | Remote | MAX96793 | Disable GMSL2 mode and enable GMSL3 mode | 0x0006 | REG6[7] = 0b0 |

| 4 | Local | MAX96792A | Hold the GMSL link in RESET | 0x0010 | CTRL0[6] = 0b1 |

| 5 | Local | MAX96792A | Change Rx rate to 12Gbps | 0x0001 | REG1[1:0] = 0b11 |

| 6 | Local | MAX96792A | Enable FEC | 0x0028 | TX0[1] = 0b1 |

| 7 | Local | MAX96792A | Disable GMSL2 mode and enable GMSL3 mode | 0x0004 | REG4[7:6] = 0b11* |

| 8 | Local | MAX96792A | Release the GMSL link from RESET | 0x0010 | CTRL0[6] = 0b0 |

| *これによりGMSL3 とのリンクの両方が設定されます。各リンクは個別に設定できます。 | |||||

| STEP | LOCATION | DEVICE | DESCRIPTION | REGISTER | VALUE |

| 1 | Remote | MAX96793 | Change Tx rate to 6Gbps | 0x0001 | REG1[3:2] = 0b10 |

| 2 | Remote | MAX96793 | Disable FEC | 0x0028 | TX0[1] = 0b0 |

| 3 | Remote | MAX96793 | Enable GMSL2 mode and disable GMSL3 mode | 0x0006 | REG6[7] = 0b0 |

| 4 | Local | MAX96792A | Hold the GMSL link in RESET | 0x0010 | CTRL0[6] = 0b1 |

| 5 | Local | MAX96792A | Change Rx rate to 6Gbps | 0x0001 | REG1[1:0] = 0b10 |

| 6 | Local | MAX96792A | Disable FEC | 0x0028 | TX0[1] = 0b0 |

| 7 | Local | MAX96792A | Enable GMSL2 mode and disable GMSL3 mode | 0x0004 | REG4[7:6] = 0b00* |

| 8 | Local | MAX96792A | Release the GMSL link from RESET | 0x0010 | CTRL0[6] = 0b0 |

| *これによりGMSL3 とのリンクの両方が設定されます。各リンクは個別に設定できます。 | |||||

エラーのレポートのセクションで説明したように、FEC のレポートに応じてエラー・モニタの考え方を変える必要があります。

| MAX96793 | MAX96792A | |||

| BIT NAME | REGISTER | VALUE | REGISTER | VALUE |

| DEC_ERR_OEN_A | 0x001A | INTR2[0] = 0b1 | 0x001A | INTR2[0] = 0b1 |

| DEC_ERR_OEN_B | — | — | 0x001A | INTR2[1] = 0b1 |

| IDLE_ERR_OEN | 0x001A | INTR2[2] = 0b1 | 0x001A | INTR2[2] = 0b1 |

| IDLE_ERR_OEN_B | — | — | 0x5010 | INTR10[6] = 0b1 |

| FEC_RX_ERR_OEN | — | — | 0x001C | INTR4[5] = 0b0* |

| FEC_RX_ERR_OEN_B | — | — | 0x5010 | INTR10[5] = 0b0* |

| *各リンクは個別に設定できます。 | ||||

| MAX96793 | MAX96792A | |||

| BIT NAME | REGISTER | VALUE | REGISTER | VALUE |

| DEC_ERR_OEN_A | 0x001A | INTR2[0] = 0b0 | 0x001A | INTR2[0] = 0b0 |

| DEC_ERR_OEN_B | — | — | 0x001A | INTR2[1] = 0b0 |

| IDLE_ERR_OEN | 0x001A | INTR2[2] = 0b0 | 0x001A | INTR2[2] = 0b0 |

| IDLE_ERR_OEN_B | — | — | 0x5010 | INTR10[6] = 0b0 |

| FEC_RX_ERR_OEN | — | — | 0x001C | INTR4[5] = 0b1* |

| FEC_RX_ERR_OEN_B | — | — | 0x5010 | INTR10[5] = 0b1* |

| *各リンクは個別に設定できます。 | ||||

FEC を有効化した場合、アプリケーションの要件に応じてFEC の統計情報を個別に設定できます。MAX96792A には、両方のリンクの統計情報の読出し、およびエラー閾値の設定用にレジスタ・ブロック・アドレス0x2000 から始まる豊富なレジスタが用意されています。

例えば、アプリケーションによっては、訂正可能なビット・エラーが一定数あってもアラームを出さなくてもよい場合があり、その場合は許容される訂正ビット数にCORRECTED_THRESHOLD_0/1/2/3 を設定します。訂正不可能なビット・エラーのほうが重要で、システムに重大な問題があることを示しています。

豊富な統計情報によって、GMSL リンクの健全性を包括的に把握することが可能です。

まとめ

GMSL2 およびGMSL3 デバイス・ファミリは、設計の進化に対応可能な設計がなされており、ここでは、システムをアップグレードする場合に考慮すべき変更点の詳細を示しました。一般的に、GMSL2 およびGMSL3 デバイスは、可能な限り一貫性が保たれており、アップグレードの際に必要な設計の負担を軽減します。この記事では、具体的に2 つのデバイスのアップグレードについて説明しましたが、その他のGMSL2 およびGMSL3 デバイスを設計に使用する場合には、各デバイスの技術文書を必ず確認してください。ただし、GMSL の帯域幅の計算、およびGMSL のチャンネル仕様はすべてのGMSL デバイスで同一です。

参考資料

[1] Canterbury、「QR codes - Coding - Error control - Computer Science Field Guide」、Csfieldguide.org.nz、2024 年。 https://www.csfieldguide.org.nz/en/chapters/coding-error-control/qr-codes