AN-1368: フェライト・ビーズの特性を知る

はじめに

高分解能で高性能のコンバータや高周波(RF)システムは、低ノイズ設計の電源がないと最適性能が得られません。特にミックスド・シグナル・コンバータやトランシーバは、電源ノイズを十分除去することも必要ですが、アナログ領域とデジタル領域との間の高周波クロストークを減らすことも必要です。

電源の中でも特にノイズの多いのがスイッチング・レギュレータです。スイッチング・レギュレータの出力には、望ましくない成分が含まれているので、ノイズに敏感なシステムに害を与えることがあります。しかし電力変換効率が高いため、バッテリによる長時間駆動の必要な携帯機器や、熱的制限の存在するシステムにはよく使われています。

ミックスド・シグナルIC の場合は、デジタル系とアナログ系とで電源電圧が同じであっても、別々の電源から電力を供給するのが普通です。そうすれば、影響を受けやすいアナログ電源レールに高速のデジタル・スイッチング・ノイズが結合せず、コンバータの性能を落とさずに済むからです。ただし、システム・レベルでは複雑になってコストがかさみます。複数の電源系どうしでうまく高周波絶縁ができれば、アナログ系とデジタル系とで電源を共有できるので、設計が単純になってコストが減ります。

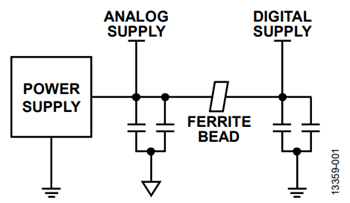

電源の高周波ノイズを除去してクリーンな電源を共有する効果的な方法の1 つは、フェライト・ビーズを使うことです。フェライト・ビーズは、広い周波数範囲にわたって高周波ノイズ・エネルギーを除去する受動部品です。所定の周波数範囲で抵抗性を示し、ノイズ・エネルギーを熱として消費します。フェライト・ビーズは電源ラインに直列に接続します。多くの場合、フェライト・ビーズのどちらの端子も、接地したコンデンサに接続します。この構成にするとローパス・フィルタ回路が形成されるので、電源の高周波ノイズがさらに減ります。

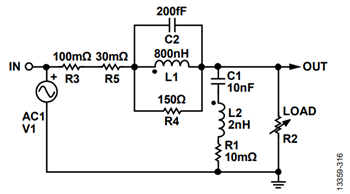

図 1 は、アナログ系とデジタル系とで電源を分けるために、ミックスド・シグナルIC によく使われるフィルタ回路の例です。この回路構成は、どの配電ネットワークにも適しています。ただし、その有効性と限界を理解することは、例えば高性能コンバータにとって害をなすおそれのある特性を避けるのに役立ちます。

このアプリケーション・ノートでは、フェライト・ビーズの応答特性、フェライト・ビーズの簡略モデル、シミュレーション、DC 電流の問題、LC 共振作用、ダンピング方法など、電源システムにフェライト・ビーズを使用するときにシステム設計者が知っておく必要のある重要事項を説明します。これらの理解により、システム設計の短期化と効率化が図れます。

出力フィルタとしてのフェライト・ビーズの効果を実証するために使ったアナログ・デバイセズの製品は、1.25 A、1.2 MHz の同期整流式降圧スイッチング・レギュレータ(ADP2120)と、独立した正負の出力を備えた2 A/1.2 A のDC-DC スイッチング・レギュレータ(ADP5071)です。

フェライト・ビーズの応答特性

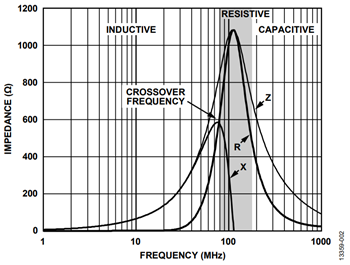

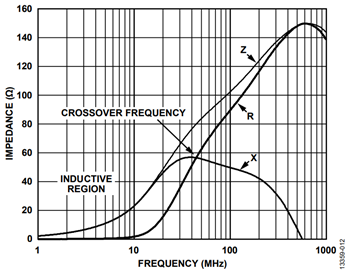

フェライト・ビーズは、誘導性、抵抗性、容量性という3 つの応答領域に分類されます。各領域はZRX のプロットで確認できます。Z はフェライト・ビーズのインピーダンス、R は抵抗成分、X はリアクタンス成分です。高周波ノイズを減らすためには、フェライト・ビーズが抵抗性の領域にあることが必要です。特に、電磁干渉(EMI)フィルタリングを行う場合はなおさらです。抵抗性領域にあるときは抵抗と同じように働くので、高周波ノイズを阻止して熱として消費します。抵抗性領域は、図2 に示すように、フェライト・ビーズのクロスオーバー周波数(X = R)から、フェライト・ビーズが容量性に変わる周波数までの領域です。容量性になるのは、容量性リアクタンスの絶対値がR に等しくなる周波数のところです。

クロスオーバー周波数以下の、比較的低い周波数では誘導性を示し、高い周波数では容量性を示します。容量性領域では、周波数に対するインピーダンスの減衰曲線の傾きはフェライト・ビーズの寄生容量によって決まります。

フェライト・ビーズの簡略モデルとシミュレーション

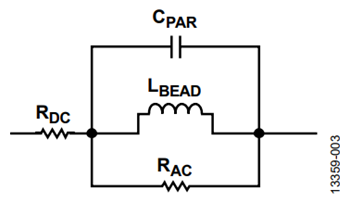

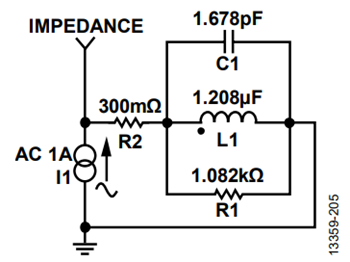

フェライト・ビーズは、図3 に示すように、抵抗、インダクタ、コンデンサから成る簡略回路としてモデル化できます。RDC はフェライト・ビーズのDC 抵抗成分です。CPAR、LBEAD、RACはそれぞれ、フェライト・ビーズの寄生容量、インダクタンス成分、AC 抵抗成分(AC コア損失)です。

図 3 に示す簡略回路モデルを使えば、場合によってはフェライト・ビーズのインピーダンス特性をGHz に達しない範囲で近似することができます。

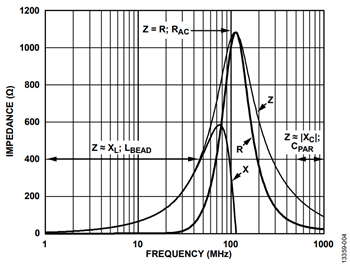

例としてTyco Electronics 製の積層フェライト・ビーズBMB2A1000LN2 を使います。インピーダンス・アナライザで測定した、DC バイアス電流がゼロのときのBMB2A1000LN2 のZRX 応答特性を図4 に示します。使用した回路シミュレータは、アナログ回路とミックスド・シグナル回路の設計と開発に最適化したシミュレーション・ツールADIsimPE です。ADIsimPE にはSIMetrix/SIMPLIS が統合されています。

上の ZRX のプロット(実測値)でビーズがほぼ誘導性を示す領域(Z ≈ XL)のインダクタンス(LBEAD)は、次式で計算されます。

ここで

f は、ビーズが誘導性を示す領域内のある周波数です。この例ではf = 30.7 MHz です。

XL は、30.7 MHz のときのリアクタンス233 Ω です。

式 1 に代入すると、インダクタンス(LBEAD)は1.208 μH と計算されます。

上の ZRX のプロットで、ほぼ容量性を示す領域(Z ≈ |XC|)の寄生容量(CPAR)は、次式で計算されます。

ここで

f は、容量性を示す領域内のある周波数です。この例ではf =803 MHz です。

|XC| は、803 MHz のときのリアクタンス118.1 Ω です。

式 2 に代入すると、寄生容量(CPAR)は1.678 pF と計算されます。

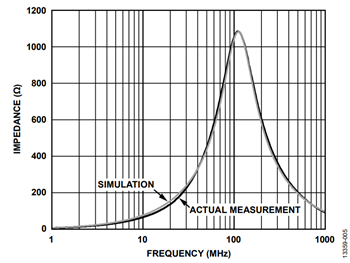

DC 抵抗成分(RDC)は、メーカーのデータシートによると300mΩ です。AC 抵抗成分(RAC)は、フェライト・ビーズが純粋な抵抗性を示す周波数でのピーク・インピーダンスです。RACは、Z からRDC を引くと求まります。RDC は、このピーク・インピーダンスに比べて非常に小さいので無視できます。したがって、この例のRAC は 1.082 kΩ です。回路シミュレータ・ツールADIsimPE を使ってインピーダンスの周波数特性を生成しました。DC バイアス電流がゼロのときのインピーダンスの周波数応答特性の実測値とシミュレーション結果の両方を図5に示します。回路シミュレーション・モデルを図6 に示します。各成分の値は、計算で求めた値です。この例では、シミュレーションで得られたインピーダンス曲線と実測値が非常によく一致しています。

フェライト・ビーズのこのモデルは、ノイズ・フィルタ回路の設計と分析に便利です。例えば、フェライト・ビーズのインダクタンスが近似できれば、ローパス・フィルタ・ネットワークでデカップリング・コンデンサと組み合わせたときの共振周波数(カットオフ周波数)を求めるのに便利です。しかし、このアプリケーション・ノートに示した回路モデルは、DC バイアス電流がゼロのときの近似です。このモデルは、DC バイアス電流によって違ってくる可能性があり、場合によってはもっと複雑なモデルが必要となります。

DC バイアス電流の問題

電源回路にふさわしいフェライト・ビーズを選ぶには、フィルタの帯域幅についてだけでなく、DC バイアス電流によってフェライト・ビーズのインピーダンス特性がどう変化するのかについても慎重に検討する必要があります。ほとんどの場合は100 MHz でのインピーダンスしか規定されていませんし、図2 に示すような、DC バイアス電流がゼロのときの周波数特性しかデータシートには掲載されていません。しかし電源のフィルタリングにフェライト・ビーズを使用する場合、そのフェライト・ビーズを通過する負荷電流は決してゼロではありません。DC バイアス電流がゼロから増えれば、フェライト・ビーズの特性はすべて著しく変化します。

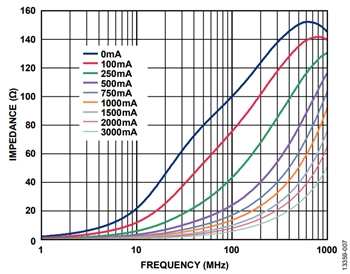

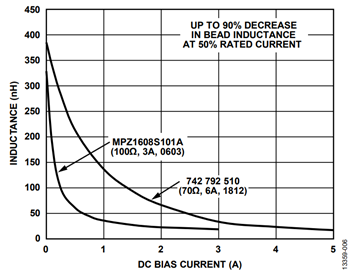

DC バイアス電流が増えるとコア材の飽和が始まり、フェライト・ビーズのインダクタンスは著しく減少します。インダクタンスの飽和の程度は、フェライト・ビーズのコア材によって異なります。2 種類のフェライト・ビーズのインダクタンスがDC バイアスによってどう変化するかを図7 に示します。定格電流の50 % でインダクタンスは最大90 % 低下しています。

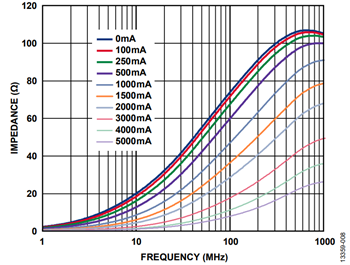

周波数特性を見ても、DC バイアス電流によってインピーダンスが低下することがわかります。これもやはり、フェライト・ビーズの有効性とそのEMI 除去能力を低下させる原因です。フェライト・ビーズのインピーダンスがDC バイアス電流によってどう変化するかを図8 と図9 に示します。

図 8 と図9 に示すように、100 MHz での実効インピーダンスは、定格電流のわずか50 % を流しただけで、TDK MPZ1608S101A(100 Ω、3 A、0603)が100 Ω から 10 Ω へ、Wurth Elektronik742 792 510(70 Ω、6 A、1812)が70 Ω から 15 Ω へと激減しています。

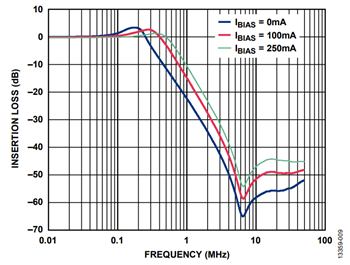

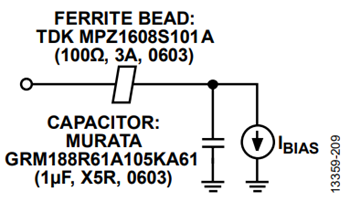

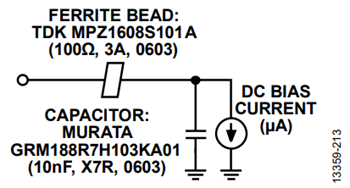

システム設計者は、DC バイアス電流がフェライト・ビーズのインダクタンスと実効インピーダンスに及ぼす影響を十分認識しなければなりません。このことが大きな電源電流を必要とするアプリケーションで重要な要件となることがあるからです。図10 は、100 Ω、3 A 定格のフェライト・ビーズと1 μF のコンデンサを組み合わせた回路の減衰特性(実測値)です。パラメータとしてDC バイアス電流を変化させています。図11 はテスト回路モデルです。

定格 3 A のフェライト・ビーズにDC バイアス電流を250 mA流すと、共振周波数(カットオフ周波数)が右にずれます。その主な理由は、図7 に示したインダクタンスの低下です。

また、このローパス・フィルタの実効減衰率は、今のほとんどのスイッチング・レギュレータの動作周波数である1 MHz で15dB も低下しています。システム設計者が、DC バイアス電流がゼロのときのインピーダンスしか示していないデータシートに頼り切ってしまうと、この減衰率の低下が問題を生じることがあります。したがって、フェライト・ビーズ・フィルタの有効性を確認して正確な結果を得るには、広いDC バイアス電流範囲にわたってインダクタンスをモデル化し、実際の動作条件でのインピーダンス特性を明らかにすることが必要です。

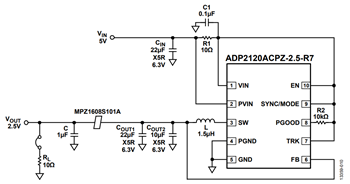

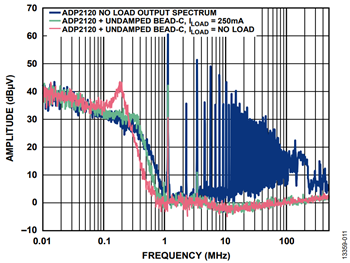

図12 は、強制パルス幅変調(FPWM)モードで動作する降圧レギュレータADP2120 に図11 のフェライト・ビーズ・フィルタを接続したアプリケーション回路です。FPWMモードで動作しているADP2120 は、負荷電流が変化してもスイッチング・ノイズ・スペクトル出力は大きくは変化しません。FPWM モードの詳細については、ADP2120 のデータシートを参照してください。スペクトル出力が図13 にプロットされており、DC バイアスがフェライト・ビーズの応答特性に及ぼす影響を示しています。

図 13 を見ると、フィルタ・カットオフ周波数は、負荷電流がゼロのときの約180 kHz(赤の曲線)から、負荷電流が250 mA のときの約370 kHz(緑の曲線)へと、右にずれています。1.2MHz 付近の基本波リップルに対する減衰率は、負荷電流がゼロのときには30 dB ですが、負荷電流が250 mA のときには約18dB に低下します。

LC 共振作用

フェライト・ビーズとデカップリング・コンデンサを組み合わせると、共振ピークの生じる可能性があります。この作用は見過ごされがちですが、システムによってはリップルとノイズを減衰せずに増幅するので有害です。多くの場合、このピークが生じるのは、DC/DC コンバータによく採用されるスイッチング周波数付近です。

フェライト・ビーズのインダクタンスとQ の高いデカップリング容量で形成されるローパス・フィルタ・ネットワークの共振周波数がそのフェライト・ビーズのクロスオーバー周波数よりも低いとピークが生じます。こうして得られるフィルタは減衰不足になります。図14 は、TDK MPZ1608S101A のインピーダンスの周波数特性(実測値)です。不要なエネルギーを消費してくれる抵抗成分は、約20 MHz ~ 30 MHz まで大きくなりません。この周波数より低い領域だと、フェライト・ビーズは依然としてQ が非常に高くて、理想的なインダクタとして作用します。フェライト・ビーズを用いた典型的なフィルタのLC 共振周波数は、0.1 MHz ~ 10 MHz の範囲になるのが普通です。300 kHz ~ 5 MHzの範囲にある典型的なスイッチング周波数の場合、フィルタのQを下げるため、さらに減衰させる必要があります。

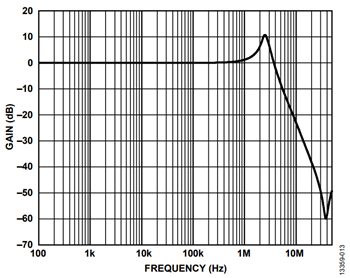

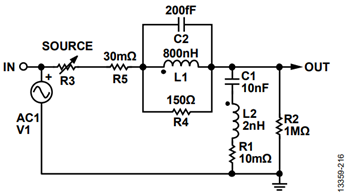

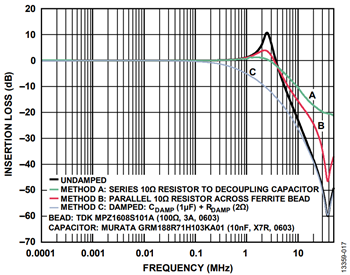

ピークの生じる例として、フェライト・ビーズとコンデンサで構成したローパス・フィルタのS21 周波数特性を図15 に示します。ピークの生じているのが見て取れます。使用したフェライト・ビーズは、TDK MPZ1608S101A(100 Ω、3 A、0603)です。使用したデカップリング・コンデンサは、低ESR のセラミック・コンデンサである村田製作所GRM188R71H103KA01(10 nF、X7R、0603)です。負荷電流はマイクロアンペア程度です。

不足減衰のフェライト・ビーズ・フィルタは、フィルタ回路のQ によって違いはありますが、約10 dB ~ 約 15 dB のピークを生じる可能性があります。図15 では、利得が 10 dB もあるピークが2.5 MHz 付近に生じています。

また、1 MHz ~ 3.5 MHz には信号利得が見られます。このピーキング作用は、スイッチング・レギュレータの動作周波数帯域に生じると問題となります。不要なスイッチング・ノイズが増幅されるからです。そうなると、フェーズ・ロック・ループ(PLL)、電圧制御発振器(VCO)、高分解能のA/Dコンバータ(ADC)のような、敏感な負荷の性能が台無しになりかねません。図15 に示す結果は、マイクロアンペア程度の非常に軽い負荷で得られたものですが、必要な負荷電流がわずか数マイクロアンペアから1 mA の回路や、動作モードによっては節電手段としてスイッチがオフになる装置では、実際的な使い方です。ピークが生じてしまうと、不要なクロストークを生むおそれのあるノイズがシステム内に増えます。

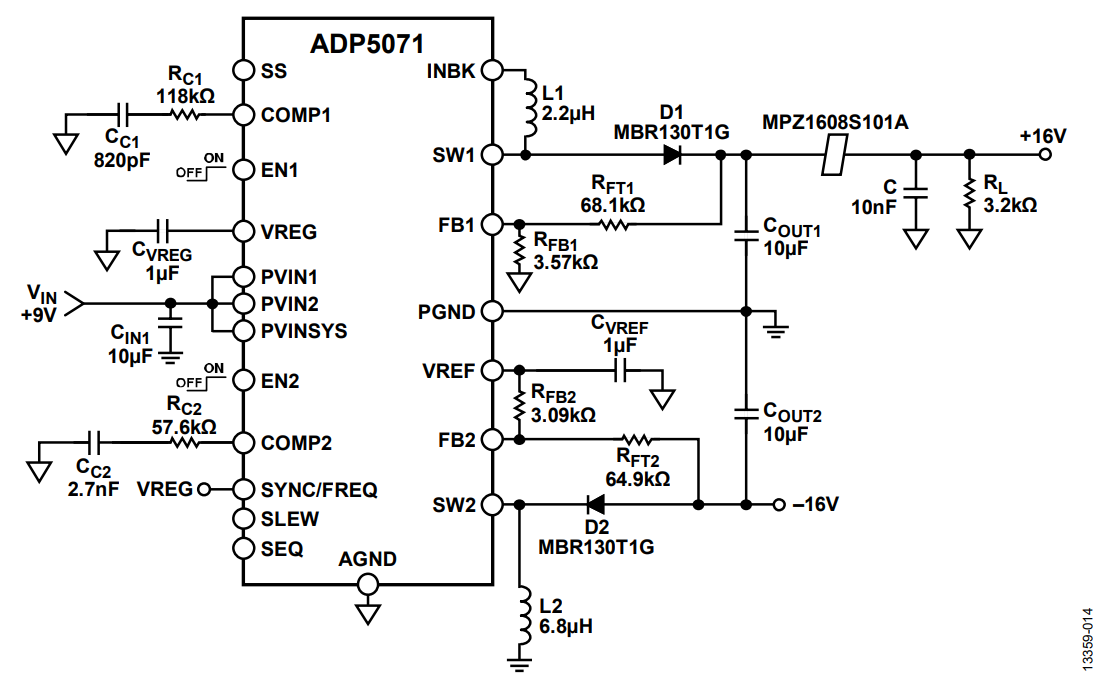

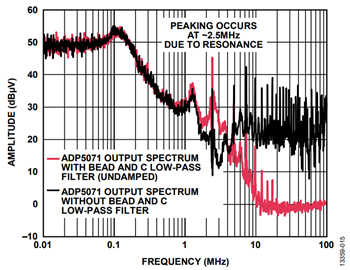

例として、フェライト・ビーズ・フィルタを接続したADP5071のアプリケーション回路を図17 に示します。図18 には、正出力のスペクトルのプロットを示します。スイッチング周波数は2.4 MHz、入力電圧は9 V、出力電圧は16 V、負荷電流は5 mAにそれぞれ設定されています。

フェライト・ビーズのインダクタンスと10 nF のセラミック・コンデンサにより、2.4 MHz 付近に共振ピークが生じています。基本波リップル周波数は減衰されずに10 dB の利得が生じています。

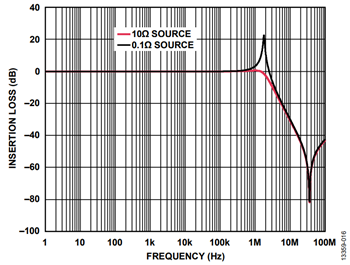

共振ピークに影響するその他の要因は、フェライト・ビーズ・フィルタの直列インピーダンスと負荷インピーダンスです。図19 は、10 Ω と0.1 Ω の直列ソース抵抗で比較したシミュレーション結果です。ピークは、ソース抵抗の高い方が大きく下がって減衰しています。しかしこの方法は負荷レギュレーションが悪化するので、実際には採用できません。直列抵抗成分によって電圧降下が生じるため、負荷電流が増えるとその分だけDC 電圧が下がってしまうからです。

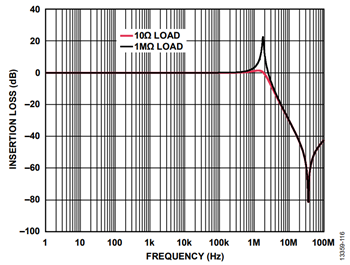

負荷インピーダンスもピーク特性に影響を及ぼします。ピークが最悪となるのは、負荷の軽いとき(負荷抵抗が大きくて負荷電流が小さいとき)です。

図 21 は、ソース抵抗は同じままで負荷を1 MΩ から 10 Ω に変えたときのシミュレーション結果です。ピークは、負荷抵抗の小さいときの方が大きく下がって減衰しています。実際には、図13に示したように、DC 負荷電流が増えるとフェライト・ビーズの性能は大きな影響を受けます。DC 電流が増えるとフェライト・ビーズのインダクタンスが下がって共振周波数(カットオフ周波数)に影響が出ます。

ダンピング方法

ここでは、共振ピークを大幅に低下させるのに使える3 つのダンピング方法を説明します(図23 を参照)。

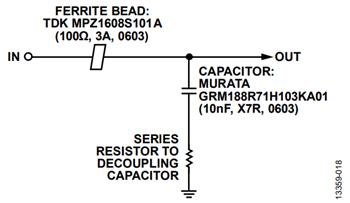

方法 A は、デカップリング・コンデンサの経路に抵抗を直列接続します(図24 を参照)。共振は減衰しますが、高い周波数でのバイパス効果は劣化します。

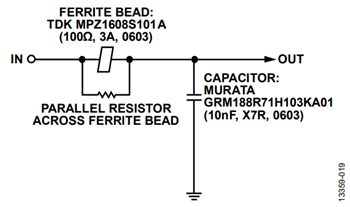

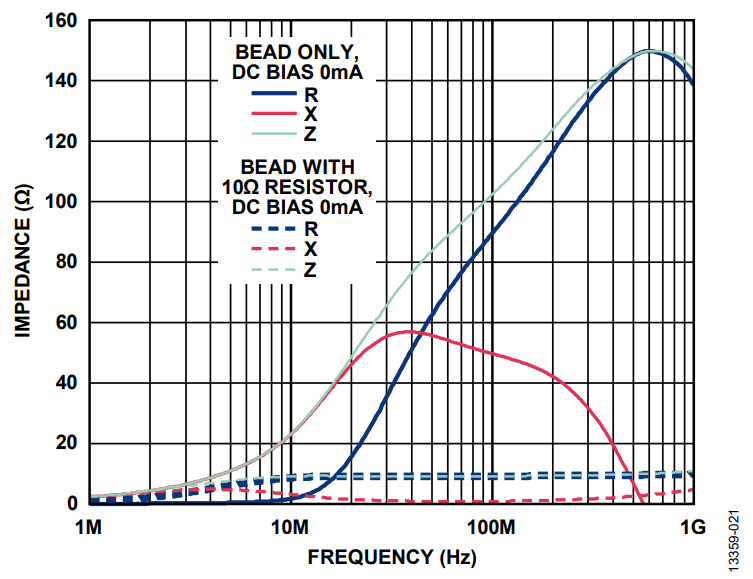

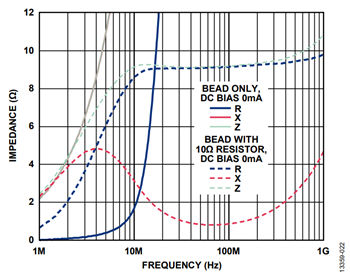

方法 B は、フェライト・ビーズに並列に小さな抵抗を接続します(図25 を参照)。この方法でもフィルタ回路の共振は減衰しますが、高い周波数では減衰特性が劣化します。図26 と図27 に、10 Ω の並列抵抗を接続した場合と接続しない場合の、MPZ1608S101A のインピーダンスの周波数特性曲線を示します。緑色の点線は、10 Ω の抵抗を並列接続したフェライト・ビーズ全体のインピーダンスです。フェライト・ビーズと抵抗を組み合わせたこのインピーダンスは著しく小さく、10 Ω 抵抗が支配的となっています。ただし、10 Ω の並列抵抗を接続したフェライト・ビーズのクロスオーバー周波数3.8 MHz は、フェライト・ビーズ単体でのクロスオーバー周波数40.3 MHz に比べてはるかに低くなります。そのため、はるかに低い周波数範囲でフェライト・ビーズが抵抗性を示し、Q が下がって、ダンピング性能が改善されます。

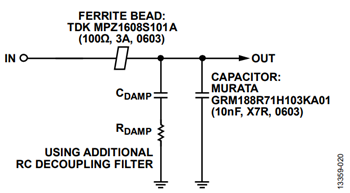

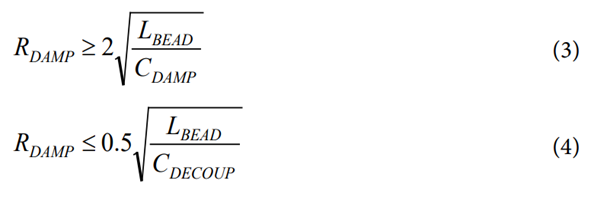

方法 C は、容量の大きいコンデンサ(CDAMP)にダンピング抵抗(RDAMP)を直列接続します。多くの場合、これが最善の方法です(図28 を参照)。

図 23 に示すように、このコンデンサと抵抗を追加すると、フィルタ回路の共振が減衰するうえに、高い周波数でのバイパスの有効性は劣化しません。この方法では、容量の大きなダンピング・コンデンサのおかげで、ダンピング抵抗で過度の電力が消費されることはありません。ダンピング・コンデンサは、デカップリング・コンデンサを全部合わせたよりもずっと大きな容量にしなければなりませんが、ダンピング抵抗の値は小さくて済みます。共振周波数でのダンピング・コンデンサのインピーダンスは、ピーキングの作用を減らせる程度にダンピング抵抗よりも小さくなければなりません。RDAMP の値の範囲は、式3および式4 で求まります。ダンピング容量(CDAMP)とデカップリング容量(CDECOUP)の比を16 以上にすると、両方の式を満足するダンピング抵抗の範囲が求まります。

ここで

RDAMP はダンピング抵抗です。

LBEAD は、フェライト・ビーズのインダクタンス(式1)です。基板パターンの寄生インダクタンスのような外部のインダクタンスも含みます

CDAMP はダンピング容量です。

CDECOUP はデカップリング容量です。

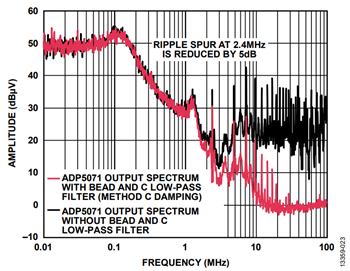

図 29 は、図17 に示したアプリケーション回路に方法C のダンピングを適用したときのADP5071 の正出力のスペクトル・プロットです。使用したCDAMP およびRDAMP はそれぞれ、1 μF のセラミック・コンデンサと2 Ω のチップ抵抗です。2.4 MHz での基本波リップルが5 dB 減少しており、図18 で 10 dB 増加しているのとは対照的です。

一般に、方法C が一番洗練された方法であり、高価な専用のダンピング・コンデンサを購入しなくてもセラミック・コンデンサに直列に抵抗を接続すれば実現できます。試作のとき調整できて、不要なら取り外せる抵抗を常に用意しておくのが最も安全な設計です。欠点は、追加部品のコストと、基板面積が余計に必要になることです。

まとめ

このアプリケーション・ノートでは、フェライト・ビーズを使用するとき考慮すべき重要事項を示しました。また、フェライト・ビーズの簡略回路モデルについても詳述しました。インピーダンスの周波数特性は、DC バイアス電流がゼロであれば、シミュレーション結果と実測値がよく一致することがわかりました。

DC バイアス電流がフェライト・ビーズの特性に及ぼす影響についても論じました。定格電流の20 % よりDC バイアス電流が大きいと、フェライト・ビーズのインダクタンスが著しく低下するおそれがあることを示しました。そうした電流は、フェライト・ビーズの実効インピーダンスを下げてEMI フィルタリング能力を劣化させるおそれもあります。DC バイアス電流の流れる電源ラインにフェライト・ビーズを使用するときは、そのDC バイアス電流がフェライト材を飽和させてインダクタンスを大きく変化させることがないようにする必要があります。

フェライト・ビーズは誘導性なので、Q の高いデカップリング・コンデンサと組み合わせるときは注意が必要です。不要な共振が回路に発生して、益するどころか害をなすことがあります。しかし、このアプリケーション・ノートで提案したダンピング方法は、容量の大きなデカップリング・コンデンサとダンピング抵抗を直列接続して負荷の両端に使用し、不要な共振を防止することにより、簡単なソリューションを与えます。フェライト・ビーズを正しく利用すれば、効果的かつ安価に、高周波ノイズとスイッチング・トランジェントを減らせます。

参考資料

AN 583 Application Note Designing Power Isolation Filters with Ferrite Beads for Altera FPGAs(アプリケーション・ノートAN 583 アルテラFPGA によるフェライト・ビーズの電源分離フィルタのデザイン), Altera Corporation, 2009.

Applications Manual for Power Supply Noise Suppression and Decoupling for Digital ICs(デジタルIC の電源ノイズ対策・デカップリング Application Manual), 村田製作所, 2010.

Burket, Chris. All Ferrite Beads Are Not Created Equal –Understanding the Importance of Ferrite Bead Material Behavior. TDK Corporation, 2011.

Fancher, David B. ILB, ILBB Ferrite Beads: Electro-Magnetic Interference and Electro-Magnetic Compatibility (EMI/EMC).Vishay Dale, 1999.

Hill, Lee and Rick Meadors. Steward EMI Suppression Technical Presentation. Steward.

Kundert, Ken. Power Supply Noise Reduction. Designer’s Guide Consulting, Inc., 2004.

Solving Electromagnetic Interference (EMI) with Ferrites, Fair-Rite Products Corp.

Weir, Steve. PDN Application of Ferrite Beads. IPBLOX, LLC, 2011