AN-1254: 複数の DDS ベース・シンセサイザAD9915 を同期する

はじめに

様々なアプリケーションで、2 つもしくはそれ以上の正弦波または方形波を発生できる回路の要求が高まっています。しかもそれら複数の信号は、期待される位相値で同期関係にあることが必要です。アナログ・デバイセズが提供するAD9915 DDS ICは、上記で説明した信号を発生させる能力を有します。このアプリケーション・ノートでは、2 つもしくはそれ以上のデバイスを、どのようにすれば同期できるかを解説し、位相誤差を生じさせる可能性のある原因についても考察したいと思います。

同期を成功させるには、各デバイスのREF CLK、SYNC_CLK、そしてIO_UPDATE のタイミング全てを制御しなければなりません。そして全てのDDS デバイスが同じ内部システム・クロックで動作し、±1 クロック・カウントまたはそれ以上の誤差を生じないようにすることが重要です。それゆえ、各デバイスのSYNC_CLK 相互の位相補正を必ず行わなければなりません。また、各デバイスのIO_UPDATE 信号は、SYNC_CLK と同期して発生させる必要があります。これらを行うことで、DDS 出力信号間の位相誤差不確定性が、±1 もしくはそれ以上のシステム・クロック周期を超えることはありません。

出力フィルターのミスマッチ、REF CLK のスキュー、もしくはその他の事柄に起因する位相誤差は、ある一定値の誤差として(出力信号に)現れます。しかしながら、DDS はプログラマブルな位相調整機能を持っているので、この一定値の誤差をキャンセルすることができます。このアプリケーション・ノートでは、複数のDDS 部品を同期させる為に求められる基本を解説します。各部品の位相同期を成功させる為の第一歩は、REF CLKの分配方法からスタートします。

複数の部品を同期するには

同期すべき全ての部品に位相の一致したREFCLK を入力する

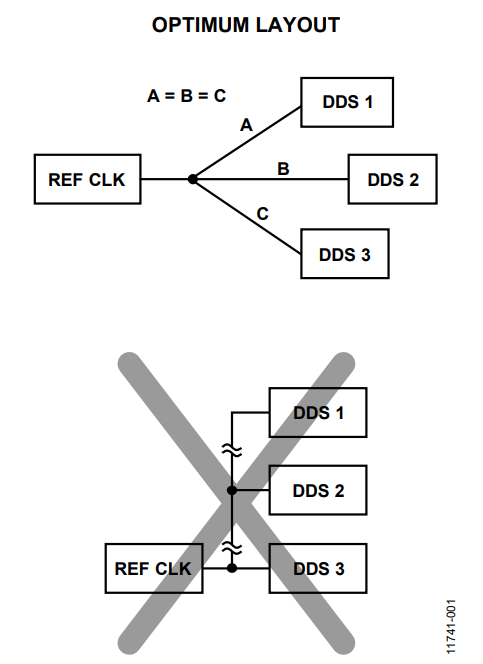

複数の AD9915 を使った同期動作を成功に導くため最初にやらなければならないことは、各部品のREF CLK端子に入力される信号間の位相誤差を最小にすることです。もしREF CLKへの入力信号が複数のDDS 部品に入力されるとき、その信号の位相が合っていないと、出力信号の位相誤差は、他の誤差要因を除いたとしても、少なくともREF CLKへ入力された信号の位相誤差と同じ値を持ちます。したがって、標準的なクロック分配回路における慣行を忠実に守って、PCB 上の配線レイアウトを行って下さい ( 図1)。

現実には、REF CLK の位相誤差、もしくは入力信号のクロック・スキューが非常に大きいと、複数のDDS 部品間において、SYNC_CLK を同じREF CLK のエッジに合わせることが出来なくなります。SYNC_CLK の位相補正を行わないと、複数のDDS 部品間における同期は不可能です。DDS 内部のシステム・クロックは、REF CLK から位相の遅れた同一信号であり、それぞれのデバイスは同じ内部クロック・レートになることに注意して下さい。但しこれは内部のPLL が無効になっている場合です。PLL が有効になっている場合は、(DDS 内部の)システム・クロック・レートは、設定されたPLL の乗算係数倍になります。

複数の DDS 部品を同期させることが可能な、最高システム・クロック・レートは2.5GSPS です。このレートを超えて動作させた場合、信頼性の高いなタイミング・ソリューションを構成することは、より困難になります。

全てのDDS 部品に対するSYNC_CLK の位相を合わせる

SYNC_CLK はCMOS レベルの信号出力で、その周波数はシステム・クロックの1/16 です。同期動作の最終段階で、SYNC_CLK 信号はDDS デバイス内部にてIO_UPDATE 信号をサンプリングしています。従って、SYNC_CLK 信号は外部でUPDATE と同期をとるため、外部に出力されます。電源投入時、各部品が出力するSYNC_CLK 信号のエッジ位置は、たとえそれぞれの部品に対するREF CLK 信号の位相を完全に一致する形で入力していたとしても、1 つの信号の位相を基準として16 段階ある位相のうち、どれか1 つになります。

上記の理由から、複数の部品を適切に同期させるには、最初にそれぞれのSYNC_CLK エッジの位相を合わせこむ必要があります。そうでないと複数のデバイスが持つフェーズ・アキュムレーターが、位相の差分値を同じシステム・クロック・カウント内に積算することが出来ないからです。

複数のデバイスから出力されるSYNC_CLK を同期させるには、各々のパーツに於いて、幾つかのレジスター・ビットの設定、位相の一致しているSYNC_IN 信号の入力、そして自動DAC キャリブレーションの実行が必要です。要約すると、SYNC_CLKを発生させている内部分周回路をSYNC_IN 信号経由でリセットすることになります。これは各DDS 部品に対して、位相の合ったSYNC_IN 信号を送ることで達成されます。さらにSYNC_IN のエッジ位置は、DDS 部品内部において、内部のシステム・クロックに対しそのセットアップ・タイムの規格値を満たさなければなりません。

多くの場合、SYNC_IN 信号は、マスターDDS 部品が出力しているSYNC_OUT 信号が元になります。SYNC_OUT のクロック・レートは、システム・クロックの1/384 になります。各DDS 部品のSYNC_IN は、マスターDDS デバイスから出力されているSYNC_OUT で直接駆動しない場合があることにも注意して下さい。これは、SYNC_IN とSYNC_OUT は両方とも3.3VのCMOS ロジックであるため、ファン・アウトが取れない場合があるからです。なお、複数のDDS 部品の同期を行う為には、SYNC_IN への信号クロック・レートは、システム・クロックの整数分の1 とし、かつ50MHz 以下になるように設定して下さい。

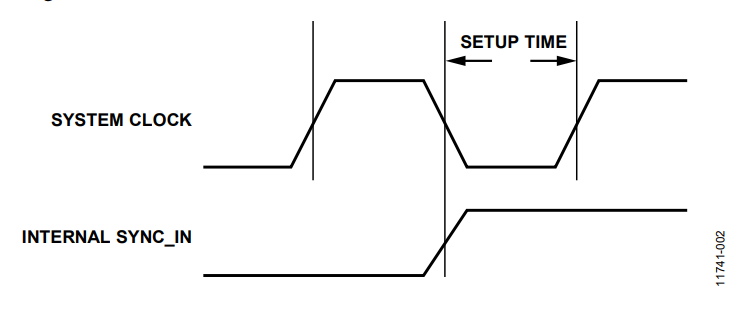

2.5GPS の最高クロック・レートで動作させる時、内部のシステム・クロックの周期は400ps です。複数のデバイスの同期動作を行い、且つデバイス内部におけるタイミング・マージンを最大化させる為には、図 2 に示すように、SYNC_IN のエッジを、システム・クロック周期の中央に持ってくる必要があります。

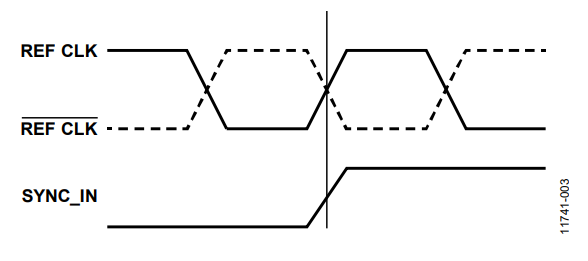

しかしながら、図 2 に示されたSYNC_IN とREF CLK 信号は、デバイス内部で伝搬している為、それらの信号の時間関係に直接アクセス出来ません。一方でAD9915 は外部にあるSYNC_INピンと、同じく外部にあるREF CLK ピンにおいて、SYNC_IN信号の立ち上がり部のエッジが、REF CLK 信号の立ち上がり部のエッジと同時に入力されていれば、2.5GSPS 以下で動作している限り、内部信号のセットアップ・タイムが最小になるよう設計されています。SYNC_IN とREF CLK との時間関係は図 3を参照ください。

もしこの時間関係が全てのデバイスの該当ピンで満足しなかったとしても、REF CLK のエッジに対するSYNC_IN 信号の時間関係は、デバイス内部のSYNC_OUT 信号の時間位置を調整できるレジスタ 0x1B 内のプログラマブル・ディレイ・ビットを設定することで調整することができます。これによりSYNC_OUT の時間位置が調整され、DDS デバイスに供給されているSYNC_OUT 由来である全てのSYNC_IN 信号のエッジ位置を同時に調整することができます。詳しくはAD9915 のデータシートを参照ください。

加えて、SYNC_IN の内部経路における遅延時間を、レジスタ0x1B 内の別のビットを設定することで調整できます。その結果、個別デバイス内部の、システム・クロックに対するSYNC_IN信号の遅延時間を調整することができます。SYNC_IN の内部経路における遅延時間を過剰に設定してしまうと、その遅延量によっては、SYNC_CLK出力信号の位相が、デバイス内部のシステム・クロックの別の周期にジャンプしてしまいます。この現象が起きると、それぞれのデバイスから出力されるSYNC_CLKエッジが、本来あるべき時間位置から外れてしまいます。SYNC_CLKの時間位置を調整する手順は、複数の部品に対してSYNC_CLK の位相を合わせるセクションを参照ください。各デバイスのSYNC_CLKの時間位置の調整が完了すれば、SYNC_OUT 出力をオフにできます。

全てのDDS デバイスに位相が一致したIO_UPDATE を入力する

各部品の SYNC_CLK の位相調整が完了した後、全ての部品に共用のIO_UPDATE 信号を使ったさらなるプログラミングが必要です。例えば、IO_UPDATE を送らなくとも、各デバイスの周波数調整用ワード・レジスタと位相オフセット用ワード・レジスタは、最初にそれぞれのデバイス毎に必要な値に非同期でプログラミングできます。しかしながら、全てのデバイスのDDS コアは、IO_UPDATE 信号が発行されるまで上記プログラミング結果を反映した動作をしません。その後、共通IO_UPDATE 信号を入力すると、その直後、周波数調整用ワード・レジスタと位相オフセット用ワード・レジスタの設定値は、内部システム・クロック・カウントのタイミングで、各デバイスが必要とする値へと同時にアップデートされます。

IO_UPDATE 信号は、SYNC_CLK と同期して発生する必要があります。そのセットアップ・タイムは2ns、ホールド・タイムは0ns です。このタイミングを満足し、SYNC_CLK が全てのデバイスに対して正確な時間位置に調整されていれば、複数デバイスの同期が可能です。

複数の部品に対してSYNC_CLK の位相を合わせる

8 ステップが必要で、それらを以下に示します。

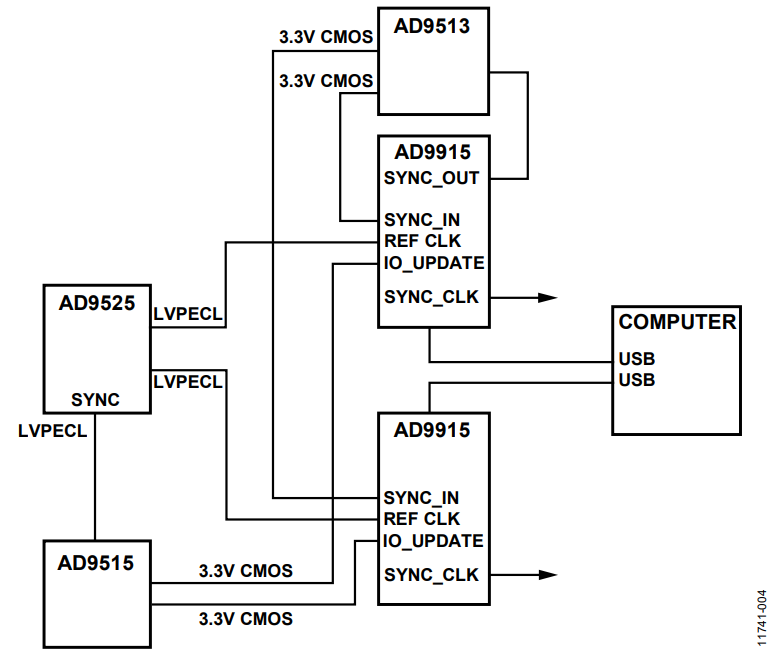

- 全てのデバイスの電源を投入し、REF CLK を与えます。システムブロック・ダイアグラムを 図 4 に示します。繰り返しになりますが、全てのデバイスに与えるREF CLK 信号は、できる限りタイミング・スキューが小さくなるようにして下さい。またシステム・クロックを2.5GBPS 以上に設定して動作を試みた場合、複数チップの同期が成功する確率は非常に低くなります。

- 全てのDDS デバイスにマスター・リセット信号を送ります。このマスター・リセット信号は、各デバイスに対して非同期に送ることができます。マスター・リセットにより、内部レジスタの値を予め決められたデフォルト値にします。

- 全てのDDS デバイスにDAC CAL を行うように指示します。これはレジスタ0x03 の中のDAC CAL ビットをロジック1とし、その後クリアします。この動作は、まず1つのIO_UPDATE 信号を送って、DAC CAL ビットをハイ・レベルにし、続いて別のIO_UPDATE 信号を送ってDAC CALビットをクリアします。この段階でIO_UPDATE を全てのDDS デバイスに与えるとき、非同期でも問題ありません。

- マスターDDS デバイスのSYNC_OUT イネーブル・ビットのみをロジック1 とします。このビットは、レジスタ0x01のビット9 です。設定が終了したら、IO_UPDATE を送ります。この動作により、SYNC_OUT が出力され、そのSYNC_OUT 由来のSYNC_IN 信号が、マスター及び他のスレーブDDS デバイスのSYNC_IN ピンに与えられます。多くの場合、SYNC_OUT 信号は、複数のデバイスをドライブできるだけのファン・アウトを備えたデバイスによってバッファすべきです。SYNC_OUT 信号の周波数は、システム・クロックの1/384 になります。この段階においても、IO_UPDATE を全てのDDS デバイスに与えるとき、非同期でも問題ありません。

- 全てのDDS デバイスのレジスタ 0x10 内、CAL with SYNCビットをロジック1 に設定します。繰り返しになりますが、この時点でもIO_UPDATE を全てのデバイスに与えるとき、非同期でも問題ありません。

- レジスタ0x1B 内のSYNC_OUT ディレイ調整用ビットの値を変化させ、マスター・デバイスにけるSYNC_IN の立ち上がりエッジとREF CLK の位相関係が、 図 3 に示した最適な時間位置になるように調整します。

- ステップ3 を繰り返すことになりますが、マスター・デバイスを含む全てのデバイスに対して、再度DAC CAL を行います。ここでもIO_UPDATE を全てのデバイスに与えるとき、非同期でも問題ありません。このステップ7 で、各デバイスのSYNC_CLK とマスター・デバイスのSYNC_CLK との位相関係が補正されるはずです。

- 各部品のSYNC_CLK がマスター・デバイスと一定の位相関係に調整されたことを受け、同期関係が適切かどうかのテストを行います。全てのデバイスの3 本のプロファイルピンをロジック0 に設定します。

- IO_UPDATE 信号を送らずに、全てのデバイスは、個別にプロファイル・モードになり、プロファイル0 レジスタへ、必要とされる周波数調整用ワードデータをプログラムします。

- 続いて、全デバイス共通のIO_UPDATE ピンに対して、位相の一致したIO_UPDATE 信号に送ります。この時、IO_UPDATE は、SYNC_CLK と同期した上で、定められたセットアップ・タイムとホールド・タイムの規格を満足するように発生させる必要があります。このステップで全てのDDS 出力は同期し、お互いの位相が調整されているはずです。

まとめ

このアプリケーション・ノートで紹介した手順を注意深く実行すれば、複数のDDS 部品から出力される信号を同期させることが出来ます。

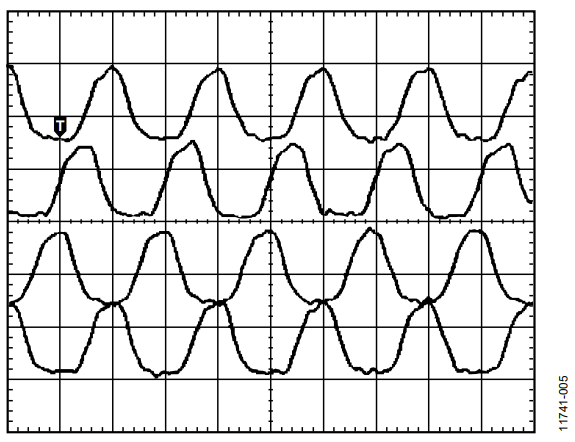

図 5 から 図 7 にそれぞれの場面で4 つのデバイス間における、期待される時間関係を示します。図 5 は、電源投入直後の状態を示しています。同期動作をするための手順を踏む前であり、4つのSYNC_CLK の時間位置がランダムになっています。それぞれの部品に対するREF CLK の入力位相が完璧に一致していても、この状態になります。

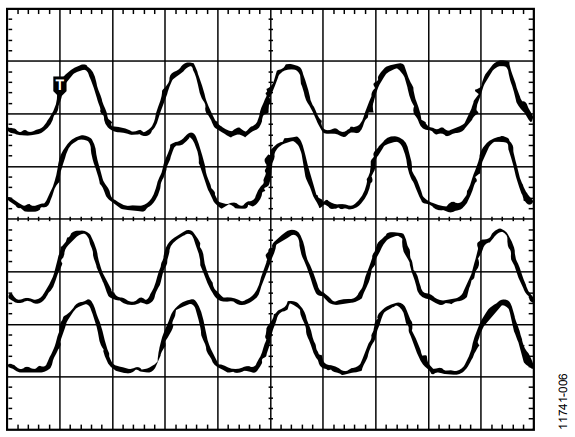

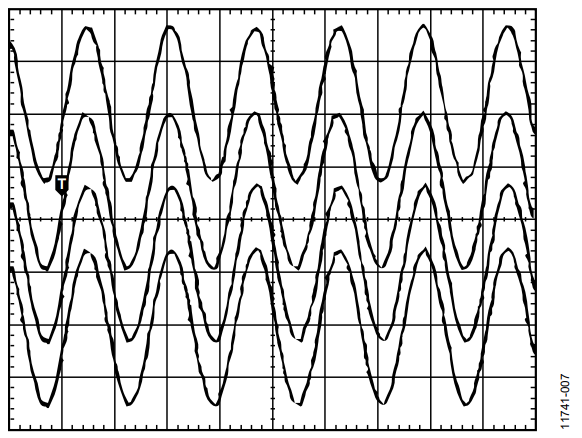

図 6 と 図 7 は SYNC_CLK とDDS 出力波形との時間位置を観測・表示したものです。SYNC_CLK の時間位置調整後のSYNC_CLK 波形と、ステップ8 で示したそれぞれのデバイスにIO_UPDATE を同時に入力という行為を行った後のDDS 出力波形を示しています。

図 7に示した各デバイス間のDDS出力信号位相オフセット値は、同じ値であることは予想されていたことです。もし1つのデバイスの位相を90°変化させた場合、その信号の位相は、他の3つのデバイスからの信号に対して、90°の位相オフセットを持つことになります。