AN-1178: AD7292 DAC ディスエーブル時間の測定

はじめに

AD7292 は汎用のアナログ信号のモニタリングや外部デバイスの制御に必要な機能をすべて備えており、シングルチップ・ソリューションとして集積されています。

AD7292 は、8 チャンネルのアナログ入力、10 ビットのSAR 型ADC、4 個の10 ビットDAC、±1°C 精度の内部温度センサー、システム・モニタリングと制御を目的とする12 本のGPIO を内蔵しています。

DAC 出力VOUT0~VOUT3 の出力電圧範囲は最大5V です(LSB= 4.88 mV)。DAC 出力バッファは、コンフィギュレーション・レジスタ・バンク内のGPIO2/DAC DISABLE0 サブレジスタとGPIO4/DAC DISABLE1 サブレジスタを使ってソフトウェアで制御するか、あるいはGPIO2/DAC DISABLE0 ピンとGPIO4/DACDISABLE1 ピンを使ってハードウェアで制御することができます。

ここでは、AD7292 のDAC ディスエーブル時間の測定について説明します。

DACディスエーブル出力タイミングの測定

ハードウェア構成

ここで説明する測定は、EVAL-AD7292SDZ 評価用ボードとEVAL-SDP-CB1Z システム・デモ用プラットフォーム・ボードとプラットフォーム・ボード上で動作する測定用ソフトウェアを組み合わせて行いました。セットアップとソフトウェアのインストールの詳細については、UG-449 を参照してください。

評価用ボードの変更

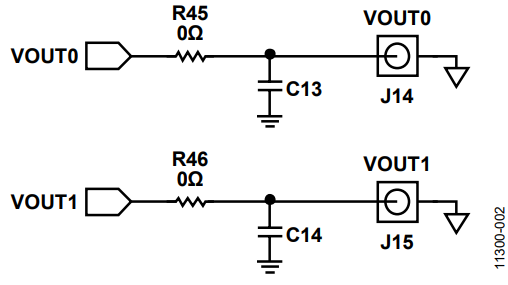

DAC 出力負荷容量を変更した場合にDAC ディスエーブル・タイミングにどのような影響があるか調べました。これを行うために、EVAL-AD7292SDZ 評価用ボードに2 つの小さな変更を加えることが必要でした。EVAL-AD7292SDZ 評価用ボードのBOM では、デフォルトでC13 とC14 が未実装となります。この2 つのコンデンサ・スペースへの実装により、負荷容量をVOUT0 とVOUT1に加えることができます。C13 とC14 には、それぞれ100 pF、330 pFのコンデンサを実装しました。

図 1. VOUT0 とVOUT1 の負荷容量の変更(C13 = 100 pF、C14 = 330 pF)

図 2. ハードウェア構成—評価用ボードのセットアップ

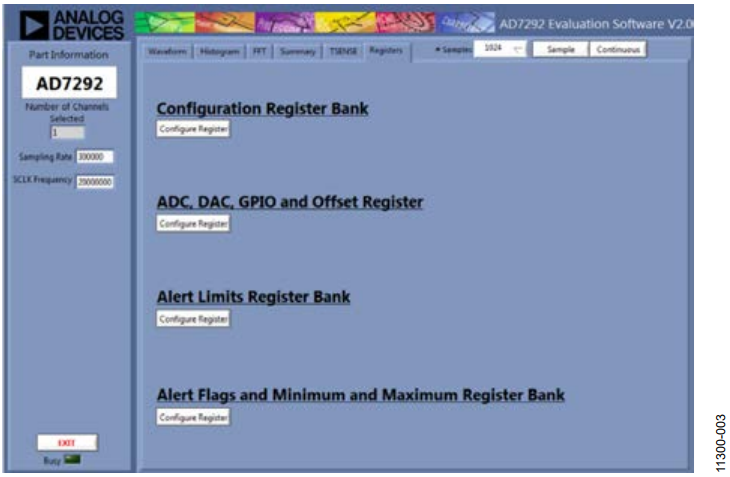

ソフトウェア設定

評価用ソフトウェア内のRegisters タブでは、内部のAD7292 レジスタを設定できます。

図 3. EVAL-AD7292SDZ 評価用ソフトウェア内のRegisters タブ

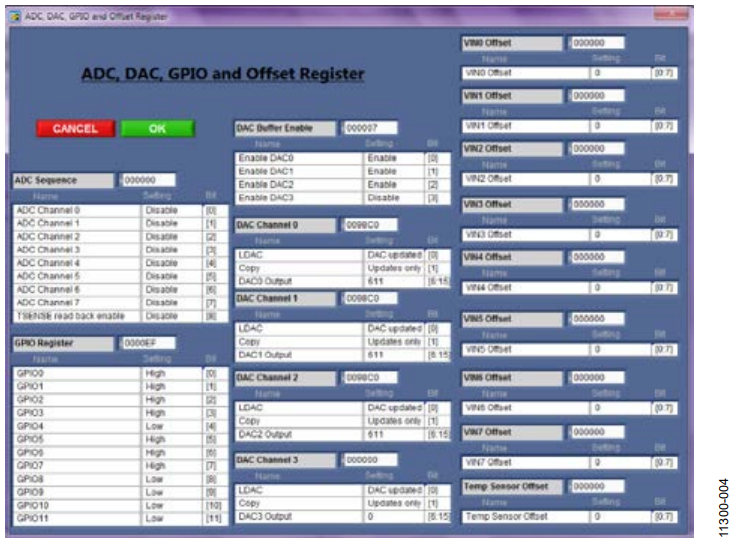

ADC、DAC、GPIO、およびOFFSET レジスタの設定

DAC バッファ・イネーブル・レジスタ(0x0A)

パワーアップ時には、DAC 出力バッファがデフォルトでディスエーブルされています。DAC 出力バッファをイネーブルするには、ビットD0~D3 を1 に設定します。

DAC チャンネル・レジスタ(0x30~0x33)

DACチャンネル・レジスタのビット[D6:D15]への書込みにより、DAC 出力VOUT1、VOUT2、VOUT3 が3 V に設定されています。

図 4. ADC、DAC、GPIO、オフセット・レジスタ

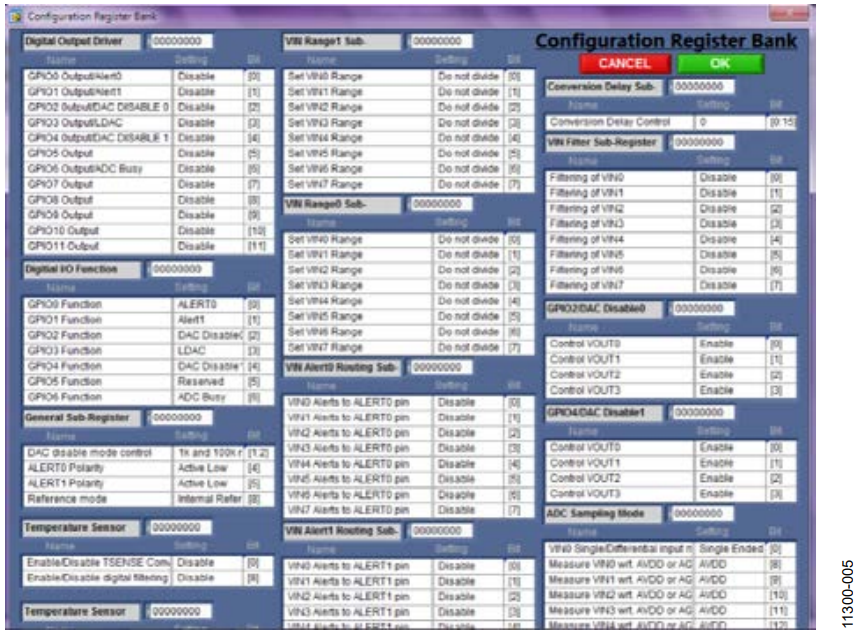

コンフィギュレーション・レジスタ・バンクの設定

GPIO2/DAC DISABLE0 およびGPIO4/DAC DISABLE1

GPIO2/DAC DISABLE0 レジスタの内容は変更されていないので、DAC DISABLE機能はディスエーブルです。DAC disable timingを見ると、ビット[D0:D2]が設定されており、DAC 出力VOUT0~VOUT3 はディスエーブルです。GPIO4/DAC DISABLE1 レジスタを使用して同じ機能を実現することもできます。

汎用サブレジスタ内のDAC ディスエーブル・モード制御ビット(デフォルト)はデフォルト値のままであったので、ディスエーブル・モードが使用され、1kΩ と100 kΩ の抵抗が並列でグラウンドに接続されます。

図 5. コンフィギュレーション・レジスタ・バンク

測定結果

DAC ディスエーブル時間

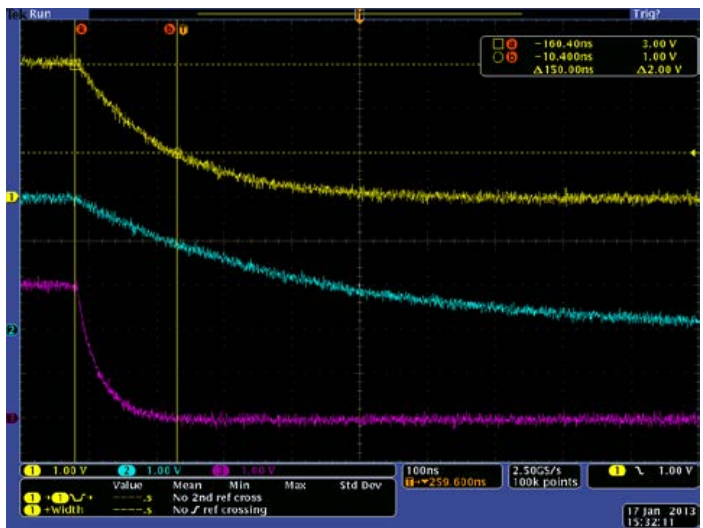

DAC ディスエーブル時間を調べるときに、GPIO2/DACDISABLE0 レジスタのビット[D0:D2]は1 に設定されていたので、DAC 出力VOUT0~VOUT3 はディスエーブルです。DAC 出力の電圧が3 V から1 V に低下するまでの時間を、Tektronix TDS 3054オシロスコープを使って計測しました(図6 を参照)。

図 6. DAC ディスエーブル・タイミングのオシロスコープ・プロット

| DAC Output | Load Capacitance | Oscilloscope Trace | Time for VOUTx to Decrease from 3 V to 1 V (Typ) |

| VOUT0 | 100 p F | Yellow | 150 ns |

| VOUT1 | 330 pF | Blue | 380 ns |

| VOUT2 | 0 pF | Pink | 40 ns |

DAC イネーブル時間

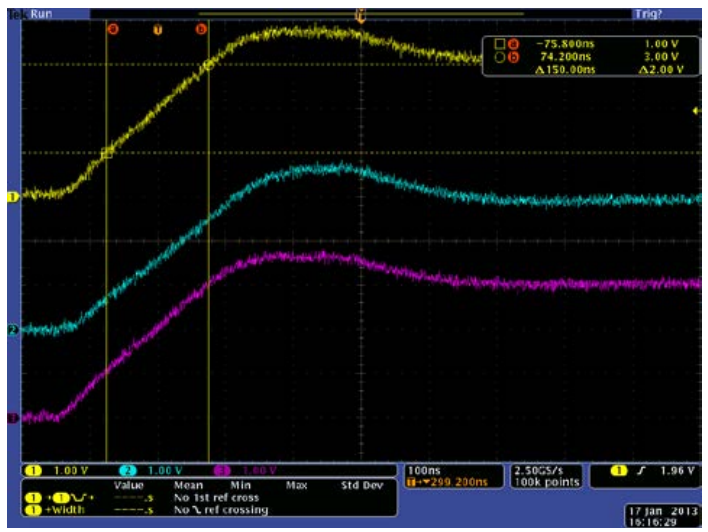

完全性を期すために、逆方向の遷移時間も測定しています。DAC出力は、GPIO2/DAC DISABLE0 レジスタのビット[D0:D2]に0 を書き込んで再度イネーブルにしました。DAC 出力の電圧が1 Vから3 V に上昇するまでの時間を計測しました(図7 を参照)。

図 7. 逆方向のタイミング

| DAC Output | Load Capacitance | Oscilloscope Trace | Time for VOUTx to Decrease from 3 V to 1 V (Typ) |

| VOUT0 | 100 p F | Yellow | 150 ns |

| VOUT1 | 330 pF | Blue | 164 ns |

| VOUT2 | 0 pF | Pink | 150 ns |