LDO設計とアプリケーションの基礎

LDO設計とアプリケーションの基礎

- ADI Linear Regulator設計ツール /パラメータによる検索 をダウンロードする

- LDO設計とアプリケーションの基礎 (pdf)

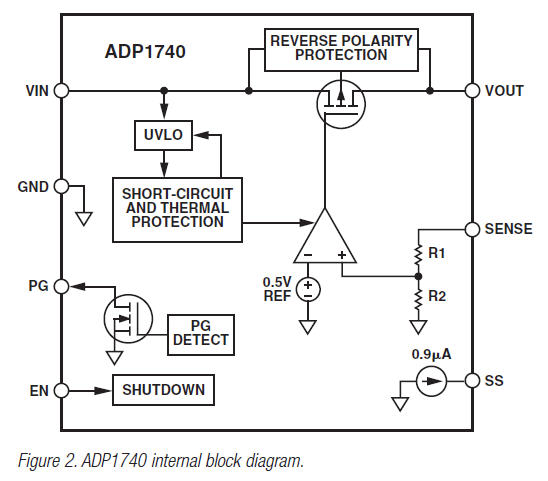

低ドロップアウト・レギュレータ(LDO)は、図1に示すように、電圧リファレンス、誤差アンプ、帰還分圧器、および直列パス・エレメント(通常はバイポーラまたはCMOSトランジスタ)から構成されます。出力電流はPMOSトランジスタによって制御され、PMOSトランジスタは誤差アンプによって同様に制御されます。このアンプは、出力からの帰還電圧をリファレンス電圧と比較し、その差を増幅します。帰還電圧がリファレンス電圧より低い場合は、PMOSデバイスのゲートがローに制御され、より多くの電流が流れて出力電圧が増大します。帰還電圧がリファレンス電圧より高い場合は、PMOSデバイスのゲートがハイに制御され、より少ない電流が流れて出力電圧が減少します。これは、誤差アンプ/パス・トランジスタの内部ポールと、出力コンデンサの等価直列抵抗(ESR)の外部ポールという、2つの主ポールをベースにしたクローズド・ループ・システムです。

アナログ・デバイセズのLDOは、推奨コンデンサの使用時に、仕様規定された動作温度と電圧範囲にわたって安定であるように設計されています。出力コンデンサのESRは、LDO制御ループの安定性に影響を与えます。安定性のためには、1Ω以下の最小ESRを推奨します。負荷電流の急激な変化に対するLDOの応答(つまり過渡応答)も、出力容量の影響を受けます。大きな値の出力コンデンサを使用すると、LDOの過渡応答は改善されますが、起動時間は増えることがあります。

LDOレギュレータは、主電源またはバッテリから低い出力電圧を得るために使用されます。この出力電圧は、理論上はライン/負荷変動に対して安定であり、周囲温度の変化に影響されず、時間に対して安定です。LDOでは、入力電圧と出力電圧の差(ドロップアウト電圧)をできるだけ低く抑える必要があります。たとえば、2.8VのLDOに接続されたリチウムイオン電池を使用するバッテリ駆動の設計では、バッテリ電圧が4.2V(完全充電)から3.0V(放電状態)まで降下します。一定の2.8V出力を提供するためには、LDOのドロップアウト電圧は200mV以下が必要です。システムによっては、LDOはポストレギュレーションに使用されます。LDOは、高効率スイッチング・レギュレータの出力に接続され、安定した一定の出力電圧を提供するだけでなく、ノイズ・フィルタ機能も提供します。