Overview

Design Resources

Design & Integration File

- Schematic

- PCB Layout

- ODB++ Files

- BOM

- Test Results

Description

The MAX17599 low IQ active clamp current mode pulsewidth modulation (PWM) controller contains all the control circuitry required for the design of isolated forward converter power supplies. The MAX17599 is optimized for low-voltage industrial (4.5VDC to 36VDC) power supply applications.

The device includes the two ground referenced MOSFET drivers, NDRV and AUXDRV, required to implement the active clamp transformer reset topology for forward converters. Programmable dead time between NDRV and AUXDRV enables low loss zero voltage switching (ZVS) over a wide load range.

The MAX17599 features a programmable switching frequency from 100kHz to 1MHz that allows the power supply designer to optimize the passive components in the power train, resulting in a compact, efficient, and cost-effective isolated power supply. It incorporates adjustable switching-frequency dithering that enables low EMI spread spectrum operation.

Features & Benefits

- 20µA Startup Current in UVLO

- Programmable Input Under-Voltage Lockout

- Programmable Input Over-Voltage Protection

- Switching Frequency Synchronization

- Adjustable Soft-Start

- Programmable Slope Compensation

- Fast Cycle-by-Cycle Peak Current Limit

- 70ns Internal Leading Edge Current Sense Blanking

- Hiccup Mode Output Short Circuit Protection

Parts Used

Details Section

The MAX17599 low IQ active clamp current mode pulsewidth modulation (PWM) controller contains all the control circuitry required for the design of isolated forward converter power supplies. The MAX17599 is optimized for low-voltage industrial (4.5VDC to 36VDC) power supply applications.

The device includes the two ground referenced MOSFET drivers, NDRV and AUXDRV, required to implement the active clamp transformer reset topology for forward converters. Programmable dead time between NDRV and AUXDRV enables low loss zero voltage switching (ZVS) over a wide load range.

The MAX17599 features a programmable switching frequency from 100kHz to 1MHz that allows the power supply designer to optimize the passive components in the power train, resulting in a compact, efficient, and cost-effective isolated power supply. It incorporates adjustable switching-frequency dithering that enables low EMI spread spectrum operation.

Other features include:

- 20µA Startup Current in UVLO

- Programmable Input Under-Voltage Lockout

- Programmable Input Over-Voltage Protection

- Switching Frequency Synchronization

- Adjustable Soft-Start

- Programmable Slope Compensation

- Fast Cycle-by-Cycle Peak Current Limit

- 70ns Internal Leading Edge Current Sense Blanking

- Hiccup Mode Output Short Circuit Protection

An active clamp forward DC-DC converter (ACFC) using the MAX17599 is demonstrated for a 24VDC output application. The power supply delivers up to 2A at 24V. An overview of the design specification is shown in Table 1.

| Parameter | Symbol | MIN | MAX |

| Input Voltage | VIN | 18V | 36V |

| Switching Frequency | fSW | 250kHz | |

| Peak Efficiency | η | 93% | |

| Duty Cycle | D | 31% | 63% |

| Output Voltage | VOUT | 23.76V | 24.24V |

| Output Voltage Current | ∆VOUT | 240mV | |

| Output Current | IOUT | 0A | 2A |

| Output Power | POUT | 48W | |

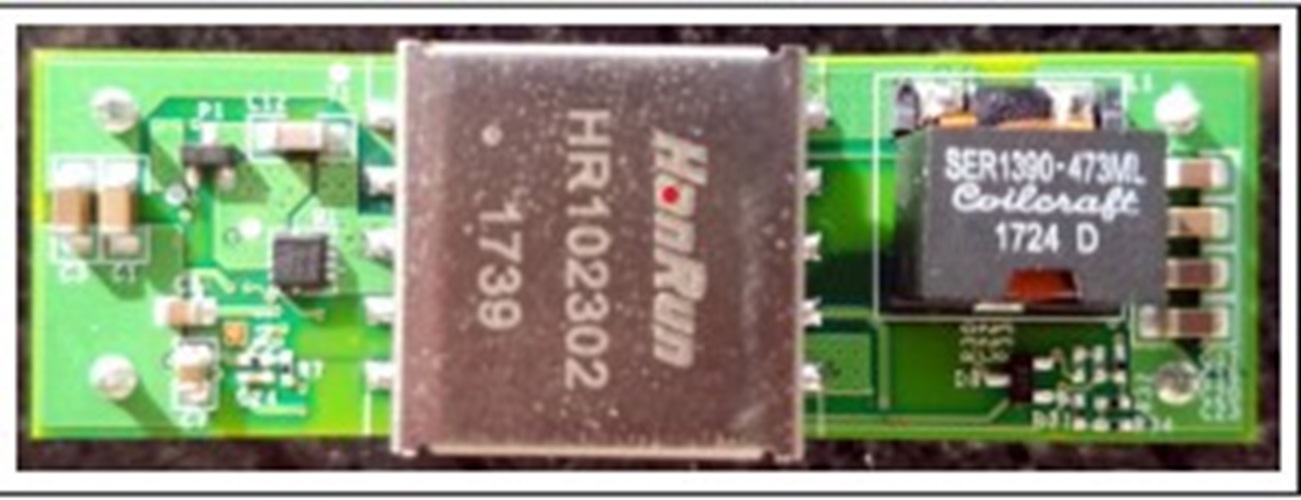

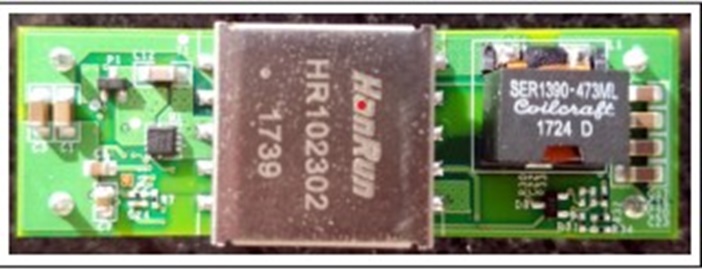

This application note describes the hardware shown in Figure 1. It provides a detailed systematic technical guide to design an ACFC using Analog Devices' MAX17599 current mode controller. The power supply has been built and tested, details of which follow in this document.

Single-ended forward converters have always been a favorite of designers for single and multiple output power supplies in the range of watts to kilowatts. In this topology, a second out-of-phase winding (reset winding) is used to reset the magnetic flux in the power transformer's core while the secondary-side freewheeling diode is conducting. If the number of turns on this winding is equal to the number of turns on the main transformer's primary winding, the drain-source voltage of the main power switch is limited (excluding ringing due to leakage inductance and parasitic capacitance in the circuit) to two times the input voltage of the power supply, but so, too, is the maximum duty cycle limited to less than 50%. This duty cycle limit can be extended above 50% to improve transformer utilization by increasing the number of turns on the reset winding but only at the expense of a higher drain-source voltage (increased voltage stress and switching power losses) on the main power switch.

These and other limitations of the forward converter can easily be overcome when the designer fully understands the operation and unique benefits of the ACFC topology.

The main components of an ACFC are shown in Figure 2. The active clamp comprises a P-channel MOSFET (QAUX) and a clamp capacitor CCLAMP. The difference between the traditional forward converter and the ACFC occurs when main power MOSFET (QMAIN) is off. The reset winding and diode of the traditional forward converter clamps the drain-source voltage of QMAIN to approximately twice the power supply input voltage during the first half of the interval when QMAIN is off, whereas in the ACFC the drain-source voltage of QMAIN will be clamped to an intermediate voltage between VIN and 2 VIN for the full interval when QMAIN is off.

The benefits of the ACFC topology go far beyond reducing the voltage stress on the main power MOSFET and increasing the duty cycle limit.

Further benefits provided by the ACFC topology are as follows:

- Zero voltage switching (ZVS) can be achieved for QMAIN and QAUX over the full load range by careful design, thus significantly improving power supply efficiency.

- A smaller output inductance can be used due to higher operating duty cycle.

- Operating at a duty cycle higher than 50% allows a higher secondary-to-primary turns ratio on the transformer leading to a lower reflected current from the secondary to primary, and thus a lower peak current in the main power MOSFET.

- Lower EMI due to the ZVS nature of the switching.

Figure 3 shows the main steady state waveforms of the ACFC.

It is important to understand what is happening during one complete switching cycle of the converter. The table below describes what occurs at each time interval of the switching cycle.

| Interval | Description |

| t0 - t1 | QMAIN turns on at t0. QAUX remains off. The primary current IP, which is the sum of the transformer magnetizing IMAG and the reflected secondary current ISEN, flows through the primary of the transformer and QMAIN. IP ramps up linearly while QMAIN is on. Current also flows in the secondary side through the rectifying MOSFET QR while QMAIN is on. No current flows through QAUX during this interval. |

| t1 - t2 | QMAIN turns off at t1. The current in the primary of the transformer is now zero. The reflected secondary current component of IP is zero. IP is now only the transformer magnetizing current. It decreases toward zero, charging the drain capacitance of QMAIN, CdMAIN. |

| t2 - t3 | At t2 the drain voltage of QMAIN reaches the same voltage level as that voltage across CCLAMP, the body diode of QAUX becomes forward-biased and voltage across CCLAMP increases. The rate of increase of the drain voltage of QMAIN is now much lower, because CCLAMP >> CdMAIN. |

| t3 - t4 | At t3 QAUX turns on. QAUX switches under the ZVS condition providing it turns on after its body diode starts conducting (at t2) and before IP goes negative (at t4). QAUX must be on before t4, otherwise IP has no path to go negative at t4. |

| t4 - t5 | At t4 IP is now negative and is discharging CCLAMP through QAUX, which is on. IP continues to become more negative and the drain voltage of QMAIN decreases. QAUX turns off at t5 and the voltage across CCLAMP stops decreasing. The only current path now available for the negative IP to flow is out of CdMAIN. The voltage across CdMAIN decreases until IP reaches zero. VDS decays to zero by t6 providing the energy stored in the magnetizing and leakage inductance at t5 is greater than the energy stored in CdMAIN at t5. ZVS occurs if this condition is met, otherwise QMAIN switches on at t6 at some intermediate voltage between zero and VDSMAX. |

IMPORTANT: Reducing LMAG increases the inductive energy stored in LMAG so if LMAG is too big, ZVS does not occur as shown by the dashed line on the VDS graph.

Now that the principle of operation of the ACFC is understood a practical design example can be illustrated. The converter design process can be divided into several stages: power stage design, setup of the MAX17599 ACFC current mode controller, and the feedback loop. This document is primarily concerned with the power stage design, and the feedback loop is intended to complement the information contained in the MAX17599 data sheet for details on how to set up supervisory and protection functions of the controller.

The following design parameters are used throughout:

| Parameter | Symbol |

| VIN | Input Voltage |

| VSTART | Undervoltage Turn-on Threshold |

| VOVI | Overvoltage Turn-off Threshold |

| tSS | Soft-Start Time |

| VOUT | Output Voltage |

| ΔVOUT | Output Ripple Voltage |

| IOUT | Output Current |

| POUT | Output Power |

| η | Target Maximum Efficiency |

| PIN | Input Power |

| fSW | Switching Frequency |

| D | Duty Cycle |

| n | Primary-Secondary Turns Ratio |

| NP | Turns of Primary Winding |

| NS | Turns of Secondary Winding |

| NSD | Turns of Secondary Self-Driven |

The above symbols are sometimes followed by parentheses to indicate whether minimum or maximum values of the parameters are intended; for example, minimum input voltage is intended by the symbol VIN(MIN). Otherwise, typical values are intended.

In addition, through the design, procedure reference is made to the schematic in another document.

Step 1: Choosing a Suitable Switching Frequency

The MAX17599 can operate at a switching frequency between 100kHz and 1MHz. A lower switching frequency optimizes the design for efficiency, whereas a higher frequency allows for smaller inductive and capacitive components as well as lower costs. A switching frequency of 250kHz was chosen for this design. R1 sets the switching frequency according to the following expression:

Step 2: Setting the Maximum Duty Cycle

One advantage of using the MAX17599 for the ACFC is the maximum allowable duty cycle. If the duty cycle is not clamped at some maximum value, transformer saturation can occur, resulting in catastrophic failure, and QMAIN can be subjected to increased voltage stress. A maximum duty cycle of 72.5% is recommended at switching frequencies up to 400kHz. An initial choice of 63% allows for some design margin.

Step 3: Calculating the Transformer Turns Ratio

For the forward converter topology, the transformer turns ratio is given by the following expression:

where VMDS(ON) is the drain-source voltage of QMAIN in the on state, VRDS(ON) is the drain-source voltage of QQR in the on state, and VLOUT is the resistive DC voltage drop across the output inductor winding. DMAX occurs at VIN(MIN). Assuming VMDS(ON) = 0.2V, VRDS(ON) = 0.2V, and VLOUT = 0.2V then,

Step 4: Calculating Turns of the Primary Winding NP, Secondary Winding NS, Secondary Self-Driven Winding NSD

For the forward converter topology, the transformer turns of the primary winding is given by the following expression:

where ∆B is the Flux density deviation of the transformer, which should be below or equal to 2000GS, Ae is the effective magnetic cross-section of the transformer core. Considering the maximum output power and the size of this design, we chose EFD20 as the transformer core. The effective magnetic cross-section of EFD20 is 0.31cm2, then,

We use eight turns for the primary winding; for the secondary turns,

We use 17 turns for the secondary winding, then,

The secondary self-driven voltage VSD of the rectifying MOSFET and freewheeling MOSFET is 5V.

We use four turns for the secondary self-driven winding.

Step 5: Calculate D at VIN(TYP) and VIN(MAX)

Re-arranging the expression in step 3 above gives

And,

| DMIN | DTYP | DMAX |

| 0.32 | 0.48 | 0.64 |

Step 6: Calculate VMDS(MAX) of QMAIN at DMIN, DTYP and DMAX

For the forward converter topology, VMDS is given by the following expression:

Given the DMAX occurs at VIN(MIN), DTYP occurs at VIN(TYP), and DMIN occurs at VIN(MAX), we have

| VMDS at VIN(MAX) | VMDS at VIN(TYP) | VMDS at VIN(MIN) |

| 53V | 46V | 50V |

The critical operating parameters of the converter are now fixed, so it is possible to continue the design process of calculating and selecting suitable components for the power train.

Step 7: Calculating and Selecting LOUT

The output inductance is calculated assuming a maximum peak-to-peak output ripple (∆ISEC), which occurs at maximum input voltage. The output inductance can be calculated as follows:

Where VDSFW is the drain-source voltage of the secondary freewheeling MOSFET, %∆ISEC (0.6, typical) is the ratio of peak-to-peak output inductor current ripple to the average output current at maximum input voltage. We have

Where IOUT = 2A and VDSFW = 0.2V.

In this design, we can choose a standard ±20% tolerance 47µH inductor.

Finally, we must choose an output inductor with a DC winding resistance that is sufficiently low to ensure that VLOUT is less than 0.2V at IO(MAX), because this is the value we have used for VLOUT in the preceding calculations. We should choose an inductor with

The final inductor value chosen for this design is a 20% tolerance 47µH/7.7A/23.1mΩ inductor.

Step 8: Calculate the Transformer Magnetizing Inductance LMAG and the Secondary and Primary Peak Winding Currents, IS(PK) and IP(PK)

The physical design of the power transformer is outside the scope of this document; however it is necessary to calculate the critical parameters of the transformer.

We must first calculate the minimum output inductor ripple current by rearranging the expression in Step 7 and remembering that minimum ripple occurs at DMAX as follows:

LOUT(MAX) for the selected ±20% 47µH inductor is 56.4µH. So,

For the MAX17599 ACFC current mode controller to function properly the maximum magnetizing current referred to the primary side of the transformer must be less than the minimum output inductor ripple current reflected to the primary side of the transformer. So:

And,

To allow for design margin we chose a value for IMAG = 1.1A (85% of IMAG(MAX)).

The next step is to calculate a minimum magnetizing inductance that ensures that IMAG(MAX) < 1.1A. We use the following expression to calculate LMAG(MIN):

So,

Allowing for a ±30% tolerance for the magnetizing inductance we can choose LMAG = 60µH ±30%.

Figure 4 illustrates the output inductor current IL, the secondary transformer current IS, primary transformer current IP and the current flowing in main power MOSFET, IQM.

Although IP appears linear when both IQM and IQA are off (t1 to t3 and t5 to t6), there is a resonance between the two end points, which makes ZVS possible.

The peak current in the secondary winding IS(PK) is equal to the peak current in the output inductor IL(PK). IL(PK) is a maximum at VIN(MAX) and IOUT(MAX), therefore:

And,

IS(PK) = IL(PK)

So,

The peak current in the primary winding IP(PK) is the peak current in the secondary winding reflected back to the primary side of the transformer plus IMAG.

Therefore,

So,

The transformer must not saturate at a magnetizing force of (NP x IP(PK)) where NP is the number of turns on the primary winding.

Step 9: Calculate the Maximum RMS Currents in the Transformer Secondary and Primary Windings, IS(RMS) and IP(RMS)

The maximum RMS currents in the transformer primary and secondary windings occur at VIN(MIN) and IOUT(MAX), i.e., at DMAX. To calculate IS(PK) at VIN(MIN) we must first calculate IL(PK) in the output inductor at VIN(MIN).

Following the process of Step 8 we have,

At VIN(MIN),

And,

IS(PK) = IL(PK)

So,

The current at which the secondary rectifying MOSFET QR starts to conduct IS(V), corresponds to IL(MIN).

So,

We can now calculate the maximum RMS current in the secondary winding as follows:

So,

Referring to Figure 4, we can calculate the instantaneous current in QM at turn-on and turn-off, IQM(t-on) and IQM(t-off), respectively.

So,

The maximum RMS current in QM can now be calculated as follows:

The transformer primary current IP in Figure 4 is a more complex waveform that IQM. IP is a superposition of IQM and IQA, and the resonant currents that flow during the time intervals when both QM and QA are off. Nevertheless, it is reasonable to use the approximation that

We now have all the critical parameters of the transformer, as detailed in the following table.

| Parameter | Symbol | Value |

| Primary Magnetizing Inductance | LMAG | 60µH ±30% |

| Primary Peak Current | IP(PK) | 6.8A |

| Primary RMS Current | IP(RMS) | 3.88A |

| Turns Ratio (NS/NP) | n | 0.47 |

| Primary Turns | NP | 8 |

| Secondary Turns | NS | 17 |

| Secondary Self-Driven Turns | NSD | 4 |

| Secondary Peak Current | IS(PK) | 2.36A |

| Secondary RMS Current | IS(RMS) | 1.6A |

Using the parameters in the table above, a suitable transformer can be designed.

Step 10: Choose a Suitable MOSFET for QM

All the necessary parameters for selecting a suitable QM have already been calculated.

From step 6, VDS(MAX) = 53V.

From step 8, IQM(PK) = IIP(PK) = 6.8A.

And IQM(RMS) = 3.87A.

Allowing for reasonable design margin, Vishay part number SIS468DN-T1-GE3 was chosen for this design with the following specifications:

| Function | Value |

| Maximum D-S Voltage | 80V |

| Continuous Drain Current | 30A |

| D-S Resistance at VGS = 4.5V | 32mΩ |

| Total Gate Charge Qg | 8.7nC |

Step 11: Choose Suitable Rectifying and Freewheeling MOSFET for QR and QFW, Respectively

Almost all the necessary parameters for selecting a suitable QR have already been calculated. In step 8, we calculated IS(PK), the same peak current that flows in QR.

So,

In step 9, we calculated the maximum RMS current in the transformer secondary winding IS(RMS), the same RMS current that flows in QR.

So,

The peak drain-source voltage seen by QR is given by

So,

For the freewheeling MOSFET QFW we have

The maximum RMS current in the freewheeling diode occurs at VIN(MAX) and is calculated using

Where,

So,

Finally, the peak drain-source voltage seen by QFW is given by

Allowing for a reasonable design margin, a Vishay n-MOSFET, part number SISS40DN-T1-GE3, was selected for both QR and QFW.

Step 12: Choose Suitable P-Channel MOSFET for the Active Clamp Switch QA

Only a portion of the primary magnetizing current flows in the drain of the active clamp switch during the interval between t3 and t5. If we assume as the worst case that all the magnetizing current flows in QA, then we can estimate the RMS current flowing in the drain of QA as follows:

At such a low RMS current, conduction losses will be very low, so choosing a MOSFET with a low gate charge should be the primary consideration, with low RDS(ON) being only a secondary concern. In addition to conduction losses being very low, switching losses are also negligible, because the body diode of QA is conducting before QA turns on. The repetitive peak current in QA is the maximum primary magnetizing current:

The active clamp switch will experience the same voltage stress as the main power switch;referring to step 6 this is as follows:

Allowing for reasonable design margin, Vishay P-Channel MOSFET, Si2337DS, was chosen for this design, with the following specifications:

| Function | Value |

| Maximum D-S Voltage | 80V |

| Peak Repetitive Drain Current | 2.2A |

| D-S Resistance at VGS = 7V | 0.215Ω |

Step 13: Choose a Suitable Clamp Capacitor C12

The clamp capacitor (C12) helps in resetting the flux in the transformer core as well absorbing leakage inductance energy, and it forms a complex pole-zero pair with the magnetizing inductance (LMAG) of the transformer, at a frequency fR.

The value of the clamp capacitor for a 20% voltage ripple is calculated as:

We chose 22nF as the clamp capacitor.

The voltage stress on the clamp capacitor can be calculated as:

The C12 should be rated for at least 1.4x the calculated worst-case VC12 stress.

Step 14: Calculate and Choose the Output Capacitor COUT

Output capacitance value can be calculated based on either steady-state voltage ripple or transient voltage ripple. If the design consideration is the transient steadystate voltage ripple, then the output capacitor is usually sized to support a step load of 25% of the rated output current (IOUT) in isolated applications so that the output-voltage deviation is contained to 3% of the rated output voltage. The output capacitance can be calculated as follows:

where COUT is the total capacitance required at the output, ISTEP is the load step, tRESPONSE is the response time of the controller, and ∆VOUT is the allowable output voltage deviation during transient.

Response time of the controller tRESPONSE is given as

The complex pole-zero pair frequency formed due to clamp capacitor and magnetizing inductance of the converter is given as

fC is the target closed-loop crossover frequency, which is given as

So, the response time of the controller tRESPONSE is given as

Choose ISTEP equal to 25% of output current, ISTEP, ∆VOUT = 3% of output voltage, which is equal to 720mV.

So, the output capacitance is given as

In this design, to get smaller output voltage ripple, 4 x 10µF ceramic capacitors are used. Considering 20% derating of the ceramic capacitors, the total ceramic output capacitance would be 4 × 10µF × 0.8 = 32µF.

Step 15: Calculate and Choose the Input Capacitor CIN

Capacitor selection is based on switching ripple. The maximum average input current drawn from the input power supply at minimum input voltage can be calculated as

The voltage ripple present on the input capacitor is 2% of the minimum input voltage and is given as

The value of the input ceramic capacitor with the above assumed ripple voltage can be calculated as follows:

In this design, 3 × 10µF ceramic capacitors are used for the input capacitor.

Step 16: Calculating and Selecting the UVLO and OVI Resistor

Figure 5 illustrates how undervoltage lockout (UVLO) and overvoltage inhibit (OVI) are implemented in this design. The EN/UVLO pin on the MAX17599 serves as an enable/ disable input, as well as an accurate programmable UVLO pin. MAX17599 operation is only guaranteed when the voltage on the EN/UVLO pin exceeds 1.26V. Once operating, the MAX17599 continues to operate, providing the voltage on the EN/UVLO pin exceeds 1.20V.

The OVI pin on the MAX17599 serves as an accurate programmable OVI input. The MAX17599 is guaranteed to shut when the voltage on the OVI pin exceeds 1.26V. Switching is guaranteed to resume only when the voltage on the OCI pin falls below 1.1V. In this instance, the MAX17599 performs the soft-start sequence.

Because R11, R7, and R6 are applied across VIN, the starting point for choosing appropriate values for these resistors is setting a limit for the maximum power PIVP dissipated in the resistors. By choosing a maximum allowable power loss in the resistor divider R11, R7, R6, we can calculate the maximum current in the resistors at VIN(OVI) as follows:

At VIN(OVI) the voltage across R4 should be 1.26V to ensure OVI shutdown, so,

At VIN(UVLO) the current in the resistors R11, R7, R6 is

At VIN(UVLO) the voltage across (R4+R7) should be 1.26V to ensure start-up of the MAX17599 at the UVLO threshold, so,

Substituting for R4, we have

at VIN(UVLO):

and

Substituting for VR5 we have

For this design, we have set PIVP = 2mW, VIN(OVI) = 38V, and VIN(UVLO) = 16V. The closest standard values for R11, R7, and R6 are 680kΩ, 30kΩ, and 24kΩ, respectively.

Step 17: Calculating and Selecting the Peak Current Limit Resistor (R18)

The current sense resistor R18 is connected between the source of QMAIN and PGND. This resistor sets the peak current limit of the power supply. When QMAIN is on the primary transformer current IP flows through R18 and the voltage developed across R18 is measured at the CS pin of the MAX17599.

The MAX17599 implements 70ns of leading-edge blanking to suppress leading edge-current spikes that might be encountered due to circuit and component parasitic. An additional RC filter (R17, C11) can be placed between the source of QMAIN and the CS pin of the MAX17599 to increase the amount of leading-edge blanking.

The signal voltage obtained at the CS pin is used for current mode control and peak current limiting purposes. A voltage of 305mV on the CS pin terminates the NDRV and AUXDRV drives to the MOSFETs until the next switching cycle begins.

R18 can be calculated so that when the peak primary current (plus 50% design margin) is flowing in QMAIN, the voltage across R21 is 305mV, so,

A standard 20mΩ current sense resistor is used in the design. A low inductance current sense resistor should be used for R18.

Step 18: Calculating and Selecting the Dead-Time Resistor (R3)

Placing dead-time between the NDRV and AUXDRV drive edges allows ZVS to occur, minimizing switching losses and improving efficiency. Resistor R8 connected from the DT pin of the MAX17599 to SGND programs the amount of dead-time. This amount of dead time is applied to both leading and trailing edges of the drive signals. A deadtime between 25ns and 250ns can be calculated by:

Where R3 is in kΩ and tDT is in ns. A value of 100k is chosen to give a dead-time of 250ns. The dead-time can be increased by experiment to ensure ZVS across the widest range of line and load conditions.

Documentation & Resources

-

MAXREFDES1051 Design Files5/19/2021ZIP9 M

-

EE-Sim OASIS Free Simulator7/9/2019

-

MAXREFDES1051: 24V/2A, Active Clamp Forward DC-DC Converter Using MAX175997/9/2019PDF594 K

Support & Training

Search our knowledge base for answers to your technical questions. Our dedicated team of Applications Engineers are also available to answer your technical questions.