Overview

Product Details

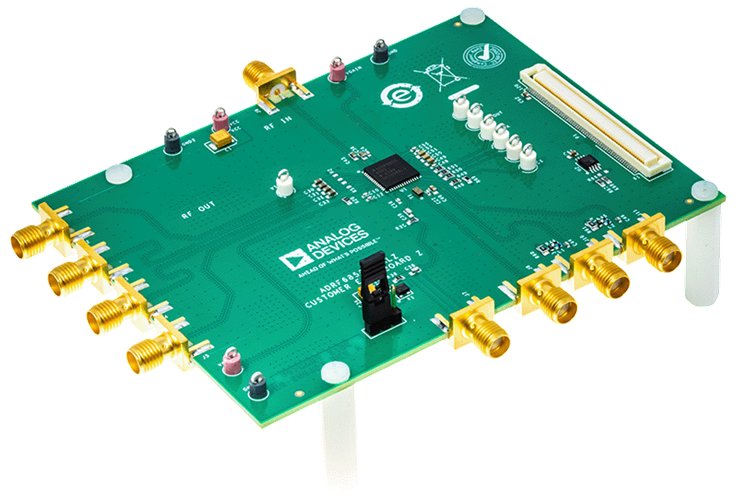

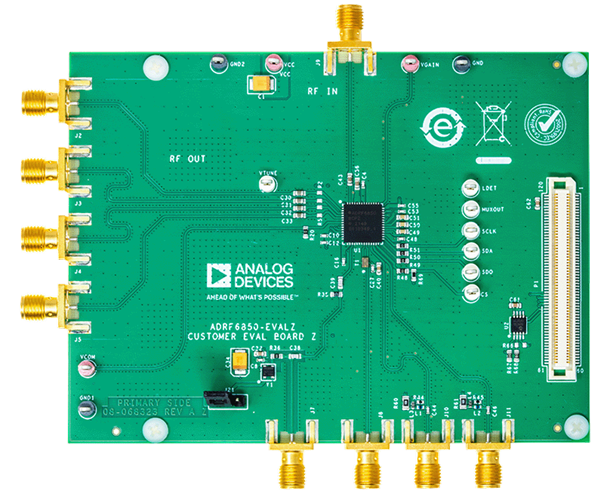

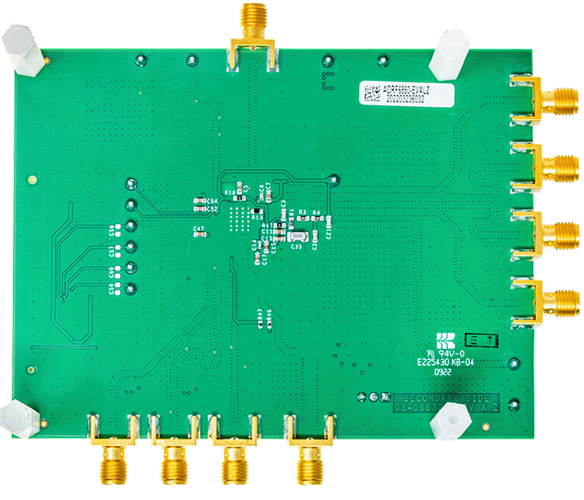

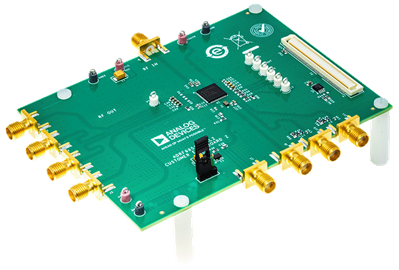

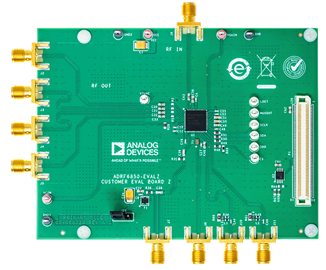

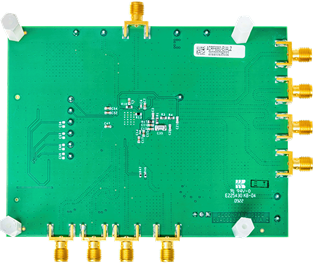

The ADRF6850-EVALZ evaluates the performance of the ADRF6850. The evaluation board contains the ADRF6850, a connector suited for the SDP-S controller board, power supply connectors, subminiature Version A (SMA) connectors, and on-board 13.5MHz reference oscillator. The ADRF6850-EVALZ requires an SDP-S controller board and a Labview-based software to program the ADRF6850.

The ADRF6850 evaluation board documentation provides additional information and should be consulted when using the evaluation board.

Applicable Parts

Documentation & Resources

-

ADRF6850-EVALZ - Design Files7/19/2017ZIP3 M