ADI公司最新的PLL⁄VCO器件ADF4371提供极为出色的低相位噪声和杂散性能

简介

随着人们对通信系统的频率带宽、吞吐量和动态范围的需求日益提高,同时还要求毫米波5G使用更高的天线频率,因此对于通信系统或混合信号系统中使用的本地振荡器(LO)或时钟的质量也分别提出了更高的要求。

新推出的集成压控振荡器(VCO)的锁相环(PLL)ADF4371以及类似的 ADF4372, 都充分体现了ADI公司为满足这些严苛的应用需求所付出的努力。

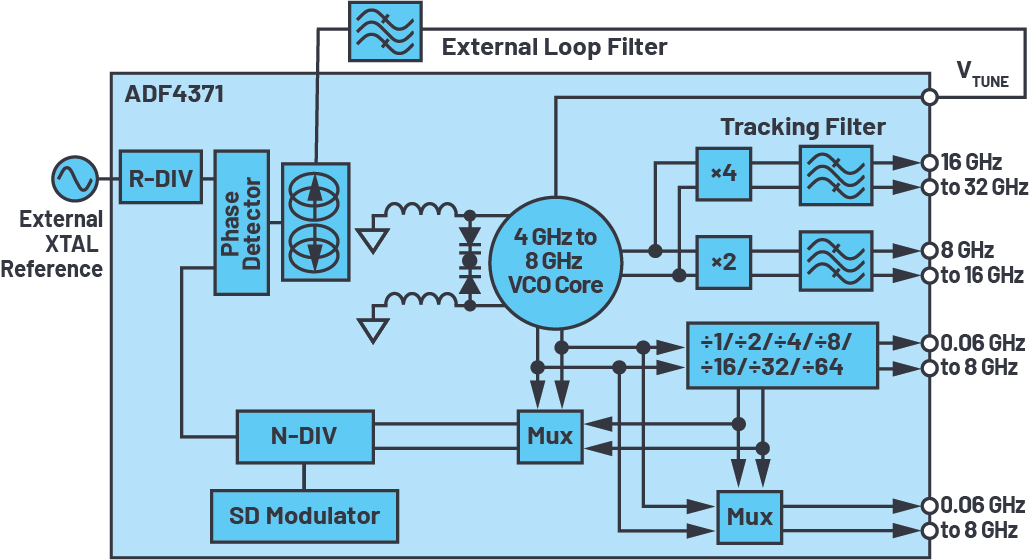

图1. ADF4371框图。

频率覆盖范围

为了尽可能扩大频率覆盖范围,ADF4371/ADF4372 的VCO可覆盖4 GHz至8 GHz的倍频范围,此外,通过在输出端使用分频器,进行1/2/4/8/16/32/64分频,能够在主输出端RF8实现62.5 Mhz至8000 MHz之间的全频覆盖。同时提供完全相同的第二个输出,支持用户驱动转换器时钟。对于8 GHz输出频率,在100 kHz偏置下,VCO的开环相位噪声为–109 dBc/Hz。

直到最近,生成高频率还需要使用外部倍频器,该器件通常采用GaAs工艺制造,通常需要进行额外的滤波和放大,以解决滤波带来的问题。

为了获得更高频率,ADF4371/ADF4372集成了一个倍频器,通过差分引脚RF16提供8 GHz至16 GHz的输出。ADF4371还配有四倍频器,在差分输出端RF32生成16 GHz至32GHz的输出。为了较大限度降低生成的倍频器噪声,ADF4371/ADF4372内置跟踪滤波器,以优化实现所需频率的功率等级,同时抑制倍频器噪声。在二倍频输出端,VCO馈通噪声为–45 dBc。在四倍频输出端,噪声被抑制在约为–35 dBc的水平。

适合转换器时钟应用的出色PLL性能

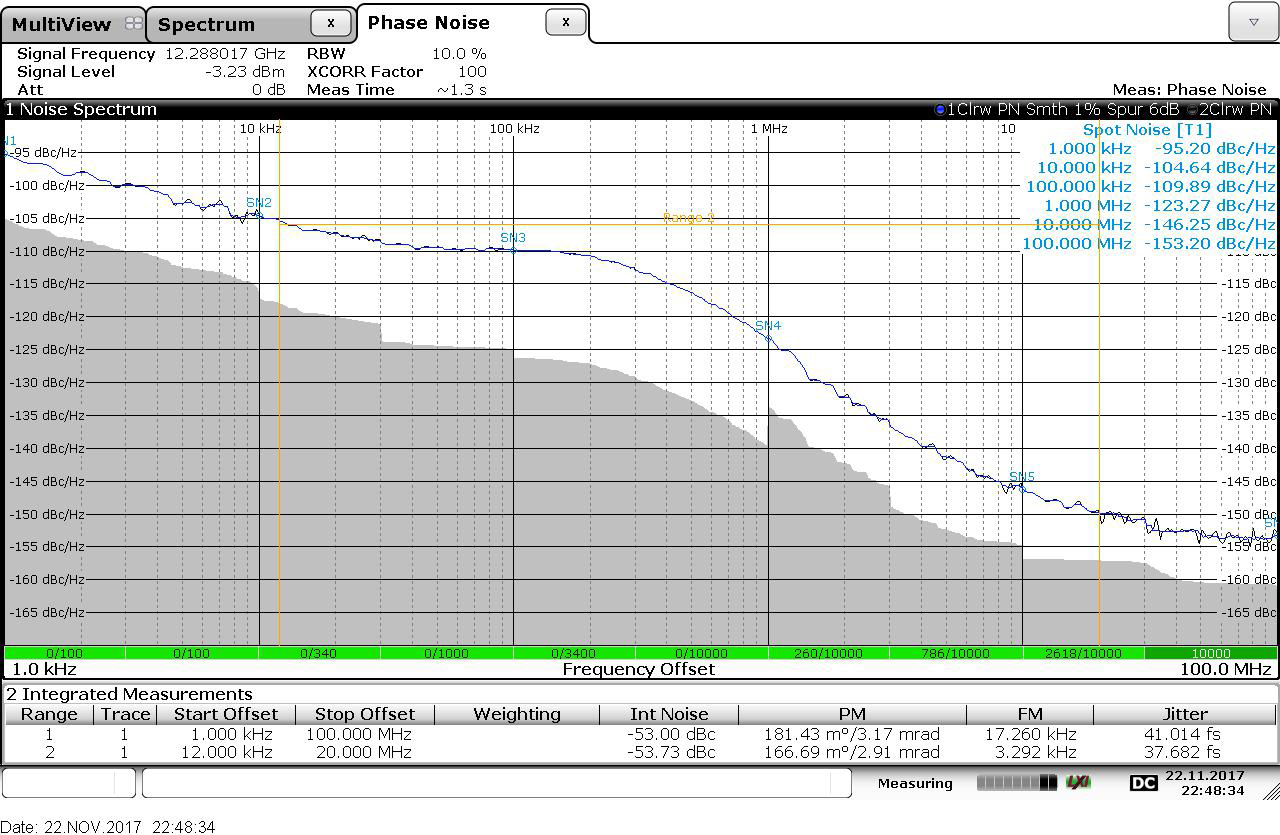

对PLL电路实施改进意味着ADF4371/ADF4372产品的PLL品质因数可以低至–234 dBc/Hz,在同时具有–127 dBc/Hz的低1/f噪声(在1 GHz标称输出频率下,10 kHz偏置)时,用户就可以实现低至40 fsrms抖动量(1 kHz至100 MHz积分范围)的时钟,非常适合要求严苛的转换器时钟应用。为了尽可能减少环路中可能出现的电阻噪声, 建议使用简单的低通滤波器,并使用小阻值。要实现低噪声目标,必须使用高频率(250 MHz,或在使能基准频率倍频器时,使用125 MHz)超低噪声的参考源。对于整数N分频应用,鉴频鉴 相器(PFD)的最大工作频率可达到 250 MHz。倍频VCO差分输出RF16可直接连接至一些ADI转换器,无需使用会增加成本和提高性能的外部巴伦电路。6.144 GHz至12.288 GHz的性能不会恶化。

图2. 6.144 GHz时的RMS抖动。

通信和仪器仪表LO

对于无线和仪器仪表应用,ADF4371/ADF4372内置的39位分辨率∑-∆调制器,可以实现0Hz频率误差的亚毫赫兹级(submillihertz)的分辨率。在这种情况下,ADF4371 PFD能够以最大160 MHz PFD频率运行。在这些应用中,ADF4371/ADF4372提供< 48 fs的rms抖动。ADF4371还具有行业较领先的PLL杂散性能,PFD杂散低至–100 dBc,未滤波的整数边界杂散低至–55 dBc。这种性能水平极大简化了频率规划工作,可缩短产品上市时间。许多小数N分频PLL和VCO器件采用罕有的小数N分频杂散机制,会导致额外的未知特性和频率规划工作,由此增加复杂性和成本。

图3. 12.288 GHz时的RMS抖动。

小尺寸

ADF4371/ADF4372 PLL/VCO器件采用7 mm × 7 mm、48引脚基板栅格阵列(LGA)封装。只需极少的额外去耦,因此可以使用小型解决方案实现出色性能。

为实现优质性能,建议使用优质低压差(LDO)稳压器,例如 ADM7150 或 LT3045 VCO可以采用3.3 V或5 V电源,剩余部分的电路则由3.3 V电轨供电。ADF4371可以使用ADIsimPLL™进行仿真,以帮助用户设计实现整个PLL系统所需的适当外部元件电路。

结论

ADF4371具有行业较领先的频率覆盖范围、性能和小尺寸,可以满足新通信和仪器仪表系统的高要求。