AN-2064: ADF7030-1接收器降敏避除算

简介

由于时钟源与敏感的模拟和RF电路之间存在有限隔离,片上集成式收发器系统(SoC)经常会出现杂散现象。当收发器在特定的通道上以接收模式运行时,这些杂散现象可能导致其灵敏度降低(降敏)。解决降敏问题的传统方法是,在通道规划时将这些通道列入黑名单,从而避免使用这些通道。但是,减少通道数量会降低网络的容量,在跳频应用中,则会降低网络规避干扰的能力。

本应用笔记描述了适用于ADF7030-1的简单软件算法,可以有效避除某些杂散现象导致的降敏。使用此软件算法之后,无需再将通道加入黑名单,因此能够更充分地利用可用的频谱。

ADF7030-1

如果ADF7030-1接收器必须在通道化系统中按宽频段运行,例如902 MHz至928 MHz、863 MHz至876 MHz,或450 MHz至470 MHz,少量特定频率会因为杂散现象出现降敏。

一般来说,降敏主要由以下几种杂散现象导致:

- 时钟源的原始谐波在接收器的带宽范围中。

- 内部时钟的谐波与本地振荡器(LO)的高阶谐波混频,且落在接收器的基带带宽范围内。

软件算法要求主机在使用出现降敏问题的通道频率之前,先更改某些接收器设置。更改后的接收器设置会利用多个片上特性,将干扰源移到接收器的带宽范围之外,使ADF7030-1接收器能在该通道上实现全部的灵敏度。

寄存器设置

PROFILE_RADIO_DIG_RX_CFG和PROFILE_RADIO_AFC_CFG2寄存器中包含有在主机处理器上运行,必须作为软件算法的一部分进行修改的接收器设置。表1和表2描述了每个寄存器的位段。软件算法使用这些位段。

接收器配置寄存器

地址:0x20000300,复位:0x00000000,名称:PROFILE_RADIO_DIG_RX_CFG

| 位 | 位名称 | 描述 | 复位 | 访问 |

| [31:30] | DEMOD_SCALING | 由ADF7030-1设计中心生成,或由ADI公司提供 | 0x0 | R/W |

| [29:27] | 保留 | 设为0。 | 0x0 | R/W |

| 26 | 反转型 | 0:使用点积配置解调。 1:使用交叉乘积配置解调。 |

0x0 | R/W |

| [25:22] | ADC_ANALOG_CLK_DIVIDE | 相对于主时钟频率,对Σ-Δ模数转换器(ADC)时钟进行分频。 | 0x0 | R/W |

| [21:18] | DECIMATE_8XIF_CLK_DIVIDE | 相对于主时钟频率,对DECIMATE_8XIF_CLK进行分频。 | 0x0 | R/W |

| 17 | LOW_SIDE | 选择高端或低端注入。 0:高端注入。 1:低端注入。 |

0x0 | R/W |

| [16:13] | DEMOD_CORE_CLK_DIVIDE | 相对于主时钟,对解调核心时钟进行分频。 | 0x0 | R/W |

| 12 | DEMOD_PRODUCT_SEL | 点积/交叉乘积选择。 | 0x0 | R/W |

| [11:8] | DEMOD_POST_DEMOD_FILTER_BW | 由ADF7030-1设计中心生成,或由ADI公司提供。 | 0x0 | R/W |

| [7:0] | DEMOD_DISC_BW | 接收器鉴频器带宽。 | 0x0 | R/W |

自动频率控制(AFC)配置寄存器2

地址:0x20000320,复位:0x00000003,名称:PROFILE_RADIO_AFC_CFG2

| 位 | 位名称 | 描述 | 复位 | 访问 |

| [31:30] | 保留 | 保留。 | 0x0 | R |

| 29 | AFC_PRODUCT_SEL | 由ADF7030-1设计中心生成,或由ADI公司提供。 | 0x0 | R/W |

| 28 | AFC_INVERT | AFC反相。 | 0x0 | R/W |

| [27:22] | AFC_BW | AFC测量带宽(BW)。 | 0x0 | R/W |

| [21:19] | AFC_SAMPLE_RATE | 由ADF7030-1设计中心生成,或由ADI公司提供。 | 0x0 | R/W |

| [18:3] | AFC_INITIAL_CONDITION | 由ADF7030-1设计中心生成,或由ADI公司提供。 | 0x0 | R/W |

| [2:0] | AFC_MODE | 由ADF7030-1设计中心生成,或由ADI公司提供。 | 0x3 | R/W |

FCC PART 15频段内的降敏频率—902 MHz至928 MHz

用例

表3描述了本应用笔记中讲解的7个用例。其中也包含接收器和降敏带宽。降敏带宽设置为接收器带宽的1.5倍。

| 用例 | 数据速率 (kbps) | 频率偏差(kHz) | 最大频率误差(ppm) | 中频(kHz) | 接收器带宽(kHz) | 降敏带宽(kHz) |

| UC10 | 10 | 5.0 | 10 | 81.25 | 20.0 | 30.0 |

| UC12p5 | 12.5 | 50.0 | 10 | 180.55 | 135.42 | 203.13 |

| UC25 | 25 | 6.3 | 10 | 103.17 | 77.38 | 116.07 |

| UC50 | 50 | 25.0 | 10 | 135.42 | 101.57 | 152.35 |

| UC100 | 100 | 25.0 | 13 | 180.55 | 135.42 | 203.13 |

| UC150 | 150 | 37.5 | 25 | 270.83 | 203.12 | 304.68 |

| UC300 | 300 | 75.0 | 10 | 406.25 | 395.00 | 592.50 |

分类

表4至表10描述了使用902 MHz至928 MHz频段的7个用例的通道频率,这些频率因为杂散现象出现了接收器降敏。每个频率都分了类别,这种分类在软件算法中也有使用。

| 频率(MHz) | 导致接收器降敏的原因 | 软件算法可以解决问题 | 软件算法的分类 |

| 903.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 910.0 | 26 MHz晶体(XTAL)的谐波 | 否 | 不适用 |

| 916.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 923.0 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 频率(MHz) | 导致接收器降敏的原因 | 软件算法可以解决问题 | 软件算法的分类 |

| 903.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 905.9 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 910.0 | 26 MHz XTAL的谐波 | 否 | 不适用 |

| 912.4 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 916.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 918.9 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 923.0 | ADC时钟谐波和解调器时钟谐波 | 是 | ADC_DESENSE_CHAN 和 DEMOD_DESENSE_CHAN |

| 频率(MHz) | 导致接收器降敏的原因 | 软件算法可以解决问题 | 软件算法的分类 |

| 903.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 905.8 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 910.0 | 26 MHz XTAL的谐波 | 否 | 不适用 |

| 912.3 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 916.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 918.8 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 923.0 | ADC时钟谐波和解调器时钟谐波 | 是 | ADC_DESENSE_CHAN 和 DEMOD_DESENSE_CHAN |

| 925.3 | 时钟和LO谐波混频 | Yes | CLOCK_LO_HARM_DESENSE_CHAN |

| 频率(MHz) | 导致接收器降敏的原因 | 软件算法可以解决问题 | 软件算法的分类 |

| 903.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 910.0 | 26 MHz XTAL的谐波 | 否 | 不适用 |

| 914.5 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 916.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 923.0 | ADC时钟谐波和解调器时钟谐波 | 是 | ADC_DESENSE_CHAN 和 DEMOD_DESENSE_CHAN |

| 927.5 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 频率(MHz) | 导致接收器降敏的原因 | 软件算法可以解决问题 | 软件算法的分类 |

| 903.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 905.9 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 910.0 | 26 MHz XTAL的谐波 | 否 | 不适用 |

| 916.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 918.9 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 923.0 | ADC时钟谐波和解调器时钟谐波 | 是 | ADC_DESENSE_CHAN 和 DEMOD_DESENSE_CHAN |

| 927.6 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 频率(MHz) | 导致接收器降敏的原因 | 软件算法可以解决问题 | 软件算法的分类 |

| 903.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 906.0 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 910.0 | 26 MHz XTAL的谐波 | 否 | 不适用 |

| 916.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 923.0 | ADC时钟谐波和解调器时钟谐波 | 是 | ADC_DESENSE_CHAN 和 DEMOD_DESENSE_CHAN |

| 927.7 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 频率(MHz) | 导致接收器降敏的原因 | 软件算法可以解决问题 | 软件算法的分类 |

| 903.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 903.7 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 910.0 | 26 MHz XTAL的谐波 | 否 | 不适用 |

| 910.5 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 916.5 | ADC时钟谐波 | 是 | ADC_DESENSE_CHAN |

| 923.0 | ADC时钟谐波和解调器时钟谐波 | 是 | ADC_DESENSE_CHAN 和 DEMOD_DESENSE_CHAN |

| 923.5 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

| 927.9 | 时钟和LO谐波混频 | 是 | CLOCK_LO_HARM_DESENSE_CHAN |

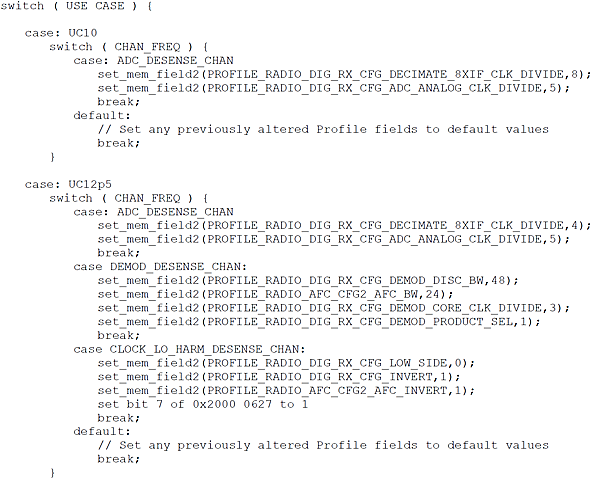

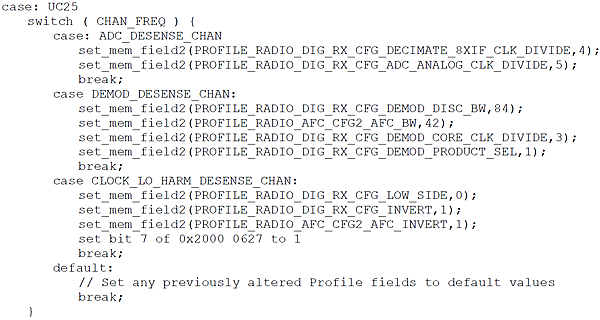

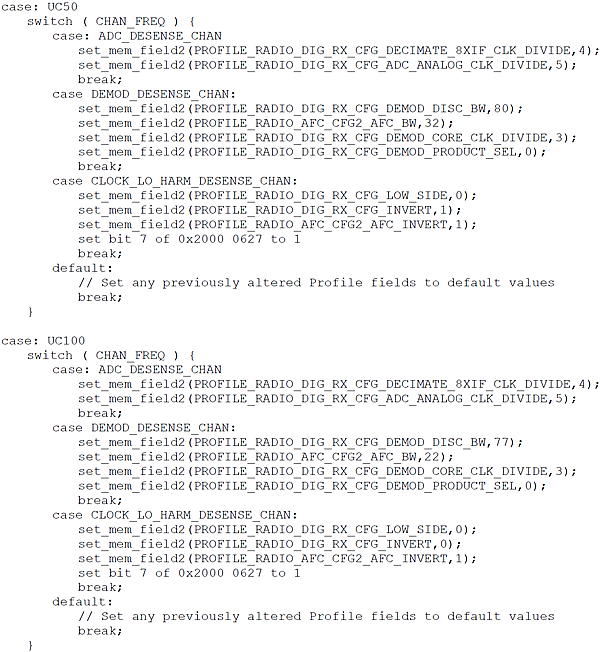

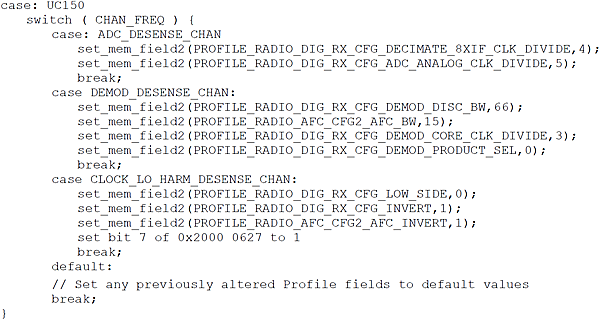

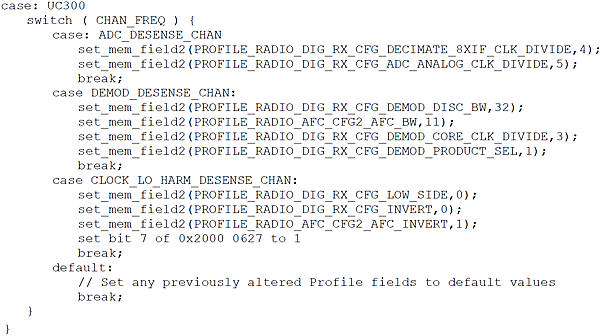

主机软件算法

参考表 4 至表 10,下列伪 C 代码从概念上描述了主机如何基于所需的通道频率来更改ADF7030-1射频配置文件,以规避降敏问题。在发布 CMD_PHY_RX 命令之前,在 PHY_ON 中实施这些射频配置文件设置更改。在更改这些设置之后,无需再发布CMD_CFG_DEV 命令。

发射器/接收器匹配的组合结果

本测试使用的评估板支持次最优 RF 匹配。因此,基线接收灵敏度不能代表可达到的最佳性能。