與EMI濾波器和諧共舞

與EMI濾波器和諧共舞

作者:ADI核心應用部門資深工程師 Marc Smith

摘要

本文介紹了通常應用於心電圖(ECG)和生物阻抗(BioZ)類比前端(AFE)電路的傳統共模/差模被動電磁干擾(EMI)濾波器的分析與設計準則。文中詳細說明不平衡的EMI濾波器如何造成共模雜訊混入差模訊號路徑,進而降低訊號雜訊比(SNR)性能。這種現象稱為共模至差模轉換(共模轉差模)。透過審慎選擇元件,設計人員將能減輕相關的SNR下降問題,同時為ECG和BioZ AFE提供合適的訊號濾波。

讀者將從本文瞭解的內容

- 瞭解如何分析共模轉差模濾波器的傳遞函數。

- 識別可能會降低不平衡濾波器電路性能的噪音源。

- 深入瞭解共模轉差模過程。

- 瞭解如何設定共模濾波器頻寬和差模濾波器頻寬。

- 適用於MAX3000x ECG和BioZ AFE元件的濾波器設定建議。

引言

本文對傳統共模(CM)至差模(DM)被動濾波器中因失衡問題所導致的性能限制進行了分析與探討。

圖1展示了MAX30001心電圖(ECG)類比前端(AFE)的典型電路原理圖。圖1所示的兩個外部電磁干擾(EMI)濾波器(其中一個以藍色著重標記)是傳統的共模轉差模濾波器電路。

上述外部EMI濾波器(採用傳統的共模轉差模濾波電路實現)同時兼具共模和差模頻寬限制功能。此外,設計人員只需審慎選擇一個元件參數值(差模電容),就能緩解因共模訊號路徑失衡而導致的訊號雜訊比(SNR)下降問題。對於僅由五個被動元件組成的電路而言,實屬不易!

在深入探討此種電路之前,我們先簡要討論一下可能遭遇的外部電磁干擾源有哪些。電磁干擾(EMI)是一種與外部電磁感應源(如磁耦合)、靜電耦合(如電容耦合)或傳導相關的電路干擾現象。從根本上來看,電磁干擾可以透過輻射和/或傳導的方式耦合到電路中。圖2展示了包含幾種常見電磁干擾源示例的頻譜圖。

傳統的共模轉差模被動濾波器

圖3展示了通常用於減輕環境雜訊的傳統共模轉差模被動濾波器。在心電圖應用中,頻寬通常限制為256 Hz(512 SPS)或更低,交流電源線產生的訊號(如50 Hz/60 Hz)往往成為最具破壞性的電磁干擾源頭。這些訊號可能以共模訊號的形態出現,而我們的目標是防止其對差模訊號造成干擾。如果共模轉差模被動濾波器存在失衡問題,不需要的訊號(也稱為雜訊)就可能會損壞目標差模訊號。

共模濾波器和共模轉差模

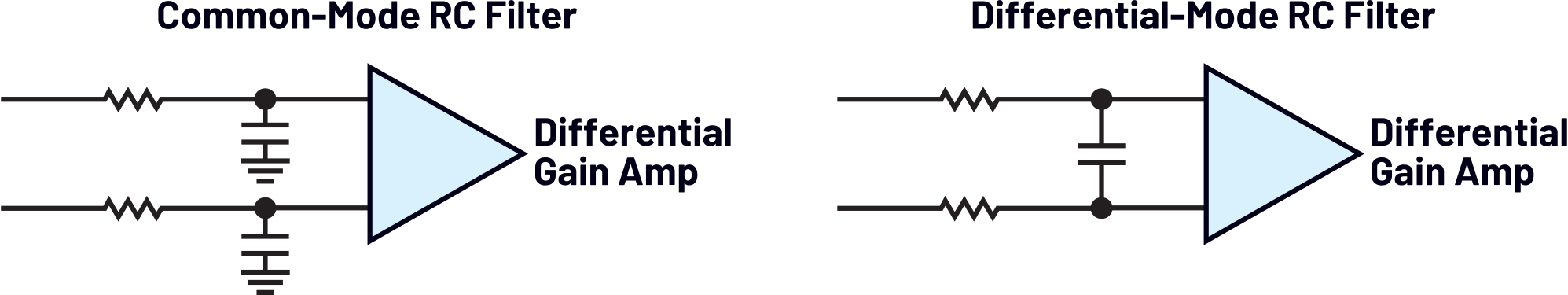

共模轉差模被動(EMI)濾波器可以看成是一個由共模RC濾波器和差模RC濾波器組成的複合濾波器。圖4展示了這兩種濾波器配置作為獨立電路的情況。需要注意的是,這些濾波器結構(包括共模轉差模被動濾波器)常常在諸如Δ-Σ調變器之類的採樣類比數位電路中用於抗混疊濾波器(AAF)。因此,此處的分析同樣適用於AAF和其他差模訊號電路。

共模濾波器尤其值得關注,因為當電路出現不平衡時(即兩條輸入訊號路徑的時間常數不相等時),其可能會成為雜訊的傳播媒介。考慮到元件容差、溫度係數、電壓係數等因素,此種不平衡是一種常見的情況。在存在電雜訊的環境中,共模濾波器的共模抑制能力決定了有多少雜訊可能會注入到差模通道中。此種注入的雜訊會降低目標訊號(差模通道訊號)的訊號雜訊比(SNR)。這稱為共模至差模轉換(共模轉差模)。透過預估電氣環境,設計人員可以採用適量的元件匹配措施來減少共模至差模的轉換。

實用頻寬近似計算

在分析共模轉差模傳遞函數之前,我們不妨先計算平衡共模轉差模濾波器的共模和差模電路頻寬。這些計算不僅能為設計人員在ECG/BioZ應用中進行電路調諧,提供一系列實用的公式依據,還能輔助理解共模至差模轉換運算式的深層含義。

圖5展示了平衡共模配置和平衡差模配置的等效電路。在圖5a中,平衡共模電路在輸出端產生相同的訊號位準(VOUT = 0 V)。因此,差模電容 CDM不會影響電路頻寬,所以在等效電路模型中可以將其去除。共模頻寬由R × CCM的時間常數決定。

在圖5b中,應用了電路鏡像技術,用兩個數值為2 × CDM (CDM等效阻抗)的串聯電容代替差模電容。對於平衡電路而言,在 2 × CDM 電容之間存在一個虛地點,這就產生了兩條完全相同的支路,其中任意一條支路都能決定電路的頻寬。差模頻寬由R(CCM + 2 × CDM)的時間常數來設定。

儘管這些實用的頻寬運算式很有用,但它們只是理想值。任何電路不平衡都會影響共模和差模頻寬。雖然電路不平衡可能會導致差模訊號強度減弱(差模至共模轉換),但這可以透過增加後續級的增益來彌補。另一方面,在外部存在雜訊的環境中,電路不平衡會透過共模轉差模轉換導致差模通道的訊號雜訊比下降。

共模轉差模傳遞函數

圖6展示了一個共模轉差模電路分析的等效拓撲結構:橋式電路。

自十九世紀中葉以來,橋式電路(例如惠斯通電橋)就已得到了廣泛應用。儘管橋式電路在眾多領域都有應用,但它在這裡用於一種分析工具。圖7著重展示了通用橋式電路的傳遞函數方程式(由惠斯通電橋推導擴展而來)。

將這些公式應用於圖6中的電路,可得到以下共模至差模轉換的傳遞函數:

請注意,這個傳遞函數有三個極點和兩個零點。從系統工程的角度來看,這是一個3階1型系統傳遞函數。公式2展示了通用的公式形式,突出了電路不平衡的影響(即當 τ2 ≠ τ1時)。

令人驚訝的是,對於僅有五個被動元件的情況而言,這個包含五項的傳遞函數相當複雜。研究各個單獨的項有助於深入瞭解如何進行可能的簡化。極點p1和p2將確定兩個較高的頻率轉捩點,而極點p0將確定一個較低的頻率轉捩點。預設情況下(由於存在額外的電容), BWp0 < BWp1 ≈ BWp2。如果採用了較大的CDIFF (CDIFF >> C1||C2),則較低頻率(即低於BWp0)的共模雜訊傳遞對於C1和C2的不匹配將變得不那麼敏感。

實用共模轉差模傳遞函數近似值

參考圖5中的頻寬近似值,請注意,極點p1和p2與共模頻寬相對應。此外,如果R1≈ R2且C1≈ C2,極點p0則與差模頻寬相對應(具體推導過程留給讀者自行完成)。

進一步來看,如果R1≈ R2且C1≈ C2,零點Z1近似等於兩個極點p1和p2中的任意一個。消去一對近似相等的極點/零點,不僅會簡化我們的運算式,還能得到一個實用的傳遞函數近似值。

被消去的這對極點/零點在低頻時不會影響共模轉差模的增益。在高頻情況下(對於調幅(AM)無線電發射而言,頻率≥535 kHz時),根據EMI濾波器的不匹配程度,它確實會帶來一些增益誤差。

近似的共模轉差模轉換傳遞函數為:

註:運算式中保留了極點p1,假定其相較於極點p2設定了一個更高的轉折頻率。這個極點對更高頻率的衰減會有更大的影響。

對公式3進行分析可以發現,當分子中的兩個時間常數相等時,電路處於完全平衡狀態,此時傳遞增益為零(即具有無限大的共模抑制能力)。雖然從理論上來說這是可能的,但在實際中這種情況非常罕見。即便有人手動對電路進行平衡調節,諸多其他因素(諸如元件老化、溫度變化、電壓影響等)仍會致使電路偏離這種理想狀態。對設計人員而言,應當投入更多時間來瞭解共模轉差模轉換對元件容差的敏感程度。這將有助於為共模電磁干擾雜訊設定初始的抑制級別。

註:共模轉差模EMI濾波器通常不被視為精密電路。其應用於環境雜訊訊號強度不太明確的情形。正因如此,它的目的在協助抑制常見的已知噪音源(例如電力線干擾、調幅無線電干擾等)。

在跨越了「無限之橋」後,讓我們回到現實世界,要明白,電路不平衡才是常態。實際上,我們關注的重點正是最壞情況下的電路不平衡狀態。重新審視公式3,請注意,該傳遞函數以20 dB/dec的速率上升,在低頻極點(fL)處趨於平緩,然後在高於高頻極點(fH)的頻率段以-20 dB/dec的速率下降。中心頻率可以透過取兩個極點頻率的幾何平均值來近似計算。然而,這種近似計算的誤差會隨著元件失配程度的增加而增大。對於較大的失配誤差(例如,容差為±1%的電阻和容差為±20%的電容),建議(透過手動分析和/或模擬的方式)找出在相移為-180°時的峰值增益。

峰值中頻增益的近似計算方法如下:

如果CDIFF >> C1 ≈ C2,則峰值中頻增益可以進一步簡化,如下所示:

如果對所有元件都選擇用δ表示的相同容差,公式5可簡化為:

雖然從設計的角度來看,這(選擇具有相同容差的元件)在某種程度上具有一定的侷限性,但它強調了一個要點,即電容比(共模電容與差模電容之比)越小,電路對共模雜訊的衰減能力就越強。

回到公式5,在分析電路在最壞容差條件下的情況時,假定元件的值是有偏差的,使得分子達到最大值。RC時間常數的失配(電路不平衡)越大,更多的共模雜訊就會混入差模通道中。將注意力轉向分母項,注意到電阻之和簡單來說就是標稱電阻的兩倍,運算式可以簡化如下:

把公式7代入公式5,得到:

公式8是一個非常簡單且實用的共模轉差模轉換中頻增益的近似公式:即共模時間常數失配值除以標稱差模時間常數。只要CDIFF很大(CDIFF ≥ 100 × (C1和C2的值)),公式8就相當精準。

有人可能會想隨意增大CDIFF的值,以降低分子(即電阻電容時間常數失配)的敏感度。但此種做法是受限的,因為其會設定差模通道的頻寬(也就是我們所關注的訊號的頻寬)。因此,需要進行權衡取捨。

現在,可以利用峰值中頻增益以及低頻和高頻轉折頻率,來近似估算在 50 Hz/60 Hz(潛在電力線干擾)和535 kHz(潛在的AM無線電頻譜干擾的低頻端)時的共模抑制能力。以下的例子著重說明了這一點。

共模轉差模傳遞函數示例

我們假設每個元件都有0.1%的容差。這將提供一個參考水準,以便與其他EMI濾波器電路場景進行比較(見圖8)。對於最壞情況(wc)下的抑制近似計算,請使用以下數值:

應用公式8:

請注意,前面運算式的分母是低頻轉折頻率的時間常數,我們可以很容易地計算出fL:

現在使用較小的RC時間常數來確定較高頻率的極點:

有了這些數值,我們現在可以按如下方式估算在50 Hz/60 Hz和535 kHz時的衰減:

這些手動計算結果與電路模擬結果非常吻合(見圖9)。請記住,這並不是一個精密電路。對於EMI濾波器的應用來說,幾分貝(dB)以內的近似值通常是可以接受的。

表1重點顯示了該電路在50 Hz/60 Hz和535 kHz頻率下,針對不同元件容差水準的共模轉差模抑制能力。第一種情況(容差為±0.1%)在某種程度上是一個任意參考點,基於在實驗室工作台手動測量被動元件而設定。其他情況則反映了市面上常見的電阻和電容的容差水準,以便進行比較。

| 最壞情況下共模轉差模的衰減估算 | ||||||

| 抑制能力估算(公式4——手動計算) | EMI濾波器衰減(LTspice模擬結果) | |||||

| 場景 | Gv (dB) at 50 Hz | Gv (dB) at 60 Hz | Gv (dB) at 535 kHz | Gv (dB) at 50 Hz | Gv (dB) at 60 Hz | Gv (dB) at 535 kHz |

| 所有元件0.1% | −112.3 | −110.8 | −116.6 | −112.3 | −110.8 | −116.7 |

| 所有電阻1%;電容0.1% | −97.5 | −96.0 | −101.7 | −97.4 | −96.0 | −101.9 |

| 所有元件1% | −92.3 | −90.8 | −96.4 | −92.2 | −90.8 | −96.6 |

| 所有電阻1%;電容 5% | −82.7 | −81.2 | −86.2 | −82.7 | −81.2 | −86.7 |

| 所有電阻1%;電容 10% | −77.4 | −75.9 | −80.0 | −77.4 | −75.9 | −81.0 |

| 所有電阻1%;電容 20% | −71.7 | −70.2 | −72.3 | −71.7 | −70.2 | −74.3 |

請注意,在進行最壞情況的估計時,RC時間常數的容差會翻倍。也就是說,如果差模電路的一側增加X個百分點,另一側可能會減少X個百分點。例如,如果R1和R2是容差為1%的元件,C1和C2是容差為10%的元件,那麼最壞情況下的RC時間常數失配率為22%。與容差為0.1%(即時間常數失配為8 ns)的參考情況相比,440 ns(22%)的失配會使共模抑制能力降低35 dB。這無疑是相當大的損耗!至於這種損耗能否被接受,需視具體使用場景而定。

圖10展示了共模抑制比與Telta Tau的關係曲線,其中Telta Tau表示RC時間常數失配量。在底部橫軸旁,幾個對應的RC容差水準以紅色標註。為作說明,64 ns Delta Tau水準對應於1.6%的RC容差(64 ns/2 µs = 3.2%最壞情況失配 = ±1.6%RC容差)。從該曲線圖的斜率可知,每當RC時間常數失配量翻倍時,共模抑制比就會降低6 dB。

要點總結

- 預測並驗證電磁干擾(EMI)環境。

- 等效的共模轉差模電路是一種橋式電路,屬於非線性電路。

- 透過合理選擇CDIFF,設計人員能夠利用公式8及計算得出的轉折頻率,輕鬆估算共模轉差模的轉換情況。

- 增大CDIFF的值,會降低電路對C1和C2之間失配的敏感度,也會降低對Delta Tau(即共模RC時間常數失配)的敏感度。

- 根據一階近似,每當RC失配量翻倍時,共模抑制比就會下降6 dB。

- 元件製造容差只是其中一個影響因素。溫度、電壓以及元件老化也會對元件之間的失配產生影響。

- 所有的計算都是基於最壞情況下的失配進行的。其他任何情況只會使電路性能更好,最終達到理想的無限大共模抑制比。

- 分析並理解所用的電路,找出性能方面的權衡取捨及適用的近似計算方法。不要僅僅依靠模擬來進行設計。

- 這種分析方法可以擴展應用到AAF的設計中。

針對ECG應用調整EMI濾波器

為ECG應用設計EMI濾波器時,首先要設定差模訊號頻寬。在健康應用場景中,通常以心率的R'-R'測量為目標,這可以在較低的頻寬(40 Hz)下實現,而心律失常檢測應用則需要更高的頻寬(256 Hz)。

在此示例中,將為心律失常檢測應用設計一個頻寬為256 Hz的EMI濾波器。根據IEC 60601-1安全合規性要求,電阻值存在一個最低限度。具體而言,為了保護患者,單一故障條件下的直流電必須限制在50 µA以內。因此,如果ECG AFE IC(例如MAX30001、MAX30003, MAX30005, MAX86176或MAX86178))由1.8 V電源供電,則最小電阻值應為36 kΩ(1.8 V/50 µA)。

在選擇電阻值之前,有必要重新審視一下公式5。透過增大分母的值(增加電阻值,同時保持CDIFF與CCM比率恆定),可以降低共模到差模的轉換。雖然這在設計上有一定的彈性,但電阻會產生詹森熱雜訊,這種雜訊可能會導致差模訊號出現誤差。為了大幅減少這種噪音源,建議電阻值小於兆歐(MΩ)級。

我們將設計目標設定如下:

差模通道頻寬 = 282 Hz(允許與標稱的256 Hz有10%的誤差)。

共模通道頻寬 = 48.2 kHz(允許與標稱的53.5 kHz有10%的誤差,比最低AM無線電波段的535 kHz低一個數量級)。

註:初始容差假設僅僅是起始參考,假定共模RC時間常數大約有10%的容差。

使用10 pF電容並且fc= 48.2 kHz時,計算所得的電阻值應為330.2 kΩ。

根據圖5中提供的差模頻寬公式計算 CDIFF值,得到851.3 pF。

選擇電阻值為330 kΩ、容差為0.1%的電阻。為實現更好的共模抑制效果,建議選用精度(容差)更高的電阻。透過合理選擇差模電容的值,可以降低電路對共模電容的敏感度。因此,兩個共模電容可以具有較大的容差,這樣還能節省成本。

註:當使用幹電極進行ECG測量時,通常不建議使用EMI濾波器。這是因為,對於幹電極與組織之間較高的阻抗介面而言,EMI濾波器提供了一條較低阻抗的路徑。從根本上來說,EMI濾波器會使AFE元件中儀錶放大器的高共模抑制能力失效。如果無法在所有環境條件下做到極其精準的匹配,EMI濾波器可能會降低整個系統的共模抑制性能。

計算得出的電阻和電容值並不總是與市面上可採購到的元件相匹配。因此,設計人員需要進行研究,並根據尺寸、成本、容差、溫度係數、電壓應力、老化等因素,選擇所能得到的最接近的元件值。此處的分析僅考慮了標稱製造容差示例所產生的影響。建議設計人員深入分析具體應用場景,以便充分考慮所有相關的變化因素。

選擇以下EMI濾波器設計元件:

R1 = R2 = 330 kΩ, 0.1%; C1 = C2 = 10 pF*, 10%; CDIFF = 850 pF, 10%

* 由於PCB存在雜散電容,不建議使用電容值較低的電容器。

使用公式8及用於計算一階升緣和降緣衰減的公式,可得出以下電路特性:

共模頻寬 ≈ (2π × (330 k)(10 pF))–1 = 48.2 kHz標稱值;頻寬(容差)範圍:43.8 kHz至53.6 kHz

差模頻寬 ≈ (2π × (330 k)(10 pF + 2 × 850 pF))–1 = 282 kHz標稱值;頻寬(容差)範圍:257 Hz至313 Hz

50 Hz時的最壞情況下的共模抑制 =–74 dB

60 Hz時的最壞情況下的共模抑制 =–72 dB

535 kHz時的最壞情況下的共模抑制 =–78 dB

使用一種名為Spice的電路模擬軟體來驗證上述計算結果(具體的計算和模擬過程留給讀者自行完成)。對於最壞情況場景,使用LTspice®軟體進行的模擬可得出以下結果:

fH= 49 kHz和 fL = 311 Hz

50 Hz時的最壞情況下的共模抑制 =–74 dB,60 Hz時的最壞情況下的共模抑制 =–72 dB

535 kHz時的最壞情況下的共模抑制 =–78.6 dB*

*如前文所述,極點/零點項的抵消會給高頻衰減近似計算帶來一定誤差。在此實例中,我們的估算值在535kHz處與實際值相差0.6 dB。

請注意,採用容差更小的電容器可以提高抑制水準。有鑑於EMI濾波器會直接影響前端電子元件的共模抑制性能,甚至可能導致前端放大器的共模抑制作用形同虛設,採取此一措施顯得尤為必要。

針對BioZ應用調整EMI濾波器

為BioZ應用設計EMI濾波器時,首先要做的同樣是設定差模訊號頻寬。然而,BioZ技術涉及將交流訊號注入人體組織,然後對返回訊號的幅度和相位資訊進行分析。因此,濾波器產生的任何相位失真都會引入訊號誤差。

為避免相位失真,建議將差模轉折頻率設定為比驅動頻率高出幾個數量級。MAX30001 BioZ電路提供了125 Hz至131.072 kHz的注入訊號範圍。由於差模頻寬不能大於共模頻寬,因此將差模頻率轉折設定為535 Hz,同時將標稱共模轉折頻率設定為53.5 kHz(比AM無線電波段低一個數量級)。

我們將設計目標設定如下:

差模通道頻寬 = 595 Hz(允許與標稱的535 Hz有10%的誤差)。

共模通道頻寬 = 48.2 kHz(允許與標稱的53.5 kHz有10%的誤差,比最低AM無線電波段的535 kHz低一個數量級)。

註:初始容差假設僅僅是起始參考,假定共模RC時間常數大約有10%的容差。

使用10 pF電容並且fc= 48.2 kHz時,電阻應為330.2 kΩ。

根據圖5中提供的差模頻寬公式計算CDIFF值,得到400 pF。

選擇以下EMI濾波器設計元件:

R1 = R2 = 330 kΩ, 0.1%; C1 = C2 = 10 pF*, 10%; CDIFF = 400 pF, 10%

*由於PCB存在雜散電容,不建議使用電容值較低的電容器。

使用公式8及用於計算一階升緣和降緣衰減的公式,可得出以下電路特性:

共模頻寬 ≈ (2π × (330 k)(10 pF))–1 = 48.2 kHz標稱值;頻寬(容差)範圍:43.8 kHz至53.6 kHz

差模頻寬 ≈ (2π × (330 k)(10 pF + 2 × 400 pF))–1 = 595 Hz標稱值;頻寬(容差)範圍:542 Hz至661 Hz

50 Hz時的最壞情況下的共模抑制 =–73.6 dB

60 Hz時的最壞情況下的共模抑制 =–72.2 dB

535 kHz時的最壞情況下的共模抑制 =–71.2 dB

使用了一種名為Spice的電路模擬軟體來驗證上述計算結果(具體的計算和模擬過程留給讀者自行完成)。對於最壞情況場景,使用LTspice軟體進行的模擬得出了以下結果:

FH= 49 kHz和FL= 311 Hz

50 Hz時的最壞情況下的共模抑制 =–73.6 dB,60 Hz時的最壞情況下的共模抑制 =–72 dB

535 kHz時的最壞情況下的共模抑制 =–72 dB*

*如上文所述,極點/零點項的抵消會給高頻衰減近似計算帶來一定誤差。在此用例中,我們的估算值在535kHz處與實際值相差0.8 dB。

關於BioZ應用中EMI濾波器的最後幾點思考

在為BioZ應用設計EMI濾波器時,如果注入訊號頻率較高(大於535 Hz),對AM無線電頻段的共模抑制能力將會減弱。此外,較高的BioZ注入頻率會促使設計採用電阻值更低的電阻。使用36 kΩ的電阻(這是在電源電壓為1.8 V時,為符合IEC 60601-1安全標準而計算得出的值),搭配10 pF的電容,可將共模頻寬設定在440 kHz左右。將差模轉折頻率降低兩個數量級,會把注入頻率限制在4 kHz左右。如果需要更高的BioZ注入頻率(比如MAX30001的最大注入頻率為131 kHz),則需要使用電阻值更低的電阻。

共模抑制比與共模轉差模轉換

共模抑制比(CMRR)與共模轉差模轉換存在反向關聯特性。CMRR是一個正項(通常情況下),共模轉差模傳遞函數則是電路增益,其值通常小於1 V/V(即一個負的dB值)。需要注意的是,CMRR運算式中的增益項僅僅是輸出訊號與輸入訊號的比值,透過對CMRR運算式進行重新整理,可以透過公式16來說明這種關係。

*這是 VDIFF,RTI(折合到輸入端)。

CMRR是用於比較不同電路性能的一個實用指標。儘管具有自身的作用,但其無法直接解釋在EMI濾波器電路的傳遞函數中所發生的共模轉差模行為。有鑑於此,本文採用的分析方法將能夠更有效地評估和解釋不平衡EMI濾波器所帶來的影響。

結論

本文探討了關於傳統共模轉差模濾波器的應用場景、工作原理及性能侷限等方面的知識。在內容呈現上,儘量精簡運算過程和模擬圖表,重點在於闡釋不平衡EMI濾波器的數學模型。此外,文中對相關公式進行了適度簡化,並著重提煉出可供設計人員彈性運用的關鍵要點。

令人驚歎的是,看似僅由五個被動元件構成的簡易電路,一旦出現不平衡狀況,便會展現出超乎想像的複雜特性。