全差分放大器為精密資料擷取訊號鏈提供高壓低雜訊訊號

全差分放大器為精密資料擷取訊號鏈提供高壓低雜訊訊號

作者:ADI產品/測試開發經理 Darwin P. Tolentino

摘要

全差分放大器(FDA)具有差分輸入和差分輸出,其輸出共模由直流(DC)輸入電壓獨立控制,主要用在資料擷取系統中類比數位轉換的前端,用於將訊號處理為合適的位準以供下一級(通常是類比數位轉換器(ADC))使用。FDA一般採用單晶片設計,電源電壓較小,因此輸出動態範圍有限。本文將介紹具有可調共模輸出的高壓低雜訊FDA的設計方法,並完整分析FDA雜訊,以及其對高性能資料擷取系統訊號鏈的總體訊號雜訊比(SNR)的影響。

引言

高壓FDA適用於需要寬廣輸出動態範圍和與高性能FDA類似的交流(AC)性能的應用。例如,測試和評估具有寬廣輸入範圍的精密資料擷取訊號鏈可能需要高壓FDA。由於電源電壓較小,目前大多數FDA的輸出電壓範圍一般都很有限。FDA適合用於驅動高性能ADC的輸入,後者通常需要單電源。FDA具有卓越交流性能,其SNR和總諧波失真(THD)十分優異。不過,在失調、軌間擺幅、偏置電流和漂移性能方面,FDA不如許多更高電壓的精密運算放大器。但這完全不是問題,因為其滿足ADC驅動要求,而且ADI提供了一系列用於各種應用的ADC驅動器。

FDA支援單端或差分輸入,具有增益,並提供差分輸出,其共模通常可透過輸出共模輸入接腳(VOCM)進行調整(見圖1)。FDA的優勢在於擁有更大的輸出動態範圍,最大輸出是輸出軌的兩倍,並且其雜訊和偶次諧波失真更低。例如,±5 V FDA的最大輸出峰對峰值接近±10 V或20 V p-p。

圖1.FDA

±18 V電路的輸出大於60 V p-p。 ADA4625-1/ADA4625-2 是低雜訊JFET放大器,雜訊和失真性能非常高,並且電源範圍寬達±18 V。當需要滿足應用的所有直流和交流性能要求時,使用分立運算放大器設計FDA可能會很棘手。

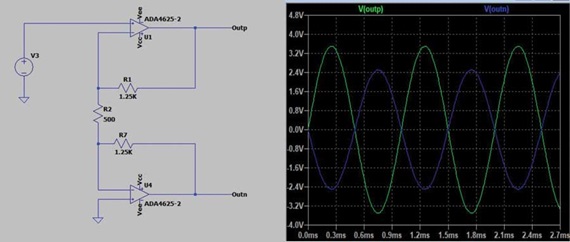

要創建差分放大器,比較簡單的方法是使用同相和反相放大器在輸出端產生差模訊號(圖2),但此種方法的缺點是兩個放大器U1和U2不能以非常對稱的方式運行,因而性能無法得到優化。

圖2.單端轉差分電路

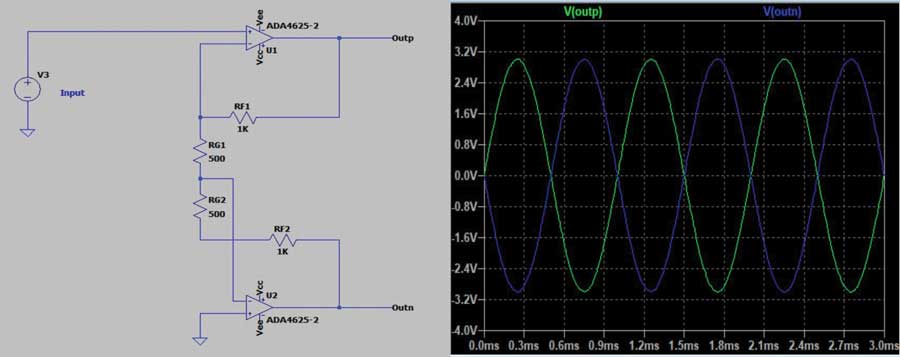

更好的方法是將兩個運算放大器配置成差分方式,類似於基本差分放大器,其中U1和U2共用回饋和增益電阻,增益Av = (RG + 2RF)/RG(見圖3)。

圖3.差分放大器電路

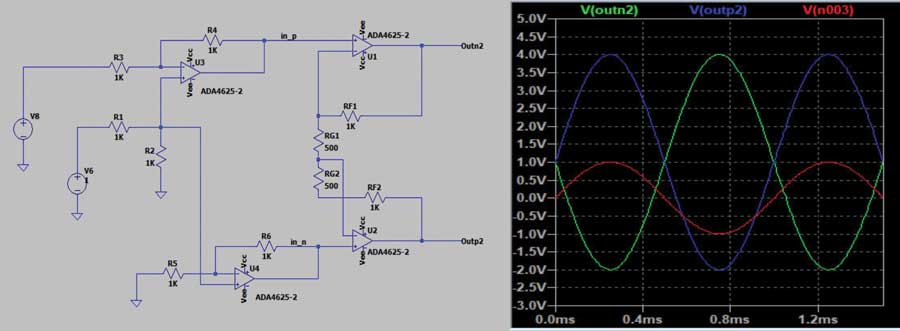

此配置透過簡化的增益網路提供平衡輸出,並可透過增益設定電阻RG輕鬆調整增益大小。然而,當輸入為單端時,差分輸出在幅度上將是不對稱的(見圖4)。不對稱輸出會使輸出範圍嚴重受限,因為其中一個輸出會先於另一個輸出達到供電軌。透過調整電阻增益網路使輸出對稱,可以解決此問題(圖5)。請注意,增益電阻被分成兩部分,即RG1和RG2,並且U2從RG1和RG2的中心獲得回饋,進而使輸出對稱。增益由下式提供:Av = (RG1 + RG2 + RF1 + RF2)/RG1。

圖4.不對稱輸出

圖5.對稱輸出

增加可調輸出共模

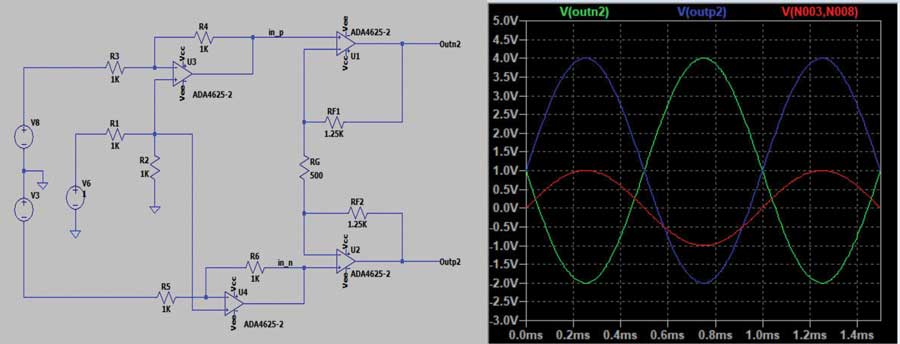

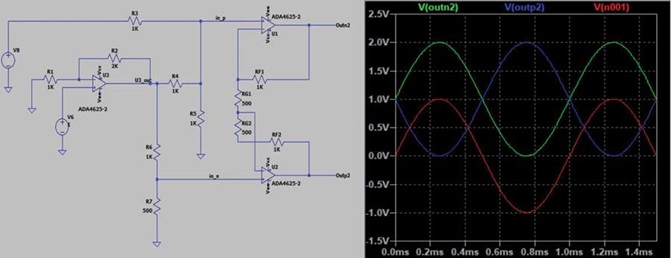

增加可調共模的方法有兩種:一種方法是使用兩個ADA4625元件為每個輸入增加一個VOCM放大器(圖6和圖7);另一種方法是僅使用一個ADA4625-1作為VOCM放大器(圖8和圖9)。這些方法各有利弊,下文將展開詳細討論。

透過增加放大器U3和U4,所施加的任何直流輸入電壓(V6)都會加到正負輸入上。由於每個輸入都增加了相同電壓,因此其在輸出端表現為直流共模。然而,除了U1和U2差分級會進一步放大額外雜訊之外,U3和U4還會在電路中產生額外的功耗。不過,其非常簡單,並且不會影響整體訊號增益。對於圖6中的電路,訊號增益為Av = (RG1 + RG2 + RF1 + RF2)/RG1;對於圖7中的電路,訊號增益為Av = (RG + RF1 + RF2)/RG。

圖6.採用雙放大器的單端轉差分可調共模電路。右圖為輸入(紅色)和輸出(藍色和綠色)的LTspice®模擬。

圖7.採用雙通道放大器的差分轉差分可調共模電路。右圖為輸入(紅色)和輸出(藍色和綠色)的LTspice模擬。

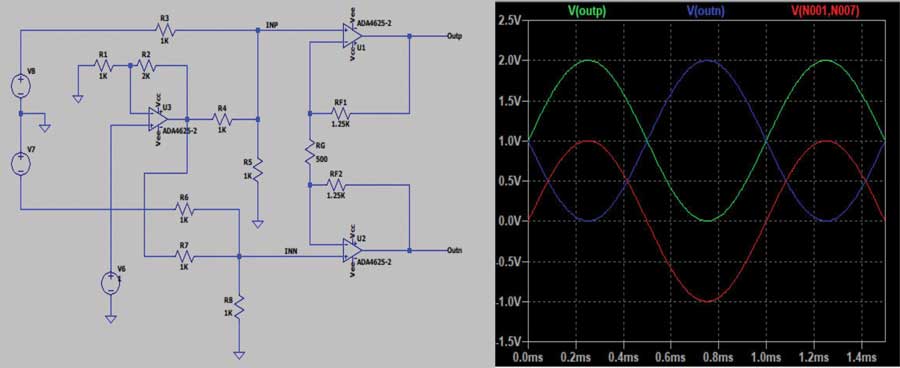

增加可調 VOCM的另一種方法是加入一個放大器,將其輸出加到每個輸入上。此種方法的優點包括:使用的元件(僅一個放大器)和電阻更少,以及所增加元件產生的雜訊貢獻更低。實際上,U3不會產生任何額外雜訊,因為除了來自電阻分壓器R4至R7的雜訊外,其折合到輸出的雜訊表現為U1和U2輸入的共模。

電阻R3至R7構成電阻加法器網路,將VOCM加到輸入訊號上。R3至R5將共模加到正輸入訊號上,而R6至R8(單端輸入則為R6和R7)將共模加到負輸入上。請注意,該電阻網路會衰減輸入訊號,這會降低電路的整體訊號增益。對於圖8中的電路,總訊號增益為 Av = [(RG1 + RG2 + RF1 + RF2)/RG1][(R4//R5)/(R4//R5 + R3)] ;對於圖9中的電路,總訊號增益為 Av = [(RG + RF1 + RF2)/RG][(R4//R5)/(R4//R5 + R3)]。雜訊分析部分說明主要噪音源,並且根據所需的總增益和設計人員需重點考慮的其他因素,討論了第二種增加VOCM的方法是否比第一種方法更有益。

圖8.採用單放大器的單端轉差分可調共模電路。右圖為輸入(紅色)和輸出(藍色和綠色)的LTspice模擬。

圖9.採用單放大器的差分轉差分可調共模電路。右圖為輸入(紅色)和輸出(藍色和綠色)的LTspice模擬。

雜訊分析

在為高性能精密資料擷取訊號鏈提供激發時,雜訊是一個關鍵考慮因素,最終將決定系統在動態範圍和SNR方面的限制。16位元ADC的理論SNR為98 dB(6.02 N + 1.76 dB,N = 位數),這表示4.096 Vp輸出(或8.192 V p-p)的等效雜訊約為36 μV rms。此種雜訊稱為量化雜訊,是由ADC的量化誤差引起的。-98 dB SNR是16位元系統的理想極限,任何性能下降都將是由ADC的輸入或周圍電路的額外雜訊引起的。以下是單通道和雙通道放大器VOCM全差分電路中各元元件的雜訊貢獻分析。圖10為具有雙放大器VOCM的FDA電路雜訊模型。

圖10.雙放大器VOCM雜訊模型

差分級 — U1和U2雜訊貢獻

ADA4625-1/ADA4625-2的電流雜訊密度非常低,在1 kHz時為4.5 fA/√Hz,而折合到輸入(RTI)的電壓雜訊在1 kHz時約為3 nV /√Hz,本分析將其視為寬頻雜訊。U1和U2的電流和電壓雜訊在差分輸出端的總雜訊貢獻(均方根值)可以表示為:

其中,eNv,U1U2是U1和U2的RTI電壓雜訊引起的輸出電壓雜訊,而eNI,U1U2是輸入電流雜訊引起的輸出電壓雜訊。對輸入端各分量雜訊的平方和求平方根(RSS)可以得到RTI電壓雜訊,然後由增益和回饋網路 RF和RG進行放大。類似地,電流雜訊經過RSS處理後,由RG轉換為電壓雜訊,再經放大傳輸至輸出。輸入電流雜訊非常小,其貢獻微不足道,因此電阻和放大器的電壓雜訊是輸出端的主要噪音源。

由U1和U2的增益和回饋電阻網路(RF1、 RF2和RG)引起的輸出雜訊為:

其中,室溫下1 kΩ電阻的熱雜訊為4.06 nV⁄√Hz。

在輸出端合併U1和U2的電壓雜訊及其回饋電阻網路雜訊,忽略電流雜訊,使用公式1和3可得到:

從之前的討論可以得知,隨著增益的提高,放大器的電壓雜訊很容易成為主導雜訊。使用較小的 RG值(例如500 Ω)可以大幅降低電阻的雜訊。

VOCM 電路 — U3和U4雜訊

接下來分析圖10中VOCM電路的雜訊。VOCM電路(U3和U4)的總雜訊(包括電阻雜訊,並忽略每個放大器的輸入電流雜訊)計算方式如下:

其中,R1//R2為R1和R2的並聯等效電阻。從之前的討論還可以明顯看出,U3和U4的總雜訊主要由放大器電壓雜訊和電阻雜訊組成,因此最好保持較低電阻值,以有效減少其對整體雜訊的貢獻,使放大器雜訊成為唯一的主要噪音源。VOCM電路輸出端的雜訊會出現在差分級的輸入端,隨後由差分級放大並傳輸至輸出端。

VOCM電路 — 單放大器U3雜訊

如前所述,U3輸出端的雜訊作為U1和U2輸入端的共模出現(顯示為inp和inn,見圖 11),因此不會為差分級帶來雜訊。額外的雜訊來自電阻R3至R8。仔細檢查可發現,差分級的每個輸入端都有三個並聯電阻——正輸入端為R3至R5,負輸入端為R6至R8(圖11c),這也使得電阻的雜訊貢獻非常小。

圖11.單放大器VOCM雜訊模型

在雙放大器和單放大器 VOCM電路這兩種電路中,後者的雜訊貢獻要低得多,但其整體訊號增益較低。此外,其功耗更低,所需的放大器也更少。公式7表示圖11中 VOCM電路輸出端的雜訊;公式8表示差分級輸出端變化對U1和U2的對應雜訊貢獻。

綜合考慮 — ADC訊號鏈的總SNR

ADC訊號的總SNR由類比前端(AFE)和ADC的總雜訊貢獻決定,其中可能包括來自其他噪音源的雜訊。ADC訊號鏈的總SNR由下式得出:

其中, VREF被認為是雙極性輸出ADC的正滿量程。

總體而言,訊號鏈的總SNR可以用圖12來總結。

圖12.資料擷取前端訊號鏈

ADC的雜訊與AFE輸入端的雜訊相結合,會使ADC的實際總SNR低於理論或理想值。為將AFE的雜訊與ADC的雜訊結合起來,需要將ADC的SNR轉換為其均方根積分雜訊等效值,如下所示:

例如,ADAQ7767-1的典型SNR為-106 dB,等效有效值雜訊為14.5 μV。

ADAQ7767-1為一款24位元資料擷取解決方案,具有整合ADC驅動器和抗混疊濾波器,增益為1、0.364、0.143 V/V,250 kSPS時雜訊頻寬(BW)為110 kHz,其陡峭截止頻率主要由其數位磚牆濾波器決定。ADA4625-1/ADA4625-2的典型寬頻電壓雜訊為3.3 nV⁄√Hz,因此圖13中差分級(U1和U2)的輸出雜訊貢獻(雜訊增益為6)為:

eN,V_U1U2 = [√2(3.3 nV)2] (500 Ω + 1.5 kΩ + 1 kΩ)/500 Ω = 28 nV⁄√Hz;U1和U2 RTI雜訊引起,使用公式1。

eN,RES_U1U2 = √[2.87 nV(6)]2 + (4 nV)2 + (4.97 nV)2 = 18.4 nV⁄√Hz電阻增益網路引起,使用公式3。

eN,U1U2 = √(28 nV)2 + (18.4 nV)2 = 33.5 nV⁄√Hz,差分級的總輸出雜訊貢獻。

圖13.具有高壓輸入的ADAQ7767-1精密訊號鏈

根據公式 8,其中差分級輸入端三個電阻(1 kΩ)的並聯等效值為333.3 Ω,雜訊為2.3 nV⁄√Hz :

eNO,VOCM_U3 = 6√2(2.3 nV)2 = 19.5 nV⁄√Hz, ,電阻R3至R8引起的輸出雜訊貢獻。

因此,ADAQ7767-1輸入端的總輸出雜訊計算如下:

ADAQ7767-1的輸入增益級配置設定為0.143 V/V,輸入範圍為±28 V (56 V p-p)。有鑑於-106 dB的典型SNR相當於14.5 μv有效值雜訊,將輸入電路雜訊與元件雜訊相結合可得出如下結果:

輸入電路對系統總雜訊的貢獻非常小,部分原因在於ADAQ7767-1的輸入增益較小。請注意,110 kHz來自磚牆式數位濾波器,因此乘以頻寬時無需帶上濾波器頻寬調整因數。根據-106 dB的典型SNR,訊號鏈的最終SNR將為:

使用LTspice對圖13中的輸入電路進行雜訊模擬(圖14),顯示110 kHz頻寬的總有效值雜訊為12.3 μV rms。將其乘以0.143 V/V的增益,得到ADAQ7767-1輸入端雜訊為1.8 μV有效值雜訊,這與計算出的總輸入雜訊值相同。

圖14.圖13所示ADAQ7767-1輸入電路中的LTspice雜訊

表1為使用ADAQ7767-1的其他增益時所得的訊號鏈總SNR。

| 總AFE (FDA)雜訊(V rms) | 頻寬(Hz)(磚牆) | ADAQ7767-1增益 | ADC輸入總雜訊(V rms) | 系統總雜訊(V rms) | 總SNR (dB) |

| 3.88E-08 | 1.10E+05 | 0.143 | 1.84E-06 | 1.46E-05 | –105.94 |

| 3.88E-08 | 1.10E+05 | 0.364 | 4.68E-06 | 1.52E-05 | –105.58 |

| 3.88E-08 | 1.10E+05 | 1 | 1.29E-05 | 1.94E-05 | –103.49 |

圖13中僅使用了單放大器VOCM電路。該電路可用於向前端訊號鏈系統提供大輸入電壓,而不會對雜訊性能產生明顯影響。雙通道放大器VOCM電路可以在相同的總訊號增益下提供類似的雜訊性能。雜訊分析部分“VOCM電路 — U3和U4雜訊”中提供的雜訊方程式可用於計算雙通道放大器VOCM電路輸出端的總雜訊,並且可以應用同樣的方法和概念來計算訊號鏈的總SNR。

結論

在本文介紹的電路中使用ADA4625-1/ADA4625-2創建複合FDA,可實現具有可調共模的低雜訊、高電壓輸出解決方案,進而可以驅動具有寬廣輸入範圍的高性能資料擷取訊號鏈。透過適當配置差分級的回饋網路,該方案既能支援單端輸入,也能支援差分輸入。單放大器VOCM電路功耗更低,使用的放大器更少,因此優於雙放大器VOCM電路。根據上述示例,在增益較低時,FDA電路不會對ADAQ7767-1訊號鏈的總SNR產生明顯影響,而對於增益1 V/V、0.364 V/V和0.143 V/V,其輸入範圍分別為±4.096 V、±11.264 V和±28 V;增益最低時輸入範圍最寬,並且從該解決方案中也受益最大。