輕鬆完成控制迴路模擬

輕鬆完成控制迴路模擬

作者:ADI電源管理專家 Frederik Dostal

摘要

本文介紹了一種進行控制迴路模擬的簡便方法,同時,也說明如何透過LTspice®來輕鬆生成波特圖。

引言

在設計電源時,仔細檢查控制迴路十分重要。控制迴路設定不當可能會導致電源轉換器振盪或運行不穩定。這種振盪不僅會在輸出端產生過高的電壓漣波,還會降低電磁相容性(EMC)性能。此外,倘若控制迴路設定不佳,電壓轉換器對負載瞬變和電源電壓變化的反應速度也會變慢。

檢查控制迴路的簡單步驟

波特圖為檢查控制迴路提供了一個有用的依據。借助諸如 LTspice(17.1以上版本)等模擬工具,可以輕鬆、快速地生成波特圖。本文便將探討進行波特圖模擬的三個步驟。

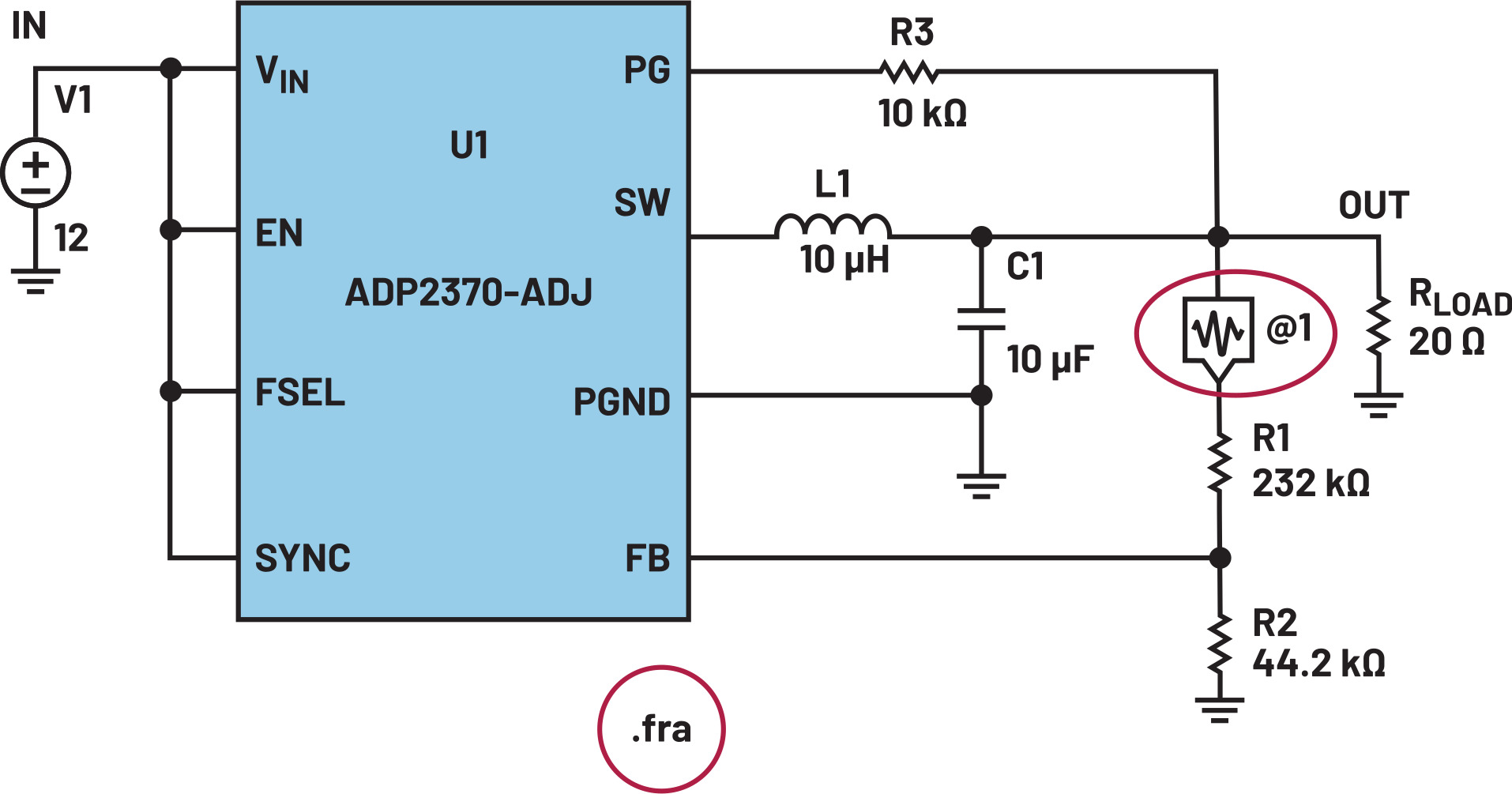

第一個步驟是使用LTspice打開電源電路,例如一個開關穩壓器電路。圖1顯示了 ADP2370 降壓型開關穩壓器的電路。在LTspice中,測試電路(也就是外部電路)可以從現成的電路中選擇。當電路出現在顯示幕上後,從「元件」選項卡中選擇一個頻率響應分析儀(FRA)。其將增加至上分壓電阻(R1)的上方。圖1顯示了本例中所使用的FRA。

圖1.在開關穩壓器電路中增加頻率響應分析儀,以便進行波特圖模擬。

接下來,選擇一種用於生成波特圖的模擬類型。在圖1中,模擬類型顯示為“.fra”。

在開始波特圖模擬之前,必須輸入所需的參數。有諸多可進行優化的選項。按右鍵FRA元件會彈出一個視窗,可以在其中配置波特圖的各項設定。圖2中紅色圓圈標注的“Help Me Configure This for a Switching Regulator”(幫我完成開關穩壓器的此項配置)選項,可進行自動配置,使得操作變得輕而易舉。

圖2.頻率響應分析儀視窗中的波特圖設定。

輸入開關穩壓器的直流輸出電壓、開關頻率和預期穩壓器頻寬(0 dB交越頻率)。完成這些設定之後,按下模擬鍵。

圖3顯示了波特圖視窗,該視窗會在模擬過程結束後自動打開。在波特圖中,頻率表示0 dB交越點處的控制迴路頻寬。在示例中,大約是23 kHz。控制迴路的穩定性可透過相位餘裕進行評估。相位餘裕是指控制迴路在0 dB增益交越頻率處的相移,圖3中標記為“gain_1”。相位餘裕應大於40°,示例中大約為53°,說明該開關穩壓器具備足夠的穩定性。

圖3.使用LTspice版本17.1為開關穩壓器生成的波特圖。

結論

使用LTspice 17.1以上版本時,FRA模組可使波特圖的創建過程變得格外輕鬆。不僅如此,模擬計算過程得以優化,使得模擬所花費的時間大幅縮短,進而讓開關穩壓器控制迴路優化變得輕而易舉。