# 広帯域IFアンプを備えた 直線性の高い300MHz~9GHz I/Q復調器

## 特長

- 真のゼロIF復調

- 500MHz~9GHzで整合する広帯域入力

- 広いIF帯域幅:DC~1GHz(平坦度:1dB)

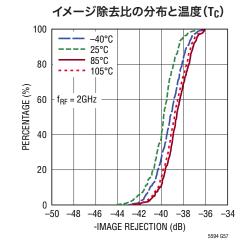

- イメージ除去比:37dB、60dBまで調整可能

- 高い合計 OIP3:37dBm(5.8GHz)

- 5.8GHzでのOIP2:58dBm、65dBmまで調整可能

- 最大電力変換利得:9.2dB(5.8GHz)

- トランス内蔵のシングルエンドRF入力

- ユーザーがDCオフセットのゼロ調整可能

- シリアル・インタフェース

- 8段階に調整可能なIFアンプの利得

- IFアンプのシャットダウン/イネーブル

- 低消費電力のシャットダウン・モード

- 動作温度範囲(T<sub>C</sub>):-40°C~105°C

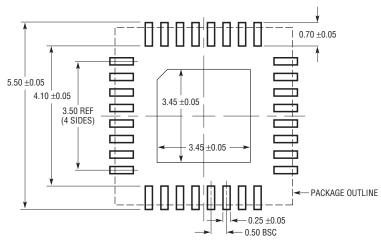

- 32ピン5mm×5mm QFNパッケージ

## アプリケーション

- 5G基地局のフロントホール/バックホール・レシーバ

- 軍用受信機および衛星放送受信機

- 2地点間広帯域無線

- 直線性の高い直接変換方式I/Q SDR

- テスト計測器

- DPDレシーバ

### 概要

LTC<sup>®</sup>5594は、周波数範囲が300MHz~9GHzの直線性の 高いゼロIFおよび低IFレシーバ・アプリケーション向けに最 適化された直接変換方式の直交復調器です。LTC5594は、 1GHzを超えるきわめて広いIF帯域幅を備えているので、特 に5Gフロントホール/バックホール・レシーバ・アプリケーショ ンにおける超広帯域信号の復調に最適です。LTC5594のき わめて優れたダイナミックレンジのため、このデバイスは、要求 の厳しいインフラ向け直接変換方式アプリケーションに適し ています。LTC5594内部の独自技術により、OIP2を65dBmま で最適化する機能を提供し、60dBを超える優れたイメージ 除去比を実現します。DCオフセット制御機能を使用して、A/D コンバータ入力でのDCオフセットをゼロにすることができ、そ れによって、DC結合されたIF信号経路を使用する真のゼロ IFレシーバのダイナミックレンジを最適化します。広帯域のRF およびLO入力ポートにより、1つのデバイスを使用して主要 な全ての無線インフラ周波数帯域を対象にすることができま す。LTC5594のIF出力は、最も一般的なA/Dコンバータ入力 インタフェースとインタフェースをとるように設計されています。 デバイスの高いOIP3および高い変換利得によって、IF信号 経路にアンプを追加する必要がなくなります。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。

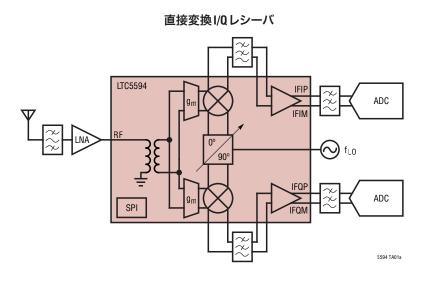

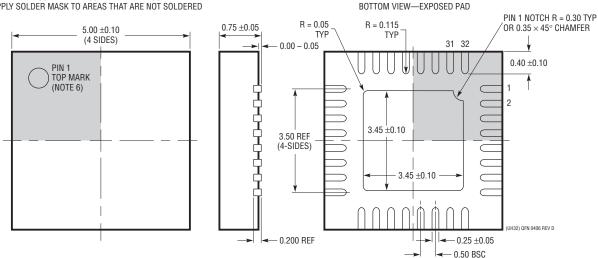

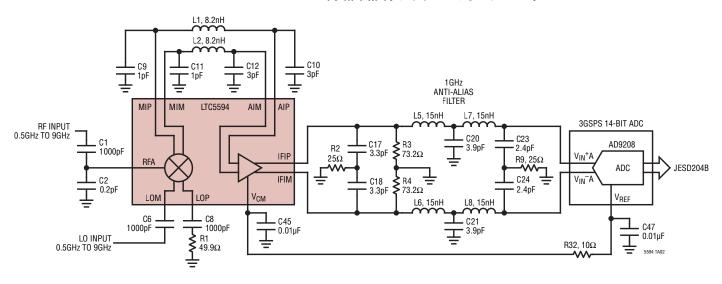

### 標準的応用例

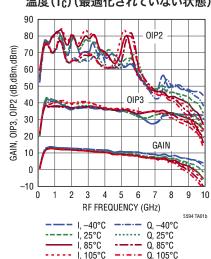

### 利得、OIP3、およびOIP2と 温度(T<sub>C</sub>)(最適化されていない状態)

5594f

# 絶対最大定格

### (Note 1)

| V <sub>CC</sub> 電源電圧(Note 23)                                   |

|-----------------------------------------------------------------|

| OV <sub>DD</sub> 、SDOの電圧(Note 20)                               |

| RFのDC電圧1.5V~2.0V                                                |

| LOP、LOMのDC電圧2.1V~2.8V                                           |

| IFIM、IFIP、IFQP、IFQMのDC電圧0.3V~3.5V                               |

| AIM、AIP、AQM、AQPのDC電圧V <sub>CC</sub> -1.7V~V <sub>CC</sub> -1.2V |

| MIM、MIP、MQM、MQPのDC電圧 $V_{CC}$ – 1.7 $V \sim V_{CC}$ – 1.2 $V$   |

| 他の全てのピンの電圧0.3V~5.5V                                             |

| LOP、LOM、RFの入力電力(Note 19)+20dBm                                  |

| 出力短絡時間(Note 16、19) 無期限                                          |

| 最大接合部温度(T <sub>JMAX</sub> )150°C                                |

| ケース動作温度                                                         |

| 範囲(T <sub>C</sub> )40°C ~ 105°C                                 |

| 保存温度範囲65°C~150°C                                                |

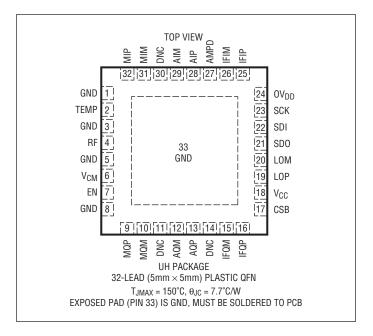

# ピン配置

# 発注情報 http://www.linear-tech.co.jp/product/LTC5594#orderinfo

| 無鉛仕上げ          | テープ・アンド・リール      | 製品マーキング | パッケージ                         | 温度範囲           |

|----------------|------------------|---------|-------------------------------|----------------|

| LTC5594IUH#PBF | LTC5594IUH#TRPBF | 5594    | 32-Lead (5mm×5mm) Plastic QFN | -40°C to 105°C |

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、http://www.linear-tech.co.jp/leadfree/をご覧ください。 テープ・アンド・リールの仕様の詳細については、http://www.linear-tech.co.jp/tapeandreel/をご覧ください。 一部のパッケージは、指定販売チャネルを通じて、#TRMPBFの接尾辞付きで500単位のリールで供給されます。

電気的特性 注記がない限り、 $T_C=25^{\circ}C$ 、 $V_{CC}=5V$ 、 $OV_{DD}=EN=CSB=3.3V$ 、SDI=SCK=AMPD=0V、 $V_{CM}=0.9V$ 、 $P_{IF}=1.5dBm$ (2トーン・テストの場合、-1.5dBm/トーン)、 $P_{LO}=6dBm$ 、全てのレジスタはデフォルト値であり、全てのパラメータは復調器とアンプの複合性能を対象に記載されている。(Note 2、3、6、9、21、24)

| SYMBOL                 | PARAMETER                                                                                                             | CONDITIONS                                                                                                                                                                                            | MIN TYP MAX                                        | UNITS                                  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|

| f <sub>RF(RANGE)</sub> | RF Input Frequency Range                                                                                              | (Note 12)                                                                                                                                                                                             | 0.3 to 9.0                                         | GHz                                    |

| f <sub>LO(RANGE)</sub> | LO Input Frequency Range                                                                                              | (Note 12)                                                                                                                                                                                             | 0.3 to 9.0                                         | GHz                                    |

| BWIF                   | IF Output Bandwidth                                                                                                   | -1dB Corner Frequency (Note 22)                                                                                                                                                                       | 1.0                                                | GHz                                    |

| RL <sub>RF</sub>       | RF Input Return Loss (Note 5)                                                                                         | $f_{RF} = 300MHz$ to $500MHz$<br>$f_{RF} = 500MHz$ to $9.0GHz$                                                                                                                                        | >10<br>>10                                         | dB<br>dB                               |

| RL <sub>L0</sub>       | LO Input Return Loss                                                                                                  | $f_{L0} = 300MHz$ to $9.0GHz$                                                                                                                                                                         | >10                                                | dB                                     |

| P <sub>LO(RANGE)</sub> | LO Input Power Range                                                                                                  | (Note 12)                                                                                                                                                                                             | -6 to 12                                           | dBm                                    |

| GP                     | Power Conversion Gain AMPG = $0x06$ , $R_{LOAD} = 100\Omega$ Differential (Note 8)                                    | $\begin{split} f_{RF} &= 400 \text{MHz} \\ f_{RF} &= 1900 \text{MHz} \\ f_{RF} &= 3500 \text{MHz} \\ f_{RF} &= 5800 \text{MHz} \\ f_{RF} &= 7200 \text{MHz} \\ f_{RF} &= 8500 \text{MHz} \end{split}$ | 11.5<br>12.3<br>11.0<br>9.2<br>7.0<br>5.2          | dB<br>dB<br>dB<br>dB<br>dB             |

| NF                     | Noise Figure, Double Side Band (Note 4)                                                                               | $ f_{RF} = 400 MHz \\ f_{RF} = 1900 MHz \\ f_{RF} = 3500 MHz \\ f_{RF} = 5800 MHz \\ f_{RF} = 7200 MHz \\ f_{RF} = 8500 MHz $                                                                         | 15.7<br>16.0<br>17.9<br>21.2<br>23.5<br>28.6       | dB<br>dB<br>dB<br>dB<br>dB             |

| NFBLOCKING             | Noise Figure Under Blocking Conditions<br>Double Side Band, P <sub>IF</sub> , <sub>BLOCKER</sub> = 1.5dBm<br>(Note 7) | $f_{RF} = 400 \text{MHz} \\ f_{RF} = 1900 \text{MHz} \\ f_{RF} = 3500 \text{MHz} \\ f_{RF} = 5800 \text{MHz} \\ f_{RF} = 7200 \text{MHz} \\ f_{RF} = 8500 \text{MHz}$                                 | 16.7<br>17.0<br>18.9<br>22.2<br>24.5<br>29.6       | dB<br>dB<br>dB<br>dB<br>dB             |

| OIP3                   | Output 3rd Order Intercept<br>Unadjusted/Adjusted                                                                     | $f_{RF} = 400 \text{MHz}$ $f_{RF} = 1900 \text{MHz}$ $f_{RF} = 3500 \text{MHz}$ $f_{RF} = 5800 \text{MHz}$ $f_{RF} = 7200 \text{MHz}$ $f_{RF} = 8500 \text{MHz}$                                      | 40/44<br>37/43<br>37/42<br>37/40<br>33/38<br>33/35 | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| OIP2                   | Output 2nd Order Intercept<br>Unadjusted/Adjusted                                                                     | $\begin{split} f_{RF} &= 400 \text{MHz} \\ f_{RF} &= 1900 \text{MHz} \\ f_{RF} &= 3500 \text{MHz} \\ f_{RF} &= 5800 \text{MHz} \\ f_{RF} &= 7200 \text{MHz} \\ f_{RF} &= 8500 \text{MHz} \end{split}$ | 75/80<br>68/75<br>68/70<br>58/65<br>48/55<br>43/48 | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| IIP3 <sub>DEMOD</sub>  | Input 3rd Order Intercept without Amplifier Unadjusted                                                                | $f_{RF} = 400 MHz \\ f_{RF} = 1900 MHz \\ f_{RF} = 3500 MHz \\ f_{RF} = 5800 MHz \\ f_{RF} = 7200 MHz \\ f_{RF} = 8500 MHz$                                                                           | 30<br>26<br>27<br>24<br>24<br>27                   | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| OIP3 <sub>AMP</sub>    | Output 3rd Order Intercept, Amplifier Only (Note 17)                                                                  | $\begin{split} f_{IF} &= 10 MHz \\ f_{IF} &= 100 MHz \\ f_{IF} &= 200 MHz \\ f_{IF} &= 300 MHz \\ f_{IF} &= 500 MHz \\ f_{IF} &= 1000 MHz \end{split}$                                                | 42<br>41<br>38<br>37<br>35<br>30                   | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

# LTC5594

電気的特性 注記がない限り、 $T_C=25^{\circ}C$ 、 $V_{CC}=5V$ 、 $OV_{DD}=EN=CSB=3.3V$ 、SDI=SCK=AMPD=0V、 $V_{CM}=0.9V$ 、 $P_{IF}=1.5dBm(2$ トーン・テストの場合、-1.5dBm/トーン)、 $P_{LO}=6dBm$ 、全てのレジスタはデフォルト値であり、全てのパラメータは復調器とアンプの複合性能を対象に記載されている。(Note 2、3、6、9、21、24)

| SYMBOL                    | PARAMETER                                                 | CONDITIONS                                                                                                                                                                | MIN TYP MAX                                        | UNITS                                  |

|---------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|

| HD2                       | 2nd Order Harmonic Distortion<br>Unadjusted/Adjusted      | f <sub>RF</sub> = 400MHz<br>f <sub>RF</sub> = 1900MHz<br>f <sub>RF</sub> = 3500MHz<br>f <sub>RF</sub> = 5800MHz<br>f <sub>RF</sub> = 7200MHz<br>f <sub>RF</sub> = 8500MHz |                                                    | dBc<br>dBc<br>dBc<br>dBc<br>dBc<br>dBc |

| HD3                       | 3rd Order Harmonic Distortion<br>Unadjusted/Adjusted      | f <sub>RF</sub> = 400MHz<br>f <sub>RF</sub> = 1900MHz<br>f <sub>RF</sub> = 3500MHz<br>f <sub>RF</sub> = 5800MHz<br>f <sub>RF</sub> = 7200MHz<br>f <sub>RF</sub> = 8500MHz | -82<br>-80<br>-76<br>-70<br>-65<br>-68             | dBc<br>dBc<br>dBc<br>dBc<br>dBc<br>dBc |

| P1dB                      | Output 1dB Compression Point                              | f <sub>RF</sub> = 400MHz<br>f <sub>RF</sub> = 1900MHz<br>f <sub>RF</sub> = 3500MHz<br>f <sub>RF</sub> = 5800MHz<br>f <sub>RF</sub> = 7200MHz<br>f <sub>RF</sub> = 8500MHz | 13.2<br>13.2<br>13.2<br>13.2<br>13.2<br>13.2       | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| DCOFFSET                  | DC Offset, Unadjusted (Note 13)                           | f <sub>RF</sub> = 400MHz<br>f <sub>RF</sub> = 1900MHz<br>f <sub>RF</sub> = 3500MHz<br>f <sub>RF</sub> = 5800MHz<br>f <sub>RF</sub> = 7200MHz<br>f <sub>RF</sub> = 8500MHz | 19<br>17<br>17<br>-26<br>-63<br>-19                | mV<br>mV<br>mV<br>mV<br>mV             |

| DC <sub>OFF</sub> (RANGE) | DC Offset Adjustment Range                                | DCOI, DCOQ = 0x00 to 0xFF                                                                                                                                                 | -75 to 75                                          | mV                                     |

| DC <sub>OFF(STEP)</sub>   | DC Offset Step Size                                       |                                                                                                                                                                           | 640                                                | μV                                     |

| ΔG                        | I/Q Gain Mismatch, Unadjusted                             | f <sub>RF</sub> = 400MHz<br>f <sub>RF</sub> = 1900MHz<br>f <sub>RF</sub> = 3500MHz<br>f <sub>RF</sub> = 5800MHz<br>f <sub>RF</sub> = 7200MHz<br>f <sub>RF</sub> = 8500MHz | 0.05<br>0.05<br>0.06<br>0.06<br>0.07<br>0.44       | dB<br>dB<br>dB<br>dB<br>dB             |

| $\Delta G_{(RANGE)}$      | I/Q Gain Mismatch Adjustment Range                        | GERR = 0x00 to 0x3F                                                                                                                                                       | -0.5 to 0.5                                        | dB                                     |

| ΔG(STEP)                  | I/Q Gain Mismatch Adjustment Step Size                    |                                                                                                                                                                           | 0.016                                              | dB                                     |

| Δφ                        | I/Q Phase Mismatch, Unadjusted                            | f <sub>RF</sub> = 400MHz<br>f <sub>RF</sub> = 1900MHz<br>f <sub>RF</sub> = 3500MHz<br>f <sub>RF</sub> = 5800MHz<br>f <sub>RF</sub> = 7200MHz<br>f <sub>RF</sub> = 8500MHz | 0.9<br>1.1<br>3.1<br>1.6<br>1.1                    | Deg<br>Deg<br>Deg<br>Deg<br>Deg<br>Deg |

| $\Delta \phi$ (RANGE)     | I/Q Phase Mismatch Adjustment Range                       | PHA = 0x000 to 0x1FF                                                                                                                                                      | -2.5 to 2.5                                        | Deg                                    |

| $\Delta \phi$ (STEP)      | I/Q Phase Mismatch Adjustment Step Size                   |                                                                                                                                                                           | 0.05                                               | Deg                                    |

| IRR                       | Image Rejection Ratio<br>Unadjusted/Adjusted<br>(Note 10) | f <sub>RF</sub> = 400MHz<br>f <sub>RF</sub> = 1900MHz<br>f <sub>RF</sub> = 3500MHz<br>f <sub>RF</sub> = 5800MHz<br>f <sub>RF</sub> = 7200MHz<br>f <sub>RF</sub> = 8500MHz | 43/70<br>42/65<br>33/65<br>37/60<br>40/60<br>33/60 | dB<br>dB<br>dB<br>dB<br>dB             |

電気的特性 注記がない限り、 $T_C=25^{\circ}C$ 、 $V_{CC}=5V$ 、 $OV_{DD}=EN=CSB=3.3V$ 、SDI=SCK=AMPD=0V、 $V_{CM}=0.9V$ 、 $P_{IF}=1.5dBm$ (2トーン・テストの場合、-1.5dBm/トーン)、 $P_{LO}=6dBm$ 、全てのレジスタはデフォルト値であり、全てのパラメータは復調器とアンプの複合性能を対象に記載されている。(Note 2、3、6、9、21、24)

| SYMBOL                 | PARAMETER                                        | CONDITIONS                                                                                                                                                                                         | MIN                    | TYP                                    | MAX                    | UNITS                                  |

|------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------|------------------------|----------------------------------------|

| LR <sub>LEAK</sub>     | LO to RF Leakage                                 | $\begin{array}{l} f_{L0} = 400 \text{MHz} \\ f_{L0} = 1900 \text{MHz} \\ f_{L0} = 3500 \text{MHz} \\ f_{L0} = 5800 \text{MHz} \\ f_{L0} = 7200 \text{MHz} \\ f_{L0} = 8500 \text{MHz} \end{array}$ |                        | -67<br>-65<br>-56<br>-52<br>-50<br>-55 |                        | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| RL <sub>ISO</sub>      | RF to LO Isolation                               | $ \begin{array}{l} f_{RF} = 400 MHz \\ f_{RF} = 1900 MHz \\ f_{RF} = 3500 MHz \\ f_{RF} = 5800 MHz \\ f_{RF} = 7200 MHz \\ f_{RF} = 8500 MHz \\ \end{array} $                                      |                        | 69<br>57<br>66<br>55<br>57<br>53       |                        | dB<br>dB<br>dB<br>dB<br>dB             |

| RI <sub>ISO</sub>      | RF to IF Isolation (Note 18)                     | $\begin{array}{l} f_{RF} = 400 MHz \\ f_{RF} = 1900 MHz \\ f_{RF} = 3500 MHz \\ f_{RF} = 5800 MHz \\ f_{RF} = 7200 MHz \\ f_{RF} = 8500 MHz \end{array}$                                           |                        | 70<br>48<br>59<br>48<br>40<br>43       |                        | dB<br>dB<br>dB<br>dB<br>dB             |

| Lliso                  | LO to IF Isolation (Note 18)                     | $\begin{array}{l} f_{L0} = 400 \text{MHz} \\ f_{L0} = 1900 \text{MHz} \\ f_{L0} = 3500 \text{MHz} \\ f_{L0} = 5800 \text{MHz} \\ f_{L0} = 7200 \text{MHz} \\ f_{L0} = 8500 \text{MHz} \end{array}$ |                        | 40<br>29<br>38<br>36<br>33<br>35       |                        | dB<br>dB<br>dB<br>dB<br>dB             |

| 電源および                  | 也のパラメータ                                          |                                                                                                                                                                                                    |                        |                                        |                        |                                        |

| Vcc                    | Supply Voltage                                   |                                                                                                                                                                                                    | 4.75                   | 5.0                                    | 5.25                   | V                                      |

| Icc                    | Supply Current                                   |                                                                                                                                                                                                    | 450                    | 470                                    | 500                    | mA                                     |

| ICC(MIX)               | Mixer Supply Current                             | Amplifier Disabled, AMPD = 3.3V                                                                                                                                                                    | 230                    | 250                                    | 270                    | mA                                     |

| I <sub>CC(OFF)</sub>   | Shutdown Current                                 | EN < 0.3V                                                                                                                                                                                          |                        | 20                                     | 900                    | μΑ                                     |

| ICC(SLEEP)             | Sleep Current                                    | EDEM = EDC = EADJ = EAMP = 0                                                                                                                                                                       |                        | 4                                      |                        | mA                                     |

| ton                    | Turn-On Time (Note 14)                           | EN Transition from Logic Low to High                                                                                                                                                               |                        | 1                                      |                        | μs                                     |

| toff                   | Turn-Off Time (Note 15)                          | EN Transition from Logic High to Low                                                                                                                                                               |                        | 1                                      |                        | μs                                     |

| OV <sub>DD</sub>       | Digital I/O Supply Voltage                       |                                                                                                                                                                                                    |                        | 1.2 to 3.                              | 3                      | V                                      |

| V <sub>DH</sub>        | EN Input High Voltage (On)                       |                                                                                                                                                                                                    | 0.7 • OV <sub>DE</sub> | )                                      |                        | V                                      |

| V <sub>DL</sub>        | EN Input Low Voltage (Off)                       |                                                                                                                                                                                                    |                        |                                        | 0.3 • OV <sub>DD</sub> | V                                      |

| I <sub>EN</sub>        | EN Pin Input Current                             | EN = 3.3V                                                                                                                                                                                          |                        | 41                                     |                        | μА                                     |

| V <sub>TEMP</sub>      | TEMP Diode Bias Voltage                          | I <sub>TEMP</sub> = 100 μA into TEMP pin                                                                                                                                                           |                        | 0.774                                  |                        | V                                      |

|                        | TEMP Diode Temperature Slope                     | I <sub>TEMP</sub> = 100 μ A into TEMP pin                                                                                                                                                          |                        | -1.52                                  |                        | mV/°C                                  |

| ZMIX(OUT)              | Mixer Output Impedance                           | Differential                                                                                                                                                                                       |                        | 100  0.6                               | 3                      | $\Omega  pF$                           |

| V <sub>MIX(OUT)</sub>  | Mixer Output DC Voltage                          | Common Mode                                                                                                                                                                                        |                        | 3.6                                    |                        | V                                      |

| Z <sub>AMP(IN)</sub>   | Amplifier Input Impedance                        | Differential                                                                                                                                                                                       |                        | 200  0.2                               | 2                      | $\Omega  pF$                           |

| V <sub>AMP(IN)</sub>   | Amplifier DC Input Voltage                       | Common Mode                                                                                                                                                                                        |                        | 3.6                                    |                        | V                                      |

| Z <sub>AMP(OUT)</sub>  | Amplifier Output Impedance                       | Differential                                                                                                                                                                                       |                        | 4  0.5                                 |                        | kΩ  pF                                 |

| I <sub>AMP(SC)</sub>   | Amplifier DC Output Short Circuit Current        | IFIP = IFIM = IFQP = IFQM = 0V                                                                                                                                                                     |                        | 100                                    |                        | mA                                     |

| V <sub>CM(RANGE)</sub> | V <sub>CM</sub> Pin Voltage Range (Notes 11, 12) |                                                                                                                                                                                                    |                        | 0.5 to 2.                              | 0                      | V                                      |

電気的特性 注記がない限り、 $T_C = 25^{\circ}C$ 、 $V_{CC} = 5V$ 、 $OV_{DD} = EN = CSB = 3.3V$ 、SDI = SCK = AMPD = OV、 $V_{CM} = 0.9V$ 、 $P_{IF} = 1.5dBm(2$ トーン・テストの場合、-1.5dBm/トーン)、 $P_{LO} = 6dBm$ 、全てのレジスタはデフォルト値であり、全てのパラメータは復調器とアンプの複合性能を対象に記載されている。(Note 2、3、6、9、21、24)

| SYMBOL            | PARAMETER                 | CONDITIONS                                               | MIN                    | TYP | MAX                | UNITS |

|-------------------|---------------------------|----------------------------------------------------------|------------------------|-----|--------------------|-------|

| シリアル・イ            | ンタフェース・ピン                 |                                                          |                        |     |                    |       |

| V <sub>IH</sub>   | High Level Input Voltage  | CSB, SDI, SCK                                            | 0.7 • OV <sub>DD</sub> |     |                    | V     |

| V <sub>IL</sub>   | Low Level Input Voltage   | CSB, SDI, SCK                                            |                        | 0.3 | • OV <sub>DD</sub> | V     |

| V <sub>IHYS</sub> | Input Hysteresis Voltage  | CSB, SDI, SCK                                            |                        | 250 |                    | mV    |

| IIN(SER)          | Input Current             | CSB, SDI, SCK (Note 19)                                  |                        |     | 10                 | μA    |

| V <sub>OH</sub>   | High Level Output Voltage | SDO, 10mA Current Sink                                   | 0.7 • OV <sub>DD</sub> |     |                    | V     |

| V <sub>OL</sub>   | Low Level Output Voltage  | SDO, 10mA Current Source                                 |                        | 0.3 | • OV <sub>DD</sub> | V     |

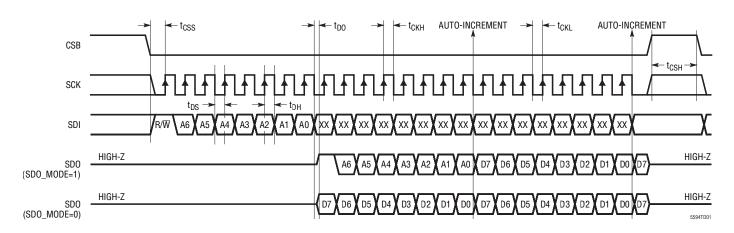

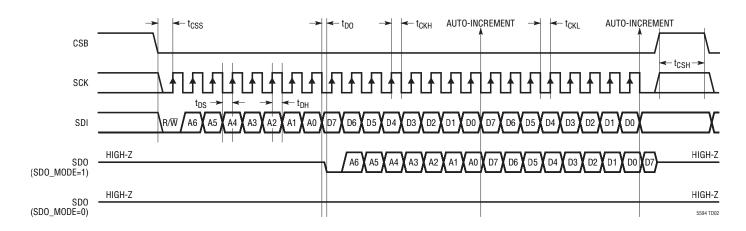

| シリアル・イ            | ンタフェースのタイミング              |                                                          |                        |     |                    |       |

| t <sub>CKH</sub>  | SCK High Time             |                                                          | 25                     |     |                    | ns    |

| t <sub>CKL</sub>  | SCK Low Time              |                                                          | 25                     |     |                    | ns    |

| tcss              | CSB Setup Time            |                                                          | 10                     |     |                    | ns    |

| t <sub>CSH</sub>  | CSB High Time             |                                                          | 10                     |     |                    | ns    |

| t <sub>DS</sub>   | SDI to SCK Setup Time     |                                                          | 6                      |     |                    | ns    |

| t <sub>DH</sub>   | SDI to SCK Hold Time      |                                                          | 6                      |     |                    | ns    |

| t <sub>DO</sub>   | SCK to SD0 Time           | To V <sub>IH</sub> /V <sub>IL</sub> /Hi-Z with 30pF Load |                        |     | 16                 | ns    |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。全てのピンの電圧は、 $V_{\rm CC}$ +0.3 $V_{\rm CC}$ +0.3 $V_{\rm CC}$ +0.3 $V_{\rm CC}$ +0.5 $V_{\rm CC}$ +0.5

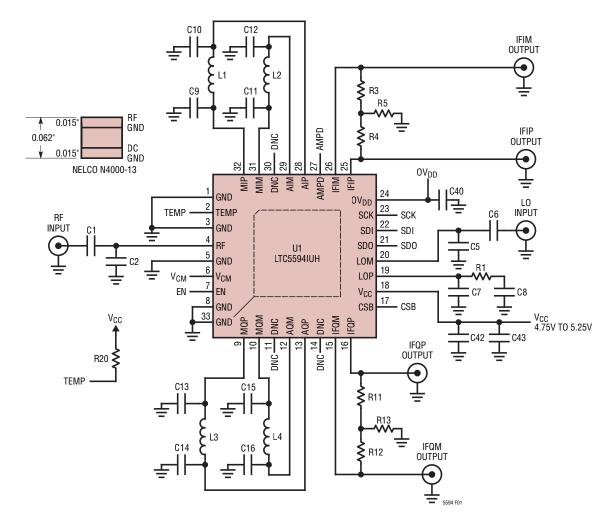

Note 2: テストは図1のテスト回路で行われる。

Note 3:LTC5594は $-40^{\circ}$ C~ $105^{\circ}$ Cのケース温度の動作範囲で動作することが保証されている。

Note 4: DSB ノイズフィギュアは、小信号雑音源を使い、RF入力にはフィルタを使わず、他のRF信号を与えずに、15MHzのベースパンド周波数で測定される。

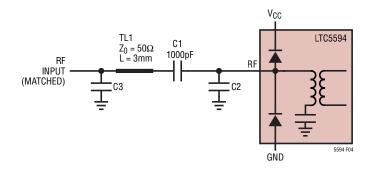

**Note 5**: 300MHz~500MHzの場合、RF入力で6.8pFのシャント・コンデンサを使用する。500MHz~9GHzの場合、0.2pFを使用する。

**Note 6**: 差動アンプ出力(IFIP、IFIM、および IFQP、IFQM)は、180°コンパイナを使用して結合される。

Note 7: ブロッキング状態のノイズフィギュア (NF<sub>BLOCKING</sub>) は、f<sub>LO</sub> + 1MHzの RF 入力信号を使い、60MHzの出力周波数で測定される。RFとLOの両方の入力信号は、ベースバンド出力とともに、適切なフィルタを通す。

Note 8:電力変換利得は、RF入力からI出力またはQ出力までの範囲で定義される。電力変換利得は、I出力とQ出力に100Ωの差動負荷インピーダンスを使って測定される。IFコンバイナおよびスペクトラム・アナライザの終端に起因する全ての損失は除かれている。

**Note 9:** 入力 $P_{RF}$ は、アンプ出力で $P_{IF}$  = -1.5dBm/トーンになるように調整される。RFトーン間隔は、ハイサイドLO の $f_{LO}$  =  $f_{RF}$  + 30MHz の場合、4MHzに設定される。

**Note 10:** イメージ除去比は、 $f_{\rm lf}$  = 12MHz で測定され、測定された利得誤差および位相誤差から計算される。

Note 11: V<sub>CM</sub>ピンは、フロート状態のままにすると、公称 0.9V に自己バイアスされる。

Note 12: これは推奨動作範囲であり、示されている範囲外での動作は可能だが、パラメータによっては性能が低下する可能性がある。

Note 13: IFIPとIFIMの間、およびIFQPとIFQMの間で差動で測定したDCオフセット。示されている値は特性評価データの分布の絶対値の平均である。

Note 14: IFの振幅は最終値の10%以内である。

Note 15: IFの振幅はそのオン状態より少なくとも30dB低い。

Note 16: IF出力はグランドに短絡される。

Note 17:IFトーン間隔は1MHzで設定される。

Note 18:ワーストケースの分離性能は、シングルエンドの各IFポートで測定される。

Note 19: 設計特性によって保証されているが、製造時にはテストされない。

**Note 20**:  $OV_{DD}$ ピンの電圧は、 $V_{CC}+0.3V$  を超えてはならない。超えた場合、ESD ダイオードに損傷が発生する可能性がある。

Note 21:レジスタ定義およびデフォルト値については、付録を参照。

Note 22:ミキサ出力は、アンプ入力に直接接続される。帯域幅は、1つのアンプ出力(IまたはQ)で測定される。

Note 23: $V_{CC}$  は、損傷を防ぐために、5V/msよりも遅い速度で上昇する必要がある。

Note 24: PIF は、アンプの差動出力で測定される。

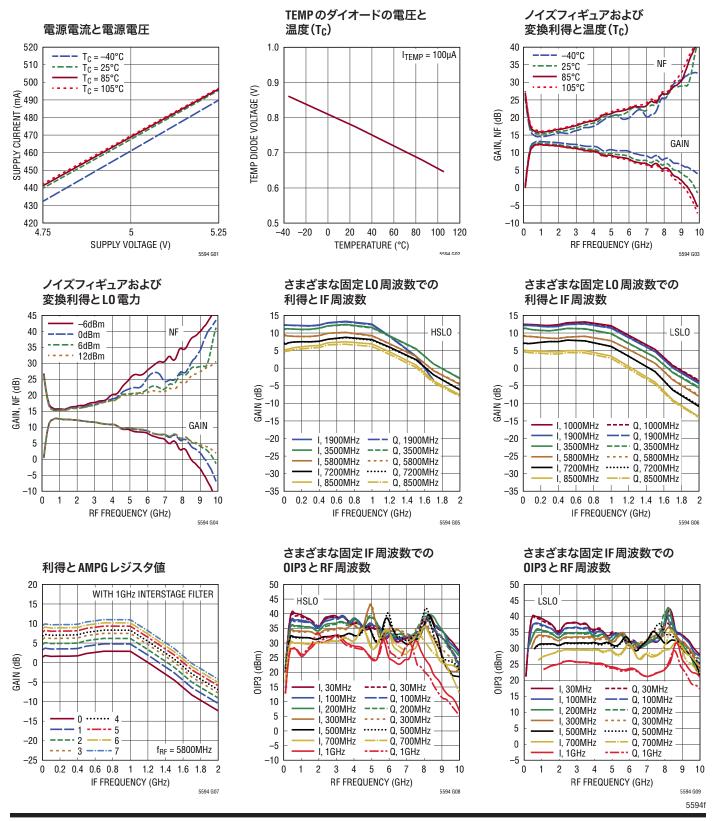

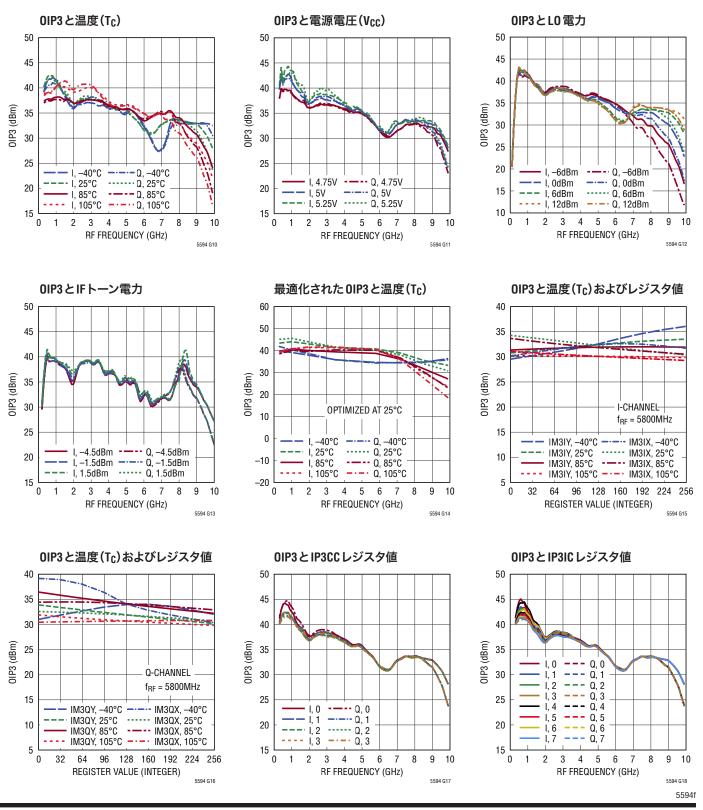

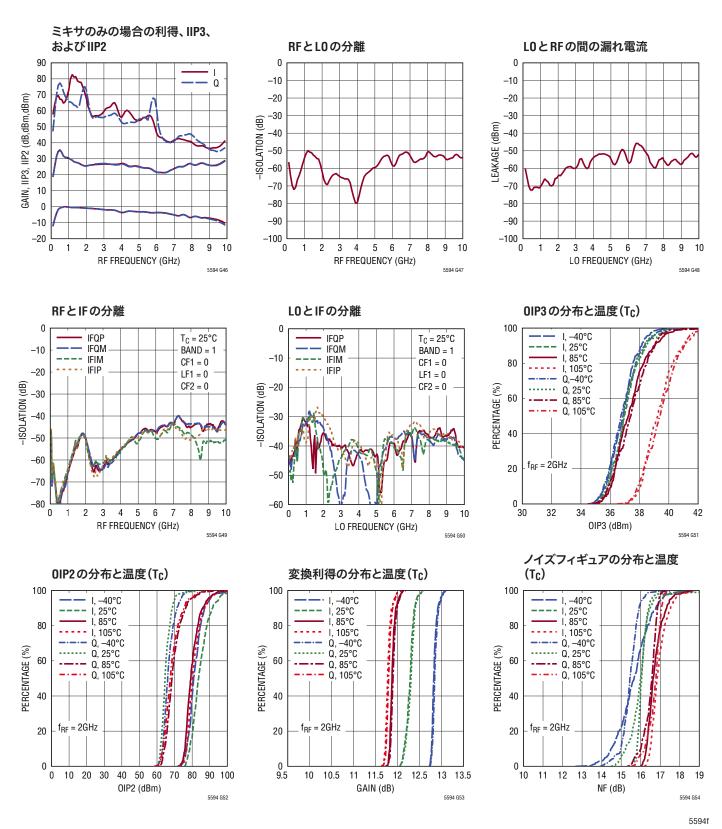

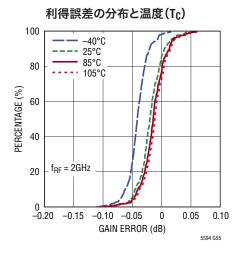

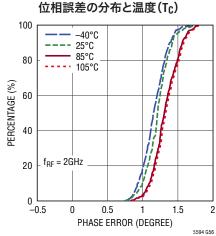

標準的性能特性  $V_{CC} = 5V$ 、EN = 3.3V、 $T_C = 25^{\circ}C$ 、 $P_{LO} = 6dBm$ 、HSLO、RF トーン間隔 = 4MHz、 $f_{IF} = 30MHz$ 、 $P_{IF} = -1.5dBm/$ トーン、レジスタはデフォルト値。注記がない限り、DC ブロック、 $50\Omega$  の終端、および測定からディエンベディングされたアンプ出力での MACOM H9  $180^{\circ}$ コンバイナ。1GHz の段間フィルタを備える図1 に示すテスト回路。

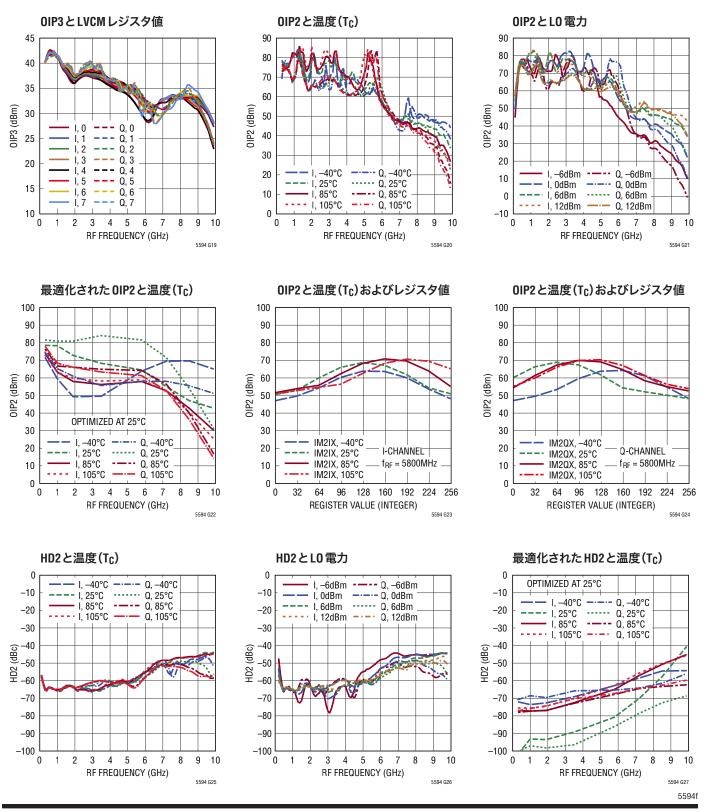

標準的性能特性 V<sub>CC</sub> = 5V、EN = 3.3V、T<sub>C</sub> = 25°C、P<sub>LO</sub> = 6dBm、HSLO、RFトーン間隔 = 4MHz、f<sub>IF</sub> = 30MHz、 P<sub>IF</sub> = −1.5dBm/トーン、レジスタはデフォルト値。注記がない限り、DCブロック、50Ωの終端、および測定からディエンベディングされた アンプ出力でのMACOM H9 180°コンバイナ。1GHzの段間フィルタを備える図1に示すテスト回路。

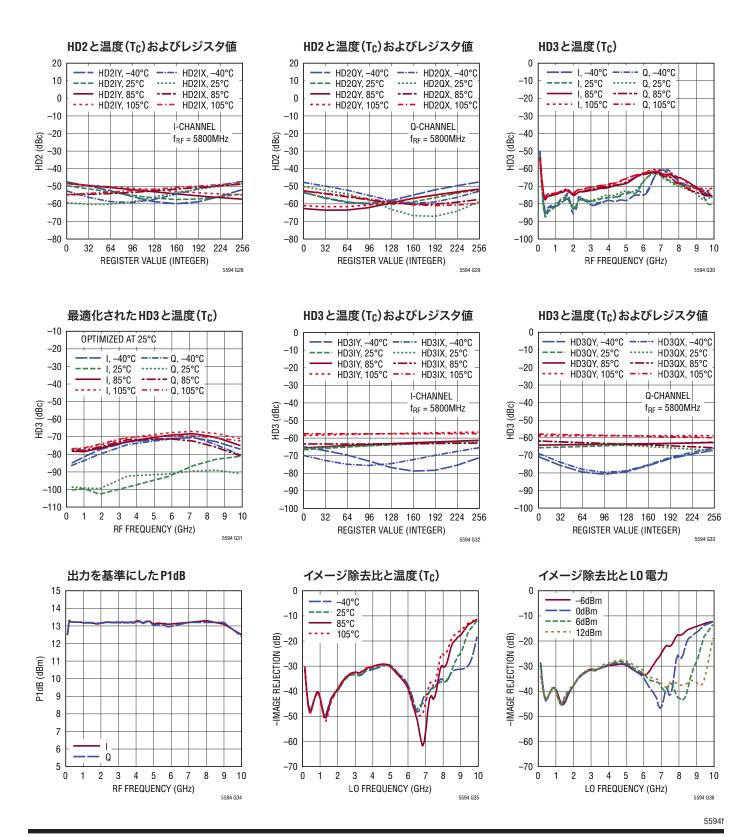

標準的性能特性  $V_{CC} = 5V$ 、EN = 3.3V、 $T_C = 25^{\circ}C$ 、 $P_{LO} = 6dBm$ 、HSLO、RF トーン間隔 = 4MHz、 $f_{IF} = 30MHz$ 、 $P_{IF} = -1.5dBm/$ トーン、レジスタはデフォルト値。注記がない限り、DC ブロック、 $50\Omega$  の終端、および測定からディエンベディングされたアンプ出力での MACOM H9  $180^{\circ}$ コンバイナ。1GHz の段間フィルタを備える図1 に示すテスト回路。

標準的性能特性 V<sub>CC</sub> = 5V、EN = 3.3V、T<sub>C</sub> = 25°C、P<sub>LO</sub> = 6dBm、HSLO、RFトーン間隔 = 4MHz、f<sub>IF</sub> = 30MHz、 P<sub>IF</sub> = −1.5dBm/トーン、レジスタはデフォルト値。注記がない限り、DCブロック、50Ωの終端、および測定からディエンベディングされた アンプ出力でのMACOM H9 180°コンバイナ。1GHzの段間フィルタを備える図1に示すテスト回路。

10

詳細: www.linear-tech.co.jp/LTC5594

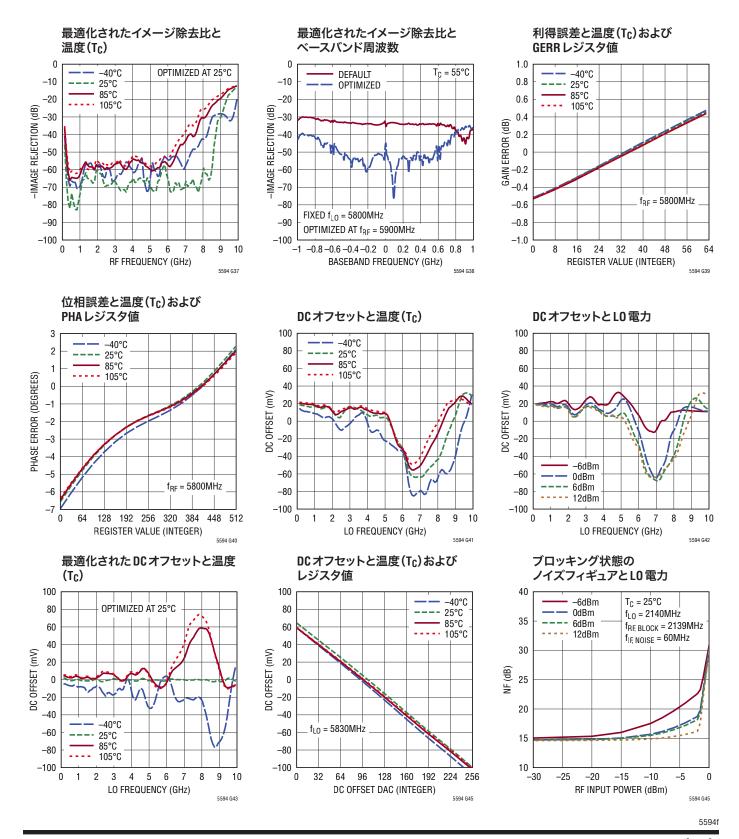

標準的性能特性  $V_{CC} = 5V$ 、EN = 3.3V、 $T_C = 25^{\circ}C$ 、 $P_{LO} = 6dBm$ 、HSLO、RF トーン間隔 = 4MHz、 $f_{IF} = 30MHz$ 、 $P_{IF} = -1.5dBm/$ トーン、レジスタはデフォルト値。注記がない限り、DC ブロック、 $50\Omega$  の終端、および測定からディエンベディングされたアンプ出力での MACOM H9  $180^{\circ}$ コンバイナ。1GHz の段間フィルタを備える図1 に示すテスト回路。

標準的性能特性  $V_{CC} = 5V$ 、EN = 3.3V、 $T_C = 25^{\circ}C$ 、 $P_{LO} = 6dBm$ 、HSLO、RF トーン間隔 = 4MHz、 $f_{IF} = 30MHz$ 、 $P_{IF} = -1.5dBm/$ トーン、レジスタはデフォルト値。注記がない限り、DC ブロック、 $50\Omega$  の終端、および測定からディエンベディングされたアンプ出力での MACOM H9  $180^{\circ}$ コンバイナ。1GHz の段間フィルタを備える図1 に示すテスト回路。

詳細: www.linear-tech.co.jp/LTC5594

標準的性能特性  $V_{CC} = 5V$ 、EN = 3.3V、 $T_C = 25°C$ 、 $P_{LO} = 6dBm$ 、HSLO、RF トーン間隔 = 4MHz、 $f_{IF} = 30MHz$ 、 $P_{IF} = -1.5dBm/トーン、レジスタはデフォルト値。注記がない限り、DCブロック、<math>50\Omega$ の終端、および測定からディエンベディングされたアンプ出力でのMACOM H9 180°コンバイナ。1GHzの段間フィルタを備える図1に示すテスト回路。

### ピン機能

TEMP(ピン2): 温度モニタ・ダイオード。このピンとグランドの間にダイオードを接続して、ダイ温度を測定できます。100μAの順方向バイアス電流をこのピンに入力することができ、順方向電圧降下をダイ温度の関数として測定できます。

**RF(ピン4)**:50ΩのRF入力。このピンは、カップリング・コンデンサ(1000pFを推奨)を使用してDCを遮断する必要があります。

V<sub>CM</sub> (ピン6): IFアンプの同相出力電圧調整。ソース抵抗を、 1k以下にする必要があります。このピンを未接続のままにする と、内部で0.9Vに自己バイアスします。

**EN(ピン7)**: イネーブル・ピン。このピンをロジック"H"にすると、デバイスがイネーブルされます。このピンがどこにも接続されていないと(開放回路状態)、内部の200kプルダウン抵抗により、デバイスは確実にディスエーブル状態に留まります。

MQP、MQM、MIM、MIP(ピン9、10、31、32): ミキサの差動出力ピン。アンプ入力ピンに接続した場合、各ピンのDCバイアス点は $V_{CC}$  – 1.4Vになります。通常は、MQM (P)ピンまたはMIM (P)ピンとAQM (P)ピンまたはAIM (P)ピンの間でローパス・フィルタを使用して、高周波数の混合積を抑制します。詳細については「アプリケーション情報」のセクションを参照してください。

**DNC(ピン11、14、30)**:接続しないでください。これらのピンには、何も接続しないでください。

AQM、AQP、AIP、AIM(ピン12、13、28、29): アンプの差動入力ピン。ミキサ出力ピンに接続した場合、各ピンのDCバイアス点は $V_{CC}$  – 1.4V になります。通常は、AQM (P) ピンまたはAIM (P) ピンと MQM (P) ピンまたはMIM (P) ピンの間でローパス・フィルタを使用して、高周波数の混合積を抑制します。詳細については「アプリケーション情報」のセクションを参照してください。

IFQM、IFQP、IFIP、IFIM (ピン15、16、25、26): IFアンプの出力ピン。出力アンプによって使用される電流は、各ピンとグランドの間に接続された $25\Omega\sim200\Omega$ の抵抗および $V_{CM}$ 制御電圧によって設定されます。

**CSB**(ピン17):チップ選択バー。CSBが"L"の場合、シリアル・インタフェースがイネーブルされます。このピンは  $1.2V \sim 3.3V$  のロジック・レベルで駆動できます。

**V<sub>CC</sub> (ピン18)**:正電源ピン。このピンは並列接続した1000pF と4.7μFのコンデンサを使ってグランドにバイパスします。

**LOP、LOM(ピン19、20)**: LO入力。外部整合は必要ありません。 $50\Omega$ のシングルエンドまたは $100\Omega$ の差動で駆動できます。 LOピンは、カップリング・コンデンサ(1000pFを推奨)を使用してDCブロックする必要があります。シングルエンドで駆動した場合、未使用のピンは、DCブロッキング・コンデンサと直列に接続した $50\Omega$ の抵抗を使用して終端する必要があります。

**SDO(ピン21)**:シリアル・データ出力。この出力は、1.2V~3.3V のロジック・レベルに対応できます。 読み出しモードの間、データは MSB を先頭にして読み出されます。

SDI(ピン22):シリアル・データ入力。データは、SCKの立ち上がりエッジで、MSBを先頭にしてモード制御レジスタにクロックインされます。SDIは $1.2V \sim 3.3V$ のロジック・レベルで駆動できます。

**SCK+ (ピン23)**:シリアル・クロック入力。SDIは1.2V  $\sim$  3.3V のロジック・レベルで駆動できます。

$\mathbf{OV_{DD}}$ (ピン24): 正のデジタル・インタフェース電源ピン。このピンは、デジタル・インタフェースのロジック・レベルを設定します。  $1.2V\sim3.3V$ を使用できます。このピンは、 $1\mu F$ のコンデンサを使ってグランドにバイパスする必要があります。  $\mathbf{ESD}$  ダイオードへの損傷を防ぐため、 $\mathbf{V_{CC}}$  電源を供給してから  $\mathbf{OV_{DD}}$  電源を供給する必要があります。

AMPD(ピン27): IFアンプのディスエーブル・ピン。このピンをロジック"H"にすると、IFアンプがディスエーブルされます。IFアンプの状態は、AMPDとEAMPレジスタの論理積です。このピンがどこにも接続されていない(開放回路状態)場合、内部の200kプルダウン抵抗により、IFアンプはデフォルトでイネーブル状態になります。

GND(ピン1、3、5、8、露出パッド・ピン33): グランド・ピン。これらのピンは、回路基板のRFグランド・プレーンに半田付けする必要があります。裏面の露出パッドのグランド接続は、多数のスルーホール・ビアを使って、プリント回路基板のグランド・プレーンに低インダクタンスで接続し、熱的に十分接触させます。レイアウト情報を参照。

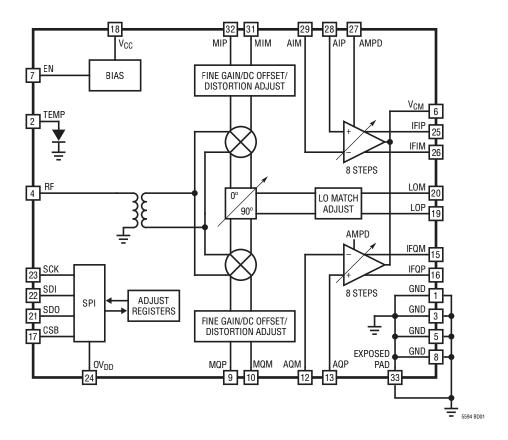

# ブロック図

### タイミング図

### SPIポートのタイミング(読み出しモード)

### SPIポートのタイミング(書き込みモード)

# テスト回路

| REF DES            | VALUE   | SIZE | VENDOR | REF DES              | VALUE  | SIZE | VENDOR    |

|--------------------|---------|------|--------|----------------------|--------|------|-----------|

| C1, C6, C8, C42    | 1000pF  | 0402 | Murata | L1 T0 L4             | 8.2nH  | 0805 | Coilcraft |

| C2                 | 0.2pF   | 0402 | Murata | R1, R3, R4, R11, R12 | 49.9Ω  | 0402 |           |

| C5, C7             | 0.3pF   | 0402 | Murata | R5, R13              | 0Ω     | 0402 |           |

| C9, C11, C13, C15  | 1.0pF   | 0201 | Murata | R20                  | 40.2kΩ | 0402 |           |

| C10, C12, C14, C16 | 3.0pF   | 0201 | Murata |                      |        |      |           |

| C40                | 1μF     | 0603 | Murata |                      |        |      |           |

| C43                | 4.7 µ F | 0805 | Murata |                      |        |      |           |

図1. テスト回路図

# テスト回路

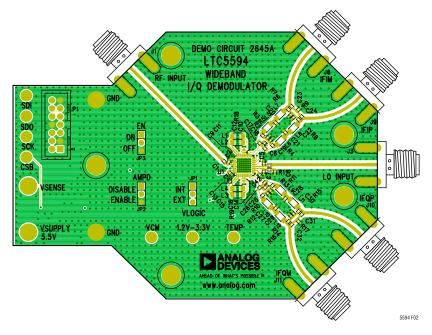

図2. 評価用ボードの部品面

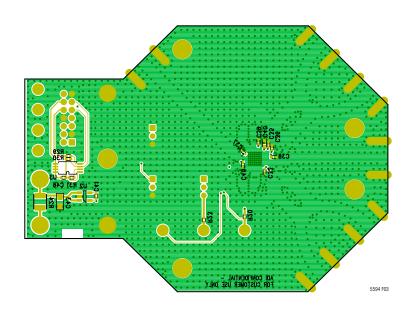

図3. 評価用ボードの底面

LTC5594は高ダイナミックレンジのレシーバ・アプリケーション向けに設計されたIQ復調器です。RFバラン、I/Qミキサ、直交LOアンプ、IFアンプ、ならびにDCオフセット、イメージ除去比、および非直線性の補正回路で構成されています。

#### 動作

LTC5594のブロック図に示すように、RF入力信号は、内蔵のバラン・トランスによって差動信号に変換されてから、IチャネルとQチャネルのミキサに進みます。

LO入力は、プログラム可能な回路網を使用してインピーダンス整合され、その後、内部高精度位相シフタによって、その位相が正確に90°シフトされます。この位相シフタは、300MHz~9GHzの範囲のLO入力範囲全体にわたって正確な直交関係を維持します。さらに、位相シフタは、ミキサ間の位相の不整合、およびフィルタ部品の不整合によってIF経路に発生する位相の不整合を補償するために、約0.05°の分解能でのIチャネルとQチャネルのLOの間の位相差の微調整を可能にします。

差動ミキサIF出力信号は、内蔵IFアンプに入力される前に、fRF+fLO信号およびその他の高周波数の混合積を除去するために、デバイスの外部でフィルタリングされます。IFアンプは、調整可能な利得および同相出力電圧を備えており、A/Dコンバータと直接インタフェースをとることができます。LTC5594の両方のIF出力チャネル間の利得バランスは、約0.016dBの分解能で微調整することができ、それによって、デバイスの内部で発生するか、または外部アンプおよびフィルタによって発生するIF信号経路における利得の不整合を補償します。両方のIFチャネルにおけるDCオフセットは、A/Dコンバータの入力で累積されるDCオフセットを最小限に抑えるように調整できます。

IF利得レジスタ、利得誤差および位相誤差調整レジスタ、DC オフセット調整レジスタ、ならびに非直線性調整レジスタは、 4線式のシリアル・インタフェースを介してデジタル制御されます。レジスタ・マップについては、付録で詳述されています。

#### RF入力ポート

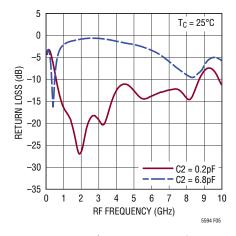

図4に、内蔵のバラン・トランスに接続された復調器のRF入力の簡略回路図を示します。RF入力ピンには外部のDC電圧を印加しないでください。このピンに流れ込むDC電流はデバイスに損傷を与える可能性があります。直列のDCブロッキング・コンデンサを使ってRF入力ピンをRF信号源に結合します。図5に示すように、RF入力ポートは、C2に0.2pFのコンデンサを使用した場合、500MHz~9GHzの周波数範囲にわたって10dBよりも大きいリターン・ロスとよく整合しています。C3の0.1pFのコンデンサを、50Ωの入力伝送線路上にあるC1から3mm離して配置すると、高周波でのリターン・ロスが向上することがあります。また、C2を6.8pFに変更することによって、RFピンを300MHz~500MHzの周波数範囲で外部から整合させることもできます。C2が0.2pFである場合のRF入力のインピーダンスおよび入力反射係数を表1に示します。入力の伝送線路の長さの影響は測定値から除かれています。

図4. RF入力と外部整合部品の簡略回路図

表1. RF 入力インピーダンス

|          |              | \$11  |        |

|----------|--------------|-------|--------|

| 周波数(MHz) | 入力インピーダンス(Ω) | 振幅    | 位相(°)  |

| 300      | 30.0 + j57.1 | 0.594 | 122.5  |

| 1000     | 66.8 – j5.3  | 0.151 | -17.6  |

| 1500     | 49.4 – j10.4 | 0.092 | -94.0  |

| 2000     | 46.8 + j4.0  | 0.048 | 133.7  |

| 2500     | 48.9 + j12.8 | 0.113 | 96.0   |

| 3000     | 56.5 + j10.6 | 0.111 | 56.5   |

| 3500     | 62.7 – j5.8  | 0.124 | -24.0  |

| 4000     | 61.5 – j23.6 | 0.233 | -62.6  |

| 4500     | 55.4 – j30.6 | 0.278 | -78.5  |

| 5000     | 47.0 – j26.3 | 0.236 | -97.9  |

| 5500     | 38.6 – j16.1 | 0.191 | -133.2 |

| 6000     | 33.7 – j7.5  | 0.206 | -162.0 |

| 7000     | 32.3 – j12.0 | 0.240 | -155.2 |

| 8000     | 33.9 + j0.1  | 0.192 | 179.7  |

| 9000     | 48.0 + j44.0 | 0.404 | 93.6   |

図5. C2 = 0.2pFおよび6.8pFでのRF入力のリターン・ロス

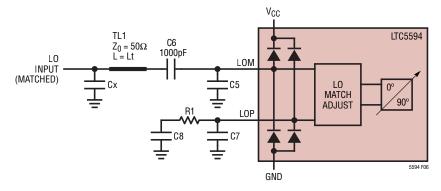

### LO 入力ポート

復調器のLO入力インタフェースを図6に示します。入力はプログラム可能な入力整合および高精度直交位相シフタによって構成されており、I/Qミキサを駆動するLOバッファ・アンプ向けに位相を0°および90°シフトさせたLO信号を生成します。LOPとLOMの入力にはDCブロッキング・コンデンサが必要です。シングルエンドのLO入力を使用する場合、未使用のLO入力(図6のLOP)を $50\Omega$ で終端する必要があります。

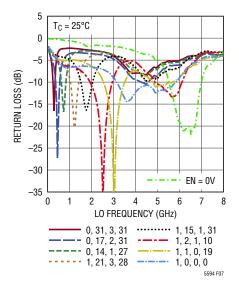

プログラム可能な入力整合調整は、表2に示すレジスタ・マップに詳述されているように、BAND、CF1、LF1、およびCF2の各レジスタによって制御されます。表2におけるレジスタ設定のリターン・ロスを図7に示します。

表2. シングルエンドLO整合のためのレジスタ設定

| LO周波数(MHz)   | 帯域 | CF1 | LF1 | CF2 |

|--------------|----|-----|-----|-----|

| 300 to 339   | 0  | 31  | 3   | 31  |

| 339 to 398   | 0  | 21  | 3   | 24  |

| 398 to 419   | 0  | 14  | 3   | 23  |

| 419 to 556   | 0  | 17  | 2   | 31  |

| 556 to 625   | 0  | 10  | 2   | 23  |

| 625 to 801   | 0  | 15  | 1   | 31  |

| 801 to 831   | 0  | 14  | 1   | 27  |

| 831 to 1046  | 0  | 8   | 1   | 21  |

| 1046 to 1242 | 1  | 31  | 3   | 31  |

| 1242 to 1411 | 1  | 21  | 3   | 28  |

| 1411 to 1696 | 1  | 17  | 2   | 26  |

| 1696 to 2070 | 1  | 15  | 1   | 31  |

| Default      | 1  | 8   | 3   | 3   |

| 2070 to 2470 | 1  | 8   | 1   | 21  |

| 2470 to 2980 | 1  | 2   | 1   | 10  |

| 2980 to 3500 | 1  | 1   | 0   | 19  |

| 3500 to 9000 | 1  | 0   | 0   | 0   |

図 6. LO 入力とシングルエンド駆動回路の簡略回路図

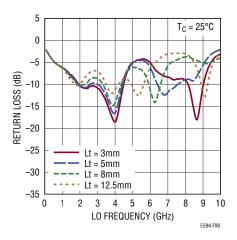

LOの入力周波数が6GHzから9GHzまでの場合に、さまざまな長さの入力TL1 伝送線路に対する高帯域LOの入力リターン・ロスを図8に示します。50Ωの入力伝送線路上にあるCxに0.2pFのコンデンサを使用することにより、リターン・ロスを10dBより大きくすることができます。Cxにコンデンサがない場合で、BAND、CF1、LF1、およびCF2レジスタを1、0、0、0に設定した場合、高帯域LOの入力リターン・ロスを表3に示します。

図7. シングルエンドLO入力のリターン・ロスと BAND、CF1、LF1、およびCF2

図8. 高帯域LOの入力リターン・ロスと 入力伝送線路の長さLt

表3. 高帯域LOの入力インピーダンス

|          |               | \$11  |        |

|----------|---------------|-------|--------|

| 周波数(MHz) | 入力インピーダンス(Ω)  | 振幅    | 位相(°)  |

| 5000     | 87.2 + j37.9  | 0.436 | 46.4   |

| 5500     | 121.5 + j32.1 | 0.503 | 27.8   |

| 6000     | 132.1 + j5.4  | 0.453 | 4.8    |

| 6500     | 95.2 – j17.7  | 0.347 | -23.8  |

| 7000     | 73.5 – j39.5  | 0.406 | -58.2  |

| 7500     | 69.0 – j47.5  | 0.467 | -66.0  |

| 8000     | 77.8 – j51.9  | 0.531 | -59.9  |

| 8500     | 77.8 – j38.8  | 0.361 | -75.4  |

| 9000     | 58.8 – j38.8  | 0.402 | -122.6 |

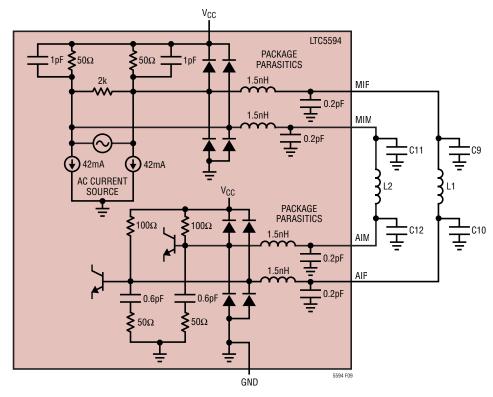

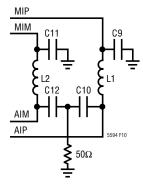

### 段間フィルタ

大きいf<sub>RF</sub>+f<sub>LO</sub>およびミキサ出力からのその他の混合積を抑制するために、段間IFフィルタをMIP(MIM)ピンとAIP(AIM)ピンの間、およびMQP(MQM)ピンとAQP(AQM)ピンの間で使用する必要があります。このフィルタを使用しなかった場合、目的の信号に関して、アンプの直線性が悪化する可能性があります。図9に、推奨されるローパス・フィルタを示します。表4に、さまざまな帯域幅のローパス応答に使用される標準値を示します。

表 4. 段間ローパス・フィルタの部品値

| 1dB BW (MHz) | L1、L2(nH) | C9、C11(pF) | C10、C12(pF) |  |  |

|--------------|-----------|------------|-------------|--|--|

| 20           | 330       | 39         | 120         |  |  |

| 50           | 150       | 15         | 47          |  |  |

| 100          | 68        | 10         | 22          |  |  |

| 300          | 33        | 4.7        | 6.8         |  |  |

| 500          | 22        | 3.0        | 3.0         |  |  |

| 1000         | 8.2       | 1.0        | 3.0         |  |  |

C10とC12を、アンプ入力にできるだけ近づけて配置することは重要です。アンプ入力に長いラインを接続すると、不安定になる可能性があります。図10に示すように、 $50\Omega$ の同相終端抵抗を使用して、長いラインまたはより高次のフィルタリング(あるいはその両方)での良好な安定性を保証することができます。2xLO、 $f_{RF}+f_{LO}$ 、およびその他の混合積の効率的なフィルタリングを実現するために、C9とC11をミキサ出力にできるだけ近づけて配置する必要があります。

フィルタ内のコンデンサの値を調整することによって、IF応答の周波数スロープを追加または削除することができます。RF入力には、2GHzより高い周波数では約-1dB/GHzの周波数スロープがあります。ハイサイドLO(HSLO)を使用した場

図9. 段間フィルタを接続したミキサ出力およびIFアンプ入力の簡略回路図

図10. 同相終端抵抗を接続した段間IFフィルタ

合、得られるIFスロープは1dB/GHzになります。ローサイドLO (LSLO)を使用した場合、得られるIFスロープは-1dB/GHzになります。HSLOまたはLSLOの場合、全体的に平坦なIF 応答を得るために、フィルタ帯域幅にわたって約1dBのピーキングまたはロールオフを実現できるように、IFフィルタ部品の値を調整できます。

### IチャネルとQチャネルの出力

IチャネルとQチャネルの出力信号間の位相関係は固定されています。LO入力周波数がRF入力周波数より高い(または低い)とき、Qチャネルの出力(IFQP、IFQM)はIチャネルの出力(IFIP、IFIM)より90°だけ位相が進みます(または遅れます)。

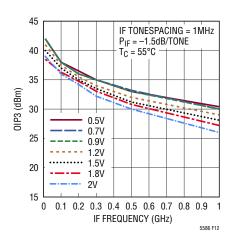

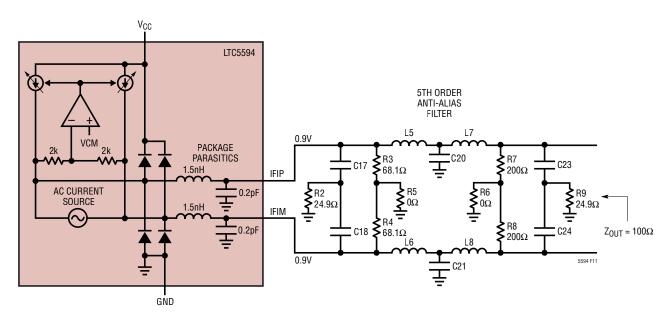

図11に、IFアンプ出力の簡略回路図を示します。電流モード出力には、同相電圧レベルを設定するために、終端抵抗が必要です。最適な動作電流は、1つの出力につき18mAです。同相電圧が0.9Vの場合は、各出力を50 $\Omega$ で終端することを推奨します(R5、R6)。同相終端抵抗を追加することにより、より高い同相電圧での動作が可能になります。例えば、1.8Vで動作させるには、25 $\Omega$ (R5 = 66.5 $\Omega$ およびR6 = 0 $\Omega$ またはR5 = R6 = 43.2 $\Omega$ )の同相抵抗を追加して、18mAの出力電流を維持します。あるいは、各出力とグランドの間に100 $\Omega$ の終端抵抗を使用することにより、1.8Vの同相電圧と6dB超の変換利得を確保します。より低い同相電圧で動作させるには、変換利得を犠牲にして各出力により低い終端抵抗を使用するか、あるいは終端抵抗の接続部に負電源を使用します。図12に、さまざまな同相電圧でのアンプ単独のOIP3を示します。

図12. アンプ単独のOIP3と出力同相電圧 (V<sub>CM</sub>)

アンプの利得は、AMPGレジスタを使用して、8dBから 15dBまで約 1dB刻みの 8 段階に調整できます。AMPG = 0x7に設定すると、利得は約 15dBに設定され、AMPG = 0x0に設定すると、利得は約 8dBに設定されます。

A/D コンバータとインタフェースをとる場合の標準的なアンチ エイリアス・フィルタを図11に示します。R3||R7およびR4||R8 という並列の組み合わせによって、A/Dコンバータの差動イ ンピーダンスが設定されます。このフィルタの入力および出力 は、高周波数用の同相終端抵抗を内蔵しています。これらは、 入力でのC17、C18、および24.9Ω、ならびに出力でのC23、 C24、および24.9Ωで形成されています。アンプ出力での同相 終端は安定性確保の役割を果たし、A/Dコンバータ入力での 同相終端は、A/Dコンバータ内でのサンプリング・コンデンサ からの高周波キックバックに対する終端の役割を果たします。 表5に、アンチエイリアス・フィルタの標準値の一部と1dBのカッ トオフ周波数を示します。IF帯域の平坦性とリップルを最適 化するために、パッケージの寄生要素を含めて、シミュレータ でIF段間フィルタとアンチエイリアス・フィルタの両方を一緒 に設計できます。RFスロープおよびHSLOまたはLSLOに起 因する追加スロープは、この方法を使用して補償できます。ア ンチエイリアス・フィルタのレイアウトは、アンプの出力および A/Dコンバータの入力ができるだけ近くなるように行う必要が あります。これは、長いラインで追加寄生要素が発生するのを 防ぐためです。

図 11. アンチエイリアス・フィルタを接続したIFアンプ出力の簡略回路図

表5. アンチエイリアス・ローパス・フィルタの部品値

| 1dB BW<br>(MHz) | L5∼L8<br>(nH) | C17、C18<br>(pF) | C20、C21<br>(pF) | C23、C24<br>(pF) |

|-----------------|---------------|-----------------|-----------------|-----------------|

| 20              | 560           | 56              | 180             | 82              |

| 50              | 240           | 22              | 68              | 33              |

| 100             | 120           | 12              | 39              | 22              |

| 300             | 33            | 3.9             | 8.2             | 6.8             |

| 500             | 22            | 1.8             | 6.8             | 3.3             |

| 1000            | 8             | 1.0             | 3.3             | 1.8             |

表6および表7に、全てのポートで $50\Omega$ の終端抵抗を使用した場合のアンプ単独での差動Sパラメータと同相Sパラメータを示します。加えて、入力ポートと出力ポートには、 $50\Omega$ と直列に2pFの値を持つ同相終端抵抗が使用されています。

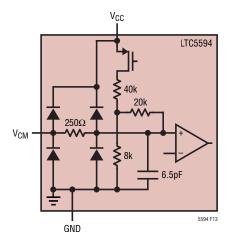

同相帰還アンプは、同相出力電圧を $V_{CM}$ ピンの電圧の約 20mV以内に維持します。 $V_{CM}$ ピンのインタフェースを図 13 に示します。 $V_{CM}$ ピンは、出力インピーダンスが  $1k\Omega$ 未満の電圧源で駆動する必要があります。 $V_{CM}$ ピンをバイアスしない場合、出力同相電圧は、 $40k\Omega$ と  $8k\Omega$ の抵抗で形成される内部分圧器によって与えられる公称 0.9V に維持されます。 $V_{CM}$ ピンを A/Dコンバータの同相リファレンス・ピンに接続することにより、IFアンプの出力同相電圧を A/Dコンバータの同相電圧に追随させることができます。

図13. V<sub>CM</sub>入力ピンの簡略回路図

表 6. IFアンプの S パラメータ (差動モード)

| 20, 110 100 100 100 100 100 100 100 100 1 |                 |        |                 |        |                 |       |                 |        |

|-------------------------------------------|-----------------|--------|-----------------|--------|-----------------|-------|-----------------|--------|

| IF                                        | S <sub>11</sub> |        | S <sub>21</sub> |        | S <sub>12</sub> |       | S <sub>22</sub> |        |

| (MHz)                                     | 振幅              | 位相     | 振幅              | 位相     | 振幅              | 位相    | 振幅              | 位相     |

| 0.001                                     | 0.204           | -179.9 | 2.129           | 180.0  | 1.8e-4          | 164.8 | 0.014           | 178.5  |

| 100                                       | 0.203           | 176.0  | 2.154           | 171.9  | 5.4e-4          | 118.0 | 0.026           | -120.9 |

| 200                                       | 0.205           | 172.2  | 2.170           | 163.7  | 1.0e-4          | 102.8 | 0.050           | -112.0 |

| 300                                       | 0.207           | 168.5  | 2.197           | 155.6  | 1.7e-4          | 92.8  | 0.079           | -113.5 |

| 400                                       | 0.210           | 164.8  | 2.239           | 147.3  | 2.8e-4          | 93.7  | 0.111           | -118.3 |

| 500                                       | 0.215           | 160.9  | 2.292           | 138.8  | 3.2e-4          | 95.4  | 0.147           | -125.0 |

| 600                                       | 0.221           | 157.0  | 2.363           | 130.1  | 4.0e-4          | 92.0  | 0.186           | -132.1 |

| 700                                       | 0.227           | 153.0  | 2.445           | 121.2  | 5.0e-4          | 92.1  | 0.230           | -140.0 |

| 800                                       | 0.235           | 149.0  | 2.535           | 112.0  | 5.5e-4          | 86.2  | 0.279           | -148.1 |

| 900                                       | 0.242           | 144.6  | 2.642           | 102.0  | 6.9e-4          | 93.2  | 0.334           | -157.0 |

| 1000                                      | 0.251           | 140.6  | 2.770           | 92.3   | 7.9e-4          | 92.7  | 0.396           | -166.2 |

| 1500                                      | 0.303           | 117.6  | 3.420           | 32.3   | 0.003           | 92.6  | 0.738           | 134.4  |

| 2000                                      | 0.365           | 90.2   | 3.318           | -45.5  | 0.005           | 33.2  | 0.828           | 70.0   |

| 2500                                      | 0.385           | 56.1   | 2.232           | -105.2 | 0.005           | -3.1  | 0.666           | 13.1   |

| 3000                                      | 0.365           | 16.6   | 2.620           | -160.2 | 0.005           | -34.2 | 0.488           | -38.4  |

| 3500                                      | 0.319           | -28.2  | 1.021           | 157.4  | 0.005           | -61.9 | 0.418           | -94.7  |

| 4000                                      | 0.307           | -83.4  | 0.742           | 113.3  | 0.005           | -79.5 | 0.409           | -150.6 |

表7. IFアンプのSパラメータ(同相モード)

| IF    | S <sub>11</sub> |        | S <sub>21</sub> |        | S <sub>12</sub> |        | \$22  |        |

|-------|-----------------|--------|-----------------|--------|-----------------|--------|-------|--------|

| (MHz) | 振幅              | 位相     | 振幅              | 位相     | 振幅              | 位相     | 振幅    | 位相     |

| 0.001 | 0.184           | -138.7 | 9.2e-4          | -112.8 | 0.037           | -65.3  | 0.985 | 179.8  |

| 100   | 0.186           | 172.5  | 0.085           | -118.9 | 0.013           | -68.6  | 0.152 | 126.7  |

| 200   | 0.188           | 166.6  | 0.173           | -134.7 | 0.007           | -91.8  | 0.125 | 116.7  |

| 300   | 0.191           | 160.2  | 0.237           | -150.0 | 0.004           | -113.1 | 0.097 | 97.3   |

| 400   | 0.196           | 154.4  | 0.291           | -163.8 | 0.002           | -145.4 | 0.067 | 75.2   |

| 500   | 0.202           | 148.4  | 0.340           | -176.8 | 0.002           | 170.2  | 0.037 | 43.6   |

| 600   | 0.210           | 142.8  | 0.387           | 170.9  | 0.002           | 137.0  | 0.023 | -38.0  |

| 700   | 0.219           | 137.2  | 0.436           | 159.1  | 0.003           | 118.1  | 0.051 | -97.8  |

| 800   | 0.230           | 132.0  | 0.488           | 147.1  | 0.003           | 107.8  | 0.094 | -121.5 |

| 900   | 0.243           | 126.5  | 0.550           | 134.9  | 0.004           | 106.6  | 0.148 | -137.0 |

| 1000  | 0.252           | 120.9  | 0.612           | 122.2  | 0.006           | 104.8  | 0.211 | -151.3 |

| 1500  | 0.325           | 96.7   | 0.981           | 43.4   | 0.020           | 80.4   | 0.749 | 136.1  |

| 2000  | 0.438           | 72.1   | 0.776           | -46.1  | 0.036           | 18.6   | 1.005 | 55.9   |

| 2500  | 0.549           | 40.1   | 0.496           | -97.1  | 0.041           | -21.9  | 0.873 | 2.9    |

| 3000  | 0.601           | 6.9    | 0.397           | -143.2 | 0.042           | -52.2  | 0.764 | -37.3  |

| 3500  | 0.618           | -27.5  | 0.281           | -175.7 | 0.044           | -80.3  | 0.668 | -72.7  |

| 4000  | 0.595           | -60.3  | 0.254           | 147.3  | 0.046           | -101.2 | 0.620 | -107.0 |

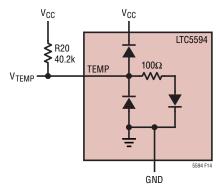

### 温度ダイオード

TEMPピンの回路図を図14に示します。温度ダイオードを使用して、ダイ温度を直接測定できます。 $100\mu$ Aの電流源を生成してダイオードを読み出すため、 $40k\Omega$ の抵抗を $V_{CC}$ に接続することを推奨します。温度スロープは、約-1.52mV/ $^{\circ}$ Cです。

図14. TEMPピンの回路図

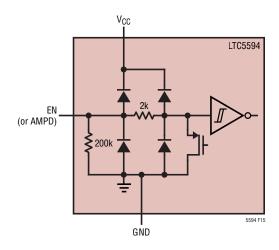

### イネーブル・インタフェース

ENピンの簡略回路図を図15に示します。LTC5594をオンするのに必要なイネーブル電圧は0.7・OVDDです。デバイスをディスエーブルまたはオフするには、この電圧を0.3・OVDDより低くします。ENピンが接続されていないと、デバイスはディスエーブルされます。このピンがフロート状態のままの場合、内部の200kΩプルダウン抵抗により、デバイスはシャットダウン・モードに維持されます。レジスタ0x16に0x00を書き込むことにより、LTC5594はシリアル・インタフェースを介して低電流のスリープ・モードにすることができます。これにより、復調器、アンプ、DCオフセット、および非直線性調整回路がディスエーブルされます。これらはEDEM、EAMP、EDC、およびEADJビッ

図 15. EN(または AMPD) ピンのインタフェースの 簡略回路図

トで制御します。あるいは、レジスタ0x16の4つのMSBに任意の組み合わせビットを書き込むと、個々の回路ブロックをイネーブルまたはディスエーブルすることができます。

#### AMPD インタフェース

図15には、AMPD IFアンプのディスエーブル・ピンの簡略回路図も示されています。 AMPD とEAMPレジスタの論理積が1の場合、IFアンプはイネーブルされます。 IFアンプの状態を表8に詳細に示します。

表 8. IF アンプの状態とロジック・レベル

| EAMP | AMPDピン |      |  |  |  |

|------|--------|------|--|--|--|

| レジスタ | 0      | 1    |  |  |  |

| 0    | OFF:   | OFF: |  |  |  |

| 1.   | ON     | OFF: |  |  |  |

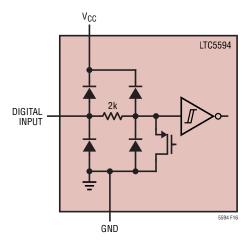

#### デジタル入力ピン

図16に、デジタル入力ピン(SCK、CSB、およびSDI)の簡略 回路図を示します。これらのピンは、内部プルダウンまたはプ ルアップがないため、フロート状態のままにしないでください。

図16. デジタル入力ピン(SCK、CSB、SDI)の 簡略回路図

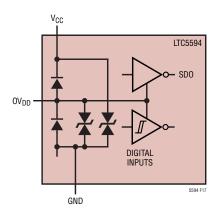

### OVDDインタフェース

図17に、 $OV_{DD}$ インタフェースの簡略回路図を示します。 $OV_{DD}$ ピンは、デジタル入力およびSDOピンに電圧を供給します。このピンを $1.2V \sim 3.3V$ に設定することによって、シリアル・ポートは $1.2V \sim 3.3V$ のロジック・レベルで機能することができます。デバイスの電源電圧をシーケンス制御する場合は、 $V_{CC}$ 電源を先に起動してから $OV_{DD}$ を起動することが重要で

す。これは、 $OV_{DD}$ と $V_{CC}$ の間に接続されたESDダイオードが損傷するのを防ぐためです。

図17. 0VDDピンのインタフェースの簡略回路図

### シリアル・ポート

SPI互換のシリアル・ポートは、制御およびモニタ機能を備えています。

#### 通信シーケンス

シリアル・バスは、CSB、SCK、SDI、およびSDOで構成されています。デバイスへのデータ転送は、シリアル・バスのマスタ・デバイスが最初にCSBを"L"にしてLTC5594のポートをイネーブルすることにより行われます。SDIに与えられた入力データはSCKの立ち上がりエッジでクロックされます。データは常にMSBを先頭にして転送されます。通信バーストは、シリアル・バスのマスタがCSBを"H"に戻すと終了します。詳細は、タイミング図を参照してください。

データは、通信バーストの間にSDOを使ってデバイスから読み出されます。CSB = 1のとき、SDOは高インピーダンス(Hi-Z)になるので、読み出しをマルチドロップにする(シリアル・バスに複数のLTC5594またはその他のシリアル・デバイスを並列に接続する)ことができます。

### 1バイトの転送

シリアル・ポートは簡単なメモリ・マップとして構成されており、付録に示されているように、23個のレジスタで、状態と制御のデータを利用できます。全てのデータ・バーストは少なくとも2つの8ビット・バイトで構成されます。最初のバイトの最上位ビットは、読み出し/書き込みビットです。このビットを1に設定すると、シリアル・ポートが読み出しモードになります。最初のバイトの次の7ビットはアドレス・ビットであり、0x00~0x17に設定できます。それに続く1バイト、または複数バイトは、指定

されたアドレスからのデータ、または指定されたアドレスへの データです。詳細は、タイミング図を参照してください。なお、 書き込まれたデータは、16番目のクロック・サイクルの立ち下 がりエッジで内部レジスタに転送されます(並列読み込み)。

#### 複数バイトの転送

LTC5594のレジスタ・アドレス自動インクリメント機能を使用すれば、タイミング図に示すように、複数バイトのデータ転送をより効率的に行うことができます。シリアル・ポート・マスタは、1番目のバイトで宛先レジスタ・アドレスを送信し、前と同様に2番目のバイトのデータを読み出すか、書き込みますが、3番目のバイトでは、アドレス・ポインタが自動的に1だけインクリメントされ、シリアル・ポート・マスタはその後のレジスタに対して読み出すか、書き込むことができます。レジスタ・アドレス・ポインタが23(0x17)を過ぎてインクリメントしようとすると、自動的に0にリセットされます。

### SDO MODE制御ビット

SDO出力には、タイミング図に示すように2つの動作モードがあります。レジスタ0x16の制御ビットSDO\_MODEが0である場合、SDOピンは通常の出力として機能し、書き込みコマンドの間は高インピーダンスになります。SDO\_MODEが1である場合、SDO出力は、読み出しモードまたは書き込みモードのいずれかでレジスタの内容を読み出す前に、SDOがSDIへのコマンド書き込みを繰り返すシリアル・リピータ・モードになります。これは、シリアル・ポートに送信されたコマンドに対してエラー検査を実行する必要のある、バス・ノイズの高い環境で使用できます。

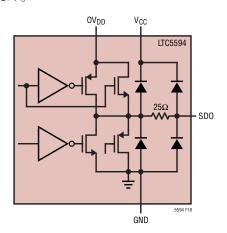

SDO出力の簡略回路図を図 18 に示します。 $OV_{DD}$  電源は出力のロジック・レベルを設定し、 $25\Omega$ の直列抵抗は出力電流を制限します。

図18. SDOピンのインタフェースの簡略回路図

#### レジスタのデフォルト値

レジスタ・マップおよびデフォルト値を付録の表9および10に示します。デバイスの電源が投入されるときに、レジスタをデフォルト値にリセットすることはできません。レジスタ0x16のSRSTビット(ビット[3])に1を書き込むことによって、デバイスはソフト・リセットに移行し、レジスタがそれらのデフォルト値にリセットされます。

#### 機能低下の最小化

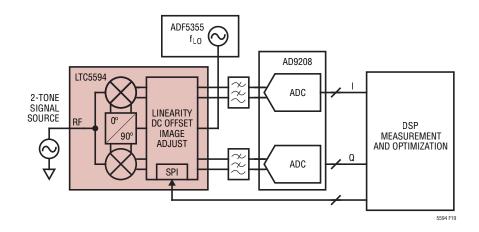

LTC5594は、DCオフセット、位相誤差、利得誤差、非直線性などのレシーバの機能低下を最小限に抑えるための回路を内蔵しています。レシーバ・アプリケーションのブロック図の例を図19に示します。RF入力に2トーンの源信号を入力し、デジタル領域でA/DコンバータのI出力とQ出力を測定して、機能の低下が最小限で済むようにLTC5594での最適化レジスタ設定値を決定します。

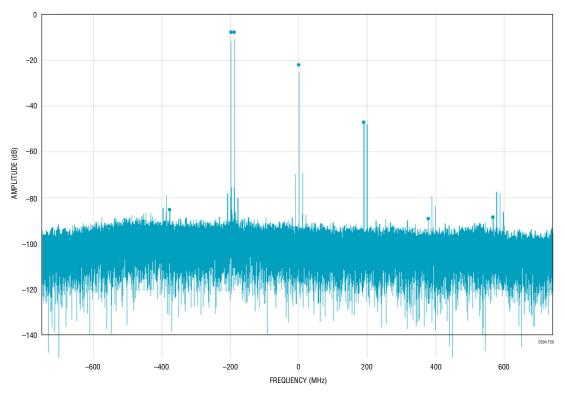

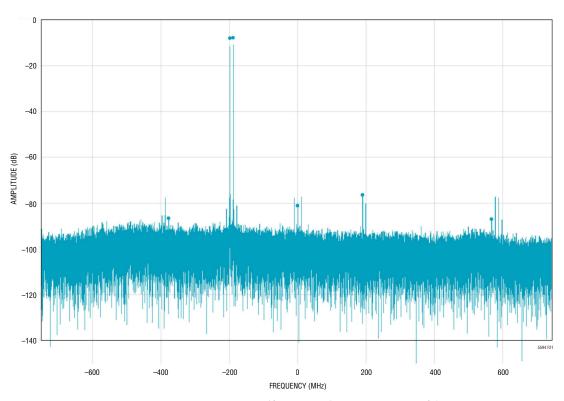

5.8GHzの2トーン・テスト信号について、最適化されていないベースバンド・スペクトラムを図20に示し、最適化されたベースバンド・スペクトラムを図21に示します。

図19. 機能の低下を最小限に抑えるため2トーンのテスト信号を入力したレシーバのブロック図の例

図20. 1GHzのアンチエイリアス・フィルタを使用した場合の5.8GHzでの非最適化2トーン・スペクトラム

図21. 1GHzのアンチエイリアス・フィルタを使用した場合の5.8GHzでの最適化2トーン・スペクトラム

# 付録

表9.シリアル・ポート・レジスタの内容

| ADDR | MSB       | [6]       | [5]      | [4]      | [3]      | [2]      | [1]      | LSB      | R/W | デフォルト |

|------|-----------|-----------|----------|----------|----------|----------|----------|----------|-----|-------|

| 0x00 | IM3QY[7]  | IM3QY[6]  | IM3QY[5] | IM3QY[4] | IM3QY[3] | IM3QY[2] | IM3QY[1] | IM3QY[0] | R/W | 0x80  |

| 0x01 | IM3QX[7]  | IM3QX[6]  | IM3QX[5] | IM3QX[4] | IM3QX[3] | IM3QX[2] | IM3QX[1] | IM3QX[0] | R/W | 0x80  |

| 0x02 | IM3IY[7]  | IM3IY[6]  | IM3IY[5] | IM3IY[4] | IM3IY[3] | IM3IY[2] | IM3IY[1] | IM3IY[0] | R/W | 0x80  |

| 0x03 | IM3IX[7]  | IM3IX[6]  | IM3IX[5] | IM3IX[4] | IM3IX[3] | IM3IX[2] | IM3IX[1] | IM3IX[0] | R/W | 0x80  |

| 0x04 | IM2QX[7]  | IM2QX[6]  | IM2QX[5] | IM2QX[4] | IM2QX[3] | IM2QX[2] | IM2QX[1] | IM2QX[0] | R/W | 0x80  |

| 0x05 | IM2IX[7]  | IM2IX[6]  | IM2IX[5] | IM2IX[4] | IM2IX[3] | IM2IX[2] | IM2IX[1] | IM2IX[0] | R/W | 0x80  |

| 0x06 | HD3QY[7]  | HD3QY[6]  | HD3QY[5] | HD3QY[4] | HD3QY[3] | HD3QY[2] | HD3QY[1] | HD3QY[0] | R/W | 0x80  |

| 0x07 | HD3QX[7]  | HD3QX[6]  | HD3QX[5] | HD3QX[4] | HD3QX[3] | HD3QX[2] | HD3QX[1] | HD3QX[0] | R/W | 0x80  |

| 0x08 | HD3IY[7]  | HD3IY[6]  | HD3IY[5] | HD3IY[4] | HD3IY[3] | HD3IY[2] | HD3IY[1] | HD3IY[0] | R/W | 0x80  |

| 0x09 | HD3IX[7]  | HD3IX[6]  | HD3IX[5] | HD3IX[4] | HD3IX[3] | HD3IX[2] | HD3IX[1] | HD3IX[0] | R/W | 0x80  |

| 0x0A | HD2QY[7]  | HD2QY[6]  | HD2QY[5] | HD2QY[4] | HD2QY[3] | HD2QY[2] | HD2QY[1] | HD2QY[0] | R/W | 0x80  |

| 0x0B | HD2QX[7]  | HD2QX[6]  | HD2QX[5] | HD2QX[4] | HD2QX[3] | HD2QX[2] | HD2QX[1] | HD2QX[0] | R/W | 0x80  |

| 0x0C | HD2IY[7]  | HD2IY[6]  | HD2IY[5] | HD2IY[4] | HD2IY[3] | HD2IY[2] | HD2IY[1] | HD2IY[0] | R/W | 0x80  |

| 0x0D | HD2IX[7]  | HD2IX[6]  | HD2IX[5] | HD2IX[4] | HD2IX[3] | HD2IX[2] | HD2IX[1] | HD2IX[0] | R/W | 0x80  |

| 0x0E | DCOI[7]   | DC01[6]   | DC01[5]  | DCOI[4]  | DC01[3]  | DCOI[2]  | DCOI[1]  | DC01[0]  | R/W | 0x80  |

| 0x0F | DCOQ[7]   | DCOQ[6]   | DCOQ[5]  | DCOQ[4]  | DCOQ[3]  | DCOQ[2]  | DCOQ[1]  | DCOQ[0]  | R/W | 0x80  |

| 0x10 | 0*        | 0*        | 0*       | 0*       | 0*       | IP3IC[2] | IP3IC[1] | IP3IC[0] | R/W | 0x04  |

| 0x11 | GERR[5]   | GERR[4]   | GERR[3]  | GERR[2]  | GERR[1]  | GERR[0]  | IP3CC[1] | IP3CC[0] | R/W | 0x82  |

| 0x12 | LVCM[2]   | LVCM[1]   | LVCM[0]  | CF1[4]   | CF1[3]   | CF1[2]   | CF1[1]   | CF1[0]   | R/W | 0x48  |

| 0x13 | BAND      | LF1[1]    | LF1[0]   | CF2[4]   | CF2[3]   | CF2[2]   | CF2[1]   | CF2[0]   | R/W | 0xE3  |

| 0x14 | PHA[8]    | PHA[7]    | PHA[6]   | PHA[5]   | PHA[4]   | PHA[3]   | PHA[2]   | PHA[1]   | R/W | 0x80  |

| 0x15 | PHA[0]    | AMPG[2]   | AMPG[1]  | AMPG[0]  | AMPCC[1] | AMPCC[0] | AMPIC[1] | AMPIC[0] | R/W | 0x6A  |

| 0x16 | EDEM      | EDC       | EADJ     | EAMP     | SRST     | SDO_MODE | 0*       | 0*       | R/W | 0xF0  |

| 0x17 | CHIPID[1] | CHIPID[0] | 0*       | 0*       | 0*       | 0*       | 0*       | 1*       | R/W | 0x01  |

<sup>\*</sup>未使用。デフォルト値を変更しないでください。

# 付録

## 表 10. シリアル・ポート・レジスタのビット・フィールドのまとめ

| ビット数       | 機能                         | 概要                                                     | 有効な値           | デフォルト |

|------------|----------------------------|--------------------------------------------------------|----------------|-------|

| AMPCC[1:0] | IF Amplifier IM3 CC Adjust | IFアンプのIM3を最適化するために使用される。                               | 0x00 to 0x03   | 0x02  |

| AMPIC[1:0] | IF Amplifier IM3 IC Adjust | IFアンプのIM3を最適化するために使用される。                               | 0x00 to 0x03   | 0x02  |

| AMPG[2:0]  | IF Amplifier Gain Adjust   | アンプの利得を8dB~15dBの範囲で調整する。                               | 0x00 to 0x07   | 0x06  |

| BAND       | LO Band Select             | 使用するLO整合帯域を選択する。高周波帯域では BAND = 1。<br>低周波帯域では BAND = 0。 | 0, 1           | 1     |

| CF1[5:0]   | LO Matching Capacitor CF1  | LO整合回路網内のCF1コンデンサを制御する。                                | 0x00 to 0x1F   | 0x08  |

| CF2[5:0]   | LO Matching Capacitor CF2  | LO整合回路網内のCF2コンデンサを制御する。                                | 0x00 to 0x1F   | 0x03  |

| CHIPID     | Chip Identification Bits   | 出荷時にデフォルト値に設定される。                                      | 0x00 to 0x03   | 0x00  |

| DC0I[7:0]  | I-Channel DC Offset        | -200mV~200mVの範囲でIチャネルのDCオフセットを制御する。                    | 0x00 to 0xFF   | 0x80  |

| DCOQ[7:0]  | Q-Channel DC Offset        | -200mV~200mVの範囲でQチャネルのDCオフセットを制御する。                    | 0x00 to 0xFF   | 0x80  |

| EADJ       | Enable Nonlinearity Adjust | EADJ = 1の場合は非直線性調整回路をイネーブルする。                          | 0, 1           | 1     |

| EAMP       | Enable IF Amplifiers       | EAMP = 1 の場合はIFアンプをイネーブルする。                            | 0, 1           | 1     |

| EDC        | Enable DC Offset Adjust    | EDC = 1の場合はDCオフセット調整回路をイネーブルする。                        | 0, 1           | 1     |

| EDEM       | Enable Demodulator         | EDEM = 1 の場合は復調器回路をイネーブルする。                            | 0, 1           | 1     |

| GERR[5:0]  | IQ Gain Error Adjust       | -0.5dB~0.5dBの範囲でIQの利得誤差を制御する。                          | 0x00 ~ 0x3F    | 0x20  |

| HD2IX[7:0] | HD2 I-Channel X-Vector     | EADJ = 1 の場合に、I チャネルの HD2 X ベクトル調整を制御する。               | 0x00 to 0xFF   | 0x80  |

| HD2IY[7:0] | HD2 I-Channel Y-Vector     | EADJ = 1 の場合に、I チャネルの HD2 Y ベクトル調整を制御する。               | 0x00 to 0xFF   | 0x80  |

| HD2QX[7:0] | HD2 Q-Channel X-Vector     | EADJ = 1の場合に、QチャネルのHD2 Xベクトル調整を制御する。                   | 0x00 to 0xFF   | 0x80  |

| HD2QY[7:0] | HD2 Q-Channel Y-Vector     | EADJ = 1の場合に、QチャネルのHD2 Yベクトル調整を制御する。                   | 0x00 to 0xFF   | 0x80  |

| HD3IX[7:0] | HD3 I-Channel X-Vector     | EADJ = 1 の場合に、I チャネルの HD3 X ベクトル調整を制御する。               | 0x00 to 0xFF   | 0x80  |

| HD3IY[7:0] | HD3 I-Channel Y-Vector     | EADJ = 1 の場合に、I チャネルの HD3 Y ベクトル調整を制御する。               | 0x00 to 0xFF   | 0x80  |

| HD3QX[7:0] | HD3 Q-Channel X-Vector     | EADJ = 1 の場合に、QチャネルのHD3 Xベクトル調整を制御する。                  | 0x00 to 0xFF   | 0x80  |

| HD3QY[7:0] | HD3 Q-Channel Y-Vector     | EADJ = 1 の場合に、QチャネルのHD3 Yベクトル調整を制御する。                  | 0x00 to 0xFF   | 0x80  |

| IM2IX[7:0] | IM2 I-Channel X-Vector     | EADJ = 1 の場合に、I チャネルの IM2 X ベクトル調整を制御する。               | 0x00 to 0xFF   | 0x80  |

| IM2QX[7:0] | IM2 Q-Channel X-Vector     | EADJ = 1 の場合に、Q チャネルの IM2 X ベクトル調整を制御する。               | 0x00 to 0xFF   | 0x80  |

| IM3IX[7:0] | IM3 I-Channel X-Vector     | EADJ = 1 の場合に、I チャネルの IM3 X ベクトル調整を制御する。               | 0x00 to 0xFF   | 0x80  |

| IM3IY[7:0] | IM3 I-Channel Y-Vector     | EADJ = 1 の場合に、I チャネルの IM3 Y ベクトル調整を制御する。               | 0x00 to 0xFF   | 0x80  |

| IM3QX[7:0] | IM3 Q-Channel X-Vector     | EADJ = 1 の場合に、Qチャネルの IM3 Xベクトル調整を制御する。                 | 0x00 to 0xFF   | 0x80  |

| IM3QY[7:0] | IM3 Q-Channel Y-Vector     | EADJ = 1 の場合に、Q チャネルの IM3 Y ベクトル調整を制御する。               | 0x00 to 0xFF   | 0x80  |

| IP3CC[1:0] | RF Input IP3 CC Adjust     | RF入力のIP3の最適化に使用される。                                    | 0x00 to 0x03   | 0x02  |

| IP3IC[2:0] | RF Input IP3 IC Adjust     | RF入力のIP3の最適化に使用される。                                    | 0x00 to 0x07   | 0x04  |

| LF1[1:0]   | LO Matching Inductor LF1   | LO整合回路網内のLF1インダクタを制御する。                                | 0x00 to 0x03   | 0x03  |

| LVCM[2:0]  | LO Bias Adjust             | ミキサのIP3の最適化に使用される。                                     | 0x00 to 0x07   | 0x02  |

| PHA[8:0]   | IQ Phase Error Adjust      | -2.5°~2.5°の範囲でIQの位相誤差を制御する。                            | 0x000 to 0x1FF | 0x100 |

| SDO_MODE   | SDO Readback Mode          | SDO_MODE = 1 の場合にSDO読み出しモードをイネーブルする。                   | 0, 1           | 0     |

| SRST       | Soft Reset                 | このビットに1を書き込むと、全てのレジスタがデフォルト値に<br>リセットされる。              | 0, 1           | 0     |

詳細: www.linear-tech.co.jp/LTC5594

### パッケージ

最新のパッケージ図は、http://www.linear-tech.co.jp/product/LTC5594#packaging を参照してください。

### **UH Package** 32-Lead Plastic QFN (5mm × 5mm)

(Reference LTC DWG # 05-08-1693 Rev D)

RECOMMENDED SOLDER PAD LAYOUT APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

#### 注記:

- 1. 図は JEDEC のパッケージ外形 MO-220 のバリエーション(WHHD-(X))に 含めるよう提案されている(承認待ち)

- 2. 図は実寸とは異なる

- モールドのバリは(もしあれば)各サイドで 0.20mm を超えないこと

- 5. 露出パッドは半田メッキとする

- 6. 灰色の部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

# 標準的応用例

### 0.5GHz~9.0GHzレシーバの簡略回路図(Iチャネルのみ示されている)

# 関連製品

| 製品番号       | 概要                                               | 注釈                                                                                              |  |  |  |  |

|------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| インフラスト     | ラクチャ                                             |                                                                                                 |  |  |  |  |

| LTC5553    | 500MHz~9GHzのIFポートを備えた3GHz~20GHz<br>マイクロ波ミキサ      | アップコンバージョンまたはダウンコンバージョン、IIP3:17GHzで21.5dBm、LO駆動:0dBm                                            |  |  |  |  |

| LTC5552    | DC~6GHzのIFポートを備えた3GHz~20GHz<br>マイクロ波ミキサ          | アップコンバージョンまたはダウンコンバージョン、IIP3:17GHzで<br>18.3dBm、LO駆動:0dBm                                        |  |  |  |  |

| LTC5549    | LOダブラが内蔵された2GHz~14GHzミキサ                         | 超広帯域双方向アップコンバージョンまたはダウンコンバージョン・ミ<br>キサ、12GHzでのIIP3:22.8dBm、LO駆動:0dBm、<br>IF帯域幅:500MHz~6GHz      |  |  |  |  |

| LTC5548    | DCまでの範囲のIF周波数を備える2GHz~14GHz<br>ミキサ               | 超広帯域双方向アップコンバージョンまたはダウンコンバージョン・<br>ミキサ、12GHzでのIIP3:18.7dBm、周波数ダブラ内蔵のLO駆動:<br>0dBm、IF帯域幅:DC~6GHz |  |  |  |  |

| LTC5588-1  | 200MHz~6GHz直交変調器                                 | OIP3:+31dBm、出力ノイズフロア:-160dBm/Hz、優れたACPR性能                                                       |  |  |  |  |

| LTC6433-15 | 100kHz未満~1.4GHzの高OIP3アンプ                         | 固定利得:15dB、シングルエンドの50Ω入力および出力、<br>240MHzでのOIP3:41dBm、NF:3.3dB                                    |  |  |  |  |

| VCO内蔵のR    | F PLL/シンセサイザ                                     |                                                                                                 |  |  |  |  |

| ADF5355    | マイクロ波広帯域シンセサイザ、VCO内蔵                             | 54MHz~13.6GHz、正規化された帯域内位相ノイズフロア:<br>-221dBc/Hz                                                  |  |  |  |  |

| LTC6948    | ノイズをきわめて低く抑えたVCO内蔵の分数分周方式<br>シンセサイザ              | 370MHz~6.39GHz PLL、 $\Delta\Sigma$ 変調器のスプリアスなし、分数の分母: 18ビット、正規化された帯域内位相/イズフロア: $-226$ dBc/Hz    |  |  |  |  |

| A/D コンバー   | হ                                                |                                                                                                 |  |  |  |  |

| AD9208     | 14ビット、3Gsps、JESD204B デュアル ADC                    | SFDR:70dB、入力バッファ内蔵                                                                              |  |  |  |  |

| LTC2185    | 16ビット、125Msps、1.8V デュアル ADC                      | SNR:76.8dB、SFDR:90dB、消費電力:185mW(チャネル当たり)                                                        |  |  |  |  |

| LTC2158-14 | フルパワー帯域幅が1.25GHzの14ビット、310Msps、<br>1.8V デュアル ADC | SNR:68.8dB、SFDR:88dB、消費電力:362mW/チャネル、入力範囲:<br>1.32V <sub>P-P</sub>                              |  |  |  |  |