## Easy Drive入力電流 キャンセル機能付き 16ビット2/4チャネルΔΣ ADC

### 特長

- 最大2つの差動入力または最大4つのシングルエンド入力

- Easy Driveテクノロジーにより、差動入力電流がゼロの レール・トゥ・レール入力が可能

- 全精度で高インピーダンス・センサを直接デジタル化

- 600nV RMSのノイズ (0.02LSBの遷移ノイズ)

- GND~Vccの入力/リファレンス同相範囲

- 50Hz/60Hzの同時除去

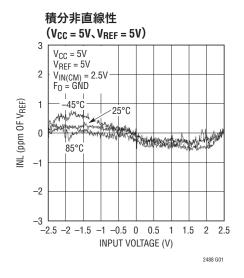

- INL:2ppm、ミッシング・コードなし

- オフセット:1ppm、フルスケール誤差:15ppm

- 待ち時間なし: 新しいチャネル選択後でも デジタル・フィルタが1サイクル内にセトリング

- 2.7V~5.5V単一電源動作(0.8mW)

- 内部発振器

- 小型4mm×3mmのDFNパッケージ

### アプリケーション

- ダイレクト・センサ・デジタイザ

- 直接温度測定

- 計測

- 産業用プロセス制御

### 概要

LTC<sup>®</sup>2488は、Easy Drive<sup>™</sup>テクノロジーを使った、4チャネル(2チャネル差動)、16ビット、No Latency  $\Delta\Sigma^{™}$  ADCです。特許取得のサンプリング回路は、差動入力電流の自動キャンセルにより、ダイナミック入力電流誤差や内部バッファの弱点を除去します。このため、並外れたDC精度を維持しながら、大きな外部ソース・インピーダンスやレール・トゥ・レールの入力信号を直接デジタル化することができます。

LTC2488には発振器が内蔵されています。このデバイスはシングルエンド・モードまたは差動モードで動作する4本のアナログ入力チャネルの組合せから外部信号を測定するように構成することができます。50Hzと60Hzのライン周波数を同時に自動的に除去します。

LTC2488は、リファレンス電圧と関係なく、広い同相入力電圧 範囲(0V~V<sub>CC</sub>)が可能です。シングルエンド入力または差動 入力の任意の組合せを選択することができ、新しいチャネル を選択した後の最初の変換が有効です。

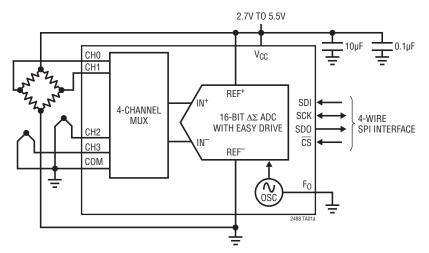

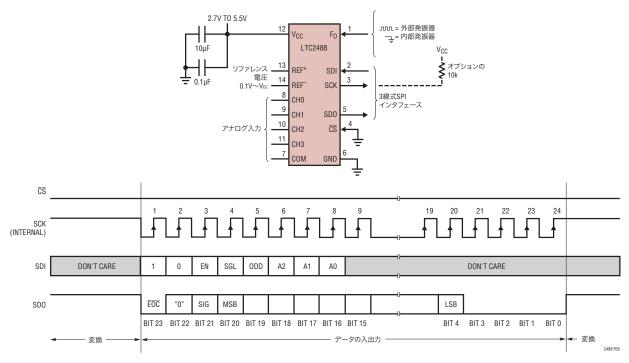

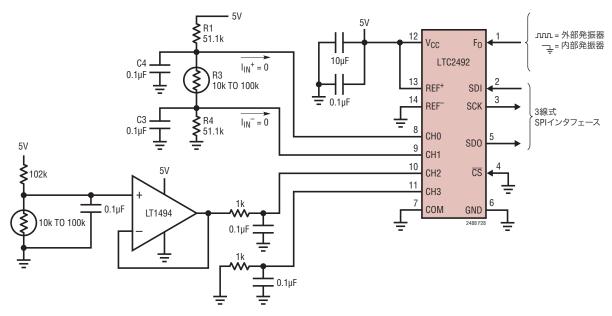

### 標準的応用例

#### データ収集システム

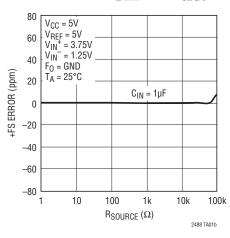

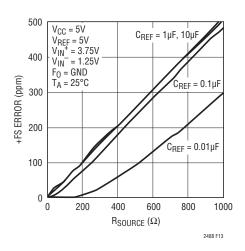

### フルスケール誤差とソース抵抗

# 絶対最大定格

(Note 1,2)

| 電源電圧(V <sub>CC</sub> )             | 0.3V~6V                             |

|------------------------------------|-------------------------------------|

| アナログ入力電圧                           |                                     |

| (CH0~CH3、COM)                      | 0.3V $\sim$ (V <sub>CC</sub> +0.3V) |

| REF <sup>+</sup> 、REF <sup>-</sup> | 0.3V $\sim$ (V <sub>CC</sub> +0.3V) |

| デジタル入力電圧                           | 0.3V $\sim$ (V <sub>CC</sub> +0.3V) |

| デジタル出力電圧                           | 0.3V $\sim$ (V <sub>CC</sub> +0.3V) |

| 動作温度範囲                             |                                     |

| LTC2488C                           | 0°C∼70°C                            |

| LTC24881                           | −40°C~85°C                          |

| 保存温度範囲                             | 65°C~150°C                          |

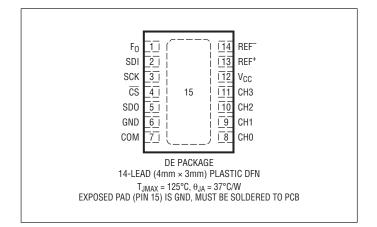

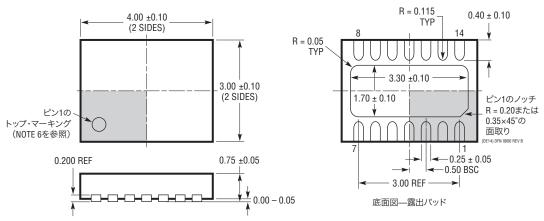

## ピン配置

## 発注情報

| 鉛フリー仕様         | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲          |

|----------------|------------------|----------|---------------------------------|---------------|

| LTC2488CDE#PBF | LTC2488CDE#TRPBF | 2488     | 14-Lead (4mm × 3mm) Plastic DFN | 0°C to 70°C   |

| LTC2488IDE#PBF | LTC2488IDE#TRPBF | 2488     | 14-Lead (4mm × 3mm) Plastic DFN | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。 非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、http://www.linear-tech.co.jp/leadfree/をご覧ください。テープアンドリールの仕様の詳細については、http://www.linear-tech.co.jp/tapeandree/をご覧ください。

### 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外はTA = 25°Cでの値。(Note 3、4)

| PARAMETER                       | CONDITIONS                                                                                                                                                                                                                       |   | MIN | TYP            | MAX | UNITS                                                                         |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----------------|-----|-------------------------------------------------------------------------------|

| Resolution (No Missing Codes)   | $0.1V \le V_{REF} \le V_{CC}$ , $-FS \le V_{IN} \le +FS$ (Note 5)                                                                                                                                                                |   | 16  |                |     | Bits                                                                          |

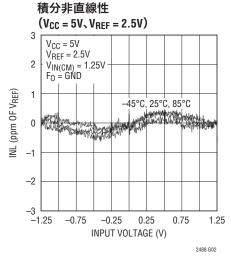

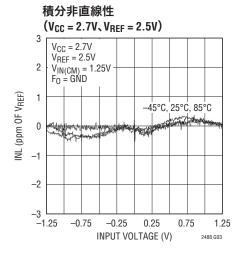

| Integral Nonlinearity           | $5V \le V_{CC} \le 5.5V$ , $V_{REF} = 5V$ , $V_{IN(CM)} = 2.5V$ (Note 6) $2.7V \le V_{CC} \le 5.5V$ , $V_{REF} = 2.5V$ , $V_{IN(CM)} = 1.25V$ (Note 6)                                                                           | • |     | 2<br>1         | 20  | ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub>                            |

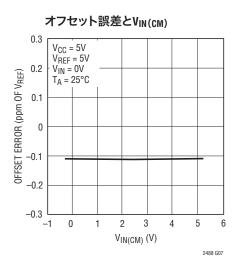

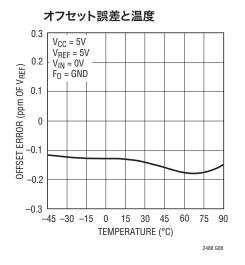

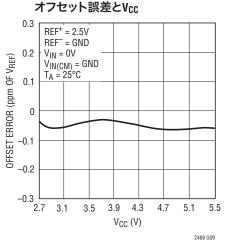

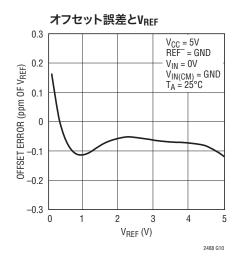

| Offset Error                    | $2.5V \le V_{REF} \le V_{CC}$ , $GND \le IN^+ = IN^- \le V_{CC}$ (Note 14)                                                                                                                                                       | • |     | 0.5            | 5   | μV                                                                            |

| Offset Error Drift              | $2.5V \le V_{REF} \le V_{CC}$ , $GND \le IN^+ = IN^- \le V_{CC}$                                                                                                                                                                 |   |     | 10             |     | nV/°C                                                                         |

| Positive Full-Scale Error       | $2.5V \le V_{REF} \le V_{CC}$ , $IN^+ = 0.75V_{REF}$ , $IN^- = 0.25V_{REF}$                                                                                                                                                      | • |     |                | 32  | ppm of V <sub>REF</sub>                                                       |

| Positive Full-Scale Error Drift | $2.5V \le V_{REF} \le V_{CC}$ , $IN^+ = 0.75V_{REF}$ $IN^- = 0.25V_{REF}$                                                                                                                                                        |   |     | 0.1            |     | ppm of V <sub>REF</sub> /°C                                                   |

| Negative Full-Scale Error       | $2.5V \le V_{REF} \le V_{CC}$ , $IN^+ = 0.25V_{REF}$ $IN^- = 0.75V_{REF}$                                                                                                                                                        | • |     |                | 32  | ppm of V <sub>REF</sub>                                                       |

| Negative Full-Scale Error Drift | $2.5V \le V_{REF} \le V_{CC}$ , $IN^+ = 0.25V_{REF}$ $IN^- = 0.75V_{REF}$                                                                                                                                                        |   |     | 0.1            |     | ppm of V <sub>REF</sub> /°C                                                   |

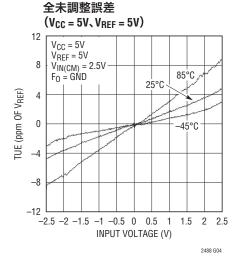

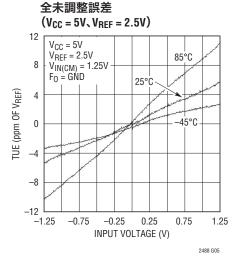

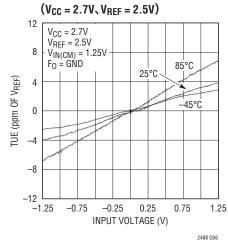

| Total Unadjusted Error          | $\begin{array}{l} 5V \leq V_{CC} \leq 5.5V,  V_{REF} = 2.5V,  V_{IN(CM)} = 1.25V \\ 5V \leq V_{CC} \leq 5.5V,  V_{REF} = 5V,  V_{IN(CM)} = 2.5V \\ 2.7V \leq V_{CC} \leq 5.5V,  V_{REF} = 2.5V,  V_{IN(CM)} = 1.25V \end{array}$ |   |     | 15<br>15<br>15 |     | ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub> |

| Output Noise                    | $2.7V < V_{CC} < 5.5V$ , $2.5V \le V_{REF} \le V_{CC}$ , $GND \le IN^+ = IN^- \le V_{CC}$ (Note 13)                                                                                                                              |   | ·   | 0.6            |     | μV <sub>RMS</sub>                                                             |

## コンバータの特性

### ●は全動作温度範囲の規格値を意味する。それ以外はTA = 25°Cでの値。(Note 3)

| PARAMETER                                 | CONDITIONS                                                                    |   | MIN | TYP | MAX | UNITS |

|-------------------------------------------|-------------------------------------------------------------------------------|---|-----|-----|-----|-------|

| Input Common Mode Rejection DC            | $2.5V \le V_{REF} \le V_{CC}$ , GND $\le IN^+ = IN^- \le V_{CC}$ (Note 5)     | • | 140 |     |     | dB    |

| Input Common Mode Rejection 50Hz ±2%      | $2.5V \le V_{REF} \le V_{CC}$ , GND $\le IN^+ = IN^- \le V_{CC}$ (Note 5)     | • | 140 |     |     | dB    |

| Input Common Mode Rejection 60Hz ±2%      | $2.5V \le V_{REF} \le V_{CC}$ , GND $\le IN^+ = IN^- \le V_{CC}$ (Note 5)     | • | 140 |     |     | dB    |

| Input Normal Mode Rejection 50Hz ±2%      | $2.5V \le V_{REF} \le V_{CC}$ , GND $\le IN^+ = IN^- \le V_{CC}$ (Notes 5, 7) | • | 110 | 120 |     | dB    |

| Input Normal Mode Rejection 60Hz ±2%      | $2.5V \le V_{REF} \le V_{CC}$ , GND $\le IN^+ = IN^- \le V_{CC}$ (Notes 5, 8) | • | 110 | 120 |     | dB    |

| Input Normal Mode Rejection 50Hz/60Hz ±2% | $2.5V \le V_{REF} \le V_{CC}$ , GND $\le IN^+ = IN^- \le V_{CC}$ (Notes 5, 9) | • | 87  |     |     | dB    |

| Reference Common Mode Rejection DC        | $2.5V \le V_{REF} \le V_{CC}$ , GND $\le IN^+ = IN^- \le V_{CC}$ (Note 5)     | • | 120 | 140 |     | dB    |

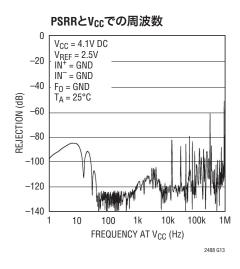

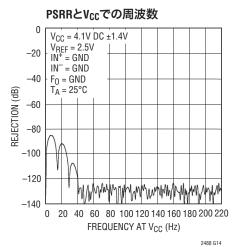

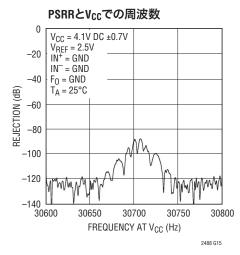

| Power Supply Rejection DC                 | $V_{REF} = 2.5V, IN^{+} = IN^{-} = GND$                                       |   |     | 120 |     | dB    |

| Power Supply Rejection, 50Hz ±2%          | $V_{REF} = 2.5V$ , $IN^+ = IN^- = GND$ (Notes 7, 9)                           |   |     | 120 |     | dB    |

| Power Supply Rejection, 60Hz ±2%          | $V_{REF} = 2.5V$ , $IN^+ = IN^- = GND$ (Notes 8, 9)                           |   |     | 120 |     | dB    |

## アナログ入力とリファレンス

### ●は全動作温度範囲の規格値を意味する。それ以外はTA = 25°Cでの値。(Note 3)

| SYMBOL                                 | PARAMETER                                                                                                         | CONDITIONS                         |   | MIN                 | TYP | MAX                    | UNITS |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------|---|---------------------|-----|------------------------|-------|

| IN+                                    | Absolute/Common Mode IN <sup>+</sup> Voltage (IN <sup>+</sup> Corresponds to the Selected Positive Input Channel) |                                    |   | GND - 0.3V          |     | V <sub>CC</sub> + 0.3V | V     |

| IN <sup>-</sup>                        | Absolute/Common Mode IN <sup>-</sup> Voltage (IN <sup>-</sup> Corresponds to the Selected Negative Input Channel) |                                    |   | GND - 0.3V          |     | V <sub>CC</sub> + 0.3V | V     |

| V <sub>IN</sub>                        | Input Differential Voltage Range (IN+ – IN-)                                                                      |                                    | • | –FS                 |     | +FS                    | V     |

| FS                                     | Full Scale of the Differential Input (IN+ – IN-)                                                                  |                                    | • | 0.5V <sub>REF</sub> |     |                        | V     |

| LSB                                    | Least Significant Bit of the Output Code                                                                          |                                    | • | FS/2 <sup>16</sup>  |     |                        |       |

| REF+                                   | Absolute/Common Mode REF+ Voltage                                                                                 |                                    | • | 0.1                 |     | V <sub>CC</sub>        | V     |

| REF-                                   | Absolute/Common Mode REF <sup>-</sup> Voltage                                                                     |                                    | • | GND                 |     | REF+ - 0.1V            | V     |

| $V_{REF}$                              | Reference Voltage Range (REF+ – REF <sup>-</sup> )                                                                |                                    | • | 0.1                 |     | V <sub>CC</sub>        | V     |

| C <sub>S(IN+)</sub>                    | IN+ Sampling Capacitance                                                                                          |                                    |   |                     | 11  |                        | pF    |

| C <sub>S(IN-)</sub>                    | IN <sup>-</sup> Sampling Capacitance                                                                              |                                    |   |                     | 11  |                        | pF    |

| C <sub>S(VREF)</sub>                   | V <sub>REF</sub> Sampling Capacitance                                                                             |                                    |   |                     | 11  |                        | pF    |

| I <sub>DC_LEAK(IN</sub> <sup>+</sup> ) | IN+ DC Leakage Current                                                                                            | Sleep Mode, IN+ = GND              | • | -10                 | 1   | 10                     | nA    |

| I <sub>DC_LEAK(IN</sub> -)             | IN <sup>-</sup> DC Leakage Current                                                                                | Sleep Mode, IN <sup>-</sup> = GND  | • | -10                 | 1   | 10                     | nA    |

| I <sub>DC_LEAK(REF</sub> +)            | REF+ DC Leakage Current                                                                                           | Sleep Mode, REF+ = V <sub>CC</sub> | • | -100                | 1   | 100                    | nA    |

| I <sub>DC_LEAK(REF</sub> )             | REF <sup>-</sup> DC Leakage Current                                                                               | Sleep Mode, REF <sup>-</sup> = GND | • | -100                | 1   | 100                    | nA    |

| t <sub>OPEN</sub>                      | MUX Break-Before-Make                                                                                             |                                    |   |                     | 50  |                        | ns    |

| QIRR                                   | MUX Off Isolation                                                                                                 | $V_{IN} = 2V_{P-P}$ DC to 1.8MHz   |   |                     | 120 |                        | dB    |

## デジタル入力とデジタル出力

## ●は全動作温度範囲の規格値を意味する。それ以外はTA = 25°Cでの値。(Note 3)

| SYMBOL          | PARAMETER                                                                 | CONDITIONS                                        |   | MIN                   | TYP | MAX | UNITS |

|-----------------|---------------------------------------------------------------------------|---------------------------------------------------|---|-----------------------|-----|-----|-------|

| $V_{IH}$        | High Level Input Voltage ( $\overline{\text{CS}}$ , F <sub>0</sub> , SDI) | $2.7V \le V_{CC} \le 5.5V \text{ (Note 18)}$      | • | V <sub>CC</sub> - 0.5 |     |     | V     |

| $V_{IL}$        | Low Level Input Voltage (CS, F <sub>0</sub> , SDI)                        | $2.7V \le V_{CC} \le 5.5V$                        | • |                       |     | 0.5 | V     |

| V <sub>IH</sub> | High Level Input Voltage (SCK)                                            | $2.7V \le V_{CC} \le 5.5V \text{ (Notes 10, 15)}$ | • | V <sub>CC</sub> - 0.5 |     |     | V     |

| $V_{IL}$        | Low Level Input Voltage (SCK)                                             | $2.7V \le V_{CC} \le 5.5V \text{ (Notes 10, 15)}$ | • |                       |     | 0.5 | V     |

| I <sub>IN</sub> | Digital Input Current (CS, F <sub>0</sub> , SDI)                          | $0V \le V_{IN} \le V_{CC}$                        | • | -10                   |     | 10  | μА    |

| I <sub>IN</sub> | Digital Input Current (SCK)                                               | $0V \le V_{IN} \le V_{CC}$ (Notes 10, 15)         | • | -10                   |     | 10  | μА    |

| C <sub>IN</sub> | Digital Input Capacitance (CS, F <sub>0</sub> , SDI)                      |                                                   |   |                       | 10  |     | pF    |

| C <sub>IN</sub> | Digital Input Capacitance (SCK)                                           | (Notes 10, 15)                                    |   |                       | 10  |     | pF    |

| V <sub>OH</sub> | High Level Output Voltage (SDO)                                           | $I_0 = -800 \mu A$                                | • | $V_{CC} - 0.5$        |     |     | V     |

| $V_{OL}$        | Low Level Output Voltage (SDO)                                            | I <sub>0</sub> = 1.6mA                            | • |                       |     | 0.4 | V     |

| $V_{OH}$        | High Level Output Voltage (SCK)                                           | $I_0 = -800\mu A \text{ (Notes 10, 17)}$          | • | V <sub>CC</sub> - 0.5 |     |     | V     |

| $V_{0L}$        | Low Level Output Voltage (SCK)                                            | I <sub>0</sub> = 1.6mA (Notes 10, 17)             | • |                       |     | 0.4 | V     |

| I <sub>OZ</sub> | Hi-Z Output Leakage (SDO)                                                 |                                                   | • | -10                   |     | 10  | μΑ    |

## 電源要件

### ●は全動作温度範囲の規格値を意味する。それ以外はT<sub>A</sub> = 25℃での値。(Note 3)

| SYMBOL          | PARAMETER      | CONDITIONS                                           |   | MIN | TYP      | MAX      | UNITS    |

|-----------------|----------------|------------------------------------------------------|---|-----|----------|----------|----------|

| $V_{CC}$        | Supply Voltage |                                                      | • | 2.7 |          | 5.5      | V        |

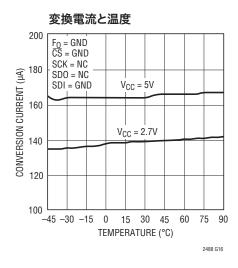

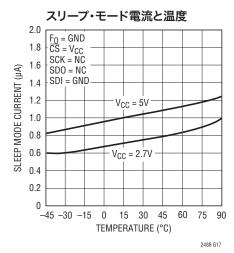

| I <sub>CC</sub> | Supply Current | Conversion Current (Note 12)<br>Sleep Mode (Note 12) | • |     | 160<br>1 | 275<br>2 | μA<br>μA |

## デジタル入力とデジタル出力

#### ●は全動作温度範囲の規格値を意味する。それ以外はTA = 25°Cでの値。(Note 3)

| SYMBOL                 | PARAMETER                            | CONDITIONS                                                                   |   | MIN   | ТҮР                                       | MAX   | UNITS      |

|------------------------|--------------------------------------|------------------------------------------------------------------------------|---|-------|-------------------------------------------|-------|------------|

| f <sub>EOSC</sub>      | External Oscillator Frequency Range  | (Note 16)                                                                    | • | 10    |                                           | 4000  | kHz        |

| t <sub>HEO</sub>       | External Oscillator High Period      |                                                                              | • | 0.125 |                                           | 100   | μs         |

| t <sub>LEO</sub>       | External Oscillator Low Period       |                                                                              | • | 0.125 |                                           | 100   | μs         |

| t <sub>CONV</sub>      | Conversion Time                      | Simultaneous 50Hz/60Hz<br>External Oscillator                                | • | 144.1 | 146.9<br>41036/f <sub>EOSC</sub> (in kHz) | 149.9 | ms<br>ms   |

| f <sub>ISCK</sub>      | Internal SCK Frequency               | Internal Oscillator (Notes 10, 17)<br>External Oscillator (Notes 10, 11, 15) |   |       | 38.4<br>f <sub>EOSC</sub> /8              |       | kHz<br>kHz |

| D <sub>ISCK</sub>      | Internal SCK Duty Cycle              | (Notes 10, 17)                                                               | • | 45    |                                           | 55    | %          |

| f <sub>ESCK</sub>      | External SCK Frequency Range         | (Notes 10, 11, 15)                                                           | • |       |                                           | 4000  | kHz        |

| t <sub>LESCK</sub>     | External SCK Low Period              | (Notes 10, 11, 15)                                                           | • | 125   |                                           |       | ns         |

| t <sub>HESCK</sub>     | External SCK High Period             | (Notes 10, 11, 15)                                                           | • | 125   |                                           |       | ns         |

| t <sub>DOUT_ISCK</sub> | Internal SCK 24-Bit Data Output Time | Internal Oscillator (Notes 10, 17)<br>External Oscillator (Notes 10, 11, 15) | • | 0.61  | 0.625<br>192/f <sub>EOSC</sub> (in kHz)   | 0.64  | ms<br>ms   |

| t <sub>DOUT_ESCK</sub> | External SCK 24-Bit Data Output Time |                                                                              |   |       | 24/f <sub>ESCK</sub> (in kHz)             |       | ms         |

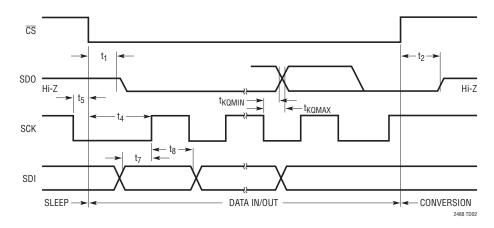

| t <sub>1</sub>         | CS↓ to SD0 Low                       |                                                                              | • | 0     |                                           | 200   | ns         |

| t <sub>2</sub>         | CS↑ to SDO High Z                    |                                                                              | • | 0     |                                           | 200   | ns         |

| $t_3$                  | CS↓ to SCK↓                          | Internal SCK Mode                                                            | • | 0     |                                           | 200   | ns         |

| t <sub>4</sub>         | CS↓ to SCK↑                          | External SCK Mode                                                            | • | 50    |                                           |       | ns         |

| t <sub>KQMAX</sub>     | SCK↓ to SDO Valid                    |                                                                              | • |       |                                           | 200   | ns         |

| t <sub>KQMIN</sub>     | SDO Hold After SCK↓                  | (Note 5)                                                                     | • | 15    |                                           |       | ns         |

| t <sub>5</sub>         | SCK Set-Up Before CS↓                |                                                                              | • | 50    |                                           |       | ns         |

| t <sub>7</sub>         | SDI Setup Before SCK↑                | (Note 5)                                                                     | • | 100   |                                           |       | ns         |

| t <sub>8</sub>         | SDI Hold After SCK↑                  | (Note 5)                                                                     | • | 100   |                                           |       | ns         |

Note 1: 絶対最大定格に記載された値を超すストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

Note 2:すべての電圧値はGNDを基準にしている。

Note 3:注記がない限り:

$V_{CC} = 2.7V \sim 5.5V$

$V_{REFCM} = V_{REF}/2 \, , F_S = 0.5 V_{REF}$

$V_{IN} = IN^{+} - IN^{-}, V_{IN(CM)} = (IN^{+} + IN^{-})/2$

ここで、 $IN^+$ と $IN^-$ は選択された入力チャネルである。

**Note 4:**注記がない限り、内部変換クロックまたは $f_{EOSC}$  = 307.2kHzの外部変換クロック・ソースを使う。

Note 5: 設計によって保証されているが、テストされない。

Note 6: 積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

Note 7:f<sub>EOSC</sub> = 256kHz±2%(外部発振器)。

Note 8: f<sub>EOSC</sub> = 307.2Hz±2%(外部発振器)。

Note 9:同時50Hz/60Hz(内部発振器)またはfeosc = 280kHz±2%(外部発振器)

Note 10: SCKは外部SCKモードまたは内部SCKモードで構成設定することができる。外部SCKモードでは、SCKピンはデジタル入力として使われ、ドライビング・クロックは $f_{\rm ESCK}$ である。内部SCKモードでは、SCKピンはデジタル出力として使われ、データ出力時の出力クロック信号は $f_{\rm ISCK}$ である。

Note 11: 外部発振器は $F_0$ ピンに接続される。外部発振器の周波数 ( $f_{EOSC}$ ) はkHzで表されている。

Note 12:コンバータは内部発振器を使用する。

Note 13: 出力ノイズには内部較正動作によって生じる分が含まれる。 $V_{REF} \le V_{CC}$ 。

Note 14:設計およびテストの相関により保証されている。

Note 15:用されている。データの出力時にSCKをドライブするクロック信号の周波数は $f_{\rm ESCK}$ であり、Hzで表される。

**Note 16:**性能とデータ・レートのグラフについては、「アプリケーション情報」のセクションを参照。

Note 17:コンバータは内部SCKモードで動作しているので、SCKピンはデジタル出力として使用されている。

Note 18: V<sub>CC</sub> < 3Vの場合、f<sub>O</sub>ピンのV<sub>IH</sub>は2.5V。

### 標準的性能特性

全未調整誤差

### 標準的性能特性

### ピン機能

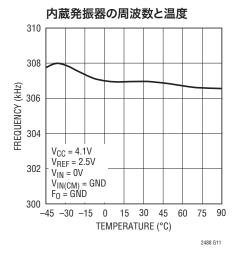

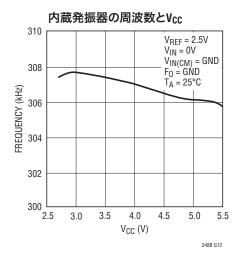

Fo(ピン1):周波数制御ピン。内部変換クロック・レートを制御するデジタル入力。Foがグランドに接続されていると、コンバータは307.2kHzで動作している内部発振器を使います。出力レートとデジタル・フィルタの除去ヌルを変更するため、Foピンを外部クロックでドライブして変換クロックを無効にすることもできます。

**SDI(ピン2)**:シリアル・データ入力。このピンは入力チャネルを 選択するのに使われます。シリアル・データ入力は、データの 入出力動作の間にシリアル・クロック(SCK)で制御されてデバ イスに与えられます。新しい入力後の最初の変換は有効です。

SCK(ピン3): 双方向、デジタルI/O、クロック・ピン。内部シリアル・クロック動作モードでは、SCKは内部で発生し、SCKピンの出力として現れます。外部シリアル・クロック動作モードでは、デジタルI/Oクロックが外部からSCKピンに与えられます。シリアル・クロック動作モードは、電源立上げ時およびでの最新の立下りエッジの間にSCKピンに与えられるロジック・レベルによって決まります。

でS(ピン4):アクティブ"L"のチップ・セレクト。このピンを"L"にすると、デジタル入力/出力がイネーブルされ、ADCが覚醒します。各変換の後、ADCは自動的にスリープ・モードに入り、でSが"H"に留まる限りこの省電力状態に保たれます。データ出力中にでSが"L"から"H"に遷移すると、データ転送が中止され、新しい変換が開始されます。

SDO(ピン5): スリーステートのデジタル出力。データ出力の期間中、このピンはシリアル・データの出力として使われます。チップ・セレクト・ピンが"H"のとき、SDOピンは高インピーダンス状態になります。変換中およびスリープ中、このピンは変換状態の出力として使われます。変換の進行中このピンは"H"になり、変換が完了すると"L"になります。変換状態はCSを"L"に引き下げてモニタします。

**GND(ピン6)**:グランド。このピンを1つの共通グランド・プレーンに低インピーダンスで接続します。

COM(ピン7): すべてのシングルエンド・マルチプレクサ構成の共通負入力 $(IN^-)$ 。 $CH0\sim CH3$ およびCOMの各ピンの電圧は $(GND-0.3V)\sim (V_{CC}+0.3V)$ の任意の値にすることができます。これらのリミット内では、2つの選択された入力 $(IN^+$ と $IN^-)$ により、 $-0.5 \bullet V_{REF}\sim 0.5 \bullet V_{REF}$ のバイポーラの入力範囲 $(V_{IN}=IN^+-IN^-)$ が与えられます。この入力範囲の外側では、コンバータは固有のオーバーレンジとアンダーレンジの出力コードを発生します。

**CH0~CH3(ピン8~11)**:アナログ入力。シングルエンド・モード または差動モードにプログラムすることができます。

**V<sub>CC</sub>(ピン12)**:正電源電圧。10μFのタンタル・コンデンサと 0.1μFのセラミック・コンデンサを並列に使って、デバイスのできるだけ近くでGNDにバイパスします。

REF<sup>+</sup>(ピン13)、REF<sup>-</sup>(ピン14): 差動リファレンス入力。これらのピンの電圧は、リファレンスの正入力(REF<sup>+</sup>)がリファレンスの負入力(REF<sup>-</sup>)より少なくとも0.1Vだけ高く保たれる限り、GND~ $V_{CC}$ の任意の電圧にすることができます。 差動電圧( $V_{REF} = REF^+ - REF^-$ )により、すべての入力チャネルのフルスケール・レンジが設定されます。

**露出パッド(ピン15)**:グランド。このピンはグランドで、PCBのグランド・プレーンに半田付けする必要があります。プロトタイプの作成では、このピンをフロートさせたままでもかまいません。

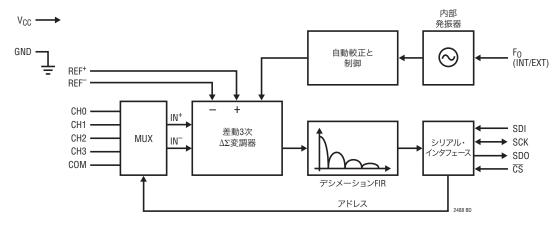

## 機能ブロック図

図1. 機能ブロック図

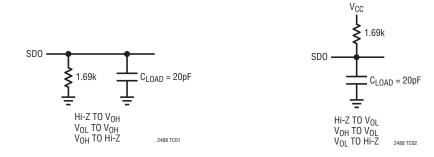

## テスト回路

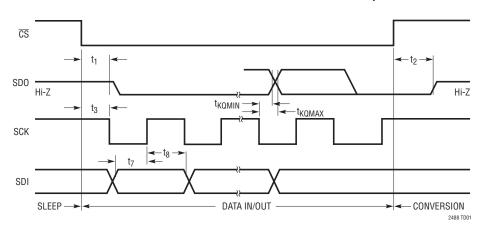

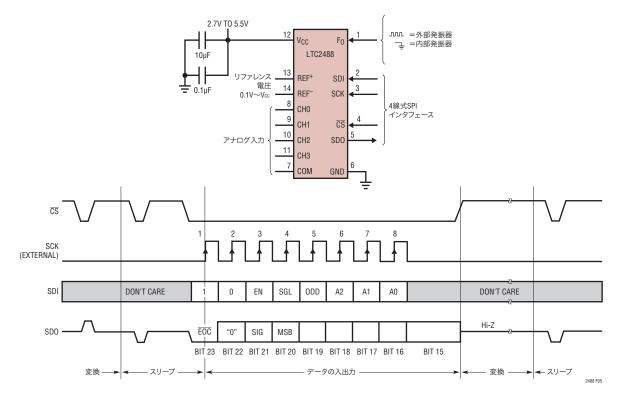

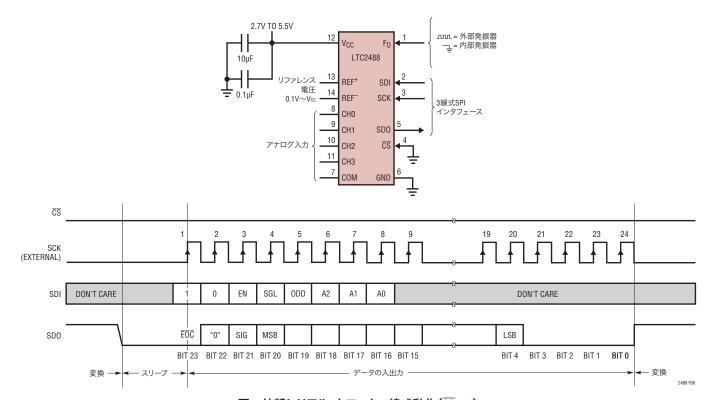

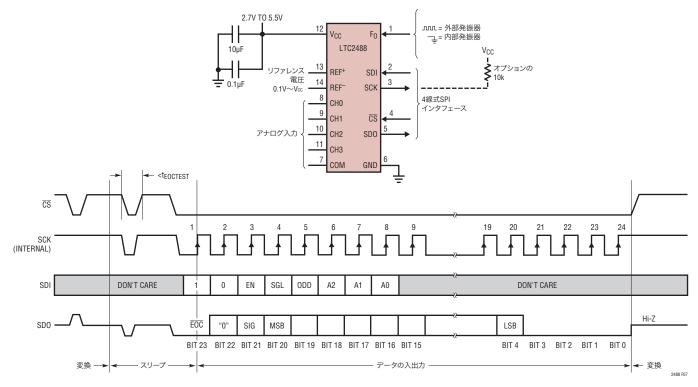

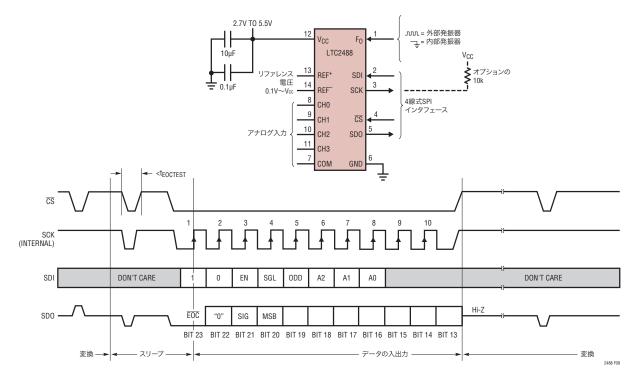

## タイミング図

### 内部SCKを使った場合のタイミング図(SCKは"H"でCS↓)

### 外部SCKを使った場合のタイミング図(SCKは"L"でCS↓)

#### コンバータの動作

#### コンバータの動作サイクル

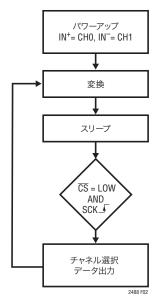

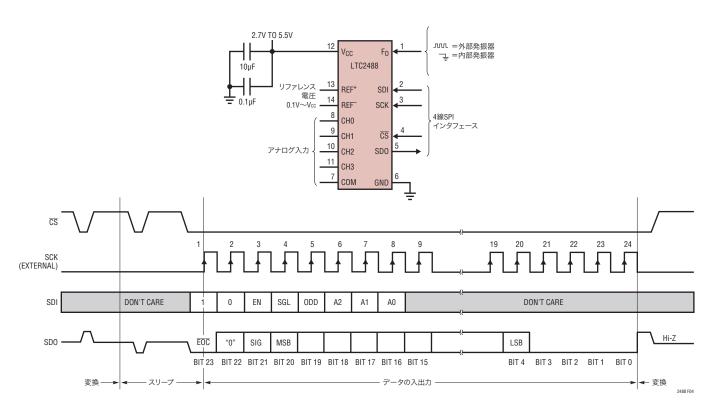

LTC2488はマルチチャネルの低電力デルタシグマADコンバータで、使いやすい4線式シリアル・インタフェースと自動差動入力電流キャンセル機能を備えています。その動作は4つの状態で構成されています(図2を参照)。コンバータの動作サイクルは変換から始まり、スリープ・ステートがそれに続き、データの入力/出力サイクルで終了します。4線式のインタフェースはシリアル・データ出力(SDO)、シリアル・クロック(SCK)、チップ・セレクト(CS)およびシリアル・データ入力(SDI)で構成されています。インタフェース、タイミング、動作サイクル、およびデータの出力フォーマットはリニアテクノロジー社のすべてのΔΣコンバータと互換性があります。

LTC2488は最初に(起動時に)変換をおこないます。変換が完了すると、デバイスはスリープ・ステートに入ります。スリープ・ステートの間、CSが"H"であれば、電力消費は2桁減少します。CSが"H"に保たれている限り、デバイスはスリープ・ステートに留まります。デバイスがスリープ・ステートの間、変換結果は無期限にスタチック・シフトレジスタ内に保存されます。

でSが"L"に引き下げられると、デバイスはパワーアップし、スリープ・ステートから出て、データ入力/出力ステートに入ります。SCKの最初の立上りエッジより前にでSが"H"になると、デバイスはスリープ・ステートに戻り、電力が低下します。SCK

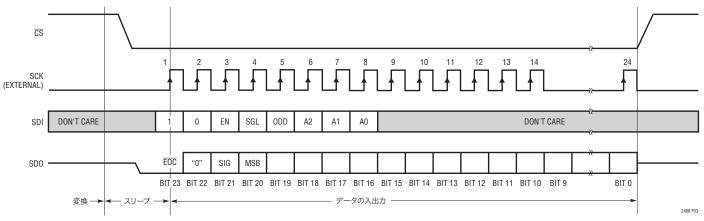

図2, LTC2488の状態遷移図

の最初の立上りエッジより後にCSが"H"になると、データ出力サイクルが中止され、新しい変換サイクルが開始されます。データの出力は直前に完了した変換に対応しています。この結果はシリアル・クロック・ピン(SCK)によって制御されて、シリアル・データ出力ピン(SDO)からシフトされて出力されます。データはSCKの立下りエッジによって更新されるので、ユーザーはSCKの立上りエッジを使って確実にデータをラッチすることができます(図3を参照)。次の変換のチャネル選択データもこの時点でデバイスにロードされます。データはSCKの各立上りエッジでシリアル・データ入力ピン(SDI)からロードされます。データ入力/出力サイクルは24ビットがADCから読み出されるか、またはCSが"H"に引き上げられると終了します。デバイスは自動的に新しい変換を開始し、このサイクルが繰り返されます。

でSピンとSCKピンのタイミング制御によって、LTC2488はいくつかの動作モード(内部または外部のSCKと自走変換の各モード)を柔軟に提供します。これらの多様なモードはプログラミングを必要とせず、上述の周期動作を乱すことがありません。これらの動作モードについては「シリアル・インタフェースのタイミング・モード」のセクションで詳しく説明します。

#### 使いやすさ

LTC2488のデータ出力には、待ち時間、フィルタのセトリング遅延、または変換サイクルに関連した冗長データがありません。変換と出力データの間には1対1対応の関係があります。したがって、複数のアナログ入力の多重化は簡単です。新しく入力が選択された直後に続く各変換は有効であり、精度はデバイスの仕様を完全に満たします。

LTC2488は、選択されたチャネルには無関係に、変換サイクル毎にオフセットとフルスケールの較正を自動的におこないます。この較正はユーザーからは見えず、上述の動作サイクルには影響を与えません。連続較正の利点は、時間経過、電源電圧の変動、入力チャネル、および温度ドリフトに対してオフセットとフルスケールの測定値がきわめて安定していることです。

#### Easy Drive入力電流キャンセル

LTC2488は高精度デルタシグマADCを自動差動入力電流 キャンセル・フロントエンドと組み合わせています。独自のフロントエンド受動サンプリング・ネットワークが透過的に差動入力電流を除去します。これにより、外部RCネットワークと高イ

ンピーダンス・センサを、外部アンプなしに、直接LTC2488にインタフェースさせることができます。残りの同相入力電流は、差動入力のインピーダンスをバランスさせるか、または同相入力を同相リファレンスに等しく設定して除去します(「自動差動入力電流キャンセル」のセクションを参照)。このユニークなアーキテクチャには内蔵バッファが不要なので、信号はグランドおよびVCCを超えて振幅することができます。さらに、このキャンセル機能はオフセットとフルスケールの透過的な自動較正と干渉することがないので、外部RCネットワークが付加されても、絶対精度(フルスケール+オフセット+直線性+ドリフト)が維持されます。

#### パワーアップ・シーケンス

LTC2488は電源電圧V<sub>CC</sub>が約2Vより下に下がると自動的に 内部リセット状態になります。この機能により、変換結果、入力 チャネルの選択、およびシリアル・クロック・モードの一貫性が 保証されます。

V<sub>CC</sub>がこのスレッショルドを超えると、コンバータは約4msの内部パワーオン・リセット(POR)信号を発生します。このPOR信号により、すべての内部レジスタがクリアされます。PORサイクル直後の変換は、入力チャネルIN<sup>+</sup> = CH0およびIN<sup>-</sup> = CH1で実行されます。PORサイクルに続く最初の変換の精度は、PORのインターバルが経過する前に電源電圧が2.7V~5.5Vの範囲に回復していれば、デバイスの仕様を満たします。この最初のデータ入力/出力サイクルの間に、新しい入力チャネルをデバイスにプログラムすることができます。

#### リファレンス電圧範囲

このコンバータは真に差動の外部リファレンス電圧を受け取ります。 $REF^+$ ピンと $REF^-$ ピンの絶対/同相電圧範囲はデバイスの全動作範囲( $GND \sim V_{CC}$ )を含みます。コンバータを正しく動作させるには、 $V_{REF}$ は正でなければなりません( $REF^+ > REF^-$ )。

LTC2488の差動リファレンスの入力範囲は0.1V~V<sub>CC</sub>です。 最も簡単に動作させるには、REF<sup>+</sup>をV<sub>CC</sub>に短絡し、REF<sup>-</sup>を GNDに短絡することができます。コンバータの出力ノイズはフ ロントエンド回路の熱雑音によって決まります。遷移ノイズは 1LSBよりはるかに低いので(0.02LSB)、リファレンス電圧を下 げれば比例してコンバータの分解能とINLが改善されます。

#### 入力電圧範囲

アナログ入力は真に差動で、CH0~CH3およびCOMの各入力ピンの絶対/同相範囲はGND-0.3Vから $V_{CC}$ +0.3Vまでです。これらのリミットの外側では、ESD保護用デバイスがオンし始め、入力のリーク電流による誤差が急速に増加します。これらのリミット内では、LTC2488はバイポーラ差動入力信号 $V_{IN}$  =  $IN^+$ - $IN^-$ (ここで、 $IN^+$ と $IN^-$ は選択された入力チャネル)を一FS =  $-0.5 \cdot V_{REF}$ から+FS =  $0.5 \cdot V_{REF}$ に変換します。ここで、 $V_{REF}$  =  $REF^+$ - $REF^-$ です。この範囲の外側では、コンバータは固有の出力コードを使ってオーバーレンジまたはアンダーレンジの状態を表示します(表1を参照)。

#### シリアル・インタフェース・ピン

LTC2488は、3線または4線の同期式インタフェースを介して、変換結果を伝送し、入力チャネルの選択を読み込み、変換開始コマンドを受け取ります。変換中およびスリープ・ステートの間、このインタフェースを使ってコンバータの状態にアクセスすることができます。データ出力ステートの間は、このインタフェースは変換結果を読み出し、入力チャネルをプログラムするのに使われます。

#### シリアル・クロックの入力/出力(SCK)

シリアル・クロック・ピン(SCK)は入力/出力のデータ転送の同期に使われます。各ビットはSCKの立下りエッジでシフトされてSDOピンから出力され、データはSCKの立上りエッジでシフトされてSDIピンに入力されます。

LINEAR

シリアル・クロック・ピン(SCK)は、マスタ(SCKは内部で発生させた出力)またはスレーブ(SCKは外部から与えられる入力)のどちらかに設定することができます。マスタ・モード(内部SCK)は単にSCKピンをフロートさせて選択します。スレーブ・モード(外部SCK)は、パワーアップ時およびCSの各立下りエッジの間にSCKを"L"にドライブして選択します。SCKモードの詳細は「シリアル・インタフェースのタイミング・モード」のセクションで説明されています。

#### シリアル・データ出力(SDO)

シリアル・データ出力ピン(SDO)は、データ出力ステートの間に最後の変換の結果をシリアル・ビット・ストリームとして (MSBを最初に)出力します。さらに、SDOピンは変換ステートおよびスリープ・ステートの間、変換終了インジケータとして使われます。

でSが"H"のとき、他のデバイスとデータ出力ラインを共有するため、SDOドライバは高インピーダンス状態に切り替わります。変換フェーズの間にでSを"L"にすると、EOCビット(SDOピン)が"H"にドライブされます。変換が完了後、でSが"L"になると、EOCが"L"にドライブされ、変換が完了してその結果をデバイスからシフトして出力する用意ができていることを知らせます。

#### チップ・セレクト(CS)

アクティブ"L"のCSピンは、変換状態をテストし、I/Oデータ転送をイネーブルし、新しい変換を開始し、スリープ・ステートの時間を制御し、さらにSCKモードを設定するのに使われます。

変換サイクルが終了すると、 $\overline{CS}$ が"H"の間、デバイスは低電力スリープ・ステートに留まり、電源電流は数桁減少します。スリープ・ステートから抜け出してデータ出力ステートに入るには、 $\overline{CS}$ を"L"に引き下げる必要があります。前述のように、データはSCKピンによって制御されるSDOピンからシフトされて出力されます。

新しい変換サイクルは、データ出力サイクルが終了すると(すべての24データ・ビットが読み出されると)、またはシリアル・クロック(SCK)の1番目と24番目の立上りエッジの間の任意の時間にCSを"H"に引き上げると開始されます。この場合、データの出力は中止され、新しい変換が開始されます。

#### シリアル・データ入力(SDI)

シリアル・データ入力(SDI)は入力チャネルの選択に使います。データは、CSが"L"のとき、データ出力/入力ステートの間にSCKの立上りエッジでシフトされてデバイスに入力されます。

#### 出力データのフォーマット

LTC2488のシリアル出力ストリームは24ビット長です。1番目のビットは変換状態を示し、2番目のビットは常にゼロで、3番目のビットは符号情報を伝えます。次の17ビットは変換結果で、MSBが最初にきます。残りの4ビットは常に"L"です。

ビット23(最初の出力ビット)は変換終了( $\overline{EOC}$ )のインジケータです。このビットは、変換ステートおよびスリープ・ステートの間、 $\overline{CS}$ が"L"のときSDOピンから読み出せます。このビットは変換サイクル中は"H"で、変換が完了すると"L"になり、 $\overline{CS}$ が"H"のときは"H"になります。

ビット22(2番目の出力ビット)はダミービット(DMY)で、常に "L"です。

ビット21(3番目の出力ビット) は変換結果の符合のインジケータ(SIG)です。選択された入力 $(V_{\rm IN}={\rm IN}^+-{\rm IN}^-)$ が0V以上あれば、このビットは"H"になります。 $V_{\rm IN}<0$ ならば、このビットは"L"になります。

ビット20(4番目の出力ビット)は結果の最上位ビット(MSB)です。このビットはビット21と組み合わされてアンダーレンジまたはオーバーレンジも表示します。ビット21とビット20が両方とも"H"の場合、差動入力電圧が+FSを超えています。ビット21とビット20が両方とも"L"の場合、差動入力電圧が-FSよりも下に下がっています。これらのビットの機能を表1にまとめてあります。

#### 表1, LTC2488の状態ビット

| 入力レンジ                                  | Bit 23<br>EOC | Bit 22<br>DMY | Bit 21<br>SIG | Bit 20<br>MSB |

|----------------------------------------|---------------|---------------|---------------|---------------|

| $V_{IN} \ge 0.5 \bullet V_{REF}$       | 0             | 0             | 1             | 1             |

| $0V \le V_{IN} < 0.5 \bullet V_{REF}$  | 0             | 0             | 1             | 0             |

| $-0.5 \bullet V_{REF} \le V_{IN} < 0V$ | 0             | 0             | 0             | 1             |

| $V_{IN} < -0.5 \bullet V_{REF}$        | 0             | 0             | 0             | 0             |

ビット20~ビット4は16ビットと符合からなる変換結果で、MSBが先にきます。

ビット4は最下位ビット(LSB<sub>16</sub>)です。

ビット3~ビット0は常に"L"です。

データはシリアル・クロック(SCK)の制御のもとにSDOピンからシフトされて出力されます(図3を参照)。 $\overline{CS}$ が"H"のときは常にSDOは高インピーダンスになり、SCKは無視されます。

変換結果をデバイスからシフトして出力するには、最初に区を "L"にドライブする必要があります。区Sが"L"に引き下げられると、デバイスのSDOピンにEOCが現われます。変換が完了すると、EOCは内部発振器またはfoピンに与えられたクロックの 関数としてリアルタイムで"H"から"L"に変化します。この信号は外部のマイクロコントローラへの割り込み信号として使うことができます。ビット23(EOC)はSCKの最初の立上りエッジで捕捉することができます。ビット22はSCKの最初の立下りエッジでシフトされてデバイスから出力されます。最後のデータ・ビット(ビットの)は23番目のSCKの立下りエッジでシフトされて出力され、24番目のSCKパルスの立上がりエッジでラッチすることができます。24番目のSCKパルスの立下りエッジでSDO

は"H"になり、新しい変換サイクルの開始を示します。このビットは次の変換サイクルのEOC(ビット23)として機能します。出力データのフォーマットが表2にまとめてあります。

$IN^+$ ピンと $IN^-$ ピンの電圧が-0.3V~ $(V_{CC}+0.3V)$ の絶対最大動作範囲に留まる限り、 $-FS=-0.5 \cdot V_{REF}$ から $+FS=0.5 \cdot V_{REF}$ までの任意の差動入力電圧 $V_{IN}$ に対して変換結果が生成されます。+FSを超える差動入力電圧の場合、変換結果は+FS+1LSBに相当する値にクランプされます。-FSより低い差動入力電圧の場合、変換結果は-FS-1LSBの値にクランプされます。

#### 入力データのフォーマット

LTC2488のシリアル入力ワードは8ビット長です。入力ビット (SGL、ODD、A2、A1、A0)は入力チャネルを選択するのに使われます。

図3. チャネル選択とデータ出力のタイミング

表2. 出力データのフォーマット

| 差動入力電圧<br>V <sub>IN</sub> *                    | Bit 23<br>EOC | Bit 22<br>DMY | Bit 21<br>SIG | Bit 20<br>MSB | Bit 19 | Bit 18 | Bit 17 | ••• | Bit 4<br>LSB | ビット3~0<br>は常に0 |

|------------------------------------------------|---------------|---------------|---------------|---------------|--------|--------|--------|-----|--------------|----------------|

| V <sub>IN</sub> * ≥ 0.5 • V <sub>REF</sub> **  | 0             | 0             | 1             | 1             | 0      | 0      | 0      |     | 0            | 0000           |

| 0.5 • V <sub>REF</sub> ** – 1LSB               | 0             | 0             | 1             | 0             | 1      | 1      | 1      |     | 1            | 0000           |

| 0.25 • V <sub>REF</sub> **                     | 0             | 0             | 1             | 0             | 1      | 0      | 0      |     | 0            | 0000           |

| 0.25 • V <sub>REF</sub> ** – 1LSB              | 0             | 0             | 1             | 0             | 0      | 1      | 1      |     | 1            | 0000           |

| 0                                              | 0             | 0             | 1             | 0             | 0      | 0      | 0      |     | 0            | 0000           |

| -1LSB                                          | 0             | 0             | 0             | 1             | 1      | 1      | 1      |     | 1            | 0000           |

| -0.25 • V <sub>REF</sub> **                    | 0             | 0             | 0             | 1             | 1      | 0      | 0      |     | 0            | 0000           |

| -0.25 • V <sub>REF</sub> ** − 1LSB             | 0             | 0             | 0             | 1             | 0      | 1      | 1      |     | 1            | 0000           |

| -0.5 • V <sub>REF</sub> **                     | 0             | 0             | 0             | 1             | 0      | 0      | 0      |     | 0            | 0000           |

| V <sub>IN</sub> * < −0.5 • V <sub>REF</sub> ** | 0             | 0             | 0             | 0             | 1      | 1      | 1      |     | 1            | 0000           |

<sup>\*</sup>差動入力電圧V<sub>IN</sub> = IN<sup>+</sup>-IN<sup>-</sup> \*\*差動リファレンス電圧V<sub>REF</sub> = REF<sup>+</sup>-REF<sup>-</sup>。

WI INEAD

パワーアップ後、デバイスは内部リセット・サイクルを開始し、 入力チャネルを $CH0 \& CH1 (IN^+ = CH0, IN^- = CH1)$ に設定 します。最初の変換はパワーアップ時にこのデフォルトの入力 チャネルを使って自動的に開始されます。変換が完了したら、 新しいワードをデバイスに書き込むことができます。

入力ワードの最初の3ビットは2個のプリアンブル・ビットと1個のイネーブル・ビットで構成されます。これらの3ビットは入力チャネルの選択に使われます。これらの3ビットの有効な設定は000、100、および101です。他の組合せは避けます。

最初の3ビットが000または100に設定されると、後続のデータは無視され(ドントケア)、前回選択された入力チャネルが次の変換に対しても依然有効です。

シフトされてデバイスに入力された最初の3ビットが101であれば、それに続く5ビットにより次の変換サイクルの入力チャネルが選択されます(表3を参照)。

101のシーケンスに続く最初の入力ビット(SGL)は、入力選択が差動(SGL=0)であるか、またはシングルエンド(SGL=1)であるかを決定します。SGL=0の場合、隣接する2本のチャネルを選択して差動入力を構成することができます。SGL=1の場合、4本のチャネルの中の1本が正入力として選択されます。負入力はすべてのシングルエンド動作でCOMです。残りの4ビット(ODD、A2、A1、A0)により、選択されるチャネルと(差動入力の場合)その極性が決定されます。

#### シリアル・インタフェースのタイミング・モード

LTC2488の4線式インタフェースはSPIおよびMICROWIREと互換性があります。このインタフェースにより、いくつかの柔軟な動作モードが実現できます。これらには内部/外部シリアル・クロック、3線または4線のI/O、シングル・サイクル変換または連続変換が含まれます。以下のセクションではこれらのそれぞれのタイミング・モードを詳細に説明します。すべての場合に、コンバータは内部発振器( $F_0$ ="L")または $F_0$ ピンに接続された外部発振器を使うことができます。各モードで、動作サイクル、データ入力のフォーマット、データ出力のフォーマット、および性能は変わりません。表4にまとめられていますので参照してください。

表3. チャネルの選択

|     | MUXアドレス チャネルの選択 |    |    |    |     |     |     |     |     |

|-----|-----------------|----|----|----|-----|-----|-----|-----|-----|

| SGL | ODD/<br>SIGN    | A2 | A1 | AO | 0   | 1   | 2   | 3   | сом |

| *0  | 0               | 0  | 0  | 0  | IN+ | IN- |     |     |     |

| 0   | 0               | 0  | 0  | 1  |     |     | IN+ | IN- |     |

| 0   | 1               | 0  | 0  | 0  | IN- | IN+ |     |     |     |

| 0   | 1               | 0  | 0  | 1  |     |     | IN- | IN+ |     |

| 1   | 0               | 0  | 0  | 0  | IN+ |     |     |     | IN- |

| 1   | 0               | 0  | 0  | 1  |     |     | IN+ |     | IN- |

| 1   | 1               | 0  | 0  | 0  |     | IN+ |     |     | IN- |

| 1   | 1               | 0  | 0  | 1  |     |     |     | IN+ | IN- |

<sup>\*</sup>起動時のデフォルト設定

表4. シリアル・インタフェースのタイミング・モード

| 構成設定                  | SCK<br>信号源 | 変換サイクルの<br>制御 | データ出力<br>制御 | 接続と波形 |

|-----------------------|------------|---------------|-------------|-------|

| 外部SCK、<br>シングル・サイクル変換 | 外部         | でSおよびSCK      | ℂSおよびSCK    | 図4、図5 |

| 外部SCK、3線式I/O          | 外部         | SCK           | SCK         | 図6    |

| 内部SCK、<br>シングル・サイクル変換 | 内部         | CS↓           | CS↓         | 図7、図8 |

| 内部SCK、3線式I/O、<br>連続変換 | 内部         | 連続            | 内部          | 図9    |

#### 外部シリアル・クロック、シングル・サイクル動作

このタイミング・モードでは、外部シリアル・クロックを使って変換結果をシフトして出力し、CS信号を使って変換サイクルの状態をモニタして制御します(図4を参照)。

パワーアップ・シーケンスの間および $\overline{CS}$ の各立下りエッジで外部シリアル・クロック・モードが選択されます。外部SCKモードの動作に入り、そこに留まるには、パワーアップと $\overline{CS}$ の各立下りエッジでSCKを"L"にドライブする必要があります。 $\overline{CS}$ の立下りエッジでSCKが"H"だと、デバイスは内部SCKモードに切り替わります。

シリアル・データ出力ピン(SDO)は、 $\overline{\text{CS}}$ が"H"である間は高インピーダンスになります。変換サイクルの間はいつでも、コンバータの状態をモニタするために $\overline{\text{CS}}$ を"L"に引き下げることができます。 $\overline{\text{CS}}$ が"L"の間は $\overline{\text{EOC}}$ がSDOピンに出力されます。

変換が進行中は $\overline{EOC}$  = 1になり、変換が完了してデバイスが スリープ・ステートに入ると $\overline{EOC}$  = 0になります。 $\overline{CS}$ には関係なく、変換が完了すると、デバイスは自動的にスリープ・ステート に入ります。ただし、電力を下げるため、 $\overline{CS}$ は"H"にする必要 があります。

デバイスがスリープ・ステートのとき、変換結果は内部のスタ チック・シフトレジスタに保存されます。CSが"L"の間にSCK の最初の立上りエッジが現れるまで、デバイスはスリープ・ス テートに留まります。それから、入力データがSCKの(最初の 立上りエッジを含む)各立上りエッジでシフトされSDIピンを 介して入力されます。後続の変換サイクルではチャネル選択が 使われます。I/Oサイクルの間に入力チャネルが変更されると、 そのデータ入出力サイクルに続く変換サイクルに対して新しい 設定が有効になります。出力データはSCKの各立下りエッジ でシフトされてSDOピンから出力されます。このため、外部回 路はSCKの立上りエッジを使って出力をラッチすることができ ます。EOCはSCKの最初の立上りエッジを使ってラッチするこ とができ、変換結果の最後のビットはSCKの24番目の立上り エッジを使ってラッチすることができます。SCKの24番目の立 下りエッジで、デバイスは新しい変換を開始し、SDOは"H"に なり(EOC = 1)、新しい変換サイクルが進行中であることを示 します。

データ・サイクルの完了時にCSを"L"のままにしておき、EOCを変換終了時の割り込み信号としてモニタすることができます。

通常、CSはデータの入力/出力ステートの間"L"に保たれます。

図4. 外部シリアル・クロック、シングル・サイクル動作

ただし、SCKの最初の立下りエッジと24番目の立下りエッジの間に、いつでもCSを"H"に引き上げてデータ出力ステートを中止することができます(図5を参照)。CSの立上りエッジでデバイスはデータ出力ステートを中止し、直ちに新しい変換を開始します。新しい入力チャネルをプログラムするには、8個のSCKクロック・パルスが必要です。データ出力シーケンスがSCKの8番目の立下りエッジより前に中止されると、新しい入力データは無視され、前回選択された入力チャネルがそのまま有効に保たれます。SCKの8番目の立下りエッジの後にCSの立上りエッジが生じると、新しい入力チャネルがロードされ、次の変換サイクルで有効になります。

#### 外部シリアル・クロック、3線式1/0

このタイミング・モードでは3線式シリアルI/Oインタフェースが使われます。変換結果は外部で作られたシリアル・クロック(SCK)信号によってシフトされてデバイスから出力されます(図6参照)。CSは永続的にグランドに接続され、ユーザー・インタフェースや絶縁バリヤが簡素化されます。

外部シリアル・クロック・モードが起動時リセット(POR)サイクルの終わりに選択されます。PORサイクルはVCCが約2Vを超えてから標準で4ms後に終了します。この時点でSCKに与えられるレベルによって、SCKが内部で作られるかそれとも外部から与えられるかが決まります。外部SCKモードに入るには、PORサイクルの終了前にSCKを"L"にドライブする必要があります。

でSが"L"に固定されているので、変換ステートおよびスリープ・ステートの間、変換終了(EOC)をSDOピンで連続してモニタすることができます。EOCは外部コントローラの割り込み信号として使うことができます。変換進行中はEOC = 1になり、変換が完了するとEOC = 0になります。EOCの立下りエッジで、変換結果が内部のスタチック・シフトレジスタにロードされます。これで、外部から与えられるSCK信号の制御によって出力データをシフトさせて、SDOピンから出力することができます。SCKの立下りエッジでデータを更新します。入力データは、SCKの立上りエッジでジフトされ、SDIピンを通してデバイスに入力されます。SCKの24番目の立下りエッジで、SDOは"H"になり、新しい変換サイクルが開始されたことを示します。このデータは次の変換サイクルのEOCとして機能します。

図5. 外部シリアル・クロック、短縮された出力データ長および有効なチャネル選択

図6. 外部シリアル・クロック、3線式動作(CS = 0)

#### 内部シリアル・クロック、シングル・サイクル動作

このタイミング・モードでは、内部シリアル・クロックを使って変換結果をシフトして出力し、CS信号を使って変換サイクルの状態をモニタして制御します(図7を参照)。

内部シリアル・クロック・タイミング・モードを選択するには、PORサイクルの終了前と $\overline{CS}$ の各立下りエッジより前に、シリアル・クロック・ピン(SCK)をフロートさせるか、または"H"に引き上げる必要があります。 $\overline{CS}$ が立ち下がる間、SCKピンは内部の弱いプルアップ抵抗がアクティブになっています。したがって、SCKが外部からドライブされていなければ、内部SCKモードが自動的に選択されます。

シリアル・データ出力ピン(SDO)は、 $\overline{\text{CS}}$ が"H"である間は高インピーダンスになります。変換サイクルの間はいつでも、コンバータの状態をモニタするために $\overline{\text{CS}}$ を"L"に引き下げることができます。 $\overline{\text{CS}}$ が"L"に引き下げられると、SCKが"L"になり、 $\overline{\text{EOC}}$ がSDOピンに出力されます。変換の進行中は $\overline{\text{EOC}}$  = 1になり、デバイスがスリープ・ステートだと $\overline{\text{EOC}}$  = 0になります。

EOCをテストすると、変換が完了していれば(EOC = 0)、デバイスはスリープ・ステートから出ます。スリープ・ステートに

戻って電力消費を下げるには、デバイスがSCKを"H"に引き上げる前に $\overline{\text{CS}}$ を"H"に引き上げる必要があります。デバイスが自己の内部発振器を使っているとき( $F_{\text{O}}$ が"L"に接続されている)、SCKの最初の立上りは $\overline{\text{CS}}$ の立下り後12 $\mu$ sに生じます( $t_{\text{EOCTEST}} = 12\mu$ s)。周波数が $t_{\text{EOSC}}$ の外部発振器によって $t_{\text{CO}}$ でがドライブされていると、 $t_{\text{EOCTEST}} = 3.6/f_{\text{EOSC}}$ になります。

でSがt<sub>EOCTEST</sub>より長く"L"に留まると、SCKの最初の立上り エッジが生じ、変換結果がSCKの立下りエッジでシフトされて SDOピンから出力されます。シリアル入力ワード(SDI)はSCK の立上りエッジでシフトされてデバイスに入力されます。

SCKの24番目の立上りエッジの後、新しい変換が自動的に開始されます。SDOは"H"になり( $\overline{EOC}=1$ )、SCKは変換サイクルの間"H"に保たれます。変換が完了すると、サイクルが繰り返されます。

通常、 $\overline{CS}$ はデータ出力ステートの間"L"に保たれます。ただし、SCKの1番目の立上りエッジと24番目の立下りエッジの間に、いつでも $\overline{CS}$ を"H"に引き上げてデータ出力ステートを中止することができます(図8を参照)。 $\overline{CS}$ の立上りエッジでデバイスはデータ出力ステートを中止し、直ちに新しい変換を開始し

図7. 内部シリアル・クロック、シングル・サイクル動作

ます。新しい入力チャネルをプログラムするには、8個のSCKクロック・パルスが必要です。データ出力シーケンスがSCKの8番目の立下りエッジより前に中止されると、新しい入力データは無視され、前回選択された入力チャネルがそのまま有効に保たれます。SCKの8番目の立下りエッジの後にCSの立上りエッジが生じると、新しい入力チャネルがロードされ、次の変換サイクルで有効になります。

#### 内部シリアル・クロック、3線式1/0、連続変換

このタイミング・モードでは3線式インタフェースを使います。 変換結果は内部で作られたシリアル・クロック(SCK)信号に よってシフトされてデバイスから出力されます(図9参照)。こ の場合、CSは永続的にグランドに接続され、ユーザー・インタ フェースや、絶縁バリヤを超えた転送が簡素化されます。

内部シリアル・クロック・モードは起動時リセット(POR)サイクルの終わりに選択されます。PORサイクルはV<sub>CC</sub>が2Vを超えてから約4ms後に終了します。内部の弱いプルアップ抵抗はPORサイクルの間アクティブです。したがって、SCKがフロート状態だと、または"H"にドライブされると、内部シリアル・クロック・タイミング・モードが自動的に選択されます。

変換中、SCKとシリアル・データ出力ピン(SDO)は"H"になります(EOC = 1)。変換が完了すると、SCKとSDOは"L"になり(EOC = 0)、変換が終了してデバイスがスリープ・ステートに入ったことを示します。デバイスは最小時間(内部SCKの周期の1/2)の間スリープ・ステートに留まってから、直ちにデータの入出力を開始します。入力データがSCKの(最初の立上りエッジを含む)立上りエッジでシフトされてSDIピンに入力され、出力データがSCKの立下りエッジでシフトされてSDOピンから出力されます。SCKの24番目の立上りエッジの後、データの入出力サイクルが終了し、新しい変換が自動的に開始されます。次の変換中、SCKとSDLは変換が完了するまで"H"に保たれます。

#### 10kプルアップをSCKに使用して内部SCKを選択

コンバータがSCKを"L"にドライブしている状態で $\overline{\text{CS}}$ が"H"に引き上げられると、SCKがフロート状態でも、SCKをロジック"H"の状態に戻すのに内部プルアップは使えません。このため、 $\overline{\text{CS}}$ の次の立下りエッジでデバイスは内部SCKモードから抜け出します。これは、外部10kプルアップ抵抗をSCKピンに追加することにより避けることができます。

図8. 内部シリアル・クロック、短縮された出力データ長および有効なチャネルと構成の選択

図9. 内部シリアル・クロック、連続動作

LINEAD

SCKが"L"のときはLTC3726のSCKの内部プルアップはディスエーブルされます。通常、デバイスが内部SCKタイミング・モードで動作していると、SCKは外部からドライブされません。ただし、特定のアプリケーションでは、SCKに外部ドライバが必要なことがあります。ドライバが"L"信号を出力した後Hi-Zになると、内部プルアップはディスエーブルされます。外部10kプルアップ抵抗を追加すれば、この条件でデバイスが内部SCKモードから抜け出すのを防ぐことができます。

変換状態をテストするために $\overline{\text{CS}}$ を"H-L-H"とトグルするとき、スリープ・ステートで同様の状況が起きることがあります。デバイスがスリープ・ステート( $\overline{\text{EOC}}$  = 0)ならば、 $\overline{\text{SCK}}$ は" $\overline{\text{L}}$ "になります。時間 $\overline{\text{teoCtest}}$ が経過する前に $\overline{\text{CS}}$ が" $\overline{\text{H}}$ "になると、内部プルアップが $\overline{\text{POF}}$  7 になります。 $\overline{\text{SCK}}$  9 できないことがあります。 $\overline{\text{POF}}$  9 か部 10 kプルアップ抵抗を追加すれば、 $\overline{\text{L}}$  2 の条件でデバイスが内部 $\overline{\text{SCK}}$  8 に回復できないことがあります。 $\overline{\text{POF}}$  1 から抜け出すのを防ぎます。

#### コンバータの精度の維持

LTC2488は、デバイスのデカップリング、PCBのレイアウト、アンチエイリアシング回路、ライン周波数の乱れ、温度変化などの影響をできるだけ受けないように設計されています。最高性能を達成するには、いくつかの簡単な注意を守る必要があります。

#### デジタル信号レベル

LTC2488のデジタル・インタフェースは使うのが簡単です。そのデジタル入力であるSDI、Fo、CSおよびSCK(外部シリアル・クロック・モードの場合)は標準CMOSロジック・レベルを受け入れます。内部ヒステリシス回路は100μsの遅いエッジ遷移時間を許容することができます。

デジタル入力信号の範囲は0.5V~(V<sub>CC</sub>-0.5V)です。遷移の間、CMOS入力回路にはダイナミック電流が流れます。最適性能を実現するには、シリアル・データ・インタフェースへ信号を与えるのはスリープ期間とデータ出力期間に限定します。

変換中にシリアル・デジタル・インタフェースや外部発振器ピン(Fo)に与えられる高速デジタル信号のオーバーシュートやアンダーシュートは、コンバータの性能を低下させることがあります。アンダーシュートとオーバーシュートは、外部制御

信号の遷移時間がドライバから入力ピンまでの伝播遅延の2倍より短いとき、回路基板のコンバータのピンのトレースのインピーダンスの不整合によって生じます。参考までに、普通のFR-4基板では、伝播遅延は約183ps/インチです。オーバーシュートを防ぐには、1nsの遷移時間のドライバは2.5インチより短いトレースでコンバータに接続する必要があります。これは、共通制御ラインが使用され、多数の反射が起きると困難になります。

LTC2488の入力ピンの近くで並列終端すればこの問題は解決されますが、ドライバの電力消費が増加します。ドライバの近くに配置された(トレースのインピーダンスと接続に依存した) $27\Omega\sim54\Omega$ の直列抵抗も、ドライバの追加の電力消費なしにオーバーシュート/アンダーシュートを除去します。

多くのアプリケーションでは、シリアル・インタフェース・ピン (SCK、SDI、CS、Fo)は変換サイクルの間は静かに保たれ、性能低下は生じません。他方、外部発振器が使われると(Fo が外部からドライブされると)、それは変換サイクルの間アクティブなままです。さらに、Foに与えられるクロック・レートではデジタル・フィルタによる除去はわずかです。外部入力とリファレンス・ラインがこの信号と交差しないように、また近くを通らないように注意する必要があります。これらの問題は内部発振器を使用すると避けられます。

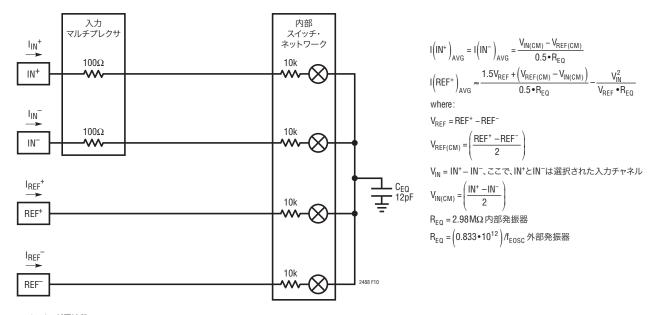

#### 入力とリファレンスのドライブ

LTC2488の入力ピンとリファレンス・ピンはスイッチトキャパシタのネットワークに直接接続されています。差動入力電圧と差動リファレンス電圧の関係に依存して、これらのコンデンサはこれらの4つのピンの間で切り替えられます。コンデンサがこれらのピンの2本の間で切り替えられるたびに、少量の電荷が転送されます。簡略等価回路図を図10に示します。

LTC2488の内部発振器を使っているとき、入力コンデンサ・アレイは123kHzで切り替えられます。電荷転送の効果は入力ピン/リファレンス・ピンをドライブしている回路に依存します。全外部RCの時定数が580nsより小さいと、完全にセトリングするので、サンプリング過程で生じる誤差は無視できます。

一般に、リファレンス入力は低インピーダンスのソースでドライブされます。この場合、大きな外部バイパス・コンデンサが使われていても完全にセトリングします。他方、入力(CH0~

スイッチング周波数 f<sub>SW</sub> = 123kHz 内部発振器 f<sub>SW</sub> = 0.4 • f<sub>EOSC</sub> 外部発振器

#### 図10, LTC2488の等価アナログ入力回路

CH3、COM) は一般に大きなソース抵抗からドライブされます。10kまでのソース抵抗は直接LTC2488にインタフェースすることができ、完全にセトリングします。ただし、不要のノイズを除去するため(アンチエイリアシング)、入力端子に外部コンデンサを追加すると、セトリングが完了しません。

#### 自動差動入力電流キャンセル

センサの出力インピーダンスが低い(外部バイパス・コンデンサなしで最大 $10k\Omega$ 、または $0.001\mu$ Fのバイパス付きで最大 $500\Omega$ )アプリケーションでは、入力は完全にセトリングします。この場合、誤差は入り込まないので、センサを直接デジタル化することが可能です。

多くのアプリケーションでは、センサの出力インピーダンスは外部入力バイパス・コンデンサと結合して1ppmの精度に必要な580nsをはるかに超えるRC時定数を生じます。たとえば、 $0.1\mu$ Fのコンデンサをドライブする $10k\Omega$ のブリッジでは、必要な最大値より1桁大きな時定数になります。

LTC2488は独自のスイッチング・アルゴリズムを使って、外部のセトリング誤差とは無関係に、平均差動入力電流をゼロに強制します。これにより、バッファは不要で、高インピーダンスのセンサを直接デジタル化できます。

このスイッチング・アルゴリズムは、正入力 $(I_{IN}^+)$ の平均入力電流を負入力 $(I_{IN}^-)$ の平均入力電流に等しくなるように強制します。変換サイクル全体にわたって、平均差動入力電流 $(I_{IN}^+-I_{IN}^-)$ はゼロになります。差動入力電流はゼロですが、同相入力電流 $(I_{IN}^++I_{IN}^-)$ /2は同相入力電圧 $(V_{IN}(C_{IN})$ と同相リファレンス電圧 $(V_{REF}(C_{IN})$ の差に比例します。

平衡ブリッジのように、入力同相電圧がリファレンス同相電圧に等しいアプリケーションでは、差動と同相の両方の入力電流がゼロになります。コンバータの精度はセトリング誤差によって低下することはありません。

入力同相電圧が一定だがリファレンス同相電圧とは異なるアプリケーションでは、差動入力電流はゼロに保たれますが、同相入力電流はV<sub>IN</sub>(CM)とV<sub>REF</sub>(CM)の差に比例します。リファレンス同相電圧が2.5Vで、入力同相電圧が1.5Vの場合、同相入力電流は約0.74µAです。この同相入力電流は、IN<sup>+</sup>とIN<sup>-</sup>に接続されたソースのインピーダンスが整合していれば、精度を低下させることはありません。ソース・インピーダンスが整合していないと、固定オフセット誤差が生じますが、直線性やフルスケールの測定値には影響を与えません。1kソース抵抗の1%の不整合により、オフセット電圧が74µVシフトします。

LINEAR TECHNOLOGY

同相入力電圧が入力信号レベルの関数として変化するアプリケーション(シングルエンドのセンサなど)では、同相入力電流は入力電圧に比例して変化します。バランスのとれた入力インピーダンスの場合、同相入力電流の影響はLTC2488の大きなCMRRによって除去され、精度はほとんど低下しません。ソース・インピーダンスが整合していないと、同相入力電圧と同相リファレンス電圧の差に比例した利得誤差が生じます。1kソース抵抗に1%の不整合があると、15ppm程度の利得誤差が生じます。内部サンプリング・コンデンサの安定性と内部発振器の精度に基づいて、一度較正すればこの誤差は取り除かれます。

入力サンプリング電流に加えて、入力ESD保護ダイオードには温度に依存したリーク電流が流れます。公称1nA(最大  $\pm 10nA$ )のこの電流により、オフセットがわずかにシフトします。1kのソース抵抗により、標準 $1\mu V$ 、最大 $10\mu V$ のオフセット電圧が生じます。

#### リファレンス電流

アナログ入力と同様に、LTC2488は差動リファレンス・ピン (REF<sup>+</sup>とREF<sup>-</sup>)をサンプリングして、少量の電荷をこれらのピンとやり取りしますので、ダイナミックなリファレンス電流が生じます。セトリングが(リファレンスのソース抵抗とリファレンスのバイパス・コンデンサに依存して)不完全だと、直線性誤差と利得誤差が生じます。

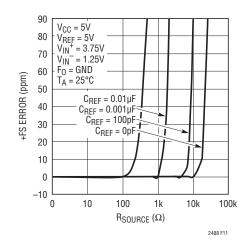

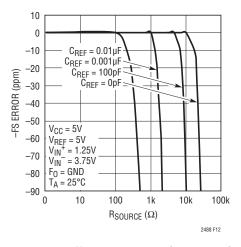

外部リファレンスの容量の値が比較的小さいと  $(C_{REF} < 1nF)$ 、サンプリング・コンデンサの電圧は大きな $k\Omega$ のリファレンス・インピーダンスでもセトリングします  $(C_{REF} = 100pF$ ならば、最大10kまで性能は低下しません) (図11と図12を参照)。

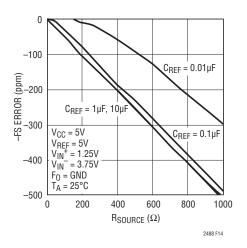

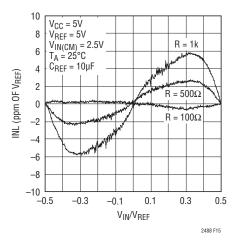

リファレンス入力に大きなバイパス・コンデンサが必要な場合  $(C_{REF} > 0.01 \mu F)$ 、フルスケール誤差と直線性誤差はリファレンス抵抗の値に比例します。リファレンス抵抗の10年に、約0.5ppmのフルスケール誤差が生じます(内部発振器で動作しているとき)(図13と図14を参照)。入力同相電圧がリファレンス同相電圧に等しい場合、リファレンス抵抗の1000年に約0.67ppmの直線性誤差が生じます(図15を参照)。入力同相電圧とリファレンス同相電圧が異なるアプリケーションでは、誤差が増加します。同相入力と同相リファレンスの間の1Vの

図11. +FS誤差とVREFのRSOURCE(小さなCREF)

図12. -FS誤差とVREFのRSOURCE(小さなCREF)

差は、リファレンスの抵抗の $100\Omega$ 毎に6.7ppmのINL誤差を生じます。

リファレンスのサンプリング電荷に加えて、リファレンスのESD 保護ダイオードには温度に依存したリーク電流が流れます。 公称1nA(最大 $\pm 10nA$ )のこのリーク電流により小さな利得誤差が生じます。リファレンスの $100\Omega$ の抵抗により、 $0.5\mu V$ のフルスケール誤差が生じます。

図13. +FS誤差とVREFのRSOURCE(大きなCREF)

図14. -FS誤差とVREFのRSOURCE(大きなCREF)

図15. INLと差動入力電圧および リファレンスのソース抵抗(C<sub>REF</sub> > 1μF)

#### 通常モードの除去率とアンチエイリアシング

従来のADCに比べたデルタシグマADCの利点の1つは、チップに内蔵されたデジタル・フィルタです。大きなオーバーサンプリング率と組み合わせることにより、LTC2488はアンチエイリアシング・フィルタの必要条件を大幅に簡素化します。さらに、入力電流キャンセル機能により、デバイスのDC性能を下げることなく、外部ローパス・フィルタを利用できます。

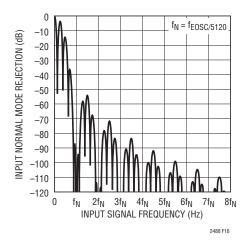

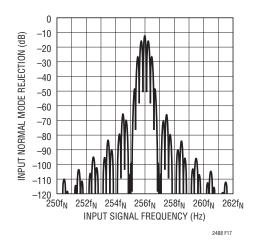

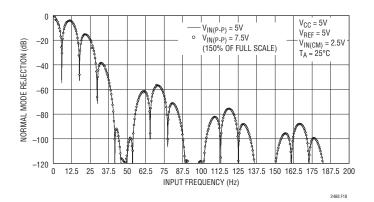

SINC<sup>4</sup>デジタル・フィルタにより、DCと変調器のサンプリング周波数  $(f_S)$  の整数倍を除く全ての周波数で優れた通常モードの除去を与えます。変調器のサンプリング周波数は、内部発振器で動作しているときは $f_S = 15,360$ Hz、周波数が $F_{EOSC}$ の外部発振器で動作しているときは $f_S = F_{EOSC}/20$ です。

LTC2488は内部発振器を使用しているときライン周波数を除去するように設計されています。図16に示されているように、除去ヌルは周波数 $f_N$ の倍数で生じます。ここで、同時50Hz/60Hz 除去の場合 $f_N=55$ Hzです。変調器のサンプリング・レートの倍数 ( $f_S=f_N \bullet 256$ )では、ノイズを15dB除去するだけですが(図17を参照)、これらの周波数にノイズ源が存在すれば、アンチエイリアシングにより、それらの影響が減少します。

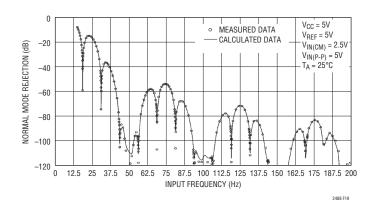

図18に示されているように、ユーザーは内部発振器を使ってこのレベルの性能を達成することを期待することができます。 通常モードの除去の測定値が理論値の上に重ね合わされて示されています。

従来の高次デルタシグマ変調器は、大きな入力信号レベルでは潜在的に不安定です。LTC2488の3次変調器に使われて

図16, DCでの入力通常モードの除去率

図17. f<sub>S</sub> = 256 • f<sub>N</sub>での入力通常モードの除去率

図18. 入力通常モードの除去率と入力周波数、100%の入力の撹乱(50Hz/60Hzのノッチ)

図19. 測定された入力通常モードの除去率と入力周波数、 150%の入力の撹乱(60Hzのノッチ)

いる独自アーキテクチャはこの問題を解決し、フルスケールの150%の入力信号で安定動作を保証します。多くの産業用アプリケーションでは、数ボルトのピーク・トゥ・ピーク・ノイズを含む不要の誤差源に重ね合わされたマイクロボルト・レベルの信号が珍しくありません。LTC2488に与えられた7.5Vのピーク・トゥ・ピーク・ノイズ源(フルスケールの150%)の除去率の測定結果を図19に示します。この曲線は、極端にノイズの大きい環境でさえ、除去性能が維持されていることを示しています。

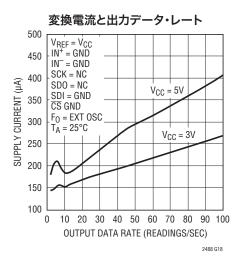

#### 出力データ・レート

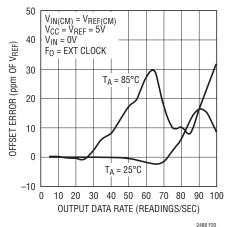

内部発振器を使用しているとき、LTC2488は55Hzのノッチ周波数で毎秒6.9のサンプリング(sps)を行います。実際の出力データ・レートはスリープ・サイクルとデータ出力サイクルの長さに依存しますが、これらはユーザーによって制御され、無視できるほど短くすることができます。外部変換クロックを使って動作させると(Foを外部発振器に接続)、LTC2488の出力データ・レートを増加させることができます。変換サイクルの持続時間は41036/f<sub>EOSC</sub>です。f<sub>EOSC</sub> = 307.2kHzならば、コンバータは、まるで内部発振器が使われているかのように動作します。

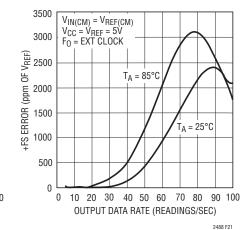

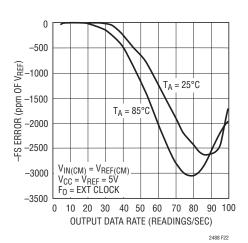

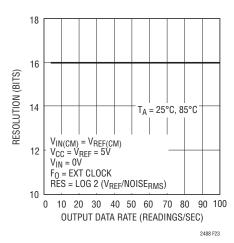

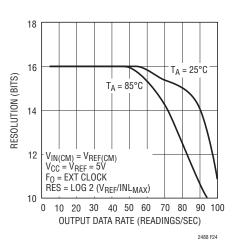

f<sub>EOSC</sub>を公称307.2kHzを超えて増加させると、最大出力データ・レートが比例して増加します(最大100spsまで)。出力レートが増加するとオフセットとフルスケール誤差が大きくなり、実効分解能が低下し、周波数除去がシフトします。

feoscが変化すると、内部のノッチの位置が比例して変化します。これにより、ライン周波数の差動モード除去が低下します。ライン周波数の同相除去は変化せずに保たれますので、IN<sup>+</sup>とIN<sup>-</sup>の両方のピンが高度に対称性をもった完全な差動入力信号は引き続きライン周波数のノイズを除去します。

また、fEOSCが増加すると、入力およびリファレンスの実効ダイナミック電流が増加します。外部RCネットワークの差動入力電流は引き続きゼロですが、セトリングの完了に要する時間(fEOSC = 307.2kHzで580ns)は比例して短くなります。

外部発振器の周波数が1MHzを超えると(出力レートが3倍以上増加すると)、内部自動較正回路の効果が低下し始めます。

このため、オフセット誤差とフルスケール誤差が大きくなり、分解能が低下します(図20と図27を参照)。

### Easy Drive ADCによる高インピーダンス・センサの 測定の簡素化

デルタシグマADCは精度が高くノイズ耐性が高いので、多種のセンサを直接測定するのに最適です。にもかかわらず、入力サンプリング電流が、高いソース・インピーダンスや帯域幅の低いマイクロパワー信号調整回路を圧倒してしまうことがあります。LTC2488は入力電流をバランスさせることによってこの問題を解決しますので、信号調整回路を簡素化するか、あるいは不要にします。

デルタシグマADCはサーミスタの測定に広く使用されます。 Easy Driveテクノロジーの利点を生かした、サーミスタのデジタル化の2つの例を図28に示します。

最初の回路(入力チャネルのCH0とCH1に適用)には、同相入力電圧/同相リファレンス電圧をバランスさせるため、また、差動入力ソース抵抗をバランスさせるために、バランス基準抵抗が使われています。基準抵抗R1とR4が正確に等しければ入力電流がゼロになり、誤差は生じません。これらの抵抗の許容誤差が1%であれば、測定された抵抗の最大誤差は同相電圧

のシフトにより1.6Ωとなり、基準抵抗自体の1%の誤差よりはるかに小さくなります。アンプは不要ですから、これはマイクロパワーのアプリケーションに最適なソリューションです。

Easy Driveは、非常にローパワーで低帯域幅のアンプがLTC2488の入力をドライブすることも可能にします。図28に示されているように、CH2はLT1494によってドライブされています。LT1494のDC仕様は電源電流が1.5 $\mu$ Aのアンプとしては非常に優れています(最大オフセット電圧は150 $\mu$ V、開ループ利得は100,000です)。その帯域幅は2 $\mu$ Hzなので、従来のデルタングマADCをドライブするのには適していません。 $\mu$ LT1494から分離し、LTC2488の瞬時電流を供給するための電荷はコンデンサに貯蔵されるので、この問題が解決されます。

従来のデルタシグマADCでは、外部RCネットワークの不完全なセトリングの結果として、入力サンプリング電流によりDC誤差が生じます。

Easy Driveテクノロジーは差動入力電流をキャンセルします。 負入力(CH3)を $1k\Omega$ 、 $0.1\mu$ Fのネットワークでバランスさせることにより、同相入力電流による誤差がキャンセルされます。

図20. オフセット誤差と 出力データ・レートおよび温度

図21. +FS誤差と 出力データ・レートおよび温度

図22. -FS誤差と 出力データ・レートおよび温度

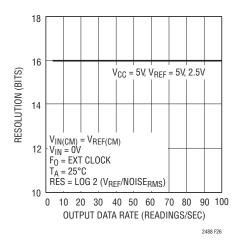

図23. 分解能(Noise<sub>RMS</sub> ≤ 1LSB)と 出力データ・レートおよび温度

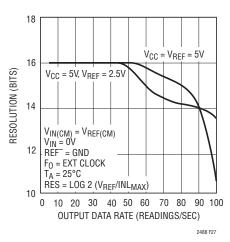

図24. 分解能 (INL<sub>MAX</sub> ≤ 1LSB)と 出力データ・レートおよび温度

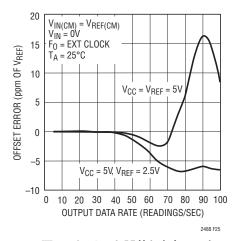

図25. オフセット誤差と出力データ・ レートおよびリファレンス電圧

図26. 分解能(Noise<sub>RMS</sub> ≤ 1LSB)と 出力データ・レート およびリファレンス電圧

図27. 分解能(INL<sub>MAX</sub> ≤ 1LSB)と 出力データ・レート およびリファレンス電圧

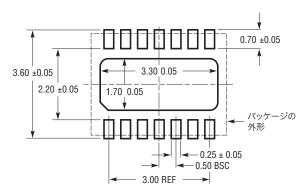

#### DEパッケージ 14ピン・プラスチックDFN(4mm×3mm)

(Reference LTC DWG # 05-08-1708 Rev B)

推奨する半田パッドのピッチと寸法 半田付けされない領域には半田マスクを使用する

#### NOTE:

- 1. 図はJEDECパッケージ・アウトラインMO-229のバージョンのバリエーション (WGED-3)として提案

- 2. 図は実寸とは異なる

- 3. すべての寸法はミリメートル 4. パッケージ底面の露出パッドの寸法にはモールドのパリを含まない モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

- 5. 露出パッドは半田メッキとする

- 6. 網掛けの部分はパッケージのトップとボトムのピン1の位置の参考に過ぎない

## 改訂履歴

| REV | 日付   | 概要            | ページ番号 |

|-----|------|---------------|-------|

| Α   | 7/10 | 「標準的応用例」の図の改訂 | 1     |

|     |      | Note 18の追加    | 4、5   |

### 標準的応用例

図28. Easy Drive ADCによる高インピーダンス・センサの測定の簡素化

### 関連製品

| 製品番号                        | 説明                                                                                                    | 注釈                                                               |

|-----------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| LT1236A-5                   | 高精度バンドギャップ・リファレンス、5V                                                                                  | 初期精度:最大0.05%、ドリフト:5ppm/°C                                        |

| LT1460                      | マイクロパワー・シリーズのリファレンス                                                                                   | 初期精度:最大0.075%、ドリフト:最大10ppm/°C                                    |

| LT1790                      | マイクロパワーSOT-23低ドロップアウト・リファレンス・ファミリー                                                                    | 初期精度:最大0.05%、ドリフト:最大10ppm/°C                                     |

| LTC2400                     | 24ビット、No Latency ΔΣ ADC、SO-8                                                                          | ノイズ:0.3ppm、INL:4ppm、全未調整誤差:10ppm、200μA                           |

| LTC2410                     | 24ビット、No Latency ΔΣ ADC、差動入力付き                                                                        | ノイズ:0.8μV <sub>RMS</sub> 、INL:2ppm                               |

| LTC2411/LTC2411-1           | 24ビット、No Latency ΔΣ ADC、差動入力付き、MSOP                                                                   | ノイズ:1.45μV <sub>RMS</sub> 、INL:4ppm、<br>同時50Hz/60Hz除去(LTC2411-1) |

| LTC2413                     | 24ビット、No Latency ΔΣ ADC、差動入力付き                                                                        | 同時50Hz/60Hz除去、ノイズ:800nV <sub>RMS</sub>                           |

| LTC2440                     | 高速、低ノイズ、24ビット ΔΣ ADC                                                                                  | 3.5kHz出力レート、ノイズ:200nV、24.6 ENOB                                  |

| LTC2442                     | 内蔵アンプ付き24ビット高速4チャネル/2チャネル ΔΣ ADC                                                                      | 出力レート:8kHz、ノイズ:220nV、同時50/60Hz除去                                 |

| LTC2449                     | 24ビット高速8チャネル/16チャネル ΔΣ ADC                                                                            | 出力レート:8kHz、ノイズ:200nV、同時50/60Hz除去                                 |

| LTC2480/LTC2482/<br>LTC2484 | 16ビット/24ビット ΔΣ ADC、Easy Drive入力付き、<br>600nVノイズ、プログラム可能な利得、および温度センサ                                    | 16ビットと24ビットのバージョンはピン互換                                           |

| LTC2481/LTC2483/<br>LTC2485 | $16$ ビット/ $24$ ビット $\Delta\Sigma$ ADC、Easy Drive入力付き、 $600$ nVノイズ、 $I^2$ Cインタフェース、プログラム可能な利得、および温度センサ | 16ビットと24ビットのバージョンはピン互換                                           |

| LTC2492                     | 2チャネル、14チャネル24ビット ΔΣ ADC、<br>Easy Drive入力と温度センサ付き                                                     | LTC2488とピン互換                                                     |

| LTC2496/LTC2498             | 16チャネル/8チャネル、16ビット/24ビット ΔΣ ADC、<br>Easy Drive入力とSPIインタフェース付き                                         | LTC2492とタイミングが互換                                                 |

| LTC2449                     | 高速16入力 ΔΣ ADC                                                                                         | 出力レート:8kHz、可変速度分解能                                               |