# 遅延クロック付きSPI用 3.75 kV, 6CH, SPIsolator デジタル・アイソレータ

ータシート

ADuM3150

#### 特長

遅延クロックモードで最大40 MHzのSPIクロック速度をサポ

4線式で最大17 MHzのSPIクロック速度をサポート 4つの高速、低伝搬遅延のSPI信号絶縁チャンネル 2つの250kbpsデータ・チャンネル 遅延補償クロック・ライン

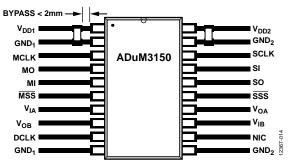

沿面距離5.1 mmの20ピンSSOPパッケージを採用

高温動作:~125°C

高コモン・モード過渡電圧耐性:>25 kV/μs

安全性と規制の認可

UL 1577に基づいたUL規格の認定(申請中)

3750 V rmsで 1 分間

CSA 部品承認通告 #5A(申請中)

VDE適合性認定(申請中)

DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12

$V_{IORM} = 560 \text{ V peak}$

#### アプリケーション

工業用プログラマブル・ロジック・コントローラ(PLC) センサー・アイソレーション

#### 概要

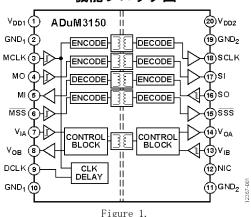

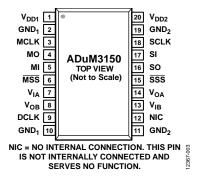

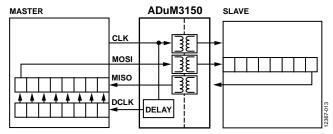

ADuM31501 は絶縁型シリアル・ペリフェラル・インターフェ ース(SPI)用に最適化された 6チャンネル SPIsolator™ デジ タル・アイソレータ です。アナログ・デバイセズ社の iCoup ler®チップ・スケール・トランス技術に基づき、CLK、 MO/S I、MI/SO、SSのSPIバス信号の伝搬遅延を小さくできるの で、最大17 MHzまでのSPIクロック・レートまでサポートして います。これらのチャンネルはSPI用にタイミングを最適化し ており、伝搬遅延14 ns、ジッタ1 nsで動作します。

アイソレータADuM3150は、別用途向けに2つの独立した低デー タ・レートの絶縁チャンネル(各方向に1チャンネル)も内蔵 しています。低速チャンネルのデータはジッタ2.5 μsで、デ ータ・レート250 kbpsが可能なようにサンプリングされ、シ リアル伝送されます。

ADuM3150には、このデバイスのマスター側に遅延クロック出 力があります。この出力は40MHzのクロック性能に対応するた

#### 機能ブロック図

めにマスターのもう1つのクロック動作ポートとともに使用 できます。詳細については、遅延クロックセクションを参照 してください。表 1. 関連製品

| 製品       | 説明                              |

|----------|---------------------------------|

| ADuM3151 | 3.75 kV、マルチチャンネル SPI アイソレ<br>ータ |

| ADuM3152 | 3.75 kV、マルチチャンネル SPI アイソレ<br>ータ |

| ADuM3153 | 3.75 kV、マルチチャンネル SPI アイソレ<br>ータ |

1米国特許番号5,952,849、6,873,065、6,262,600、7,075,329により保護されています。その他の特許は申請中です。

アナログ・デバイヤズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用に ステン・ハイ・とれば、提供する情報が正確に信頼できるものであることを例じていますが、その情報の利用に関じて、あるいは利用に よって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナダ・デバイセズ社の特許または特許の権利 の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標 は、各社の所有に属します。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

@2015 s s Analog Devices, Inc. All rights reserved.

Rev. 0

# データシートData Sh

## ADuM3150

eet

## 目次

| 特長1                                                    |

|--------------------------------------------------------|

| アプリケーション1                                              |

| 機能ブロック図1                                               |

| 概要1                                                    |

| 改訂履歴2                                                  |

| 仕様3                                                    |

| 電気的特性-5 V動作3                                           |

| 電気的特性-3.3 V動作5                                         |

| 電気的特性-ミックス電源5 V/3.3 V動作7                               |

| 電気的特性-ミックス電源3.3 V/5 V動作                                |

| パッケージ特性11                                              |

| 適用規格11                                                 |

| 絶縁および安全性関連の仕様11                                        |

| DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12絶縁特性1<br>2 |

| 推奨動作条件12                                               |

| 絶対最大定格               | 13 |

|----------------------|----|

| ESDに関する注意            | 13 |

| ピン配置およびピン機能説明        | 14 |

| 代表的な性能特性             | 15 |

| アプリケーション情報           | 16 |

| はじめに                 | 16 |

| プリント回路基板 (PCB)のレイアウト | 17 |

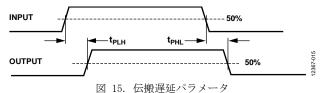

| 伝搬遅延に関連するパラメータ       | 18 |

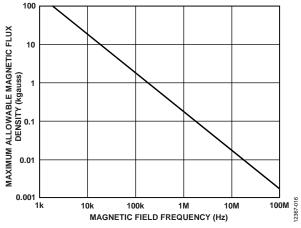

| DCの再現と磁界耐性           | 18 |

| 消費電力                 | 19 |

| 絶縁寿命                 | 19 |

| 外形寸法                 | 21 |

| オーダー・ガイド             | 21 |

#### 改訂履歴

7/14-Revision 0:初版

### 仕様

#### 電気的特性-5 V動作

すべてのtyp仕様は、 $T_A=25^\circ$  C、  $V_{DD1}=V_{DD2}=5V$  での値です。 特に指定のない限り、最小/最大仕様は全ての推奨動作範囲に適用されます: $4.5~V \le V_{DD1} \le 5.5~V$ 、  $4.5~V \le V_{DD2} \le 5.5~V$ 、  $-40^\circ$  C  $\le T_A \le +125^\circ$  C。特に指定のない限り、スイッチング仕様は $C_L=15~pF$  と CMOS信号レベルでテストされます。

#### 表 2. スイッチング仕様

|                                         |                             |      | A Grad | е   |      | B Grad | е   |      |                                      |

|-----------------------------------------|-----------------------------|------|--------|-----|------|--------|-----|------|--------------------------------------|

| Parameter                               | Symbol                      | Min  | Тур    | Max | Min  | Тур    | Max | Unit | Test Conditions/Comments             |

| MCLK, MO, SO                            |                             |      |        |     |      |        |     |      |                                      |

| SPI Clock Rate                          | $SPI_{MCLK}$                |      |        | 10  |      |        | 17  | MHz  |                                      |

| Data Rate Fast (MO, SO)                 | DR <sub>FAST</sub>          |      |        | 40  |      |        | 40  | Mbps | Within PWD limit                     |

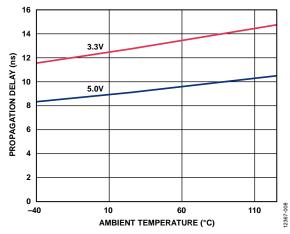

| Propagation Delay                       | $t_{PHL}$ , $t_{PLH}$       |      |        | 25  |      | 12     | 14  | ns   | 50% input to 50% output              |

| Pulse Width                             | PW                          | 12.5 |        |     | 12.5 |        |     | ns   | Within PWD limit                     |

| Pulse Width Distortion                  | PWD                         |      |        | 2   |      |        | 2   | ns   | $ t_{PLH} - t_{PHL} $                |

| Codirectional Channel Match             | t <sub>PSKCD</sub>          |      |        | 2   |      |        | 2   | ns   |                                      |

| Jitter, High Speed                      | $J_{\scriptscriptstyle HS}$ |      | 1      |     |      | 1      |     | ns   |                                      |

| MSS <sup>*</sup>                        |                             |      |        |     |      |        |     |      |                                      |

| Data Rate Fast                          | $DR_{FAST}$                 |      |        | 40  |      |        | 40  | Mbps | Within PWD limit                     |

| Propagation Delay                       | $t_{PHL}$ , $t_{PLH}$       |      | 21     | 25  |      | 21     | 25  | ns   | 50% input to 50% output              |

| Pulse Width                             | PW                          | 12.5 |        |     | 12.5 |        |     | ns   | Within PWD limit                     |

| Pulse Width Distortion                  | PWD                         |      |        | 2   |      |        | 2   | ns   | t <sub>PLH</sub> - t <sub>PHL</sub>  |

| Setup Time. <sup>2</sup>                | MSS SETUP                   | 1.5  |        |     | 10   |        |     | ns   |                                      |

| Jitter, High Speed                      | $J_{\scriptscriptstyle HS}$ |      | 1      |     |      | 1      |     | ns   |                                      |

| DCLK                                    |                             |      |        |     |      |        |     |      |                                      |

| Data Rate                               |                             |      |        | 40  |      |        | 40  | MHz  |                                      |

| Propagation Delay                       | $t_{PHL}$ , $t_{PLH}$       |      |        | 50  |      |        | 35  | ns   | $t_{PMCLK} + t_{PSO} + 3 \text{ ns}$ |

| Pulse Width Distortion                  | PWD                         |      |        | 3   |      |        | 3   | ns   | t <sub>PLH</sub> - t <sub>PHL</sub>  |

| Pulse Width                             | PW                          | 12   |        |     | 12   |        |     | ns   | Within PWD limit                     |

| Clock Delay Error                       | DCLK <sub>ERR</sub>         | 0    | 4.5    | 12  | 1    | 5.5    | 12  | ns   | $t_{PDCLK} - (t_{PMCLK} + t_{PSO})$  |

| Jitter                                  | $J_{	ext{DCLK}}$            |      | 1      |     |      | 1      |     | ns   |                                      |

| $V_{IA}$ , $V_{IB}$                     |                             |      |        |     |      |        |     |      |                                      |

| Data Rate Slow                          | $DR_{SLOW}$                 |      |        | 250 |      |        | 250 | kbps | Within PWD limit                     |

| Propagation Delay                       | $t_{PHL}$ , $t_{PLH}$       | 0. 1 |        | 2.6 | 0. 1 |        | 2.6 | μs   | 50% input to 50% output              |

| Pulse Width                             | PW                          | 4    |        |     | 4    |        |     | μs   | Within PWD limit                     |

| Jitter, Low Speed                       | $J_{\scriptscriptstyle LS}$ |      |        | 2.5 |      |        | 2.5 | μs   |                                      |

| V <sub>Ix</sub> .3 Minimum Input Skew.4 | t <sub>VIx SKEW</sub>       | 10   |        |     | 10   |        |     | ns   |                                      |

<sup>1</sup> 同方向チャンネル間マッチングは、アイソレーション・バリアの同じ側に入力を持つ任意の2つのチャンネル間の伝搬遅延差の絶対値です。

<sup>&</sup>lt;sup>2</sup> MSS信号にはすべてのグレードでグリッジ・フィルタが入っています・しかしBグレード品では、その他の高速信号にはグリッジ・フィルタが入っていません。MSSが確実に他の高速信号より先に出力に到達するように、速度グレードによって時間は異なりますが、MSSを競い合う信号より前に設定してください。

$<sup>^3</sup>$   $V_{Ix}$  =  $V_{IA}$   $\nearrow l \ddagger$   $V_{IB}$ .

$<sup>^4</sup>$  内部の非同期クロック(ユーザーは使用できません)が低速信号をサンプリングします。同方向チャンネルのエッジ・シーケンスがエンド・アプリケーションで重要な場合、出力に正しい順番あるいは同時に到達する事を保証するために、先行パルスは後発パルスより少なくても $1\ {

m tv_{IX}\ SKEW}$ 時間前でなければなりません。

表 3.全グレード共通<sup>1, 2, 3</sup>

| Parameter                                                                   | Symbol                     | Min            | Тур        | Max            | Unit    | Test Conditions/Comments                                                                        |

|-----------------------------------------------------------------------------|----------------------------|----------------|------------|----------------|---------|-------------------------------------------------------------------------------------------------|

| SUPPLY CURRENT                                                              |                            |                |            |                |         |                                                                                                 |

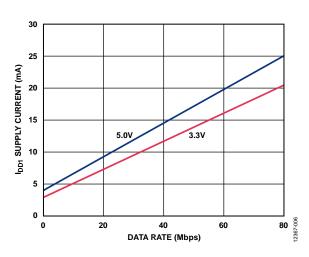

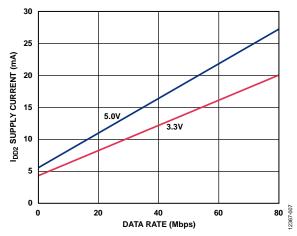

| 1 MHz, A Grade and B Grade                                                  | $I_{	ext{DD1}}$            |                | 5          | 6. 5           | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                          |

|                                                                             | $I_{	ext{DD2}}$            |                | 6. 2       | 8.5            | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                          |

| 17 MHz, B Grade                                                             | $I_{	ext{DD1}}$            |                | 15         | 18             | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                         |

|                                                                             | $I_{	ext{DD2}}$            |                | 13. 5      | 16             | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                         |

| DC SPECIFICATIONS                                                           |                            |                |            |                |         |                                                                                                 |

| MCKL, $\overline{\text{MSS}}$ , MO, SO, $V_{\text{IA}}$ , $V_{\text{IB}}$   |                            |                |            |                |         |                                                                                                 |

| Input Threshold                                                             |                            |                |            |                |         |                                                                                                 |

| Logic High                                                                  | $V_{\mathrm{IH}}$          | $0.7 \times V$ |            |                | V       |                                                                                                 |

|                                                                             |                            | DDx            |            |                |         |                                                                                                 |

| Logic Low                                                                   | $V_{IL}$                   |                |            | $0.3 \times V$ | V       |                                                                                                 |

| T TI                                                                        | **                         |                | 500        | DDx            | 17      |                                                                                                 |

| Input Hysteresis                                                            | V <sub>IHYST</sub>         |                | 500        |                | mV      |                                                                                                 |

| Input Current per Channel                                                   | $I_{I}$                    | -1             | +0. 0<br>1 | +1             | μА      | $0 \text{ V} \leq V_{\text{INPUT}} \leq V_{\text{DDx}}$                                         |

| SCLK, $\overline{\rm SSS}$ , MI, SI, ${\rm V_{OA}}$ , ${\rm V_{OB}}$ , DCLK |                            |                | 1          |                |         |                                                                                                 |

| Output Voltages                                                             |                            |                |            |                |         |                                                                                                 |

| Logic High                                                                  | $V_{OH}$                   | $V_{DDx} - 0.$ | 5. 0       |                | V       | $I_{OUTPUT} = -20 \mu A$ , $V_{INPUT} = V_{IH}$                                                 |

| Bogro mign                                                                  | OH                         | 1              | 0.0        |                | ,       | TOUTPUT TO party INPUT IN                                                                       |

|                                                                             |                            | $V_{DDx} - 0.$ | 4.8        |                | V       | $I_{OUTPUT} = -4 \text{ mA}, V_{INPUT} = V_{IH}$                                                |

| Logic Low                                                                   | $V_{OL}$                   |                | 0.0        | 0.1            | V       | $I_{OUTPUT} = 20 \mu A, V_{INPUT} = V_{IL}$                                                     |

|                                                                             |                            |                | 0.2        | 0.4            | V       | $I_{OUTPUT} = 4$ mA, $V_{INPUT} = V_{IL}$                                                       |

| $V_{\text{DD1}}$ , $V_{\text{DD2}}$ Undervoltage Lockout                    | UVLO                       |                | 2.6        |                | V       |                                                                                                 |

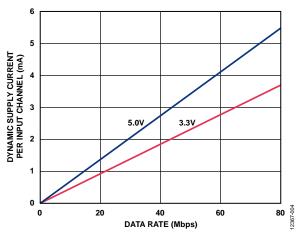

| Supply Current for High Speed Channel                                       |                            |                |            |                |         |                                                                                                 |

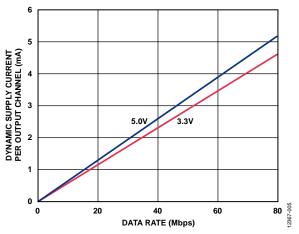

| Dynamic Input                                                               | $I_{\text{DDI}(D)}$        |                | 0.09       |                | mA/Mbps |                                                                                                 |

| Dynamic Output                                                              | $I_{\text{DDO}(D)}$        |                | 0.02       |                | mA/Mbps |                                                                                                 |

| Supply Current for All Low Speed Channels                                   |                            |                |            |                |         |                                                                                                 |

| Quiescent Input                                                             | $I_{\text{DDI}(Q)}$        |                | 4.0        |                | mA      |                                                                                                 |

| Quiescent Output                                                            | $I_{\text{DDO}(\text{Q})}$ |                | 6.4        |                | mA      |                                                                                                 |

| AC SPECIFICATIONS                                                           |                            |                |            |                |         |                                                                                                 |

| Output Rise/Fall Time                                                       | $t_{R}/t_{F}$              |                | 2.5        |                | ns      | 10% to 90%                                                                                      |

| Common-Mode Transient Immunity. <sup>4</sup>                                | CM                         | 25             | 35         |                | kV/μs   | $V_{\text{INPUT}} = V_{\text{DDx}}, V_{\text{CM}} = 1000 \text{ V}$ Transient magnitude = 800 V |

$<sup>^{1}</sup>$   $V_{DDx} = V_{DD1}$  又は  $\overline{V_{DD2}}$  。  $^{2}$   $V_{INPUT}$ は MCLK、  $\overline{MSS}$  ピン、  $\overline{MO}$  ピン、  $\overline{SO}$  ピン、  $\overline{V_{IA}}$  ピン又は  $\overline{V_{IB}}$  ピンのいずれかの入力電圧です。

$<sup>^3</sup>$  IOUTPUTはSCLKピン、 DCLKピン、 $\overline{\rm SSS}$ ピン、 MIピン、 SIピン、 VOAピン 又は VOBのいずれかの出力電流です。

$<sup>^4</sup>$  |CM| は出力電圧が $V_{OH}$  と  $V_{OL}$ の 制限値内を維持している間に維持できるコモン・モード電圧の最大スルーレートです。コモン・モード電圧スルーレ ートは、立ち上がりと立ち下がりの両コモン・モード電圧エッジに適用されます。

#### 電気的特性-3.3 V動作

すべてのtyp仕様は、 $T_A=25^\circ$  C、  $V_{DD1}=V_{DD2}=3.3$  V での値です。 特に指定のない限り、最小/最大仕様はすべての推奨動作範囲に適用されます: 3.0 V  $\leq$   $V_{DD1} \leq$  3.6 V、 3.0 V  $\leq$   $V_{DD2} \leq$  3.6 V、  $-40^\circ$  C  $\leq$   $T_A \leq$   $+125^\circ$  C。特に指定のない限り、スイッチング仕様は $C_L=15$  pF  $\geq$  CMOS信号レベルでテストされます。

#### 表 4. スイッチング仕様

| <u>ж. п., г.) / т. м.</u>                    |                               |     | A Grad | e   |     | B Grad | e    |      |                                      |

|----------------------------------------------|-------------------------------|-----|--------|-----|-----|--------|------|------|--------------------------------------|

| Parameter                                    | Symbol                        | Min | Тур    | Max | Min | Тур    | Max  | Unit | Test Conditions/Comments             |

| MCLK, MO, SO                                 |                               |     |        |     |     |        |      |      |                                      |

| SPI Clock Rate                               | $SPI_{MCLK}$                  |     |        | 8.3 |     |        | 12.5 | MHz  |                                      |

| Data Rate Fast (MO, SO)                      | $DR_{FAST}$                   |     |        | 40  |     |        | 40   | Mbps | Within PWD limit                     |

| Propagation Delay                            | $t_{PHL}$ , $t_{PLH}$         |     |        | 30  |     |        | 20   | ns   | 50% input to 50% output              |

| Pulse Width                                  | PW                            | 12. |        |     | 12. |        |      | ns   | Within PWD limit                     |

|                                              |                               | 5   |        |     | 5   |        |      |      |                                      |

| Pulse Width Distortion                       | PWD                           |     |        | 3   |     |        | 3    | ns   | $ t_{PLH} - t_{PHL} $                |

| Codirectional Channel Matchi                 | $t_{PSKCD}$                   |     |        | 3   |     |        | 3    | ns   |                                      |

| ng. <sup>1</sup>                             |                               |     |        |     |     |        |      |      |                                      |

| Jitter, High Speed                           | J <sub>HS</sub>               |     | 1      |     |     | 1      |      | ns   |                                      |

| MSS                                          |                               |     |        |     |     |        |      |      |                                      |

| Data Rate Fast                               | $DR_{FAST}$                   |     |        | 40  |     |        | 40   | Mbps | Within PWD limit                     |

| Propagation Delay                            | $t_{PHL}$ , $t_{PLH}$         |     |        | 30  |     |        | 30   | ns   | 50% input to 50% output              |

| Pulse Width                                  | PW                            | 12. |        |     | 12. |        |      | ns   | Within PWD limit                     |

|                                              |                               | 5   |        |     | 5   |        |      |      |                                      |

| Pulse Width Distortion                       | PWD                           |     |        | 3   |     |        | 3    | ns   | $ t_{PLH} - t_{PHL} $                |

| Setup Time. <sup>2</sup>                     | MSS SETUP                     | 1.5 |        |     | 10  |        |      | ns   |                                      |

| Jitter, High Speed                           | $J_{\scriptscriptstyle HS}$   |     | 1      |     |     | 1      |      | ns   |                                      |

| DCLK                                         |                               |     |        |     |     |        |      |      |                                      |

| Data Rate                                    |                               |     |        | 40  |     |        | 40   | MHz  |                                      |

| Propagation Delay                            | $t_{PHL}$ , $t_{PLH}$         |     |        | 60  |     |        | 40   | ns   | $t_{PMCLK} + t_{PSO} + 3 \text{ ns}$ |

| Pulse Width Distortion                       | PWD                           |     |        | 3   |     |        | 3    | ns   | t <sub>PLH</sub> - t <sub>PHL</sub>  |

| Pulse Width                                  | PW                            | 12  |        |     | 12  |        |      | ns   | Within PWD limit                     |

| Clock Delay Error                            | $DCLK_{ERR}$                  | -4  | +2.    | +9  | -3  | +2.    | +8   | ns   | $t_{PDCLK} - (t_{PMCLK} + t_{PSO})$  |

|                                              |                               |     | 4      |     |     | 5      |      |      |                                      |

| Jitter                                       | $J_{	ext{DCLK}}$              |     | 1      |     |     | 1      |      | ns   |                                      |

| $V_{IA}$ , $V_{IB}$                          |                               |     |        |     |     |        |      |      |                                      |

| Data Rate Slow                               | $\mathrm{DR}_{\mathrm{SLOW}}$ |     |        | 250 |     |        | 250  | kbps | Within PWD limit                     |

| Propagation Delay                            | $t_{PHL}$ , $t_{PLH}$         | 0.1 |        | 2.6 | 0.1 |        | 2.6  | μs   | 50% input to 50% output              |

| Pulse Width                                  | PW                            | 4   |        |     | 4   |        |      | μs   | Within PWD limit                     |

| Jitter, Low Speed                            | $J_{\scriptscriptstyle LS}$   |     |        | 2.5 |     |        | 2.5  | μs   |                                      |

| ${\rm V_{Ix}}^{-3}$ Minimum Input Skew. $^4$ | t <sub>VIx SKEW</sub>         | 10  |        |     | 10  |        |      | ns   |                                      |

<sup>&</sup>lt;sup>1</sup> 同方向チャンネル間マッチングは、アイソレーション・バリアの同じ側に入力を持つ任意の2つのチャンネル間の伝搬遅延差の絶対値です。

<sup>2</sup>MSS 信号はすべてのグレードにグリッジ・フィルタが入っています。しかしBグレード品では、その他の高速信号にははグリッジ・フィルタが入っていません。MSSが確実に他の高速信号より先に出力に到達するように、速度グレードによって時間は異なりますがMSSを競い合う信号の前に設定してください。

$<sup>^3</sup>$   $V_{\rm Ix}$  =  $V_{\rm IA}$   $\not\subset$   $\not \sim$   $V_{\rm IB}.$

<sup>&</sup>lt;sup>4</sup> 内部の非同期クロック(ユーザーは使用できません)が低速信号をサンプリングします。同方向チャンネルのエッジ・シーケンスがエンド・アプリケーションで重要な場合、出力に正しい順番あるいは同時に到達する事を保証するために、先行パルスは後発パルスより少なくても1 t<sub>VIx SKEW</sub>時間前でなければなりません。

#### 表 5. 全グレード共通1, 2, 3

| Parameter                                                                   | Symbol                      | Min              | Тур        | Max            | Unit    | Test Conditions/Comments                                                                        |

|-----------------------------------------------------------------------------|-----------------------------|------------------|------------|----------------|---------|-------------------------------------------------------------------------------------------------|

| SUPPLY CURRENT                                                              |                             |                  |            |                |         |                                                                                                 |

| 1 MHz, A Grade and B Grade                                                  | $I_{	ext{DD1}}$             |                  | 3. 4       | 4.5            | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                          |

|                                                                             | $I_{	ext{DD2}}$             |                  | 4. 7       | 6.0            | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                          |

| 17 MHz, B Grade                                                             | $I_{	ext{DD1}}$             |                  | 9.5        | 15             | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                         |

|                                                                             | $I_{	ext{DD2}}$             |                  | 8          | 12             | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                         |

| DC SPECIFICATIONS                                                           |                             |                  |            |                |         |                                                                                                 |

| MCKL, $\overline{\text{MSS}}$ , MO, SO, $V_{\text{IA}}$ , $V_{\text{IB}}$   |                             |                  |            |                |         |                                                                                                 |

| Input Threshold                                                             |                             |                  |            |                |         |                                                                                                 |

| Logic High                                                                  | $V_{IH}$                    | $0.7 \times V$   |            |                | V       |                                                                                                 |

|                                                                             |                             | DDx              |            |                |         |                                                                                                 |

| Logic Low                                                                   | $V_{\mathrm{IL}}$           |                  |            | $0.3 \times V$ | V       |                                                                                                 |

|                                                                             |                             |                  |            | DDx            |         |                                                                                                 |

| Input Hysteresis                                                            | $V_{IHYST}$                 |                  | 500        |                | mV      |                                                                                                 |

| Input Current per Channel                                                   | II                          | -1               | +0. 0<br>1 | +1             | μА      | $0 \text{ V} \leq V_{\text{INPUT}} \leq V_{\text{DDx}}$                                         |

| SCLK, $\overline{\rm SSS}$ , MI, SI, ${\rm V_{OA}}$ , ${\rm V_{OB}}$ , DCLK |                             |                  |            |                |         |                                                                                                 |

| Output Voltages                                                             |                             |                  |            |                |         |                                                                                                 |

| Logic High                                                                  | $V_{OH}$                    | $V_{DDx} - 0.$ 1 | 5. 0       |                | V       | $I_{OUTPUT} = -20 \mu A$ , $V_{INPUT} = V_{IH}$                                                 |

|                                                                             |                             | $V_{DDx} - 0.$   | 4.8        |                | V       | $I_{OUTPUT} = -4 \text{ mA}, V_{INPUT} = V_{IH}$                                                |

| Logic Low                                                                   | $V_{OL}$                    |                  | 0.0        | 0.1            | V       | $I_{OUTPUT}$ = 20 $\mu$ A, $V_{INPUT}$ = $V_{IL}$                                               |

|                                                                             |                             |                  | 0.2        | 0.4            | V       | $I_{OUTPUT}$ = 4 mA, $V_{INPUT}$ = $V_{IL}$                                                     |

| $V_{\text{DD1}}$ , $V_{\text{DD2}}$ Undervoltage Lockout                    | UVLO                        |                  | 2.6        |                | V       |                                                                                                 |

| Supply Current for High Speed Channel                                       |                             |                  |            |                |         |                                                                                                 |

| Dynamic Input                                                               | $I_{\text{DDI}(D)}$         |                  | 0.09       |                | mA/Mbps |                                                                                                 |

| Dynamic Output                                                              | $I_{\text{DDO}(D)}$         |                  | 0.02       |                | mA/Mbps |                                                                                                 |

| Supply Current for All Low Speed Channels                                   |                             |                  |            |                |         |                                                                                                 |

| Quiescent Input                                                             | $I_{\text{DDI}(\text{Q})}$  |                  | 4. 5       |                | mA      |                                                                                                 |

| Quiescent Output                                                            | $I_{\text{DDO}(Q)}$         |                  | 5. 5       |                | mA      |                                                                                                 |

| AC SPECIFICATIONS                                                           |                             |                  |            |                |         |                                                                                                 |

| Output Rise/Fall Time                                                       | $t_{\text{R}}/t_{\text{F}}$ |                  | 2.5        |                | ns      | 10% to 90%                                                                                      |

| Common-Mode Transient Immunity.4                                            | CM                          | 25               | 35         |                | kV/μs   | $V_{\text{INPUT}} = V_{\text{DDx}}, V_{\text{CM}} = 1000 \text{ V}$ Transient magnitude = 800 V |

$<sup>^{1}</sup>$   $V_{DDx}$  =  $V_{DD1}$   $\nearrow l \ddagger V_{DD2}$

$<sup>^2</sup>$   $V_{INPUT}$ は MCLK、  $\overline{\rm MSS}$ ピン、 MOピン、 SOピン、  $V_{IA}$ ピン又は  $V_{IB}$ ピンのいずれかの入力電圧です。

$<sup>^3</sup>$  IOUTPUTはSCLKピン、 DCLKピン、 $\overline{\rm SSS}$ 、 MIピン、 SIピン、 VOAピン 又は VOBのいずれかの出力電流です。

$<sup>^4</sup>$  |CM| は出力電圧が $V_{OH}$  と  $V_{OL}$ の 制限値内を維持している間に維持できるコモン・モード電圧の最大スルーレートです。コモン・モード電圧スルーレートは、立ち上がりと立ち下がりの両コモン・モード電圧エッジに適用されます。

#### 電気的特性-ミックス電源5 V/3.3 V動作

すべてのtyp仕様は、 $T_A=25^\circ$  C、  $V_{DD1}=5$ V、 $V_{DD2}=3.3$  V での値です。 特に指定のない限り、最小/最大仕様はすべての推奨動作範囲に適用されます: 4.5 V  $\leq$   $V_{DD1}\leq5.5$  V、 3.0 V  $\leq$   $V_{DD2}\leq3.6$  V、  $-40^\circ$  C  $\leq$   $T_A\leq+125^\circ$  C。特に指定のない限り、スイッチング仕様は $C_L=15$  pF と CMOS信号レベルでテストされます。

#### 表 6. スイッチング仕様

|                                                                |                                    |          | A Grad | le   |          | B Grad | е    |      |                                      |

|----------------------------------------------------------------|------------------------------------|----------|--------|------|----------|--------|------|------|--------------------------------------|

| Parameter                                                      | Symbol                             | Min      | Тур    | Max  | Min      | Тур    | Max  | Unit | Test Conditions/Comments             |

| MCLK, MO, SO                                                   |                                    |          |        |      |          |        |      |      |                                      |

| SPI Clock Rate                                                 | $SPI_{MCLK}$                       |          |        | 9.2  |          |        | 15.6 | MHz  |                                      |

| Data Rate Fast (MO, SO)                                        | $DR_{FAST}$                        |          |        | 40   |          |        | 40   | Mbps | Within PWD limit                     |

| Propagation Delay                                              | t <sub>PHL</sub> , t <sub>PL</sub> |          |        | 27   |          |        | 16   | ns   | 50% input to 50% output              |

| Pulse Width                                                    | PW                                 | 12.<br>5 |        |      | 12.<br>5 |        |      | ns   | Within PWD limit                     |

| Pulse Width Distortion                                         | PWD                                |          |        | 3    |          |        | 2    | ns   | $ t_{PLH} - t_{PHL} $                |

| Codirectional Channel Matchin g.1                              | t <sub>PSKCD</sub>                 |          |        | 2    |          |        | 2    | ns   |                                      |

| Jitter, High Speed                                             | $J_{\scriptscriptstyle HS}$        |          | 1      |      |          | 1      |      | ns   |                                      |

| MSS                                                            |                                    |          |        |      |          |        |      |      |                                      |

| Data Rate Fast                                                 | $\mathrm{DR}_{\mathrm{FAST}}$      |          |        | 40   |          |        | 40   | Mbps | Within PWD limit                     |

| Propagation Delay                                              | $t_{PHL}$ , $t_{PL}$               |          |        | 27   |          |        | 26   | ns   | 50% input to 50% output              |

| Pulse Width                                                    | н<br>PW                            | 12.<br>5 |        |      | 12.<br>5 |        |      | ns   | Within PWD limit                     |

| Pulse Width Distortion                                         | PWD                                | υ        |        | 2    | υ        |        | 2    | ns   | $ t_{PLH} - t_{PHL} $                |

| Setup Time. <sup>2</sup>                                       | MSS SETUP                          | 1.5      |        | 2    | 10       |        | 2    | ns   | CPLH CPHL                            |

| Jitter, High Speed                                             | J <sub>HS</sub>                    | 1.0      | 1      |      | 10       | 1      |      | ns   |                                      |

| DCLK                                                           | 343                                |          | -      |      |          |        |      | 110  |                                      |

| Data Rate                                                      |                                    |          |        | 40   |          |        | 40   | MHz  |                                      |

| Propagation Delay                                              | t <sub>PHL</sub> , t <sub>PL</sub> |          |        | 50   |          |        | 35   | ns   | $t_{PMCLK} + t_{PSO} + 3 \text{ ns}$ |

| Tropagation Dota,                                              | H H                                |          |        |      |          |        |      | 110  | OT MOLIK OT 50                       |

| Pulse Width Distortion                                         | PWD                                |          |        | 3    |          |        | 3    | ns   | t <sub>PLH</sub> - t <sub>PHL</sub>  |

| Pulse Width                                                    | PW                                 | 12       |        |      | 12       |        |      | ns   | Within PWD limit                     |

| Clock Delay Error                                              | DCLK <sub>ERR</sub>                | -5       | 0      | +7   | -5       | +1.    | +9   | ns   | $t_{PDCLK} - (t_{PMCLK} + t_{PSO})$  |

|                                                                |                                    |          |        |      |          | 2      |      |      |                                      |

| Jitter                                                         | J <sub>DCLK</sub>                  |          | 1      |      |          | 1      |      | ns   |                                      |

| $V_{IA}$ , $V_{IB}$                                            |                                    |          |        |      |          |        |      |      |                                      |

| Data Rate Slow                                                 | $DR_{SLOW}$                        |          |        | 250  |          |        | 250  | kbps | Within PWD limit                     |

| Propagation Delay                                              | $t_{PHL}$ , $t_{PL}$               | 0. 1     |        | 2.6  | 0. 1     |        | 2.6  | μs   | 50% input to 50% output              |

| D 1 W:1/1                                                      | H                                  | ١,       |        |      | ١,       |        |      |      | m.··i. Dmb i                         |

| Pulse Width                                                    | PW                                 | 4        |        | 0.5  | 4        |        | 0.5  | μs   | Within PWD limit                     |

| Jitter, Low Speed                                              | JLS                                | 1.0      |        | 2. 5 | 1.0      |        | 2. 5 | μs   |                                      |

| V <sub>Ix-</sub> <sup>3</sup> Minimum Input Skew- <sup>4</sup> | t <sub>VIx</sub> SKEW              | 10       |        |      | 10       |        |      | ns   |                                      |

<sup>&</sup>lt;sup>1</sup> 同方向チャンネル間マッチングは、アイソレーション・バリアの同じ側に入力を持つ任意の2つのチャンネル間の伝搬遅延差の絶対値です。

<sup>2</sup>MSS信号はすべてのグレードでグリッジ・フィルタが入っています。、しかしBグレード品では、その他の高速信号にはグリッジ・フィルタが入っていません。MSSが確実に他の高速信号より先に出力に到達するように、速度グレードによって時間は異なりますが、MSSを競い合う信号の前に設定してください。

$<sup>^{3}</sup>$   $V_{Ix} = V_{IA} \times V_{I} \times V_{IB}$ .

<sup>&</sup>lt;sup>4</sup> 内部の非同期クロック(ユーザーは使用できません)が低速信号をサンプリングします。同方向チャンネルのエッジ・シーケンスがエンド・アプリケーションで重要な場合、出力に正しい順番あるいは同時に到達する事を保証するために、先行パルスは後発パルスより少なくても1 tvix skem時間前でなければなりません。

#### 表 7. 全グレード共通1, 2, 3

| Parameter                                                                        | Symbol            | Min                        | Тур        | Max            | Unit    | Test Conditions/Comments                                                                           |

|----------------------------------------------------------------------------------|-------------------|----------------------------|------------|----------------|---------|----------------------------------------------------------------------------------------------------|

| SUPPLY CURRENT                                                                   |                   |                            |            |                |         |                                                                                                    |

| 1 MHz, A Grade and B Grade                                                       | $I_{	ext{DD1}}$   |                            | 5. 3       | 6.2            | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                             |

|                                                                                  | $I_{	ext{DD2}}$   |                            | 4. 9       | 6              | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                             |

| 17 MHz, B Grade                                                                  | $I_{	ext{DD1}}$   |                            | 16         | 18             | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                            |

|                                                                                  | $I_{	ext{DD2}}$   |                            | 10         | 12             | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                            |

| DC SPECIFICATIONS                                                                |                   |                            |            |                |         |                                                                                                    |

| MCKL, $\overline{\text{MSS}}$ , MO, SO, $V_{\text{IA}}$ , $V_{\text{IB}}$        |                   |                            |            |                |         |                                                                                                    |

| Input Threshold                                                                  |                   |                            |            |                |         |                                                                                                    |

| Logic High                                                                       | $V_{\mathrm{IH}}$ | $0.7 \times V$             |            |                | V       |                                                                                                    |

|                                                                                  |                   | $\mathrm{DD}_{\mathrm{X}}$ |            |                |         |                                                                                                    |

| Logic Low                                                                        | $V_{\rm IL}$      |                            |            | $0.3 \times V$ | V       |                                                                                                    |

|                                                                                  |                   |                            |            | DDx            |         |                                                                                                    |

| Input Hysteresis                                                                 | $V_{IHYST}$       |                            | 500        |                | mV      |                                                                                                    |

| Input Current per Channel                                                        | $I_{I}$           | -1                         | +0. 0<br>1 | +1             | μA      | $0 \text{ V} \leq V_{\text{INPUT}} \leq V_{\text{DDx}}$                                            |

| SCLK, $\overline{\text{SSS}}$ , MI, SI, $V_{\text{OA}}$ , $V_{\text{OB}}$ , DCLK |                   |                            |            |                |         |                                                                                                    |

| Output Voltages                                                                  |                   |                            |            |                |         |                                                                                                    |

| Logic High                                                                       | $V_{OH}$          | $V_{DDx} - 0.$             | 5. 0       |                | V       | $I_{OUTPUT} = -20 \mu A$ , $V_{INPUT} = V_{IH}$                                                    |

|                                                                                  |                   | $V_{DDx} - 0.$             | 4.8        |                | V       | $I_{OUTPUT} = -4$ mA, $V_{INPUT} = V_{IH}$                                                         |

| Logic Low                                                                        | $V_{OL}$          |                            | 0.0        | 0.1            | V       | $I_{OUTPUT} = 20 \mu A, V_{INPUT} = V_{IL}$                                                        |

|                                                                                  |                   |                            | 0.2        | 0.4            | V       | $I_{OUTPUT} = 4$ mA, $V_{INPUT} = V_{IL}$                                                          |

| $V_{\text{DD1}}$ , $V_{\text{DD2}}$ Undervoltage Lockout                         | UVLO              |                            | 2.6        |                | V       |                                                                                                    |

| Supply Current for High Speed Channel                                            |                   |                            |            |                |         |                                                                                                    |

| Dynamic Input                                                                    | $I_{DDI(D)}$      |                            | 0.09       |                | mA/Mbps |                                                                                                    |

| Dynamic Output                                                                   | $I_{DDO(D)}$      |                            | 0.02       |                | mA/Mbps |                                                                                                    |

| Supply Current for All Low Speed Channels                                        |                   |                            |            |                |         |                                                                                                    |

| Quiescent Input                                                                  | $I_{DDI(Q)}$      |                            | 4.0        |                | mA      |                                                                                                    |

| Quiescent Output                                                                 | $I_{DDO(Q)}$      |                            | 4. 7       |                | mA      |                                                                                                    |

| AC SPECIFICATIONS                                                                |                   |                            |            |                |         |                                                                                                    |

| Output Rise/Fall Time                                                            | $t_{R}/t_{F}$     |                            | 2.5        |                | ns      | 10% to 90%                                                                                         |

| Common-Mode Transient Immunity.4                                                 | CM                | 25                         | 35         |                | kV/μs   | $V_{\text{INPUT}} = V_{\text{DDx}}, V_{\text{CM}} = 1000 \text{ V}$<br>Transient magnitude = 800 V |

$<sup>\</sup>frac{1}{2}$   $V_{INPUT}$ は MCLK、 MSSピン、 MOピン、 SOピン、  $V_{IA}$ ピン又は  $V_{IB}$ ピンのいずれかの入力電圧です。

$<sup>^3</sup>$   $I_{OUTPUT}$ はSCLKピン、 DCLKピン、  $\overline{SSS}$ ピン、 MIピン、 SIピン、  $V_{OA}$ ピン 又は  $V_{OB}$ のいずれかの出力電流です。

<sup>4 |</sup> CM| は出力電圧がV<sub>0H</sub> と V<sub>0L</sub>の 制限値内を維持している間に維持できるコモン・モード電圧の最大スルーレートです。コモン・モード電圧スルーレートは、立ち上がりと立ち下がりの両コモン・モード電圧エッジに適用されます。

#### 電気的特性-ミックス電源3.3 V/5 V動作

すべてのtyp仕様は、 $T_A=25^\circ$  C、  $V_{DD1}=3.3V$ 、  $V_{DD2}=5V$  での値です。 特に指定のない限り、最小/最大仕様は、全推奨動作範囲に適用されます:  $3.0~V \le V_{DD1} \le 3.6~V$ 、  $4.5~V \le V_{DD2} \le 5.5~V$ 、  $-40^\circ$  C  $\le T_A \le +125^\circ$  C。特に指定のない限り、スイッチング仕様は  $C_L=15~pF$  と CMOS信号レベルでテストされます。

#### 表 8. スイッチング仕様

|                                                                |                                    |          | A Grad | le  |          | B Grad | e    |      |                                      |

|----------------------------------------------------------------|------------------------------------|----------|--------|-----|----------|--------|------|------|--------------------------------------|

| Parameter                                                      | Symbol                             | Min      | Тур    | Max | Min      | Тур    | Max  | Unit | Test Conditions/Comments             |

| MCLK, MO, SO                                                   |                                    |          |        |     |          |        |      |      |                                      |

| SPI Clock Rate                                                 | $SPI_{MCLK}$                       |          |        | 9.2 |          |        | 15.6 | MHz  |                                      |

| Data Rate Fast (MO, SO)                                        | $DR_{FAST}$                        |          |        | 40  |          |        | 40   | Mbps | Within PWD limit                     |

| Propagation Delay                                              | $t_{PHL}$ , $t_{PL}$               |          |        | 27  |          |        | 16   | ns   | 50% input to 50% output              |

| Pulse Width                                                    | н<br>PW                            | 12.<br>5 |        |     | 12.<br>5 |        |      | ns   | Within PWD limit                     |

| Pulse Width Distortion                                         | PWD                                |          |        | 2   |          |        | 2    | ns   | $ t_{PLH} - t_{PHL} $                |

| Codirectional Channel Matchin                                  | t <sub>PSKCD</sub>                 |          |        | 3   |          |        | 3    | ns   |                                      |

| g. <sup>1</sup>                                                |                                    |          |        |     |          |        |      |      |                                      |

| Jitter, High Speed                                             | $J_{	ext{	t HS}}$                  |          | 1      |     |          | 1      |      | ns   |                                      |

| MSS <sup>*</sup>                                               |                                    |          |        |     |          |        |      |      |                                      |

| Data Rate Fast                                                 | $\mathrm{DR}_{\mathrm{FAST}}$      |          |        | 40  |          |        | 40   | Mbps | Within PWD limit                     |

| Propagation Delay                                              | $t_{PHL}$ , $t_{PL}$               |          |        | 26  |          |        | 26   | ns   | 50% input to 50% output              |

| Pulse Width                                                    | н<br>PW                            | 12.<br>5 |        |     | 12.<br>5 |        |      | ns   | Within PWD limit                     |

| Pulse Width Distortion                                         | PWD                                |          |        | 3   |          |        | 3    | ns   | $ t_{PLH} - t_{PHL} $                |

| Setup Time. <sup>2</sup>                                       | MSS SETUP                          | 1. 5     |        |     | 10       |        |      | ns   | TEN THE                              |

| Jitter, High Speed                                             | $ m J_{HS}$                        |          | 1      |     |          | 1      |      | ns   |                                      |

| DCLK                                                           | 0.10                               |          |        |     |          |        |      |      |                                      |

| Data Rate                                                      |                                    |          |        | 40  |          |        | 40   | MHz  |                                      |

| Propagation Delay                                              | t <sub>PHL</sub> , t <sub>PL</sub> |          |        | 60  |          |        | 40   | ns   | $t_{PMCLK} + t_{PSO} + 3 \text{ ns}$ |

|                                                                | Н                                  |          |        |     |          |        |      |      |                                      |

| Pulse Width Distortion                                         | PWD                                |          |        | 3   |          |        | 3    | ns   | t <sub>PLH</sub> - t <sub>PHL</sub>  |

| Pulse Width                                                    | PW                                 | 12       | _      |     | 12       |        |      | ns   | Within PWD limit                     |

| Clock Delay Error                                              | DCLK <sub>ERR</sub>                | 2        | 7      | 13  | 2        | 6.8    | 11   | ns   | $t_{PDCLK} - (t_{PMCLK} + t_{PSO})$  |

| Jitter                                                         | J <sub>DCLK</sub>                  |          | 1      |     |          | 1      |      | ns   |                                      |

| $V_{IA}$ , $V_{IB}$                                            |                                    |          |        |     |          |        |      |      |                                      |

| Data Rate Slow                                                 | $DR_{SLOW}$                        |          |        | 250 |          |        | 250  | kbps | Within PWD limit                     |

| Propagation Delay                                              | t <sub>PHL</sub> , t <sub>PL</sub> | 0. 1     |        | 2.6 | 0. 1     |        | 2.6  | μs   | 50% input to 50% output              |

| Pulse Width                                                    | н<br>PW                            | 4        |        |     | 4        |        |      | μs   | Within PWD limit                     |

| Jitter, Low Speed                                              | J <sub>LS</sub>                    | 1        |        | 2.5 | 1        |        | 2.5  | μs   | "I VIIII I "D IIIIII I               |

| V <sub>Ix-</sub> <sup>3</sup> Minimum Input Skew. <sup>4</sup> | t <sub>VIx SKEW</sub>              | 10       |        |     | 10       |        |      | ns   |                                      |

<sup>&</sup>lt;sup>1</sup> 同方向チャンネル間マッチングは、アイソレーション・バリアの同じ側に入力を持つ任意の2つのチャンネル間の伝搬遅延差の絶対値です。

<sup>2</sup>MSS信号はすべてのグレードでグリッジ・フィルタが入っています。しかしBグレード品では、その他の高速信号にグリッジ・フィルタが入っていません。MSSが確実に他の高速信号より先に出力に到達するように、速度グレードによって時間は異なりますが、MSSを競い合う信号の前に設定してください。

$<sup>^3</sup>$   $V_{Ix} = V_{IA}$  又は  $V_{IB}$ .

<sup>&</sup>lt;sup>4</sup> 内部の非同期クロック(ユーザーは使用できません)が低速信号をサンプリングします。同方向チャンネルのエッジ・シーケンスがエンド・アプリケーションで重要な場合、出力に正しい順番あるいは同時に到達する事を保証するために、先行パルスは後発パルスより少なくても1 tvix skew時間前でなければなりません。

#### 表 9. 全グレード共通1, 2, 3

| Parameter                                                                 | Symbol                     | Min            | Тур        | Max            | Unit    | Test Conditions/Comments                                                                           |

|---------------------------------------------------------------------------|----------------------------|----------------|------------|----------------|---------|----------------------------------------------------------------------------------------------------|

| SUPPLY CURRENT                                                            |                            |                |            |                |         |                                                                                                    |

| 1 MHz, A Grade and B Grade                                                | $I_{	ext{DD1}}$            |                | 3. 5       | 4.5            | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                             |

|                                                                           | $I_{	ext{DD2}}$            |                | 6.8        | 9              | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                             |

| 17 MHz, B Grade                                                           | $I_{	ext{DD1}}$            |                | 12. 5      | 14. 5          | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                            |

|                                                                           | $I_{	ext{DD2}}$            |                | 14         | 16             | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                            |

| DC SPECIFICATIONS                                                         |                            |                |            |                |         |                                                                                                    |

| MCKL, $\overline{\text{MSS}}$ , MO, SO, $V_{\text{IA}}$ , $V_{\text{IB}}$ |                            |                |            |                |         |                                                                                                    |

| Input Threshold                                                           |                            |                |            |                |         |                                                                                                    |

| Logic High                                                                | $V_{\mathrm{IH}}$          | $0.7 \times V$ |            |                | V       |                                                                                                    |

|                                                                           |                            | DDx            |            |                |         |                                                                                                    |

| Logic Low                                                                 | $V_{\rm IL}$               |                |            | $0.3 \times V$ | V       |                                                                                                    |

|                                                                           |                            |                |            | DDx            |         |                                                                                                    |

| Input Hysteresis                                                          | $V_{IHYST}$                |                | 500        |                | mV      |                                                                                                    |

| Input Current per Channel                                                 | $I_{I}$                    | -1             | +0. 0<br>1 | +1             | μА      | $0 \text{ V} \leq V_{\text{INPUT}} \leq V_{\text{DDx}}$                                            |

| SCLK, SSS, MI, SI, VOA, VOB, DCLK                                         |                            |                | •          |                |         |                                                                                                    |

| Output Voltages                                                           |                            |                |            |                |         |                                                                                                    |

| Logic High                                                                | $V_{OH}$                   | $V_{DDx} - 0.$ | 5. 0       |                | V       | $I_{OUTPUT} = -20 \mu A$ , $V_{INPUT} = V_{IH}$                                                    |

|                                                                           |                            | $V_{DDx} - 0.$ | 4.8        |                | V       | $I_{OUTPUT} = -4$ mA, $V_{INPUT} = V_{IH}$                                                         |

| Logic Low                                                                 | $V_{OL}$                   |                | 0.0        | 0.1            | V       | $I_{OUTPUT}$ = 20 $\mu$ A, $V_{INPUT}$ = $V_{IL}$                                                  |

|                                                                           |                            |                | 0.2        | 0.4            | V       | $I_{OUTPUT} = 4$ mA, $V_{INPUT} = V_{IL}$                                                          |

| $V_{\text{DD1}}$ , $V_{\text{DD2}}$ Undervoltage Lockout                  | UVLO                       |                | 2.6        |                | V       |                                                                                                    |

| Supply Current for High Speed Channel                                     |                            |                |            |                |         |                                                                                                    |

| Dynamic Input                                                             | $I_{\text{DDI}(D)}$        |                | 0.09       |                | mA/Mbps |                                                                                                    |

| Dynamic Output                                                            | $I_{DDO(D)}$               |                | 0.02       |                | mA/Mbps |                                                                                                    |

| Supply Current for All Low Speed Channels                                 |                            |                |            |                |         |                                                                                                    |

| Quiescent Input                                                           | $I_{\text{DDI}(\text{Q})}$ |                | 2.8        |                | mA      |                                                                                                    |

| Quiescent Output                                                          | $I_{DDO(Q)}$               |                | 6.4        |                | mA      |                                                                                                    |

| AC SPECIFICATIONS                                                         |                            |                |            |                |         |                                                                                                    |

| Output Rise/Fall Time                                                     | $t_{R}/t_{F}$              |                | 2.5        |                | ns      | 10% to 90%                                                                                         |

| Common-Mode Transient Immunity.4                                          | CM                         | 25             | 35         |                | kV/μs   | $V_{\text{INPUT}} = V_{\text{DDx}}, V_{\text{CM}} = 1000 \text{ V}$<br>Transient magnitude = 800 V |

$<sup>^2</sup>$   $V_{\rm INPUT}$ は MCLK、  $\overline{\rm MSS}$  ピン、 MOピン、 SOピン、  $V_{\rm IA}$ ピン又は  $V_{\rm IB}$ ピンのいずれかの入力電圧です。

$<sup>^3</sup>$   $I_{OUTPUT}$ はSCLKピン、 DCLKピン、 $\overline{\rm SSS}$ ピン、 MIピン、 SIピン、 VOAピン 又は VOBのいずれかの出力電流です。

$<sup>^4</sup>$  |CM| は出力電圧が $V_{OH}$  と  $V_{OL}$ の 制限値内を維持している間に維持できるコモン・モード電圧の最大スルーレートです。コモン・モード電圧スルーレートは、立ち上がりと立ち下がりの両コモン・モード電圧エッジに適用されます。

#### パッケージ特性

#### 表 10.

| Parameter                        | Symbol           | Min | Тур       | Max | Unit | Test Conditions/Comments                      |

|----------------------------------|------------------|-----|-----------|-----|------|-----------------------------------------------|

| Resistance (Input-to-Output).1   | $R_{I=0}$        |     | $10^{12}$ |     | Ω    |                                               |

| Capacitance (Input-to-Output)1   | $C_{I=0}$        |     | 1.0       |     | pF   | f = 1 MHz                                     |

| Input Capacitance <sup>2</sup>   | $C_{\mathrm{I}}$ |     | 4.0       |     | pF   |                                               |

| IC Junction-to-Case Thermal Resi | heta JC          |     | 75        |     | ° C/ | Thermocouple located at center of package und |

| stance                           |                  |     |           |     | W    | erside                                        |

¹ デバイスは 2 端子デバイスと見なします:ピン1~ピン8 を相互に接続し、ピン9~ピン16 を相互に接続します。

#### 適用規格

ADuM3150は、表 11に記載する組織の認定を申請中です。特定のクロス・アイソレーション波形と絶縁レベルに対する推奨最大動作電圧については、表 16 と絶縁寿命のセクションを参照してください。

#### 表 11.

| UL (Pending)                                                          | CSA (Pending)                                                                                                                            | VDE (Pending)                                                                |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Recognized under 1577 Componen<br>t Recognition Program. <sup>1</sup> | Approved under CSA Component Acceptance Notice 5                                                                                         | Certified according to DIN V VD<br>E V 0884-10 (VDE V 0884-10):200<br>6-12.2 |

| 3750 V rms Single Protection                                          | Basic insulation per CSA 60950-1-07 and IEC 6095<br>0-1 second edition, 510 V rms (721 V peak) maxim<br>um working voltage. <sup>3</sup> | Reinforced insulation, 560 V pe<br>ak                                        |

| File E214100                                                          | File 205078                                                                                                                              | File 2471900-4880-0001                                                       |

$<sup>^1</sup>$  UL1577 に従い、絶縁テスト電圧 1,200 V rms 以上を1 秒間加えてADuM3150 を確認テストします(リーク電流検出規定値 =  $5\,\mu$  A)。

#### 絶縁および安全性関連の仕様

表 12.

| Parameter                                        | Symbol | Value | Unit   | Conditions                                                                           |

|--------------------------------------------------|--------|-------|--------|--------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage              |        | 3750  | V rms  | 1-minute duration                                                                    |

| Minimum External Air Gap (Clearance)             | L(I01) | 5. 1  | mm min | Measured from input terminals to output terminals, shortest distance through air     |

| Minimum External Tracking (Creepage)             | L(I02) | 5. 1  | mm min | Measured from input terminals to output terminals, shortest distance path along body |

| Minimum Internal Gap (Internal Clearance)        |        | 0.017 | mm min | Insulation distance through insulation                                               |

| Tracking Resistance (Comparative Tracking Index) | CTI    | >400  | V      | DIN IEC 112/VDE 0303 Part 1                                                          |

| Material Group                                   |        | II    |        | Material Group (DIN VDE 0110, 1/89, Table 1)                                         |

<sup>2</sup> 入力容量は任意の入力データ・ピンとグラウンドの間。

<sup>&</sup>lt;sup>2</sup> DIN V VDE V 0884-10 に従い、 ADuM3150に525Vpeak 以上の絶縁テスト電圧を1 秒間加えることによりテストして保証されています(部分放電の検出 規定値=5 pC)。部品のアスタリスク(\*)マークは、DIN V VDE V 0884-10 認定製品を表します。

<sup>&</sup>lt;sup>3</sup> 各種動作条件下での推奨最大動作電圧については表 16を参照してください。

#### DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12絶縁特性

このアイソレータは、安全性制限値内でのみ、強化された電気的絶縁を満たします。安全性データの維持は、保護回路を使って確実にする必要があります。パッケージ上のアスタリスク(\*)マークは、DIN V VDE V 0884-10認定製品を表します。

表 13.

| Description                                              | Test Conditions/Comments                                                                                                                           | Symbol               | Characterist ic | Unit       |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|------------|

| Installation Classification per DIN VD                   |                                                                                                                                                    |                      |                 |            |

| E 0110                                                   |                                                                                                                                                    |                      |                 |            |

| For Rated Mains Voltage ≤ 150 V rms                      |                                                                                                                                                    |                      | I to IV         |            |

| For Rated Mains Voltage ≤ 300 V rms                      |                                                                                                                                                    |                      | I to III        |            |

| For Rated Mains Voltage ≤ 400 V rms                      |                                                                                                                                                    |                      | I to II         |            |

| Climatic Classification                                  |                                                                                                                                                    |                      | 40/105/21       |            |

| Pollution Degree per DIN VDE 0110, Tab<br>le 1           |                                                                                                                                                    |                      | 2               |            |

| Maximum Working Insulation Voltage                       |                                                                                                                                                    | $V_{IORM}$           | 560             | V pea<br>k |

| Input-to-Output Test Voltage, Method b                   | $V_{\text{IORM}}$ $	imes$ 1.875 = $V_{\text{pd(m)}}$ , 100% production test, $t_{\text{ini}}$ = $t_{\text{m}}$ = 1 sec, partial discharge $<$ 5 pC | $V_{\mathrm{pd}(m)}$ | 1050            | V pea<br>k |

| Input-to-Output Test Voltage, Method a                   |                                                                                                                                                    |                      |                 |            |

| After Environmental Tests Subgroup 1                     | $V_{\text{IORM}}~\times~1.5$ = $V_{\text{pd(m)}},~t_{\text{ini}}$ = 60 sec, $t_{\text{m}}$ = 10 se c,                                              | $V_{\mathrm{pd}(m)}$ | 840             | V pea<br>k |

|                                                          | partial discharge < 5 pC                                                                                                                           |                      |                 |            |

| After Input and/or Safety Test Subgroup 2 and Subgroup 3 | $V_{\text{IORM}}$ $\times$ 1.2 = $V_{\text{pd}(\text{m})}$ , $t_{\text{ini}}$ = 60 sec, $t_{\text{m}}$ = 10 se c, partial discharge < 5 pC         | $V_{\mathrm{pd}(m)}$ | 672             | V pea<br>k |

| Highest Allewahle Overwelters                            | partial discharge \ 5 pc                                                                                                                           | V                    | 5300            | V          |

| Highest Allowable Overvoltage                            |                                                                                                                                                    | V <sub>IOTM</sub>    | 5500            | V pea<br>k |

| Surge Isolation Voltage                                  | $V_{\text{IOSM(TEST)}}$ = 10 kV, 1.2 µs rise time, 50 µs, 5 0% fall time                                                                           | $V_{IOSM}$           | 6000            | V pea<br>k |

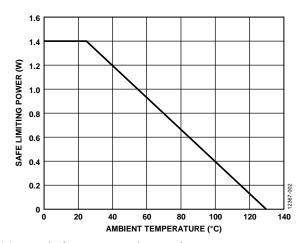

| Safety Limiting Values                                   | Maximum value allowed in the event of a failure (see 図 2)                                                                                          |                      |                 |            |

| Case Temperature                                         |                                                                                                                                                    | $T_{\rm S}$          | 130             | ° C        |

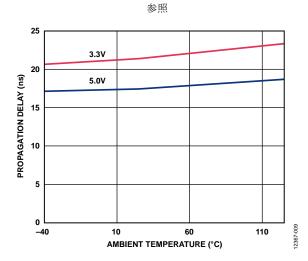

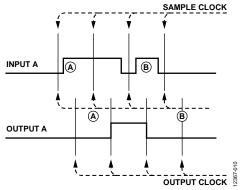

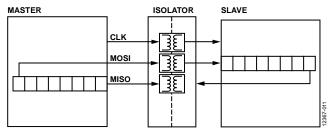

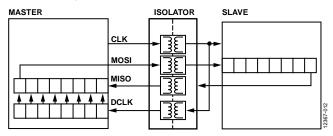

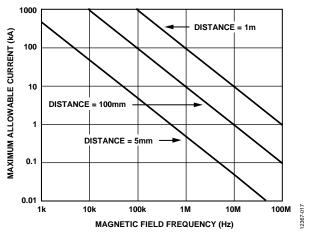

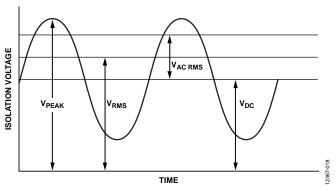

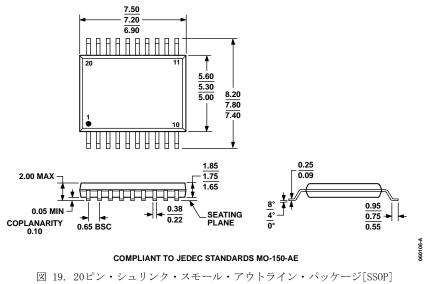

| Safety Total Dissipated Power                            |                                                                                                                                                    | $I_{s_1}$            | 1.4             | W          |