# 3.0 kV rms、2 チャンネル・ デジタル・アイソレータ

### データシート

# ADuM120N/ADuM121N

#### 特長

Η 高いコモンモード過渡耐性: 100 kV/μs(typ) 放射ノイズと導通ノイズに対する高いロバスト性 小さい伝搬遅延

5 V 動作時で最大 13 ns

1.8 V 動作時で最大 15 ns

最小データ・レート: 150 Mbps 安全と規制に関する認定 (申請中)

UL 認定

3000 V rms、1 分間の UL 1577 規格に準拠 「CSA Component Acceptance Notice 5A」に準拠 VDE の適合性認定済み

DIN V VDE V 0884-10 (VDE V 0884-10) : 2006-12

V<sub>IORM</sub> = 565 V peak

GB4943.1-2011 による CQC 証明

#### 後方互換性

ADuM120N0 は ADuM1285 とピン互換

ADuM120N1 は ADuM1280 および ADuM1200 とピン互換

ADuM121N0 は ADuM1286 とピン互換

ADuM121N1 は ADuM1281 および ADuM1201 とピン互換

低ダイナミック消費電力

1.8 V から 5 V へのレベル変換

高温動作:125 °C

フェイルセーフ・ハイまたはロー・オプション

RoHS 準拠の 8 ピン SOIC パッケージ

#### アプリケーション

汎用のマルチチャンネル・アイソレーション 工業用フィールドのパス・アイソレーション

#### 概要

ADuM120N/ADuM121N¹は、アナログデバイセズの *i*Coupler® 技術を採用した 2 チャンネルのデジタル・アイソレータです。これらのアイソレーション・デバイスは、高速 CMOS 技術と空芯コアを使ったモノリシック・トランス技術の組み合わせによって、フォトカプラ・デバイスやその他の集積カプラといった他方式の製品よりも優れた性能特性を提供します。5 V 動作時の最大伝搬遅延は 13 ns で、パルス幅歪みは 3 ns 未満です。チャンネル間マッチングは厳しく、最大 3.0 ns です。

ADuM120N/ADuM121N のデータ・チャンネルは独立していて、耐電圧定格 3 kV rms の様々な構成で提供できます(オーダー・ガイド参照)。このデバイスは両側とも 1.8 V  $\sim 5$  V の電

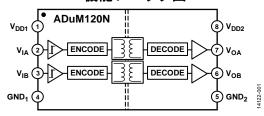

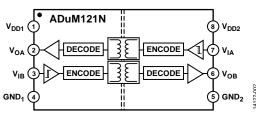

#### 機能ブロック図

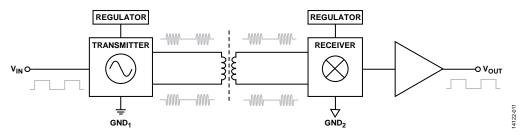

図 1. ADuM120N の機能ブロック図

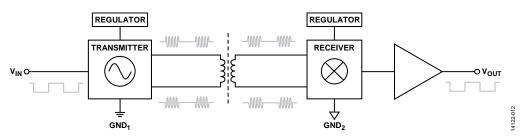

図 2. ADuM121N の機能ブロック図

源電圧で動作するため、低電圧システムにも使用できる他、絶 縁バリアをまたぐ電圧変換機能も備えています。

フォトカプラを使用した他製品と異なり、入力ロジックの遷移がないので正確な DC レベルが得られます。また、2 つの異なるフェイルセーフ・オプションを選択でき、入力電源が加えられていない場合や入力がディスエーブルされている場合でも、あらかじめ設定されたステートに出力が遷移します。

ADuM120N0 は ADuM1285 とピン互換で、ADuM120N1 は ADuM1280 および ADuM1200 とピン互換です。 ADuM121N0 は ADuM1286 とピン互換で、ADuM121N0 は ADuM1281 および ADuM1201 とピン互換です。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2016 Analog Devices, Inc. All rights reserved

Rev. o

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03 (5402) 8200

大阪営業所/〒532-0003

<sup>1</sup>米国特許5,952,849;6,873,065;6,903,578;7,075,329により保護されています。その他の特許は申請中です。

# データシート

# ADuM120N/ADuM121N

### 目次

| 符長                                       |     |

|------------------------------------------|-----|

| アプリケーション                                 |     |

| , , , , , , , , , , , , , , , , , , ,    |     |

| 概要                                       |     |

| 改訂履歴                                     |     |

| <b>仕様</b>                                |     |

| 電気的特性 — 5 V 動作時                          |     |

| 電気的特性 — 3.3 V 動作時                        |     |

| 電気的特性 — 2.5 V 動作時                        |     |

| 電気的特性 — 1.8 V 動作時                        |     |

| 絶縁および安全性関連の仕様                            |     |

| パッケージ特性                                  |     |

| 適用規格                                     |     |

| 回用及钳                                     |     |

| DII V VDL V U004-1U (VDL V U004-1U) 配物付出 | 1 4 |

| 推奨動作条件             | 12 |

|--------------------|----|

| 絶対最大定格             | 13 |

| ESD に関する注意         | 13 |

| ピン配置およびピン機能の説明     | 14 |

| 代表的な性能特性           | 15 |

| アプリケーション情報         | 16 |

| 概要                 | 16 |

| プリント回路基板(PCB)レイアウト | 16 |

| 伝搬遅延に関係するパラメータ     | 17 |

| ジッタの測定             | 17 |

| 絶縁寿命               | 17 |

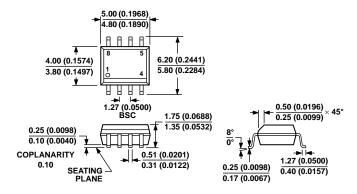

| 外形寸法               | 19 |

| オーダー・ガイド           | 10 |

### 改訂履歴

1/16—Revision 0: Initial Version

# 仕様

### 電気的特性 — 5 V 動作時

すべての typ 仕様は  $T_A=25$  °C、 $V_{DD1}=V_{DD2}=5$  V で規定されます。最小/最大仕様は、特に指定がない限り、4.5 V  $\leq$   $V_{DD1}\leq$  5.5 V、-40 °C  $\leq$   $T_A\leq$  +125 °C の全推奨動作範囲に適用されます。特に指定がない限り、スイッチング仕様は  $C_L=15$  pF および CMOS 信号レベルで試験されます。電源電流の仕様は 50 % デューティ・サイクルで指定されています。

表 1.

| 表 1.                                |                       |                               |                     |                             |         |                                                                  |

|-------------------------------------|-----------------------|-------------------------------|---------------------|-----------------------------|---------|------------------------------------------------------------------|

| Parameter                           | Symbol                | Min                           | Тур                 | Max                         | Unit    | Test Conditions/Comments                                         |

| SWITCHING SPECIFICATIONS            |                       |                               |                     |                             |         |                                                                  |

| Pulse Width                         | PW                    | 6.6                           |                     |                             | ns      | Within pulse width distortion (PWD) limit                        |

| Data Rate                           |                       | 150                           |                     |                             | Mbps    | Within PWD limit                                                 |

| Propagation Delay                   | $t_{PHL}$ , $t_{PLH}$ | 4.8                           | 7.2                 | 13                          | ns      | 50% input to 50% output                                          |

| Pulse Width Distortion              | PWD                   |                               | 0.5                 | 3                           | ns      | $ t_{PLH} - t_{PHL} $                                            |

| Change vs. Temperature              |                       |                               | 1.5                 |                             | ps/°C   |                                                                  |

| Propagation Delay Skew              | t <sub>PSK</sub>      |                               |                     | 6.0                         | ns      | Between any two units at the same temperature, voltage, and load |

| Channel Matching                    |                       |                               |                     |                             |         |                                                                  |

| Codirectional                       | $t_{PSKCD}$           |                               | 0.5                 | 3.0                         | ns      |                                                                  |

| Opposing Direction                  | $t_{PSKOD}$           |                               | 0.5                 | 3.0                         | ns      |                                                                  |

| Jitter                              |                       |                               | 380                 |                             | ps p-p  | See the Jitter Measurement section                               |

|                                     |                       |                               | 55                  |                             | ps rms  | See the Jitter Measurement section                               |

| DC SPECIFICATIONS                   |                       |                               |                     |                             |         |                                                                  |

| Input Threshold Voltage             |                       |                               |                     |                             |         |                                                                  |

| Logic High                          | $V_{IH}$              | $0.7 \times V_{\mathrm{DDx}}$ |                     |                             | V       |                                                                  |

| Logic Low                           | $V_{IL}$              |                               |                     | $0.3 \times V_{\text{DDx}}$ | V       |                                                                  |

| Output Voltage                      |                       |                               |                     |                             |         |                                                                  |

| Logic High                          | $V_{OH}$              | $V_{\mathrm{DDx}} - 0.1$      | $V_{\mathrm{DDx}}$  |                             | V       | $I_{Ox}^{1} = -20 \mu A, V_{Ix} = V_{IxH}^{2}$                   |

|                                     |                       | $V_{\mathrm{DDx}} - 0.4$      | $V_{\rm DDx} - 0.2$ |                             | V       | $I_{Ox}^{1} = -4 \text{ mA}, V_{Ix} = V_{IxH}^{2}$               |

| Logic Low                           | $V_{OL}$              |                               | 0.0                 | 0.1                         | V       | $I_{Ox}^{1} = 20 \mu A, V_{Ix} = V_{IxL}^{3}$                    |

|                                     |                       |                               | 0.2                 | 0.4                         | V       | $I_{Ox}^{1} = 4 \text{ mA}, V_{Ix} = V_{IxL}^{3}$                |

| Input Current per Channel           | $I_{\rm I}$           | -10                           | +0.01               | +10                         | μΑ      | $0 \text{ V} \leq V_{Ix} \leq V_{DDx}$                           |

| Quiescent Supply Current            |                       |                               |                     |                             |         |                                                                  |

| ADuM120N                            | $I_{DD1(Q)}$          |                               | 0.9                 | 1.3                         | mA      | $V_1^4 = 0$ (N0), 1 (N1) <sup>5</sup>                            |

|                                     | $I_{DD2(Q)}$          |                               | 1.3                 | 1.8                         | mA      | $V_1^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                       |

|                                     | $I_{DD1\;(Q)}$        |                               | 6.4                 | 10.0                        | mA      | $V_1^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                      |

|                                     | $I_{DD2(Q)}$          |                               | 1.4                 | 1.9                         | mA      | $V_1^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                      |

| ADuM121N                            | $I_{DD1\;(Q)}$        |                               | 1.1                 | 1.6                         | mA      | $V_1^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                       |

|                                     | $I_{DD2\;(Q)}$        |                               | 1.1                 | 1.5                         | mA      | $V_1^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                       |

|                                     | $I_{DD1(Q)}$          |                               | 4.0                 | 5.8                         | mA      | $V_I^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                      |

|                                     | $I_{DD2(Q)}$          |                               | 4.9                 | 6.4                         | mA      | $V_1^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                      |

| Dynamic Supply Current              |                       |                               |                     |                             |         |                                                                  |

| Dynamic Input                       | $I_{DDI(D)}$          |                               | 0.01                |                             | mA/Mbps | Inputs switching, 50% duty cycle                                 |

| Dynamic Output                      | $I_{DDO(D)}$          |                               | 0.02                |                             | mA/Mbps | Inputs switching, 50% duty cycle                                 |

| Undervoltage Lockout                | UVLO                  |                               |                     |                             |         |                                                                  |

| Positive V <sub>DDx</sub> Threshold | $V_{DDxUV+}$          |                               | 1.6                 |                             | V       |                                                                  |

| Negative V <sub>DDx</sub> Threshold | $V_{\mathrm{DDxUV-}}$ |                               | 1.5                 |                             | V       |                                                                  |

| V <sub>DDx</sub> Hysteresis         | $V_{\text{DDxUVH}}$   |                               | 0.1                 |                             | V       |                                                                  |

Rev. 0 -3/19 -

| Parameter                                      | Symbol          | Min | Тур | Max | Unit  | Test Conditions/Comments                                                                |

|------------------------------------------------|-----------------|-----|-----|-----|-------|-----------------------------------------------------------------------------------------|

| AC SPECIFICATIONS                              |                 |     |     |     |       |                                                                                         |

| Output Rise/Fall Time                          | $t_R/t_F$       |     | 2.5 |     | ns    | 10% to 90%                                                                              |

| Common-Mode Transient<br>Immunity <sup>6</sup> | CM <sub>H</sub> | 75  | 100 |     | kV/μs | $V_{Ix} = V_{DDx}$ , $V_{CM} = 1000$ V, transient magnitude = 800 V                     |

|                                                | $ CM_L $        | 75  | 100 |     | kV/μs | $V_{Ix} = 0 \text{ V}, V_{CM} = 1000 \text{ V}, \text{ transient magnitude}$<br>= 800 V |

$<sup>^1\,</sup>I_{Ox}$  はチャンネル l x の出力電流です(x = A または B)。

### 表 2. データ・スループット対合計電源電流

|                       |                    |     |     | 1 Mbps |     |     | 25 Mbps |     |     | 100 Mbps |      |  |

|-----------------------|--------------------|-----|-----|--------|-----|-----|---------|-----|-----|----------|------|--|

| Parameter             | Symbol             | Min | Тур | Max    | Min | Тур | Max     | Min | Тур | Max      | Unit |  |

| SUPPLY CURRENT        |                    |     |     |        |     |     |         |     |     |          |      |  |

| ADuM120N              |                    |     |     |        |     |     |         |     |     |          |      |  |

| Supply Current Side 1 | $I_{\mathrm{DD1}}$ |     | 3.7 | 6.8    |     | 4.2 | 7.2     |     | 6.2 | 9.3      | mA   |  |

| Supply Current Side 2 | $I_{\mathrm{DD2}}$ |     | 1.4 | 2.0    |     | 2.5 | 3.2     |     | 6.0 | 8.1      | mA   |  |

| ADuM121N              |                    |     |     |        |     |     |         |     |     |          |      |  |

| Supply Current Side 1 | $I_{\mathrm{DD1}}$ |     | 2.6 | 4.5    |     | 3.2 | 5.4     |     | 5.4 | 8.2      | mA   |  |

| Supply Current Side 2 | $I_{\mathrm{DD2}}$ |     | 3.0 | 4.9    |     | 3.7 | 5.9     |     | 5.8 | 8.6      | mA   |  |

Rev. 0 - 4/19 -

$<sup>^2</sup>V_{IxH}$  は入力側のロジック・ハイ電圧です。

$<sup>^3\,</sup>V_{\rm lxL}$  は入力側のロジック・ロー電圧です。

<sup>&</sup>lt;sup>4</sup> V<sub>I</sub> は入力電圧です。

$<sup>^5</sup>$  N0 は ADuM120N0/ADuM121N0 モデル、N1 は ADuM120N1/ADuM121N1 モデルです。オーダー・ガイドを参照してください。

$<sup>^6</sup>$   $|CM_H|$  は、 $(V_0)>0.8$   $V_{DDX}$  の電圧出力を維持しながら持続できるコモンモード電圧の最大スルー・レートです。 $|CM_L|$  は  $V_0>0.8$  V を維持しながら持続できるコモンモード電圧の最大スルー・レートです。コモンモード電圧スルー・レートは、立ち上がりと立ち下がり両方のコモンモード電圧エッジに適用されます。

### 電気的特性 - 3.3 V 動作時

すべての typ 仕様は  $T_A=25$  °C、 $V_{DD1}=V_{DD2}=3.3$  V で規定されます。最小/最大仕様は、特に指定がない限り、3.0 V  $\leq$   $V_{DD1}\leq 3.6$  V、3.0 V  $\leq$   $V_{DD2}\leq 3.6$  V、-40 °C  $\leq$   $T_A\leq +125$  °C の全推奨動作範囲に適用されます。特に指定がない限り、スイッチング仕様は  $C_L=15$  pF および CMOS 信号レベルで試験されます。電源電流の仕様は 50 % デューティ・サイクルで指定されています。

表 3.

| Parameter                           | Symbol                | Min                         | Тур                      | Max                         | Unit    | Test Conditions/Comments                                         |

|-------------------------------------|-----------------------|-----------------------------|--------------------------|-----------------------------|---------|------------------------------------------------------------------|

| SWITCHING SPECIFICATIONS            |                       |                             |                          |                             |         |                                                                  |

| Pulse Width                         | PW                    | 6.6                         |                          |                             | ns      | Within PWD limit                                                 |

| Data Rate                           |                       | 150                         |                          |                             | Mbps    | Within PWD limit                                                 |

| Propagation Delay                   | $t_{PHL}, t_{PLH}$    | 4.8                         | 6.8                      | 14                          | ns      | 50% input to 50% output                                          |

| Pulse Width Distortion              | PWD                   |                             | 0.7                      | 3                           | ns      | $ t_{\rm PLH}-t_{\rm PHL} $                                      |

| Change vs. Temperature              |                       |                             | 1.5                      |                             | ps/°C   |                                                                  |

| Propagation Delay Skew              | $t_{PSK}$             |                             |                          | 7.0                         | ns      | Between any two units at the same temperature, voltage, and load |

| Channel Matching                    |                       |                             |                          |                             |         |                                                                  |

| Codirectional                       | $t_{PSKCD}$           |                             | 0.7                      | 3.0                         | ns      |                                                                  |

| Opposing Direction                  | $t_{PSKOD}$           |                             | 0.7                      | 3.0                         | ns      |                                                                  |

| Jitter                              |                       |                             | 290                      |                             | ps p-p  | See the Jitter Measurement section                               |

|                                     |                       |                             | 45                       |                             | ps rms  | See the Jitter Measurement section                               |

| DC SPECIFICATIONS                   |                       |                             |                          |                             |         |                                                                  |

| Input Threshold Voltage             |                       |                             |                          |                             |         |                                                                  |

| Logic High                          | $V_{IH}$              | $0.7 \times V_{\text{DDx}}$ |                          |                             | V       |                                                                  |

| Logic Low                           | $V_{\rm IL}$          |                             |                          | $0.3 \times V_{\text{DDx}}$ | V       |                                                                  |

| Output Voltage                      |                       |                             |                          |                             |         |                                                                  |

| Logic High                          | $V_{OH}$              | $V_{\mathrm{DDx}} - 0.1$    | $V_{\mathrm{DDx}}$       |                             | V       | $I_{Ox}^{1} = -20 \mu A, V_{Ix} = V_{IxH}^{2}$                   |

|                                     |                       | $V_{\mathrm{DDx}} - 0.4$    | $V_{\mathrm{DDx}} - 0.2$ |                             | V       | $I_{Ox}^{1} = -2 \text{ mA}, V_{Ix} = V_{IxH}^{2}$               |

| Logic Low                           | $V_{OL}$              |                             | 0.0                      | 0.1                         | V       | $I_{Ox}^{1} = 20 \mu A, V_{Ix} = V_{IxL}^{3}$                    |

|                                     |                       |                             | 0.2                      | 0.4                         | V       | $I_{Ox}^{1} = 2 \text{ mA}, V_{Ix} = V_{IxL}^{3}$                |

| Input Current per Channel           | $I_{I}$               | -10                         | +0.01                    | +10                         | μΑ      | $0 \text{ V} \leq V_{Ix} \leq V_{DDx}$                           |

| Quiescent Supply Current            |                       |                             |                          |                             |         |                                                                  |

| ADuM120N                            | $I_{DD1\ (Q)}$        |                             | 0.8                      | 1.3                         | mA      | $V_I^4 = 0$ (N0), 1 (N1) <sup>5</sup>                            |

|                                     | $I_{DD2(Q)}$          |                             | 1.2                      | 1.8                         | mA      | $V_I^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                       |

|                                     | $I_{DD1 (Q)}$         |                             | 6.3                      | 9.7                         | mA      | $V_I^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                      |

|                                     | I <sub>DD2 (Q)</sub>  |                             | 1.3                      | 1.8                         | mA      | $V_I^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                      |

| ADuM121N                            | I <sub>DD1 (Q)</sub>  |                             | 1.0                      | 1.6                         | mA      | $V_I^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                       |

|                                     | I <sub>DD2 (Q)</sub>  |                             | 1.0                      | 1.5                         | mA      | $V_I^4 = 01 \text{ (N0)}, 1 \text{ (N1)}^5$                      |

|                                     | I <sub>DD1 (Q)</sub>  |                             | 3.9                      | 5.8                         | mA      | $V_I^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                      |

|                                     | I <sub>DD2 (Q)</sub>  |                             | 4.8                      | 6.4                         | mA      | $V_I^4 = 1 \text{ (N0)}, 0 \text{ (N1)}^5$                       |

| Dynamic Supply Current              |                       |                             |                          |                             |         |                                                                  |

| Dynamic Input                       | I <sub>DDI (D)</sub>  |                             | 0.01                     |                             | mA/Mbps | Inputs switching, 50% duty cycle                                 |

| Dynamic Output                      | I <sub>DDO (D)</sub>  |                             | 0.01                     |                             | mA/Mbps | Inputs switching, 50% duty cycle                                 |

| Undervoltage Lockout                | UVLO                  |                             |                          |                             |         |                                                                  |

| Positive V <sub>DDx</sub> Threshold | $V_{\mathrm{DDxUV}+}$ |                             | 1.6                      |                             | V       |                                                                  |

| Negative V <sub>DDx</sub> Threshold | $V_{\mathrm{DDxUV}-}$ |                             | 1.5                      |                             | V       |                                                                  |

| V <sub>DDx</sub> Hysteresis         | $V_{\mathrm{DDxUVH}}$ |                             | 0.1                      |                             | v       |                                                                  |

Rev. 0 - 5/19 -

| Parameter                                      | Symbol                | Min | Тур | Max | Unit  | Test Conditions/Comments                                                                          |

|------------------------------------------------|-----------------------|-----|-----|-----|-------|---------------------------------------------------------------------------------------------------|

| AC SPECIFICATIONS                              |                       |     |     |     |       |                                                                                                   |

| Output Rise/Fall Time                          | $t_{\rm R}/t_{\rm F}$ |     | 2.5 |     | ns    | 10% to 90%                                                                                        |

| Common-Mode Transient<br>Immunity <sup>6</sup> | CM <sub>H</sub>       | 75  | 100 |     | kV/μs | $V_{Ix} = V_{DDx}$ , $V_{CM} = 1000$ V, transient magnitude = $800$ V                             |

|                                                | $ CM_L $              | 75  | 100 |     | kV/μs | $V_{lx} = 0 \text{ V}, V_{CM} = 1000 \text{ V}, \text{ transient}$<br>magnitude = $800 \text{ V}$ |

$<sup>^1\,</sup>I_{Ox}$  はチャンネル l x の出力電流です(x = A または B)。

#### 表 4. データ・スループット対合計電源電流

|                       |                    |     | 1 Mbps |     |     | 25 Mbps |     |     | 100 Mbps |     |      |

|-----------------------|--------------------|-----|--------|-----|-----|---------|-----|-----|----------|-----|------|

| Parameter             | Symbol             | Min | Тур    | Max | Min | Тур     | Max | Min | Тур      | Max | Unit |

| SUPPLY CURRENT        |                    |     |        |     |     |         |     |     |          |     |      |

| ADuM120N              |                    |     |        |     |     |         |     |     |          |     |      |

| Supply Current Side 1 | $I_{\mathrm{DD1}}$ |     | 3.6    | 6.2 |     | 4.0     | 6.7 |     | 5.6      | 9.1 | mA   |

| Supply Current Side 2 | $I_{\mathrm{DD2}}$ |     | 1.3    | 1.9 |     | 2.3     | 3.1 |     | 5.2      | 6.8 | mA   |

| ADuM121N              |                    |     |        |     |     |         |     |     |          |     |      |

| Supply Current Side 1 | $I_{\mathrm{DD1}}$ |     | 2.5    | 4.6 |     | 3.0     | 5.5 |     | 5.0      | 8.1 | mA   |

| Supply Current Side 2 | $I_{\mathrm{DD2}}$ |     | 2.9    | 4.8 |     | 3.5     | 5.8 |     | 5.4      | 8.3 | mA   |

Rev. 0 - 6/19 -

$<sup>^2</sup>V_{IxH}$  は入力側のロジック・ハイ電圧です。

$<sup>^3\,</sup>V_{\rm lxL}$  は入力側のロジック・ロー電圧です。

<sup>&</sup>lt;sup>4</sup> V<sub>I</sub> は入力電圧です。

<sup>&</sup>lt;sup>5</sup> N0 は ADuM120N0/ADuM121N0 モデル、N1 は ADuM120N1/ADuM121N1 モデルです。オーダー・ガイドを参照してください。

$<sup>^6</sup>$   $|CM_H|$  は、 $V_0>0.8\ V_{DDx}$  の電圧出力を維持しながら持続できるコモンモード電圧の最大スルー・レートです。 $|CM_L|$  は  $V_0>0.8\ V$  を維持しながら持続できるコモンモード電圧の最大スルー・レートです。コモンモード電圧スルー・レートは、立ち上がりと立ち下がり両方のコモンモード電圧エッジに適用されます。

### 電気的特性 — 2.5 V 動作時

すべての typ 仕様は  $T_A = 25$ °C、 $V_{DD1} = V_{DD2} = 2.5$  V で規定されます。最小/最大仕様は、特に指定がない限り、2.25 V  $\leq$   $V_{DD1} \leq$  2.75 V、2.25 V  $\leq$   $V_{DD2} \leq$  2.75 V、-40 °C  $\leq$   $T_A \leq$  +125 °C の全推奨動作範囲に適用されます。特に指定がない限り、スイッチング仕様は  $C_L = 15$  pF および CMOS 信号レベルで試験されます。電源電流の仕様は 50 % デューティ・サイクルで指定されています。

表 5.

| Parameter                           | Symbol                | Min                         | Тур                      | Max                         | Unit    | Test Conditions/Comments                                     |

|-------------------------------------|-----------------------|-----------------------------|--------------------------|-----------------------------|---------|--------------------------------------------------------------|

| SWITCHING SPECIFICATIONS            |                       |                             |                          |                             | _       |                                                              |

| Pulse Width                         | PW                    | 6.6                         |                          |                             | ns      | Within PWD limit                                             |

| Data Rate                           |                       | 150                         |                          |                             | Mbps    | Within PWD limit                                             |

| Propagation Delay                   | $t_{PHL}$ , $t_{PLH}$ | 5.0                         | 7.0                      | 14                          | ns      | 50% input to 50% output                                      |

| Pulse Width Distortion              | PWD                   |                             | 0.7                      | 3                           | ns      | $ t_{\rm PLH}-t_{\rm PHL} $                                  |

| Change vs. Temperature              |                       |                             | 1.5                      |                             | ps/°C   |                                                              |

| Propagation Delay Skew              | $t_{PSK}$             |                             |                          | 7.0                         | ns      | Between any two units at the same temperature, voltage, load |

| Channel Matching                    |                       |                             |                          |                             |         |                                                              |

| Codirectional                       | $t_{PSKCD}$           |                             | 0.7                      | 3.0                         | ns      |                                                              |

| Opposing Direction                  | $t_{PSKOD}$           |                             | 0.7                      | 3.0                         | ns      |                                                              |

| Jitter                              |                       |                             | 320                      |                             | ps p-p  | See the Jitter Measurement section                           |

|                                     |                       |                             | 65                       |                             | ps rms  | See the Jitter Measurement section                           |

| DC SPECIFICATIONS                   |                       |                             |                          |                             |         |                                                              |

| Input Threshold Voltage             |                       |                             |                          |                             |         |                                                              |

| Logic High                          | $V_{IH}$              | $0.7 \times V_{\text{DDx}}$ |                          |                             | V       |                                                              |

| Logic Low                           | $V_{\rm IL}$          |                             |                          | $0.3 \times V_{\text{DDx}}$ | V       |                                                              |

| Output Voltage                      |                       |                             |                          |                             |         |                                                              |

| Logic High                          | $V_{OH}$              | $V_{\rm DDx} - 0.1$         | $V_{\mathrm{DDx}}$       |                             | V       | $I_{Ox}^{1} = -20 \mu A, V_{Ix} = V_{IxH}^{2}$               |

|                                     |                       | $V_{\rm DDx} - 0.4$         | $V_{\mathrm{DDx}} - 0.2$ |                             | V       | $I_{Ox}^{1} = -2 \text{ mA}, V_{Ix} = V_{IxH}^{2}$           |

| Logic Low                           | $V_{OL}$              |                             | 0.0                      | 0.1                         | V       | $I_{Ox}^{1} = 20 \mu A, V_{Ix} = V_{IxL}^{3}$                |

|                                     |                       |                             | 0.2                      | 0.4                         | V       | $I_{Ox}^{1} = 2 \text{ mA}, V_{Ix} = V_{IxL}^{3}$            |

| Input Current per Channel           | $I_{\rm I}$           | -10                         | +0.01                    | +10                         | μΑ      | $0\ V \leq V_{Ix} \leq V_{DDx}$                              |

| Quiescent Supply Current            |                       |                             |                          |                             |         |                                                              |

| ADuM120N                            | $I_{DD1(Q)}$          |                             | 0.8                      | 1.2                         | mA      | $V_1^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                   |

|                                     | $I_{DD2(Q)}$          |                             | 1.2                      | 1.8                         | mA      | $V_1^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                   |

|                                     | $I_{DD1(Q)}$          |                             | 6.2                      | 9.5                         | mA      | $V_I^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                  |

|                                     | I <sub>DD2 (Q)</sub>  |                             | 1.3                      | 1.8                         | mA      | $V_I^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                  |

| ADuM121N                            | $I_{DD1(Q)}$          |                             | 1.0                      | 1.5                         | mA      | $V_I^4 = 0 \text{ (N0), } 1 \text{ (N1)}^5$                  |

|                                     | I <sub>DD2 (Q)</sub>  |                             | 1.0                      | 1.4                         | mA      | $V_I^4 = 0 \text{ (N0), } 1 \text{ (N1)}^5$                  |

|                                     | $I_{DD1(Q)}$          |                             | 3.9                      | 5.8                         | mA      | $V_1^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                  |

|                                     | $I_{DD2(Q)}$          |                             | 4.8                      | 6.4                         | mA      | $V_1^4 = 1 \text{ (N0), } 0 \text{ (N1)}^5$                  |

| Dynamic Supply Current              |                       |                             |                          |                             |         |                                                              |

| Dynamic Input                       | I <sub>DDI (D)</sub>  |                             | 0.01                     |                             | mA/Mbps | Inputs switching, 50% duty cycle                             |

| Dynamic Output                      | $I_{DDO(D)}$          |                             | 0.01                     |                             | mA/Mbps | Inputs switching, 50% duty cycle                             |

| Undervoltage Lockout                |                       |                             |                          |                             |         |                                                              |

| Positive V <sub>DDx</sub> Threshold | $V_{\mathrm{DDxUV}+}$ |                             | 1.6                      |                             | V       |                                                              |

| Negative V <sub>DDx</sub> Threshold | $V_{\mathrm{DDxUV}-}$ |                             | 1.5                      |                             | V       |                                                              |

| V <sub>DDx</sub> Hysteresis         | $V_{\mathrm{DDxUVH}}$ |                             | 0.1                      |                             | V       |                                                              |

Rev. 0 - 7/19 -

# データシート

# ADuM120N/ADuM121N

| Parameter                                      | Symbol    | Min | Тур | Max | Unit  | Test Conditions/Comments                                                                          |

|------------------------------------------------|-----------|-----|-----|-----|-------|---------------------------------------------------------------------------------------------------|

| AC SPECIFICATIONS                              |           |     |     |     |       |                                                                                                   |

| Output Rise/Fall Time                          | $t_R/t_F$ |     | 2.5 |     | ns    | 10% to 90%                                                                                        |

| Common-Mode Transient<br>Immunity <sup>6</sup> | $ CM_H $  | 75  | 100 |     | kV/μs | $V_{Ix} = V_{DDx}$ , $V_{CM} = 1000 \text{ V}$ , transient magnitude = 800 V                      |

|                                                | $ CM_L $  | 75  | 100 |     | kV/μs | $V_{Ix} = 0 \text{ V}, V_{CM} = 1000 \text{ V}, \text{ transient}$<br>magnitude = $800 \text{ V}$ |

$<sup>^1\,</sup>I_{Ox}$  はチャンネル l x の出力電流です(x = A または B)。

### 表 6. データ・スループット対合計電源電流

|                       |                    |     | 1 Mbps | S   |     | 25 Mbp | S   |     | 100 Mb <sub>l</sub> | os  |      |

|-----------------------|--------------------|-----|--------|-----|-----|--------|-----|-----|---------------------|-----|------|

| Parameter             | Symbol             | Min | Тур    | Max | Min | Тур    | Max | Min | Тур                 | Max | Unit |

| SUPPLY CURRENT        |                    |     |        |     |     |        |     |     |                     |     |      |

| ADuM120N              |                    |     |        |     |     |        |     |     |                     |     |      |

| Supply Current Side 1 | $I_{\mathrm{DD1}}$ |     | 3.5    | 6.2 |     | 3.9    | 6.6 |     | 5.4                 | 9.0 | mA   |

| Supply Current Side 2 | $I_{\mathrm{DD2}}$ |     | 1.3    | 1.9 |     | 2.0    | 2.8 |     | 4.2                 | 5.8 | mA   |

| ADuM121N              |                    |     |        |     |     |        |     |     |                     |     |      |

| Supply Current Side 1 | $I_{\mathrm{DD1}}$ |     | 2.4    | 4.7 |     | 2.9    | 5.5 |     | 4.5                 | 8.0 | mA   |

| Supply Current Side 2 | $I_{\mathrm{DD2}}$ |     | 2.9    | 4.9 |     | 3.3    | 5.7 |     | 4.9                 | 7.7 | mA   |

Rev. 0 - 8/19 -

$<sup>^2</sup>V_{IxH}$  は入力側のロジック・ハイ電圧です。

$<sup>^3\,</sup>V_{\rm lxL}$  は入力側のロジック・ロー電圧です。

<sup>&</sup>lt;sup>4</sup> V<sub>I</sub> は入力電圧です。

<sup>&</sup>lt;sup>5</sup> N0 は ADuM120N0/ADuM121N0 モデル、N1 は ADuM120N1/ADuM121N1 モデルです。オーダー・ガイドを参照してください。

$<sup>^6</sup>$   $|CM_H|$  は、 $V_0>0.8$   $V_{DDx}$  の電圧出力を維持しながら持続できるコモンモード電圧の最大スルー・レートです。 $|CM_L|$  は、 $V_0>0.8$  V を維持しながら持続できるコモンモード電圧の最大スルー・レートです。コモンモード電圧スルー・レートは、立ち上がりと立ち下がり両方のコモンモード電圧エッジに適用されます。

### 電気的特性 — 1.8 V 動作時

すべての typ 仕様は  $T_A=25$  °C、 $V_{DD1}=V_{DD2}=1.8$  V で規定されます。最小/最大仕様は、特に指定がない限り、1.7 V  $\leq$   $V_{DD1} \leq 1.9$  V、1.7 V  $\leq$   $V_{DD2} \leq 1.9$  V、-40 °C  $\leq$   $T_A \leq +125$  °C の全推奨動作範囲に適用されます。特に指定がない限り、スイッチング仕様は  $C_L=15$  pF および CMOS 信号レベルで試験されます。電源電流の仕様は 50 % デューティ・サイクルで指定されています。

表 7.

| Parameter                           | Symbol                              | Min                  | Тур                | Max                         | Unit    | Test Conditions/Comments                                         |

|-------------------------------------|-------------------------------------|----------------------|--------------------|-----------------------------|---------|------------------------------------------------------------------|

| SWITCHING SPECIFICATIONS            |                                     |                      |                    |                             |         |                                                                  |

| Pulse Width                         | PW                                  | 6.6                  |                    |                             | ns      | Within PWD limit                                                 |

| Data Rate                           |                                     | 150                  |                    |                             | Mbps    | Within PWD limit                                                 |

| Propagation Delay                   | t <sub>PHL</sub> , t <sub>PLH</sub> | 5.8                  | 8.7                | 15                          | ns      | 50% input to 50% output                                          |

| Pulse Width Distortion              | PWD                                 |                      | 0.7                | 3                           | ns      | $ t_{\rm PLH}-t_{\rm PHL} $                                      |

| Change vs. Temperature              |                                     |                      | 1.5                |                             | ps/°C   |                                                                  |

| Propagation Delay Skew              | $t_{PSK}$                           |                      |                    | 7.0                         | ns      | Between any two units at the same temperature, voltage, and load |

| Channel Matching                    |                                     |                      |                    |                             |         |                                                                  |

| Codirectional                       | $t_{PSKCD}$                         |                      | 0.7                | 3.0                         | ns      |                                                                  |

| Opposing Direction                  | $t_{PSKOD}$                         |                      | 0.7                | 3.0                         | ns      |                                                                  |

| Jitter                              |                                     |                      | 630                |                             | ps p-p  | See the Jitter Measurement section                               |

|                                     |                                     |                      | 190                |                             | ps rms  | See the Jitter Measurement section                               |

| DC SPECIFICATIONS                   |                                     |                      |                    |                             |         |                                                                  |

| Input Threshold Voltage             |                                     |                      |                    |                             |         |                                                                  |

| Logic High                          | $V_{IH}$                            | $0.7 \times V_{DDx}$ |                    |                             | V       |                                                                  |

| Logic Low                           | V <sub>IL</sub>                     |                      |                    | $0.3 \times V_{\text{DDx}}$ | V       |                                                                  |

| Output Voltage                      |                                     |                      |                    |                             |         |                                                                  |

| Logic High                          | $V_{OH}$                            | $V_{\rm DDx} - 0.1$  | $V_{\mathrm{DDx}}$ |                             | V       | $I_{Ox}^{1} = -20 \mu A, V_{Ix} = V_{IxH}^{2}$                   |

|                                     |                                     | $V_{\rm DDx} - 0.4$  | $V_{DDx} - 0.2$    |                             | V       | $I_{Ox}^{1} = -2 \text{ mA}, V_{Ix} = V_{IxH}^{2}$               |

| Logic Low                           | $V_{OL}$                            |                      | 0.0                | 0.1                         | V       | $I_{Ox}^{-1} = 20 \mu A, V_{Ix} = V_{IxL}^{-3}$                  |

|                                     |                                     |                      | 0.2                | 0.4                         | V       | $I_{Ox}^{1} = 2 \text{ mA}, V_{Ix} = V_{IxL}^{3}$                |

| Input Current per Channel           | $I_{\rm I}$                         | -10                  | +0.01              | +10                         | μΑ      | $0 \text{ V} \leq V_{Ix} \leq V_{DDx}$                           |

| Quiescent Supply Current            |                                     |                      |                    |                             |         |                                                                  |

| ADuM120N                            | $I_{DD1\ (Q)}$                      |                      | 0.7                | 1.2                         | mA      | $V_1^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                       |

|                                     | I <sub>DD2 (Q)</sub>                |                      | 1.2                | 1.8                         | mA      | $V_1^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                       |

|                                     | I <sub>DD1 (Q)</sub>                |                      | 6.2                | 9.6                         | mA      | $V_1^4 = 1 \text{ (N0)}, 0 \text{ (N1)}^5$                       |

|                                     | I <sub>DD2 (Q)</sub>                |                      | 1.3                | 1.8                         | mA      | $V_1^4 = 1 \text{ (N0)}, 0 \text{ (N1)}^5$                       |

| ADuM121N                            | I <sub>DD1 (Q)</sub>                |                      | 1.0                | 1.5                         | mA      | $V_1^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                       |

|                                     | I <sub>DD2 (Q)</sub>                |                      | 1.0                | 1.4                         | mA      | $V_1^4 = 0 \text{ (N0)}, 1 \text{ (N1)}^5$                       |

|                                     | I <sub>DD1 (Q)</sub>                |                      | 3.8                | 5.8                         | mA      | $V_1^4 = 1 \text{ (N0)}, 0 \text{ (N1)}^5$                       |

|                                     | $I_{DD2(Q)}$                        |                      | 4.7                | 6.4                         | mA      | $V_1^4 = 1 \text{ (N0)}, 0 \text{ (N1)}^5$                       |

| Dynamic Supply Current              | 322(4)                              |                      |                    |                             |         |                                                                  |

| Dynamic Input                       | $I_{DDI(D)}$                        |                      | 0.01               |                             | mA/Mbps | Inputs switching, 50% duty cycle                                 |

| Dynamic Output                      | I <sub>DDO (D)</sub>                |                      | 0.01               |                             | mA/Mbps | Inputs switching, 50% duty cycle                                 |

| Undervoltage Lockout                | UVLO                                |                      |                    |                             |         |                                                                  |

| Positive V <sub>DDx</sub> Threshold | $V_{\mathrm{DDxUV}+}$               |                      | 1.6                |                             | V       |                                                                  |

| Negative V <sub>DDx</sub> Threshold | $V_{\mathrm{DDxUV-}}$               |                      | 1.5                |                             | V       |                                                                  |

| V <sub>DDx</sub> Hysteresis         | V <sub>DDxUVH</sub>                 |                      | 0.1                |                             | V       |                                                                  |

Rev. 0 -9/19 -

| Parameter                                   | Symbol    | Min | Тур | Max | Unit  | Test Conditions/Comments                                                                                  |

|---------------------------------------------|-----------|-----|-----|-----|-------|-----------------------------------------------------------------------------------------------------------|

| AC SPECIFICATIONS                           |           |     |     |     |       |                                                                                                           |

| Output Rise/Fall Time                       | $t_R/t_F$ |     | 2.5 |     | ns    | 10% to 90%                                                                                                |

| Common-Mode Transient Immunity <sup>6</sup> | $ CM_H $  | 75  | 100 |     | kV/μs | $\begin{aligned} V_{Ix} &= V_{DDx},  V_{CM} = 1000   V,  transient \\ magnitude &= 800   V \end{aligned}$ |

|                                             | $ CM_L $  | 75  | 100 |     | kV/μs | $V_{Ix} = 0 \text{ V}, V_{CM} = 1000 \text{ V}, \text{ transient}$<br>magnitude = 800 V                   |

$<sup>^{1}</sup>I_{Ox}$  はチャンネル1x の出力電流です(x=A またはB)。

#### 表 8. データ・スループット対合計電源電流

|                       |                    |     | 1 Mbp | S   |     | 25 Mbp | S   |     | 100 Mb <sub>l</sub> | os  |      |

|-----------------------|--------------------|-----|-------|-----|-----|--------|-----|-----|---------------------|-----|------|

| Parameter             | Symbol             | Min | Тур   | Max | Min | Тур    | Max | Min | Тур                 | Max | Unit |

| SUPPLY CURRENT        |                    |     |       |     |     |        |     |     |                     |     |      |

| ADuM120N              |                    |     |       |     |     |        |     |     |                     |     |      |

| Supply Current Side 1 | $I_{\mathrm{DD1}}$ |     | 3.4   | 6.0 |     | 3.8    | 6.4 |     | 5.2                 | 8.4 | mA   |

| Supply Current Side 2 | $I_{\mathrm{DD2}}$ |     | 1.2   | 1.8 |     | 1.9    | 2.8 |     | 4.0                 | 5.8 | mA   |

| ADuM121N              |                    |     |       |     |     |        |     |     |                     |     |      |

| Supply Current Side 1 | $I_{\mathrm{DD1}}$ |     | 2.4   | 4.7 |     | 2.8    | 5.5 |     | 4.4                 | 7.8 | mA   |

| Supply Current Side 2 | $I_{\mathrm{DD2}}$ |     | 2.8   | 4.8 |     | 3.2    | 5.6 |     | 4.8                 | 7.9 | mA   |

### 絶縁および安全性関連の仕様

詳細については www.analog.com/icouplersafety を参照してください。

### 表 9.

| Parameter                                                                      | Symbol  | Value | Unit   | Test Conditions/Comments                                                                                                   |

|--------------------------------------------------------------------------------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage                                            |         | 3000  | V rms  | 1-minute duration                                                                                                          |

| Minimum External Air Gap (Clearance)                                           | L (I01) | 4.0   | mm min | Measured from input terminals to output terminals, shortest distance through air                                           |

| Minimum External Tracking (Creepage)                                           | L (I02) | 4.0   | mm min | Measured from input terminals to output terminals, shortest distance path along body                                       |

| Minimum Clearance in the Plane of the Printed Circuit<br>Board (PCB Clearance) | L (PCB) | 4.5   | mm min | Measured from input terminals to output terminals, shortest distance through air, line of sight, in the PCB mounting plane |

| Minimum Internal Gap (Internal Clearance)                                      |         | 25.5  | μm min | Insulation distance through insulation                                                                                     |

| Tracking Resistance (Comparative Tracking Index)                               | CTI     | >400  | V      | DIN IEC 112/VDE 0303 Part 1                                                                                                |

| Material Group                                                                 |         | II    |        | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                               |

### パッケージ特性

#### 表 10

| 五 10.                                      |                        |     |           |     |      |                                                     |

|--------------------------------------------|------------------------|-----|-----------|-----|------|-----------------------------------------------------|

| Parameter                                  | Symbol                 | Min | Тур       | Max | Unit | Test Conditions/Comments                            |

| Resistance (Input to Output) <sup>1</sup>  | R <sub>I-O</sub>       |     | $10^{13}$ |     | Ω    |                                                     |

| Capacitance (Input to Output) <sup>1</sup> | $C_{\text{I-O}}$       |     | 2         |     | pF   | f = 1  MHz                                          |

| Input Capacitance <sup>2</sup>             | $C_{I}$                |     | 4.0       |     | pF   |                                                     |

| IC Junction to Ambient Thermal Resistance  | $\theta_{\mathrm{JA}}$ |     | 80        |     | °C/W | Thermocouple located at center of package underside |

<sup>「</sup>デバイスは 2 端子デバイスとみなします。すなわち、ピン 1 ~ ピン 4 が相互接続し、ピン 5 ~ ピン 8 を相互に接続します。

Rev. 0 - 10/19 -

$<sup>^{2}</sup>V_{IxH}$  は入力側のロジック・ハイ電圧です。

$<sup>^3\,</sup>V_{\rm lxL}$  は入力側のロジック・ロー電圧です。

$<sup>^4</sup>V_I$  は入力電圧です。

<sup>&</sup>lt;sup>5</sup> NO は ADuM120NO/ADuM121NO モデルで、N1 は ADuM120N1/ADuM121N1 モデルです。オーダー・ガイドを参照してください。

$<sup>^6</sup>$   $|CM_H|$  は、 $V_O>0.8$   $V_{DDx}$  の電圧出力を維持しながら持続できるコモンモード電圧の最大スルー・レートです。 $|CM_L|$  は  $V_O>0.8$  V を維持しながら持続できるコモンモード電圧の最大スルー・レートです。コモンモード電圧スルー・レートは、コモンモード電圧の立ち上がりと立ち下がりの両エッジに適用されます。

<sup>2</sup>入力容量は、任意の入力データ・ピンとグランド間に接続します。

### 適用規格

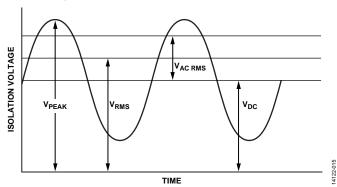

特定のクロス・アイソレーション波形と絶縁レベルに対する推奨最大動作電圧については、表 15 および「絶縁寿命」のセクションを参照してください。

表 11.

| UL (Pending)                                                              | CSA (Pending)                                                          | VDE (Pending)                                                         | CQC (Pending)                                               |

|---------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------|

| Recognized under UL 1577<br>Component Recognition<br>Program <sup>1</sup> | Approved under CSA Component<br>Acceptance Notice 5A                   | DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 <sup>2</sup>              | Certified under<br>CQC11-471543-2012                        |

| Single Protection, 3000 V rms<br>Isolation Voltage                        | CSA 60950-1-07+A1+A2 and IEC 60950-<br>1, second edition, +A1+A2:      | Reinforced insulation, 565 V<br>peak, V <sub>IOSM</sub> = 6000 V peak | GB4943.1-2011                                               |

| Double Protection, 3000 V rms<br>Isolation Voltage                        | Basic insulation at 400 V rms (565 V peak)                             | Basic insulation, 565 V peak,<br>V <sub>IOSM</sub> = 10000 V peak     | Basic insulation at 770 V rms (1089 V peak) working voltage |

|                                                                           | Reinforced insulation at 200 V rms (283 V peak)                        |                                                                       | Reinforced insulation at 385 V rms (545 V peak)             |

|                                                                           | IEC 60601-1 Edition 3.1:                                               |                                                                       |                                                             |

|                                                                           | Basic insulation (1 MOPP), 250 V rms (354 V peak)                      |                                                                       |                                                             |

|                                                                           | CSA 61010-1-12 and IEC 61010-1 third edition                           |                                                                       |                                                             |

|                                                                           | Basic insulation at 300 V rms mains, 400 V rms (565 V peak)            |                                                                       |                                                             |

|                                                                           | Reinforced insulation at 300 V rms mains, 200 V secondary (283 V peak) |                                                                       |                                                             |

| File E214100                                                              | File 205078                                                            | File 2471900-4880-0001                                                | File (pending)                                              |

<sup>&</sup>lt;sup>1</sup> UL 1577 に従い、それぞれの ADuM120N/ADuM121N には 3600 V rms 以上の絶縁テスト電圧を 1 秒間加える耐電圧テストを実施しています。

Rev. 0 — 11/19 —

$<sup>^2</sup>$  DIN V VDE V 0884-10 に従い、それぞれの ADuM120N/ADuM121N には 1059 V peak 以上の絶縁テスト電圧を 1 秒間加える耐電圧テストを実施しています(部分放電検出限界 = 5 pC)。デバイス表面のアスタリスク(\*)は、DIN V VDE V 0884-10 認定製品であることを示します。

### DIN V VDE V 0884-10 (VDE V 0884-10) 絶縁特性

これらのアイソレータは、安全性制限値データ以内でのみ強化された電気的絶縁に適しています。保護回路を使用すれば、安全データを維持しやすくなります。パッケージ表面のアスタリスク(\*)は、DIN V VDE V 0884-10 認定製品であることを表します。

表 12.

| Description                                              | Test Conditions/Comments                                                                                                                                                 | Symbol            | Characteristic | Unit   |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------|

| Installation Classification per DIN VDE 0110             |                                                                                                                                                                          |                   |                |        |

| For Rated Mains Voltage ≤ 150 V rms                      |                                                                                                                                                                          |                   | I to IV        |        |

| For Rated Mains Voltage ≤ 300 V rms                      |                                                                                                                                                                          |                   | I to III       |        |

| For Rated Mains Voltage ≤ 400 V rms                      |                                                                                                                                                                          |                   | I to III       |        |

| Climatic Classification                                  |                                                                                                                                                                          |                   | 40/105/21      |        |

| Pollution Degree per DIN VDE 0110, Table 1               |                                                                                                                                                                          |                   | 2              |        |

| Maximum Working Insulation Voltage                       |                                                                                                                                                                          | V <sub>IORM</sub> | 565            | V peak |

| Input to Output Test Voltage, Method B1                  | $\begin{aligned} &V_{IORM} \times 1.875 = V_{pd~(m)},  100\% \text{ production test,} \\ &t_{ini} = t_m = 1 \text{ sec, partial discharge} < 5 \text{ pC} \end{aligned}$ | $V_{pd\ (m)}$     | 1059           | V peak |

| Input to Output Test Voltage, Method A                   |                                                                                                                                                                          |                   |                |        |

| After Environmental Tests Subgroup 1                     | $\begin{aligned} V_{IORM} \times 1.5 &= V_{pd  (m)}, t_{ini} = 60 \text{ sec, } t_m = 10 \text{ sec,} \\ partial \ discharge < 5 \ pC \end{aligned}$                     | $V_{pd\;(m)}$     | 848            | V peak |

| After Input and/or Safety Test Subgroup 2 and Subgroup 3 | $\begin{aligned} V_{IORM} \times 1.2 &= V_{pd  (m)}, t_{ini} = 60 \text{ sec, } t_m = 10 \text{ sec,} \\ partial \ discharge < 5 \ pC \end{aligned}$                     |                   | 678            | V peak |

| Highest Allowable Overvoltage                            |                                                                                                                                                                          | $V_{IOTM}$        | 4200           | V peak |

| Surge Isolation Voltage Basic                            | V peak = $10$ kV, $1.2$ $\mu$ s rise time, $50$ $\mu$ s, $50$ % fall time                                                                                                | $V_{IOSM}$        | 10000          | V peak |

| Surge Isolation Voltage Reinforced                       | V peak = $10$ kV, $1.2$ $\mu s$ rise time, $50$ $\mu s$ , $50\%$ fall time                                                                                               | V <sub>IOSM</sub> | 6000           | V peak |

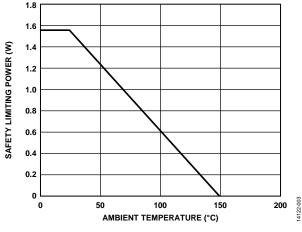

| Safety Limiting Values                                   | Maximum value allowed in the event of a failure (see Figure 3)                                                                                                           |                   |                |        |

| Maximum Junction Temperature                             |                                                                                                                                                                          | $T_S$             | 150            | °C     |

| Total Power Dissipation at 25°C                          |                                                                                                                                                                          | $P_S$             | 1.56           | W      |

| Insulation Resistance at T <sub>S</sub>                  | $V_{IO} = 500 \text{ V}$                                                                                                                                                 | $R_S$             | >109           | Ω      |

図 3. 熱ディレーティング曲線、DIN V VDE V 0884-10 による 安全限界電力の周囲温度への依存性

### 推奨動作条件

表 13.

| Parameter                        | Symbol                                                            | Rating          |

|----------------------------------|-------------------------------------------------------------------|-----------------|

| Operating Temperature            | $T_A$                                                             | −40°C to +125°C |

| Supply Voltages                  | $egin{array}{c} V_{\mathrm{DD1}}, \ V_{\mathrm{DD2}} \end{array}$ | 1.7 V to 5.5 V  |

|                                  | $V_{\mathrm{DD2}}$                                                |                 |

| Input Signal Rise and Fall Times |                                                                   | 1.0 ms          |

Rev. 0 - 12/19 -

### 絶対最大定格

特に指定のない限り、TA=25℃。

#### 表 14.

| Parameter                                                        | Rating                                                         |

|------------------------------------------------------------------|----------------------------------------------------------------|

| Supply Voltages (V <sub>DD1</sub> , V <sub>DD2</sub> )           | -0.5 V to +7.0 V                                               |

| Input Voltages (V <sub>IA</sub> , V <sub>IB</sub> ) <sup>1</sup> | $-0.5 \text{ V}$ to $V_{DDI} + 0.5 \text{ V}$                  |

| Output Voltages $(V_{OA}, V_{OB})^2$                             | $-0.5 \text{ V}$ to $V_{DDO} + 0.5 \text{ V}$                  |

| Average Output Current per Pin <sup>3</sup>                      |                                                                |

| Side 1 Output Current (I <sub>O1</sub> )                         | -10 mA to +10 mA                                               |

| Side 2 Output Current (I <sub>O2</sub> )                         | -10 mA to +10 mA                                               |

| Common-Mode Transients <sup>4</sup>                              | $-150 \text{ kV/}\mu\text{s}$ to $+150 \text{ kV/}\mu\text{s}$ |

| Storage Temperature (T <sub>ST</sub> ) Range                     | −65°C to +150°C                                                |

| Ambient Operating Temperature (T <sub>A</sub> )                  | −40°C to +125°C                                                |

| Range                                                            |                                                                |

<sup>&</sup>lt;sup>1</sup> V<sub>DDI</sub> は入力側電源電圧です。

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間絶対最大定格状態に置くと、デバイス の信頼性に影響を与えることがあります。

### ESD に関する注意

#### ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

#### 表 15. 最大連続動作電圧 1

| Parameter             | Rating     | Constraint <sup>2</sup>                                                               |

|-----------------------|------------|---------------------------------------------------------------------------------------|

| AC VOLTAGE            |            | Lifetime limited by package creepage maximum approved working voltage per IEC 60950-1 |

| Bipolar Waveform      |            |                                                                                       |

| Basic Insulation      | 789 V peak |                                                                                       |

| Reinforced Insulation | 403 V peak |                                                                                       |

| Unipolar Waveform     |            |                                                                                       |

| Basic Insulation      | 909 V peak |                                                                                       |

| Reinforced Insulation | 469 V peak |                                                                                       |

| DC VOLTAGE            |            | Lifetime limited by package creepage maximum approved working voltage per IEC 60950-1 |

| Basic Insulation      | 558 V peak |                                                                                       |

| Reinforced Insulation | 285 V peak |                                                                                       |

<sup>「</sup>最大連続動作電圧は、絶縁バリアに加わる連続電圧の大きさを表わします。詳細については「絶縁寿命」のセクションを参照してください。

#### 真理値表

#### 表 16. ADuM120N/ADuM121N の真理値表(正論理)

| V <sub>Ix</sub> Input <sup>1</sup> | V <sub>DDI</sub> State <sup>1</sup> | V <sub>DDO</sub> State <sup>1</sup> | Default Low (N0),<br>V <sub>Ox</sub> Output <sup>1, 2</sup> | Default High (N1),<br>V <sub>Ox</sub> Output <sup>1,2</sup> | Test Conditions/Comments |

|------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|--------------------------|

| Low                                | Powered                             | Powered                             | Low                                                         | Low                                                         | Normal operation         |

| High                               | Powered                             | Powered                             | High                                                        | High                                                        | Normal operation         |

| Don't Care <sup>3</sup>            | Unpowered                           | Powered                             | Low                                                         | High                                                        | Fail-safe output         |

| Don't Care <sup>3</sup>            | Powered                             | Unpowered                           | Indeterminate                                               | Indeterminate                                               |                          |

$<sup>^1</sup>$   $V_{Ix}$  と  $V_{Ox}$  は、所定のチャンネル(A または B)の入出力信号を指します。 $V_{DDI}$  と  $V_{DDO}$  はそれぞれ、所定のチャンネルの入力側と出力側の電源電圧を指します。

Rev. 0 – 13/19 –

<sup>&</sup>lt;sup>2</sup> V<sub>DDO</sub> は出力側電源電圧です。

$<sup>^{3}</sup>$ 種々の温度に対する最大定格電力値については、図 $^{3}$ を参照してください。

<sup>&</sup>lt;sup>4</sup> Common-mode transients は、絶縁バリアをまたぐコモンモード過渡電圧 を表します。絶対最大定格を超えるコモンモード過渡電圧は、ラッチ アップまたは恒久的な故障の原因になり得ます。

<sup>2</sup>規定されたテスト条件での絶縁寿命は50年より長くなります。

$<sup>^2</sup>$  N0 は ADuM120N0/ADuM121N0 モデル、N1 は ADuM120N1/ADuM121N1 モデルです。オーダー・ガイドを参照してください。

$<sup>^3</sup>$ 電源が供給されていない側と同じ側の入力ピン( $V_{tx}$ )は、ESD 保護回路を通ってデバイスに電源が供給されるのを防ぐために、ロー状態になっていなければなりません。

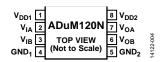

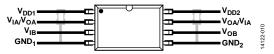

# ピン配置およびピン機能の説明

図 4. ADuM120N のピン配置

特定のレイアウト・ガイドラインについては、AN-1109 アプリケーション・ノートを参照してください。

表 17. ADuM120N のピン機能の説明

| Pin No. | Mnemonic           | Description                   |

|---------|--------------------|-------------------------------|

| 1       | $V_{\mathrm{DD1}}$ | アイソレータ・サイド1の電源電圧。             |

| 2       | $V_{IA}$           | ロジック入力 A。                     |

| 3       | $ m V_{IB}$        | ロジック入力 B。                     |

| 4       | $GND_1$            | グラウンド1。アイソレータ・サイド1のグラウンド基準です。 |

| 5       | $\mathrm{GND}_2$   | グラウンド2。アイソレータ・サイド2のグラウンド基準です。 |

| 6       | $V_{OB}$           | ロジック出力 B。                     |

| 7       | $V_{OA}$           | ロジック出力 A。                     |

| 8       | $V_{\mathrm{DD2}}$ | アイソレータ・サイド 2 の電源電圧。           |

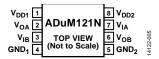

図 5. ADuM121N のピン配置

特定のレイアウト・ガイドラインについては、AN-1109 アプリケーション・ノートを参照してください。

表 18. ADuM121N のピン機能の説明

| Pin No. | Mnemonic           | Description                   |

|---------|--------------------|-------------------------------|

| 1       | $V_{\mathrm{DD1}}$ | アイソレータ・サイド 1 の電源電圧。           |

| 2       | $V_{OA}$           | ロジック出力 A。                     |

| 3       | $ m V_{IB}$        | ロジック入力 B。                     |

| 4       | $GND_1$            | グラウンド1。アイソレータ・サイド1のグラウンド基準です。 |

| 5       | $\mathrm{GND}_2$   | グラウンド2。アイソレータ・サイド2のグラウンド基準です。 |

| 6       | $V_{OB}$           | ロジック出力 B。                     |

| 7       | $V_{IA}$           | ロジック入力 A。                     |

| 8       | $V_{\mathrm{DD2}}$ | アイソレータ・サイド2の電源電圧。             |

Rev. 0 - 14/19 -

# 代表的な性能特性

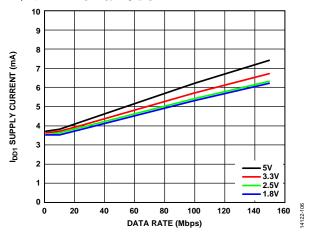

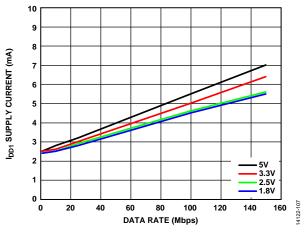

図 6. ADuM120N の各種電圧でのデータ・レート対 I<sub>DD1</sub> 電源電流

図 **7**. ADuM120N の各種電圧での データ・レート対 I<sub>DD2</sub> 電源電流

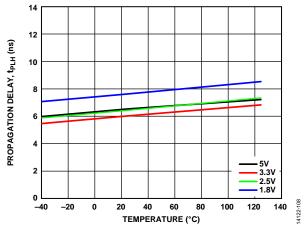

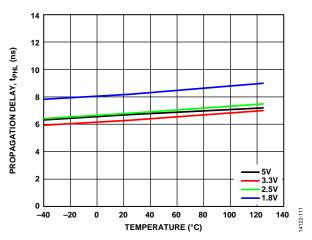

図 8. 各種電圧でのロジック・ハイ出力での 伝搬遅延(t<sub>PLH</sub>)の温度特性

図 9. ADuM121N の各種電圧でのデータ・レート対  $I_{DD1}$  電源電流

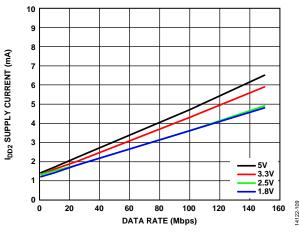

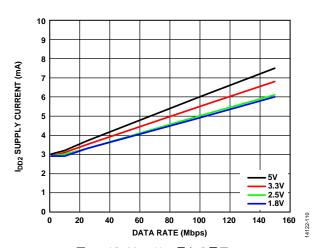

図 10. ADuM121N の異なる電圧での データ・レート対  $I_{DD2}$  電源電流

図 11. 各種電圧でロジック・ロー出力での 温度対伝搬遅延(t<sub>PHL</sub>)の温度特性

Rev. 0 - 15/19 -

### アプリケーション情報

### 概要

ADuM120N/ADuM121N は、高周波搬送波を使用して、複数のポリイミド絶縁層によって分離された iCoupler チップ・スケール・トランス・コイルを使った絶縁バリアをまたいでデータを伝送します。オン/オフ・キーイング(OOK)方式と図 13 および図 14 に示す差動アーキテクチャにより、

ADuM120N/ADuM121N は非常に小さい伝搬遅延と高速性を実現します。内蔵レギュレータと入出力設計手法により 1.7 V ~ 5.5 V の幅広いロジック電圧および電源電圧を使用可能で、1.8 V、2.5 V、3.3 V、および 5 V ロジックの電圧変換を行います。アーキテクチャは、高いコモンモード過渡耐圧と、電気的ノイズおよび磁気干渉に対する高い耐性を実現できるように設計されています。放射妨害波は、スペクトラム拡散 OOK 搬送波その他の手法によって最小限に抑えられています。

ADuM120N0/ADuM121N0 モデルの1 チャンネルの動作ブロック図を図13 に示します。このモデルはフェイルセーフ出力状態の条件がロー・レベルなので、入力状態がロー・レベルになると搬送波の波形がオフになります。入力側がオフになっているか動作していない場合は、ロー・レベルのフェイルセーフ出力状態(モデル番号に0が付きます)により、出力がロー・レベルに設定されます。ADuM120N1/ADuM121N1のフェイルセーフ出力状態はハイ・レベルです。入力状態がハイ・レベルの時に搬送波の波形がオフになる条件を図14に示します。入力側がオフになっているか動作していない場合は、ハイ・レベルのフェイルセーフ出力状態(モデル番号に1が付きます)により、出力がハイ・レベルに設定されます。フェイルセーフ出力状態がロー・レベルまたはフェイルセーフ出力状態がハイ・レベル

のモデル番号については、オーダー・ガイドを参照してください。

#### プリント回路基板(PCB)レイアウト

ADuM120N/ADuM121N デジタル・アイソレータに、ロジック・インタフェース用の外付けインタフェース回路は不要です。入力および出力電源ピンには、電源バイパスを行うことを強く推奨します(図 12 参照)。 $V_{DD1}$  のバイパス・コンデンサはピン 1 とピン 4 の間に、 $V_{DD2}$  のバイパス・コンデンサはピン 5 とピン 8 の間に接続するのが最も簡単です。バイパス・コンデンサの推奨値は  $0.01~\mu F \sim 0.1~\mu F$  です。コンデンサ両端と入力電源ピンの間のパターン長は 10~mm 以下にしてください。

図 12. 推奨するプリント回路基板 (PCB) レイアウト

高いコモンモード過渡電圧が発生するアプリケーションでは、 絶縁バリアをまたぐボード結合を最小限に抑えてください。さらに、すべての結合がデバイス側のすべてのピンで等しく生じるように基板レイアウトを設計する必要があります。この注意を怠ると、ピン間で生じる電位差がデバイスの絶対最大定格を超えてしまい、ラッチアップまたは恒久的な損傷が発生することがあります。

ボード・レイアウトのガイドラインについては、AN-1109 アプリケーション・ノートを参照してください。

図 13. ロー・フェイルセーフ出力ステート、1 チャンネル時の動作ブロック図

図 14. ハイ・フェイルセーフ出力ステート、1 チャンネル時の動作ブロック図

Rev. 0 — 16/19 —

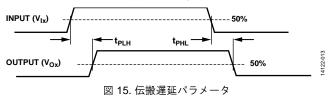

### 伝搬遅延に関係するパラメータ

伝搬遅延時間は、ロジック信号がデバイスを通過するのに要する時間を表わすパラメータです。ロジック 0 への伝搬遅延とロジック 1 への伝搬遅延は異なります。

パルス幅歪みは、これら2値間の最大差であり、入力信号のタイミングが出力信号で再現される精度を表します。

チャンネル間マッチングは、1 つの ADuM120N/ADuM121N デバイス内にある複数のチャンネル間の伝播遅延差の最大値を意味します。

伝搬遅延スキューは、同じ条件下で動作する複数の ADuM120N/ADuM121N デバイス間での伝搬遅延差の最大値で す。

#### ジッタの測定

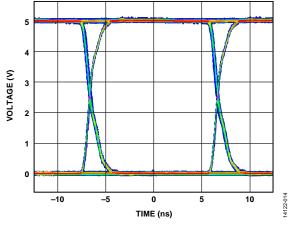

ADuM120N/ADuM121N のアイ・ダイアグラムを図 14 に示します。測定は Agilent 81110A パルス・パターン・ジェネレータを使用し、疑似ランダム・ビット・シーケンス(PRBS)2(n-1)により 150 Mbps で行いました。n = 14 で電源は 5 V です。 ジッタは、Tektronix Model 5104B オシロスコープ(1 GHz、10 GS/s)によって測定し、DPOJET ジッタおよびアイ・ダイアグラム解析ツールを使用しました。測定により得られたジッタは380 ps p-p で、これは ADuM120N/ADuM121N における標準的な値です。

図 16. ADuM120N/ADuM121N のアイ・ダイアグラム

### 絶縁寿命

すべての絶縁構造は、長時間電圧ストレスを受けると最終的に は劣化します。絶縁性能の低下率は、絶縁に加えられる電圧波 形の特性、および材料と材料接合部に依存します。