# 低ノイズ、低ドリフト、低消費電力 3軸 MEMS 加速度センサー

# ータシート

# ADXL356/ADXL357

#### SS特長

ハーメチック・パッケージによる長期にわたる優れた安定性 0 g オフセットの温度特性(全軸): 0.75 mg/°C(最大)

超低ノイズ密度(全軸): 80 μg/√Hz 低消費電力、V<sub>SUPPLY</sub>(LDO イネーブル)

ADXL356 測定モード: 150 µA ADXL357 測定モード: 200 µA

ADXL356/ADXL357 スタンパイ・モード: 21 µA

ADXL356 では、アナログ出力帯域幅を調整可能

ADXL357 のデジタル出力機能

デジタル・シリアル周辺機器インターフェース(SPI)/

機能限定 I2C インターフェースをサポート

20 ビット、A/D コンパータ(ADC)

同期サンプリングのデータ・インターポレーション・ルーチ ン

プログラマブル・ハイパス/ローパス・デジタル・フィルタ

温度センサー内蔵 電圧範囲のオプション

内部レギュレータ付き VsuppLy: 2.25 V ~ 3.6 V

内部低ドロップアウト(LDO)レギュレータをバイパスした

V<sub>1P8ANA</sub>、V<sub>1P8DIG</sub>: 1.8 V (代表値) ±10 %

動作温度範囲: -40 °C ~ +125 °C

14 端子、6 mm×5.6 mm×2.05 mm、LCC パッケージ、 0.26 g

#### アプリケーション

慣性計測ユニット(IMU)/姿勢方位基準装置(AHRS) プラットフォーム安定化装置

社会インフラの構造物モニタリング

地震画像処理

傾斜検知

ロボット

状態監視

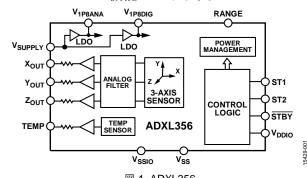

## 機能ブロック図

図 1. ADXL356

概要

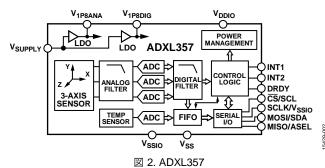

アナログ出力の ADXL356 とデジタル出力の ADXL357 は、低ノ イズ密度、低0gオフセット・ドリフト、低消費電力の3軸 MEMS 加速度センサーで、測定範囲選択可能です。ADXL356B は範囲  $\pm 10\,g$  と範囲  $\pm 20\,g$  をサポートし、ADXL356C は範囲  $\pm 10\,$ gと範囲 ±40 g を、ADXL357 は ±10.24 g、±20.48 g、±40.96 g の 範囲をサポートします。

ADXL356/ADXL357 は業界最先端のノイズ、全温度範囲にわた る最小オフセット・ドリフト、長時間安定性を提供し、最小の

キャリブレーションで高精度なアプリケーションを可能にしま

低ドリフト、低ノイズ、低消費電力の ADXL357 は、飛行中の IMU のような高い振動のある環境で高精度な傾斜計測が可能で す。ADXL356はより高い周波数まで低ノイズなので、無線によ る状態監視に最適です。

ADXL357 の多機能ピンの名称は、SPI または限定 I<sup>2</sup>C インター フェースの該当する機能のみで表されることがあります。

1米国特許8.472.270:9.041.462:8.665.627:8.917.099:6.892.576:9.297.825:7.956.621により保護されています。

アナログ・デバイヤズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって イン・ハインを入ばる、歴史学の情報が正確に目標とさるものであることを別していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

©2017 Analog Devices, Inc. All rights reserved

Rev. o

社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03(5402)8200

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 大阪営業所/〒532-0003 電話 06 (6350) 6868

# ADXL356/ADXL357

# 目次

| 特長                            | 1  |

|-------------------------------|----|

| アプリケーション                      | 1  |

| 機能ブロック図                       | 1  |

| 概要                            | 1  |

| 改訂履壓                          | 2  |

| 仕様                            | 3  |

| ADXL356 のアナログ出力               | 3  |

| ADXL357 のデジタル出力               | 4  |

| ADXL357 の SPI デジタル・インターフェース特性 | 6  |

| ADXL357 の PC デジタル・インターフェース特性  | 7  |

| 絶対最大定格                        | 8  |

| 熱抵抗                           | 8  |

| 推奨のハンダ付けプロファイル                | 8  |

| ESD に関する注意                    | 8  |

| ピン配置およびピン機能の説明                | 9  |

| 代表的な性能特性                      | 11 |

| アラン偏差(RAV)ADXL357 特性          | 19 |

| 動作原理                          | 20 |

| アプリケーション情報                    | 21 |

| アナログ出力                        | 21 |

| デジタル出力                        | 21 |

| 加速度検出軸                        | 22 |

| 電源シーケンス                       | 22 |

| 電源の説明                         | 22 |

| オーバーレンジ保護                     | 22 |

| セルフ・テスト                       | 22 |

| Filter                        | 23 |

| シリアル通信                        | 25 |

| SPI プロトコル                     | 25 |

| I <sup>2</sup> C プロトコル        | 26 |

| インターフェースからの加速度または温度の読出し       | 26 |

| FIFO                          | 28 |

| 割込み                           | 29 |

| DATA_RDY                      | 29 |

| DRDY ピン                       | 29 |

|   | FIFO_FULL                         | .29 |

|---|-----------------------------------|-----|

|   | FIFO_OVR                          | .29 |

|   | アクティビティ                           | .29 |

|   | 外部同期とインターポレーション                   | 29  |

| ١ | DXL357 のレジスタ・マップ                  | .32 |

| レ | ·ジスタの定義                           | .33 |

|   | アナログ・デバイセズ ID レジスタ                | .33 |

|   | アナログ・デバイセズ MEMS ID レジスタ           | .33 |

|   | デバイス ID レジスタ                      | .33 |

|   | 製品リビジョン ID レジスタ                   | .33 |

|   | ステータス・レジスタ                        | .33 |

|   | FIFO エントリ・レジスタ                    | .34 |

|   | 温度データ・レジスタ                        | .34 |

|   | X 軸データ・レジスタ                       | .34 |

|   | Y 軸データ・レジスタ                       | 35  |

|   | Z 軸データ・レジスタ                       | .35 |

|   | FIFO アクセス・レジスタ                    | 36  |

|   | X 軸のオフセット・トリム・レジスタ                | 36  |

|   | Y軸オフセット・トリム・レジスタ                  | 36  |

|   | Z軸オフセット・トリム・レジスタ                  | 37  |

|   | アクティビティ・イネーブル・レジスタ                | 37  |

|   | アクティビティ閾値レジスタ                     | .37 |

|   | アクティビティ・カウント・レジスタ                 | .37 |

|   | フィルタ設定レジスタ                        | .38 |

|   | FIFO サンプル・レジスタ                    | .38 |

|   | 割り込みピン (INTx) の機能マップレジスタ          | .38 |

|   | データ同期                             | .39 |

|   | I <sup>2</sup> C 速度、割り込み極性、範囲レジスタ | .39 |

|   | パワー・コントロール・レジスタ                   | .39 |

|   | セルフ・テスト・レジスタ                      | 40  |

|   | リセット・レジスタ                         | 40  |

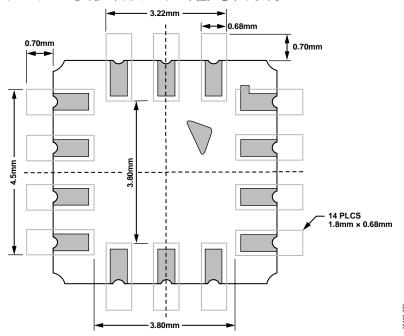

| 9 | CB フットプリント・パターン                   | .41 |

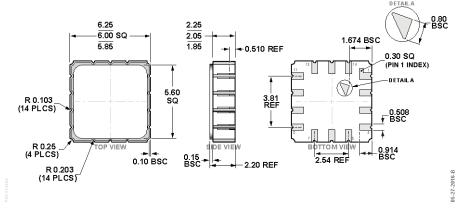

| ሃ | 形寸法                               | .42 |

|   | オーダー・ガイド                          | .42 |

# 改訂履歴

2/2017—Revision 0: Initial Version

# 仕様

# ADXL356 のアナログ出力

特に指定がない限り、 $T_A=25$  °C、 $V_{SUPPLY}=3.3$  V、x 軸加速度および y 軸加速度 = 0 g、z 軸加速度 = 1 g、フルスケール・レンジ = ±10 g。

表 1.

| 衣 1.<br>Parameter                                                              | Test Conditions/Comments                             | Min          | Тур          | Max                   | Unit            |

|--------------------------------------------------------------------------------|------------------------------------------------------|--------------|--------------|-----------------------|-----------------|

| SENSOR INPUT                                                                   | Each axis                                            |              |              |                       |                 |

| Output Full-Scale Range (FSR)                                                  | ADXL356B, supports two ranges                        |              | ±10/±20      |                       | g               |

|                                                                                | ADXL356C, supports two ranges                        |              | ±10/±40      |                       | g               |

| Resonant Frequency <sup>1</sup>                                                | , 11                                                 |              | 5.5          |                       | kHz             |

| Nonlinearity                                                                   | ±10 g                                                |              | 0.1          |                       | %               |

| Cross Axis Sensitivity                                                         |                                                      |              | 1            |                       | %               |

| SENSITIVITY                                                                    | Ratiometric to V <sub>1P8ANA</sub>                   |              |              |                       | 1.2             |

| Sensitivity at X <sub>OUT</sub> , Y <sub>OUT</sub> , Z <sub>OUT</sub>          | ±10 g                                                | 73.6         | 80           | 86.4                  | mV/g            |

| Sensitivity at 12001, 1001, 2001                                               | ±20 g                                                | 36.8         | 40           | 43.2                  | mV/g            |

|                                                                                | ±40 g                                                | 18.4         | 20           | 21.6                  | mV/g            |

| Sensitivity Change due to Temperature                                          | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 10.4         | ±0.01        | 21.0                  | %/°C            |

| 0 g OFFSET                                                                     | Each axis, $\pm 10 g$                                |              | ±0.01        |                       | 707 C           |

| $0 g$ Output for $X_{OUT}$ , $Y_{OUT}$ , $Z_{OUT}$                             | Referred to V <sub>1P8ANA</sub> /2                   | -375         | ±125         | +375                  | ma              |

| 0 g Offset vs. Temperature (X-Axis, Y-Axis, and Z-Axis) <sup>2</sup>           | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | -0.75        | ±0.5         | +0.75                 | mg<br>mg/°C     |

| Vibration Rectification Error (VRE) <sup>3</sup>                               | Offset due to 7.5 g rms vibration,                   | -0.73        | ±0.3<br><0.1 | +0.75                 |                 |

| Vioration Rectification Effor (VRE)                                            | $\pm 10 g$ range, in a 1 g orientation               |              | <0.1         |                       | g               |

| NOISE DENSITY                                                                  | ±10 g                                                |              |              |                       |                 |

| X-Axis, Y-Axis, and Z-Axis                                                     | ±10 g                                                |              | 80           |                       | μ <i>g</i> /√Hz |

| Velocity Random Walk                                                           | X-axis and y-axis                                    |              | 45           |                       | μm/sec/√Hr      |

| Velocity Random Walk                                                           | •                                                    |              |              |                       |                 |

| D. L. VIDANIA DINA                                                             | Z-axis                                               |              | 65           |                       | μm/sec/√Hr      |

| BANDWIDTH                                                                      |                                                      |              |              |                       |                 |

| Internal Low-Pass Filter Frequency                                             | Fixed frequency, 50% response attenuation            |              | 1500         |                       | Hz              |

| SELF TEST                                                                      |                                                      |              |              |                       |                 |

| Output Change                                                                  |                                                      |              |              |                       |                 |

| Z-Axis                                                                         | ±10 g range                                          |              | 1.25         |                       | g               |

| POWER SUPPLY                                                                   |                                                      |              |              |                       |                 |

| Voltage Range                                                                  |                                                      |              |              |                       |                 |

| ${ m V_{SUPPLY}}^4$                                                            |                                                      | 2.25         | 2.5          | 3.6                   | V               |

| $V_{ m DDIO}$                                                                  |                                                      | $V_{1P8DIG}$ | 2.5          | 3.6                   | V               |

| $V_{IP8ANA}$ , $V_{IP8DIG}$ with Internal Low Dropout Regulator (LDO) Bypassed | $V_{SUPPLY} = 0 V$                                   | 1.62         | 1.8          | 1.98                  | V               |

| Current                                                                        |                                                      |              |              |                       |                 |

| Measurement Mode                                                               |                                                      |              |              |                       |                 |

| V <sub>SUPPLY</sub> (LDO Enabled)                                              |                                                      |              | 150          |                       | μA              |

| V <sub>IPSANA</sub> (LDO Disabled)                                             |                                                      |              | 138          |                       | μA              |

| V <sub>IPSDIG</sub> (LDO Disabled)                                             |                                                      |              | 12           |                       | μA              |

| Standby Mode                                                                   |                                                      |              |              |                       | m''             |

| V <sub>SUPPLY</sub> (LDO Enabled)                                              |                                                      |              | 21           |                       | μΑ              |

| V <sub>1P8ANA</sub> (LDO Disabled)                                             |                                                      |              | 7            |                       | μΑ              |

| V <sub>IPSDIG</sub> (LDO Disabled)                                             |                                                      |              | 10           |                       | μΑ              |

| Turn On Time <sup>5</sup>                                                      | 10 g range                                           |              | <10          |                       | ms              |

| Turn On Thine                                                                  | Power-off to standby                                 |              | <10          |                       | ms              |

| OUTPUT AMPLIFIER                                                               | 1 ower-our to standay                                |              | <b>\10</b>   |                       | 1115            |

| Swing                                                                          | No load                                              | 0.03         |              | V <sub>IP8ANA</sub> – | v               |

| Output Series Resistance                                                       |                                                      |              | 32           | 0.03                  | kΩ              |

| output sories resistance                                                       |                                                      |              | ے د          |                       | N22             |

# ADXL356/ADXL357

| Parameter                   | Test Conditions/Comments | Min | Тур   | Max  | Unit  |

|-----------------------------|--------------------------|-----|-------|------|-------|

| TEMPERATURE SENSOR          |                          |     |       |      |       |

| Output at 25°C              |                          |     | 892.2 |      | mV    |

| Scale Factor                |                          |     | 3.0   |      | mV/°C |

| TEMPERATURE                 |                          |     |       |      |       |

| Operating Temperature Range |                          | -40 |       | +125 | °C    |

<sup>1</sup> 共振周波数は、センサーの特性です。バイパス不能な内蔵アナログ 1.5 kHz (-6 dB) の sinc ローパス・フィルタが実際の出力応答を制限します。

# ADXL357 のデジタル出力

特に指定のない限り、 $T_A = 25$  °C、 $V_{SUPPLY} = 3.3$  V、X 軸加速度および Y 軸加速度 = 0 g、Z 軸加速度 = 1 g、フルスケール・レンジ  $= \pm 10.24$  g、出力データ・レート (ODR) = 500 Hz。多機能ピンの名称は、該当する機能のみで表されることがあります。

#### 表 2.

| Parameter                                                              | Test Conditions/Comments                                                        | Min    | Тур         | Max    | Unit      |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------|-------------|--------|-----------|

| SENSOR INPUT                                                           | Each axis                                                                       |        |             |        |           |

| Output Full Scale Range (FSR)                                          | User selectable                                                                 |        | $\pm 10.24$ |        | g         |

|                                                                        |                                                                                 |        | $\pm 20.48$ |        | g         |

|                                                                        |                                                                                 |        | ±40.96      |        | g         |

| Nonlinearity                                                           | ±10 g                                                                           |        | 0.1         |        | % FSR     |

| Cross Axis Sensitivity                                                 |                                                                                 |        | 1           |        | %         |

| SENSITIVITY                                                            | Each axis                                                                       |        |             |        |           |

| X-Axis, Y-Axis, and Z-Axis Sensitivity                                 | ±10 g                                                                           | 47,104 | 51,200      | 55,296 | LSB/g     |

|                                                                        | ±20 g                                                                           | 23,552 | 25,600      | 27,648 | LSB/g     |

|                                                                        | ±40 g                                                                           | 11,776 | 12,800      | 13,824 | LSB/g     |

| X-Axis, Y-Axis, and Z-Axis Scale Factor                                | ±10 g                                                                           |        | 19.5        |        | μg/LSB    |

|                                                                        | ±20 g                                                                           |        | 39          |        | μg/LSB    |

|                                                                        | ±40 g                                                                           |        | 78          |        | μg/LSB    |

| Sensitivity Change due to Temperature                                  | $T_A = -40$ °C to $+125$ °C                                                     |        | $\pm 0.01$  |        | %/°C      |

| 0 g OFFSET                                                             | Each axis, ±10 g                                                                |        |             |        |           |

| X-Axis, Y-Axis, and Z-Axis 0 g Output                                  |                                                                                 | -375   | ±125        | +375   | mg        |

| 0 g Offset vs. Temperature (X-Axis, Y-Axis, and Z-Axis) <sup>1</sup>   | $T_A = -40$ °C to $+125$ °C                                                     | -0.75  | $\pm 0.50$  | +0.75  | mg/°C     |

| Vibration Rectification Error (VRE) <sup>2</sup>                       | Offset due to 7.5 $g$ rms vibration, $\pm 10$ $g$ range, in a 1 $g$ orientation |        | <0.1        |        | g         |

| NOISE DENSITY                                                          | ±10 g                                                                           |        |             |        |           |

| X-Axis, Y-Axis, and Z-Axis                                             |                                                                                 |        | 80          |        | μg/√Hz    |

| Velocity Random Walk                                                   | X-axis and y-axis                                                               |        | 45          |        | μm/sec/√H |

|                                                                        | Z-axis                                                                          |        | 65          |        | μm/sec/√H |

| OUTPUT DATA RATE AND BANDWIDTH                                         |                                                                                 |        |             |        |           |

| ADC Resolution                                                         |                                                                                 |        | 20          |        | bits      |

| Low-Pass Filter Passband Frequency                                     | User programmable, Register 0x28                                                | 1      |             | 1000   | Hz        |

| High-Pass Filter Passband Frequency When Enabled (Disabled by Default) | User programmable, Register 0x28 for 4 kHz ODR                                  | 0.0095 |             | 10     | Hz        |

| SELF TEST                                                              |                                                                                 |        |             |        |           |

| Output Change                                                          |                                                                                 |        |             |        |           |

| Z-Axis                                                                 | $\pm 10 g$ range                                                                |        | 1.25        |        | g         |

Rev. 0 - 4/42 -

$<sup>^2</sup>$  温度変化は  $^-40$  °C  $\sim$  +25 °C または +25 °C  $\sim$  +125 °C です。

$<sup>^3</sup>$  VRE 測定は DC オフセットのシフトで、デバイスは 50 Hz  $\sim 2$  kHz のランダムな振動 12.5 g ms の影響を受けます。テスト対象デバイス(DUT)では、  $\pm 10$  g の範囲と 4 kHz の出力データ・レートが設定されています。レンジ設定と VRE スケール

<sup>&</sup>lt;sup>4</sup> V<sub>IPSANA</sub> と V<sub>IPSDIG</sub> が内部で発生する場合、V<sub>SUPPLY</sub> が有効です。LDO を無効にして V<sub>IPSANA</sub> と V<sub>IPSDIG</sub> を外部から駆動するには、V<sub>SUPPLY</sub> を V<sub>SS</sub> に接続します。

<sup>5</sup>出力の最終値が 5 mg 以内の場合、測定スタンバイ・モードになります。

| Parameter                                                              | Test Conditions/Comments | Min                   | Тур   | Max  | Unit   |

|------------------------------------------------------------------------|--------------------------|-----------------------|-------|------|--------|

| POWER SUPPLY                                                           |                          |                       |       |      |        |

| Voltage Range                                                          |                          |                       |       |      |        |

| V <sub>SUPPLY</sub> Operating <sup>3</sup>                             |                          | 2.25                  | 2.5   | 3.6  | V      |

| $ m V_{DDIO}$                                                          |                          | $V_{1P8\mathrm{DIG}}$ | 2.5   | 3.6  | V      |

| V <sub>1P8ANA</sub> and V <sub>1P8DIG</sub> with Internal LDO Bypassed | $V_{SUPPLY} = 0 V$       | 1.62                  | 1.8   | 1.98 | V      |

| Current                                                                |                          |                       |       |      |        |

| Measurement Mode                                                       |                          |                       |       |      |        |

| V <sub>SUPPLY</sub> (LDO Enabled)                                      |                          |                       | 200   |      | μΑ     |

| V <sub>1P8ANA</sub> (LDO Disabled)                                     |                          |                       | 160   |      | μΑ     |

| V <sub>1P8DIG</sub> (LDO Disabled)                                     |                          |                       | 35.5  |      | μΑ     |

| Standby Mode                                                           |                          |                       |       |      |        |

| V <sub>SUPPLY</sub> (LDO Enabled)                                      |                          |                       | 21    |      | μΑ     |

| V <sub>1P8ANA</sub> (LDO Disabled)                                     |                          |                       | 7     |      | μΑ     |

| V <sub>1P8DIG</sub> (LDO Disabled)                                     |                          |                       | 10    |      | μΑ     |

| Turn On Time <sup>4</sup>                                              | ±10 g range              |                       | <10   |      | ms     |

|                                                                        | Power-off to standby     |                       | <10   |      | ms     |

| TEMPERATURE SENSOR                                                     |                          |                       | •     |      |        |

| Output at 25°C                                                         |                          |                       | 1852  |      | LSB    |

| Scale Factor                                                           |                          |                       | -9.05 |      | LSB/°C |

| TEMPERATURE                                                            |                          |                       |       |      |        |

| Operating Temperature Range                                            |                          | -40                   |       | +125 | °C     |

<sup>&</sup>lt;sup>1</sup> 温度変化は-40 °C  $\sim$  +25 °C または+25 °C  $\sim$  +125 °C です。

Rev. 0 - 5/42 -

$<sup>^2</sup>$  VRE 測定値は DC オフセットのシフトで、デバイスは  $50~\rm{Hz}\sim 2~\rm{kHz}$  のランダムな振動  $12.5~g~\rm{rms}$  の影響を受けます。 DUT には、 $\pm 2~g~\rm{o}$  範囲と  $4~\rm{kHz}$  の出力データ・レートが設定されています。 レンジ設定と VRE スケール

$<sup>^3</sup>$   $V_{IP8ANA}$  と  $V_{IP8DIG}$  が内部で発生する場合、 $V_{SUPPLY}$  は有効です。LDO を無効にして  $V_{IP8ANA}$  と  $V_{IP8DIG}$  を外部から駆動するには、 $V_{SUPPLY}$  を  $V_{SS}$  に接続します。

<sup>4</sup>出力の最終値が1mg以内の場合は、測定スタンバイ・モードになります。

# データシート

# ADXL357 の SPI デジタル・インターフェース特性

多機能ピンの名称は、該当する機能のみで表されることがあります。

表 3.

| Parameter              | Symbol             | Test Conditions/Comments                | Min                       | Тур | Max                       | Unit |

|------------------------|--------------------|-----------------------------------------|---------------------------|-----|---------------------------|------|

| DC INPUT LEVELS        |                    |                                         |                           |     |                           |      |

| Input Voltage          |                    |                                         |                           |     |                           |      |

| Low Level              | $V_{\rm IL}$       |                                         |                           |     | $0.3 \times V_{\rm DDIO}$ | V    |

| High Level             | $V_{IH}$           |                                         | $0.7 \times V_{DDIO}$     |     |                           | V    |

| Input Current          |                    |                                         |                           |     |                           |      |

| Low Level              | ${ m I}_{ m IL}$   | $V_{IN} = 0 V$                          | -0.1                      |     |                           | μΑ   |

| High Level             | $I_{IH}$           | $V_{\rm IN} = V_{ m DDIO}$              |                           |     | 0.1                       | μΑ   |

| DC OUTPUT LEVELS       |                    |                                         |                           |     |                           |      |

| Output Voltage         |                    |                                         |                           |     |                           |      |

| Low Level              | $V_{OL}$           | $I_{OL} = I_{OL, MIN}$                  |                           |     | $0.2 \times V_{\rm DDIO}$ | V    |

| High Level             | $V_{OH}$           | $I_{OH} = I_{OH, MAX}$                  | $0.8 \times V_{\rm DDIO}$ |     |                           | V    |

| Output Current         |                    |                                         |                           |     |                           |      |

| Low Level              | $I_{OL}$           | $V_{OL} = V_{OL, MAX}$                  | -10                       |     |                           | mA   |

| High Level             | $I_{OH}$           | $V_{\mathrm{OH}} = V_{\mathrm{OH,MIN}}$ |                           |     | 4                         | mA   |

| AC INPUT LEVELS        |                    |                                         |                           |     |                           |      |

| SCLK Frequency         |                    |                                         | 0.1                       |     | 10                        | MHz  |

| SCLK High Time         | $t_{ m HIGH}$      |                                         | 40                        |     |                           | ns   |

| SCLK Low Time          | $t_{\rm LOW}$      |                                         | 40                        |     |                           | ns   |

| CS Setup Time          | $t_{CSS}$          |                                         | 20                        |     |                           | ns   |

| CS Hold Time           | $t_{CSH}$          |                                         | 20                        |     |                           | ns   |

| CS Disable Time        | $t_{CSD}$          |                                         | 40                        |     |                           | ns   |

| Rising SCLK Setup Time | t <sub>SCLKS</sub> |                                         | 20                        |     |                           | ns   |

| MOSI Setup Time        | $t_{SU}$           |                                         | 20                        |     |                           | ns   |

| MOSI Hold Time         | $t_{ m HD}$        |                                         | 20                        |     |                           | ns   |

| AC OUTPUT LEVELS       |                    |                                         |                           |     |                           |      |

| Propagation Delay      | $t_{ m P}$         | $C_{LOAD} = 30 \text{ pF}$              |                           |     | 30                        | ns   |

| Enable MISO Time       | $t_{\rm EN}$       |                                         | 30                        |     |                           | ns   |

| Disable MISO Time      | $t_{\rm DIS}$      |                                         |                           |     | 20                        | ns   |

Rev. 0 - 6/42 -

# データシート

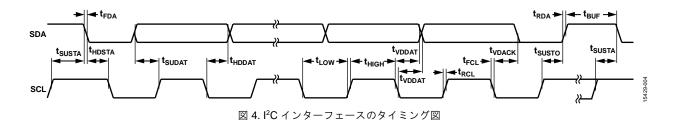

# ADXL357 の I<sup>2</sup>C デジタル・インターフェース特性

多機能ピンの名称は、該当する機能のみで表されることがあります。

表 4.

|                                           |                    | Test Conditions/                                                                     | I2C_HS =                   | 0 (Fast | Mode)                     | I2C_HS =              | 1 (High S | Speed Mode)               |      |

|-------------------------------------------|--------------------|--------------------------------------------------------------------------------------|----------------------------|---------|---------------------------|-----------------------|-----------|---------------------------|------|

| Parameter                                 | Symbol             | Comments                                                                             | Min                        | Тур     | Max                       | Min                   | Тур       | Max                       | Unit |

| DC INPUT LEVELS                           |                    |                                                                                      |                            |         |                           |                       |           |                           |      |

| Input Voltage                             |                    |                                                                                      |                            |         |                           |                       |           |                           |      |

| Low Level                                 | $V_{\rm IL}$       |                                                                                      |                            |         | $0.3 \times V_{\rm DDIO}$ |                       |           | $0.3 \times V_{\rm DDIO}$ | V    |

| High Level                                | $V_{IH}$           |                                                                                      | $0.7 \times V_{DDIO}$      |         |                           | $0.7 \times V_{DDIO}$ |           |                           | V    |

| Hysteresis of Schmitt<br>Triggered Inputs | $V_{HYS}$          |                                                                                      | $0.05 \times V_{DDIO}$     |         |                           | $0.1 \times V_{DDIO}$ |           |                           | μΑ   |

| Input Current                             | $I_{\rm IL}$       | $\begin{array}{l} 0.1 \times V_{DDIO} < V_{IN} < \\ 0.9 \times V_{DDIO} \end{array}$ | -10                        |         | +10                       |                       |           |                           | μΑ   |

| DC OUTPUT LEVELS                          |                    |                                                                                      |                            |         |                           |                       |           |                           |      |

| Output Voltage                            |                    | $I_{OL} = 3 \text{ mA}$                                                              |                            |         |                           |                       |           |                           |      |

| Low Level                                 | $V_{OL1}$          | $V_{\rm DDIO} > 2 \text{ V}$                                                         |                            |         | 0.4                       |                       |           |                           | V    |

|                                           | $V_{OL2}$          | $V_{DDIO} \le 2 V$                                                                   |                            |         | $0.2 \times V_{DDIO}$     |                       |           |                           | V    |

| Output Current                            |                    |                                                                                      |                            |         |                           |                       |           |                           |      |

| Low Level                                 | $I_{OL}$           | $V_{OL} = 0.4 \text{ V}$                                                             | 20                         |         |                           |                       |           |                           | mA   |

|                                           |                    | $V_{OL} = 0.6 \text{ V}$                                                             | 6                          |         |                           |                       |           |                           | mA   |

| AC INPUT LEVELS                           |                    |                                                                                      |                            |         |                           |                       |           |                           |      |

| SCL Frequency                             |                    |                                                                                      | 0                          |         | 1                         | 0                     |           | 3.4                       | MHz  |

| SCL High Time                             | t <sub>HIGH</sub>  |                                                                                      | 260                        |         |                           | 60                    |           |                           | ns   |

| SCL Low Time                              | $t_{LOW}$          |                                                                                      | 500                        |         |                           | 160                   |           |                           | ns   |

| Start Setup Time                          | $t_{SUSTA}$        |                                                                                      | 260                        |         |                           | 160                   |           |                           | ns   |

| Start Hold Time                           | $t_{HDSTA}$        |                                                                                      | 260                        |         |                           | 160                   |           |                           | ns   |

| SDA Setup Time                            | $t_{SUDAT}$        |                                                                                      | 50                         |         |                           | 10                    |           |                           | ns   |

| SDA Hold Time                             | $t_{HDDAT}$        |                                                                                      | 0                          |         |                           | 0                     |           |                           | ns   |

| Stop Setup Time                           | $t_{SUSTO}$        |                                                                                      | 260                        |         |                           | 160                   |           |                           | ns   |

| Bus Free Time                             | $t_{\mathrm{BUF}}$ |                                                                                      | 500                        |         |                           |                       |           |                           | ns   |

| SCL Input Rise Time                       | $t_{RCL}$          |                                                                                      |                            |         | 120                       |                       |           | 80                        | ns   |

| SCL Input Fall Time                       | $t_{FCL}$          |                                                                                      |                            |         | 120                       |                       |           | 80                        | ns   |

| SDA Input Rise Time                       | $t_{RDA}$          |                                                                                      |                            |         | 120                       |                       |           | 160                       | ns   |

| SDA Input Fall Time                       | $t_{FDA}$          |                                                                                      |                            |         | 120                       |                       |           | 160                       | ns   |

| Width of Spikes to                        | $t_{SP}$           | Not shown in Figure 4                                                                |                            |         | 50                        |                       |           | 10                        | ns   |

| Suppress                                  |                    |                                                                                      |                            |         |                           |                       |           |                           |      |

| AC OUTPUT LEVELS                          |                    |                                                                                      |                            |         |                           |                       |           |                           |      |

| Propagation Delay                         |                    | $C_{LOAD} = 500 \text{ pF}$                                                          |                            |         |                           |                       |           |                           |      |

| Data                                      | $t_{VDDAT}$        |                                                                                      | 97                         |         | 450                       | 27                    |           | 135                       | ns   |

| Acknowledge                               | t <sub>VDACK</sub> |                                                                                      | 20                         |         | 450                       |                       |           |                           | ns   |

| Output Fall Time                          | t <sub>F</sub>     | Not shown in Figure 4                                                                | $20 \times (V_{DDIO}/5.5)$ |         | 120                       |                       |           |                           | ns   |

Rev. 0 - 7/42 -

# 絶対最大定格

#### 表 5.

| Parameter                                                                                                              | Rating                                              |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Acceleration (Any Axis, 0.1 ms)                                                                                        | 5000 g                                              |

| $V_{SUPPLY}, V_{DDIO}$                                                                                                 | 5.4 V                                               |

| V <sub>1P8ANA</sub> , V <sub>1P8DIG</sub> Configured as Inputs                                                         | 1.98 V                                              |

| ADXL356                                                                                                                |                                                     |

| Digital Inputs (RANGE, ST1, ST2, STBY)                                                                                 | $-0.3 \text{ V to V}_{DDIO} + 0.3 \text{ V}$        |

| Analog Outputs $(X_{OUT}, Y_{OUT}, Z_{OUT}, TEMP)$                                                                     | $-0.3 \text{ V to V}_{1P8ANA} + 0.3 \text{ V}$      |

| ADXL357                                                                                                                |                                                     |

| Digital Pins $\overline{\text{CS}}/\text{SCL}$ , SCLK/V <sub>SSIO</sub> ,<br>MOSI/SDA, MISO/ASEL, INT1,<br>INT2, DRDY) | $-0.3 \text{ V to V}_{\text{DDIO}} + 0.3 \text{ V}$ |

| Operating Temperature Range                                                                                            | −40°C to +125°C                                     |

| Storage Temperature Range                                                                                              | −55°C to +150°C                                     |

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この仕様規定はストレ ス定格のみを指定するものであり、この仕様の動作のセクショ ンに記載する規定値以上でのデバイス動作を定めたものではあ りません。製品を長時間にわたり絶対最大定格状態に置くと、 製品の信頼性に影響を与えることがあります。

### 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接 関連しています。PCB の熱設計には、細心の注意を払う必要が あります。

θιA は、1 立方フィートの密封容器内で測定された、自然対流でのジャンクションから周囲への熱抵抗です。

表 6. 熱抵抗

| Package Type        | $\theta_{JA}$ | Unit |

|---------------------|---------------|------|

| E-14-1 <sup>1</sup> | 42            | °C/W |

<sup>「</sup>熱抵抗のシミュレーション値は、4つのサーマル・ビアを備えた JEDEC 2S2P サーマル・テスト・ボードに基づいています。JEDEC JESD51 を参照してください。

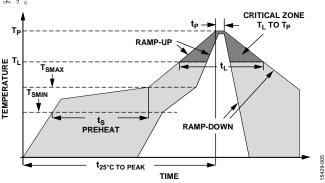

# 推奨のハンダ付けプロファイル

図5と表7に、推奨するハンダ付けプロファイルの詳細を示します。

図 5. 推奨のハンダ付けプロファイル

表 7. 推奨のハンダ付けプロファイル

|                                                                               | Condition            |                      |  |

|-------------------------------------------------------------------------------|----------------------|----------------------|--|

| Profile Feature                                                               | Sn63/Pb37            | Pb-Free              |  |

| Average Ramp Rate from Liquid Temperature $(T_L)$ to Peak Temperature $(T_P)$ | 3°C/sec<br>maximum   | 3°C/sec<br>maximum   |  |

| Preheat                                                                       |                      |                      |  |

| Minimum Temperature (T <sub>SMIN</sub> )                                      | 100°C                | 150°C                |  |

| Maximum Temperature (T <sub>SMAX</sub> )                                      | 150°C                | 200°C                |  |

| Time from $T_{SMIN}$ to $T_{SMAX}$ ( $t_S$ )                                  | 60 sec to<br>120 sec | 60 sec to<br>180 sec |  |

| $T_{SMAX}$ to $T_L$ Ramp-Up Rate                                              | 3°C/sec<br>maximum   | 3°C/sec<br>maximum   |  |

| Liquid Temperature (T <sub>L</sub> )                                          | 183°C                | 217°C                |  |

| Time Maintained Above $T_L(t_L)$                                              | 60 sec to<br>150 sec | 60 sec to<br>150 sec |  |

| Peak Temperature (T <sub>P</sub> )                                            | 240°C +<br>0°C/-5°C  | 260°C +<br>0°C/-5°C  |  |

| Time of Actual $T_P - 5^{\circ}C$ ( $t_P$ )                                   | 10 sec to<br>30 sec  | 20 sec to<br>40 sec  |  |

| Ramp-Down Rate                                                                | 6°C/sec<br>maximum   | 6°C/sec<br>maximum   |  |

| Time from 25°C to Peak<br>Temperature (t <sub>25°C TO PEAK</sub> )            | 6 minutes<br>maximum | 8 minutes<br>maximum |  |

## ESD に関する注意

#### ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. 0 - 8/42 -

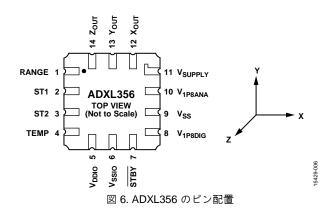

# ピン配置およびピン機能の説明

表 8. ADXL356 のピン機能の説明

| Pin No. | Mnemonic              | Description                                                                                           |

|---------|-----------------------|-------------------------------------------------------------------------------------------------------|

| 1       | RANGE                 | 範囲選択ピン。このピンをグラウンドに設定して $\pm 10g$ の範囲を選択するか、このピンを ${ m V}_{ m DDIO}$ に設定して $\pm 20g$ また                |

|         |                       | は $\pm 40g$ の範囲を選択します。このピンは、モデルによって異なります(オーダー・ガイドのセクションを参照)。                                          |

| 2       | ST1                   | セルフ・テスト・ピン 1。このピンを使用して、セルフ・テスト・モードを有効にします。                                                            |

| 3       | ST2                   | セルフ・テスト・ピン 2。このピンを使用して、電子機械式セルフ・テスト動作をアクティブにします。                                                      |

| 4       | TEMP                  | 温度センサーの出力。                                                                                            |

| 5       | $V_{ m DDIO}$         | デジタル・インターフェースの電源電圧。                                                                                   |

| 6       | $V_{SSIO}$            | デジタル・グラウンド。                                                                                           |

| 7       | STBY                  | スタンバイ・モードまたは測定モードの選択ピン。このピンをグラウンドに設定すると、スタンバイ・モードになり                                                  |

|         |                       | ます。このピンを $V_{ m DDIO}$ に設定すると、測定モードになります。                                                             |

| 8       | $V_{1P8\mathrm{DIG}}$ | デジタル電源。このピンには、デカップリング・コンデンサが必要です。 $\mathbf{V}_{	ext{SUPPLY}}$ を $\mathbf{V}_{	ext{SS}}$ に接続する場合、このピンに |

|         |                       | 外部から電圧を供給します。                                                                                         |

| 9       | $V_{SS}$              | アナログ・グラウンド。                                                                                           |

| 10      | $V_{1P8ANA}$          | アナログ電源。このピンには、デカップリング・コンデンサが必要です。 ${f V}_{	ext{SUPPLY}}$ を ${f V}_{	ext{SS}}$ に接続する場合、このピンに           |

|         |                       | 外部から電圧を供給します。                                                                                         |

| 11      | $V_{SUPPLY}$          | 電源電圧。 $V_{SUPPLY}$ が $2.25~V\sim 3.6~V$ の場合、 $V_{SUPPLY}$ によって内部 LDO レギュレータが有効になり、 $V_{IP8DIG}$ と     |

|         |                       | $V_{1P8ANA}$ が発生します。 $V_{SUPPLY} = V_{SS}$ の場合、 $V_{1P8DIG}$ と $V_{1P8ANA}$ は外部から供給されます。              |

| 12      | $X_{OUT}$             | X軸の出力。                                                                                                |

| 13      | $Y_{OUT}$             | Y軸の出力。                                                                                                |

| 14      | $Z_{OUT}$             | Z軸の出力。                                                                                                |

Rev. 0 - 9/42 -

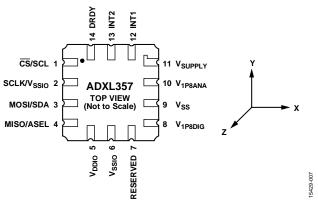

図 7. ADXL357 のピン配置(SPI/I<sup>2</sup>C)

表 9. ADXL357 のピン機能の説明

| Pin No. | Mnemonic               | Description                                                                                                                                                                             |

|---------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CS/SCL                 | SPI (CS) のチップ選択                                                                                                                                                                         |

|         |                        | I <sup>2</sup> C 用のシリアル通信クロック(SCL)。                                                                                                                                                     |

| 2       | SCLK/V <sub>SSIO</sub> | SPI 用のシリアル通信クロック (SCLK)。                                                                                                                                                                |

|         |                        | $I^2C$ モードの有効化( $V_{SSIO}$ )。このピンをピン $6$ ( $V_{SSIO}$ )に接続すると、 $I^2C$ モードが有効になります。                                                                                                      |

| 3       | MOSI/SDA               | SPI 用のマスター出力/スレーブ入力 (MOSI)。                                                                                                                                                             |

|         |                        | I <sup>2</sup> C 用のシリアル・データ (SDA)。                                                                                                                                                      |

| 4       | MISO/ASEL              | SPI インターフェース用のマスター入力/スレーブ出力 (MISO)。                                                                                                                                                     |

|         |                        | I'C 用の代替 I'C アドレス選択(ASEL)。                                                                                                                                                              |

| 5       | $V_{ m DDIO}$          | デジタル・インターフェースの電源電圧。                                                                                                                                                                     |

| 6       | $V_{SSIO}$             | デジタル・グラウンド。                                                                                                                                                                             |

| 7       | RESERVED               | 予備。このピンはグラウンドに接続するか、オープンのままにできます。                                                                                                                                                       |

| 8       | V <sub>1P8DIG</sub>    | デジタル電源。このピンには、デカップリング・コンデンサが必要です。 $V_{SUPPLY}$ を $V_{SS}$ に接続する場合、このピンに外部から電圧を供給します。                                                                                                    |

| 9       | $V_{SS}$               | アナログ・グラウンド。                                                                                                                                                                             |

| 10      | V <sub>1P8ANA</sub>    | アナログ電源。このピンには、デカップリング・コンデンサが必要です。 $V_{SUPPLY}$ を $V_{SS}$ に接続する場合、このピンに外部から電圧を供給します。                                                                                                    |

| 11      | $V_{SUPPLY}$           | 電源電圧。 $V_{SUPPLY}$ が 2.25 $V \sim 3.6 \ V$ の場合、 $V_{SUPPLY}$ によって内部 LDO が有効になり、 $V_{IP8DIG}$ と $V_{IP8ANA}$ が発生します。 $V_{SUPPLY} = V_{SS}$ の場合、 $V_{IP8DIG}$ と $V_{IP8ANA}$ は外部から供給されます。 |

| 12      | INT1                   | 割込みピン1。                                                                                                                                                                                 |

| 13      | INT2                   | 割込みピン 2。                                                                                                                                                                                |

| 14      | DRDY                   | データ・レディ・ピン。                                                                                                                                                                             |

Rev. 0 - 10/42 -

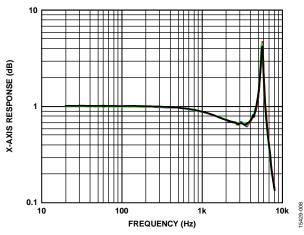

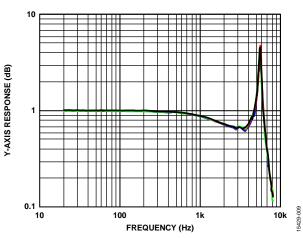

# 代表的な性能特性

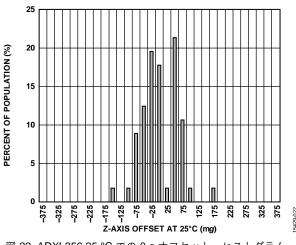

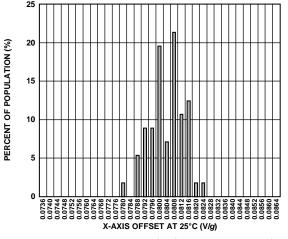

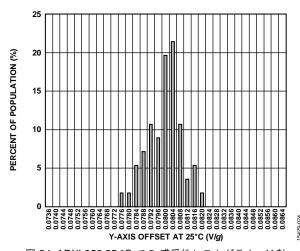

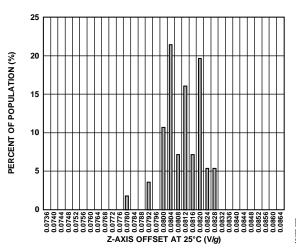

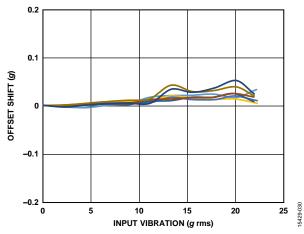

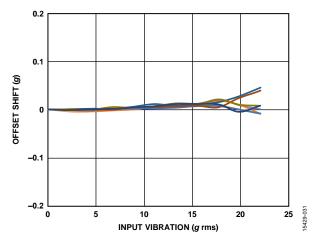

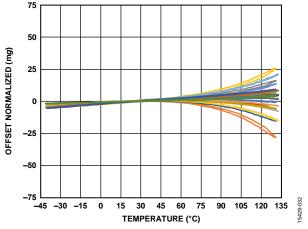

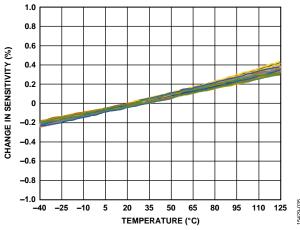

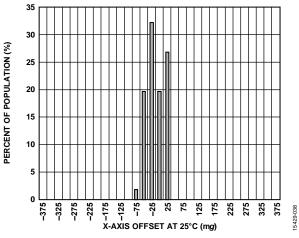

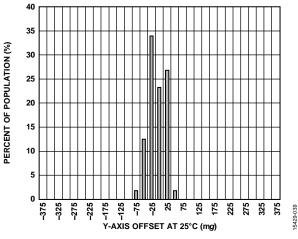

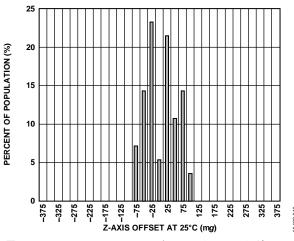

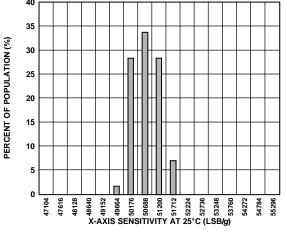

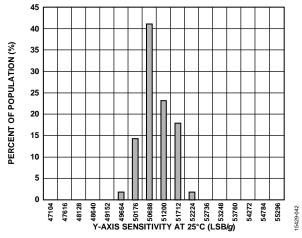

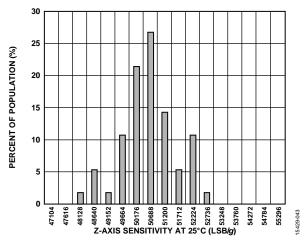

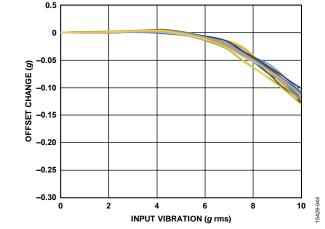

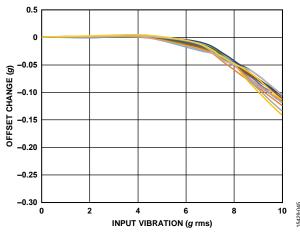

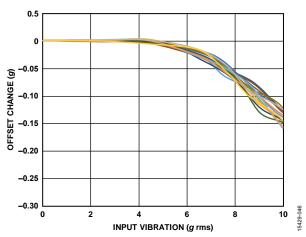

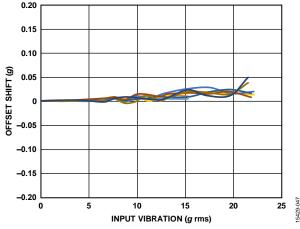

いずれの図も、複数デバイス、複数ロットのデータが含まれています。特に指定のない限り、 $\pm 10\,g$ の範囲で測定されています。

図 8. ADXL356 X 軸の周波数応答

図 9. ADXL356 Y 軸の周波数応答

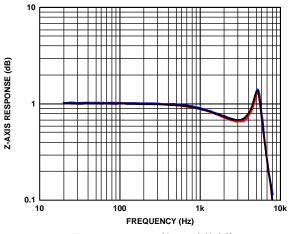

図 10. ADXL356 Z 軸の周波数応答

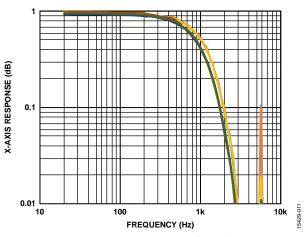

図 11. ADXL357 ODR 4 kHz での X 軸の正規化された 周波数応答

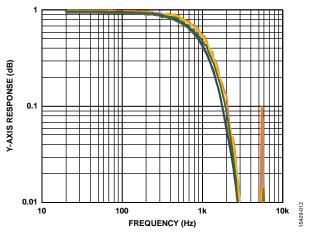

図 12. ADXL357 ODR 4 kHz での Y 軸の正規化された 周波数応答

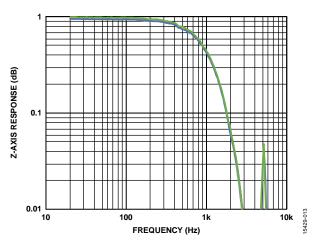

図 13. ADXL357 ODR 4 kHz での Z 軸の正規化された周波数応答

Rev. 0 - 11/42 -

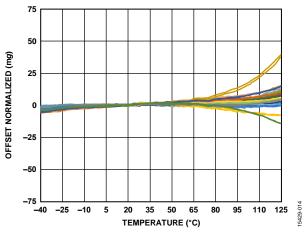

図 14. ADXL356 25 °C を基準として正規化された X 軸の 0 g オフセットの温度特性

図 15. ADXL356 25 °C を基準として正規化された Y 軸の 0 g オフセットの温度特性

図 16. ADXL356 25 °C を基準として正規化された Z 軸の 0 g オフセットの温度特性

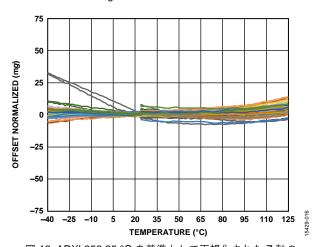

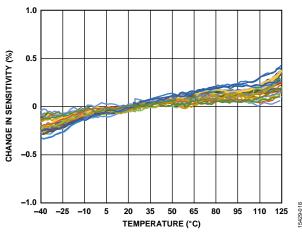

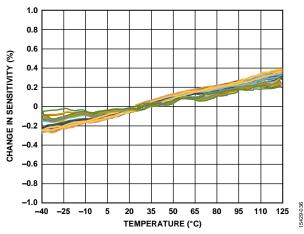

図 17. ADXL356 25°C を基準とした X 軸感度の温度変化

図 18. ADXL356 25 °C を基準とした Y 軸感度の温度変化

図 19. ADXL356 25 °C を基準とした Z 軸感度の温度変化

Rev. 0 - 12/42 -

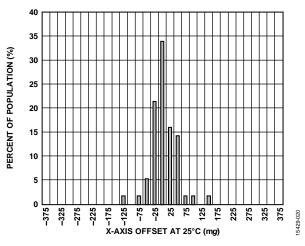

図 20. ADXL356 25 °C での 0 g オフセット・ヒストグラム、 X 軸

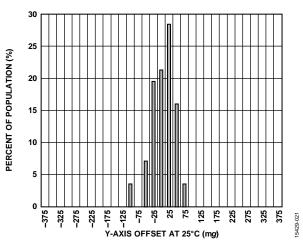

図 21. ADXL356 25 °C での 0 g オフセット・ヒストグラム、 Y 軸

図 22. ADXL356 25 °C での 0 g オフセット・ヒストグラム、 7 軸

図 23. ADXL356 25 °C での感受性ヒストグラム、X 軸

図 24. ADXL356 25°C での 感受性ヒストグラム、Y 軸

図 25. ADXL356 25°C での 感受性ヒストグラム、Z 軸

Rev. 0 – 13/42 –

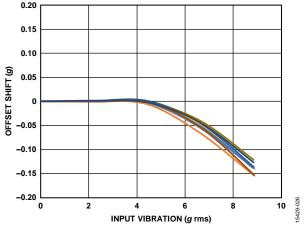

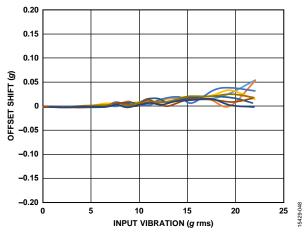

図 26. ADXL356 振動整流誤差(VRE)、+1 g からの X 軸オフセット、±10 g 範囲、X 軸方向 = -1 g

図 27. ADXL356 振動整流誤差 (VRE)、+1 g からの Y 軸オフセット、±10 g 範囲、Y 軸方向 = +1 g

図 28. ADXL356 振動整流誤差(VRE)、+1 g からの Z 軸オフセット、±10 g 範囲、Z 軸方向 = +1 g

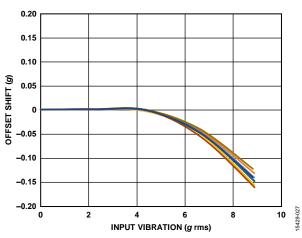

図 29. ADXL356 振動整流誤差(VRE)、+1 g からの X 軸オフセット、±40 g 範囲、X 軸方向 = -1 g

図 30. ADXL356 振動整流誤差 (VRE)、+1 g からの Y 軸オフセット、±40 g 範囲、Y 軸方向 = +1 g

図 31. ADXL356 振動整流誤差(VRE)、+1 g からの Z 軸オフセット、±40 g 範囲、Z 軸方向 = +1 g

Rev. 0 - 14/42 -

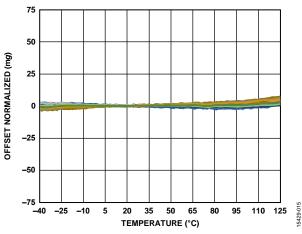

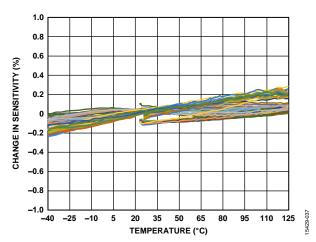

図 32. ADXL357 25 °C を基準として正規化された X 軸の 0 g オフセットの温度特性

図 33. ADXL357 25 °C を基準として正規化された Y 軸の 0 g オフセットの温度特性

図 34. ADXL357 25 °C を基準として正規化された Z 軸の 0 g オフセットの温度特性

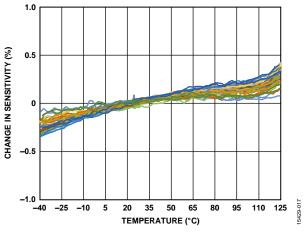

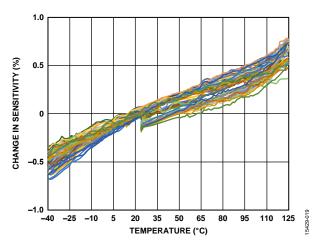

図 35. ADXL357 25°C を基準とした X 軸感度の温度変化

図 36. ADXL357 25 °C を基準とした Y 軸感度の温度変化

図 37. ADXL357 25°C を基準とした Z 軸感度の温度変化

Rev. 0 - 15/42 -

図 38. ADXL357 25 °C での 0 g オフセット・ヒストグラム、 X 軸

図 39. ADXL357 25 °C での 0 g オフセット・ヒストグラム、 Y 軸

図 40. ADXL357 25 °C での 0 g オフセット・ヒストグラム、 Z 軸

図 41. ADXL357 25°C での感受性ヒストグラム、X 軸

図 42. ADXL357 25 °C での感受性ヒストグラム、Y 軸

図 43. ADXL357 25 °C での感受性ヒストグラム、Z 軸

Rev. 0 - 16/42 -

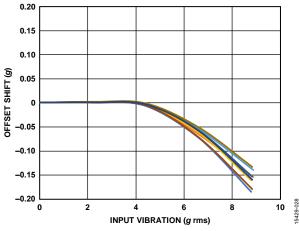

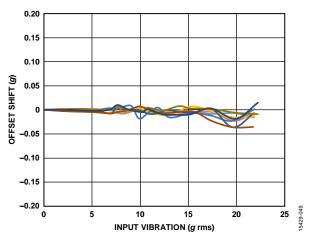

図 44. ADXL357 振動整流誤差(VRE)、+1 g からの X 軸オフセット、±10 g 範囲、X 軸方向 = -1 g

図 45. ADXL357 振動整流誤差 (VRE)、+1 g からの Y 軸オフセット、±10 g 範囲、Y 軸方向 = +1 g

図 46. ADXL357 振動整流誤差(VRE)、+1 g からの Z 軸オフセット、±10 g 範囲、Z 軸方向 = +1 g

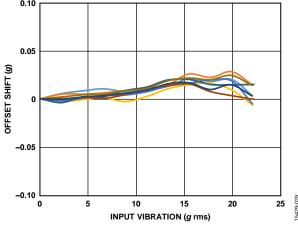

図 47. ADXL357 振動整流誤差(VRE)、+1 g からの X 軸オフセット、±40 g 範囲、X 軸方向 = -1 g

図 48. ADXL357 振動整流誤差 (VRE)、+1 g からの Y 軸オフセット、±40 g 範囲、Y 軸方向 = +1 g

図 49. ADXL357 振動整流誤差(VRE)、+1 g からの Z 軸オフセット、±40 g 範囲、Z 軸方向 = +1 g

Rev. 0 - 17/42 -

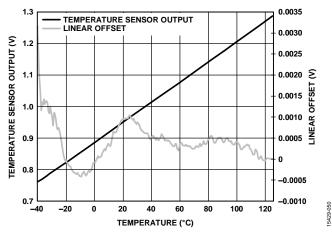

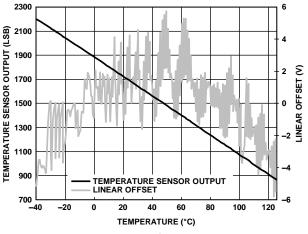

図 50. ADXL356 温度センサーの出力と 直線性オフセットの温度特性

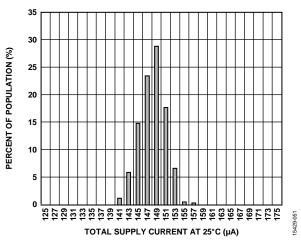

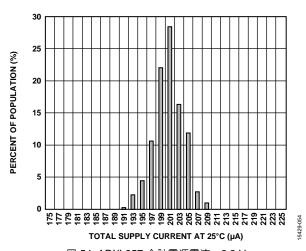

図 51. ADXL356 合計電源電流、3.3 V

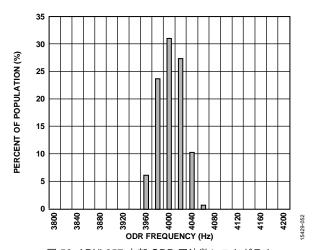

図 52. ADXL357 内部 ODR 周波数ヒストグラム

図 53. ADXL357 温度センサーの出力と 直線性オフセットの温度特性

図 54. ADXL357 合計電源電流、3.3 V

Rev. 0 - 18/42 -

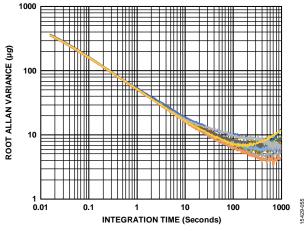

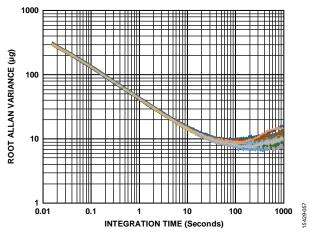

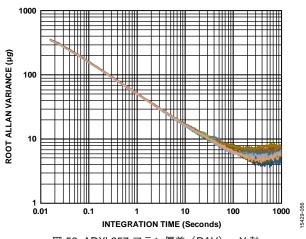

# アラン偏差(RAV)ADXL357 特性

図 55 ~図 57 には、複数デバイス、複数ロットのデータが含まれています。特に指定のない限り、 $\pm 10\,g$  の範囲で測定されています。

図 55. ADXL357 アラン偏差(RAV)、X 軸

図 57. ADXL357 アラン偏差(RAV)、Z軸

図 56. ADXL357 アラン偏差(RAV)、Y 軸

Rev. 0 – 19/42 –

# 動作原理

ADXL356 は、必要な機能をすべて備えた 3 軸、超低ノイズ、非常に安定したオフセットの MEMS 加速度センサーです。このセンサーは、 $V_{IPSANA}$  の 1.8 V アナログ電圧に比例した測定値を出力します。ADXL357 は、アナログ 1.8 V 電源をリファレンスにした 3 つの高分解能 ADC を搭載しているので、電源電圧の影響を受けにくいデジタル出力を生成します。ADXL356B は  $\pm 10$  g または  $\pm 20$  g フルスケールでピン選択可能、ADXL356C は  $\pm 10$  g または  $\pm 40$  g フルスケールでピン選択可能、ADXL357 は  $\pm 10.24$  g、 $\pm 20.48$  g、 $\pm 40.96$  g フルスケールでプログラマブルです。ADXL357 は SPI と  $I^2$ C の両方の通信ポートを備えています。

マイクロマシン構造の検出素子は完全差動型で、水平方向に X 軸と Y 軸センサー、垂直方向にシーソー Z 軸センサーを搭載しています。 X 軸、Y 軸センサー、Z 軸センサーは、オフセット・ドリフトとノイズを最低限に抑える個別の信号経路に配置

されています。ADXL356のアナログ出力での差動からシングルエンドへの変換を除き、信号経路は完全差動型です。

ADXL354のアナログ加速度センサーの出力は、 $V_{IPSANA}$ に比例するので、慎重かつ正確にデジタル化する必要があります。温度センサーの出力は、 $V_{IPSANA}$ に比例しません。 $X_{OUT}$ 、 $Y_{OUT}$ 、 $Z_{OUT}$  アナログ出力は、アンチエイリアシング・フィルタを使用して内部でフィルタ処理されます。これらのアナログ出力は、出力の帯域幅を設定する外部コンデンサと併用できる 32 k  $\Omega$ の内部直列抵抗を備えています。

ADXL357には、高分解能  $\Sigma$ - $\Delta$  ADC の前後にアンチエイリアシング・フィルタが配置されています。出力データ・レートとフィルタ・コーナーを選択できます。温度センサーの出力は、12ビット逐次比較レジスタ(SAR)ADC でデジタル化されます。

Rev. 0 — 20/42 —

# アプリケーション情報 <sub>アナログ出カ</sub>

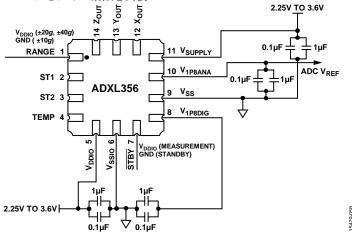

図 58 に ADXL356 のアプリケーション回路を示します。アナログ出力( $X_{OUT}$ 、 $Y_{OUT}$ 、 $Z_{OUT}$ )は、 $V_{IP8ANA}$  ピンの 1.8 V アナログ電圧に比例します。 $V_{IP8ANA}$  は、 $V_{SUPPLY}$  から給電されるオンチップ LDO レギュレータで駆動されます。 $V_{SUPPLY}$  を  $V_{SS}$  に入力して LDO レギュレータを無効にすることで、 $V_{IP8ANA}$  に外部から給電することもできます。ADXL356 の出力は供給電圧に比例するので、デジタル化して固有のノイズとオフセット性能を実現するには、アナログ出力で  $V_{IP8ANA}$  電源をリファレンスにする必要があります。0g バイアス出力は、通常  $V_{IP8ANA}$  に等しくなります。ADXL356 とレシオメトリック ADC(アナログ・デバイセズ製の AD7682 など)を  $V_{IP8ANA}$  で使用して、電圧リファレンスを提供することを推奨します。この構成を使用することで、わずかな電源変動による誤差が打ち消されます。

ADXL356では、2種類のフィルタ処理を使用しています。約1.5 kHz のカットオフ周波数を使用した内部アンチエイリアシング・フィルタ処理と外部フィルタ処理です。外部フィルタ処理では、各出力に直列接続したオンチップの32 k Ω固定抵抗に、外部コンデンサを組み合わせることで、外部 ADC の前段にローパス・フィルタ・アンチエイリアシングとノイズ削減を実装

しています。アンチエイリアシング・フィルタのカットオフ周 波数は、目的の信号帯域幅よりも大幅に高くする必要がありま す。アンチエイリアシング・フィルタ・コーナーが低すぎる と、信号の減衰がリファレンス減衰と異なる場合に、比例誤差 が大きくなる可能性があります。

#### デジタル出力

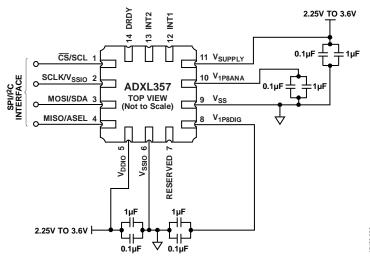

図 59 に、ADXL357 アプリケーション回路と推奨されるバイパス・コンデンサを示します。通信インターフェースは、SPI または  ${

m l}^2{

m C}$  です(詳細については、シリアル通信のセクションを参照)。

ADXL357には、内部構成可能なデジタル・バンドパス・フィルタが含まれます。フィルタ設定レジスタのセクションと表 44 で説明しているように、フィルタのハイパス極とローパス極の両方を調整できます。パワーアップ時のこれらのフィルタのデフォルト条件は、次のとおりです。

- ローパス・フィルタ (LPF) = 1000 Hz

- 出力データ・レート=4000 Hz

図 58. ADXL356 アプリケーション回路

図 59. ADXL357 アプリケーション回路

Rev. 0 — 21/42 —

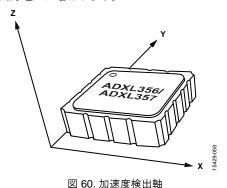

#### 加速度検出軸

図 60 に、加速度検出軸を示します。検出軸で加速が生じると、対応する出力電圧が増加します。

#### 電源シーケンス

デバイスに給電する方法は 2 つあります。通常、内部 LDO レギュレータは、アナログ電源とデジタル電源( $V_{IP8ANA}$  と  $V_{IP8DIG}$ )にそれぞれ 1.8 V の電源を生成します。オプションで、 $V_{SUPPLY}$  を  $V_{SS}$  に接続して  $V_{IP8ANA}$  と  $V_{IP8DIG}$  を外部電源で駆動すると、 $V_{IP8ANA}$  と  $V_{IP8DIG}$  を供給できます。

内部 LDO レギュレータを使用する場合は、 $V_{SUPPLY}$  を 2.25 V  $\sim$  3.6 V の間の電圧源に接続します。この場合、 $V_{DDIO}$  と  $V_{SUPPLY}$  を並列で駆動できます。 $V_{SUPPLY}$  -  $V_{DDIO}$  の電圧差が 0.5 V を超えてはいけません。必要に応じて、 $V_{DDIO}$  を  $V_{SUPPLY}$  よりも前に駆動できます。

内部 LDO レギュレータを無効にして、外部  $1.8\,V$  電源経由で  $V_{IPSANA}$  と  $V_{IPSDIG}$  の電源を駆動する場合は、 $V_{SUPPLY}$  をグラウンドに接続し、 $V_{IPSANA}$  と  $V_{IPSDIG}$  の最終電圧を同じ値に設定します。 LDO をバイパスする場合に推奨される電源シーケンスを次に示します。まず、 $V_{DDIO}$  に給電した後、約  $10\,\mu s$  経過してから電源  $V_{IPSDIG}$  を給電します。その後、約  $10\,\mu s$  経過してから  $V_{IPSANA}$  を給電します。必要に応じて、同じ  $1.8\,V$  電源で  $V_{IPSDIG}$  と  $V_{DDIO}$  を駆動できます。適切な絶縁を使用して、 $V_{IPSANA}$  に接続することもできます。この場合、センサーのノイズ性能を維持するため、適切なデカップリングと低周波絶縁が重要になります。

#### 電源の説明

ADXL356/ADXL357 には、V<sub>SUPPLY</sub>、V<sub>IPSANA</sub>、V<sub>IPSDIG</sub>、V<sub>DDIO</sub> の 4 種類の電源領域があります。内部のアナログ回路とデジタル回路は、公称 1.8 V で動作します。

#### VSUPPLY

$V_{SUPPLY}$  は 2.25 V  $\sim$  3.6 V です。これは  $V_{IP8ANA}$  と  $V_{IP8DIG}$  の公称 1.8 V の出力を生成する 2 つの LDO レギュレータの入力範囲です。LDO レギュレータを無効にするには、  $V_{SUPPLY}$  を  $V_{SS}$  に接続します。これにより、  $V_{IP8ANA}$  と  $V_{IP8DIG}$  を外部電源から駆動できます。

#### V<sub>1P8ANA</sub>

すべてのセンサーとアナログ信号処理回路は、この領域で動作します。アナログ出力の ADXL356 のオフセットと感度は、この電源電圧に比例します。外部 ADC を使用する場合は、 $V_{IPSANA}$  をリファレンス電圧として使用します。デジタル出力の ADXL357 には、 $V_{IPSANA}$  に比例する ADC が含まれます。このため、オフセットと感度が  $V_{IPSANA}$  の影響を受けなくなります。

VIPSANA は、VSUPPLY 電圧の状態によって定義される入力と出力として使用できます。

#### $V_{1P8DIG}$

$V_{IP8DIG}$  は、内部ロジック回路の電源電圧です。個別の LDO レギュレータによって、アナログ信号経路からのデジタル電源ノイズがデカップリングされます。  $V_{IP8ANA}$  は、 $V_{SUPPLY}$  電圧の状態によって定義される入力と出力として使用できます。外部駆動の場合、 $V_{IP8DIG}$  は  $V_{IP8ANA}$  電圧と同じ電圧にする必要があります。

## $V_{\text{DDIO}}$

$V_{DDIO}$  値は、ロジック・ハイ・レベルを決定します。アナログ出力の ADXL356 では、 $V_{DDIO}$  はセルフ・テスト・ピン ST1 と ST2 だけでなく、 $\overline{STBY}$  ピンのロジック・ハイ・レベルを設定します。デジタル出力の ADXL357 では、 $V_{DDIO}$  を使用して通信インターフェース・ポートだけでなく、割込みと DRDY 出力のロジック・ハイ・レベルを設定します。

LDO レギュレータは、 $V_{SUPPLY}$  が 2.25 V ~ 3.6 V の間で動作します。 $V_{IP8ANA}$  と  $V_{IP8DIG}$  は、このモードのレギュレータ出力です。代わりに、 $V_{SUPPLY}$  を  $V_{SS}$  に接続すると、 $V_{IP8ANA}$  と  $V_{IP8DIG}$  は、1.62 V ~ 1.98 V 範囲の電源電圧入力になります。

#### オーバーレンジ保護

プルーフ・マスに静電気が蓄積しないように、加速度センサーの入力がフルスケール・レンジを超えると、すべてのセンサー・ドライブ・クロックは、0.5~ms の間オフになります。 $\pm 10~g/\pm 10.24~g$  の範囲設定では、 $\pm 40~g$  ( $\pm 25~%$ ) を超える入力信号、 $\pm 20~g/\pm 20.48~g$  と  $\pm 40~g/\pm 40.95~g$  の範囲設定、約  $\pm 80~g$  ( $\pm 25~%$ ) に対応する閾値設定で、オーバーレンジ保護が有効になります。

オーバーレンジ保護が発生すると、ADXL356の X<sub>OUT</sub>、Y<sub>OUT</sub>、 Z<sub>OUT</sub> ピンはミッドスケールに駆動します。ADXL357 はゼロに 向かってフロート状態になり、このデータの処理で先入れ先出 し(FIFO)バッファが始まります。

### セルフ・テスト

ADXL356 と ADXL357 には、機械システムと電子システムを効率よく検査するセルフ・テスト機能が組み込まれています。セルフ・テストを有効にすると、静電的にセンサーを駆動し、加えられた機械的な力だけでなく、印加されたテスト信号にも対応した出力が発生します。 Z 軸の応答のみがデバイスの機能を検証するために仕様となっています。

ADXL356では、ST1ピンを  $V_{DDIO}$  に駆動して、セルフ・テスト・モードを起動します。次に、ST2ピンを  $V_{DDIO}$  に駆動することで、ADXL356は静電気力を機械センサーに適用し、静電気力への応答での出力の変化を誘導します。ST1がアサートされていて、ST2がハイの状態と ST2がローの状態の間で発生する Z 軸の出力電圧の差が、セルフ・テスト・デルタ(または応答)になります。セルフ・テスト測定が完了したら、両方のピンをロー状態に移行して、通常動作を再開します。

SELF\_TEST レジスタ(レジスタ 0x2E)から ST1 と ST2 にアクセスできることを除くと、セルフ・テスト動作は ADXL357 と同じです。

Rev. 0 – 22/42 –

セルフ・テスト機能を使用すれば、外部で付加された加速度を 除去し、セルフ・テストの力だけに応答できます。このため、 外部に機械ノイズが存在する場合でも、セルフ・テストを正確 に測定できます。

#### **FILTER**

ADXL356/ADXL357 は、アナログ、ローパス、アンチエイリアシング・フィルタを使用して、帯域外ノイズを削減し、帯域幅を制限します。ADXL357 には、各種 ODR で優れたノイズ性能を維持するため、詳細なデジタル・フィルタ処理オプションを用意しています。

ADXL356/ADXL357 のアナログ、ローパス・アンチエイリアシング・フィルタは、約1.5 kHz の固定帯域幅を実現します。この周波数での出力応答は約50%減衰します。周波数領域でのフィルタ応答の形状は、sinc3フィルタ応答の形状に一致します。

ADXL356 の X 軸、Y 軸、Z 軸のアナログ出力には、32 k  $\Omega$ の直列抵抗の前段にあるアンプや、 $X_{OUT}$ 、 $Y_{OUT}$ 、 $Z_{OUT}$  ピンへの出力が含まれます。

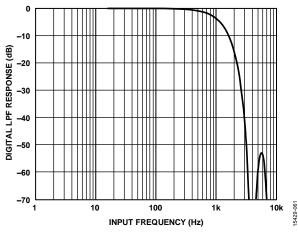

ADXL357 は、内部 20 ビット  $\Sigma$ - $\Delta$  ADC でフィルタ処理されたア ナログ信号をデジタル化します。アナログのローパス・アンチ エイリアシング・フィルタを通過した後の補助的なデジタル・ フィルタ処理は、ローパス・デジタル・デシメーション・フィ ルタと、4 kHz ~ 3.906 Hz の出力データ・レートに対応するバ イパス可能なハイパス・フィルタで構成されます。デシメーシ ョン・フィルタは2段構成になっています。1段目は、約1kHz のローパス・フィルタ・カットオフを使用した4kHzのODRで 実行する固定デシメーションです(出力応答で50%の除去)で す。2段目の可変デシメーション・フィルタは、2kHz以下の出 カデータ・レートで使用されるデシメーション・フィルタ (4 kHz ODR でパイパス) です。図 61 に、ADXL357 の 1 kHz コー ナー(4kHz ODR)を使用したローパス・フィルタの応答を示 します。図 61 には、固定帯域幅が約 1.5 kHz の固定周波数アナ ログ、ローパス・アンチエイリアシング・フィルタは含まれま せん。

図 61. ADXL357 4 kHz ODR での デジタル・ローパス・フィルタ(LPF)の応答

ADXL357の信号経路の通過帯域は、前述のアナログ・フィルタやデジタル・デシメーション・フィルタ/ODR 設定を含む、複合フィルタの応答に関連があります。表 10 に、各設定のデシメーション・フィルタに関連付けられた遅延と、ODR/4 コーナーでの減衰を示します。

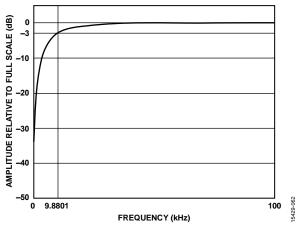

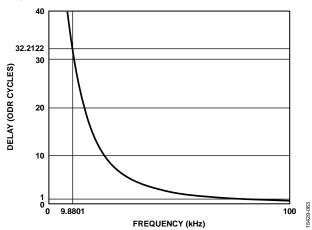

ADXL357には、プログラマブル・コーナー周波数を使用した、オプションのデジタル・ハイパス・フィルタも含まれます。デフォルトでは、ハイパス・フィルタは無効になります。出力が50%減衰するハイパス・コーナー周波数は、ODRとフィルタ・レジスタの HPF\_CORNER 設定(レジスタ 0x28 のビット[6:4])に関連があります。表11に、HPF\_CORNER の応答を示します。図 62と図 63に、シミュレートされた10 Hz カットオフのハイパス・フィルタ応答と遅延を示します。

ADXL357には、外部同期オプションを提供する、オーバーサンプリング/アップコンバートされたデータを生成するデシメーション・フィルタの後段にインターポレーション・フィルタも含まれます。詳細については、データ同期のセクションを参照してください。表12に、プログラマブル ODR に関連する遅延と減衰を示します。

図 62. 4 kHz、ODR および HPF\_CORNER 設定 001 (レジスタ 0x28 のビット [6:4] )の ハイパス・フィルタ・パスバンド応答

群遅延はデジタル・フィルタ遅延で、ADCに入力されたデータがインターフェースで使用できるようになるまでの時間に相当します(Filter セクションを参照)。この遅延は、センサーからシリアル・インターフェースまでの遅延合計の最も大きい成分です。

図 63.4 kHz、ODR および HPF\_CORNER 設定 001 (レジスタ 0x28 のビット[6:4])のハイパス・フィルタ遅延応答

Rev. 0 – 23/42 –

表 10. デジタル・フィルタの群遅延とプロファイル

|                     | Delay        |           | Attenuation             |                         |  |

|---------------------|--------------|-----------|-------------------------|-------------------------|--|

| Programmed ODR (Hz) | ODR (Cycles) | Time (ms) | Decimator at ODR/4 (dB) | Full Path at ODR/4 (dB) |  |

| 4000                | 2.52         | 0.63      | -3.44                   | -3.63                   |  |

| 4000/2 = 2000       | 2.00         | 1.00      | -2.21                   | -2.26                   |  |

| 4000/4 = 1000       | 1.78         | 1.78      | -1.92                   | -1.93                   |  |

| 4000/8 = 500        | 1.63         | 3.26      | -1.83                   | -1.83                   |  |

| 4000/16 = 250       | 1.57         | 6.27      | -1.83                   | -1.83                   |  |

| 4000/32 = 125       | 1.54         | 12.34     | -1.83                   | -1.83                   |  |

| 4000/64 = 62.5      | 1.51         | 24.18     | -1.83                   | -1.83                   |  |

| 4000/128 ~ 31       | 1.49         | 47.59     | -1.83                   | -1.83                   |  |

| 4000/256 ~ 16       | 1.50         | 96.25     | -1.83                   | -1.83                   |  |

| 4000/512 ~ 8        | 1.50         | 189.58    | -1.83                   | -1.83                   |  |

| 4000/1024 ~ 4       | 1.50         | 384.31    | -1.83                   | -1.83                   |  |

## 表 11. デジタル・ハイパス・フィルタの応答

| HPF_CORNER Register Setting (Register 0x28, Bits[6:4]) | HPF_CORNER Frequency, -3 dB Point Relative to ODR Setting | -3 dB at 4 kHz ODR (Hz) |

|--------------------------------------------------------|-----------------------------------------------------------|-------------------------|

| 000                                                    | Not applicable, no high-pass filter enabled               | Off                     |

| 001                                                    | $247 \times 10^{-3} \times ODR$                           | 9.88                    |

| 010                                                    | $62.084 \times 10^{-3} \times ODR$                        | 2.48                    |

| 011                                                    | $15.545 \times 10^{-3} \times ODR$                        | 0.62                    |

| 100                                                    | $3.862 \times 10^{-3} \times ODR$                         | 0.1545                  |

| 101                                                    | $0.954 \times 10^{-3} \times ODR$                         | 0.03816                 |

| 110                                                    | $0.238 \times 10^{-3} \times ODR$                         | 0.00952                 |

# 表 12. デジタル・インターポレーション・フィルタとデシメーション・フィルタの応答の結合

| Interpolator Data Rate Resolution Relative to 64 × ODR (Hz) | Combined Interpolator/ Decimator Delay (ODR Cycles) | Combined Interpolator/<br>Decimator Delay (ms) | Combined Interpolator/Decimator Output Attenuation at ODR/4 (dB) |

|-------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------|------------------------------------------------------------------|

| $64 \times 4000 = 256000$                                   | 3.51661                                             | 0.88                                           | -6.18                                                            |

| $64 \times 2000 = 128000$                                   | 3.0126                                              | 1.51                                           | -4.93                                                            |

| $64 \times 1000 = 64000$                                    | 2.752                                               | 2.75                                           | -4.66                                                            |

| $64 \times 500 = 32000$                                     | 2.6346                                              | 5.27                                           | -4.58                                                            |

| $64 \times 250 = 16000$                                     | 2.5773                                              | 10.31                                          | -4.55                                                            |

| $64 \times 125 = 8000$                                      | 2.5473                                              | 20.38                                          | -4.55                                                            |

| $64 \times 62.5 = 4000$                                     | 2.53257                                             | 40.52                                          | -4.55                                                            |

| $64 \times 31.25 = 2000$                                    | 2.52452                                             | 80.78                                          | -4.55                                                            |

| $64 \times 15.625 = 1000$                                   | 2.52045                                             | 161.31                                         | -4.55                                                            |

| $64 \times 7.8125 = 500$                                    | 2.5194                                              | 322.48                                         | -4.55                                                            |

| $64 \times 3.90625 = 250$                                   | 2.51714                                             | 644.39                                         | -4.55                                                            |

Rev. 0 — 24/42 —

# シリアル通信

4線式シリアル・インターフェースは、SPI または  $I^{\bullet}C$  プロトコルで通信します。使用されたフォーマットを効果的に自動検出し、フォーマットを選択するための構成制御が不要です。

# SPI プロトコル

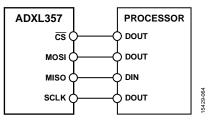

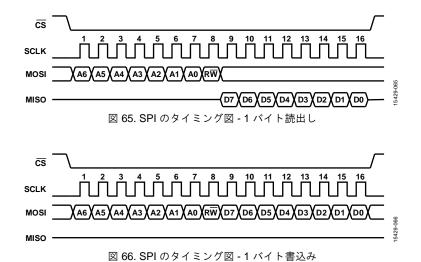

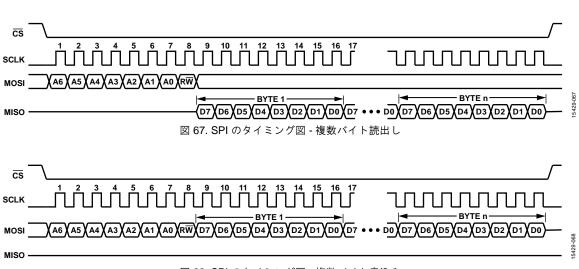

ADXL357 の SPI 通信ケーブルは、図 64 の接続図に示すように配線します。SPI プロトコルのタイミングは、図 65  $\sim$ 図 68 に示します。タイミング方式は、クロック極性(CPOL)=0 とクロック位相(CPHA)=0 に従います。SPI クロック速度は、100 kHz  $\sim$  10 MHz の範囲に収まります。

図 64.4 線式 SPI 接続

図 68. SPI のタイミング図 - 複数バイト書込み

Rev. 0 — 25/42 —

#### I2C プロトコル

されています) 必要があります。

ADXL357 は、ポイント to ポイントの I<sup>2</sup>C 通信をサポートして います。しかし、SDA バスを共有している場合には、ADXL357 はそのバス上の他のデバイスとの通信を中止してしまうことが あります。たとえ ADXL357 がアドレス指定されていない場合 でも、バイト 0x3A および 0x3B(ADXL357 のデバイス ID が 0x1D にセットされている場合)、またはバイト 0xA6 および 0xA7 (ADXL357 のデバイス ID が 0x53 にセットされている場 合)が SDA バス上に送信された場合はいつでも、ADXL357は アクノレッジ・ビットを返信し、SDA ラインをプルダウンしま す。例えば、バス上の他のセンサーに対してデータ・バイト (0x3A/0x3B または 0xA6/0xA7) を読出しまたは書込み中に、 この応答が発生する可能性があります。ADXL357が SDA ライ ンをプルダウンすると、バス上の他のデバイスとの通信が中断 してしまうことがあります。これを解決するためには、 ADXL357 を別の SDA バスに接続するか、ADXL357 と通信する 必要がない場合には SCL ピンをハイに切り替える(通常は接地

表 4 に示されたバス・パラメータを満たしている場合、 ADXL357 は標準(100~kHz)、高速(最大 1~MHz)、高速(最大 3.4~MHz)のデータ転送モードに対応します。データの読出し時において、新しいデータで上書きされる前にサンプル・セットのすべてを読み出すだけの速度がクロックに必要とされる場合を除いて、SCL に最低周波数はありません。シングル・バイトまたは複数バイトの読出し/= 基込みをサポートしています。 ASEL ピンがローの場合は、デバイスの  $1^2$ C アドレスは0x1D です。代替  $1^2$ C アドレスの  $1^2$ C アドレスは $1^2$ C アドレスの  $1^2$ C アドレスト

未使用のピンには内部にプルアップ抵抗もプルダウン抵抗もないので、フロート状態または未接続の場合は、これらのピンが既知の状態やデフォルト状態になることはありません。I'Cを使用してADXL357と通信する場合には、SCLK/V<sub>SSIO</sub>を接地する必要があります。

通信速度に制限があるため、 $400 \, \text{kHz}$  の  $I^2 C$  モードを使用しているときの最大出力データ・レートは  $800 \, \text{Hz}$  です。そして、最大出力データ・レートは  $I^2 C$  の通信速度に比例します。例えば、 $I^2 C$  を  $100 \, \text{kHz}$  で使用する場合、最大 ODR は  $200 \, \text{Hz}$  に制限されます。推奨される最大出力データ・レートを超えて動作させると、データ・サンプルが失われたりノイズが増加するなど、加速度データに望ましくない影響を与えることがあります。

図 69 ~図 71 に、 $I^2$ C プロトコル・タイミングの詳細を示します。 $I^2$ C インターフェースは、 $I^2$ C 標準モード(100 kHz)、高速モード(400 kHz)、高速モード・プラス(1 MHz)、ハイ・スピード・モード(3.4 MHz)で使用できます。ADXL357 の  $I^2$ C デバイス ID は、次のとおりです。

- ASEL ( $\forall \nu$ ) = 0、 $\forall x$ 1D

- ASEL  $(\mathbb{C}^2) = 1$ ,  $\vec{\mathcal{F}}$   $\vec$

他のデバイスを同じ  $\Gamma$ C バスに接続する場合、公称動作電圧が $V_{DDIO}$  を 0.3~V 以上上回るデバイスを接続することはできません。  $\Gamma$ C を正常に動作させるためには、外部プルアップ抵抗  $R_P$  が必要です。

# インターフェースからの加速度または温度の読出し

加速度データは左詰めで、レジスタ・アドレスの左端に最上位データが格納され、右端に最下位データが格納されます。これにより、複数バイトの転送を使用して、必要なデータ(8ビット、16ビット、または20ビットとマーカー)だけを取得できます。温度データは、符号なし12ビットで右詰めです。ADXL357の温度データの値は2バイトに分割されますが、ダブル・バッファされません。つまり、値は2つのレジスタを読出す間に更新されます。XDATA、YDATA、ZDATAは、特定のサンプル時点に対応するセットであるとは限りません。デバイスからデータを取得するために使用されるルーチンを使用して、このデータ・セットの連続性を制御します。DATA\_RDY ビットがハイになると、データ転送が開始されます。1/ODR とほぼ等しい時間で転送が完了すると、XDATA、YDATA、ZDATA が同じデータ・セットに適用されます。

いずれかのシリアル・インターフェースからの複数バイトの読出しまたは書込みトランザクションでは、内部レジスタ・アドレスが自動的にインクリメントします。レジスタ・アドレス範囲の先頭 0x3FF に到達すると、自動インクリメントは停止し、16 進数のアドレス 0x00 にラップ・バックしません。

FIFO アドレスを使用する場合、アドレス自動インクリメント機能は無効になります。このため、データは複数バイトのトランザクションとして、FIFO から連続して読出されます。複数バイト・トランザクションの開始アドレスが FIFO アドレスよりも小さい場合、アドレスは FIFO アドレスに到達するまで自動的にインクリメントし、FIFO アドレスで停止します。

# 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 SCL

START | DEVICE ADDRESS | REPEAT DEVICE ADDRESS | START | START | DEVICE ADDRESS | START |

INDICATE SDA IS CONTROLLED BY ADXL357

図 69. I<sup>2</sup>C のタイミング図 - 1 バイト読出し

Rev. 0 — 26/42 —

データシート

# ADXL356/ADXL357

図 71. I<sup>2</sup>C のタイミング図 - 複数バイト書出し

Rev. 0 - 27/42 -

## **FIFO**

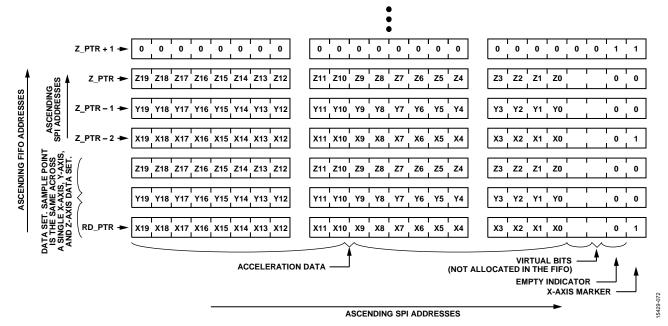

FIFO はストリームモードで動作します。つまり、FIFO でオーバーランが発生すると、新しいデータで FIFO 内の最も古いデータが上書きされます。FIFO アドレスからの読出しでは、加速度測定に関連付けられた 3 バイトが、すべて同じ測定に関連付けられます。FIFO がオーバーフローしない限り、データは常にセット(3 つのデータ・ポイントの倍数)で取得されます。

FIFO には、21 ビットの格納位置が 96 個あります。各位置には、20 ビットのデータと、X 軸データのマーカー・ビットが含まれます。FIFO アドレスから 1 バイトを読み出すと、FIFO から 1 つの格納位置がポップされます。FIFO の格納位置から複数バイトを読み出す場合、最初のバイトの読出しと後続の 3 バイトごとの読出して FIFO がポップされます。

図 72 に、FIFO のデータの編成を示します。加速度データは、2 の補数フォーマットの 20 ビット・データです。FIFO コントロール・ロジックでは、データ・ビットと空のインジケータ・ビットの間に 2 つの仮想ビット(0b00)を挿入します。ビット 1 は、空の FIFO の読出しが試行され、データが有効な加速度データではないことを示します。ビット 0 は、X 軸を特定するマーカー・ビットで、FIFO データが適切に読み出されたかどうかを確認するのに使用できます。特定の軸の加速度データ・ポイントが FIFO の格納位置を 1 つ占有します。読出しポインタ RD\_PTR は、インターフェースからの読出しが実行されていない、最も古い格納データを参照します(図 72 を参照)。物理的な X 加速度、Y 加速度、Z 加速度のデータ・レジスタはありません。また、このデータは、FIFO 内の最新のデータ・セットから直接取得され、Z ポインタ Z\_PTR で参照されます(図 72 を参照)。

図 72. FIFO のデータ構成

Rev. 0 — 28/42 —

# 割込み

ステータス・レジスタ(レジスタ 0x04)には、5 つの独立した ビットが含まれます。これらのビットの4つを INT1 ピン、 INT2 ピン、または両方にマッピングできます。割込みの極性、 アクティブ・ハイまたはアクティブ・ローは範囲(レジスタ 0x2C)レジスタの INT\_POL ビットからも選択できます。通 常、ステータス・レジスタは読出し時にクリアされます。ただ し、レジスタの読出し後も割込みが持続する場合、ステータ ス・レジスタはウリアされません。「持続」の定義はケースご とにわずかに異なりますが、DATA\_RDY、DRDY Pin、

FIFO\_FULL、FIFO\_OVR、およびアクティビティのセクションで説明します。DRDYピンは、割込みピン(INTx)に類似していますが、明白な相違点が存在します。このケースについても説明します。

#### **DATA RDY**

新しい加速度データがインターフェースで使用できるようになると、DATA\_RDY ビットが設定されます。ステータス・レジスタの読出し時にクリアされます。ステータス・レジスタの読出しよりも新しい加速度データが使用できるようになると、再度設定されます。

DATA\_RDY ビットをクリアする特別なロジックは、ステータス・レジスタの読出し中に新しいデータが到着するコーナーの状況にも対応します。この場合、データのレディ条件は完全に失われます。このロジックにより、最大4つの512 kHz サイクルのDATA RDYのクリアが遅延されます。

#### DRDY ピン

DRDY ピンは、ステータス・レジスタ・ビットではなく、マスク不能な割込みと同様に動作します。新しい加速度データがインターフェースで使用できるようになると、DRDY ビットが設定されます。FIFO の読出し時、XDATA、YDATA、ZDATAの読出し時、または出力加速度データの設定期間のほぼ中間点で発生する自動クリア機能によってクリアされます。

DRDY は常にアクティブ・ハイです。INT\_POL ビットは DRDY に影響を与えません。外部同期モード(EXT\_SYNC = 01、EXT\_SYNC = 10)では、初期同期後に最初の DRDY パルスが数 個失われるか、破損することがあります。この破損の長さは、群遅延よりも短くなります。

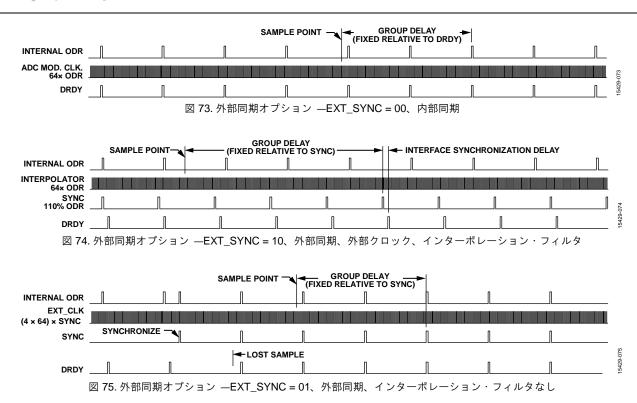

#### FIFO FULL