# SHARCプロセッサ

# ADSP-21483/ADSP-21486/ADSP-21487/ADSP-21488/ADSP-21489

# 概要

高性能オーディオ処理用に最適化された高性能 32 ビット/40 ビット浮動小数点プロセッサ

SIMD (Single-instruction, multiple-data)演算アーキテクチャを採用

内蔵メモリ―5 M ビットの内蔵 SRAM、4 M ビットのマスク・プログラマブルな内蔵 ROM

最大動作周波数: 400 MHz

すべての他の SHARC ファミリー・メンバーとコード互換

ADSP-2148x プロセッサは、デジタル・アプリケーション・インターフェース、シリアル・ポート、高精度クロック・ジェネレータ、S/PDIF トランシーバ、非同期サンプル・レート・コンバータ、入力データ・ポートなどの独自なオーディオ中心のペリフェラルを内蔵しています。

オーダー情報については、ページ65のオーダー・ガイドを参照してください。

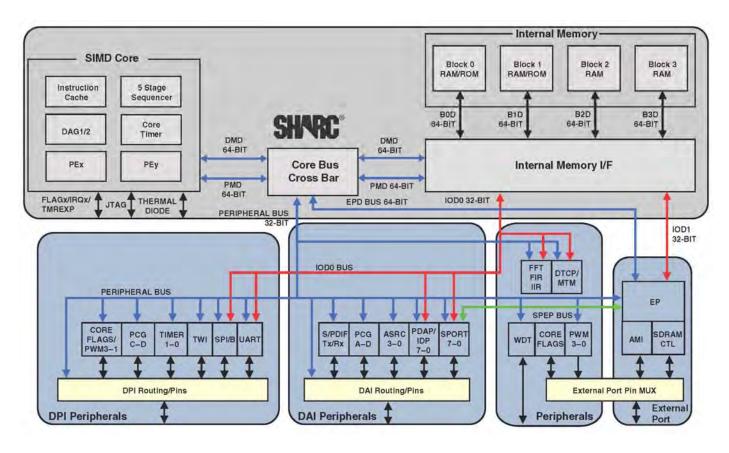

図 1. 機能ブロック図

SHARC および SHARC ロゴは、Analog Devices, Inc.の登録商標です。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。 ※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2010 Analog Devices, Inc. All rights reserved.

Rev. 0

# 目次

| まとめ                     | 1  |

|-------------------------|----|

| 目次                      | 2  |

| 改訂履壓                    | 2  |

| 概要                      | 3  |

| ファミリー・コアのアーキテクチャ        | 4  |

| ファミリー・ペリフェラルのアーキテクチャ    | 7  |

| SDRAM コントローラ            | 8  |

| SIMD の外部メモリへのアクセス       | 8  |

| VISA と ISA の外部メモリへのアクセス | 8  |

| システム・デザイン               | 11 |

| 開発ツール                   | 12 |

| その他の情報                  | 12 |

| 関連シグナル・チェーン             | 12 |

| ピン機能の説明                 | 13 |

| 仕様                      | 17 |

| 動作条件                    | 17 |

| 電気的特性                   | 18 |

| 絶対最大定格                  | 20 |

| パッケージ情報                 | 20 |

| ESD について                    | 20   |

|-----------------------------|------|

| 最大消費電力                      | 20   |

| タイミング仕様                     | 20   |

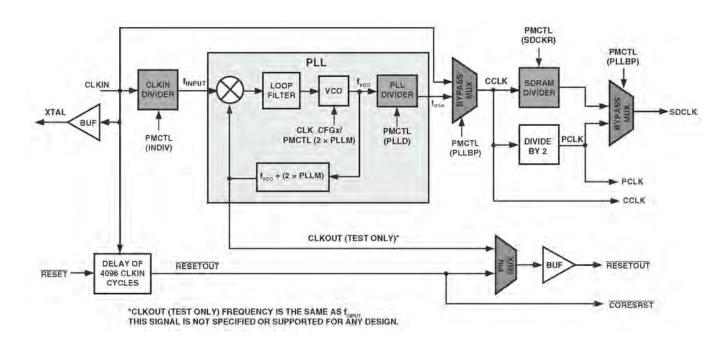

| 電圧制御発振器                     | 21   |

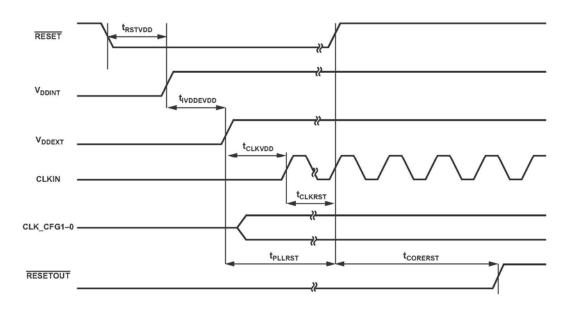

| パワーアップ・シーケンス                | 22   |

| S/PDIF トランスミッタのシリアル入力波形     | 44   |

| S/PDIF トランスミッタ入力データのタイミング   | 46   |

| オーバーサンプリング・クロック(TxCLK)のスイッチ | ング特性 |

|                             | 46   |

| 内部デジタル PLL モード              | 47   |

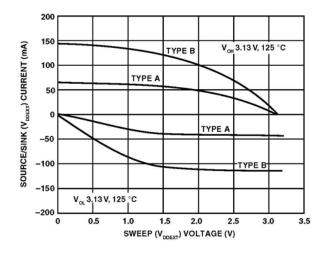

| 出力駆動電流                      | 54   |

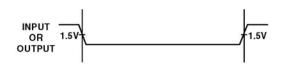

| テスト条件                       | 54   |

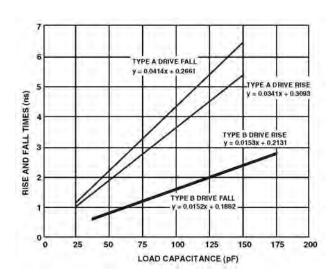

| 容量負荷                        | 54   |

| 熱特性                         | 55   |

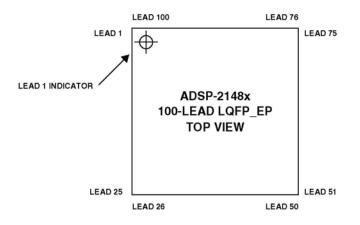

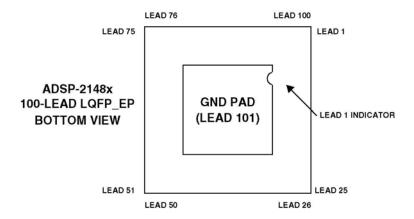

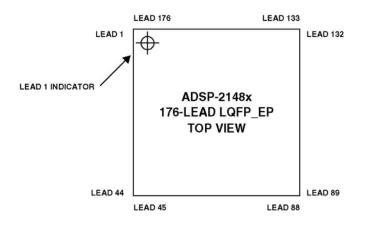

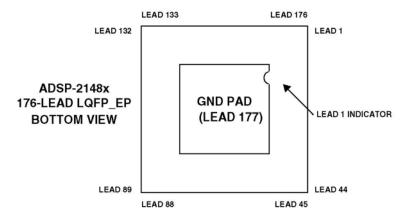

| 00-LQFP_EP のピン配置            | 57   |

| 76 ピン LQFP_EP のピン配置         | 59   |

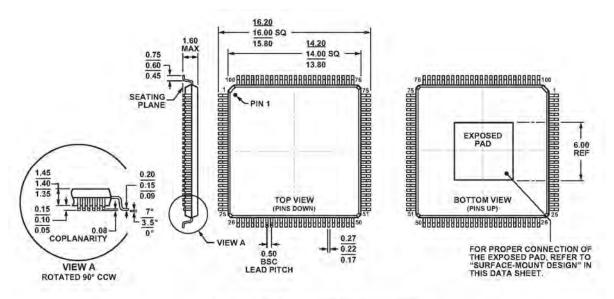

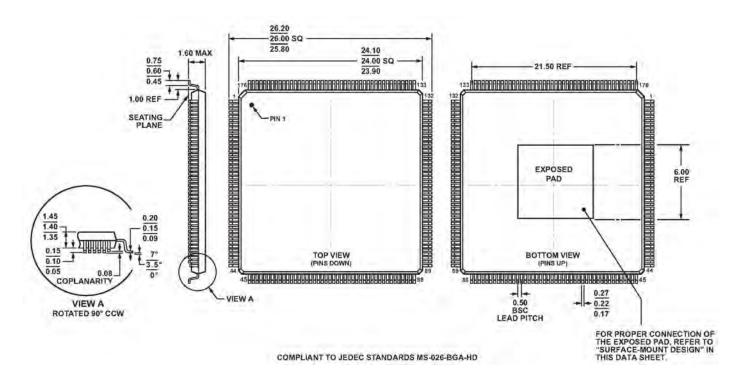

| ペッケージ寸法                     | 62   |

| 表面実装デザイン                    | 63   |

| 車載製品                        | 64   |

| 1 12 18 1 19                |      |

# 改訂履歴

12/10—Revision 0: Initial Version

# 概要

ADSP-2148x SHARC<sup>®</sup>プロセッサは、SIMD SHARC ファミリーのメンバーであり、アナログ・デバイセズのスーパー・ハーバード・アーキテクチャを採用した DSP です。このプロセッサは、ADSP-2126x、ADSP-2136x、ADSP-2137x、ADSP-2146x、ADSP-2116x の各 DSP および SISD (Single-Instruction, Single-Data)モードの第 1世代 ADSP-2106x SHARC プロセッサとソース・コード互換です。ADSP-2148x プロセッサは、大容量の内蔵 SRAM、I/O ボトルネックを解消する複数の内部バス、画期的なデジタル・アプリケーション・インターフェース(DAI)により、高性能オーディオ・アプリケーション向けに最適化された 32 ビット/40 ビットの浮動小数点プロセッサです。

表 1に、ADSP-2148x プロセッサの性能ベンチマークを示します。 表 2に、各製品の機能を示します。

表 1. プロセッサ・ベンチマーク

|                                                 | Speed        |

|-------------------------------------------------|--------------|

| Benchmark Algorithm                             | (at 400 MHz) |

| 1024 Point Complex FFT (Radix 4, with Reversal) | 23 μs        |

| FIR Filter (per Tap) <sup>1</sup>               | 1.25 ns      |

| IIR Filter (per Biquad) <sup>1</sup>            | 5 ns         |

| Matrix Multiply (Pipelined)                     |              |

| $[3 \times 3] \times [3 \times 1]$              | 11.25 ns     |

| $[4 \times 4] \times [4 \times 1]$              | 20 ns        |

| Divide $(y/x)$                                  | 7.5 ns       |

| Inverse Square Root                             | 11.25 ns     |

<sup>「</sup>マルチチャンネル SIMD モードでは 2 つのファイルを想定

#### 表 2. ADSP-2148x ファミリーの機能

| 3 Mbits                     | 5 M<br>4 Mbits           | 400 MHz<br>Abits         | 2347                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------|--------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 Mbits                     |                          | /Ibits                   | 2.341.74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                             | 4 Mbits                  |                          | 3 Mbits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 Mbits                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                             |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                             | Yes                      |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                             | 4 Units                  | (3 Units on 100-Lead I   | Packages)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                             |                          | Contact Analog Device    | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Yes (16-bit)                | AMI Only                 |                          | Yes (16-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                             |                          | 8                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Yes                         |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Yes                         |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Yes (176-Lead Package Only) |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Automotive Models Only      |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                             |                          | Yes                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                           |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Yes                         |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Yes                         |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Yes                         |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                           |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| −128 dB                     |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Yes                         |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Yes                         |                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                             | •                        | 176-Lead LQFP            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LQFP EPAD                                                                                                                                                                                                                                                                                                                                                                                                                |

|                             | 176-Lead I<br>100-Lead I | Yes (16-bit) AMI Only Ye | Yes (16-bit)         AMI Only           8         Yes           Yes (176-Lead Package Control Pac | Yes (16-bit)         AMI Only         Yes (16-bit)           Yes           Yes           Yes (176-Lead Package Only)           Automotive Models Only           Yes           1           Yes           1           -128 dB           Yes           Yes           176-Lead LQFP EPAD         176-Lead LQFP         176-Lead LQFP EPAD           100-Lead LQFP EPAD         100-Lead LQFP EPAD         100-Lead LQFP EPAD |

ROM には、Dolby Labs 社および DTS 社の最新のマルチチャンネル・オーディオ・デコーディングとポスト・プロセシング・アルゴリズムが出荷時に書込まれています。サポートされるデコーダ/ポスト・プロセッサ・アルゴリズムの組み合わせは、チップ・バージョンとシステム構成により変わります。詳細については、www.analog.com をご覧ください。

$<sup>^2</sup>$  100 ピン・パッケージには External Port Interface がありません。176 ピン・パッケージの ADSP-21486 プロセッサでは、SDRAM コントローラがありません。 詳細については、ページ59の176 ピン LQFP\_EP のピン配置を参照してください。

<sup>&</sup>lt;sup>3</sup> モデルによっては-140 dB の性能を持つ製品があります。詳細については、ページ65のオーダー・ガイドを参照してください。

ページ1の図 1に、ADSP-2148x プロセッサを構成する 2 つのクロック・ドメインを示します。コア・クロック・ドメインには次の機能があります。

- 2個の処理エレメント(PEx、PEy)。各々はALU、乗算器、シフタ、データ・レジスタ・ファイルから構成されています。

- データ・アドレス・ジェネレータ(DAG1、DAG2)

- 命令キャッシュ付きのプログラム・シーケンサ

- PM バスと DM バス。メモリとコアとの間で各コア・プロセッサ・サイクルで 2回の 64 ビット・データ転送をサポートすることが可能。

- 出力ピン付きの周期インターバル・タイマ×1

- 内蔵 SRAM (5 M ビット)およびマスク・プログラマブル ROM (4 M ビット)

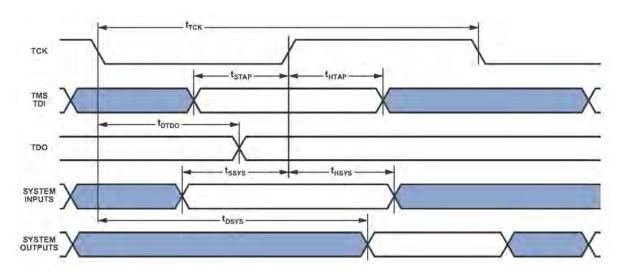

- エミュレーションとバウンダリ・スキャン用の JTAG テスト・アクセス・ポート。JTAG はユーザ・ブレーク・ポイントを使ってソフトウェア・デバッグ機能を提供するため、柔軟な例外処理が可能になります。

ページ1の ADSP-2148x ブロック図には、ペリフェラル・クロック・ドメイン(I/O プロセッサとも呼びます)も示してあり、次の機能があります。

- 32 ビット・データ転送用の IOD0 (ペリフェラル DMA)バスと IOD1 (外部ポート DMA)バス

- コア接続用のペリフェラル・バスと外部ポート・バス

- AMI および SDRAM コントローラ付きの外部ポート

- •4 ユニットの PWM 制御

- 1ユニットの内部メモリー内部メモリ間転送用 MTM

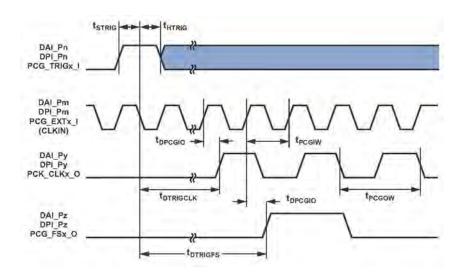

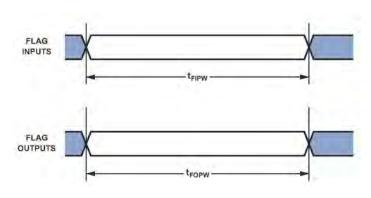

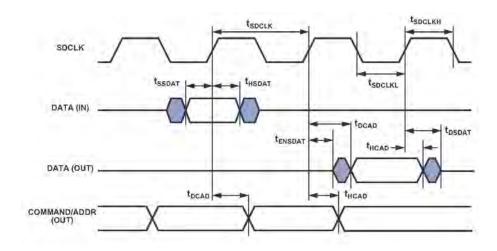

- デジタル・アプリケーション・インターフェース。これには、高精度クロック・ジェネレータ(PCG)×4、シリアル/パラレル接続用の入力データ・ポート(IDP/PDAP)×1、S/PDIF レシーバ/トランスミッタ×1、非同期サンプル・レート・コンバータ×4、シリアル・ポート×8、柔軟な信号ルーティング・ユニット(DAI SRU)×1 が含まれます。

- デジタル・ペリフェラル・インターフェース。これにはタイマ×2、2線式インターフェース(TWI)×1、UART×1、シリアル・ペリフェラル・インターフェース(SPI)×2、高精度クロック・ジェネレータ(PCG)×2、パルス幅変調器(PWM)、柔軟な信号ルーティング・ユニット(DPI SRU)×1 が含まれます。

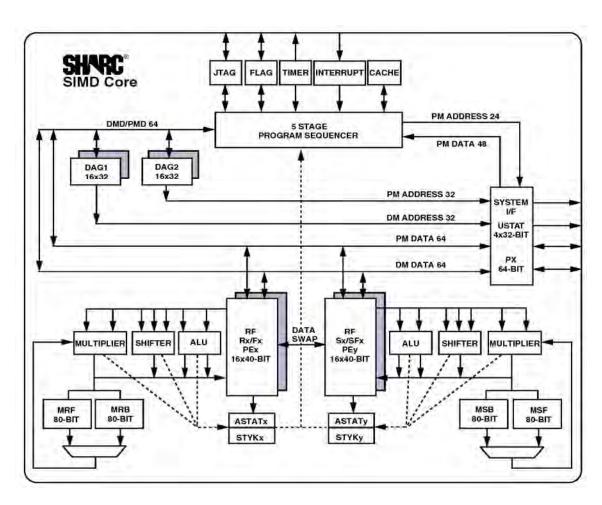

ページ5の SHARC コア機能ブロック図に示すように、これらのプロセッサは、2 個の演算ユニットを採用することにより、広範囲なDSP アルゴリズムに対して従来の SHARC プロセッサに比べて性能を大幅に改善しています。これらのプロセッサは SIMD 演算ハードウェアを使用して、 $400~\mathrm{MHz}$ で  $2.4~\mathrm{GFLOPS}$ の処理を行うことができます。

## ファミリー・コアのアーキテクチャ

ADSP-2148x は、ADSP-2146x、ADSP-2137x、ADSP-2136x、ADSP-2126x、ADSP-21160、ADSP-21161、および第 1 世代 ADSP-2106x SHARC プロセッサとアセンブラ・レベルでコード互換です。ADSP-2148x は、図 2に示すように、ADSP-2126x、ADSP-2136x、ADSP-2137x、ADSP-2146x、ADSP-2116x の各 SIMD SHARC プロセッサとアーキテクチャ機能を共用しています。

## SIMD 演算エンジン

ADSP-2148x は、SIMD (Single-Instruction, Multiple-Data)エンジンとして動作する 2 個の演算処理エレメントを内蔵しています。これらの処理エレメントは PEX と PEY と呼ばれ、各々は、ALU、乗算器、シフタ、レジスタ・ファイルを内蔵しています。 PEX は常時アクティブで、PEY は MODE1 レジスタの PEYEN モード・ビットをセットしてイネーブルすることができます。この SIMD モードがイネーブルされると、同じ命令が両処理エレメントで実行されますが、各処理エレメントは異なるデータに対して動作します。このアーキテクチャは、数学的な DSP アルゴリズムの実行に効果を発揮します。

また、SIMD モードでは、処理エレメントでの演算動作を維持するために 2 倍のデータ帯域幅が必要になるため、メモリと処理エレメントの間のデータ転送方法が影響を受けます。したがって、SIMD モードが開始されると、メモリと処理エレメントとの間の帯域幅も 2 倍になります。SIMD モードでデータ転送に DAG を使用する場合、メモリまたはレジスタ・ファイルに対する各アクセスで 2 個のデータ値が転送されます。

## 独立な並列演算ユニット

各処理エレメントには、演算ユニットのセットがあります。演算ユニットは、ALU、乗算器、シフタから構成されています。これらのユニットは、すべての命令を1サイクルで実行し、並列に動作することで、演算スループットを最大化します。1個のマルチファンクション命令により、ALUと乗算器が並行に動作します。SIMDモードでは、両処理エレメントでALUと乗算器の並行動作が発生します。これらの演算ユニットは、IEEE 32 ビット単精度浮動小数点、40 ビット拡張精度浮動小数点、32 ビット固定小数の各データ・フォーマットをサポートしています。

## タイマ

このプロセッサは、周期ソフトウェア割込みを発生できるコア・タイマを内蔵しています。コア・タイマは、タイムアウト信号としてFLAG3を使用するように設定することができます。

## データ・レジスタ・ファイル

汎用データ・レジスタ・ファイルは、各処理エレメントに内蔵されています。レジスタ・ファイルは、演算ユニットとデータ・バスとの間でデータを転送し、途中結果を保持します。これらの 10 ポート 32 レジスタからなるレジスタ・ファイル(16 個のプライマリ、16 個のセカンダリ)とプロセッサの強化型ハーバード・アーキテクチャとの組み合わせにより、演算ユニットと内部メモリとの間で制約のないデータ・フローが可能になっています。PEX 内のレジスタは  $R0\sim R15$  と呼ばれ、PEY 内のレジスタは  $S0\sim S15$  と呼ばれます。

## コンテキスト・スイッチ

多くのプロセッサ・レジスタには、割込みサービス中に高速なコンテキスト・スイッチを可能にするために使用できるセカンダリ・レジスタがあります。レジスタ・ファイル内のデータ・レジスタ、DAGレジスタ、乗算結果・レジスタにはすべてセカンダリ・レジスタがあります。プライマリ・レジスタはリセット時にアクティブになり、セカンダリ・レジスタはモード・コントロール・レジスタのコントロール・ビットを使ってアクティブにします。

## ユニバーサル・レジスタ

これらのレジスタは汎用タスクに使うことができます。USTAT (4) レジスタを使うと、すべてのペリフェラル・レジスタ(コントロール/ステータス)のビット操作(Set、Clear、Toggle、Test、XOR)を容易に行うことができます。

データ・バス交換レジスタ(PX)の使用により、64 ビット PM データ・バスと 64 ビット DM データ・バスとの間で、または 40 ビット・レジスタ・ファイルと PM/DM データ・バスとの間で、データを渡すことが可能になっています。これらのレジスタには、データ幅の違いを処理するハードウェアが内蔵されています。

## 1 サイクル命令フェッチと 4 個のオペランド

この ADSP-2148x は、データ・メモリ(DM)バスでデータを転送し、プログラム・メモリ(PM)バスで命令とデータを転送する強化型ハーバード・アーキテクチャを採用しています。これらのプロセッサではプログラム・メモリ・バスとデータ・メモリ・バスを分離し、かつ命令キャッシュを内蔵しているため、プロセッサは 4 個のオペランド(各データ・バスから 2 個)と 1 個の命令(キャッシュから)を同時に1サイクルでフェッチすることができます。

#### 命令キャッシュ

このプロセッサは、1個の命令と4個のデータ値をフェッチする3バス動作を可能にする命令キャッシュを内蔵しています。キャッシュは選択的で、PMバス・データ・アクセスとフェッチが競合する命令だけをキャッシュします。このキャッシュにより、コアのフル速度実行(デジタル・フィルタの積和やFFTでのバタフライ処理のようなループ動作)が可能になります。

## ゼロ・オーバーヘッドのハードウェア循環バッファをサポート するデータ・アドレス・ジェネレータ

2個のデータ・アドレス・ジェネレータ(DAG)は、間接アドレシング機能とハードウェアによる循環データ・バッファの構成に使用されます。循環バッファを使うと、ディレイラインの効率の良いプログラミングとデジタル信号処理に必要なその他のデータ構造が実現できるため、広くデジタル・フィルタとフーリエ変換で使用されています。2個のDAGには、最大32個の循環バッファを実現するために十分なレジスタが内蔵されています(16個はプライマリレジスタ・セット用、16個はセカンダリレジスタ・セット用)。DAGは、アドレス・ポインタのラップアラウンドを自動的に処理するため、オーバーヘッドを削減し、性能を向上させ、構成を簡素化します。循環バッファは、任意のメモリ・ロケーションから開始させて終了させることができます。

図 2. SHARC コア・ブロック図

## 柔軟な命令セット

48 ビットの命令ワードにより、多様な並行動作が可能になるため、 簡潔なプログラミングが可能になります。例えば、このプロセッ サは、両処理エレメントで、乗算、加算、減算を条件付きで実行 すると同時に、分岐や最大 4 個の 32 ビット値のメモリからのフェ ッチを 1 命令で行うことができます。

### 可変命令セット・アーキテクチャ(VISA)

ADSP-2148x では、従来型 SHARC プロセッサの標準 48 ビット命令のサポートに加えて、16 ビットと 32 ビットの新しい命令をサポートしています。可変命令セット・アーキテクチャ(VISA)と呼ばれるこの機能では、48 ビット命令の冗長/未使用ビットをなくして、コードの効率化と小型化を行っています。 プログラム・シーケンサでは、内部と外部の SDRAM メモリからの 16 ビット命令と 32 ビット命令のフェッチをサポートしています。このサポートは、非同期メモリ・インターフェース(AMI)までは含まれていません。コード生成ツールでこれらの効率良いオペコードを生成できるようにするためには、VISA オプションを使ってソース・モジュールをビルドする必要があります。

## 内蔵メモリ

ADSP-21483 プロセッサと ADSP-21488 プロセッサは、3 M ビットの RAM (表 3)を、ADSP-21486、ADSP-21487、ADSP-21489 の各プロセッサは 5 M ビットの RAM (表 4)を、それぞれ内蔵しています。各メモリ・ブロックは、コア・プロセッサと I/O プロセッサから独立な 1 サイクルのアクセスをサポートします。

プロセッサの SRAM は、最大 160k ワードの 32 ビット・データとして、320k ワードの 16 ビット・データとして、106.7k ワードの 48 ビット命令(または 40 ビット・データ)として、または最大 5M ビットの様々なワード・サイズの組み合わせとして、構成することができます。すべてのメモリは、16 ビット、32 ビット、48 ビット、または 64 ビット・ワードとしてアクセスすることができます。16 ビットの浮動小数点ストレージ・フォーマットをサポートしています。これにより内部で保存できるデータ量が実質的に 2 倍になります。32 ビット浮動小数点フォーマットと 16 ビット浮動小数点フォーマットとの間の変換は、1 命令で実行されます。各メモリ・ブロックはコードとデータの組み合わせを保存できますが、転送に DM バスを使って 1 つのブロックにデータを保存し、さらに転送に PM バスを使って別のブロックに命令とデータを保存するとき、アクセスが最も効率良くなります。

表 3. 内部メモリ空間(3 Mビット—ADSP-21483/ADSP-21488)

| IOP Registers 0x0000 0000~0x0003 FFFF |                                                            |                         |                         |

|---------------------------------------|------------------------------------------------------------|-------------------------|-------------------------|

| Long Word (64 Bits)                   | Extended Precision Normal or<br>Instruction Word (48 Bits) | Normal Word (32 Bits)   | Short Word (16 Bits)    |

| Block 0 ROM (Reserved)                | Block 0 ROM (Reserved)                                     | Block 0 ROM (Reserved)  | Block 0 ROM (Reserved)  |

| 0x0004 0000-0x0004 7FFF               | 0x0008 0000-0x0008 AAA9                                    | 0x0008 0000–0x0008 FFFF | 0x0010 0000-0x0011 FFFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0004 8000-0x0004 8FFF               | 0x0008 AAAA-0x0008 BFFF                                    | 0x0009 0000–0x0009 1FFF | 0x0012 0000-0x0012 3FFF |

| Block 0 SRAM                          | Block 0 SRAM                                               | Block 0 SRAM            | Block 0 SRAM            |

| 0x0004 9000-0x0004 CFFF               | 0x0008 C000–0x0009 1554                                    | 0x0009 2000–0x0009 9FFF | 0x0012 4000-0x0013 3FFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0004 D000-0x0004 FFFF               | 0x0009 1555–0x0009 FFFF                                    | 0x0009 A000–0x0009 FFFF | 0x0013 4000-0x0013 FFFF |

| Block 1 ROM (Reserved)                | Block 1 ROM (Reserved)                                     | Block 1 ROM (Reserved)  | Block 1 ROM (Reserved)  |

| 0x0005 0000-0x0005 7FFF               | 0x000A 0000-0x000A AAA9                                    | 0x000A 0000-0x000A FFFF | 0x0014 0000-0x0015 FFFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0005 8000-0x0005 8FFF               | 0x000A AAAA-0x000A BFFF                                    | 0x000B 0000-0x000B 1FFF | 0x0016 0000-0x0016 3FFF |

| Block 1 SRAM                          | Block 1 SRAM                                               | Block 1 SRAM            | Block 1 SRAM            |

| 0x0005 9000-0x0005 CFFF               | 0x000A C000-0x000B 1554                                    | 0x000B 2000-0x000B 9FFF | 0x0016 4000-0x0017 3FFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0005 D000-0x0005 FFFF               | 0x000B 1555-0x000B FFFF                                    | 0x000B A000-0x000B FFFF | 0x0017 4000–0x0017 FFFF |

| Block 2 SRAM                          | Block 2 SRAM                                               | Block 2 SRAM            | Block 2 SRAM            |

| 0x0006 0000-0x0006 1FFF               | 0x000C 0000-0x000C 2AA9                                    | 0x000C 0000-0x000C 3FFF | 0x0018 0000-0x0018 7FFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0006 2000- 0x0006 FFFF              | 0x000C 2AAA-0x000D FFFF                                    | 0x000C 4000–0x000D FFFF | 0x0018 8000-0x001B FFFF |

| Block 3 SRAM                          | Block 3 SRAM                                               | Block 3 SRAM            | Block 3 SRAM            |

| 0x0007 0000-0x0007 1FFF               | 0x000E 0000-0x000E 2AA9                                    | 0x000E 0000-0x000E 3FFF | 0x001C 0000-0x001C 7FFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0007 2000-0x0007 FFFF               | 0x000E 2AAA-0x000F FFFF                                    | 0x000E 4000-0x000F FFFF | 0x001C 8000–0x001F FFFF |

<sup>&</sup>lt;sup>1</sup>ADSP-2148x プロセッサによっては、カスタム定義可能な ROM ブロックを内蔵しているものもあります。これらのモデルの ROM アドレスは、この表に示すように予約されていません。詳細については、最寄りの ADI にお尋ねください。

表 4. 内部メモリ空間(5 M ビット—ADSP-21486/ADSP-21487/ADSP-21489)<sup>1</sup>

| IOP Registers 0x0000 0000~0x0003 FFFF |                                                            |                         |                         |

|---------------------------------------|------------------------------------------------------------|-------------------------|-------------------------|

| Long Word (64 Bits)                   | Extended Precision Normal or<br>Instruction Word (48 Bits) | Normal Word (32 Bits)   | Short Word (16 Bits)    |

| Block 0 ROM (Reserved)                | Block 0 ROM (Reserved)                                     | Block 0 ROM (Reserved)  | Block 0 ROM (Reserved)  |

| 0x0004 0000–0x0004 7FFF               | 0x0008 0000-0x0008 AAA9                                    | 0x0008 0000-0x0008 FFFF | 0x0010 0000–0x0011 FFFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0004 8000–0x0004 8FFF               | 0x0008 AAAA-0x0008 BFFF                                    | 0x0009 0000-0x0009 1FFF | 0x0012 0000-0x0012 3FFF |

| Block 0 SRAM                          | Block 0 SRAM                                               | Block 0 SRAM            | Block 0 SRAM            |

| 0x0004 9000–0x0004 EFFF               | 0x0008 C000-0x0009 3FFF                                    | 0x0009 2000-0x0009 DFFF | 0x0012 4000-0x0013 BFFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0004 F000-0x0004 FFFF               | 0x0009 4000-0x0009 FFFF                                    | 0x0009 E000–0x0009 FFFF | 0x0013 C000-0x0013 FFFF |

| Block 1 ROM (Reserved)                | Block 1 ROM (Reserved)                                     | Block 1 ROM (Reserved)  | Block 1 ROM (Reserved)  |

| 0x0005 0000-0x0005 7FFF               | 0x000A 0000-0x000A AAA9                                    | 0x000A 0000–0x000A FFFF | 0x0014 0000–0x0015 FFFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0005 8000–0x0005 8FFF               | 0x000A AAAA-0x000A BFFF                                    | 0x000B 0000-0x000B 1FFF | 0x0016 0000–0x0016 3FFF |

| Block 1 SRAM                          | Block 1 SRAM                                               | Block 1 SRAM            | Block 1 SRAM            |

| 0x0005 9000–0x0005 EFFF               | 0x000A C000-0x000B 3FFF                                    | 0x000B 2000–0x000B DFFF | 0x0016 4000–0x0017 BFFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0005 F000-0x0005 FFFF               | 0x000B 4000-0x000B FFFF                                    | 0x000B E000-0x000B FFFF | 0x0017 C000–0x0017 FFFF |

| Block 2 SRAM                          | Block 2 SRAM                                               | Block 2 SRAM            | Block 2 SRAM            |

| 0x0006 0000–0x0006 3FFF               | 0x000C 0000-0x000C 5554                                    | 0x000C 0000-0x000C 7FFF | 0x0018 0000–0x0018 FFFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0006 4000- 0x0006 FFFF              | 0x000C 5555-0x000D FFFF                                    | 0x000C 8000-0x000D FFFF | 0x0019 0000-0x001B FFFF |

| Block 3 SRAM                          | Block 3 SRAM                                               | Block 3 SRAM            | Block 3 SRAM            |

| 0x0007 0000-0x0007 3FFF               | 0x000E 0000-0x000E 5554                                    | 0x000E 0000-0x000E 7FFF | 0x001C 0000-0x001C FFFF |

| Reserved                              | Reserved                                                   | Reserved                | Reserved                |

| 0x0007 4000–0x0007 FFFF               | 0x000E 5555-0x0000F FFFF                                   | 0x000E 8000-0x000F FFFF | 0x001D 0000–0x001F FFFF |

<sup>&</sup>lt;sup>1</sup>ADSP-2148x プロセッサによっては、カスタム定義可能な ROM ブロックを内蔵しているものもありますが、この表に示すように予約されていません。詳細 については、最寄りの ADI にお尋ねください。

1本のバスを1つのメモリ・ブロック専用にして DM バスと PM バスを使うと、2 個のデータ転送の1サイクルでの実行を確実に行うことができます。この場合、命令はキャッシュ内に存在する必要があります。

表 3と表 4のメモリ・マップに、プロセッサの内部メモリ・アドレス空間を示します。この表で、48 ビットメモリ空間は、このアドレス範囲を48 ビット・メモリとしてアクセスする場合のメモリ領域を表わしています。また、32 ビットメモリ空間は、このアドレス範囲を32 ビット・メモリとしてアクセスする場合のメモリ領域を表わしています。

## ROM ベースのセキュリティ

ADSP-2148x は、ROM セキュリティ機能を持っています。この機能は、内部コードの不正な読出しを防止することにより、ユーザ・ソフトウェア・コードを保護するためのハードウェア・サポートを提供します。この機能を使うと、プロセッサは外部コードからブート・ロードしなくなり、内部 ROM からのみ実行するようになります。さらに、JTAG ポートからプロセッサを自由にアクセスできなくなります。代わりに、JTAG またはテスト・アクセス・ポートからスキャン入力する必要のある独自な 64 ビット・キーが各ユーザに割り当てられます。デバイスは不正なキーを無視します。エミュレート機能は、正しいキーがスキャンされたときにのみ使用可能になります。

## 内蔵メモリの帯域幅

この内部メモリ・アーキテクチャにより、プログラムは 4 個の内の任意のブロックへ同時に 4 回アクセスすることができます(競合するブロックがない場合)。合計帯域幅は、DMD バスと PMD バス (2×64 ビット、CCLK 速度)、および IODO/1 バス(2×32 ビット、PCLK 速度)を使って得られます。

## ファミリー・ペリフェラルのアーキテクチャ

ADSP-2148x ファミリーには、高品質オーディオ、医用画像、通信、軍用、テスト装置、3D グラフィックス、スピーチ認識、モーター・制御、イメージングなどの広範囲なアプリケーションをサポートする豊富なペリフェラルが内蔵されています。

## 外部ポート

外部ポート・インターフェースでは、コア・アクセスと DMA アクセスによる外部メモリへのアクセスをサポートしています。外部メモリ・アドレス空間は 4 バンクに分割されています。すべてのバンクは、非同期メモリまたは同期メモリとして設定することができます。外部ポートは、次のモジュールで構成されています。

Rev. 0 - 7/65 -

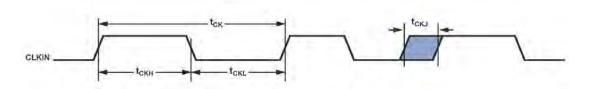

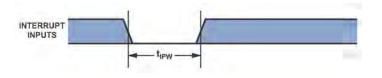

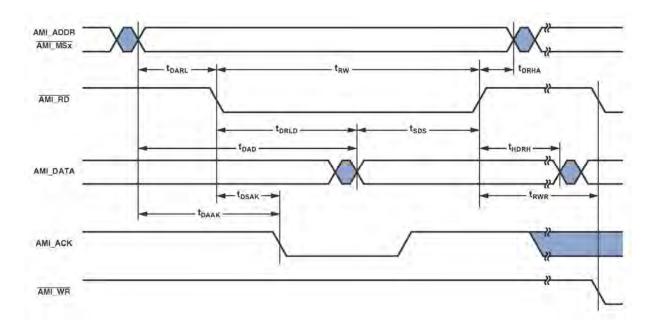

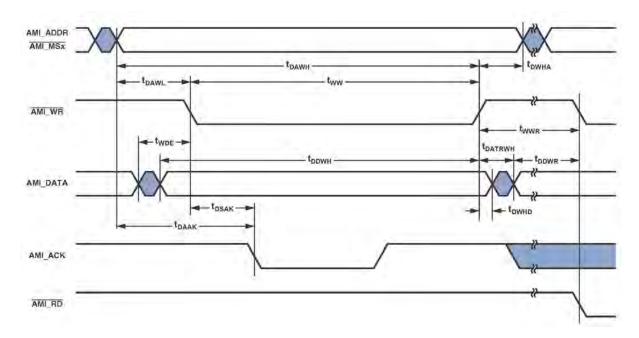

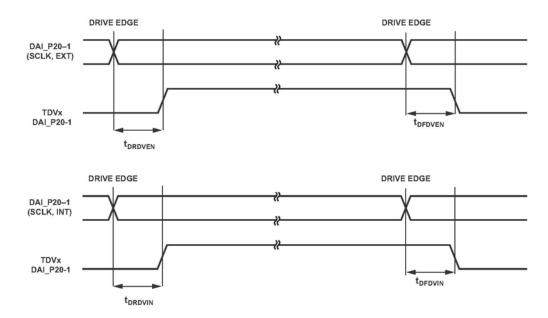

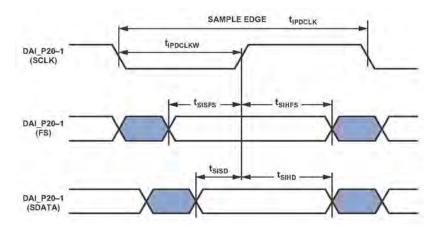

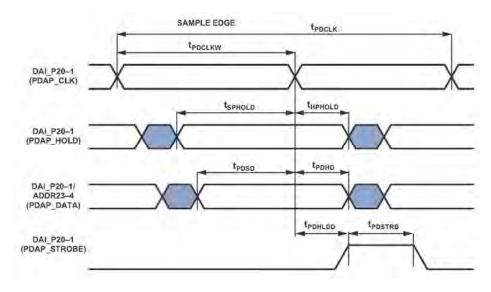

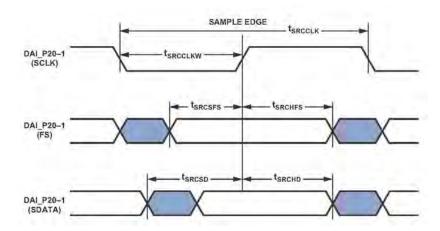

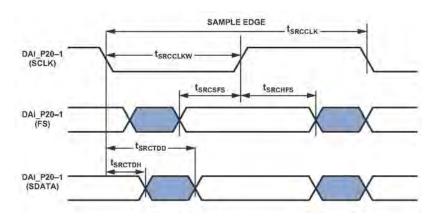

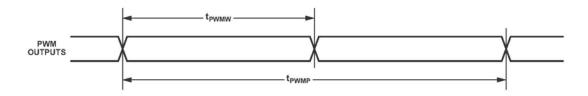

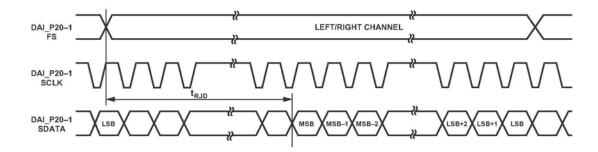

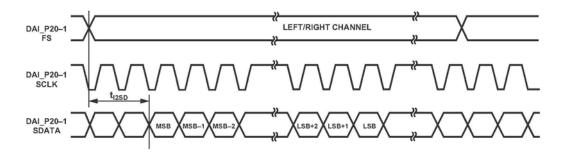

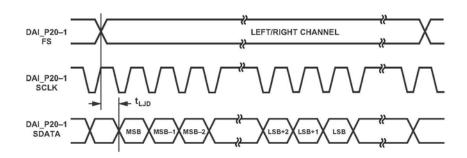

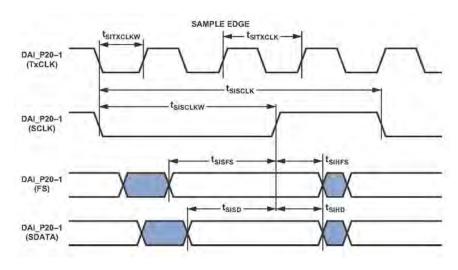

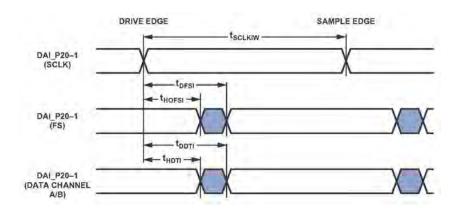

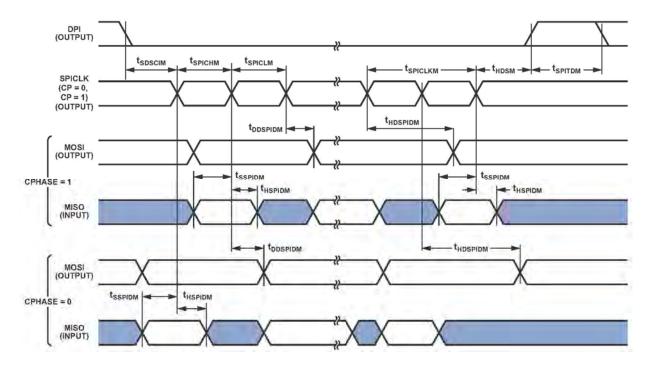

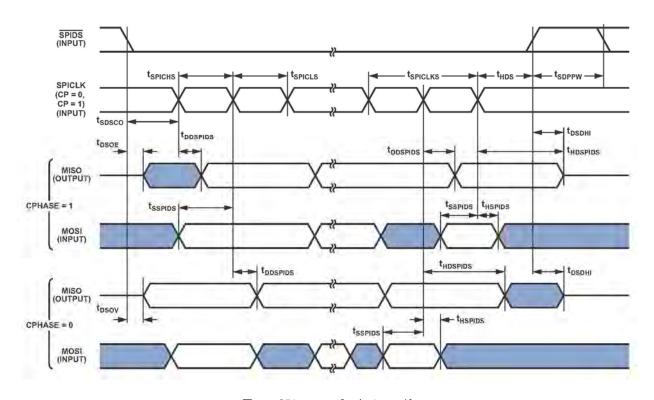

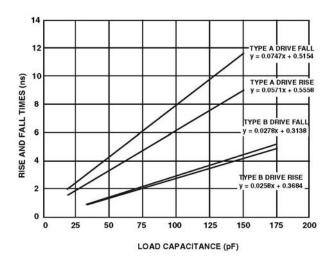

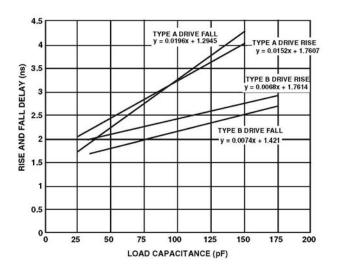

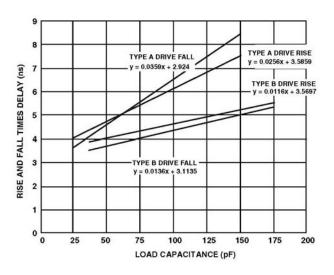

- SRAM、FLASH、一般的な非同期 SRAM アクセス・プロトコルを満たすその他のデバイスと通信する非同期メモリ・インターフェース。バンク 0 の 6M ワードの外部メモリと、バンク 1、バンク 2、バンク 3 の 8M ワードの外部メモリをサポートするAMI。