## 高速半二重*i*Coupler® 絶縁型RS-485トランシーバ

## **ADM2486**

### 特長

半二重の絶縁型RS-485トランシーバ

PROFIBUS®に準拠

ANSI EIA/TIA 485-AおよびISO 8482:1987(E)に準拠

データレート: 20Mbps

5Vまたは3V動作(V<sub>DD1</sub>)

高コモン・モード過渡耐圧: 25kV/ u s以上

絶縁型DEステータス出力

レシーバのフェイルセーフ機能

サーマル・シャットダウン保護機能

バス上に50のノード

安全性規格の認定

UL認定-UL 1577/2500V<sub>rms</sub> (1分間)

CSA component acceptance notice #5A

VDE適合認定

DIN EN 60747-5-2 (VDE 0884 Part 2):2003-01

DIN EN 60950 (VDE 0805): 2001-12; EN 60950: 2000

V<sub>IORM</sub>=560V(ピーク)

動作温度範囲:-40~十85℃

ワイド・ボディの16ピンSOICパッケージ

### アプリケーション

絶縁型RS-485/RS-422インターフェース PROFIBUSネットワーク 工業用フィールド・ネットワーク マルチポイント・データ伝送システム

#### 概要

ADM2486差動バス・トランシーバは、マルチポイント・バスの伝送ラインを使用した双方向データ通信向けに設計された特殊小型トランス絶縁を内蔵したICです。平衡伝送ライン向けに設計されており、ANSI EIA/TIA RS-485-AおよびISO 8482:1987(E)に準拠しています。

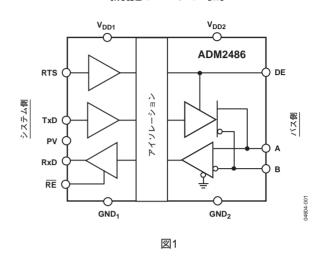

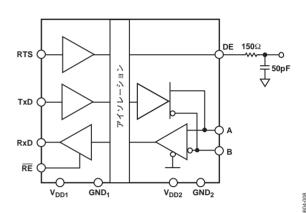

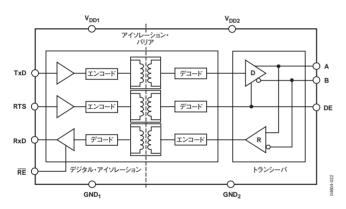

### 機能ブロック図

このデバイスはアナログ・デバイセズの*i*Coupler技術を採用し、3チャンネル・アイソレータ、スリーステート差動ライン・ドライバ、差動入力レシーバをシングル・パッケージに組み込んでいます。デバイスのシステム側は5Vまたは3V電源で動作しますが、バス側はシステムと絶縁された5V電源でのみ動作します。

ADM2486内のドライバはアクティブ・ハイのイネーブル・ピン (DE)を備えています。ドライバの差動出力とレシーバの差動入力は内部で接続され、差動入出力ポートを構成しています (半二重)。この入出力ポートは、ドライバがディスエーブルのとき、またはV<sub>DD1</sub>またはV<sub>DD2</sub>=0Vのとき、バスの負荷を最小化します。また、受信出力を高インピーダンス状態にするアクティブ・ハイのレシーバ・ディスエーブル機能も用意されています。

ADM2486には電流制限機能とサーマル・シャットダウン機能があり、出力の短絡やバス輻輳時の過度な電力消費からデバイスを保護します。 工業用温度範囲で仕様規定され、16ピンのワイド・ボディSOICパッケージを採用しています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいはその利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的また暗示的に許諾するものでもありません。仕様は予告なく変更する場合があります。本記載の商標および登録商標は、各社の所有に属します。\*\*日本語データシートは、REVISIONが古い場合があります。最新の内容については英語版をご参照ください。©2005 Analog Devices, Inc. All rights reserved.

REV.B

本 社/東京都港区海岸1-16-1 電話03(5402)8200 〒105-6891 ニューピア竹芝サウスタワービル

大阪営業所 / 大阪府大阪市淀川区宮原3-5-36 電話0( 6350 )686(代) 〒532-0003 新大阪MTビル2号

### 目次

| 仕様3                                                     | 回路の説明・・・・・・14                 |

|---------------------------------------------------------|-------------------------------|

| タイミング仕様5                                                | 電気的絶縁・・・・・14                  |

| 絶対最大定格 · · · · · · 6                                    | 真理値表・・・・・・14                  |

| ESDに関する注意 · · · · · · · 6                               | パワーアップ/パワーダウン・スレッショールド・・・・・14 |

| ADM2486の特性・・・・・7                                        | サーマル・シャットダウン・・・・・15           |

| パッケージ特性 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・            | レシーバのフェイルセーフ入力・・・・・・15        |

| 適用規格 ・・・・・・・7                                           | 磁界耐性・・・・・・15                  |

| 絶縁および安全性関連の仕様 ・・・・・・・・・7                                | アプリケーション情報・・・・・・16            |

| VDE 0884絕縁特性 · · · · · · 8                              | PV (電源有効) 入力 ·····16          |

| ピン配置および機能の説明 ・・・・・・・9                                   | 絶縁型電源回路・・・・・17                |

| テスト回路・・・・・・10                                           | 外形寸法・・・・・18                   |

| スイッチング特性・・・・・11                                         | オーダー・ガイド・・・・・18               |

| 代表的な性能特性・・・・・・12                                        |                               |

|                                                         |                               |

|                                                         |                               |

| 改訂履歴                                                    |                               |

| 1/05—Rev. A to Rev. B                                   |                               |

| Added PROFIBUS logo · · · · · 1                         |                               |

| 11/04—Rev. 0 to Rev. A                                  |                               |

| Changes to Figure 1 · · · · · · · · · · · · · · · · · · |                               |

| Changes to Figure 6                                     |                               |

| Added Figure 22 through Figure 25                       |                               |

|                                                         |                               |

| Updated Outline Dimensions · · · · · · 18               |                               |

| Changes to Ordering Guide · · · · · 18                  |                               |

## 仕様

特に指定のない限り、2.7  $\leq$  VDD1  $\leq$  5.5 V、4.75 V  $\leq$  VDD2  $\leq$  5.25 V、 $T_A = T_{MIN} \sim T_{MAX}$ 。

### 表1.

| パラメータ                          | Min                   | Тур              | Max           | 単位      | テスト条件/コメント                                                                                                                                        |

|--------------------------------|-----------------------|------------------|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| ドライバ                           |                       |                  |               |         |                                                                                                                                                   |

| 差動出力:                          |                       |                  |               |         |                                                                                                                                                   |

| 差動出力電圧(VoD)                    |                       |                  | 5             | V       | R=∞、⊠3                                                                                                                                            |

|                                | 2.1                   |                  | 5             | V       | R=50Ω (RS-422)、図3                                                                                                                                 |

|                                | 2.1                   |                  | 5             | V       | R=27Ω (RS-485)、図3                                                                                                                                 |

|                                | 2.1                   |                  | 5             | V       | V <sub>TST</sub> =-7~12V, V <sub>DD1</sub> ≥4.7, 図4                                                                                               |

| 相補出力状態のΔ   V <sub>OD</sub>     |                       |                  | 0.2           | V       | R=27Ωまたは50Ω、図3                                                                                                                                    |

| コモン・モード出力電圧(Voc)               |                       |                  | 3             | V       | R=27Ωまたは50Ω、図3                                                                                                                                    |

| 相補出力状態のΔ  Voc                  |                       |                  | 0.2           | V       | R=27Ωまたは50Ω、図3                                                                                                                                    |

| 出力短絡電流、V <sub>OUT</sub> =ハイレベル | 60                    |                  | 200           | mA      | $-7V \le V_{OUT} \le +12V$                                                                                                                        |

| 出力短絡電流、V <sub>OUT</sub> =ローレベル | 60                    |                  | 200           | mA      | $-7V \le V_{OUT} \le +12V$                                                                                                                        |

| バス・イネーブル出力                     |                       |                  |               |         |                                                                                                                                                   |

| 出力ハイレベル電圧                      | V <sub>DD2</sub> -0.1 |                  |               | V       | $I_{ODE}=20 \mu$ A                                                                                                                                |

|                                | V <sub>DD2</sub> -0.3 | $V_{DD2} = 0.1$  |               | V       | I <sub>ODE</sub> =1.6mA                                                                                                                           |

|                                | V <sub>DD2</sub> -0.4 | $V_{DD2}$ $-0.2$ |               | V       | I <sub>ODE</sub> =4mA                                                                                                                             |

| 出力ローレベル電圧                      |                       |                  | 0.1           | V       | $I_{\text{ODE}} = -20 \mu \text{A}$                                                                                                               |

|                                |                       | 0.1              | 0.3           | V       | I <sub>ODE</sub> =-1.6mA                                                                                                                          |

|                                |                       | 0.2              | 0.4           | V       | I <sub>ODE</sub> =-4mA                                                                                                                            |

| ロジック入力                         |                       |                  |               |         |                                                                                                                                                   |

| 入力ハイレベル電圧                      | $0.7V_{\mathrm{DD1}}$ |                  |               | V       | TxD, RTS, RE, PV                                                                                                                                  |

| 入力ローレベル電圧                      |                       |                  | $0.25V_{DD1}$ | V       | $TxD$ , $RTS$ , $\overline{RE}$ , $PV$                                                                                                            |

| CMOSロジック入力電流 (TxD、RTS、RE、PV)   | -10                   | 0.01             | 10            | $\mu$ A | $TxD$ , $RTS$ , $\overline{RE}$ , $PV = V_{DD1}$ $\sharp$ $\hbar$ $\iota$ |

| レシーバ                           |                       |                  |               |         |                                                                                                                                                   |

| 差動入力                           |                       |                  |               |         |                                                                                                                                                   |

| 差動入力スレッショールド電圧、V <sub>TH</sub> | -200                  |                  | 200           | mV      | $-7V \le V_{CM} \le +12V$                                                                                                                         |

| 入力ヒステリシス                       |                       | 70               |               | mV      | $-7V \le V_{CM} \le +12V$                                                                                                                         |

| 入力抵抗(A、B)                      | 20                    | 30               |               | kΩ      | $-7V \le V_{CM} \le +12V$                                                                                                                         |

| 入力電流(A、B)                      |                       |                  | 0.6           | mA      | $V_{IN}=+12V$                                                                                                                                     |

|                                |                       |                  | -0.35         | mA      | $V_{IN}=-7V$                                                                                                                                      |

| RxDロジック出力                      |                       |                  |               |         |                                                                                                                                                   |

| 出力ハイレベル電圧                      | V <sub>DD1</sub> -0.1 |                  |               | V       | $I_{OUT} = 20 \mu A,  V_A - V_B = 0.2 V$                                                                                                          |

|                                | V <sub>DD1</sub> -0.4 | $V_{DD1}$ $-0.2$ |               | V       | $I_{OUT}=4mA$ , $V_A-V_B=0.2V$                                                                                                                    |

| 出力ローレベル電圧                      |                       |                  | 0.1           | V       | $I_{OUT} = -20 \mu A, V_A - V_B = -0.2V$                                                                                                          |

|                                |                       | 0.2              | 0.4           | V       | $I_{OUT}=-4$ mA, $V_A-V_B=-0.2$ V                                                                                                                 |

| 出力短絡電流                         | 7                     |                  | 85            | mA      | V <sub>OUT</sub> =GNDまたはV <sub>CC</sub>                                                                                                           |

| スリーステート出力リーク電流                 |                       |                  | $\pm 1$       | μΑ      | $0.4V \le V_{OUT} \le 2.4V$                                                                                                                       |

| パラメータ            | Min | Тур  | Max | 単位    | テスト条件/コメント                                   |

|------------------|-----|------|-----|-------|----------------------------------------------|

| 電源電流             |     |      |     |       |                                              |

| システム側            |     |      | 1.3 | mA    | $RTS=0V$ , $V_{DD1}=5.5V$                    |

|                  |     | 2.9  |     | mA    | 2Mbps、VDD1=5.5V、図5                           |

|                  |     | 10.2 |     | mA    | 20Mbps、VDD1=5.5V、図5                          |

|                  |     |      | 0.8 | mA    | RTS=0V, VDD1=3V                              |

|                  |     |      | 1.1 | mA    | 2Mbps、VDD1=3V、図5                             |

|                  |     | 4.3  |     | mA    | 20Mbps、VDD1=3V、図5                            |

| バス側              |     |      | 3.0 | mA    | RTS=0V                                       |

|                  |     | 53.4 |     | mA    | 2Mbps、RTS=V <sub>DD1</sub> 、図5               |

|                  |     | 86.7 |     | mA    | 20Mbps、RTS=V <sub>DD1</sub> 、図5              |

| コモン・モード過渡耐圧1     | 25  |      |     | kV/μs | V <sub>CM</sub> =1kV、過渡電圧振幅=800V             |

| 高周波コモン・モード・ノイズ耐性 |     | 100  |     | mV    | $V_{HF}$ =+5 $V$ -2 $V$ < $V_{TEST2}$ <7 $V$ |

|                  |     |      |     |       | 1MHz <f<sub>TEST&lt;50MHz、図6</f<sub>         |

<sup>・</sup>コモン・モード過渡耐圧は、仕様準拠動作を維持しているときのコモン・モード電圧の最大スルーレートにあたります。V<sub>CM</sub>は、システム側とバス側の間のコモン・モードの電位差です。過渡電圧振幅は、コモン・モードの平衡が失われる範囲を表します。コモン・モード電圧スルーレートは、立上がりおよび立下がりの両コモン・モード電圧エッジに適用されます。

## タイミング仕様

特に指定のない限り、2.7  $\leq$   $V_{DD1} \leq$  5.5 V、4.75 V  $\leq$   $V_{DD2} \leq$  5.25 V、 $T_A = T_{MIN} \sim T_{MAX}$ 。

### 表2.

| パラメータ                                                                                   | Min | Тур | Max | 単位      | テスト条件/コメント                                                                                  |

|-----------------------------------------------------------------------------------------|-----|-----|-----|---------|---------------------------------------------------------------------------------------------|

| ドライバ                                                                                    |     |     |     |         |                                                                                             |

| 最大データレート                                                                                | 20  |     |     | Mbps    |                                                                                             |

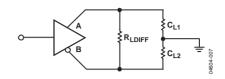

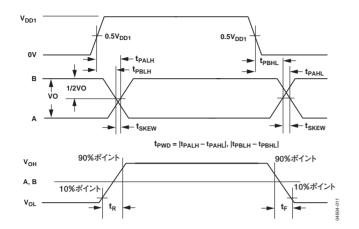

| 伝搬遅延(tpLH、tpHL)                                                                         | 25  | 45  | 55  | ns      | $R_{LDIFF}$ =54 $\Omega$ 、 $C_{L1}$ = $C_{L2}$ = $100$ pF、図7                                |

| RTSからDEまでの伝搬遅延                                                                          | 20  | 35  | 55  | ns      | 図8                                                                                          |

| パルス幅歪み (t <sub>PWD</sub> )                                                              |     |     | 5   | ns      | $R_{LDIFF}$ =54 $\Omega$ 、 $C_{L1}$ = $C_{L2}$ =100pF、図7<br>と図12                            |

| スイッチング・スキュー(t <sub>SKEW</sub> )                                                         |     | 2   | 5   | ns      | $R_{LDIFF}$ =54 $\Omega$ 、 $C_{L1}$ = $C_{L2}$ =100pF、図7<br>と図12                            |

| 立上がり/立下がり時間 $(t_R, t_F)$                                                                |     | 5   | 15  | ns      | $R_{LDIFF}$ =54 $\Omega$ , $C_{L1}$ = $C_{L2}$ =100pF, $\boxtimes$ 7 $\succeq \boxtimes 12$ |

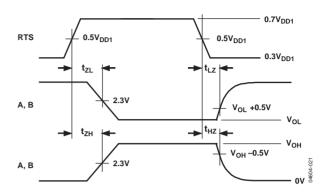

| イネーブル時間                                                                                 |     | 43  | 53  | ns      | 図9と図14                                                                                      |

| ディスエーブル時間                                                                               |     | 43  | 55  | ns      | 図9と図14                                                                                      |

| イネーブル・スキュー( t <sub>AZH</sub> ーt <sub>BZL</sub>  、 t <sub>AZL</sub> ーt <sub>BZH</sub>  ) |     | 1   | 3   | ns      | 図9と図14                                                                                      |

| ディスエーブル・スキュー $( t_{AZH}-t_{BZL} , t_{AZL}-t_{BZH} )$                                    |     | 2   | 5   | ns      | 図9と図14                                                                                      |

| レシーバ                                                                                    |     |     |     |         |                                                                                             |

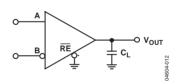

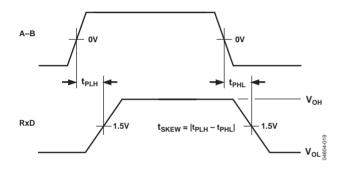

| 伝搬遅延(t <sub>PLH</sub> 、t <sub>PHL</sub> )                                               | 25  | 45  | 55  | ns      | C <sub>L</sub> =15pF、図10と図13                                                                |

| 差動スキュー(t <sub>SKEW</sub> )                                                              |     |     | 5   | ns      | C <sub>L</sub> =15pF、図10と図13                                                                |

| イネーブル時間                                                                                 |     | 3   | 13  | ns      | $R_L=1k\Omega$ 、 $C_L=15pF$ 、図11と図15                                                        |

| ディスエーブル時間                                                                               |     | 3   | 13  | ns      | $R_L=1k\Omega$ 、 $C_L=15pF$ 、図11と図15                                                        |

| PV(電源有効)入力                                                                              |     |     |     |         |                                                                                             |

| イネーブル時間                                                                                 |     | 1   | 2   | $\mu$ s |                                                                                             |

| ディスエーブル時間                                                                               |     | 3   | 5   | $\mu$ s |                                                                                             |

### 絶対最大定格

特に指定のない限り、 $T_A=25$   $\mathbb{C}$ 。すべての電圧はそれぞれのグラウンドを基準とします。

#### 表3.

| パラメータ                   | 定格                          |

|-------------------------|-----------------------------|

| V <sub>DD1</sub>        | -0.5~+7V                    |

| $V_{\mathrm{DD2}}$      | $-0.5 \sim +6 \text{V}$     |

| デジタル入力電圧(RTS、RE、TxD)    | $-0.5V \sim V_{DD1} + 0.5V$ |

| デジタル出力電圧                |                             |

| RxD                     | $-0.5V \sim V_{DD1} + 0.5V$ |

| DE                      | $-0.5V \sim V_{DD2} + 0.5V$ |

| ドライバ出力/レシーバ入力電圧         | -9~+14V                     |

| 動作温度範囲                  | -40∼+85°C                   |

| 保存温度範囲                  | -55~+150°C                  |

| ピン当たりの平均出力電流            | −35~+35mA                   |

| $	heta_{	extsf{JA}}$ 抵抗 | 73℃/W                       |

| リード・ピン温度                |                             |

| ハンダ処理(10秒)              | 260℃                        |

| ベーキング時間(60秒)            | 215℃                        |

| 赤外線(15秒)                | 220℃                        |

左記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な 損傷を与えることがあります。この規定はストレス定格のみを指定するも のであり、この仕様の動作セクションに記載する規定値以上でのデバイ ス動作を定めたものではありません。デバイスを長時間絶対最大定格状 態に置くと、デバイスの信頼性に影響を与えることがあります。

### 注意

ESD(静電放電)の影響を受けやすいデバイスです。人体や試験機器には4,000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣下や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

## ADM2486特性

### パッケージ特性

表4.

| パラメータ              | 記号                | Min | Тур       | Max | 単位   | テスト条件            |

|--------------------|-------------------|-----|-----------|-----|------|------------------|

| 抵抗(入力~出力間)1        | R <sub>I-O</sub>  |     | $10^{12}$ |     | Ω    |                  |

| 容量(入力~出力間)1        | C <sub>I-O</sub>  |     | 3         |     | pF   | f=1MHz           |

| 入力容量2              | CI                |     | 4         |     | pF   |                  |

| 入力側ICの接合点とケース間の熱抵抗 | $\theta_{ m JCI}$ |     | 33        |     | °C/W | パッケージ裏側中央に熱電対を装着 |

| 出力側ICの接合点とケース間の熱抵抗 | $\theta_{ m JCO}$ |     | 28        |     | ℃/W  |                  |

<sup>1</sup> デバイスを2ピン・デバイスとみなして1、2、3、4、5、6、7、8の各ピンを互いに接続し、9、10、11、12、13、14、15、16の各ピンを互いに接続。

### 適用規格

ADM2486は次の機関から認定を受けています。

表5.

| 機関  | 認定タイプ                                                  | 注                                                                             |

|-----|--------------------------------------------------------|-------------------------------------------------------------------------------|

| UL  | 1577部品認定プログラムによる認定。File E214100                        | UL1577に従い、各ADM2486は3000Vrms以上の絶縁テスト電圧を1秒間加えるテストを実施しています(リーク電流検出限界=5 $\mu$ A)。 |

| CSA | 「CSA Component Acceptance Notice #5A」による認定。File 205078 |                                                                               |

| VDE | 認定規格: DIN EN 60747-5-2 (VDE 0884 Part 2): 2003-01      | VDE 0884に従い、各ADM2486は1050V <sub>PEAK</sub> 以上の                                |

|     | DIN EN 60950 (VDE 0805): 2001-12;EN 60950:2000         | 絶縁テスト電圧を1秒間加えるテストを実施しています                                                     |

|     | File 2471900-4880-0001                                 | (部分放電検出限界=5pC)。                                                               |

### 絶縁および安全性関連の仕様

表6.

| パラメータ              | 記号     | 値       | 単位   | 条件                           |

|--------------------|--------|---------|------|------------------------------|

| 定格絶縁電圧             |        | 2500    | Vrms | 1分間継続                        |

| 最小外部空間距離(クリアランス)   | L(I01) | 最小7.45  | mm   | 入力ピンから出力ピンまでの空間最短距離を測定       |

| 最小外部沿面距離(クリページ)    | L(I02) | 最小8.1   | mm   | 入力ピンから出力ピンまでのボディ表面に沿う最短パス    |

|                    |        |         |      | を測定                          |

| 最小内部空間距離(内部クリアランス) |        | 最小0.017 | mm   | 絶縁体を通過する絶縁距離                 |

| 耐トラッキング性(トラッキング指数) | CTI    | >175    | V    | DIN IEC 112/VDE 0303 Part 1  |

| 絶縁グループ             |        | IIIa    |      | 材料グループ(DIN VDE 0110、1/89、表1) |

<sup>2</sup>入力容量は任意の入力データ・ピンとグラウンド間で測定。

### VDE 0884絶縁特性

このアイソレータは基本的な電気的絶縁を得るのに適していますが、必ず安全性データの範囲内で使用してください。安全性データを超えるような場合は、保護回路を使用する必要があります。

パッケージ表面のアスタリスク(\*)は、560V(ピーク)動作電圧に対してVDE 0884認定済みであることを示します。

### 表7.

| 説明                                                                         | 記号                    | 特性       | 単位           |

|----------------------------------------------------------------------------|-----------------------|----------|--------------|

| DIN VDE 0110に基づく定格電圧に対する設置カテゴリ                                             |                       |          |              |

| ≤150Vrms                                                                   |                       | I∼IV     |              |

| ≤300Vrms                                                                   |                       | I~III    |              |

| ≤400Vrms                                                                   |                       | I∼II     |              |

| 環境カテゴリ                                                                     |                       | 40/85/21 |              |

| 汚染度 (DIN VDE 0110、表I)                                                      |                       | 2        |              |

| 最大動作絶縁電圧                                                                   | V <sub>IORM</sub>     | 560      | $V_{PEAK}$   |

| 入力~出力間テスト電圧、メソッドb1                                                         | $V_{PR}$              | 1050     | $V_{PEAK}$   |

| $V_{IORM} \times 1.875 = V_{PR}$ 、 $100\%$ 出荷テスト、 $t_m = 1$ 秒、部分放電 $< 5pC$ |                       |          |              |

| 入力~出力間テスト電圧、メソッドa                                                          |                       |          |              |

| (環境テスト・サブグループ1の後)                                                          |                       |          |              |

| V <sub>IORM</sub> ×1.6=V <sub>PR</sub> 、t <sub>m</sub> =60秒、部分放電<5pC       |                       | 896      | $V_{PEAK}$   |

| (入力および/または安全性テスト・サブグループ2/3の後)                                              |                       |          |              |

| V <sub>IORM</sub> ×1.2=V <sub>PR</sub> 、t <sub>m</sub> =60秒、部分放電<5pC       | $V_{PR}$              | 672      | $V_{PEAK}$   |

| 最大許容過電圧                                                                    |                       |          |              |

| (過渡過電圧、t <sub>TR</sub> =10秒)                                               | $V_{TR}$              | 4000     | $V_{PEAK}$   |

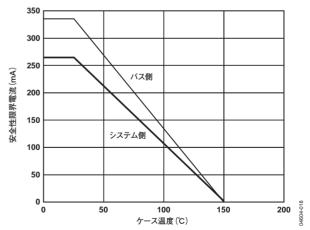

| 安全性限界値(故障時に許容できる最大値、図21のサーマル・ディレーティング・カーブを参照)                              |                       |          |              |

| ケース温度                                                                      | TS                    | 150      | $\mathbb{C}$ |

| 入力電流                                                                       | $I_{S,INPUT}$         | 265      | mA           |

| 出力電流                                                                       | I <sub>S,OUTPUT</sub> | 335      | mA           |

| Ts、V <sub>IO</sub> =500Vでの絶縁抵抗                                             | Rs                    | >109     | Ω            |

### ピン配置および機能の説明

#### NC=未接続

\* ピン2とピン8は内部で接続されており、どちらか一方または両方をGND<sub>1</sub>として使用できます。 ピン9とピン15は内部で接続されており、どちらか一方または両方をGND<sub>2</sub>として使用できます。

図2. ピン配置

### 表8.

| ピン番号   | 記号                 | 機能                                                                                                                                        |

|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | $V_{\mathrm{DD1}}$ | 電源(システム側)                                                                                                                                 |

| 2,8    | GND <sub>1</sub>   | グラウンド(システム側)                                                                                                                              |

| 3      | RxD                | レシーバの出力データ。この出力は $(A-B)>200$ mVのときハイレベル、 $(A-B)<-200$ mVのときローレベルになります。レシーバがディスエーブルのとき、すなわち $\overline{RE}$ がハイレベルに駆動されたとき、スリーステート状態になります。 |

| 4      | RE                 | レシーバのイネーブル入力。アクティブ・ロー入力。この入力をローレベルにするとレシーバがイネーブルになり、ハイレベルにするとレシーバがディスエーブルになります。                                                           |

| 5      | RTS                | 送信要求入力。この入力をハイレベルにするとドライバがイネーブルになり、ローレベルにするとドライバがディスエー<br>ブルになります。                                                                        |

| 6      | TxD                | 送信データ入力。ドライバから送信するデータがこのピンに入力されます。                                                                                                        |

| 7      | PV                 | 電源有効入力。パワーアップおよびパワーダウン時に使用します。「アプリケーション情報」を参照。                                                                                            |

| 9, 15  | GND <sub>2</sub>   | グラウンド(バス側)                                                                                                                                |

| 10     | DE                 | ドライバのイネーブル・ステータス出力。この出力はドライバのイネーブル状態またはディスエーブル状態をバス上の                                                                                     |

|        |                    | 他のデバイスに知らせます。ドライバがイネーブルのときDEはハイレベルに、ドライバがディスエーブルのときDEはローレベルになります。                                                                         |

| 11, 14 | NC                 | 未接続                                                                                                                                       |

| 12     | A                  | 非反転ドライバ出力/レシーバ入力。ドライバがディスエーブルのとき、またはV <sub>DD1</sub> かV <sub>DD2</sub> がパワーダウンのとき、ピンAは高インピーダンス状態になって、バスの過負荷を回避します。                        |

| 13     | В                  | 反転ドライバ出力/レシーバ入力。ドライバがディスエーブルのとき、またはV <sub>DD1</sub> かV <sub>DD2</sub> がパワーダウンのとき、ピンB<br>は高インピーダンス状態になって、バスの過負荷を回避します。                     |

| 16     | $V_{\mathrm{DD2}}$ | 電源(バス側)                                                                                                                                   |

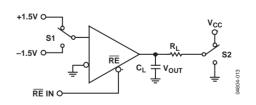

### テスト回路

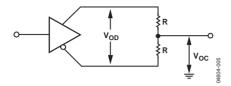

図3. ドライバ電圧測定

図4. ドライバ電圧測定

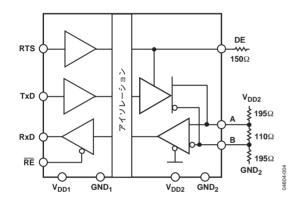

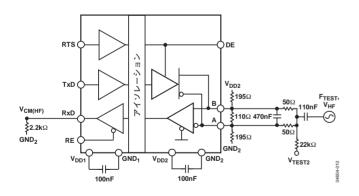

図5. 電源 - 電流測定テスト回路

図6. 高周波コモン・モード・ノイズ・テスト回路

図7. ドライバ伝搬遅延

図8. RTSからDEまでの伝搬遅延

図9. ドライバ・イネーブル / ディスエーブル

図10. レシーバ伝搬遅延

図11. レシーバ・イネーブル / ディスエーブル

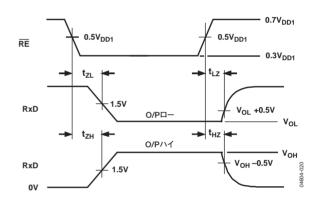

## スイッチング特性

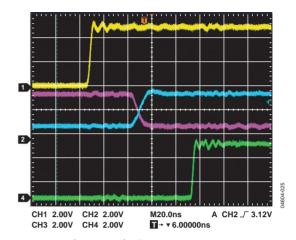

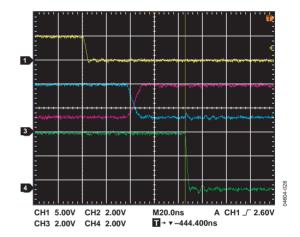

図12. ドライバ伝搬遅延、立上がり/立下がりタイミング

図13. レシーバ伝搬遅延

図14. ドライバ・イネーブル / ディスエーブル・タイミング

図15. レシーバ・イネーブル / ディスエーブル・タイミング

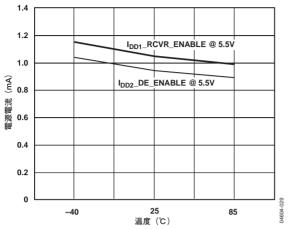

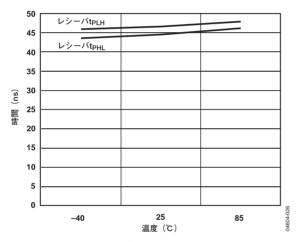

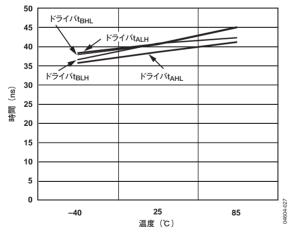

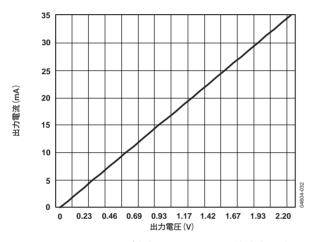

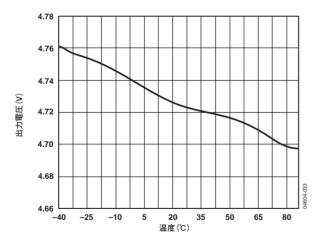

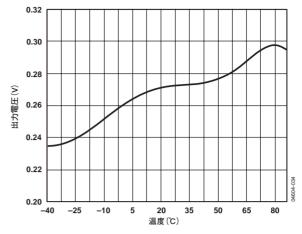

### 代表的な性能特性

図16. 無負荷時電源電流の温度特性

図17. ドライバの伝搬遅延の温度特性

図18. レシーバの伝搬遅延の温度特性

図19. ドライバ / レシーバ伝搬遅延、ローレベルからハイレベルへ (RLDiff = 54、CL1 = CL2 = 100pF)

図20. ドライバ / レシーバ伝搬遅延、ハイレベルからローレベルへ (  $R_{LDiff} = 54$  、 $C_{L1} = C_{L2} = 100 pF$  )

図21. サーマル・ディレーティング・カーブ、VDE 0884による 安全性限界値のケース温度依存性

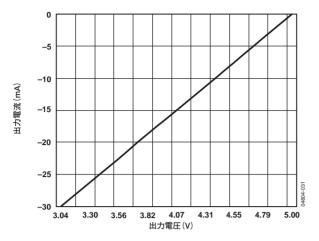

図22. レシーバ出力ハイレベル電圧 対 出力電流

図23. レシーバ出力ローレベル電圧 対 出力電流

図24. レシーバ出力ハイレベル電圧の温度特性 (I=-4mA)

図25. レシーバ出力ローレベル電圧の温度特性 (I=-4mA)

### 回路の説明

### 電気的絶縁

ADM2486では、インターフェースのシステム側で電気的絶縁を行っています。したがって、デバイスは主にデジタル・アイソレーション部とトランシーバ部からなります(図26)。 TxDピンに入力されるドライバ入力信号とRTSピンに入力される送信要求信号はロジック・グラウンド  $(GND_1)$ を基準としており、アイソレーション・バリアを越えて絶縁されたグラウンド  $(GND_2)$ を基準とするトランシーバ部に渡されます。同様に、トランシーバ部の絶縁されたグラウンドを基準とするレシーバ出力は、アイソレーション・バリアを越えてロジック・グラウンドを基準とするRxDピンに出力されます。

#### iCoupler技術

デジタル信号はiCoupler技術によってアイソレーション・バリアを越えて送信されます。この技術では、チップ・サイズのトランス巻線を使って、デジタル信号をバリアの一方から他方へ磁気的に結合します。デジタル入力は、トランスの1次巻線を励磁できる能力を持つ波形にエンコードされます。2次巻線では、エンコードされた波形が送信された元のバイナリ値にデコードされます。

図26. ADM2486のデジタル・アイソレーション部とトランシーバ部

#### 真理値表

以下の真理値表では次の略語を使っています。

| 略語 | 説明           |

|----|--------------|

| Н  | ハイレベル        |

| I  | 不定           |

| L  | ローレベル        |

| X  | 無関係          |

| Z  | 高インピーダンス(オフ) |

| NC | 切断           |

表9. 送信

| 電源状態             | Ì                | 入力  | 入力  |   |   | 出力 |  |  |  |

|------------------|------------------|-----|-----|---|---|----|--|--|--|

| V <sub>DD1</sub> | V <sub>DD2</sub> | RTS | TxD | Α | В | DE |  |  |  |

| オン               | オン               | Н   | Н   | Н | L | Н  |  |  |  |

| オン               | オン               | Н   | L   | L | Н | Н  |  |  |  |

| オン               | オン               | L   | X   | Z | Z | L  |  |  |  |

| オン               | オフ               | X   | X   | Z | Z | L  |  |  |  |

| オフ               | オン               | X   | X   | Z | Z | L  |  |  |  |

| オフ               | オフ               | X   | X   | Z | Z | L  |  |  |  |

表10. 受信

| 電源状態             |                  | 入力                 |        | 出力  |

|------------------|------------------|--------------------|--------|-----|

| V <sub>DD1</sub> | V <sub>DD2</sub> | A-B(V)             | RE     | RxD |

| オン               | オン               | >0.2               | LまたはNC | Н   |

| オン               | オン               | <-0.2              | LまたはNC | L   |

| オン               | オン               | -0.2 < A - B < 0.2 | LまたはNC | I   |

| オン               | オン               | 入力オープン             | LまたはNC | Н   |

| オン               | オン               | X                  | Н      | Z   |

| オン               | オフ               | X                  | LまたはNC | Н   |

| オフ               | オン               | X                  | LまたはNC | Н   |

| オフ               | オフ               | X                  | LまたはNC | L   |

### パワーアップ/パワーダウン・スレッショールド

ADM2486のパワーアップ/パワーダウン特性は、表11に示す電源スレッショールドに従います。パワーアップすると、ADM2486の出力信号 (A、B、RxD、DE)は、両電源がそれぞれのスレッショールドを超えた後に、正しい状態に到達します。パワーダウンすると、ADM2486の各出力信号は少なくとも1つの電源がパワーダウン・スレッショールドを下回るまで、正しい状態を保持します。 $V_{DD1}$ のパワーダウン・スレッショールド以下になると、ADM2486の出力信号は $4\mu$  s内に無電源状態に到達します。

表11. パワーアップ / パワーダウン・スレッショールド

| 電源                 | 遷移     | スレッショールド(V) |

|--------------------|--------|-------------|

| $V_{\mathrm{DD1}}$ | パワーアップ | 2.0         |

| $V_{DD1}$          | パワーダウン | 1.0         |

| $V_{\mathrm{DD2}}$ | パワーアップ | 3.3         |

| $V_{\mathrm{DD2}}$ | パワーダウン | 2.4         |

### サーマル・シャットダウン

ADM2486はサーマル・シャットダウン回路を内蔵しており、故障時に消費電力が大きくなり過ぎないように保護します。ドライバ出力を低インピーダンス電源に短絡すると、大きなドライバ電流が流れます。温度検出回路がこの状態でのチップ温度の上昇を検出して、ドライバ出力をディスエーブルにします。この回路は、チップ温度が150℃に到達したとき、ドライバ出力をディスエーブルにするように設計されています。デバイスが冷えて140℃になると、ドライバは再びイネーブルになります。

### レシーバのフェイルセーフ入力

レシーバ入力にはフェイルセーフ機能が内蔵されており、A入力とB入力がフローティングまたはオープンのとき、ロジック・ハイレベルのRxD出力を保証します。

### 磁界耐性

*i*Couplerはコアレスの技術を採用し、磁性部品がないためコア材の磁気 飽和といった問題がありません。ですから、*i*Couplerは基本的にDC磁 界に対して無限の耐性があります。

しかし、iCouplerのAC磁界耐性は、次の条件によって制限されます。すなわち、受信側コイル(この場合は下側のコイル)に発生した誘導誤差電圧が大きくなって、デコーダをセットもしくはリセットさせる誤動作が発生するような場合です。以下の解析でこの状態が発生する条件を定義します。ADM2486は3V動作が最も感受性の高い動作モードであることから、この状態を調べます。受信側コイルへの誘導電圧は次式で求められます。

$$V = \left(\frac{-d\beta}{dt}\right) \sum \pi r_n^2; \ n = 1, 2, \dots, N$$

ここで、トランス出力のパルスは1.0V以上の振幅があるとします。

$\beta =$ 磁束密度(Gauss:ガウス)

N = 受信側コイルの巻数

$r_n = 受信側コイル巻数n回目の半径(cm)$

デコーダは約0.5Vの検出スレッショールドを持つため、誘導電圧に対しては0.5Vの余裕があります。

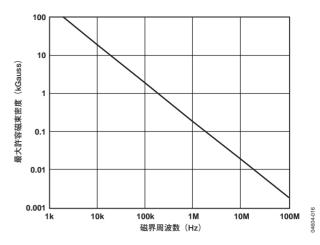

受信側コイルの形状を考え、誘導電圧がデコーダの0.5Vマージンの50% 以下とすると、最大許容磁界は図27のように計算されます。

図27. 最大許容外部磁束密度

たとえば、磁界周波数=1MHzで、最大許容磁界=0.2kGaussの場合、受信側コイルでの誘導電圧は0.25Vになります。これは検出スレッショールドの約50%であることから、出力遷移の誤動作は起きません。同様に、仮にこのような条件が送信パルス内に存在し、かつ最悪ケースの極性であっても、受信パルスが1.0V以上から0.75Vへ減少されるため、デコーダの検出スレッショールド0.5Vに対してまだ余裕があります。

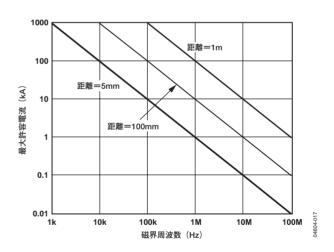

図28に磁束密度値を示します。この図では、ADM2486のトランスから一定の距離をおいたときの磁束密度値を、わかりやすい最大許容電流で表しています。

図28. 電流とADM2486との間の距離を 変えたときの最大許容電流

強い磁界と高周波が組み合わされると、PCボードのパターンで形成されるループに大きな誤差電圧が誘導され、後段回路のスレッショールドがトリガされることがあります。パターンのレイアウトでは、このようなことがないように注意が必要です。

### アプリケーション情報

### PV(電源有効)入力

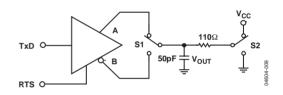

$V_{DDI}$ ではパワーアップ時とパワーダウン時の遷移がゆるやか( $>100 \mu s/V$ ) な場合、出力AとBでチャタリングが発生することがあります。ADM2486はこのチャタリングを防止するためPV(電源有効)デジタル入力を備えています。

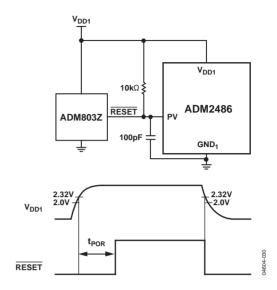

このPVピンは、 $V_{DDI}$ が2.0Vを超えるまでローレベルで駆動する必要があります。 $V_{DDI}$ が2.0Vを超えたら、このピンをハイレベルにする必要があります。逆に、パワーダウンの場合、 $V_{DDI}$ が2.0Vに到達する前にPVをローレベルにする必要があります。

このPVピンをオープン・ドレイン出力で駆動する場合、プルアップ抵抗値として $10k\Omega$ を推奨します。この抵抗は100pFのコンデンサでGNDにバイパスします(図30参照)。

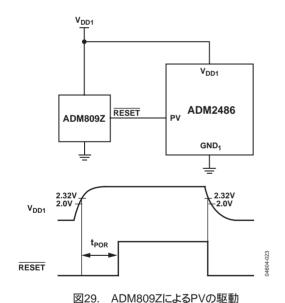

たとえば、PV入力はADM809Z(スレッショールド電圧は2.32V:プッシュ プル出力)などのシステム・リセット用ICの出力で駆動できます(図29 参照)。

図30. オープン・ドレイン出力によるPVの駆動

ADIVIOUSZICA ST V V 河上里川

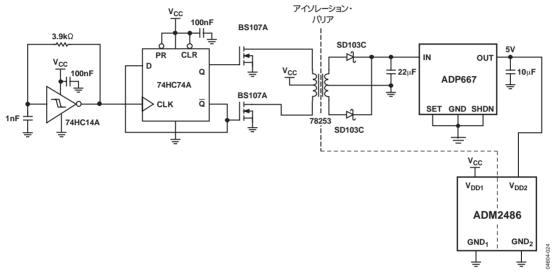

### 絶縁型電源回路

ADM2486は、V<sub>DD2</sub>ピンとGND2ピンの間で5V、100mAを供給できる絶縁型電源を必要とします。適切なIC電源がない場合は、図31に示すようなディスクリート回路を使用できます。センター・タップ付きトランスにより電気的絶縁性を確保します。位相が180度ずれた一対の方形波で1次巻線を励磁します。一対のショットキ・ダイオードと平滑コンデンサを使って、2次巻線から整流した信号を生成します。ADP667リニア電圧レギュレータは、ADM2486のバス側回路に安定化された電源を供給します。

一対の方形波を生成するには、相補 $Q/\overline{Q}$ 出力を持つD型フリップ・フロップを用います。このフリップ・フロップは、出力Qがクロック入力信号に追従するように接続できます。ローカル・クロック信号が使用できない場合は、反転シュミット・トリガ、抵抗、コンデンサを使って単純なデジタル発振器を構成できます。この場合、 $3.9k\Omega$ と1nFで364kHzの方形波を発生します。 $Q/\overline{Q}$ フリップ・フロップ出力でオンオフされる一対のディスクリートNMOSトランジスタが、トランスの1次巻線のセンター・タップから交互に電流を流します。

図31. 絶縁型電源回路

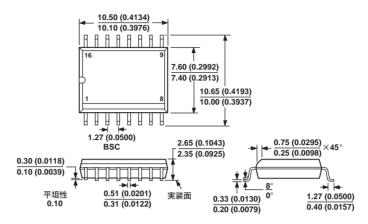

### 外形寸法

JEDEC標準MS-013AAに準拠 管理寸法はミリメートルの単位で表記しています。 カッコ内に示すインチ単位の寸法は、ミリメートル値に基づく概数で、 参考のためにのみ記載しています。設計ではこの値を使用しないでください。

> 図32. 16ピンSOIC ワイド・ボディ (RW-16) 寸法単位:mm(インチ)

### オーダー・ガイド

| 製品モデル                         | データレート<br>(Mbps) | 温度範囲      | パッケージ            | 個数   | パッケージ・<br>オプション |

|-------------------------------|------------------|-----------|------------------|------|-----------------|

| ADM2486BRW                    | 20               | -40∼+85°C | 16ピン・ワイド・ボディSOIC | 47   | RW-16           |

| ADM2486BRW-REEL               | 20               | -40∼+85℃  | 16ピン・ワイド・ボディSOIC | 1000 | RW-16           |

| ADM2486BRWZ <sup>1</sup>      | 20               | -40∼+85°C | 16ピン・ワイド・ボディSOIC | 47   | RW-16           |

| ADM2486BRWZ-REEL <sup>1</sup> | 20               | -40~+85°C | 16ピン・ワイド・ボディSOIC | 1000 | RW-16           |

<sup>1</sup> Z=鉛フリー製品

TDS03/2005/500