# 14ビット、1 GSPS JESD204B デュアルA/Dコンバータ

データシート AD9680

# 特長

JESD204B (サブクラス 1) 符号化のシリアル・デジタル出力 1 GSPS (デフォルト設定)でチャンネルあたり 1.65 W の消費電力

SFDR = 340 MHz  $\stackrel{.}{\text{c}}$  85 dBFS、1 GHz  $\stackrel{.}{\text{c}}$  80 dBFS SNR = 340 MHz  $\stackrel{.}{\text{c}}$  65.3 dBFS (A<sub>IN</sub> = -1.0 dBFS)、1 GHz  $\stackrel{.}{\text{c}}$  61.4 dBFS

ENOB = 10 MHz で 10.8 ビット

$DNL = \pm 0.5 LSB$

$INL = \pm 2.5 LSB$

ノイズ密度 = 1 GSPS で−154 dBFS/Hz

動作電源電圧: 1.25 V、2.5 V、3.3 V dc

ノーミス・コード

ADC リファレンス電圧を内蔵

フレキシブルな入力範囲と終端インピーダンス

1.46 V p-p~1.94 V p-p (公称 1.70 V p-p)

400 Ω、200 Ω、100 Ω、50 Ω 差動

有効アナログ入力フル・パワー帯域幅: 2 GHz

チャンネル・アイソレーション/クロストーク: 95 dB

AGC の実現に便利な振幅検出ビットを装備

チャンネルあたり 2 個の広帯域デジタル・プロセッサを内蔵 12 ビット NCO、最大 4 個のカスケード接続ハーフバンド・フィルタ

差動クロック入力

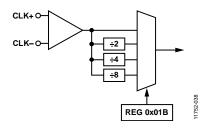

-1、2、4、または8分周

フレキシブルな JESD204B レーン構成

小信号デザー

### アプリケーション

### 通信

ダイバーシティ・マルチバンド、マルチモード・デジタル・レ シーバ

3G/4G、TD-SCDMA、W-CDMA、GSM、LTE

汎用ソフトウェア無線

超広帯域衛星レシーバ

計装機器

レーダー

シグナル・インテリジェンス (SIGINT)

DOCSIS 3.0 CMTS アップストリーム受信パス

HFC デジタル逆方向パス・レシーバ

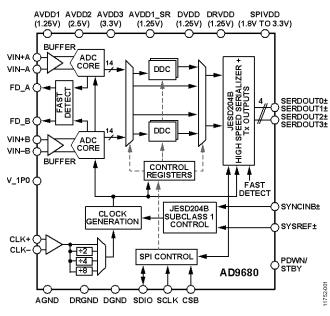

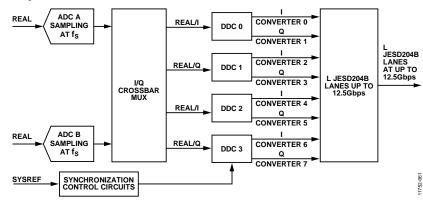

# 機能ブロック図

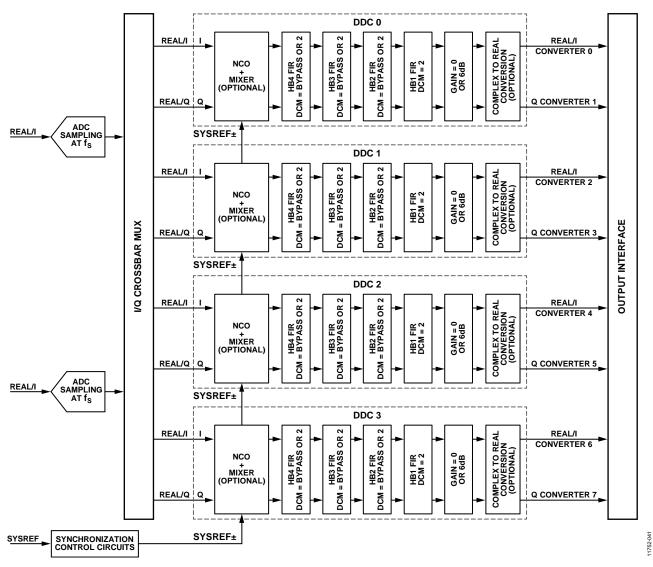

図 1.

# 製品のハイライト

- 広いフル・パワー帯域幅で最大2GHz信号のIFサンプリングをサポート

- フィルタのデザインと構成を容易にするプログラマブルな 入力終端を持つバッファ付き入力

- 3. 4 個の内蔵広帯域デシメーション・フィルタと数値制御発振器 (NCO) ブロックにより、マルチバンド・レシーバをサポート

- 4. 柔軟なシリアル・ポート・インターフェース (SPI)により、 特定のシステム条件に合わせて種々の製品機能を制御

- 5. プログラマブルな高速範囲外検出

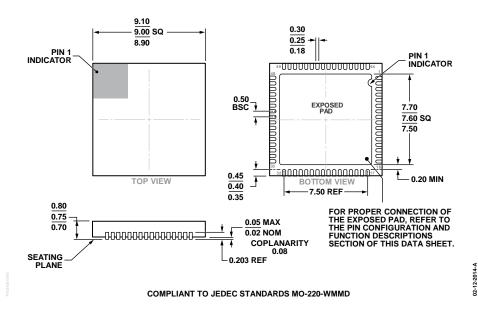

- 6. 9 mm×9 mm の 64 ピン LFCSP を採用

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標志なび登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2014 Analog Devices, Inc. All rights reserved.

# 目次

| 特長                           | 1        |

|------------------------------|----------|

| アプリケーション                     | 1        |

| 機能ブロック図                      | 1        |

| 製品のハイライト                     | 1        |

| 改訂履歴                         | 2        |

| 概要                           | 3        |

| 仕様                           | 4        |

| DC 仕様                        | 4        |

| AC 仕様                        | 5        |

| デジタル仕様                       | <i>6</i> |

| スイッチング仕様                     | 7        |

| タイミング仕様                      | 8        |

| 絶対最大定格                       | 10       |

| 熱特性                          | 10       |

| ESD の注意                      | 10       |

| ピン配置およびピン機能説明                | 11       |

| 代表的な性能特性                     | 13       |

| 等価回路                         | 16       |

| 動作原理                         | 18       |

| ADC のアーキテクチャ                 | 18       |

| アナログ入力に対する考慮                 | 18       |

| リファレンス電圧                     | 20       |

| クロック入力の考慮事項                  | 21       |

| ADC 範囲外と高速検出                 | 23       |

| ADC 範囲外                      |          |

| 高速スレッショールド検出 (FD_A および FD_B) | 23       |

| デジタル・ダウン・コンバータ (DDC)         | 24       |

| DDC I/Q 入力選択                 | 24       |

| DDC I/Q 出力の選択                | 24       |

| DDC の概要                      | 24       |

| 周波数変換                        | 30       |

| 概要                           | 30       |

| DDC NCO およびミキサーの損失と SFDR                  | 31   |

|-------------------------------------------|------|

| 数値制御オシレータ                                 | 31   |

| FIR フィルタ                                  | 33   |

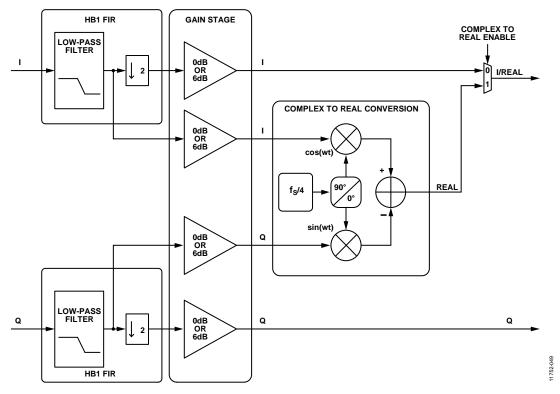

| 概要                                        | 33   |

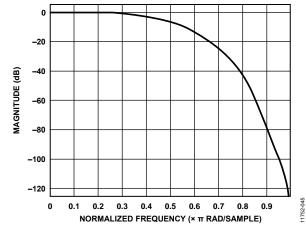

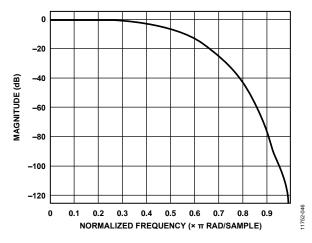

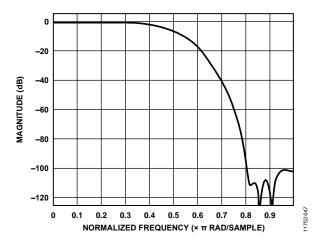

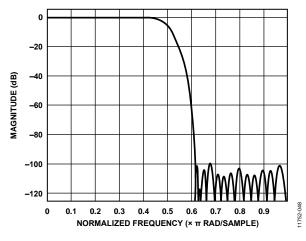

| ハーフバンド・フィルタ                               | 34   |

| DDC ゲイン・ステージ                              | 36   |

| DDC 複素数/実数変換                              | 36   |

| DDC の設定例                                  | 37   |

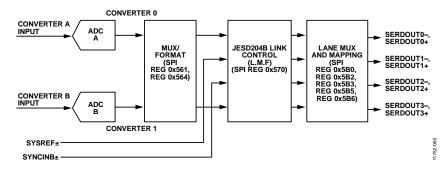

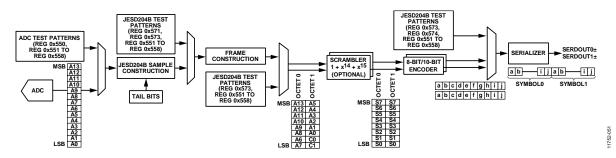

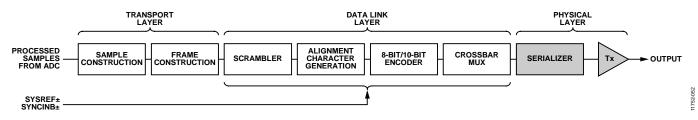

| デジタル出力                                    | 40   |

| JESD204B インターフェースの概要                      | 40   |

| JESD204B の概要                              | 40   |

| 機能概要                                      | 41   |

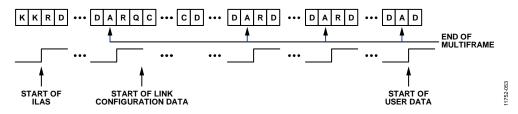

| JESD204B リンクの確立                           | 41   |

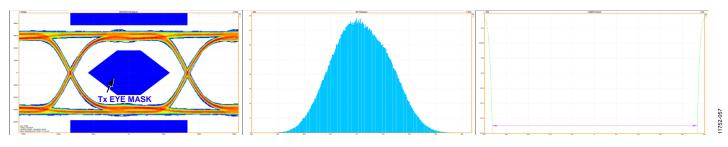

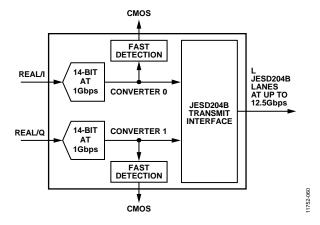

| 物理レイヤー(ドライバ)出力                            | 44   |

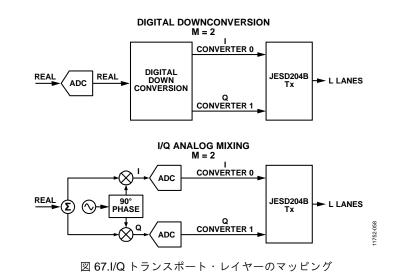

| JESD204B TX コンバータのマッピング                   | 45   |

| JESD204B リンクの設定                           | 47   |

| シリアル・ポート・インターフェース                         | 50   |

| SPI を使う設定                                 | 50   |

| ハードウェア・インターフェース                           | 50   |

| SPI からアクセス可能な機能                           | 50   |

| メモリ・マップ                                   | 51   |

| メモリ・マップ・レジスタ・テーブルの読出し                     | 51   |

| メモリ・マップ・レジスタ・テーブル                         | 52   |

| アプリケーション情報                                | 63   |

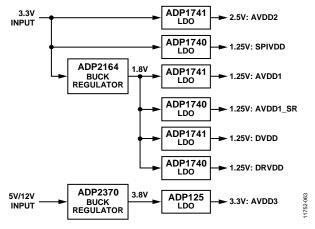

| 電源の推奨事項                                   | 63   |

| エクスポーズド・パッド・サーマル・ヒート・スラ                   | グの推奨 |

| 事項                                        | 63   |

| AVDD1_SR (ピン 57) と AGND (ピン 56 およびピン 60). | 63   |

| 外形寸法                                      | 64   |

| オーダー・ガイド                                  | 64   |

# 改訂履歴

5/14—Revision 0: Initial Version

# 概要

AD9680 は 14 ビット 1 GSPS のデュアル A/D コンバータ (ADC) です。バッファとサンプル・アンド・ホールド回路を内蔵し、低消費電力、小型、使い易いデザインになっています。このデバイスは、最大 2 GHz の広帯域アナログ信号をサンプリングするようにデザインされています。AD9680 は、広い入力帯域幅、高サンプリング・レート、優れた直線性、小型パッケージで低消費電力となるよう最適化されています。

2個の ADC コアはマルチステージの差動パイプライン・アーキテクチャを採用し、出力誤差補正ロジックを内蔵しています。各 ADCは、ユーザー選択可能な多様な入力範囲をサポートする広帯域入力を持っています。リファレンス電圧を内蔵しているためデザインが容易です。

アナログ入力とクロック信号は差動入力です。各 ADC データ 出力は、内部で 2 個のデジタル・ダウン・コンバータ (DDC)に 接続されています。各 DDC は、12 ビット周波数変換器 (NCO) と 4 個のハーフバンド・デシメーション・フィルタからなる 4 段カスケード接続信号処理ステージから構成されています。

AD9680 は、DDC ブロックの他に、通信器レシーバで自動ゲイン制御 (AGC) 機能を簡素化する複数の機能を内蔵しています。

プログラマブルなスレッショールドを持つ検出器を使うと、ADC の高速検出出力ビットを使って着信信号電力をモニタすることができます。入力信号レベルがプログラマブルなスレッショールドを超えると、高速検出インジケータがハイ・レベルになります。このスレッショールド・インジケータのレイテンシは小さいため、迅速にシステム・ゲインを下げて ADC 入力での範囲外状態を回避することができます。

DDC の構成と受信ロジック・デバイスの許容レーン・レートに応じて、サブクラス 1 JESD204B に基づく高速シリアル出力を 1 レーン、2 レーン、または 4 レーンの多様なレーン構成にすることができます。複数デバイス間の同期は、SYSREF±入力ピンと SYNCINB± 入力ピンを使ってサポートします。

AD9680 は、必要に応じて大幅な省電力を可能にする柔軟なパワーダウン・オプションを持っています。これらの機能はすべて、 $1.8 \, V \sim 3.3 \, V$  対応の 3 線式 SPI を使って設定することができます。

AD9680 は鉛フリーの 64 ピン LFCSP パッケージを採用し、仕様は  $-40^{\circ}$ C~+85 $^{\circ}$ C の工業用温度範囲で規定されています。この デバイスは、米国特許により保護されています。

Rev. **0** - 3/64 -

# 仕様

# DC 仕様

特に指定がない限り、AVDD1 = 1.25 V、AVDD2 = 2.5 V、AVDD3 = 3.3 V、AVDD1\_SR = 1.25 V、DVDD = 1.25 V、DRVDD = 1.25 V、SPIVDD = 1.8 V、規定最大サンプリング・レート (1000 MSPS)、1.7 V p-p フルスケール差動入力、1.0 V 内蔵リファレンス電圧、 $A_{IN}$  = -1.0 dBFS、デフォルト SPI 設定、 $T_A$  = 25 °C。

表 1.

| Parameter                                                          | Temperature | Min   | Тур        | Max   | Unit    |

|--------------------------------------------------------------------|-------------|-------|------------|-------|---------|

| RESOLUTION                                                         | Full        | 14    |            |       | Bits    |

| ACCURACY                                                           |             |       |            |       |         |

| No Missing Codes                                                   | Full        |       | Guaranteed | I     |         |

| Offset Error                                                       | Full        | -0.31 | 0          | +0.31 | % FSR   |

| Offset Matching                                                    | Full        |       | 0          | +0.23 | % FSR   |

| Gain Error                                                         | Full        | -5    | 0          | +5    | % FSR   |

| Gain Matching                                                      | Full        |       | 1          | +4.5  | % FSR   |

| Differential Nonlinearity (DNL)                                    | Full        | -0.7  | ±0.5       | +0.8  | LSB     |

| Integral Non-Linearity (INL)                                       | Full        | -5.7  | ±2.5       | +6.9  | LSB     |

| TEMPERATURE DRIFT                                                  |             |       |            |       |         |

| Offset Error                                                       | 25°C        |       | -14        |       | ppm/°C  |

| Gain Error                                                         | 25°C        |       | ±13.8      |       | ppm/°C  |

| INTERNAL VOLTAGE REFERENCE                                         |             |       |            |       | 1.1     |

| Voltage                                                            | Full        |       | 1.0        |       | V       |

| INPUT-REFERRED NOISE                                               |             |       |            |       |         |

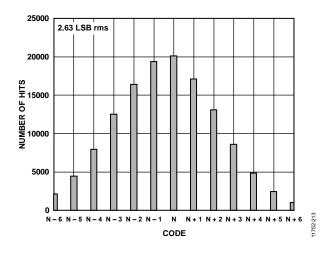

| $V_{REF} = 1.0 \text{ V}$                                          | 25°C        |       | 2.63       |       | LSB rms |

| ANALOG INPUTS                                                      |             |       |            |       |         |

| Differential Input Voltage Range (Programmable)                    | Full        | 1.46  | 1.70       | 1.94  | V p-p   |

| Common-Mode Voltage (V <sub>CM</sub> )                             | 25°C        |       | 2.05       |       | V       |

| Differential Input Capacitance <sup>1</sup>                        | 25°C        |       | 1.5        |       | pF      |

| Analog Input Full Power Bandwidth                                  | 25°C        |       | 2          |       | GHz     |

| POWER SUPPLY                                                       |             |       |            |       |         |

| AVDD1                                                              | Full        | 1.22  | 1.25       | 1.28  | V       |

| AVDD2                                                              | Full        | 2.44  | 2.50       | 2.56  | V       |

| AVDD3                                                              | Full        | 3.2   | 3.3        | 3.4   | V       |

| AVDD1_SR                                                           | Full        | 1.22  | 1.25       | 1.28  | V       |

| DVDD                                                               | Full        | 1.22  | 1.25       | 1.28  | V       |

| DRVDD                                                              | Full        | 1.22  | 1.25       | 1.28  | V       |

| SPIVDD                                                             | Full        | 1.7   | 1.8        | 3.4   | V       |

| $ m I_{AVDD1}$                                                     | Full        |       | 685        | 720   | mA      |

| $I_{\mathrm{AVDD2}}$                                               | Full        |       | 595        | 680   | mA      |

| $I_{\mathrm{AVDD3}}$                                               | Full        |       | 125        | 142   | mA      |

| $I_{\mathrm{AVDD1\_SR}}$                                           | Full        |       | 16         | 18    | mA      |

| $I_{ m DVDD}^{2}$                                                  | Full        |       | 208        | 236   | mA      |

| $I_{DRVDD}^{}^{}$                                                  | Full        |       | 200        | 225   | mA      |

| $I_{ m SPIVDD}$                                                    | Full        |       | 5          | 6     | mA      |

| POWER CONSUMPTION                                                  |             |       |            |       |         |

| Total Power Dissipation (Including Output Drivers) <sup>2, 3</sup> | Full        |       | 3.3        |       | W       |

| Power-Down Dissipation                                             | Full        |       | 835        |       | mW      |

| Standby <sup>4</sup>                                               | Full        |       | 1.4        |       | w       |

¹すべてのレーンが動作。 DRVDD の消費費力は、レーン・レートと使用するレーン数により変わります。

Rev. **0** — 4/64 —

$<sup>^2</sup>$  デフォルト・モード。 DDC 不使用。 L=4、M=2、F=1。

$<sup>^3</sup>$ デフォルト・モード。 DDC 不使用。

<sup>&</sup>lt;sup>4</sup> SPI 経由で制御可能。

# AC 仕様

特に指定がない限り、AVDD1 = 1.25 V、AVDD2 = 2.5 V、AVDD3 = 3.3 V、AVDD1\_SR = 1.25 V、DVDD = 1.25 V、DRVDD = 1.25 V、SPIVDD = 1.8 V、規定最大サンプリング・レート、1.7 V p-p フルスケール差動入力、1.0 V 内蔵リファレンス電圧、 $A_{\rm IN}$  = -1.0 dBFS、デフォルト SPI 設定、 $T_{\rm A}$  = 25°C。

表 2.

| Parameter <sup>1</sup>                                             | Temperature | Min  | Тур        | Max | Unit    |

|--------------------------------------------------------------------|-------------|------|------------|-----|---------|

| ANALOG INPUT FULL SCALE                                            | Full        |      | 1.7        |     | V p-p   |

| NOISE DENSITY <sup>2</sup>                                         | Full        |      | -154       |     | dBFS/Hz |

| SIGNAL-TO-NOISE RATIO (SNR) <sup>3</sup>                           |             |      |            |     |         |

| $f_{IN} = 10 \text{ MHz}$                                          | 25°C        |      | 67.2       |     | dBFS    |

| $f_{IN} = 170 \text{ MHz}$                                         | Full        | 65.1 | 66.6       |     | dBFS    |

| $f_{IN} = 340 \text{ MHz}$                                         | 25°C        |      | 65.3       |     | dBFS    |

| $f_{IN} = 450 \text{ MHz}$                                         | 25°C        |      | 64.0       |     | dBFS    |

| $f_{IN} = 765 \text{ MHz}$                                         | 25°C        |      | 62.4       |     | dBFS    |

| $f_{IN} = 985 \text{ MHz}$                                         | 25°C        |      | 61.4       |     | dBFS    |

| $f_{IN} = 1950 \text{ MHz}$                                        | 25°C        |      | 57.0       |     | dBFS    |

| SNR AND DISTORTION RATIO (SINAD) <sup>3</sup>                      |             |      |            |     |         |

| $f_{IN} = 10 \text{ MHz}$                                          | 25°C        |      | 67.1       |     | dBFS    |

| $f_{IN} = 170 \text{ MHz}$                                         | Full        | 65.0 | 66.4       |     | dBFS    |

| $f_{IN} = 340 \text{ MHz}$                                         | 25°C        |      | 65.2       |     | dBFS    |

| $f_{\rm IN} = 450~{\rm MHz}$                                       | 25°C        |      | 63.8       |     | dBFS    |

| $f_{\rm IN} = 765  \rm MHz$                                        | 25°C        | 1    | 62.1       |     | dBFS    |

| $f_{IN} = 985 \text{ MHz}$                                         | 25°C        | 1    | 61.1       |     | dBFS    |

| $f_{\rm IN} = 1950  \rm MHz$                                       | 25°C        | 1    | 56.0       |     | dBFS    |

| EFFECTIVE NUMBER OF BITS (ENOB)                                    |             | 1    |            |     |         |

| $f_{IN} = 10 \text{ MHz}$                                          | 25°C        | 1    | 10.8       |     | Bits    |

| $f_{\rm IN} = 170  \rm MHz$                                        | Full        | 10.5 | 10.7       |     | Bits    |

| $f_{\rm IN} = 340  \rm MHz$                                        | 25°C        |      | 10.5       |     | Bits    |

| $f_{\rm IN} = 450  \rm MHz$                                        | 25°C        |      | 10.3       |     | Bits    |

| $f_{\rm IN} = 765  \rm MHz$                                        | 25°C        |      | 10.0       |     | Bits    |

| $f_{IN} = 985 \text{ MHz}$                                         | 25°C        |      | 9.8        |     | Bits    |

| $f_{\rm IN} = 1950  \mathrm{MHz}$                                  | 25°C        |      | 9.0        |     | Bits    |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR) <sup>3</sup>                    |             |      |            |     |         |

| $f_{IN} = 10 \text{ MHz}$                                          | 25°C        |      | 88         |     | dBFS    |

| $f_{\rm IN} = 170  \rm MHz$                                        | Full        | 75   | 85         |     | dBFS    |

| $f_{\rm IN} = 340  \rm MHz$                                        | 25°C        | '    | 85         |     | dBFS    |

| $f_{\rm IN} = 450  \rm MHz$                                        | 25°C        |      | 82         |     | dBFS    |

| $f_{\rm IN} = 765  \rm MHz$                                        | 25°C        |      | 80         |     | dBFS    |

| $f_{\rm IN} = 985  \rm MHz$                                        | 25°C        |      | 80         |     | dBFS    |

| $f_{IN} = 1950 \text{ MHz}$                                        | 25°C        |      | 68         |     | dBFS    |

| WORST HARMONIC, SECOND OR THIRD <sup>3</sup>                       |             |      |            |     |         |

| $f_{\rm IN} = 10~{\rm MHz}$                                        | 25°C        |      | -95        |     | dBFS    |

| $f_{\rm IN} = 170  \rm MHz$                                        | Full        |      | -94        | -75 | dBFS    |

| $f_{\rm IN} = 340  \rm MHz$                                        | 25°C        | 1    | -88        |     | dBFS    |

| $f_{\rm IN} = 450  \rm MHz$                                        | 25°C        | 1    | -86        |     | dBFS    |

| $f_{\rm IN} = 765  \rm MHz$                                        | 25°C        | 1    | -80        |     | dBFS    |

| $f_{IN} = 985 \text{ MHz}$                                         | 25°C        | 1    | -80        |     | dBFS    |

| $f_{\rm IN} = 1950  \rm MHz$                                       | 25°C        | 1    | -80        |     | dBFS    |

| WORST OTHER, EXCLUDING SECOND OR THIRD HARMONIC <sup>3</sup>       | 1           | 1    | 30         |     |         |

| $f_{IN} = 10 \text{ MHz}$                                          | 25°C        | 1    | -95        |     | dBFS    |

| $f_{\rm IN} = 170  \rm MHz$                                        | Full        | 1    | -94        | -81 | dBFS    |

| $f_{\rm IN} = 340  \rm MHz$                                        | 25°C        | 1    | -88        | 51  | dBFS    |

| $f_{\rm IN} = 450  \rm MHz$                                        | 25°C        | 1    | -86        |     | dBFS    |

| $f_{\rm IN} = 765  \rm MHz$                                        | 25°C        | 1    | -81        |     | dBFS    |

| $f_{\rm IN} = 985  \text{MHz}$                                     | 25°C        | 1    | -82        |     | dBFS    |

| $f_{IN} = 950 \text{ MHz}$                                         | 25°C        |      | -82<br>-75 |     | dBFS    |

| TWO-TONE INTERMODULATION DISTORTION (IMD), AIN1 AND AIN2 = -7 dBFS |             |      |            |     |         |

| $f_{IN1} = 185 \text{ MHz}, f_{IN2} = 188 \text{ MHz}$             | 25°C        | 1    | -87        |     | dBFS    |

| $f_{IN1} = 338 \text{ MHz}, f_{IN2} = 341 \text{ MHz}$             | 25°C        |      | -88        |     | dBFS    |

Rev. **0** — 5/64 —

| Parameter <sup>1</sup>            | Temperature | Min | Тур | Max | Unit |

|-----------------------------------|-------------|-----|-----|-----|------|

| CROSSTALK <sup>4</sup>            | 25°C        |     | 95  |     | dB   |

| FULL POWER BANDWIDTH <sup>5</sup> | 25°C        |     | 2   |     | GHz  |

<sup>&</sup>lt;sup>1</sup> 完全な定義とこれらのテストの実施方法についてはアプリケーション・ノート AN-835「Understanding High Speed ADC Testing and Evaluation」を参照してください。

# デジタル仕様

特に指定がない限り、AVDD1 = 1.25 V、AVDD2 = 2.5 V、AVDD3 = 3.3 V、AVDD1\_SR = 1.25 V、DVDD = 1.25 V、DRVDD = 1.25 V、SPIVDD = 1.8 V、規定最大サンプリング・レート、1.7 V p-p フルスケール差動入力、1.0 V 内蔵リファレンス電圧、 $A_{\rm IN}$  = -1.0 dBFS、デフォルト SPI 設定、 $T_{\rm A}$  = 25°C。

# 表 3.

| Parameter                                  | Temperature | Min | Тур                        | Max  | Unit   |

|--------------------------------------------|-------------|-----|----------------------------|------|--------|

| CLOCK INPUTS (CLK+, CLK-)                  |             |     |                            |      |        |

| Logic Compliance                           | Full        |     | LVDS/LVPEC                 | L    |        |

| Differential Input Voltage                 | Full        | 600 | 1200                       | 1800 | mV p-p |

| Input Common-Mode Voltage                  | Full        |     | 0.85                       |      | v      |

| Input Resistance (Differential)            | Full        |     | 35                         |      | kΩ     |

| Input Capacitance                          | Full        |     |                            | 2.5  | pF     |

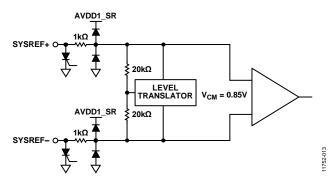

| SYSREF INPUTS (SYSREF+, SYSREF-)           |             |     |                            |      |        |

| Logic Compliance                           | Full        |     | LVDS/LVPEC                 | L    |        |

| Differential Input Voltage                 | Full        | 400 | 1200                       | 1800 | mV p-p |

| Input Common-Mode Voltage                  | Full        | 0.6 | 0.85                       | 2.0  | v      |

| Input Resistance (Differential)            | Full        |     | 35                         |      | kΩ     |

| Input Capacitance (Differential)           | Full        |     |                            | 2.5  | pF     |

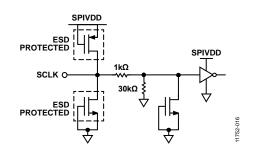

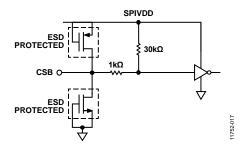

| LOGIC INPUTS (SDI, SCLK, CSB, PDWN/STBY)   |             |     |                            |      |        |

| Logic Compliance                           | Full        |     | CMOS                       |      |        |

| Logic 1 Voltage                            | Full        |     | $0.8 \times \text{SPIVDD}$ |      | v      |

| Logic 0 Voltage                            | Full        | 0   | $0.2 \times \text{SPIVDD}$ |      | V      |

| Input Resistance                           | Full        |     | 30                         |      | kΩ     |

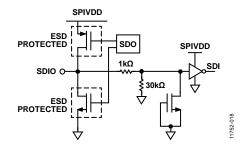

| LOGIC OUTPUT (SDIO)                        |             |     |                            |      |        |

| Logic Compliance                           | Full        |     | CMOS                       |      |        |

| Logic 1 Voltage (I <sub>OH</sub> = 800 μA) | Full        |     | $0.8 \times \text{SPIVDD}$ |      | V      |

| Logic 0 Voltage ( $I_{OL} = 50 \mu A$ )    | Full        |     | $0.2 \times \text{SPIVDD}$ |      | V      |

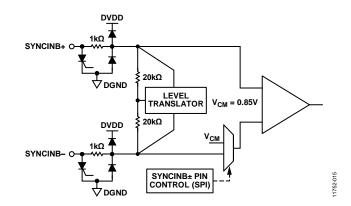

| SYNCIN INPUT (SYNCINB+/SYNCINB-)           |             |     |                            |      |        |

| Logic Compliance                           | Full        |     | LVDS/LVPECL/C              | MOS  |        |

| Differential Input Voltage                 | Full        | 400 | 1200                       | 1800 | mV p-p |

| Input Common-Mode Voltage                  | Full        | 0.6 | 0.85                       | 2.0  | V      |

| Input Resistance (Differential)            | Full        |     | 35                         |      | kΩ     |

| Input Capacitance                          | Full        |     |                            | 2.5  | pF     |

| LOGIC OUTPUTS (FD_A, FD_B)                 |             |     |                            |      |        |

| Logic Compliance                           | Full        |     | CMOS                       |      |        |

| Logic 1 Voltage                            | Full        | 0.8 | SPIVDD                     |      | V      |

| Logic 0 Voltage                            | Full        | 0   | 0                          |      | v      |

| Input Resistance                           | Full        |     | 30                         |      | kΩ     |

Rev. **0** — 6/64 —

<sup>&</sup>lt;sup>2</sup>ノイズ密度は、低いアナログ入力周波数(30 MHz)で測定した値です。

<sup>3</sup>フルスケール電圧とバッファ電流の推奨設定値については表9を参照してください。

<sup>4</sup> クロストークは、片方のアナログ・チャンネルに-1.0 dBFS を入力し、隣接チャンネルは入力なしで、170 MHz で測定。

<sup>5</sup>図36の回路で測定。

| Parameter                                                   | Temperature | Min  | Тур | Max  | Unit   |

|-------------------------------------------------------------|-------------|------|-----|------|--------|

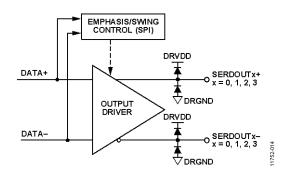

| DIGITAL OUTPUTS (SERDOUTx±, x = 0 TO 3)                     |             |      |     |      |        |

| Logic Compliance                                            | Full        |      | CML |      |        |

| Differential Output Voltage                                 | Full        | 360  |     | 770  | mV p-p |

| Output Common-Mode Voltage (V <sub>CM</sub> )               |             |      |     |      |        |

| AC Coupled                                                  | 25°C        | 0    |     | 1.8  | V      |

| Short-Circuit Current (I <sub>Dshort</sub> )                | 25°C        | -100 |     | +100 | mA     |

| Differential Return Loss (RL <sub>DIFF</sub> ) <sup>1</sup> | 25°C        | 8    |     |      | dB     |

| Common-Mode Return Loss (RL <sub>CM</sub> ) <sup>1</sup>    | 25°C        | 6    |     |      | dB     |

| Differential Termination Impedance                          | Full        | 80   | 100 | 120  | Ω      |

<sup>&</sup>lt;sup>1</sup> 差動および同相モード・リターン損失は、100 MHz~0.75 MHz×ボー・レートで測定。

# スイッチング仕様

特に指定がない限り、AVDD1 = 1.25 V、AVDD2 = 2.5 V、AVDD3 = 3.3 V、AVDD1\_SR = 1.25 V、DVDD = 1.25 V、DRVDD = 1.25 V、SPIVDD = 1.8 V、規定最大サンプリング・レート、1.7 V p-p フルスケール差動入力、1.0 V 内蔵リファレンス電圧、 $A_{IN}$  = -1.0 dBFS、デフォルト SPI 設定、 $T_A$  = 25°C。

表 4.

| Parameter                                               | Temperature | Min   | Тур | Max  | Unit         |

|---------------------------------------------------------|-------------|-------|-----|------|--------------|

| CLOCK                                                   |             |       |     |      |              |

| Clock Rate (at CLK+/CLK- Pins)                          | Full        | 0.3   |     | 4    | GHz          |

| Maximum Sample Rate <sup>1</sup>                        | Full        | 1000  |     |      | MSPS         |

| Minimum Sample Rate <sup>2</sup>                        | Full        | 300   |     |      | MSPS         |

| Clock Pulse Width High                                  | Full        | 500   |     |      | ps           |

| Clock Pulse Width Low                                   | Full        | 500   |     |      | ps           |

| OUTPUT PARAMETERS                                       |             |       |     |      |              |

| Unit Interval (UI) <sup>3</sup>                         | Full        | 80    | 100 |      | ps           |

| Rise Time ( $t_R$ ) (20% to 80% into 100 $\Omega$ Load) | 25°C        | 24    | 32  |      | ps           |

| Fall Time ( $t_F$ ) (20% to 80% into 100 $\Omega$ Load) | 25°C        | 24    | 32  |      | ps           |

| PLL Lock Time                                           | 25°C        |       | 2   |      | ms           |

| Data Rate per Channel (NRZ) <sup>4</sup>                | 25°C        | 3.125 | 10  | 12.5 | Gbps         |

| LATENCY <sup>5</sup>                                    |             |       |     |      |              |

| Pipeline Latency                                        | Full        |       | 55  |      | Clock cycles |

| Fast Detect Latency                                     | Full        |       |     | 28   | Clock cycles |

| Wake-Up Time <sup>6</sup>                               |             |       |     |      |              |

| Standby                                                 | 25°C        |       | 1   |      | Ms           |

| Power-Down                                              | 25°C        |       |     | 4    | Ms           |

| APERTURE                                                |             |       |     |      |              |

| Aperture Delay (t <sub>A</sub> )                        | Full        |       | 530 |      | Ps           |

| Aperture Uncertainty (Jitter, t <sub>j</sub> )          | Full        |       | 55  |      | fs rms       |

| Out-of-range Recovery Time                              | Full        |       | 1   |      | Clock Cycles |

<sup>「</sup>最大サンプル・レートは分周後のクロック・レートです。

Rev. **0** - 7/64 -

$<sup>^2</sup>$  最小サンプル・レートは、L=2 または L=1 の 300 MSPS で動作。

<sup>&</sup>lt;sup>3</sup>ボー・レート = 1/UI。 このレンジの一部分をサポートすることができます。

$<sup>^4</sup>$  デフォルト L = 4。この値はサンプル・レートとデシメーション比に基いて変更することができます。

<sup>&</sup>lt;sup>5</sup> DDC 不使用。 L = 4、M = 2、F = 1。

<sup>6</sup> ウェイクアップ時間は、パワーダウン・モードから通常動作へ戻るために要する時間として定義されます。

# タイミング仕様

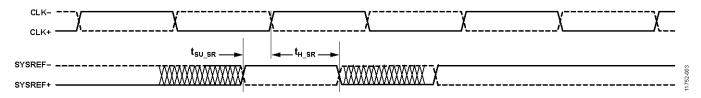

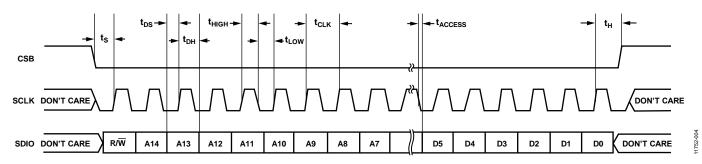

表 5.

| Parameter                              | Test Conditions/Comments                                                                                                      | Min | Тур | Max | Unit |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| CLK+ to SYSREF+ TIMING<br>REQUIREMENTS | See Figure 3                                                                                                                  |     |     |     |      |

| $t_{ m SU\_SR}$                        | Device clock to SYSREF+ setup time                                                                                            |     | 117 |     | ps   |

| $t_{H\_SR}$                            | Device clock to SYSREF+ hold time                                                                                             |     | -96 |     | ps   |

| SPI TIMING REQUIREMENTS                | See Figure 4                                                                                                                  |     |     |     |      |

| $t_{ m DS}$                            | Setup time between the data and the rising edge of SCLK                                                                       | 2   |     |     | ns   |

| $t_{ m DH}$                            | Hold time between the data and the rising edge of SCLK                                                                        | 2   |     |     | ns   |

| $t_{CLK}$                              | Period of the SCLK                                                                                                            | 40  |     |     | ns   |

| $t_{\mathrm{S}}$                       | Setup time between CSB and SCLK                                                                                               | 2   |     |     | ns   |

| $t_{\mathrm{H}}$                       | Hold time between CSB and SCLK                                                                                                | 2   |     |     | ns   |

| $t_{ m HIGH}$                          | Minimum period that SCLK must be in a logic high state                                                                        | 10  |     |     | ns   |

| $t_{LOW}$                              | Minimum period that SCLK must be in a logic low state                                                                         | 10  |     |     | ns   |

| $t_{\rm EN\_SDIO}$                     | Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge (not shown in Figure 4) |     |     |     | ns   |

| $t_{ m DIS\_SDIO}$                     | Time required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge (not shown in Figure 4)  | 10  |     |     | ns   |

# タイミング図

図 2.データ出力タイミング (フル帯域幅モード; L = 4; M = 2; F = 1)

Rev. **0** - 8/64 -

図 3.SYSREF±のセットアップとホールド・タイミング

図 4.シリアル・ポート・インターフェースのタイミング図

# 絶対最大定格

表 6.

| Parameter                           | Rating                   |

|-------------------------------------|--------------------------|

| Electrical                          |                          |

| AVDD1 to AGND                       | 1.34 V                   |

| AVDD1_SR to AGND                    | 1.34 V                   |

| AVDD2 to AGND                       | 2.75 V                   |

| AVDD3 to AGND                       | 3.63 V                   |

| DVDD to DGND                        | 1.34 V                   |

| DRVDD to DRGND                      | 1.34 V                   |

| SPIVDD to AGND                      | 3.63 V                   |

| AGND to DRGND                       | -0.3 V to +0.3 V         |

| VIN±x to AGND                       | 3.2 V                    |

| SCLK, SDIO, CSB to AGND             | -0.3 V to SPIVDD + 0.3 V |

| PDWN/STBY to AGND                   | -0.3 V to SPIVDD + 0.3 V |

| Environmental                       |                          |

| Operating Temperature Range         | −40°C to +85°C           |

| Maximum Junction Temperature        | 125°C                    |

| Storage Temperature Range (Ambient) | -65°C to +150°C          |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上での製品動作を定めたものではありません。製品を長時間絶対最大定格状態に置くと製品の信頼性に影響を与えます。

# 熱特性

$\theta_{JA}$ 、 $\theta_{JB}$ 、 $\theta_{JC}$  の typ 値は、様々な空気流 (m/sec)でプリント回路 ボード (PCB) 層数に対して規定されます。空気流があると放熱 効果が良くなるため、実質的に  $\theta_{JA}$  と  $\theta_{JB}$  が小さくなります。最 大ジャンクション温度が表 7 に示す規定値を超えないようにする ため、適切な熱管理技術の使用が推奨されます。

表 7.

| PCB<br>Type   | Airflow<br>Velocity<br>(m/sec) | $	heta_{ m JA}$      | $\Psi_{\mathrm{JB}}$ | $	heta_{	ext{JC\_TOP}}$ | $	heta_{	ext{JC\_BOT}}$ | Unit |

|---------------|--------------------------------|----------------------|----------------------|-------------------------|-------------------------|------|

| JEDEC         | 0.0                            | 17.81, 2             | 6.31,3               | 4.71,5                  | $1.2^{1,5}$             | °C/W |

| 2s2p          | 1.0                            | 15.61, 2             | $5.9^{1,3}$          | N/A <sup>4</sup>        |                         | °C/W |

| Board         | 2.5                            | 15.0 <sup>1, 2</sup> | 5.71,3               | N/A <sup>4</sup>        |                         | °C/W |

| 10-Layer      | 0.0                            | 13.8                 | 4.6                  | 4.7                     | 1.2                     | °C/W |

| PCB 81        | 1.0                            | 12.7                 | 4.6                  | N/A <sup>4</sup>        |                         | °C/W |

| Vias<br>Under | 2.5                            | 12.0                 | 4.6                  | N/A <sup>4</sup>        |                         | °C/W |

| Exposed       |                                |                      |                      |                         |                         |      |

| Pad           |                                |                      |                      |                         |                         |      |

<sup>&</sup>lt;sup>1</sup> JEDEC 51-7 と JEDEC 51-5 2s2p のテスト・ボードに準拠。

### ESD の注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. **0** — 10/64 —

<sup>&</sup>lt;sup>2</sup> JEDEC JESD51-2 (自然空冷)または JEDEC JESD51-6 (強制空冷)に準拠。

<sup>&</sup>lt;sup>3</sup>JEDEC JESD51-8 (自然空冷)に準拠。

<sup>&</sup>lt;sup>4</sup> N/A = 該当しません。

<sup>&</sup>lt;sup>5</sup> MIL-STD 883、Method 1012.1 に準拠。

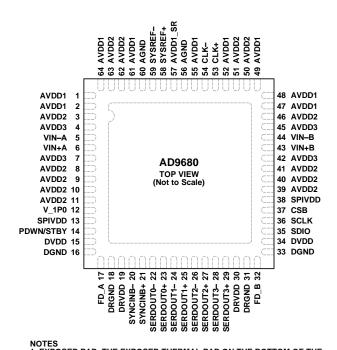

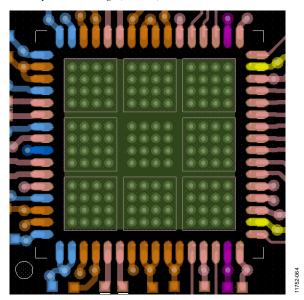

# ピン配置およびピン機能説明

NOTES

1. EXPOSED PAD. THE EXPOSED THERMAL PAD ON THE BOTTOM OF THE PACKAGE PROVIDES THE GROUND REFENCE FOR AVDDX. THIS EXPOSED PAD MUST BE CONNECTED TO GROUND FOR PROPER OPERATION.

図 5.ピン配置 (上面図)

表 8.ピン機能の説明

| ピン番号                                        | 記号                    | タイプ    | 説明                                                                                                                                                   |

|---------------------------------------------|-----------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 電源                                          |                       |        |                                                                                                                                                      |

| 0                                           | EPAD                  | グラウンド  | エクスポーズド・パッド。パッケージ底面のエクスポーズド・サーマル・パッドは、AVDDxのグラウンド基準になります。このエクスポーズド・パッドはグラウンドへ接続する必要があります。                                                            |

| 1, 2, 47, 48, 49, 52, 55, 61, 64            | AVDD1                 | 電源     | アナログ電源(公称 1.25 V)。                                                                                                                                   |

| 3、8、9、10、11、39、<br>40、41、46、50、51、<br>62、63 | AVDD2                 | 電源     | アナログ電源(公称 2.5 V)。                                                                                                                                    |

| 4、7、42、45                                   | AVDD3                 | 電源     | アナログ電源(公称 3.3 V)。                                                                                                                                    |

| 13、38                                       | SPIVDD                | 電源     | SPI 用のデジタル電源 (1.8 V~3.3 V)。                                                                                                                          |

| 15、34                                       | DVDD                  | 電源     | デジタル電源(公称 1.25 V)。                                                                                                                                   |

| 16、33                                       | DGND                  | グラウンド  | DVDDのグラウンド基準。                                                                                                                                        |

| 18, 31                                      | DRGND                 | グラウンド  | DRVDDのグラウンド基準。                                                                                                                                       |

| 19、30                                       | DRVDD                 | 電源     | デジタル・ドライバ電源 (1.25 V 公称)。                                                                                                                             |

| 56, 60                                      | AGND 1                | グラウンド  | SYSREF±のグラウンド基準。                                                                                                                                     |

| 57                                          | AVDD1_SR <sup>1</sup> | 電源     | SYSREF±のアナログ電源 (公称 1.25 V)。                                                                                                                          |

| アナログ                                        |                       |        |                                                                                                                                                      |

| 5, 6                                        | VIN-A、VIN+A           | 入力     | ADC A アナログ入力反転/非反転。                                                                                                                                  |

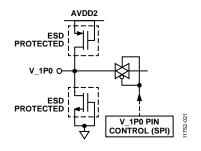

| 12                                          | V_1P0                 | 入力/DNC | 1.0 V リファレンス電圧入力、接続しないでください。このピンは、SPIを使って非接続または入力に設定することができます。<br>内蔵リファレンス電圧を使用する場合は、このピンを接続しないでください。外付けリファレンス電圧ソースを使う場合は、1.0<br>V のリファレンス電圧入力が必要です。 |

| 44、43                                       | VIN-B、VIN+B           | 入力     | ADC B アナログ入力反転/非反転。                                                                                                                                  |

| 53、54                                       | CLK+、CLK-             | 入力     | クロック入力非反転/反転。                                                                                                                                        |

Rev. **0** — 11/64 —

| ピン番号                   | 記号                      | タイプ   | 説明                                                                   |  |

|------------------------|-------------------------|-------|----------------------------------------------------------------------|--|

| CMOS 出力                |                         |       |                                                                      |  |

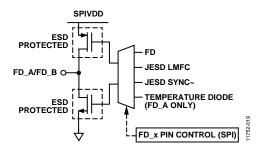

| 17、32                  | FD_A、FD_B               | 出力    | チャンネル A とチャンネル B の高速検出出力。                                            |  |

| デジタル入力                 |                         |       |                                                                      |  |

| 20、21                  | SYNCINB-\ SYNCINB+      | 入力    | アクティブ・ローの JESD204B LVDS 同期入力非反転/反転。                                  |  |

| 58、59                  | SYSREF+、SYSREF-         | 入力    | アクティブ・ローの JESD204B LVDS システム・リファレンス電<br>圧入力非反転/反転。                   |  |

| データ出力                  |                         |       |                                                                      |  |

| 22、23                  | SERDOUT0-\ SERDOUT0+    | 出力    | レーン 0 出力データ反転/非反転。                                                   |  |

| 24、25                  | SERDOUT1-\ SERDOUT1+    | 出力    | レーン1出力データ反転/非反転。                                                     |  |

| 26、27                  | SERDOUT2+<br>SERDOUT2+  | 出力    | レーン 2 出力データ反転/非反転。                                                   |  |

| 28、29                  | SERDOUT3-\<br>SERDOUT3+ | 出力    | レーン 3 出力データ反転/非反転。                                                   |  |

| 被テスト・デバイス (DUT)<br>の制御 |                         |       |                                                                      |  |

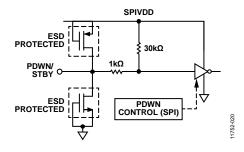

| 14                     | PDWN/STBY               | 入力    | パワーダウン入力 (アクティブ・ハイ)。このピンの動作は SPI モードに依存し、パワーダウンまたはスタンバイに設定することができます。 |  |

| 35                     | SDIO                    | 入力/出力 | SPI シリアル・データ入力/出力。                                                   |  |

| 36                     | SCLK                    | 入力    | SPIシリアル・クロック。                                                        |  |

| 37                     | CSB                     | 入力    | SPIチップ・セレクト(アクティブ・ロー)。                                               |  |

$<sup>^1</sup>$ 正しい ADC 動作を保証するために、AVDD1\_SR と AGND の接続は AVDD1 と EPAD の接続と別にしてください。 詳細については、アプリケーション情報のセクションを参照してください。

Rev. **0** — 12/64 —

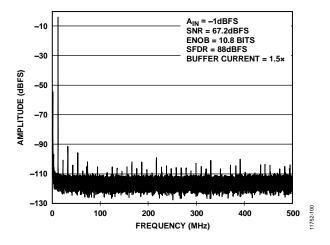

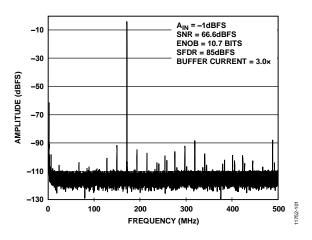

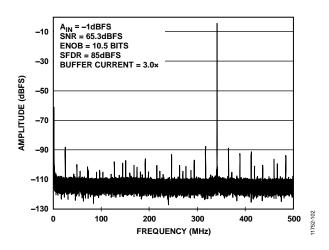

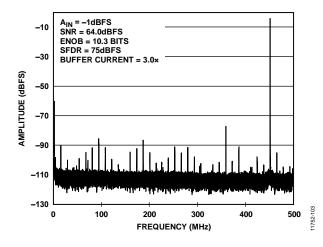

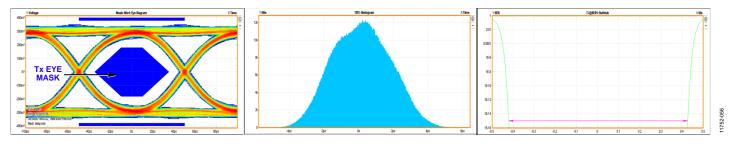

# 代表的な性能特性

特に指定がない限り、AVDD1 = 1.25 V、AVDD1\_SR = 1.25 V、AVDD2 = 2.5 V、AVDD3 = 3.3 V、DVDD = 1.25 V、DRVDD = 1.25 V、SPIVDD = 1.8 V、1.7 V p-p フルスケール差動入力、 $A_{IN}$  = -1.0 dBFS、デフォルト SPI 設定、クロック分周器 = 2、 $T_A$  = 25°C、128k FFT サンプル。

図 6.シングル・トーン FFT、 $f_{IN}$  = 10.3 MHz

図 7.シングル・トーン FFT、f<sub>IN</sub> = 170.3 MHz

図 8.シングル・トーン FFT、 $f_{IN}$  = 340.3 MHz

図 9.シングル・トーン FFT、f<sub>IN</sub> = 450.3 MHz

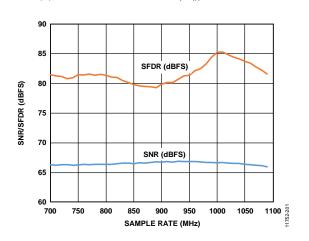

図  $10.f_S$ 対 SNR/SFDR  $f_{\text{IN}}$  = 170.3 MHz ; バッファ設定 = 3.0×

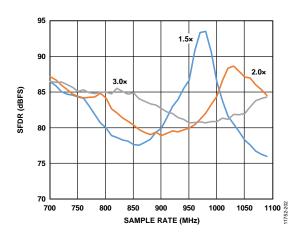

図 11. $f_S$ 対 SFDR  $f_{\text{IN}} = 10.3 \text{ MHz}、バッファ設定 = 1.5x、2.0xまたは 3.0x}$

Rev. **0** — 13/64 —

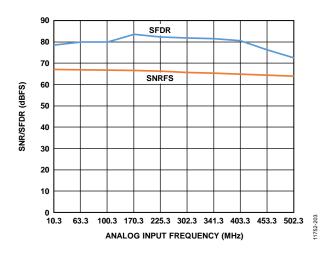

図 12. $f_{IN}$ 対 SNR/SFDR  $f_{IN} < 500 \; \text{MHz}$  ; バッファ設定 =  $3.0 \times$

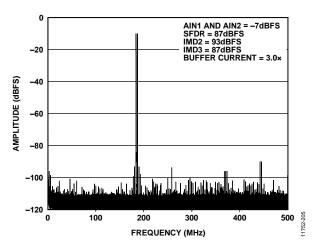

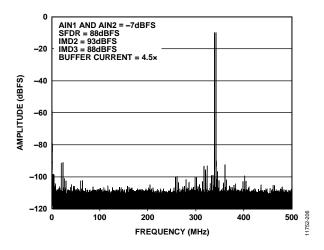

図 13.2 トーン FFT  $f_{IN1} = 184 \text{ MHz}, f_{IN2} = 187 \text{ MHz}$

図 14.2 トーン FFT  $f_{IN1} = 338 \text{ MHz}, f_{IN2} = 341 \text{ MHz}$

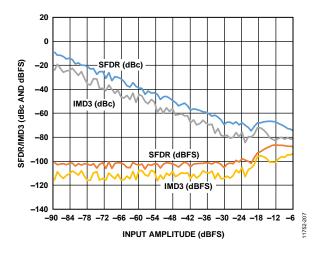

図 15.入力振幅  $(A_{IN})$ 対 2 トーン SFDR/IMD3  $f_{IN1}$  = 184 MHz、 $f_{IN2}$  = 187 MHz

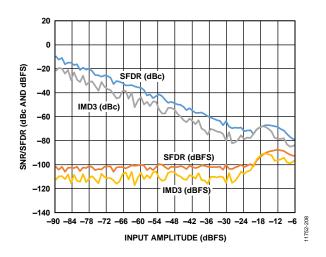

図 16.入力振幅 ( $A_{IN}$ )対 2 トーン IMD3/SFDR  $f_{IN1}$  = 338 MHz、 $f_{IN2}$  = 341 MHz

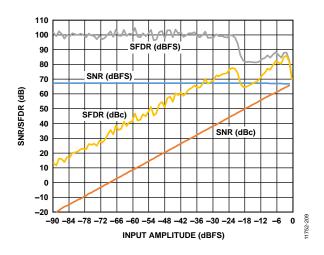

図 17.アナログ入力レベル対 SNR/SFDR  $f_{\text{IN}}$  = 170.3 MHz

Rev. **0** — 14/64 —

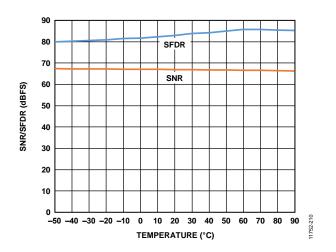

図 18.SNR/SFDR の温度特性  $f_{\text{IN}}$  = 170.3 MHz

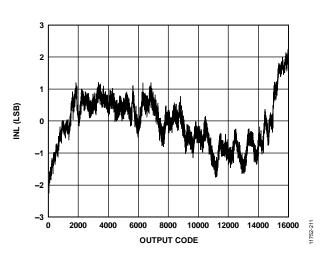

$\boxtimes$  19.INL、 $f_{IN} = 10.3 \text{ MHz}$

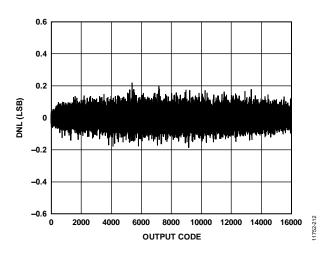

$\boxtimes$  20.DNL、  $f_{IN} = 15$  MHz.

図 21.入力換算ノイズ・ヒストグラム

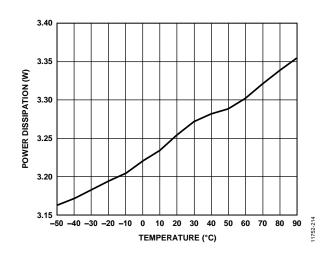

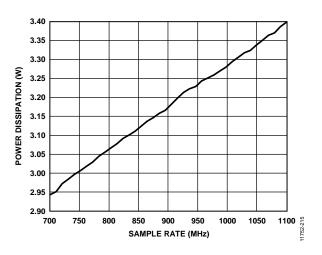

図 22.消費電力の温度特性

図 23.fs対消費電力

Rev. **0** — 15/64 —

# 等価回路

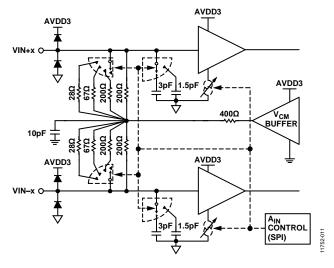

図 24.アナログ入力

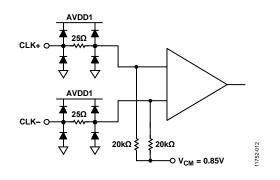

図 25.クロック入力

図 26.SYSREF± 入力

図 27.デジタル出力

図 28.SYNCINB± 入力

図 29.SCLK 入力

Rev. **0** — 16/64 —

図 30.CSB 入力

図 31.SDIO 入力

図 32.FD\_A/FD\_B 出力

図 33.PDWN/STBY 入力

図 34.V\_1P0 入力/出力

Rev. **0** — 17/64 —

# 動作原理

AD9680 には、2 つのアナログ入力チャンネルと 2 つの JESD204B 出力レーン対があります。この ADC は、最大 2 GHz の広帯域アナログ信号をサンプルするようにデザインされています。AD9680 は、広い入力帯域幅、高サンプリング・レート、優れた直線性、小型パッケージで低消費電力となるよう最適化 されています。

2個の ADC コアはマルチステージの差動パイプライン・アーキテクチャを採用し、出力誤差補正ロジックを内蔵しています。各 ADCは、ユーザー選択可能な多様な入力範囲をサポートする広帯域入力を持っています。リファレンス電圧を内蔵しているためデザインが容易です。

AD9680 は、通信レシーバの AGC 機能を簡素化する複数の機能を内蔵しています。プログラマブルなスレッショールドを持つ検出器を使うと、ADC の高速検出出力ビットを使って着信信号電力をモニタすることができます。入力信号レベルがプログラマブルなスレッショールドを超えると、高速検出インジケータがハイ・レベルになります。このスレッショールド・インジケータのレイテンシは小さいため、迅速にシステム・ゲインを下げて ADC 入力での範囲外状態を回避することができます。

サンプル・レートとデシメーション比に応じて、サブクラス 1 JESD204B に基づく高速シリアル出力データ・レートを 1 レーン (L=1)、2 レーン (L=2)、4 レーン (L=4) に設定することができます。 複数 デバイス 間の同期は、SYSREF± 入力 ピンと SYNCINB± 入力ピンを使ってサポートします。

# ADC のアーキテクチャ

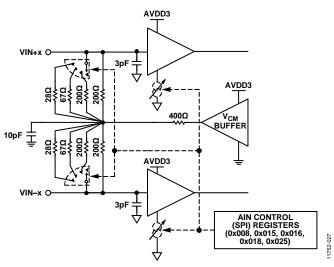

AD9680 のアーキテクチャは、入力バッファ付きパイプライン ADC で構成されています。入力バッファは、アナログ入力信号 に対する終端インピーダンスを提供するようにデザインされて います。この終端インピーダンスは、ドライバ/アンプの終端 条件に合わせて SPI 経由で変更することができます。デフォルトの終端値は 400  $\Omega$  です。アナログ入力終端の等価回路図を図 24 に示します。入力バッファは、優れた直線性、低ノイズ、低 消費電力となるように最適化されています。

入力バッファはリニアな高入力インピーダンスを提供し(駆動が容易)、ADC からの影響を小さくします。バッファは、優れた直線性、低ノイズ、低消費電力となるように最適化されています。各ステージからの量子化された出力は、デジタル補正ロジックで結合されて最終的に 14 ビットになります。パイプライン化されたアーキテクチャにより、新しい入力サンプルに対して最初のステージが動作すると同時に、残りのステージは先行しているサンプルに対して動作することができます。サンプリングはクロックの立上がりエッジで行われます。

## アナログ入力に対する考慮

AD9680 へのアナログ入力は差動バッファになっています。このバッファの内部同相モード電圧は 2.05 V です。クロック信号により、入力回路がサンプル・モードとホールド・モードの間で交互に切り替えられます。

入力回路がサンプル・モードになったとき、信号ソースはサン プル・コンデンサを充電して、クロック・サイクルの 1/2 以内 に安定する必要があります。各入力に小さい抵抗を直列に接続 すると、駆動源側の出力ステージから発生するピーク過渡電流 を減少させることに役立ちます。さらに、 Q の小さいインダク タまたはフェライト・ビーズを各入力に接続し、これによりア ナログ入力の大きな差動容量を小さくして、ADC の最大帯域幅 を実現することができます。このような低 Q インダクタまたは フェライト・ビーズの使用は、コンバータのフロントエンドを高 い IF 周波数で駆動する際に必要となります。差動コンデンサま たは2個のシングルエンド・コンデンサを入力に接続して、受動 整合回路を設けることができます。これにより入力に最終的に ローパス・フィルタが形成されて、不要な広帯域幅ノイズが制 限されます。詳細については、AN-742 アプリケーション・ノー ト、AN-827 アプリケーション・ノート、アナログ・ダイヤログ Transformer-Coupled Front-End for Wideband A/D Converters (Volume 39. April 2005)」を参照してください。一般に、正確な値はアプリ ケーションに依存します。

最適なダイナミック性能を得るためには、同相モードのセトリング誤差が対称になるように、VIN+xと VIN-xを駆動するソース・インピーダンスが一致している必要があります。これらの誤差は、ADCの同相モード除去比により小さくなります。内蔵リファレンス・バッファは、ADCコアの振幅を決定する差動リファレンスを発生します。

最大 SNR 性能は、ADC を差動構成で最大スパンに設定したときに得られます。AD9680 の場合、有効振幅は SPI ポートを介して、 $1.46 \text{ V p-p} \sim 1.94 \text{ V p-p}$  の差動に設定することができます(デフォルトは 1.70 V p-p 差動)。

#### 差動入力構成

AD9680 を能動的または受動的に駆動する方法は複数ありますが、 最適性能は、アナログ入力を差動で駆動したときに得られます。

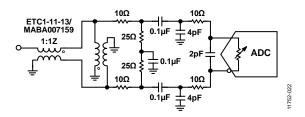

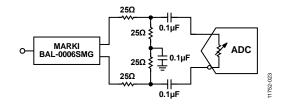

SNR と SFDR が重要なパラメータとなるアプリケーションでは、 差動トランス結合が推奨される入力構成です(図 35 と図 36参照)。 これは、大部分のアンプのノイズ性能は、AD9680 の真の性能 を実現するために不十分であるためです。

低周波から中周波の範囲では、AD9680の最適性能のために、 ダブル・バランまたはダブル・トランス回路 (図 35 参照)が推奨 されます。第2または第3ナイキスト・ゾーンの高周波では、 幾つかのフロントエンド受動部品を削除して広帯域動作を確保 することが望まれます(図 36 参照)。

Rev. **0** — 18/64 —

図35.第1および第2ナイキスト周波数での差動トランス結合構成

図36.第2および第3ナイキスト周波数での差動トランス結合構成

# 入力同相モード

AD9680 のアナログ入力は、内部で同相モードにバイアスされています (図 37 参照)。同相モード・バッファの範囲には限界があるため、同相モード電圧が 100~mV 以上低下すると、性能が影響を受けます。このため、DC 結合アプリケーションでは、同相モード電圧を  $2.05~\text{V}\pm100~\text{mV}$  に設定して正しい ADC 動作を確保してください。DC 結合アプリケーションで動作する場合は、フルスケール電圧を 1.7~V p-p 差動に設定する必要があります。

### アナログ入力の制御と SFDR の最適化

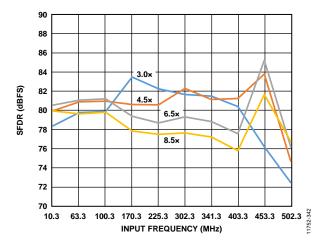

AD9680 では、入力終端、バッファ電流、入力フルスケール調整のような、アナログ入力に対する柔軟な制御を提供しています。使用可能なすべての制御を図37に示します。

図 37.アナログ入力の制御

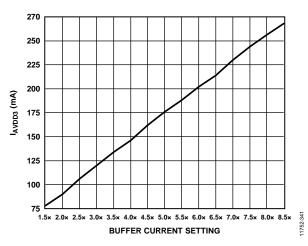

レジスタ 0x018 を使うと、各チャンネルのバッファ電流をスケーリングして、種々の入力周波数と注目する帯域幅で SFDR を最適化することができます。入力バッファ電流を設定すると、AVDD3 電源で必要とされる電流が変化します。この関係を図38 に示します。バッファ電流設定のすべての値については、表29を参照してください。

図 38.バッファ電流設定値対 AVDD3 電源

図 39.バッファ電流スィープ AD9680 (SFDR 対 I<sub>BUFF</sub>); f<sub>IN</sub> < 500 MHz

高周波アプリケーションによっては、フルスケール設定値を小さくして SFDR を向上させることができます。

Rev. **0** — 19/64 —

表 9 に、様々なアナログ入力周波数範囲での推奨バッファ電流とフルスケール電圧の設定値を示します。

表 9.入力周波数に対する SFDR の最適化

| Input<br>Frequency<br>(MHz) | Input Full-Scale<br>Range,<br>Register 0x025<br>(V p-p) | Input Buffer Current<br>Control Setting,<br>Register 0x018 |

|-----------------------------|---------------------------------------------------------|------------------------------------------------------------|

| <500 MHz                    | 1.7/1.82/1.94<br>differential                           | 3.0×                                                       |

| 500 MHz to<br>1 GHz         | 1.58/1.46 differential                                  | 4.5× or 6.5×                                               |

| >1 GHz                      | 1.46 differential                                       | 6.5×                                                       |

#### 絶対最大入力振幅

AD9680 入力で許容される絶対最大入力振幅は、4.3 V p-p 差動です。このレベルまたは近くで動作する信号により、ADC に恒久的な損傷が生ずることがあります。

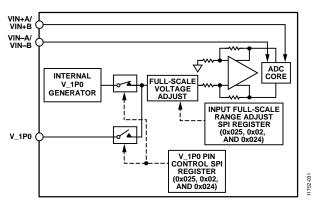

### リファレンス電圧

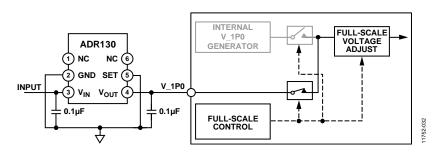

AD9680 には、安定かつ正確な  $1.0\ V$  のリファレンス電圧が内蔵されています。この内蔵  $1.0\ V$  リファレンス電圧を使って、ADC のフルスケール入力範囲を設定します。フルスケール入力範囲は、ADC ファンクション・レジスタ 0x025 を使って調整することができます。入力振幅調整の詳細については、表 29 を参照してください。図 40 に内部  $1.0\ V$  リファレンス電圧制御のブロック図を示します。

図 40.内蔵リファレンス電圧の設定と制御

SPI レジスタ 0x024 を使うと、この内部 1.0 V リファレンス電圧 の使用か、外付け 1.0 V リファレンス電圧の使用を選択することができます。外付けリファレンス電圧を使用する場合、1.0 V のリファレンス電圧を入力する必要があります。フルスケール調整は、リファレンス電圧に無関係に、SPI を経由して行うことができます。AD9680 のフルスケール・レベル調整の詳細については、メモリ・マップ・レジスタ・テーブル のセクションを参照してください。

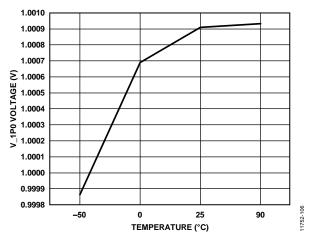

アプリケーションによっては、ADC のゲイン精度を向上させる場合または温度ドリフト特性を改善する場合、外付けリファレンス電圧の使用が必要となることがあります。図 41 に、内蔵1.0 V リファレンス電圧の代表的なドリフト特性を示します。

図 41.代表的な V\_1P0 ドリフト

外付けリファレンス電圧は、安定な 1.0 V リファレンス電圧である必要があります。ADR130 は、1.0 V リファレンス電圧の優れたオプションです。図 42 に、ADR130 を使用して外付け 1.0 V リファレンス電圧を AD9680 へ供給する方法を示します。灰色領域は AD9680 の未使用ブロックを示し、ADR130 を使用して外付けリファレンス電圧を供給しています。

図 42. ADR130 を使用した外付けリファレンス電圧

Rev. **0** — 20/64 —

# クロック入力の考慮事項

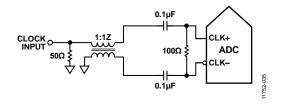

最適性能を得るためには、AD9680 のサンプル・クロック入力 (CLK+と CLK-)を差動信号で駆動する必要があります。信号は、一般にトランスまたはクロック・ドライバを介して CLK+ピンと CLK-ピンに AC 結合されます。これらのピンは内部でバイアスされているため、バイアスを追加する必要はありません。

図 43 に、AD9680 に対する推奨クロック入力方法を示します。 ジッタの少ないクロック・ソースは、RF トランスを使ってシン グルエンド信号から差動信号に変換されます。

図 43.トランス結合差動クロック

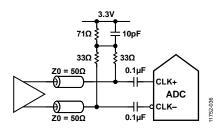

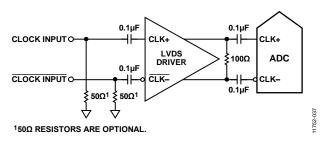

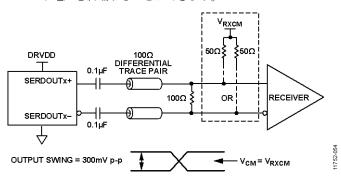

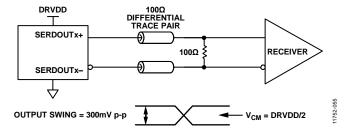

別のオプションは、差動 CML または LVDS 信号をサンプル・クロック入力ピンへ AC 結合する方法です(図 44 と図 45 参照)。

図 44.差動 CML サンプル・クロック

図 45.差動 LVDS サンプル・クロック

### クロック・デューティ・サイクルの考慮事項

一般的な高速 ADC では両クロック・エッジを使って、様々な内部タイミング信号を発生しています。このため、これらの ADC はクロックのデューティ・サイクルに敏感です。一般に、ダイナミック性能特性を維持するためにはクロック・デューティ・サイクルの許容誤差は 5%以内である必要があります。50%のクロック・デューティ・サイクルを保証できないアプリケーションでは、複数の高周波クロックをデバイスへ供給することができます。内蔵クロック分周器を 2 に設定して、2 GHz クロックでAD9680 を駆動することができます。分周器出力は、50%デューティ・サイクルで高いスルー・レート (高速エッジ) のクロック信号を内蔵 ADC へ供給します。この機能の詳細については、メモリ・マップのセクションを参照してください。

### 入力クロック・ドライバ

AD9680 は、ナイキスト入力クロックを-1、2、4、8 分周できる 入力クロック分周器を内蔵しています。分周比はレジスタ 0x10B を使って選択することができます。これを図 46 に示しま す。

CLK+ 入力の最大周波数は 4 GHz です。これは、分周器による制限です。クロック入力がサンプル・クロックの倍数であるアプリケーションでは、該当する分周比をクロック分周器に設定した後にクロック信号を供給するように注意してください。これにより、デバイス・スタートアップ時の過渡電流の制御が行われます。

図 46.クロック分周器回路

AD9680 のクロック分周器は外部 SYSREF±入力を使って同期させることができます。有効な SYSREF±により、クロック分周器はプログラマブルな状態にリセットされます。この同期機能を使うと、複数のデバイスに位相の一致したクロック分周器を持たせることができるので、同時入力サンプリングが保証されます。

# クロック・ジッタの考慮事項

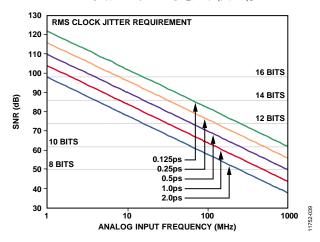

高速な高分解能 ADC は、クロック入力の品質に敏感です。与えられた入力周波数( $f_A$ )でジッタ( $t_B$ )のみにより発生する SNR 性能の低下は次式で計算されます。

$SNR = 20 \times \log 10 (2 \times \pi \times f_A \times t_J)$

この式で、rms アパーチャ・ジッタは、クロック入力、アナログ入力信号、ADC アパーチャ・ジッタ仕様を含む全ジッタ・ソースの 2 乗和平方根を表します。IF アンダーサンプリング・アプリケーションは、特にジッタに敏感です(図 47)。

図 47.入力周波数およびジッタ対理論 SNR

アパーチャ・ジッタが AD9680 のダイナミックレンジに影響を与えるケースでは、クロック入力はアナログ信号として扱う必要があります。クロック・ドライバの電源は ADC 出力ドライバの電源と分離して、クロック信号がデジタル・ノイズから変調を受けないようにする必要があります。クロックが別のタイプのソース(ゲーティング、分周、またはその他の方法)から発生される場合、最終ステップで元のクロックを使って再タイミングする必要があります。ジッタ性能については ADC に関係するため、AN-501 アプリケーション・ノートと AN-756 アプリケーション・ノートを参照してください。

### パワーダウン/スタンバイ・モード

AD9680 には PDWN/STBY ピンがあり、このピンを使って、デバイスをパワーダウン・モードまたはスタンバイ・モードに設定することができます。デフォルト動作は PDWN です。PDWN/STBY ピンはロジック・ハイ・ピンです。パワーダウン・モードのとき、JESD204B リンクは切断されます。パワーダウン・オプションは、レジスタ 0x03F とレジスタ 0x040 を使って設定することもできます。

スタンバイ・モードでは、JESD204B リンクが切断されないため、すべてのコンバータ・サンプルに対してゼロが送信されます。これは、レジスタ 0x571 のビット 7 を使って /K/文字を選択するように変更することができます。

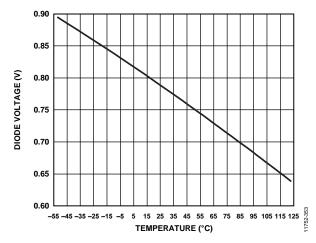

#### 温度ダイオード

AD9680 は、チップ温度を測定するダイオードを採用した温度センサーを内蔵しています。このダイオードは電圧を出力することができるため、内部チップ温度をモニタする粗調整温度センサーとして機能することができます。

温度ダイオード電圧は SPI を使って、FD\_A ピンへ出力させることができます。 レジスタ 0x028 のビット 0 を使って、ダイオー

ドをイネーブルまたはディスエーブルしてください。レジスタ 0x028 はローカル・レジスタです。温度ダイオードの読出しをイネーブルするときは、デバイス・インデックス・レジスタ (0x008)でチャンネル A を選択する必要があります。レジスタ 0x040[2:0]を設定して、FD\_A ピンにダイオード電圧を出力するように設定してください。 詳細については、表 29 を参照してください。

温度ダイオードの電圧応答を図48に示します。

図 48.温度ダイオード電圧の温度特性

Rev. **0** — 22/64 —

# ADC 範囲外と高速検出

レシーバ・アプリケーションでは、コンバータがクリップされそうなとき確実に検出できることが望まれます。JESD204B 出力の標準の範囲外ビットは、アナログ入力状態の情報を提供しますが、あまり役立ちません。したがって、クリップが実際に発生する前にゲインを小さくするための時間を確保するためには、フルスケールより下にプログラマブルなスレッショールドを設けることが有効です。さらに、入力信号が大きなスルーレートを持つことがあるため、この機能によるレイテンシが大きな問題になります。高度にパイプライン化されたコンバータは大きなレイテンシを持ちます。AD9680 は、スレッショールドをモニタし、FD\_A ピンと FD\_B ピンをアサートする高速検出回路を個々のチャンネルに対して内蔵しています。

### ADC 範囲外

ADC の入力で範囲外が検出されると、ADC 範囲外インジケータがアサートされます。範囲外インジケータは、JESD204B リンク内にコントロール・ビット (CSB > 0 の場合)として設けることができます。この範囲外インジケータのレイテンシは、サンプル・レイテンシと一致します。

また、AD9680 は8個の仮想コンバータのすべての範囲外状態を記録します。仮想コンバータの詳細については、図50を参照してください。各仮想コンバータの範囲外ステータスは、レジスタ0x563のスティキー・ビットとして保持されます。レジスタ0x562で仮想コンバータのセット位置とリセット位置に対応するビットをトグルすることにより、レジスタ0x563の値はクリアすることができます。

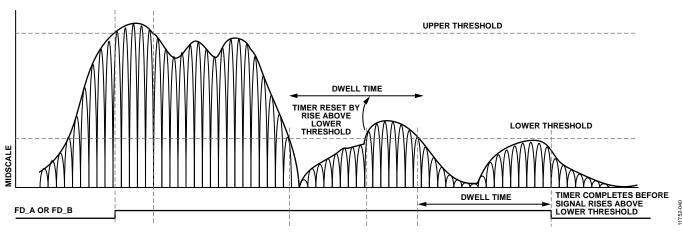

# 高速スレッショールド検出 (FD\_A および FD\_B)

入力信号の絶対値がプログラマブルな上側スレッショールド・レベルを超えるたびに FD ビットは直ちにセットされます。入力信号の絶対値がプログラマブルなドウエル時間より長い間下側スレッショールド・レベルを下回ると、FD ビットがクリアされます。この機能はヒステリシスを提供して、FD ビットの余分なトグリングを防止します。

上側スレッショールド・レジスタ、下側スレッショールド・レジスタ、およびドウエル時間レジスタの動作を図 49 に示します。 入力振幅が高速検出上側スレッショールド・レジスタ (レジスタ 0x247 とレジスタ 0x248) に設定された値を超えると、FD インジケータがアサートされます。選択されたスレッショールド・レジスタが、ADC の出力で信号振幅と比較されます。高速上側スレッショールド検出には、最大 28 クロック・サイクルのレイテンシがあります。上側スレッショールド振幅の概略値は次式で与えられます。

上側スレッショールド振幅 (dBFS) =  $20 \log (X \nu y \nu)$ ョールド振幅 $(2^{13})$

信号が設定されたドウエル時間に対する下側スレッショールドを下回るまで、FD インジケータはクリアされません。下側スレッショールドは、レジスタ 0x249 とレジスタ 0x24A の高速検出下側スレッショールド・レジスタに設定されます。高速検出下側スレッショールド・レジスタは 13 ビットのレジスタで、このレジスタは ADC の出力で信号振幅と比較されます。この比較では、ADC パイプライン・レイテンシが発生しますが、コンバータ分解能は正確です。下側スレッショールド振幅は次式で与えられます。

下側スレッショールド振幅 (dBFS) =  $20 \log (X \nu y )$  ョールド振幅 $(2^{13})$

例えば、-6 dBFS の上側スレッショールドを設定するときは、レジスタ 0x247 とレジスタ 0x248 へ 0xFFF を書込みます。-10 dBFS の下側スレッショールドを設定するときは、レジスタ 0x249 とレジスタ 0x24A へ 0xA1D を書込みます。

レジスタ 0x24B とレジスタ 0x24C の高速検出ドウエル時間レジスタに所望の値を設定して、ドウエル時間を  $1\sim65,535$  サンプル・クロック・サイクルに設定することができます。詳細については、メモリ・マップのセクション (表 29 のレジスタ 0x24C)を参照してください。

図 49.FD\_A 信号と FD\_B 信号に対するスレッショールドの設定

Rev. **0** — 23/64 —

# デジタル・ダウン・コンバータ (DDC)

AD9680 は、フィルタ機能を提供し、出力データ・レートを下げる4個のデジタル・ダウン・コンバータ (DDC 0~DDC 3)を内蔵しています。このデジタル処理セクションには、NCO、ハーフバンド・デシメーション・フィルタ、FIR フィルタ、ゲイン・ステージ、複素数/実数変換ステージが含まれています。これらの各処理ブロックは、コントロール・ラインを持っています。このラインを使うと、これらのブロックを独立にイネーブル/ディスエーブルして、所望の処理機能を提供することができます。デジタル・ダウンコンバータは、実数データまたは複素数データを出力するように設定することができます。

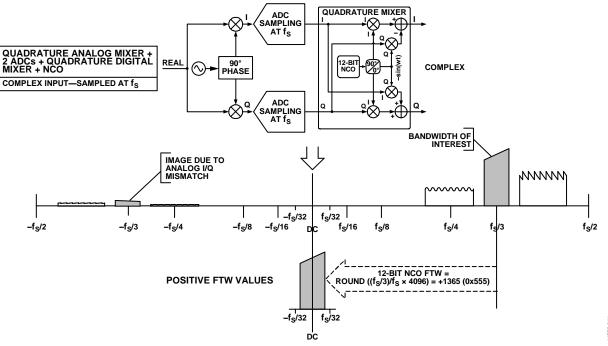

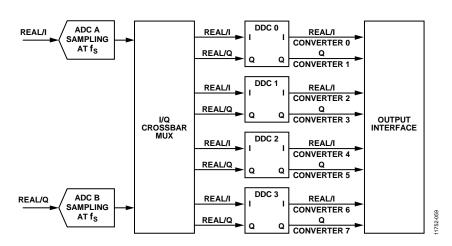

# DDC I/Q 入力選択

AD9680 には 2 つの ADC チャンネルと 4 つの DDC チャンネルがあります。各 DDC チャンネルには 2 つの入力ポートがあり、これらで対を構成して、I/Q クロスバー・マルチプレクサを介して実数入力と複素数入力をサポートすることができます。実数信号の場合、両 DDC 入力ポートで同じ ADC チャンネルを選択する必要があります (例えば、DDC 入力ポート I = ADC チャンネル A、入力ポート Q = ADC チャンネルを選択する必要があります (例えば、DDC 入力ポート Q = ADC チャンネルを選択する必要があります (例えば、DDC 入力ポート Q = ADC チャンネル B)。

各 DDC の入力は、DDC 入力選択レジスタ(レジスタ 0x311、レジスタ 0x331、レジスタ 0x351、レジスタ 0x371)から制御されます。DDC の設定方法については、表 29 を参照してください。

### DDC I/Q 出力の選択

各 DDC チャンネルには 2つの出力ポートがあり、これらで対を構成して、実数出力と複素数出力をサポートすることができます。実数出力信号の場合、DDC 出力ポート I のみを使用します (DDC 出力ポート Q は無効になります)。複素数 I/Q 出力信号の場合、DDC 出力ポート I を使用します。

各 DDC チャンネルに対する I/Q 出力は、DDC コントロール・レジスタ (レジスタ 0x310、レジスタ 0x330、レジスタ 0x350、レジスタ 0x370)の DDC 複素数/実数イネーブル・ビット (ビット 3)から制御されます。

チップ・アプリケーション・モード・レジスタ (レジスタ 0x200)のチップ Q 無視ビット (ビット 5)は、すべての DDC チャンネルのチップ出力マルチプレクスを制御します。すべての DDC チャンネルで実数出力を使用する場合は、このビットにハイ・レベルを設定して、すべての DDC Q 出力ポートを無視する必要があります。いずれかの DDC チャンネルで複素数 I/Q 出力を使用するように設定する場合は、このビットをクリアして DDC 出力ポート I と I/Q と使用する必要があります。詳細については、図 I/Q 58 を参照してください。

### DDC の概要

4個の DDC ブロックを使って、ADC で取得したフル・デジタル・スペクトルの一部を取り出します。これらは、広帯域入力信号を必要とする IF サンプリングまたはオーバーサンプルしたベースバンド無線を対象にしています。

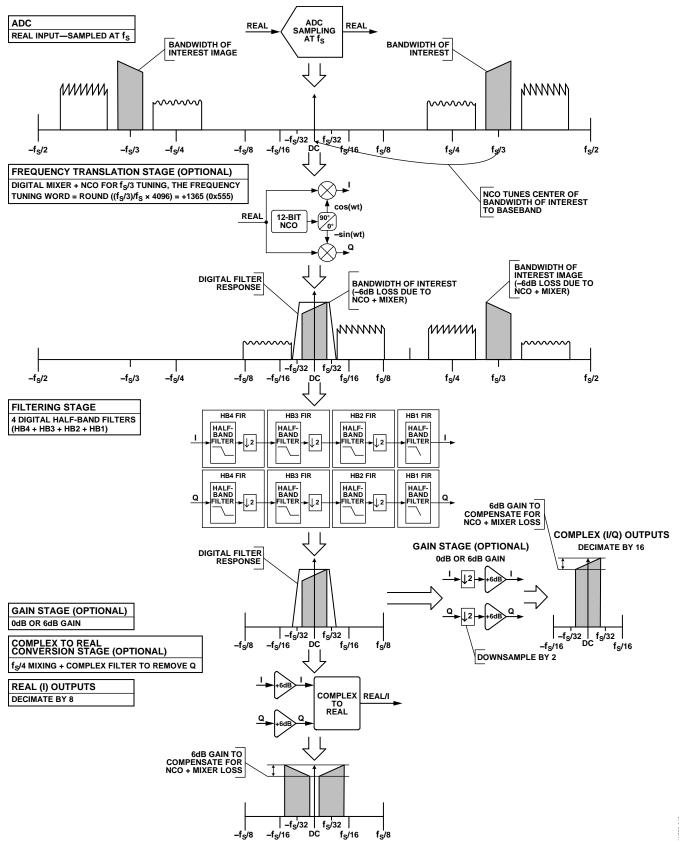

各 DDC ブロックには次の信号処理ステージが含まれます。

#### 周波数変換ステージ(オプション)

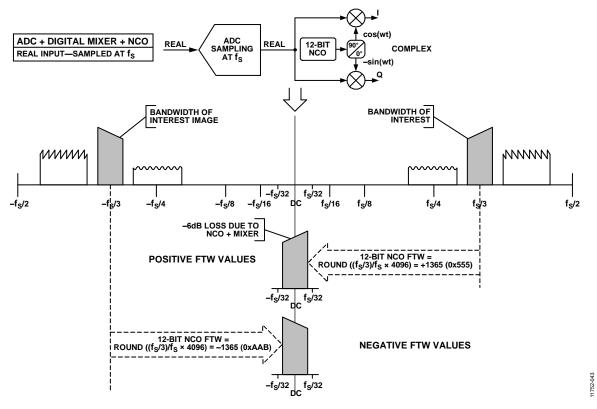

周波数変換ステージは、実数入力信号または複素数入力信号の 周波数変換に使用できる 12 ビット複素数 NCO と直交ミキサー から構成されています。 このステージは、有効なデジタル・ス ペクトル部分をベースバンドへ変換します。

#### フィルタ・ステージ

ベースバンドへ変換した後、フィルタ・ステージは、レート変換用の最大 4 個のハーフバンド・ローパス・フィルタのチェーンを使って周波数スペクトルをデシメートします。このデシメーション処理により出力データ・レートが低下するため、出力インターフェース・レートも低くなります。

## ゲイン・ステージ (オプション)

実数入力信号をミキシングしてベースバンドへ変換する際に損失が生ずるため、ゲイン・ステージは 0 dB または 6 dB のゲインを追加してこれを補償します。

#### 複素数/実数変換ステージ(オプション)

実数出力が必要な場合、複素数/実数変換ステージは、fs/4 ミキシング動作とフィルタリングにより信号の複素数成分を除去して複素数出力を実数出力に戻します。

図 50 に、AD9680 の内蔵 DDC の詳細ブロック図示をします。

図 50.DDC の詳細ブロック図

図 51 に、4 個の DDC ブロックの 1 つの使用例を示します。この例では実数入力信号と 4 個のハーフバンド・フィルタ (HB4、HB3、HB2、HB1)を使用しています。この図は、複素数 (デシメーション比 16)と実数 (デシメーション比 8) の出力オプションを示しています。

DDC が異なるデシメーション比を持つ場合、チップ・デシメーション比 (レジスタ 0x201)には、すべての DDC ブロックの最小 デシメーション比を設定する必要があります。この場合、チッ

プ・デシメーション比のサンプル・レートに一致させるため、高いデシメーション比の DDC ではサンプル値が繰り返されます。 NCO 周波数を設定または変更するごとに、DDC ソフト・リセットを発行する必要があります。DDC ソフト・リセットを発行しないと、出力振幅が変動することがあります。

表 10、表 11、表 12、表 13、表 14に、チップ・デシメーション 比をそれぞれ 1、2、4、8、16 に設定した場合の DDC サンプル を示します。

Rev. **0** — 25/64 —

ータシート AD9680

図 51.DDC の動作例 (実数入力—デシメーション比 16)

表 10.DDC サンプル、チップ・デシメーション比 = 1

| Real (I) Output (Complex to Real Enabled) |                                                |                                                          | Complex (I/Q) Outputs (Complex to Real Disabled)                   |                                |                                                |                                                          |                                                                        |

|-------------------------------------------|------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------|--------------------------------|------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------|

| HB1 FIR (DCM <sup>1</sup> = 1)            | HB2 FIR +<br>HB1 FIR<br>(DCM <sup>1</sup> = 2) | HB3 FIR + HB2<br>FIR + HB1 FIR<br>(DCM <sup>1</sup> = 4) | HB4 FIR + HB3 FIR<br>+ HB2 FIR + HB1<br>FIR (DCM <sup>1</sup> = 8) | HB1 FIR (DCM <sup>1</sup> = 2) | HB2 FIR +<br>HB1 FIR<br>(DCM <sup>1</sup> = 4) | HB3 FIR + HB2<br>FIR + HB1 FIR<br>(DCM <sup>1</sup> = 8) | HB4 FIR + HB3<br>FIR + HB2 FIR +<br>HB1 FIR (DCM <sup>1</sup> =<br>16) |

| N                                         | N                                              | N                                                        | N                                                                  | N                              | N                                              | N                                                        | N                                                                      |

| N + 1                                     | N                                              | N                                                        | N                                                                  | N                              | N                                              | N                                                        | N                                                                      |

| N+2                                       | N + 1                                          | N                                                        | N                                                                  | N + 1                          | N                                              | N                                                        | N                                                                      |

| N + 3                                     | N + 1                                          | N                                                        | N                                                                  | N + 1                          | N                                              | N                                                        | N                                                                      |

| N+4                                       | N + 2                                          | N + 1                                                    | N                                                                  | N + 2                          | N + 1                                          | N                                                        | N                                                                      |

| N + 5                                     | N + 2                                          | N + 1                                                    | N                                                                  | N + 2                          | N + 1                                          | N                                                        | N                                                                      |

| N+6                                       | N + 3                                          | N + 1                                                    | N                                                                  | N + 3                          | N + 1                                          | N                                                        | N                                                                      |

| N+7                                       | N + 3                                          | N + 1                                                    | N                                                                  | N + 3                          | N + 1                                          | N                                                        | N                                                                      |

| N+8                                       | N + 4                                          | N + 2                                                    | N + 1                                                              | N + 4                          | N + 2                                          | N + 1                                                    | N                                                                      |

| N+9                                       | N + 4                                          | N + 2                                                    | N + 1                                                              | N + 4                          | N + 2                                          | N + 1                                                    | N                                                                      |

| N + 10                                    | N + 5                                          | N + 2                                                    | N + 1                                                              | N + 5                          | N + 2                                          | N + 1                                                    | N                                                                      |

| N + 11                                    | N + 5                                          | N + 2                                                    | N + 1                                                              | N + 5                          | N + 2                                          | N + 1                                                    | N                                                                      |

| N + 12                                    | N + 6                                          | N + 3                                                    | N + 1                                                              | N + 6                          | N+3                                            | N + 1                                                    | N                                                                      |

| N + 13                                    | N + 6                                          | N + 3                                                    | N + 1                                                              | N + 6                          | N+3                                            | N + 1                                                    | N                                                                      |

| N + 14                                    | N + 7                                          | N + 3                                                    | N + 1                                                              | N + 7                          | N+3                                            | N + 1                                                    | N                                                                      |

| N + 15                                    | N + 7                                          | N + 3                                                    | N + 1                                                              | N + 7                          | N + 3                                          | N + 1                                                    | N                                                                      |

| N + 16                                    | N + 8                                          | N + 4                                                    | N+2                                                                | N + 8                          | N + 4                                          | N + 2                                                    | N + 1                                                                  |

| N + 17                                    | N + 8                                          | N + 4                                                    | N+2                                                                | N + 8                          | N + 4                                          | N + 2                                                    | N + 1                                                                  |

| N + 18                                    | N + 9                                          | N + 4                                                    | N+2                                                                | N + 9                          | N + 4                                          | N + 2                                                    | N + 1                                                                  |

| N + 19                                    | N + 9                                          | N + 4                                                    | N+2                                                                | N + 9                          | N + 4                                          | N + 2                                                    | N + 1                                                                  |

| N + 20                                    | N + 10                                         | N + 5                                                    | N+2                                                                | N + 10                         | N + 5                                          | N + 2                                                    | N + 1                                                                  |

| N + 21                                    | N + 10                                         | N + 5                                                    | N+2                                                                | N + 10                         | N + 5                                          | N + 2                                                    | N + 1                                                                  |

| N + 22                                    | N + 11                                         | N + 5                                                    | N+2                                                                | N + 11                         | N + 5                                          | N + 2                                                    | N + 1                                                                  |

| N + 23                                    | N + 11                                         | N + 5                                                    | N+2                                                                | N + 11                         | N + 5                                          | N + 2                                                    | N+1                                                                    |

| N + 24                                    | N + 12                                         | N + 6                                                    | N+3                                                                | N + 12                         | N + 6                                          | N + 3                                                    | N+1                                                                    |

| N + 25                                    | N + 12                                         | N + 6                                                    | N+3                                                                | N + 12                         | N + 6                                          | N + 3                                                    | N+1                                                                    |

| N + 26                                    | N + 13                                         | N + 6                                                    | N + 3                                                              | N + 13                         | N + 6                                          | N + 3                                                    | N + 1                                                                  |

| N + 27                                    | N + 13                                         | N + 6                                                    | N + 3                                                              | N + 13                         | N + 6                                          | N + 3                                                    | N + 1                                                                  |

| N + 28                                    | N + 14                                         | N + 7                                                    | N + 3                                                              | N + 14                         | N + 7                                          | N + 3                                                    | N + 1                                                                  |

| N + 29                                    | N + 14                                         | N + 7                                                    | N+3                                                                | N + 14                         | N + 7                                          | N + 3                                                    | N + 1                                                                  |

| N + 30                                    | N + 15                                         | N + 7                                                    | N+3                                                                | N + 15                         | N + 7                                          | N + 3                                                    | N + 1                                                                  |

| N + 31                                    | N + 15                                         | N + 7                                                    | N+3                                                                | N + 15                         | N + 7                                          | N + 3                                                    | N+1                                                                    |

$<sup>^{1}</sup>$  DCM =  $\vec{r}$  $\vec{v}$  $\vec{v$

Rev. **0** — 27/64 —

表 11.DDC サンプル、チップ・デシメーション比 = 2

| Real (I) Output (Complex to Real Enabled)      |                                                             |                                                              | Co                 | mplex (I/Q) Outputs          | (Complex to Real Dis                                        | sabled)                                           |

|------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|--------------------|------------------------------|-------------------------------------------------------------|---------------------------------------------------|

| HB2 FIR +<br>HB1 FIR<br>(DCM <sup>1</sup> = 2) | HB3 FIR +<br>HB2 FIR +<br>HB1 FIR<br>(DCM <sup>1</sup> = 4) | HB4 FIR + HB3 FIR + HB2 FIR + HB1 FIR (DCM <sup>1</sup> = 8) | HB1 FIR (DCM¹ = 2) | HB2 FIR + HB1 FIR (DCM¹ = 4) | HB3 FIR +<br>HB2 FIR +<br>HB1 FIR<br>(DCM <sup>1</sup> = 8) | HB4 FIR + HB3 FIR + HB2 FIR + HB1 FIR (DCM¹ = 16) |

| N                                              | N                                                           | N                                                            | N                  | N                            | N                                                           | N                                                 |

| N + 1                                          | N                                                           | N                                                            | N + 1              | N                            | N                                                           | N                                                 |

| N + 2                                          | N + 1                                                       | N                                                            | N + 2              | N + 1                        | N                                                           | N                                                 |

| N + 3                                          | N + 1                                                       | N                                                            | N + 3              | N + 1                        | N                                                           | N                                                 |

| N+4                                            | N + 2                                                       | N+1                                                          | N + 4              | N + 2                        | N + 1                                                       | N                                                 |

| N + 5                                          | N + 2                                                       | N+1                                                          | N + 5              | N + 2                        | N + 1                                                       | N                                                 |

| N + 6                                          | N + 3                                                       | N + 1                                                        | N + 6              | N + 3                        | N + 1                                                       | N                                                 |

| N + 7                                          | N + 3                                                       | N + 1                                                        | N + 7              | N + 3                        | N + 1                                                       | N                                                 |

| N + 8                                          | N + 4                                                       | N+2                                                          | N + 8              | N + 4                        | N + 2                                                       | N + 1                                             |

| N + 9                                          | N + 4                                                       | N+2                                                          | N + 9              | N + 4                        | N+2                                                         | N + 1                                             |

| N + 10                                         | N + 5                                                       | N+2                                                          | N + 10             | N + 5                        | N+2                                                         | N + 1                                             |

| N + 11                                         | N + 5                                                       | N+2                                                          | N + 11             | N + 5                        | N+2                                                         | N + 1                                             |

| N + 12                                         | N + 6                                                       | N+3                                                          | N + 12             | N + 6                        | N + 3                                                       | N + 1                                             |