# 310 MSPS、3.3V/1.8V デュアル 16 ビット ADC

データシート AD9652

### 特長

#### 高ダイナミックレンジ

SNR = 75.0 dBFS at 70 MHz ( $A_{IN} = -1$  dBFS)

SFDR = 87 dBc at 70 MHz  $(A_{IN} = -1 dBFS)$

Noise spectral density (NSD) = -156.7 dBFS/Hz 入力ノイズ at -1 dBFS at 70 MHz

NSD = -157.6 dBFS/Hz 小信号ノイズ at -7dBFS at 70 MHz チャンネル・アイソレーション/クロストーク: 90 dB ディザリング回路を内蔵(小信号直線性を改善)

#### 卓越した IF サンプリング性能

SNR = 73.7 dBFS at 170 MHz ( $A_{IN} = -1$  dBFS)

SFDR = 85 dBc at 170 MHz ( $A_{IN} = -1$  dBFS)

フルパワー帯域幅: 465 MHz

#### 3.3 V バッファを内蔵

プログラマブル入力スパン:2 Vp-p~2.5 Vp-p (デフォルト)

1、2、4 及び 8 分周差動クロック入力受信回路 (クロック分周 器は 1.24 GHz までのクロックを受信可能)

ADC クロックのデューティ・サイクル・スタビライザを内蔵

SYNC 入力によりマルチチップ同期が可能

総合消費電力: 2.16 W

電源電圧: 3.3 V 及び 1.8 V

DDR LVDS(ANSI-644 レベル)出力

シリアル・ポート制御

省電力のパワーダウン・モード

#### アプリケーション

軍用レーダー及び通信

マルチモード・デジタル・レシーバ(3G または 4G)

試験及び計測機器

スマート・アンテナ・システム

#### 概要

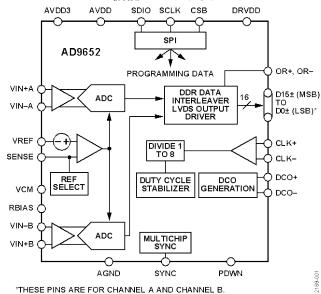

AD9652 は、デュアル、16 ビットの A/D コンバータ(ADC)で、最大 310MSPS のサンプリング速度を備えています。AD9652 は、広い周 波数帯域(最大 465 MHz まで)に渡って優れたダイナミックレンジ 性能を要求する高速信号処理アプリケーションをサポートするため に設計されています。-157.6 dBFS という優れた低ノイズ・フロア特 性と大信号スプリアス・フリー・ダイナミック・レンジ (SFDR) 特 性(通常85dBFSを超える)により、大信号が存在する場合でも低 レベルの信号を処理することができます。デュアルの ADC コアは、 マルチステージのパイプライン・アーキテクチャを採用し、出力誤 差補正ロジックを内蔵しています。内蔵の高性能バッファと基準電 圧源により、ADC の優れた性能を保持しながら、外付け駆動回路と のインタフェース を簡略化を図ることができます。AD9652 は、 ADC のサンプル・クロックを生成するために使用される 1、2、4,及 び8分周が可能な分周回路を備えており、最高1.24 GHz までの入力 クロック周波数をサポートすることができます。デューティ・サイ クル・スタビライザは、ADC へのクロック・デューティ・サイクル の変動を補償します。各 ADC からの 16 ビットの出力データ (オー

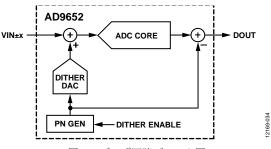

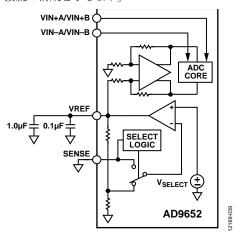

機能ブロック図

-

図 1

バーレンジ・ビットつき)は、ダブルデータレート(DDR)クロックと一緒に単一のLVDS出力上にインターリーブされます。セットアップと制御のためのプログラミングは、3線のSPI互換シリアル・インターフェースを用いて行われます。

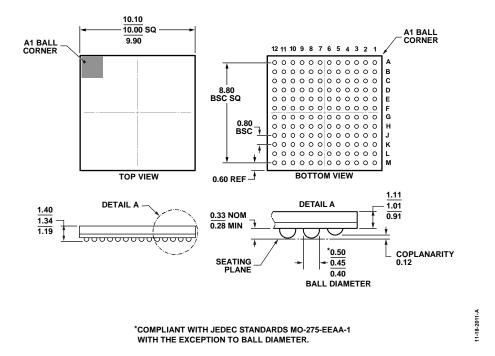

AD9652 は、144 ボール CSP\_BGA パッケージを採用し、-40℃~+85℃の標準工業用温度範囲にわたって仕様規定されています。この製品は出願中の米国特許によって保護されています。

#### 製品のハイライト

- 1.16 ビット、310MSPS の ADC を 2 個内蔵。

- 2. 内蔵のバッファで ADC のドライバ・インタフェースを簡易化。

- 3.3.3 V 及び 1.8 V の電源と、これらとは別のデジタル出力ドライバ用電源で LVDS 出力に対応。

- 4. 独自の差動入力により、最大 485 MHz までの入力周波数で優れた 信号対雑音比 (SNR) 性能を維持。

- 5. SYNC 入力により複数デバイスの同期が可能。

- 6. レジスタのプログラミングとリードバックのための、  $3.3 \, V$ または  $1.8 \, V$  の  $3 \,$ 線 SPI ポートを装備。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2010 Analog Devices, Inc. All rights reserved.

Rev. A

本 社/〒105-6891東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03(5402)8200

# 310 MSPS、3.3V/1.8V デュアル 16 ビット ADC

データシート AD9652

# 目次

| 特長            | 1  |

|---------------|----|

| アプリケーション      | 1  |

| 機能ブロック図       | 1  |

| 概要            | 1  |

| 製品のハイライト      | 1  |

| 改訂履歴          | 2  |

| 仕様            | 3  |

| ADC の直流(DC)仕様 | 3  |

| ADC の交流(AC)仕様 | 4  |

| デジタル仕様        | 5  |

| スイッチング仕様      | 7  |

| タイミング仕様       | 7  |

| 絶対最大定格        | 9  |

| 熱特性           | 9  |

| ESD に関する注意    | 9  |

| ピン配置及びピン機能説明  | 10 |

| 代表的な性能特性      | 13 |

| 等価回路          | 19 |

| 動作原理          | 20 |

| ADC のアーキテクチャ  | 20 |

| アナログ入力に対する考慮  | 20 |

| 電圧リファレンス                | 23 |

|-------------------------|----|

| クロック入力の考慮事項             | 23 |

| 消費電力とスタンバイ・モード          | 25 |

| 内部バックグラウンド・キャリブレーション    | 25 |

| デジタル出力                  | 26 |

| ADC のオーバーレンジ            | 26 |

| 高速スレッショールド検出 (FDA/FDB)  | 28 |

| シリアル・ポート・インタフェース        | 29 |

| SPI を使う設定               | 29 |

| ハードウェア・インターフェース         | 29 |

| SPI を使わない設定             | 29 |

| SPI からアクセス可能な機能         | 30 |

| メモリ・マップ                 | 31 |

| メモリ・マップ・レジスタ・テーブルの読み出し、 | 31 |

| メモリ・マップ・レジスタ・テーブル       | 32 |

| アプリケーション情報              | 36 |

| デザイン・ガイドライン             | 36 |

| 外形寸法                    | 37 |

| オーダー・ガイド                | 37 |

|                         |    |

### 改訂履歴

5/14—Rev. 0 to Rev. A

3ページ、表 1、クロック分周 = 1 の電源電流及び消費電力のパラメータを変更。

4/14—Revision 0: Initial Version

# 仕様

## ADC の直流(DC)仕様

特に指定のない限り、AVDD3 = 3.3 V、AVDD = AVDD\_CLK = 1.8 V、SPIVDD = DRVDD = 1.8 V、サンプル・レート = 310 MSPS (クロック入力 = 1240 MHz、AD9652 4 分周)、VIN = -1.0 dBFS 差動入力、2.5 V p-p フルスケール入力範囲、デューティ・サイクル・スタビライザ (DCS) イネーブル、ディザ・オフ。

表 1

| パラメータ                      | 温度   | Min  | Тур        | Max  | 単位      |

|----------------------------|------|------|------------|------|---------|

| 分解能                        | Full |      | 16         |      | Bits    |

| 精度                         |      |      |            |      |         |

| ノーミス・コード                   | Full |      | 保証         |      |         |

| オフセット誤差                    | Full |      | 1.5        |      | mV      |

| ゲイン誤差                      | Full |      | -0.3       |      | % FSR   |

| 微分非直線性(DNL) <sup>1</sup>   | Full |      | -0.76/+1.1 |      | LSB     |

| 積分非直線性(INL) <sup>1</sup>   | Full |      | -4.5/+4.5  |      | LSB     |

| マッチング特性                    |      |      |            |      |         |

| オフセット誤差                    | Full |      | ±0.7       |      | mV      |

| ゲイン誤差                      | Full |      | ±0.1       |      | %FSR    |

| 温度ドリフト                     |      |      |            |      |         |

| オフセット誤差                    | Full |      | ±0.8       |      | ppm/°C  |

| ゲイン誤差                      | Full |      | ±16        |      | ppm/°C  |

| 入力換算ノイズ                    |      |      |            |      |         |

| V <sub>REF</sub> = 1.25 V  | 25°C |      | 3.7        |      | LSB rms |

| アナログ入力                     |      |      |            |      |         |

| 入力スパン(V REF = 1.25 V に対して) | Full |      | 2.5        |      | V p-p   |

| 入力容量 <sup>2</sup>          | Full |      | 5.8        |      | pF      |

| 入力抵抗 <sup>3</sup>          | Full |      | 27         |      | kΩ      |

| 入力コモン・モード電圧                | Full |      | 2.0        | 2.4  | V       |

| 電源                         |      |      |            |      |         |

| 電源電圧                       |      |      |            |      |         |

| AVDD3                      | Full | 3.15 | 3.3        | 3.45 | V       |

| AVDD                       | Full | 1.7  | 1.8        | 1.9  | V       |

| AVDD_CLK                   | Full | 1.7  | 1.8        | 1.9  | V       |

| DRVDD                      | Full | 1.7  | 1.8        | 1.9  | V       |

| SPIVDD                     | Full | 1.7  | 1.8        | 3.6  | V       |

| 電源電流、クロック分周 = 1            |      |      |            |      |         |

| I <sub>AVDD3</sub>         | Full |      | 145        |      | mA      |

| $I_{AVDD}$                 | Full |      | 701        |      | mA      |

| I <sub>AVDD_CLK</sub>      | Full |      | 56         |      | mA      |

| $I_{DRVDD}$                | Full |      | 180        |      | mA      |

| I <sub>SPIVDD</sub>        | Full |      | 0.005      |      | mA      |

| 消費電力                       |      |      |            |      |         |

| クロック分周 <b>= 1</b>          |      |      |            |      |         |

| 通常動作 1                     | Full |      | 2160       | 2236 | mW      |

| スタンバイ電力 <sup>4</sup>       | Full |      | 80         |      | mW      |

| パワーダウン時電力                  | Full |      | 1          |      | mW      |

<sup>1</sup>低入力周波数のフルスケール正弦波を用いて測定。

$<sup>^2</sup>$ 入力容量は、1本の差動入力ピンと AGND との間の実効容量です。

<sup>&</sup>lt;sup>3</sup>入力抵抗は、1本の差動入力ピンと AGND との間の実効抵抗です。

## ADC の交流(AC)仕様

特に指定のない限り、AVDD3 = 3.3 V、AVDD = AVDD\_CLK = 1.8 V、SPIVDD = DRVDD = 1.8 V、サンプル・レート = 310 MSPS (クロック入力 = 1240 MHz、AD9652 4 分周)、VIN = -1.0 dBFS 差動入力、2.5 V p-p フルスケール入力範囲、DCS イネーブル、ディザ・オフ。

#### 表 2

|                                                     |      |                 | $V_{REF}$ |      |     |       |

|-----------------------------------------------------|------|-----------------|-----------|------|-----|-------|

|                                                     |      | $V_{REF} = 1 V$ | デ         | フォル  | · } |       |

| パラメータ 1                                             | 温度   | Min Typ Max     |           | Тур  | Max | 単位    |

| 差動入力電圧                                              | 25°C | 2.0             |           | 2.5  |     | V p-p |

| 信号対ノイズ比 <b>(SNR)</b>                                |      |                 |           |      |     |       |

| f <sub>IN</sub> = 30 MHz (ナイキスト 1 設定条件を使用)          | 25°C | 74.0            |           | 75.4 |     | dBFS  |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用)          | 25°C | 73.6            | 74.0      | 75.0 |     | dBFS  |

|                                                     | Full |                 | 73.3      |      |     | dBFS  |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用、ディザ・オン)   | 25°C | 73.1            |           | 74.3 |     | dBFS  |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用)         | 25°C | 72.1            |           | 73.7 |     | dBFS  |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用, ディザ・オン) | 25°C | 71.2            |           | 72.0 |     | dBFS  |

| f <sub>IN</sub> = 305 MHz (ナイキスト 2 設定条件を使用)         | 25°C | 70.1            |           | 70.7 |     | dBFS  |

| f <sub>IN</sub> = 400 MHz (ナイキスト 3 設定条件を使用)         | 25°C | 67.9            |           | 68.0 |     | dBFS  |

| 信号対ノイズ比及び歪み(SINAD)                                  |      |                 |           |      |     |       |

| f <sub>IN</sub> = 30 MHz (ナイキスト 1 設定条件を使用)          | 25°C | 72.8            |           | 74.2 |     | dBFS  |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用)          | 25°C | 73.5            | 73.8      | 74.6 |     | dBFS  |

|                                                     | Full |                 | 73.2      |      |     | dBFS  |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用、ディザ・オン)   | 25°C | 73.0            |           | 74.0 |     | dBFS  |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用)         | 25°C | 72.0            |           | 72.6 |     | dBFS  |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用, ディザ・オン) | 25°C | 71.1            |           | 71.7 |     | dBFS  |

| f <sub>IN</sub> = 305 MHz (ナイキスト 2 設定条件を使用)         | 25°C |                 |           | 68.5 |     | dBFS  |

| f <sub>IN</sub> = 400 MHz (ナイキスト 3 設定条件を使用)         | 25°C |                 |           | 65.8 |     | dBFS  |

| 実効ビット数(ENOB)                                        |      |                 |           |      |     |       |

| f <sub>IN</sub> = 30 MHz (ナイキスト 1 設定条件を使用)          | 25°C | 11.8            |           | 12.0 |     | Bits  |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用)          | 25°C | 12              | 12.0      | 12.1 |     | Bits  |

|                                                     | Full |                 | 11.9      |      |     | Bits  |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用、ディザ・オン)   | 25°C | 11.8            |           | 12.0 |     | Bits  |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用)         | 25°C | 11.7            |           | 11.8 |     | Bits  |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用, ディザ・オン) | 25°C | 11.5            |           | 11.6 |     | Bits  |

| f <sub>IN</sub> = 305 MHz (ナイキスト 2 設定条件を使用)         | 25°C |                 |           | 11.1 |     | Bits  |

| f <sub>IN</sub> = 400 MHz (ナイキスト 3 設定条件を使用)         | 25°C |                 |           | 10.6 |     | Bits  |

| 第2または第3高調波                                          |      |                 |           |      |     |       |

| f <sub>IN</sub> = 30 MHz (ナイキスト 1 設定条件を使用)          | 25°C | -96             |           | -94  |     | dBc   |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用)          | 25°C | -90             |           | -87  | -83 | dBc   |

|                                                     | Full |                 |           |      | -83 | dBc   |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用、ディザ・オン)   | 25°C | -92             |           | -89  |     | dBc   |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用)         | 25°C | -87             |           | -85  |     | dBc   |

| f <sub>IN</sub> = 170 MHz (ナイキスト2設定条件を使用, ディザ・オン)   | 25°C | -87             |           | -85  |     | dBc   |

| f <sub>IN</sub> = 305 MHz (ナイキスト 2 設定条件を使用)         | 25°C | -89             |           | -86  |     | dBc   |

| f <sub>IN</sub> = 400 MHz (ナイキスト 3 設定条件を使用)         | 25°C | -80             |           | -77  |     | dBc   |

| スプリアス・フリー・ダイナミック・レンジ(SFDR)                          |      |                 |           |      |     |       |

| f <sub>IN</sub> = 30 MHz (ナイキスト 1 設定条件を使用)          | 25°C | 96              |           | 94   |     | dBc   |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用)          | 25°C | 90              | 83        | 87   |     | dBc   |

$<sup>^4</sup>$ スタンバイ電力は、DC 入力と CLK±ピンを非アクティブ(すなわち AVDD または AGND に接続)にして測定。

|                                                                                   |          | V <sub>REF</sub> = 1 V |      | V <sub>REF</sub> = 1.25 V、<br>デフォルト |     |      |     |     |

|-----------------------------------------------------------------------------------|----------|------------------------|------|-------------------------------------|-----|------|-----|-----|

| パラメータ <sup>1</sup>                                                                | <br>  温度 | Min                    | Typ  | v<br>Max                            | Min | Typ  | Max | 単位  |

|                                                                                   | Full     |                        |      |                                     | 83  |      |     | dBc |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用、ディザ・オン)                                 | 25°C     |                        | 92   |                                     |     | 89   |     | dBc |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用)                                       | 25°C     |                        | 84   |                                     |     | 85   |     | dBc |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用, ディザ・オン)                               | 25°C     |                        | 87   |                                     |     | 85   |     | dBc |

| f <sub>IN</sub> = 305 MHz (ナイキスト 2 設定条件を使用)                                       | 25°C     |                        | 89   |                                     |     | 86   |     | dBc |

| f <sub>IN</sub> = 400 MHz (ナイキスト 3 設定条件を使用)                                       | 25°C     |                        | 80   |                                     |     | 77   |     | dBc |

| その他の高調波 (2 <sup>nd</sup> または 3 <sup>rd</sup> 高調波は含まない)                            |          |                        |      |                                     |     |      |     |     |

| f <sub>IN</sub> = 30 MHz (ナイキスト 1 設定条件を使用)                                        | 25°C     |                        | -101 |                                     |     | -102 |     | dBc |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用)                                        | 25°C     |                        | -99  |                                     |     | -98  | -90 | dBc |

|                                                                                   | Full     |                        |      |                                     |     |      | -86 | dBc |

| f <sub>IN</sub> = 70 MHz (ナイキスト 1 設定条件を使用、ディザ・オン)                                 | 25°C     |                        | -100 |                                     |     | -100 |     | dBc |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用)                                       | 25°C     |                        | -91  |                                     |     | -90  |     | dBc |

| f <sub>IN</sub> = 170 MHz (ナイキスト 2 設定条件を使用, ディザ・オン)                               | 25°C     |                        | -90  |                                     |     | -95  |     | dBc |

| f <sub>IN</sub> = 305 MHz (ナイキスト 2 設定条件を使用)                                       | 25°C     |                        | -98  |                                     |     | -97  |     | dBc |

| f <sub>IN</sub> = 400 MHz (ナイキスト 3 設定条件を使用)                                       | 25°C     |                        | -92  |                                     |     | -91  |     | dBc |

| 2 調波 SFDR                                                                         |          |                        |      |                                     |     |      |     |     |

| $f_{IN} = 70.1 \text{ MHz} (-7 \text{ dBFS}), 72.1 \text{ MHz} (-7 \text{ dBFS})$ | 25°C     |                        |      |                                     |     | 93   |     | dBc |

| f <sub>IN</sub> = 184.12 MHz (-7 dBFS ), 187.12 MHz (-7 dBFS )                    | 25°C     |                        |      |                                     |     | 83   |     | dBc |

| クロストーク <sup>2</sup>                                                               | Full     |                        | 90   |                                     |     | 90   |     | dB  |

| フル・パワー帯域幅 <sup>3</sup>                                                            | 25°C     |                        | 485  |                                     |     | 485  |     | MHz |

| ノイズ帯域幅 <sup>4</sup>                                                               | 25°C     |                        | 650  | •                                   |     | 650  |     | MHz |

<sup>&</sup>lt;sup>1</sup> 完全な定義については AN-835 Application Note「Understanding High Speed ADC Testing and Evaluation」を参照してください。

#### デジタル仕様

特に指定のない限り、AVDD3 = 3.3 V、AVDD = AVDD\_CLK = 1.8 V、SPIVDD = DRVDD = 1.8 V、サンプル・レート = 310 MSPS (クロック入力 = 1240 MHz、AD9652 4 分周)、VIN = -1.0 dBFS 差動入力、2.5 V p-p フルスケール入力範囲、DCS イネーブル、ディザ・オフ。

#### 表 3

|                       |           |      |           |        |             | 単    |

|-----------------------|-----------|------|-----------|--------|-------------|------|

| パラメータ                 | 試験条件/コメント | 温度   | Min       | Тур    | Max         | 位    |

| 差動クロック入力 (CLK+, CLK-) |           |      |           |        |             |      |

| ロジック互換性               |           |      | CMOS      | S/LVDS | S/LVPECL    |      |

| 差動入力電圧                |           | Full | 0.3       |        | 3.6         | V p- |

|                       |           |      |           |        |             | р    |

| 入力電圧範囲                |           | Full | AGND      |        | AVDD_CLK    | V    |

| 内部コモン・モード・バイアス        |           | Full |           | 0.9    |             | V    |

| 入力コモン・モード範囲           |           | Full | 0.9       |        | 1.4         | V    |

| ハイ・レベル入力電流            |           | Full | +10       |        | +145        | μΑ   |

| ロー・レベル入力電流            |           | Full | -155      |        | <b>−</b> 15 | μΑ   |

| 入力容量 <sup>1</sup>     |           | Full |           | 5      |             | pF   |

| 入力抵抗 <sup>1</sup>     |           | Full |           | 10     |             | kΩ   |

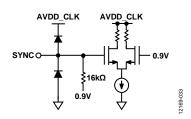

| SYNC 入力               |           |      |           |        |             |      |

| ロジック互換性               |           |      | CMOS/LVDS |        | LVDS        |      |

| 内部バイアス                |           | Full |           | 0.9    |             | ٧    |

| 入力電圧範囲                |           | Full | AGND      |        | AVDD_CLK    | V    |

<sup>&</sup>lt;sup>2</sup> クロストークは、片方のチャンネルに-1.0 dBFS を入力し、他方のチャンネルは入力なしで、100 MHz で測定。

$<sup>^3</sup>$ フルパワー帯域幅とは、適切な ADC 性能が得られる動作帯域幅です。

<sup>&</sup>lt;sup>4</sup>ノイズ帯域幅は、ADC にノイズが混入して内部で減衰されない ADC 入力の−3 dB 帯域幅です。

Data Sheet AD9652

| パラメータ                      | 試験条件/コメント            | 温度   | Min  | Тур  | Max      | 単位 |

|----------------------------|----------------------|------|------|------|----------|----|

| ハイ・レベル入力電圧                 |                      | Full | 1.2  |      | AVDD_CLK | V  |

| ロー・レベル入力電圧                 |                      | Full | AGND |      | 0.6      | V  |

| ハイ・レベル入力電流                 |                      | Full | -15  |      | +110     | μΑ |

| ロー・レベル入力電流                 |                      | Full | -105 |      | +15      | μΑ |

| 入力容量                       |                      | Full |      | 1.5  |          | pF |

| 入力抵抗                       |                      | Full |      | 16   |          | kΩ |

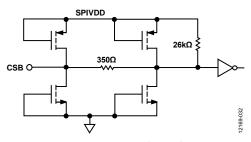

| ロジック入力 (CSB) <sup>2</sup>  |                      |      |      |      |          |    |

| ハイ・レベル入力電圧                 |                      | Full | 1.22 |      | SPIVDD   | V  |

| ロー・レベル入力電圧                 |                      | Full | 0    |      | 0.6      | V  |

| ハイ・レベル入力電流                 |                      | Full | -65  |      | +65      | μΑ |

| ロー・レベル入力電流                 |                      | Full | -135 |      | 0        | μΑ |

| 入力容量                       |                      | Full |      | 26   |          | kΩ |

| 入力抵抗                       |                      | Full |      | 2    |          | pF |

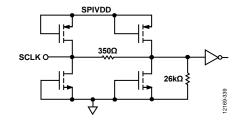

| ロジック入力 (SCLK) <sup>3</sup> |                      |      |      |      |          |    |

| ハイ・レベル入力電圧                 |                      | Full | 1.22 |      | SPIVDD   | V  |

| ロー・レベル入力電圧                 |                      | Full | 0    |      | 0.6      | V  |

| ハイ・レベル入力電流                 |                      | Full | 0    |      | 110      | μΑ |

| ロー・レベル入力電流                 |                      | Full | -60  |      | +50      | μΑ |

| 入力容量                       |                      | Full |      | 26   |          | kΩ |

| 入力抵抗                       |                      | Full |      | 2    |          | pF |

| ロジック入力 (SDIO)²             |                      |      |      |      |          |    |

| ハイ・レベル入力電圧                 |                      | Full | 1.22 |      | SPIVDD   | V  |

| ロー・レベル入力電圧                 |                      | Full | 0    |      | 0.6      | V  |

| ハイ・レベル入力電流                 |                      | Full | -65  |      | +70      | μΑ |

| ロー・レベル入力電流                 |                      | Full | -135 |      | 0        | μΑ |

| 入力容量                       |                      | Full |      | 26   |          | kΩ |

| 入力抵抗                       |                      | Full |      | 5    |          | pF |

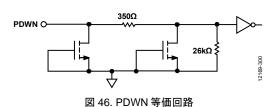

| ロジック入力 (PDWN)³             |                      |      |      |      |          |    |

| ハイ・レベル入力電圧                 |                      | Full | 1.22 |      | DRVDD    | V  |

| ロー・レベル入力電圧                 |                      | Full | 0    |      | 0.6      | V  |

| ハイ・レベル入力電流                 |                      | Full | -80  |      | +190     | μΑ |

| ロー・レベル入力電流                 |                      | Full | -145 |      | +130     | μΑ |

| 入力容量                       |                      | Full |      | 26   |          | kΩ |

| 入力抵抗                       |                      | Full |      | 5    |          | pF |

| デジタル出力                     |                      |      |      |      |          |    |

| LVDS データ及び OR± 出力          | 公称 100 Ω 差動終端を仮<br>定 |      |      |      |          |    |

| ANSI モード                   |                      |      |      |      |          |    |

| 差動出力電圧 (Vop)               | 最大設定値、デフォルト          | Full | 310  | 350  | 450      | mV |

| 出力オフセット電圧 (Vos)            |                      | Full | 1.15 | 1.22 | 1.35     | V  |

| Reduced Swing モード          |                      |      |      |      |          |    |

| 差動出力電圧 (V <sub>OD</sub> )  | 最小設定値                | Full | 150  | 200  | 280      | mV |

| 出力オフセット電圧 (Vos)            |                      | Full | 1.15 | 1.22 | 1.35     | V  |

$<sup>^1</sup>$ I 入力容量/抵抗は、1本の差動入力ピンと AGND との間の実効容量/抵抗です。  $^2$ I 内部の弱いプルアップ。.

## スイッチング仕様

### 表 4

| パラメータ                                  | 試験条件/コメント   | 温度   | Min Typ | Max  | 単位     |

|----------------------------------------|-------------|------|---------|------|--------|

| クロック入力パラメータ (CLK±)                     |             |      |         |      |        |

| 入力クロック・レート                             |             | Full | 80      | 1240 | MHz    |

| 変換レート <sup>1</sup>                     |             | Full | 80      | 310  | MSPS   |

| 周期−1 分周モード (t <sub>CLK</sub> )         |             | Full | 3.2     |      | ns     |

| ハイ・レベルの最小パルス幅 (tCH)                    |             |      |         |      |        |

| 1 分周モード                                | DCS イネーブル   | Full | 0.8     |      | ns     |

|                                        | DCS ディスエーブル | Full | 1.3     |      | ns     |

| 2分周モード~8分周モード                          |             | Full | 0.8     |      | ns     |

| アパーチャ遅延 (t <sub>A</sub> )              |             | Full | 1.0     |      | ns     |

| アパーチャ不確定性 (ジッタ、t」)                     |             | Full | 0.1     |      | ps rms |

| データ出力パラメータ                             |             |      |         |      |        |

| LVDS モード                               |             |      |         |      |        |

| データ伝播遅延 (t <sub>PD</sub> )             |             | Full | 290     |      | ps     |

| DCO± 伝播遅延 (t <sub>DCO</sub> )          |             | Full | 290     |      | ps     |

| DCO±-to-Data スキュー (t <sub>SKEW</sub> ) |             | Full | 0       |      | ns     |

| パイプライン遅延(レイテンシ)                        |             | Full | 26      |      | Cycles |

| ウェイクアップ時間                              | スタンバイから     | Full | 100     |      | μs     |

|                                        | パワーダウンから    | Full | 1       |      | sec    |

| 範囲外からの回復時間                             |             | Full | 3       |      | Cycles |

<sup>1</sup>変換レートは分周後のクロック・レートです。

## タイミング仕様

#### 表 5

| パラメータ                 | 試験条件/コメント                                                             | Min | Тур | Max | 単位 |

|-----------------------|-----------------------------------------------------------------------|-----|-----|-----|----|

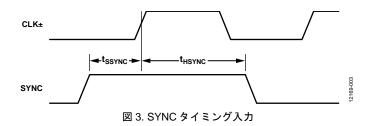

| SYNC のタイミング<br>条件     |                                                                       |     |     |     |    |

| t <sub>SSYNC</sub>    | SYNC から CLK+の立ち上がりエッジまでのセットアップ・タイム                                    |     | 0.1 |     | ns |

| t <sub>HSYNC</sub>    | SYNC から CLK+の立ち上がりエッジまでのホールド・タイム                                      |     | 0.1 |     | ns |

| SPI のタイミング条<br>件      |                                                                       |     |     |     |    |

| t <sub>DS</sub>       | データと SCLK の立ち上がりエッジとの間のセットアップ・タイム                                     | 2   |     |     | ns |

| $t_{DH}$              | データと SCLK の立ち上がりエッジとの間のホールド・タイム                                       | 2   |     |     | ns |

| t <sub>CLK</sub>      | SCLKの周期                                                               | 40  |     |     | ns |

| ts                    | CSB と SCLK との間のセットアップ・タイム                                             | 2   |     |     | ns |

| t <sub>H</sub>        | CSB と SCLK との間のホールド・タイム                                               | 2   |     |     | ns |

| t <sub>HIGH</sub>     | SCLK ハイ・レベルの最小時間                                                      | 10  |     |     | ns |

| $t_{LOW}$             | SCLK ロー・レベルの最小時間                                                      | 10  |     |     | ns |

| ten_sdio              | SCLK の立下りエッジを基準として、SDIO ピンを入力から出力に切り<br>換えるために必要な時間 (タイミング図には示されていない) | 10  |     |     | ns |

| t <sub>DIS_SDIO</sub> | SCLK の立下りエッジを基準として、SDIO ピンを出力から入力に切り<br>換えるために必要な時間 (タイミング図には示されていない) | 10  |     |     | ns |

<sup>&</sup>lt;sup>3</sup>内部の弱いプルダウン。

| パラメータ                | 試験条件/コメント                                                          | Min | Тур | Max | 単位 |

|----------------------|--------------------------------------------------------------------|-----|-----|-----|----|

| t <sub>SPI_RST</sub> | パワーアップの後、SPI アクセスが可能となるまでのハードまたはソフト・リセットのために必要な時間(タイミング図には示されていない) | 500 |     |     | μѕ |

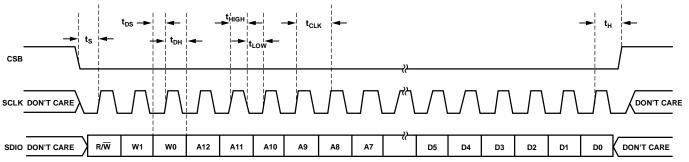

### タイミング図

図 4. シリアル・ポート・インタフェースのタイミング図

# 絶対最大定格

#### 表 6

| _ 表 6                     |                            |

|---------------------------|----------------------------|

| パラメータ                     | 定格                         |

| 電気的条件                     |                            |

| AGND を基準とする AVDD3         | -0.3 V∼+3.6 V              |

| AGND を基準とする AVDD_CLK      | -0.3 V∼+2.0 V              |

| AGND を基準とする AVDD          | -0.3 V∼+2.0 V              |

| AGND を基準とする DRVDD         | -0.3 V∼+2.0 V              |

| AGND を基準とする SPIVDD        | -0.3 V∼+3.6 V              |

| AGND を基準とする               | 1.2 V∼3.0 V                |

| VIN+A/VIN+B、VIN-A/VIN-B   |                            |

| AGND を基準とする CLK+、<br>CLK- | -0.3 V∼AVDD_CLK +<br>0.2 V |

| AGND を基準とする SYNC          | -0.3 V∼AVDD_CLK +<br>0.2 V |

| AGND を基準とする VCM           | -0.3 V $\sim$ AVDD + 0.2 V |

| AGND を基準とする CSB           | -0.3 V∼SPIVDD + 0.3<br>V   |

| AGND を基準とする SCLK          | -0.3 V∼SPIVDD + 0.3<br>V   |

| AGND を基準とする SDIO          | -0.3 V∼SPIVDD + 0.3<br>V   |

| AGND を基準とする PDWN          | -0.3 V∼DRVDD + 0.3<br>V    |

| AGND を基準とする OR+/OR-       | -0.3 V~DRVDD + 0.3<br>V    |

| AGND を基準とする D0±~D15±      | -0.3 V∼DRVDD + 0.3<br>V    |

| AGND を基準とする DCO±          | -0.3 V∼DRVDD + 0.3<br>V    |

| 環境条件                      |                            |

| 動作温度範囲(周囲)                | -40°C∼+85°C                |

| バイアス時の最高ジャンクショ            | 125°C                      |

| ン温度                       |                            |

| 保存温度範囲(周囲)                | −65°C ~150°C               |

上記の絶対最大定格またはそれ以上のストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作

の節に記載する規定値以上での製品の動作を定めたものではありません。製品を長時間最大動作条件以上で動作させると製品の信頼性に影響を与えます。

#### 熱特性

$\theta_{JA}$  (Typ) は、厚いグラウンド・プレーンを持つ JEDEC 51-2 規格の 4 層 PCB と、8 層 PCB の両方に対して規定されます。8 層 PCB は 2 オンスの銅配線層(MI と M8)、1 オンスの内部銅配線層、及び M2、M5、及び M7 層へのヴィア接続を持っています。表 7 に示されるように、空気流を与えると熱放散が大きくなり、 $\theta_{JA}$  が小さくなります。また、メタル・パターン、スルー・ホール、グラウンド・プレーン、電源プレーンとパッケージ・ピンが直接接触する場合、これらのメタルによっても  $\theta_{JA}$  が小さくなります。

#### 表 7. 熱抵抗

| パッケージ・タイプ                   | 空気流<br>の速度<br>(m/sec) | ボードのタイ<br>プ        | $\theta_{\rm JA}^{\ 2}$ | 単位   |

|-----------------------------|-----------------------|--------------------|-------------------------|------|

| 144 ボール                     | 0                     | 8層 PCB             | 15.8                    | °C/W |

| CSP_BGA                     | 1.0                   | 8層 PCB             | 13.9                    | °C/W |

| 10 mm × 10 mm<br>(BC-144-6) | 0                     | JEDEC <sup>1</sup> | 21.7                    | °C/W |

| (50 144 0)                  | 1.0                   | JEDEC <sup>1</sup> | 19.2                    | °C/W |

<sup>&</sup>lt;sup>1</sup> JEDEC 51-7 と JEDEC 25-5 2S2P テスト・ボードに準拠。

#### ESD に関する注意

SD (静電放電) の影響を受けやすいデバイスです。 電荷を帯びたデバイスや回路ボードは、検知されないまま放 電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性がありま す。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

<sup>&</sup>lt;sup>2</sup> JEDEC JESD51-2 (自然空冷)または JEDEC JESD51-6 (強制空冷)に準拠。

# ピン配置及びピン機能説明

#### AD9652 TOP VIEW (Not to Scale)

|   | 1                  | 2     | 3                  | 4     | 5      | 6            | 7                  | 8                  | 9               | 10             | 11            | 12                              |

|---|--------------------|-------|--------------------|-------|--------|--------------|--------------------|--------------------|-----------------|----------------|---------------|---------------------------------|

| Α | RBIAS              | (VCM) | AVDD3              | √(N+B | √iÑ-B  | AVDD3        | AVDD3              | VIN-A              | VIN+A           | AVDD3          | SENSE         | VREF                            |

| В | ÁGND               | AVDD3 | AVDD3              | ÁGNÞ  | ÁGNÞ   | AVDD3        | AVDD3              | ÁGND               | ÁGNÞ            | AVDD3          | AVDD3         | ÁGNÞ                            |

| С | ÁGND               | ÁGND  | ÁVDD               | ÁGNÞ  | ÁGNÞ   | AVDD_<br>CLK | AVDD_              | ÁGND               | ÁGND            | ÁVDD           | ÁGNÞ          | ÁGNÞ                            |

| D | ĆĹĸ-               | ÁGND  | ÁVDD               | ÁGNÞ  | ÁGNÞ   | AVDD-<br>CLK | AVDD<br>CLK        | ÁGND               | ÁGND            | ÁVDD           | ÁGNÞ          | (CSB)                           |

| E | ĆĹK)               | ÁGND  | ÁVDD               | ĄGND  | ÁGNÞ   | CLK<br>AVDD  | CLK<br>CLK         | ÁGND               | ÁGND            | ÁVDD           | ĄĠŊĎ          | \$DIO                           |

| F | (EST)              | ÁGND  | ÁVDÒ               | ÁGNÞ  | ÁGNÞ   | AVDD_        | AVDD_              | ÁGND               | ÁGND            | ÁVDÒ           | ÁGNÞ          | \$CLK                           |

| G | \$YNC              | ÁGND  | ÁVDD               | ÁGNÞ  | ÁGNÞ   | ÁVDÒ         | ÁVDÒ               | ĄGND               | ÁGNÞ            | ÁVDD           | ÁGND          | (OR+)                           |

| н | ROWN               | ÁGND  | ÁVDD               | ĄĠŊĎ  | ÁGNÞ   | ÁVDD         | ÁVDÒ               | ĄGND               | ÁGNÞ            | ÁVDD           | ĄGND          | (OR-)                           |

| J | ( <del>D0-</del> ) | (D0+) | DRGND              | DRGND | DRGND  | DRGND        | DRGND              | ( <del>C</del> O+  | DRGND           | DRGND          | (D15+)        | ( <del>)</del> 15-)             |

| к | (D1-)              | (D1+) | DRVDD              | DRVDD | SPIVDD | DRVDD        | DRVDD              | ( <del>CO)</del>   | DRVDD           | DRVDD          | <u>(014+)</u> | ( <del>)</del> 14-)             |

| L | (D2+)              | (D3+) | ( <del>D4+</del> ) | (D5+) | (D6+)  | (D7+)        | (D8+)              | ( <del>D9+</del> ) | (D10+)          | (D11+)         | (D12+)        | ( <del>0</del> 13+)             |

| М | (D2-)              | (D3-) | ( <del>04-</del> ) | (D5-) | (D6-)  | (D7-)        | ( <del>D8-</del> ) | ( <del>D9-</del> ) | ( <u>b10</u> -) | ( <u>þ11</u> - | (D12-)        | ( <del>0</del> 13 <del>-)</del> |

|   |                    |       |                    |       |        |              |                    |                    |                 |                |               |                                 |

図 5.ピン配置

#### 表 8. ピン機能の説明

| 衣 0. こプ放化の武明                                                               | 火 6. こン液形の武功 |     |                                             |  |  |

|----------------------------------------------------------------------------|--------------|-----|---------------------------------------------|--|--|

| ピン番号                                                                       | 記号           | タイプ | 説明                                          |  |  |

| ADC 電源                                                                     |              |     |                                             |  |  |

| K5                                                                         | SPIVDD       | 電源  | シリアル・インタフェース・ロジック電源(1.8 V Typ.、3.3 V オプション) |  |  |

| K3, K4, K6, K7, K9, K10                                                    | DRVDD        | 電源  | デジタル出力ドライバ電源(1.8 V 公称)                      |  |  |

| A3, A6, A7, A10, B2, B3, B6,<br>B7, B10, B11                               | AVDD3        | 電源  | 3.3 V アナログ電源(3.3 V 公称)                      |  |  |

| C6, C7, D6, D7, E6, E7, F6, F7                                             | AVDD_CLK     | 電源  | クロック回路用 1.8 V アナログ電源(1.8 V 公称)              |  |  |

| C3, C10, D3, D10, E3, E10,<br>F3, F10, G3, G6, G7, G10,<br>H3, H6, H7, H10 | AVDD         | 電源  | 1.8 V アナログ電源(1.8 V 公称)                      |  |  |

| <br>ピン番号                                                                                                                                                                               | 記号    | タイプ            | 説明                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|-----------------------------------------------------------------------------------------------------|

| B1, B4, B5, B8, B9, B12, C1, C2, C4, C5, C8, C9, C11, C12, D2, D4, D5, D8, D9, D11, E2, E4, E5, E8, E9, E11, F2, F4, F5, F8, F9, F11, G2, G4, G5, G8, G9, G11, H2, H4, H5, H8, H9, H11 | AGND  | アナログ・グ<br>ラウンド | AVDD3、AVDD_CLK、及び AVDD 用アナログ・グラウンド<br>基準                                                            |

| J3                                                                                                                                                                                     | DRGND | デジタル・グ<br>ラウンド | デジタル及び出力ドライバ・グラウンド基準                                                                                |

| J4                                                                                                                                                                                     | DRGND | デジタル・グラウンド     | デジタル及び出力ドライバ・グラウンド基準                                                                                |

| J5                                                                                                                                                                                     | DRGND | デジタル・グ<br>ラウンド | デジタル及び出力ドライバ・グラウンド基準                                                                                |

| J6                                                                                                                                                                                     | DRGND | デジタル・グラウンド     | デジタル及び出力ドライバ・グラウンド基準                                                                                |

| J7                                                                                                                                                                                     | DRGND | デジタル・グ<br>ラウンド | デジタル及び出力ドライバ・グラウンド基準                                                                                |

| J9                                                                                                                                                                                     | DRGND | デジタル・グ<br>ラウンド | デジタル及び出力ドライバ・グラウンド基準                                                                                |

| J10                                                                                                                                                                                    | DRGND | デジタル・グラウンド     | デジタル及び出力ドライバ・グラウンド基準                                                                                |

| ADC アナログ                                                                                                                                                                               |       |                |                                                                                                     |

| A9                                                                                                                                                                                     | VIN+A | 入力             | 差動アナログ入力ピン(+)、チャンネル A                                                                               |

| A8                                                                                                                                                                                     | VIN-A | 入力             | 差動アナログ入力ピン(-)、チャンネル A                                                                               |

| A4                                                                                                                                                                                     | VIN+B | 入力             | 差動アナログ入力ピン(+)、チャンネル B                                                                               |

| A5                                                                                                                                                                                     | VIN-B | 入力             | 差動アナログ入力ピン <b>(-)</b> 、チャンネル B                                                                      |

| A2                                                                                                                                                                                     | VCM   | 出力             | アナログ入力のコモン・モード・レベル・バイアス出力。0.1 □ μF のコンデンサでこのピンをグラウンドへデカップリング してください。                                |

| A1                                                                                                                                                                                     | RBIAS | 出力             | 外部バイアス抵抗接続。このピンとアナログ・グラウンド (AGND) との間に 10 kΩの抵抗を接続する必要があります。                                        |

| A12                                                                                                                                                                                    | VREF  | 入力/出力          | リファレンス電圧入力/出力                                                                                       |

| A11                                                                                                                                                                                    | SENSE | 入力             | リファレンス電圧モード・セレクト (表 <b>12</b> 参照 <b>)</b> 。                                                         |

| E1                                                                                                                                                                                     | CLK+  | 入力             | <b>ADC</b> クロック入力(+側)。                                                                              |

| D1                                                                                                                                                                                     | CLK-  | 入力             | <b>ADC</b> クロック入力(一側)。                                                                              |

| デジタル入力                                                                                                                                                                                 |       |                |                                                                                                     |

| F1                                                                                                                                                                                     | TEST  | 入力             | プルダウン。未使用デジタル入力。 <b>50</b> □ <b>Ω</b> の抵抗でこのピンをグラウンドヘプルダウンしてください。                                   |

| G1                                                                                                                                                                                     | SYNC  | 入力             | デジタル入力クロック同期ピン。使用しない場合はロー・レ<br>ベルに固定。                                                               |

| H1                                                                                                                                                                                     | PDWN  | 入力             | パワーダウン入力(アクティブ・ハイ)。このピンの動作は<br>SPI モードに依存し、パワーダウンまたはスタンバイに設定<br>することができます ( Table 17 内の抵抗 0x08 参照)。 |

| デジタル出力                                                                                                                                                                                 |       |                |                                                                                                     |

| J2                                                                                                                                                                                     | D0+   | 出力             | チャンネル A/チャンネル B LVDS 出力データ 0- (+側、<br>LSB)。                                                         |

| J1                                                                                                                                                                                     | D0-   | 出力             | チャンネル A/チャンネル B LVDS 出力データ 0- (-側、<br>LSB)。                                                         |

| K2                                                                                                                                                                                     | D1+   | 出力             | チャンネル A/チャンネル B LVDS 出力データ 1- (+側)。                                                                 |

| K1                                                                                                                                                                                     | D1-   | 出力             | チャンネル A/チャンネル B LVDS 出力データ 1- (一側)。                                                                 |

| ピン番号        | 記号   | タイプ   | 説明                                        |

|-------------|------|-------|-------------------------------------------|

| L1          | D2+  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 2- (+側)。       |

| M1          | D2-  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 2- (-側)。       |

| L2          | D3+  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 3- (+側)。       |

| M2          | D3-  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 3- (-側)。       |

| L3          | D4+  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 4- (+側)。       |

| M3          | D4-  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 4- (-側)。       |

| L4          | D5+  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 5- (+側)。       |

| M4          | D5-  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 5 (-側)。        |

| L5          | D6+  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 6 (+側)。        |

| M5          | D6-  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 6 (一側)。        |

| L6          | D7+  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 7 (+側)。        |

| M6          | D7-  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 7 (-側)。        |

| L7          | D8+  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 8 (+側)。        |

| M7          | D8-  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 8 (-側)。        |

| L8          | D9+  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 9 (+側)。        |

| M8          | D9-  | 出力    | チャンネル A/チャンネル B LVDS 出力データ 9 (-側)。        |

| L9          | D10+ | 出力    | チャンネル A/チャンネル B LVDS 出力データ 10 (+側)。       |

| M9          | D10- | 出力    | チャンネル A/チャンネル B LVDS 出力データ 10 (-側)。       |

| L10         | D11+ | 出力    | チャンネル A/チャンネル B LVDS 出力データ 11 (+側)。       |

| M10         | D11- | 出力    | チャンネル A/チャンネル B LVDS 出力データ 11 (一側)。       |

| L11         | D12+ | 出力    | チャンネル A/チャンネル B LVDS 出力データ 12 (+側)。       |

| M11         | D12- | 出力    | チャンネル A/チャンネル B LVDS 出力データ 12 (-側)。       |

| L12         | D13+ | 出力    | チャンネル A/チャンネル B LVDS 出力データ 13 (+側)。       |

| M12         | D13- | 出力    | チャンネル A/チャンネル B LVDS 出力データ 13(-側)。        |

| K11         | D14+ | 出力    | チャンネル A/チャンネル B LVDS 出力データ 14 (+側)。       |

| K12         | D14- | 出力    | チャンネル A/チャンネル B LVDS 出力データ 14 (-側)。       |

| J11         | D15+ | 出力    | チャンネル A/チャンネル B LVDS 出力データ 15 (+側、 MSB)。  |

| J12         | D15- | 出力    | チャンネル A/チャンネル B LVDS 出力データ 15 (-側、        |

| 312         | D10  | ЩЛ    | MSB)。                                     |

| G12         | OR+  | 出力    | チャンネル A/チャンネル B LVDS 範囲外(+側)。             |

| H12         | OR-  | 出力    | チャンネル A/チャンネル B LVDS 範囲外(一側)。             |

| J8          | DCO+ | 出力    | チャンネル A/チャンネル B LVDS データ・クロック出力-<br>(+側)。 |

| K8          | DCO- | 出力    | チャンネル A/チャンネル B LVDS データ・クロック出力-<br>(一側)。 |

| SPI 制御      |      |       | V 1/4/ 0                                  |

| F12         | SCLK | 入力    | SPI シリアル・クロック                             |

| E12         | SDIO | 入力/出力 | SPI のシリアル・データ入力/出力。                       |

| D12         | CSB  | 入力    | SPIチップ・セレクト(アクティブ・ロー)。このピンはこの             |

| <i>5</i> 12 | 005  |       | ピンはパワーアップ時はハイ・レベルにプルアップする必要があります。         |

# 代表的な性能特性

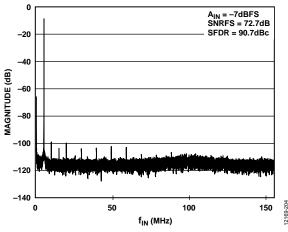

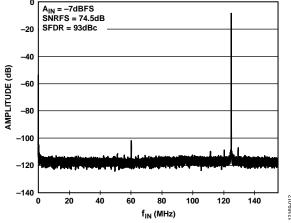

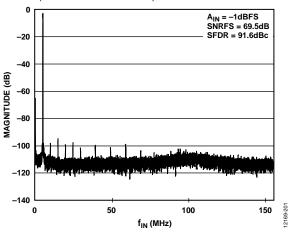

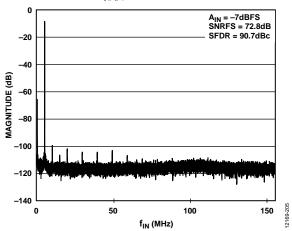

特に指定のない限り、AVDD3 = 3.3 V、AVDD = AVDD\_CLK = 1.8 V、SPIVDD = DRVDD = 1.8 V、サンプル・レート = 310 MSPS (クロック入力 = 1240 MHz、AD9652 4 分周)、VIN = -1.0 dBFS 差動、VREF = 1.25 V、DCS イネーブル、ディザ・オフ。

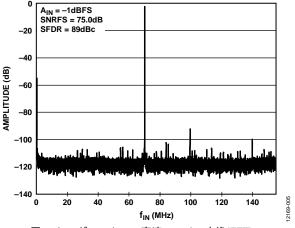

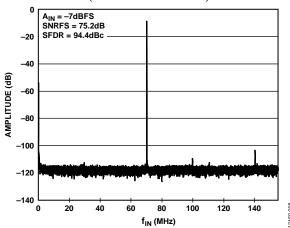

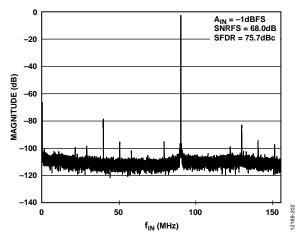

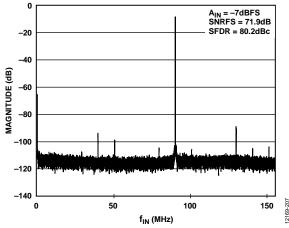

図 6. シングル・トーン高速フーリエ変換(FFT)、 f<sub>IN</sub> = 70.1 MHz、(NSD = −156.7 dBFS/Hz)

図 7. シングル・トーン高速フーリエ変換(FFT)、f<sub>IN</sub> = 70.1 MHz (NSD = -156.7 dBFS/Hz)

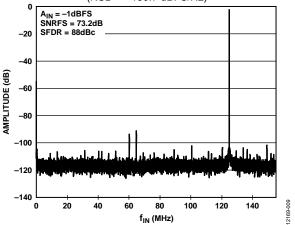

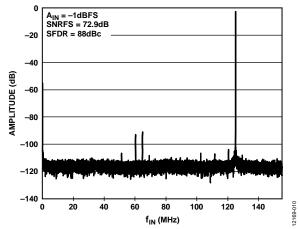

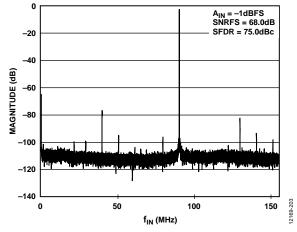

図 8. シングル・トーン FFT、f<sub>IN</sub> = 185 MHz at -1 dBFS (NSD = -155.2 dBFS/Hz)、抵抗 0x22A = 0x01

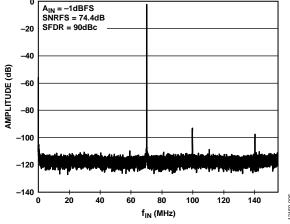

図 9. シングル・トーン FFT、f<sub>IN</sub> = 70.1 MHz、ディザ・オン、 (NSD = −156.3 dBFS/Hz)

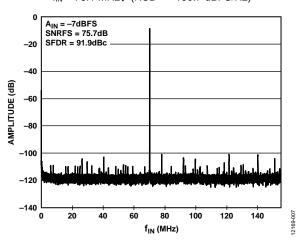

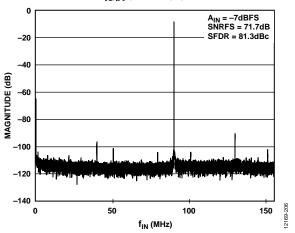

図 10. シングル・トーン FFT、 $f_{IN}$  = 70.1 MHz at -7 dBFS、ディザ・オン (NSD = -157.1 dBFS/Hz)

図 11. シングル・トーン FFT、 $f_{\text{IN}}$  = 185 MHz at -1 dBFS、ディザ・オン (NSD = -154.9 dBFS/Hz)、抵抗 0x22A = 0x01

図 12. シングル・トーン FFT、f<sub>IN</sub> = 185 MHz at -7 dBFS (NSD = -156.9 dBFS/Hz)、抵抗 0x22A = 0x01

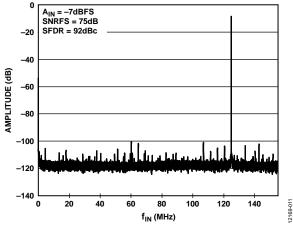

図 13. FFT、f<sub>IN</sub> = 305 MHz、A<sub>IN</sub> = −1 dBFS、ディザ・オフ、 抵抗 0x22A = 0x01

図 14. FFT、f<sub>IN</sub> = 305 MHz、A<sub>IN</sub> = -7 dBFS、ディザ・オフ、 抵抗 0x22A = 0x01

図 15. シングル・トーン FFT、f<sub>IN</sub> = 185 MHz at -7 dBFS (NSD = -156.4 dBFS/Hz)、抵抗 0x22A = 0x01

図 16. FFT、f<sub>IN</sub> = 305 MHz、A<sub>IN</sub> = −1 dBFS、ディザ・オン、 抵抗 0x22A = 0x01

図 17. FFT、f<sub>IN</sub> = 305 MHz、A<sub>IN</sub> = -7 dBFS、ディザ・オン、 抵抗 0x22A = 0x01

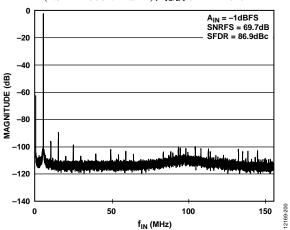

図 18. FFT、f<sub>IN</sub> = 400 MHz、A<sub>IN</sub>= -1 dBFS、ディザ・オフ、 抵抗 0x22A = 0x02

図 19. FFT、f<sub>IN</sub> = 400 MHz、A<sub>IN</sub> = -7 dBFS、ディザ・オフ、 抵抗 0x22A = 0x02

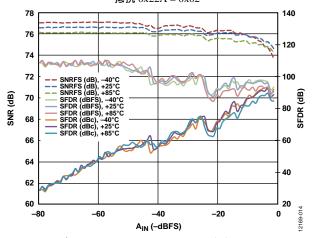

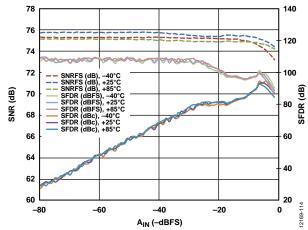

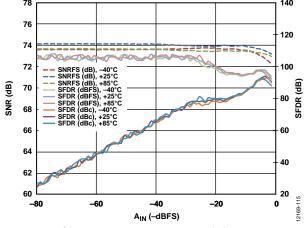

図 20. シングル・トーン SNR/SFDR 対入力振幅( $A_{IN}$ )、 $f_{IN}$  = 90.1 MHz、 $V_{REF}$  = 1.25 V、パラメータ:温度、ディザ・オフ

図 21. FFT、f<sub>IN</sub> = 400 MHz、A<sub>IN</sub> = -1 dBFS、ディザ・オン、 抵抗 0x22A = 0x02

図 22. FFT、f<sub>IN</sub> = 400 MHz、A<sub>IN</sub> = -7 dBFS、ディザ・オン、 抵抗 0x22A = 0x02

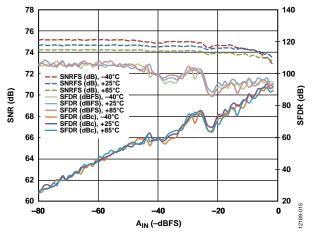

図 23. シングル・トーン SNR/SFDR 対入力振幅( $A_{IN}$ )、 $f_{IN}$  = 90.1 MHz、 $V_{REF}$  = 1.25 V、パラメータ:温度、ディザ・オン

図 24. シングル・トーン SNR/SFDR 対入力振幅(A<sub>IN</sub>)、f<sub>IN</sub> = 90.1 MHz、VREF = 1.0 V、パラメータ:温度、ディザ・オフ

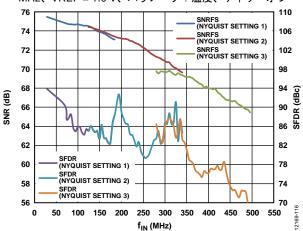

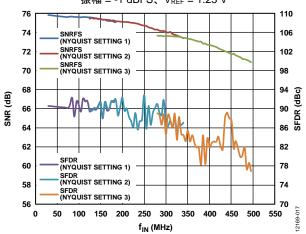

図 25. シングル・トーン SNR/SFDR 対入力周波数周波数(f<sub>N</sub>)、 振幅 = -1 dBFS、V<sub>REF</sub> = 1.25 V

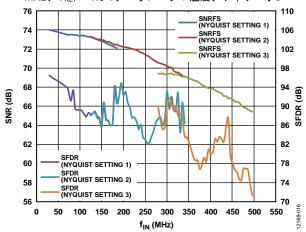

図 26. シングル・トーン SNR/SFDR 対入力周波数周波数( $f_{IN}$ )、振幅 = -7 dBFS、 $V_{REF}$  = 1.25 V

図 27. シングル・トーン SNR/SFDR 対入力振幅(A<sub>IN</sub>)、f<sub>IN</sub> = 90.1 MHz、V<sub>REF</sub> = 1.0 V、パラメータ:温度、ディザ・オン

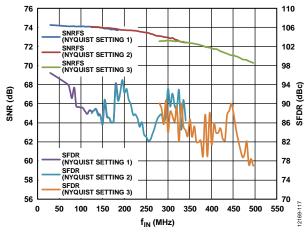

図 28. シングル・トーン SNR/SFDR 対入力周波数周波数(f<sub>IN</sub>)、 振幅 = -1 dBFS、V<sub>REF</sub> = 1.0 V

図 29. シングル・トーン SNR/SFDR 対入力周波数周波数(f<sub>iN</sub>)、 振幅 = -7 dBFS、V<sub>REF</sub> = 1.0 V

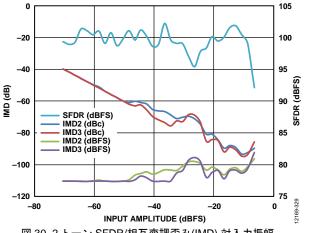

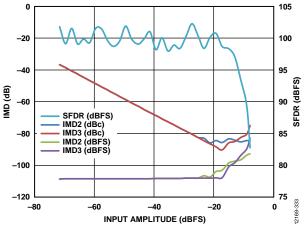

図 30. 2 トーン SFDR/相互変調歪み(IMD) 対入力振幅、 f<sub>IN</sub> = 70.1 MHz 及び 72.1 MHz、ディザ・オフ

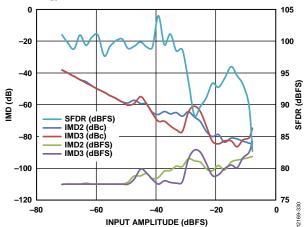

図 31. 2 トーン SFDR/IMD 対入力振幅、f<sub>IN</sub> = 184 MHz 及び 187 MHz、ディザ・オフ、抵抗 0x22A = 0x01

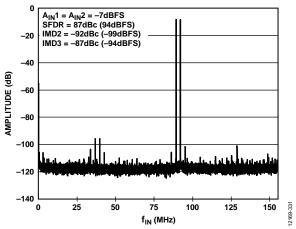

図 32. 2 トーン FFT、 $f_{\text{IN}}$  = 89.1 MHz 及び 92.1 MHz、  $V_{\text{REF}}$  = 1.25 V

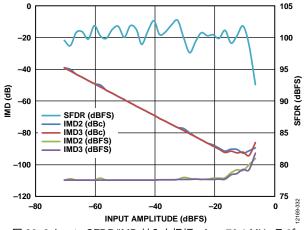

図 33. 2 トーン SFDR/IMD 対入力振幅、f<sub>IN</sub> = 70.1 MHz 及び 72.1 MHz、ディザ・オン

図 34. 2 トーン SFDR/IMD 対入力振幅、fIN = 184 MHz 及び 187 MHz、ディザ・オン、抵抗 0x22A = 0x01

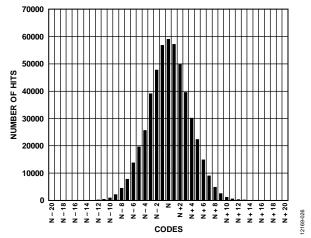

図 35. グラウンド時入力ヒストグラム

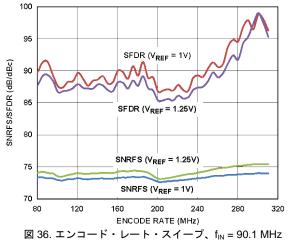

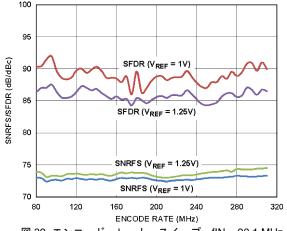

図 36. エンコード・レート・スイープ、f<sub>IN</sub> = 90.1 MHz at -7 dBFS、V<sub>REF</sub> = 1.25 V 及び 1.0 V

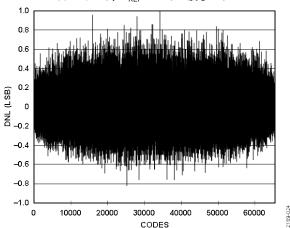

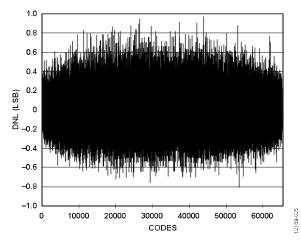

図 37. ディザ・オフ時の DNL、 $f_{IN}$  = 30 MHz

図 38. ディザ・オン時の DNL、f<sub>IN</sub> = 30 MHz

図 39. エンコード・レート・スイープ、fIN = 90.1 MHz at -1 dBFS、VREF = 1.25 V 及び 1.0 V

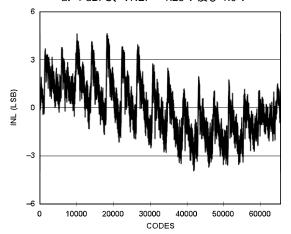

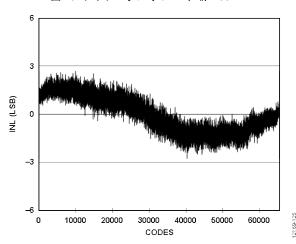

図 40. ディザ・オフ時の INL、f<sub>IN</sub> = 30 MHz

図 41. ディザ・オン時の INL、f<sub>IN</sub> = 30 MHz

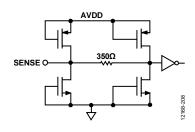

# 等価回路

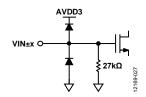

図 42. アナログ入力段等価回路

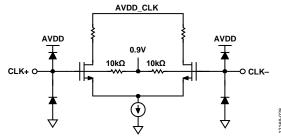

図 43. クロック入力等価回路

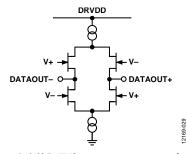

図 44. LVDS 出力等価回路 (DCO±、OR±、及び D0± ~D15±)

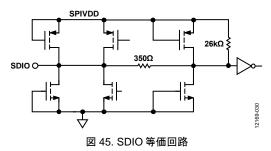

図 47. SLCK 入力等価回路

図 48. CSB 入力等価回路

図 49. SYNC 入力等価回路

図 50. SENSE 等価回路

図 51. VREF 等価回路

# 動作原理

AD9652 は、デュアル、16 ビットの ADC で、最大 310 MSPS のサンプリング速度を持っています。AD9652 は、広帯域性能が要求される通信及び計測機器のアプリケーション用に設計されています。

デュアル ADC デザインは、2つの別のアンテナから受信された同じキャリアに対して ADC が同じ動作を行うダイバーシティー受信回路で使用することができます。ADC は独立なアナログ入力に対しても使うことができます。ADC 入力に適切なローパス・フィルタまたはバンドパス・フィルタを使って、ADC 性能をほとんど損なうことなく、DC~310 MHz の周波数をサンプルすることができます。485 MHz (Typ.)アナログ入力に対する処理が許容されていますが、ADC ノイズと歪みが増える犠牲が伴います。

同期機能を内蔵しているため、複数デバイス間でタイミングを 同期させることができます。

AD9652 の設定と制御は、3線の SPI 互換シリアル・インターフェースを使って行います。

#### ADC のアーキテクチャ

AD9652 はデュアルのバッファつきフロントエンド・サンプル・アンド・ホールド回路と、パイプライン化されたスイッチド・キャパシタ型 ADC から構成されています。AD9652 は、パイプライン化されたコンバータに加えて、初段の性能を最大限に高めるための新しい入力回路の長所を利用したユニークなアーキテクチャを採用しています。

各ステージからの量子化された出力は、デジタル補正ロジックで結合されて最終的に16ビットの結果を生成します。パイプライン化されたアーキテクチャにより、新しい入力サンプルに対して最初のステージが動作し、残りのステージは先行しているサンプルに対して動作することができます。サンプリングはクロックの立ち上がりエッジで行われます。

最終ステージ以外のパイプラインの各ステージは、スイッチド・コンデンサ DAC に接続された低分解能のフラッシュ ADCとステージ間残留乗算型 DAC(MDAC)により構成されています。MDACは、再生された DAC 出力とパイプライン内の次のステージに対するフラッシュ入力の差を増幅します。各ステージ内で冗長な1ビットを使って、フラッシュ誤差のデジタル補正を可能にしています。最終ステージはフラッシュ ADC のみで構成されています。

AD9652 は、各パイプライン・ステージで発生する内部誤差を連続的に追跡し、誤差を補正することによって様々な動作条件に対して連続的な動作を保証する内部デジタル信号処理回路を備えています。この方法は、補正データのリセット及び収集を行うための余分なスタートアップ時間を必要とします。

各チャンネルの入力ステージには差動サンプリング回路が含まれており、差動モードまたはシングルエンド・モードで AC 結合または DC 結合することができます。出力ステージのブロックで、データの整列、誤差補正、出力バッファへの出力が行われます。出力バッファの電圧は、デジタル出力ノイズをアナログ・コアから隔離するためにアナログ回路とは別の電源から供給されます。パワーダウン時には、出力バッファは高インピーダンス状態になります。

#### アナログ入力に対する考慮

AD9652 のアナログ入力は、高性能な差動バッファになっています。このバッファは、差動入力信号を処理する際に最適性能

が得られるようにデザインされています。入力バッファは一貫 した入力インピーダンスを提供し、アナログ入力のインタフェ ースを容易にします。

差動アナログ入力インピーダンスは約 54 kΩの抵抗と 5.8 pF の並列容量から構成されます。個別素子の受動ネットワークを使用して ADC 入力にローパス・フィルタを構成することができますが、素子の正確な値はアプリケーションによって変わります。

中間周波数(IF)のアンダーサンプリング・アプリケーションでは、シャント・コンデンサが小さくなります。駆動源インピーダンスとの組み合わせでは、シャント・コンデンサが入力帯域幅を制限します。詳細については、資料「Analog Dialog」の

「Transformer-Coupled Front-End for Wideband A/D Converters」の項を参照してください。

AD9652 は、様々な入力信号周波数に対して、内蔵されている 最適設定を使用します。望ましい周波数帯に対する最適な ADC を構成するために抵抗 0x22A を使用します。

#### 表 9. 抵抗 0x22A の設定

| 抵抗 0x22A の設定 | 入力周波数範囲                             |

|--------------|-------------------------------------|

| 0(デフォルト)     | 0~155 MHz (1 <sup>st</sup> ナイキスト)   |

| 1            | 155~310 MHz (2 <sup>nd</sup> ナイキスト) |

| 2            | 310 MHz 以上 (3 <sup>rd</sup> ナイキスト)  |

最適なダイナミック性能を得るためには、各差動入力 VIN+と VIN-を駆動するソース・インピーダンスが一致しており、各差動入力はバランスしている必要があります。

#### 入力コモン・モード

AD9652 のアナログ入力は内部で DC バイアスされていません。 AC 結合のアプリケーションでは、ユーザーが外付けからこのバイアスを与える必要があります。最適な性能を得るためには、コモン・モード電圧が  $2.0\,\mathrm{V}$  に等しくなるように設定することが推奨されます。設計ではオンボードにコモン・モード電圧リファレンスが搭載されており、 VCM ピンから供給することができます。入力コモン・モードを設定するために VCM 出力を使用することが推奨されます。 VCM ピンはアプリケーション情報セクションで説明されているように、 $0.1\,\mu\mathrm{F}$  のコンデンサでグラウンドに対してデカップリングする必要があります。このデカップリング・コンデンサは、デバイスとこのコンデンサ間の直列抵抗とインダクタンスを最小化するためにピンにできるだけ近く配置してください。

#### コモン・モード電圧サーボ

AD9652 の VCM 出力とアナログ入力間に電圧損失があるようなアプリケーションの場合、コモン・モード電圧サーボを有効にして対処することができます。入力が交流結合され、VCM 出力とアナログ入力の間に 100Ω以上の抵抗が置かれている場合、大きな電圧降下が生ずることがあり、コモン・モード電圧サーボを有効にします。レジスタ 0x0F 内の Bit 0 をハイ・レベルにセットすると、VCM サーボ・モードが有効になります。このモードでは、AD9652 がアナログ入力部でのコモン・モード入力レベルを監視し、コモン・モード入力電圧を最適なレベルに維持するように VCM 出力レベルを調整します。

両方のチャンネルが動作している場合、チャンネルAが監視されます。しかし、チャンネルAがパワーダウンまたはスタンバ

# イ・モードである場合は、チャンネル B が監視されます。 ディザー

AD9652 は、SFDR 特性、特に小信号でのそれを改善するために使用できるオプションの内部ディザ回路を備えています。 ディザリングとは、AD9652 の入力に既知のしかし大きさがランダムな白色ノイズを注入する操作のことです。 ディザリングは ADC の伝達関数内のローカル・リニアリティを改善する効果を持っています。 AD9652 は、どちらかの ADC 入力に独立にディザリングを施すことが可能です。 ディザ DAC のフルスケールは十分小さいため、ディザリングを有効化しても外部入力信号振幅を制限することはありません。

図 52 のディザ回路ブロック図に示されるように、ディザ DAC を通して ADC の入力に加えられたディザは、SNR の劣化をデジタル的に最小化するために ADC の出力で正確に減算されます。ディザリングが有効化されると、ディザ DAC が擬似乱数発生器 (PN gen) によって駆動されます。AD9652 では、ディザ DAC が精密に較正されており、ディザを有効化することによって SNR と SINAD の劣化を極めて小さく抑えることができます。

図 52. ディザ回路ブロック図

SFDR の改善には SNR の劣化という代償が伴いますが、ディザ回路が内蔵されており両者を相関づけることができるため、SNR への影響は 1st ナイキスト領域内で通常 0.5 dB 以下に抑えられます。内蔵のディザ回路を有効化してもフルスケール・ダイナミック・レンジへの影響はありません。ディザの大きさは制御可能であり、これによってユーザーは SFDR の改善と SNRの劣化の間で望ましいトレードオフを選択することができます。ディザを有効化するには、レジスタ 0x30 の Bit 4をセットします。ディザのゲインを変更するには、レジスタ 0x212[7:4]を使

#### 表 10. ディザのゲイン

用します。

| レジスタ 0x212[7:4] の設定 | ゲイン比           | ゲイン(%) |

|---------------------|----------------|--------|

| 0b0000(デフォルト)       | Maximum dither | 100    |

| 0b0001              | 255/256 × max  | 99.6   |

| 0b0010              | 254/256 × max  | 99.2   |

| 0b0011              | 252/256 × max  | 98.4   |

| 0b0100              | 248/256 x max  | 96.8   |

| 0b0101              | 240/256 x max  | 93.75  |

| 0b0110              | 224/256 x max  | 87.5   |

| 0b0111              | 192/256 x max  | 75     |

| 0b1000              | Minimum dither | 50     |

ほとんどの場合、ディザリングはフルスケールに近い大信号に対しては、たとえば入力信号が-1dBFSのような場合は、SFDRを改善する効果はありません。入力が大信号の場合、SFDRは通常、ディザリングでは改善できないフロントエンド・サンプリングの歪みによって制約されます。しかし、そのような大信号に対しても、ディザリングはノイズ・フロアをより白色化するため、あるアプリケーションに対しては有効となることがあります。パイプライン型ADCでは一般的であるように、

AD9652 はランダム素子のミスマッチによって生ずる小さな DNL 誤差を含んでおり、ノイズ・フロアをデバイスごとに若干 ランダムに色づけるスプリアスまたはトーンを発生します。これらのトーンは通常極めて低レベルであり、ADC が大信号入力を量子化している場合は SFDR を制限しませんが、ディザリングはこれらのトーンを雑音に変換し、より白色が強いノイズ・フロアを発生します。

#### 小信号 FFT

小信号入力の場合、フロントエンド・サンプリング回路は通常 歪みにはほとんど影響を与えません。SFDR はランダム素子の ミスマッチによって生ずる DNL 誤差が発生するトーンによって 制限される傾向があります。従って、小信号の場合(通常、-6 dBFS以下)、ディザリングはこれらの DNL トーンを白色ノイ ズに変換することによって SFDR を大幅に改善することができ ます。

#### 静的直線性

ディザリングは、ADC の INL 伝達関数における鋭いローカル不連続性を除去し、総合的なピーク to ピーク INL を低減する効果もあります。

ディザリングを使用すると、INL 伝達関数に不連続性を発生するローカル小信号 DNL 誤差をランダム化するため、ピーク to ピーク INL 性能が改善されます。

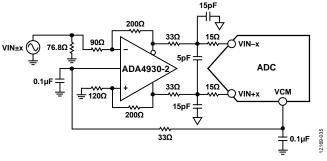

#### 差動入力構成

最適性能は、AD9652 を差動入力構成で駆動したときに得られます。ベースバンド・アプリケーションに対しては、ADL5566、AD8138、ADA4937-2、ADA4938-2、及び ADA4930-2 差動ドライバが優れた性能と ADC に対する柔軟なインタフェースを提供します。

ADA4930-2 の出力コモン・モード電圧は AD9652 の CML ピンで容易に設定できるため(図 53 参照)、ドライバを Sallen Keyフィルタ回路に組込んで入力信号の帯域制限を行うことができます。

図 53. ADA4930-2 を使用した差動入力構成

SNR が重要なパラメータとなるベースバンド・アプリケーションに対しては、入力構成に差動トランス結合を使用することが推奨されます。図 54 に例を示します。アナログ入力にバイアス

#### 大信号高速フーリエ変換

Data Sheet AD9652

を加えるため、VCM 電圧をトランス二次巻線のセンタータップ に接続することができます。

図 54. 差動トランス結合構成

トランスを選択するときは、信号特性を考慮する必要がありま す。大部分のRFトランスは、数MHzより低い周波数で飽和し ます。大きな信号電力もコア・サチレーションの原因になり、 歪みを発生させます。

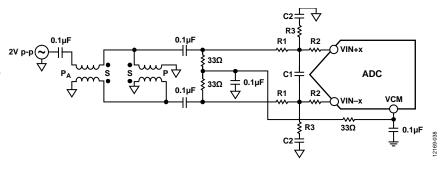

第2ナイキスト領域及びそれ以上の入力周波数では、AD9652 の真の SNR 性能を得るためには、大部分のアンプのノイズ性能 は不十分です。 SNR が重要なパラメータとなるこれらのアプリ ケーションに対しては、入力構成に差動ダブル・バラン結合を使 用することが推奨されます(図56参照)。この構成では、入 力は AC 結合され、VCM 電圧は 33Ω の抵抗を通して各入 力に供給されます。これらの抵抗は入力バランの損失を補償 し、ドライバに 50Ω のインピーダンスを供給します。

ダブル・バランとトランスの構成の場合、入力容量と抵抗の値 は入力周波数とソース・インピーダンスに依存して変わります。 これらのパラメータに基づいて、入力抵抗と容量の値を調整し たり、ある素子を削除したりする必要が生ずることがあります。 表 11 は、様々な入力周波数領域に対して RC ネットワークを設

定するための 推奨値を示します。た だし、これらの値は入力信号に依存す るため、初期ガイドとして帯域幅のみ 使用してください。表 11 の数値は図 54 及び図 56 に表示されている各 R1、 R2、C1、C2、及びR3に対する値であることに注意してくださ

表 11. RC ネットワークの例

| 周波数範<br>囲(MHz) | R1 直<br>列(Ω) | C1 差動<br>(pF) | R2 直<br>列(Ω) | C2 シャ<br>ント(pF) | R3 シャ<br>ント(Ω) |

|----------------|--------------|---------------|--------------|-----------------|----------------|

| 0~100          | 33           | Open          | 0            | 15              | 49.9           |

| 100~300        | 15           | Open          | 15           | 2.7             | 0              |

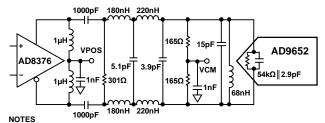

第2ナイキスト領域の周波数でトランス結合入力を使う代わり に、可変ゲイン・アンプを使う方法があります。 AD8375 また は AD8376 のデジタル可変ゲイン・アンプ (DVGA) は AD9652 を駆動するための優れた性能を提供します。図 55 は AD8376 と バンドパス・アンチエリアス・フィルタを通して AD9652 を駆 動する例を示します。

- 1. ALL INDUCTORS ARE COILCRAFT® 0603CS COMPONENTS WITH THE EXCEPTION OF THE 1µH CHOKE INDUCTORS (COIL CRAFT 0603LS).

- 2. FILTER VALUES SHOWN ARE FOR A 20MHz BANDWIDTH FILTER

- CENTERED AT 140MHz.

図 55. AD8376 を使用した差動入力構成

図 56. 差動ダブル・バラン入力構成

#### 表 12. VREE 回路構成のオプション

| 選択するモード      | SENSE 電圧 | 発生される ADC リファレンス電圧 (V)        | 発生される入力スパン(差動 V p-p) |

|--------------|----------|-------------------------------|----------------------|

| 外部リファレンス電圧   | AVDD     | N/A <sup>1</sup>              | 2×外部リファレンス電圧         |

| 内部固定リファレンス電圧 | GND      | V <sub>REF</sub> <sup>2</sup> | $2 \times V_{REF}^2$ |

<sup>&</sup>lt;sup>1</sup> N/A = 該当せず。

$<sup>^2</sup>$   $V_{REF}$  は抵抗 0x18 を通して設定される。デフォルトの VREF は  $1.25~V_{\circ}$

#### 電圧リファレンス

AD9652には、安定かつ正確なリファレンス電圧が内蔵されています。フルスケール入力範囲は、SPIを通して基準電圧を変化させることにより調整することができます。 ADC の入力スパンは、リファレンス電圧の変化に比例して追従します。

#### 内部リファレンス電圧の接続

AD9652 には安定で正確なプログラマブル・リファレンス電圧 回路が内蔵されており、このリファレンスは 1.0V から、最大 2.5 Vpp の差動フルスケール入力を供給するための 1.25V までの電圧リファレンスが可能となっています。 $V_{REF}$ 電圧はデフォルトで 1.25V に設定されていますが、レジスタ 0x18[2:0]、 $V_{REF}$  select を用いて変更することが可能です。

内部リファレンス電圧に対して AD9652 を設定するには、 SENSE ピンをロー・レベルに固定する必要があります。SENSE をロー・レベルに固定すると、ADC は VREF を直接使用して VREF 値の 2 倍の差動入力電圧を提供します。

内部リファレンス電圧を用いて最適なノイズ性能を得るためには、VREFピンを  $1.0~\mu F$  と  $0.1\mu F$  のコンデンサでピンの近傍でデカップリングすることが推奨されます。図 57 は、VREF によって 2.5~Vp-p の差動フルスケール入力電圧を設定する内部リファレンス接続の構成を示します。

図 57. 内部リファレンス電圧発生回路の構成

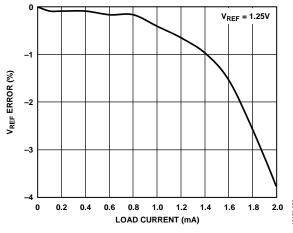

ゲイン・マッチングを改善するために、AD9652の内部リファレンス電圧を使って複数のコンバータを駆動する場合、他のコンバータによるリファレンス電圧への負荷を考慮する必要があります。図58に、内部リファレンス電圧が受ける負荷の影響を示します。

図 58. リファレンス電圧誤差対負荷電流

#### 外部リファレンス電圧による動作

ADC のゲイン精度を向上させる場合または温度ドリフト特性を改善する場合、外部リファレンス電圧の使用が必要となることがあります。 SENSE ピンを AVDD に接続すると、内部リファレンス電圧がディスエーブルされて、VREF ピンに供給される外部リファレンス電圧の使用が可能になります。内部リファレンス・バッファに対して、等価  $6 \, \mathrm{k} \Omega$  を持つ外部リファレンスが負荷になります。内部リファレンス・バッファに対して、等価  $6 \, \mathrm{k} \Omega$  を持つ外部リファレンスが負荷になります。内部リファレンス・バッファは、ADC コアに対して正側と負側のフルスケール・リファレンスを発生します。従って、入力電圧を  $2.5 \, \mathrm{Vp-p}$  差動フルスケール入力またはそれ以下に維持するには、外部リファレンス電圧が最大  $1.25 \, \mathrm{V}$  に制限される必要があります。

#### クロック入力の考慮事項

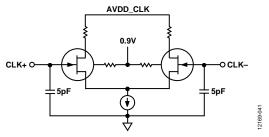

最適な性能を得るためには、AD9652のサンプル・クロック入力 (CLK+と CLK-) を高スルーレートの差動信号で駆動する必要があります。信号は一般にトランスまたはコンデンサを介して CLK+ピンと CLK-ピンに AC 結合されます。これらのピンは内部でバイアスされるため(図 59 参照)、外付けバイアスは不要です。入力がフローティングされている場合、CLK-ピンは CLK+ピンより若干低い電位にバイアスされるため、余分なクロック動作が防止されます。(これは図 59 には示されていません)

図 59. 単純化されたクロック入力等価回路

#### クロック入力オプション

AD9652 は非常に柔軟なクロック入力構造を持っています。クロック入力としては、CMOS、LVDS、LVPECL、または正弦波信号が可能です。使用する信号タイプによらず、クロック・ソース・ジッタは、「ジッタについての考慮事項」のセクションで説明するように、最も大きな問題です。

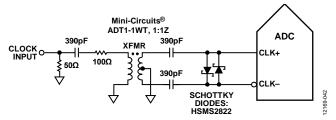

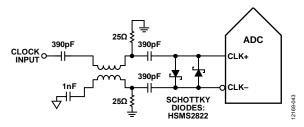

図 60 と図 61 に AD9652 をクロック駆動する(最大 1240 MHz の クロック・レートまで) 2 つの望ましい方法を示します。 ジッタの少ないクロック・ソースは、RF バランまたは RF トランスを 使ってシングルエンド信号から差動信号に変換されます。

RFバラン構成は 125 MHz~1240 MHz のクロック周波数に、RFトランスは 80 MHz~200 MHz のクロック周波数に、それぞれ推奨されます。トランス 2 次側に互いに逆向きに接続されたショットキ・ダイオードにより、 AD9652 に入力されるクロックが約 0.8 V のピーク to ピーク差動に制限されます。この制限は、クロックの大きな電圧振幅が AD9652 の別の部分に混入することを防止するのに役立つと同時に、低ジッタ性能にとって重要な、クロックの高速な立ち上がり時間と立ち下がり時間を維持します。

図 60. トランス結合の差動クロック(最大 200 MHz)

図 61. バラン結合の差動クロック(最大 1240 MHz)

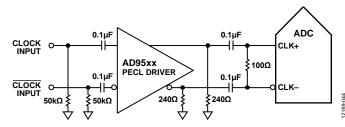

低ジッタ・クロックが使用できない場合、もう1つのオプションは差動 PECL 信号をサンプル・クロック入力ピンへ AC 結合することです(図 62 参照)。 AD9510、 AD9511、AD9512、 AD9513、 AD9514、 AD9515、 AD9516、 AD9517、 AD9518、 AD9520、 AD9522、 AD9523、 AD9524、 及び ADCLK905/ADCLK907/ADCLK925 の各クロックドライバは、優れたジッタ性能を提供します。

図 62. 差動 PECL サンプル・クロック(最大 1240 MHz)

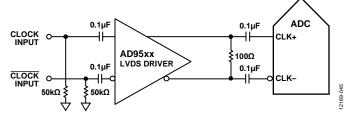

3つ目のオプションは、差動 LVDS 信号をサンプル・クロック 入力ピンへ AC 結合する方法です(図 63 参照)。 AD9510、 AD9511、AD9512、AD9513、AD9514、AD9515、AD9516、 AD9517、AD9518、AD9520、AD9522、AD9523、及び AD9524 の各クロック・ドライバは優れたジッタ性能を提供します。

図 63. 差動 LVDS サンプル・クロック(最大 625 MHz)

#### 入力クロック分周器

AD9652 は入力クロックを 1、2、4、または 8 分周できる入力クロック分周器を内蔵しています。デューティ・サイクル・スタビライザ (DCS) が、デフォルトでパワーアップ時にイネーブルされます。クロック分周比はレジスタ 0x0B にセットされます。

AD9652のクロック分周器は外部 SYNC 入力を使って同期させることができます。レジスタ 0x100のビット1とビット2を使うと、各 SYNC 信号で、またはレジスタが書き込まれた後の最初の SYNC 信号で、クロック分周器を再同期することができます。有効な SYNC により、クロック分周器は初期状態にリセットされます。この同期機能を使うと、複数のデバイスに位相の一致したクロック分周器を持たせることができるので、同時入力サンプリングが保証されます。分周器がイネーブルされ、SYNC オプションが使用される場合、ADC クロック分周器の出

SYNC オプションが使用される場合、ADC クロック分周器の出力位相は、同期後にレジスタ 0x16 を用いて入力クロック・サイクルの刻みで調整することができます。

SYNC 入力は、シングルエンドの CMOS タイプ信号を用いて駆動してください。SYNC 入力を使用しない場合は SYNC ピンをグラウンドに接続してください。

#### クロック・デューティ・サイクル

代表的な高速 ADC では両クロック・エッジを使って、さまざまな内部タイミング信号を発生しているため、クロックのデューティ・サイクルの影響を大きく受けます。一般に、ダイナミック性能特性を維持するためにはクロック・デューティ・サイクルの許容偏差は±5%以内である必要があります。

AD9652 は、非サンプリング・エッジ(立下り)の再タイミングを行って、公称50%のデューティ・サイクルを持つ内部クロック信号を発生するクロック・DCSを内蔵しています。この回路により、AD9652 の性能に影響を与えずに広範囲なクロック入力のデューティ・サイクルを許容することができます。

それでも、入力クロックの立ち上がりエッジのジッタは大きな問題であり、内部安定化回路で容易に減少させることはできません。DCS 制御ループは、公称 80 MHz 以下のクロック・レートでは機能しません。このループは時定数を持っているため、クロック・レートがダイナミックに変わるときは、これを考慮する必要があります。ダイナミックにクロック周波数が増減した後に、DCS ループが入力クロックに再ロックするまで、 $1.5~\mu s$  ~5  $\mu s$  の待ち時間が必要です。ループがロックされていない間、DCS ループはバイパスされるため、内部デバイスのタイミングは入力クロック信号のデューティ・サイクルに依存します。AD9652 その他のすべてのアプリケーションでは、AC 性能を最大にするため DCS 回路をイネーブルすることが推奨されます。

#### ジッタについての考慮事項

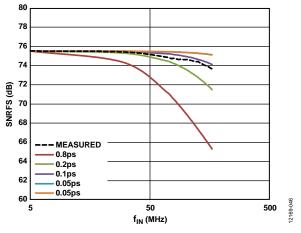

高速な高分解能 ADC は、クロック入力の品質に敏感です。与えられた入力周波数 $(f_{IN})$ でジッタ $(t_I)$ により発生する SNR 性能の低下は次式で計算されます。

$SNR_{HF} = -10 \log[(2\pi \times f_{IN} \times t_{JRMS})^2 + 10^{(-SNR_{LF}/10)}]$

この式で、rms アパーチャ・ジッタは、クロック入力、アナログ入力信号、ADC アパーチャ・ジッタ仕様を含む全ジッタ・ソースの2乗和平方根を表します。アンダーサンプリング・アプリケーションは、特にジッタに敏感です(図64)。

図 64. SNRFS 対入力周波数及びジッタ

ジッタが AD9652 のダイナミックレンジに影響を与えるケースでは、クロック入力をアナログ信号として扱ってください。

ADC クロックがノイズで変調されるのを防ぐために、外部クロック源及びバッファはクリーンな ADC 出力ドライバ電源で駆動してください。

低ジッタの水晶制御発振器は最適なクロック源です。

クロックが別のタイプのソース(ゲーティング、分周、または別の方法)から発生される場合、最終ステップで元のクロックを使って再タイミングする必要があります。

ADCに関係するジッタ性能の詳細については、AN-501「アパーチャ不確定性とADCシステム性能」とAN-756「サンプル化システムに及ぼすクロック位相ノイズとジッタの影響」を参照してください。

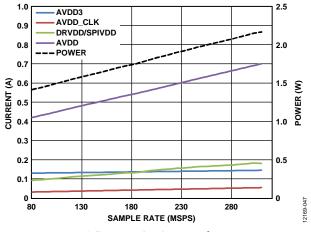

#### 消費電力とスタンバイ・モード

図 65 に示すように、AD9652 で消費される電力はサンプル・レートに比例します。図 65 のデータは代表的な性能特性のセクションと同じ動作条件で取得しました。

図 65. 消費電力及び電流対サンプル・レート

パワーダウン (レジスタ 0x08 の設定、または PDWN ピンをハイ・レベルします)をアサートすると、AD9652 はパワーダウン・モードになります。この状態では、ADC の消費電力は 1 mW(typ)になります。パワーダウン時は、出力ドライバは高インピーダンス状態になります。PDWN ピンをロー・レベルにすると、AD9652 は通常動作モードに戻ります。

PDWN ピンのレベルはデジタル出力ドライバ電源(DRVDD)を基準にしているため、この電源電圧を超えることはできないことに注意してください。

パワーダウン・モードでの低消費電力は、リファレンス電圧、 リファレンス・バッファ、バイアス回路、クロックをシャット ダウンすることにより、実現されています。スタンバイ・モー ドに入ると、デカップリング・コンデンサは放電するため、通 常動作に戻るときには再充電する必要があります。このため、 ウェイクアップ時間はパワーダウン・モードに留まる時間に関 係し、パワーダウン・サイクルが短いほど、ウェイクアップ時間も短くなります。

SPI ポート・インターフェースを使うときは、ADC をパワーダウン・モードまたはスタンバイ・モードにすることが可能です。

スタンバイ・モードにすると、高速なウェイクアップが必要な場合、内部リファレンス回路を動作させたままにしておくことができます。詳細については、AN-877「SPIを使った高速 ADCへのインタフェース」を参照してください。

#### 内部バックグラウンド・キャリブレーション

AD9652 は様々な条件に対応して高いレベルなノイズ性能を維持するために、内部アナログ回路間のエラーを継続的に補正するバックグラウンド・キャリブレーション機能を備えています。 キャリブレーション補正は様々なアナログ回路ブロック内のエラーをデジタル的に監視し、エラー量を計算して補正を行います。バックグラウンド補正は  $3 \times 2^{33}$  サンプルごとに計算されます。従って 310 MSPS で動作中は、アップデート速度は約 83 秒となります。各キャリブレーション・サイクルは、トラッキング性能を高めるため以前のキャリブレーションとは独立に行われます。バックグラウンド・キャリブレーションのための入力信号に関する制約は一切ありません。

キャリブレーションは各 ADC の経路に対して個別に行われます。 バックグラウンド・キャリブレーションは連続して行われます が、更新はキャリブレーションの計算にエラーを発生させるこ とがあるため、入力信号がある範囲から大きくずれない限り (OTR) 更新を行いません。キャリブレーション・エンジンが エラーを監視し、1回のキャリブレーション・サイクルの中で 1000 サンプルにわたって入力信号が入力範囲を超えた場合にキ ャリブレーション・サイクルをリセットします。AD9652に初 めて電源が投入され、正しいクロックが供給されたスタートア ップ時には、通常のキャリブレーション・サイクルより 64 倍高 速に収束する高速スタートアップ・バックグラウンド・キャリ ブレーションが実行されます。310 MSPS 時には、高速スタート アップ・キャリブレーションが 1.3 秒後に更新を行います。高 速スタートアップ・キャリブレーションは、AD9652の SNR性 能の低下を 0.5 dB 以下に抑えながら、フル・キャリブレーショ ン・サイクルの完了を待つよりも早く使用可能とします。この 性能の低下は最初のキャデラック・サイクルが完了するまで続

AD9652 の設定が変わって再キャリブレーションが必要になった場合、SPI レジスタの書き込みまたは PDWN ピンのアサート 及びデアサートによって高速スタートアップ・キャリブレーシ

ョンを開始させることができます。SPI レジスタを用いて開始させるには、レジスタ 0x08[1:0]を使用します。

新たに高速キャリブレーションを開始するには、ADC チャンネルの一方または両方を一旦スタンバイ状態においてから、レジスタ 0x08[1:0]に 0x2、0x0 の順に書き込みを行うことによって通常動作モードに戻します。通常動作モードに戻ると、高速キャリブレーションが一回行われた後、通常のフル・キャリブレーション・サイクルが実効されます。スタンバイの場合に加えて、パワーダウンの場合も同様のキャリブレーションが実行されます。0x1 に続いて 0x0 を書き込むことによって高速キャリブレーションが開始されます。別の方法として、レジスタ 0x4FB に 0x0C、0x08 を順番に書き込むことによっても高速キャリブレーションを開始させることができます。

PDWNピンは、レジスタ 0x08[1:0]の設定に従ってデバイスをパワーダウンまたはスタンバイ・モードに移行させるように設定することができます。パワーダウンまたはスタンバイ・モードのいずれかから通常モードに移行すると、高速キャリブレーションが開始されます。新たなキャリブレーションが必要な設定変更としては、VREFの変更、ディザ・オン/オフ、クロック入力の変更、及び DCS 状態の変更がありますが、これらには限られません。

特別な取扱いを必要とするアプリケーションのためのバックグラウンド・キャリブレーションに関連した様々な高度設定オプションもあります。これらのオプションとしては、スタンバイに対するオプションのリカバリ・モード、及びバックグラウンド・キャリブレーションの停止等があります。

アプリケーションでスタンバイ・モードが用いられる場合、AD9652 はデフォルトで電流補正を維持しますが、通常動作モードに戻ったときに新たな高速キャリブレーションを開始します。スタンバイ・モードで条件が大きく変化していない場合は、AD9652 はスタンバイ・モードに移行する前にレジスタ 0x4FAに 0x00 を書き込むことによって最近の補正係数を維持するように設定することができます。

これにより、デバイスはスタンバイ・モードに移行したときと同じ動作に戻り、スタンバイ・モードでの以前のキャリブレーション値を維持し、通常動作モードに戻ると同時に通常のキャリブレーション・サイクルを継続して実行します。

注:バックグラウンド・キャリブレーションを再度オンにする ためには、レジスタ 0x4FB の Bit 0 に 0x0 を書き込みます。

#### デジタル出力

AD9652 出力ドライバは標準の ANSI LVDS 用ドライバですが、オプションとしてレジスタ 0x15 を用いて駆動電流を小さくすることもできます。LVDS 用駆動電流を小さくするとデジタル的に誘起されたノイズを抑えられる可能性があります。.

AN-877 アプリケーション・ノート、「SPI を使った高速 ADC へのインタフェース」で説明するように、SPI 制御を使用する場合、データ・フォーマットとして、オフセット・バイナリ、2の補数、またはグレイ・コードを選択することができます。

AD9652 は、デジタル出力ピンに対して柔軟なスリー・ステート機能を持っています。スリー・ステート・モードは、デバイスがパワーダウン・モードに設定されたときにイネーブルされます。

#### タイミング

AD9652 は、26 サンプル・クロック・サイクルの遅延を持つラッチされたデータを出力します。データ出力は、クロック信号の立ち上がりエッジから 1 伝搬遅延(tPD)後に出力されます。AD9652 内部の過渡電圧を抑えるために、出力データ線の長さと対応する負荷を最小限に抑えてください。これらの過渡電圧はコンバータのダイナミック性能を低下させることがあります。AD9652 の最小変換レートは 80 MSPS(typ)です。80 MSPS より低いクロック・レートでは、ダイナミック性能が低下することがあります。

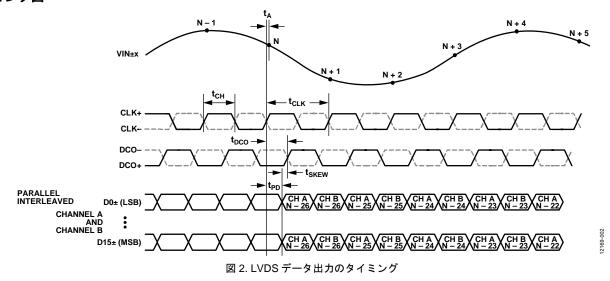

#### データ・クロック出力

AD9652 は、外部レジスタ内のデータをキャプチャするためのデータ・クロック出力 (DCO) も供給します。図 2 に、AD9652 の出力モードのタイミング図を示します。データ出力に対するDCO はレジスタ 0x17 を用いてタイミングを調整することができます。1 ステップあたり約 81 ps の刻みで 32 通りの遅延を設定するとができます。データは DDR フォーマットで出力され、DCO±から生成されたクロックの立ち上がり及び立下りエッジに整列されます。

#### ADC のオーバーレンジ

ADCの入力でオーバーレンジ (OR) が検出されると、ADC オーバーレンジ・インジケータがアサートされます。オーバーレンジ状態は ADC パイプラインの出力で決定されるため、ADC クロックで 26 サイクルのレイテンシが発生します。入力でのオーバーレンジは、それが 発生してから 26 クロック・サイクル後にこのビットで表示されます。

## 表 13. 出力データ・フォーマット

| 差動入力電圧 (V): (VIN+x) – (VIN–x)<br>入力スパン = 2.5 V p-p (V) | オフセット自然2進数出力 モード  | 2の補数モード(デフォルト)    | OR± ピンのロジッ<br>ク・レベル |

|--------------------------------------------------------|-------------------|-------------------|---------------------|

| <-1.25                                                 | 00 0000 0000 0000 | 10 0000 0000 0000 | 1                   |

| -1.25                                                  | 00 0000 0000 0000 | 10 0000 0000 0000 | 0                   |

| 0                                                      | 10 0000 0000 0000 | 00 0000 0000 0000 | 0                   |

| +1.25                                                  | 11 1111 1111 1111 | 01 1111 1111 1111 | 0                   |

| >+1.25                                                 | 11 1111 1111 1111 | 01 1111 1111 1111 | 1                   |

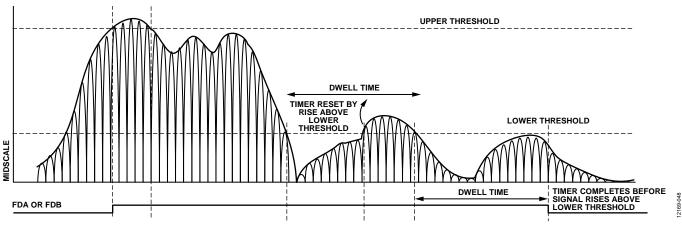

# 高速スレッショールド検出 (FDA/FDB)

レシーバ・アプリケーションでは、コンバータがクリップされそうなとき確実に検出できることが望まれます。OR±ピン上の標準オーバーフロー・インジケータは出力データで同期される遅延情報を提供します。遅延インジケータはこの場合、クリッピングの防止に限定された値しか表示しません。このため、クリップが発生する前に外部ゲインを小さくするための時間を確保するために、フルスケールより下にプログラマブルなスレッショールドを設けることが有効です。さらに、入力信号が大きなスルーレートを持つことがあるため、この機能によるレイテンシが大きな問題になります。

SPI ポートを使うと、超えたときに高速検出 (FD) 出力がアクティブになるスレッショールドを設定することができます。レジスタ 0x45 の Bit 0 が FD 機能をオンにします。レジスタ 0x47 ~レジスタ 0x4C によってスレッショールド・レベルとタイミングを設定することができます。信号が選択されたスレッショールドを下回っている限り、FD 出力はロー・レベルを維持します。このモードでは、データの振幅が条件の計算に使用されますが、データの符号(正か負のいずれか)は考慮されません。スレッショールド検出機能は、所望の範囲外にある正と負の信号(振幅)に対して同じ応答をします。チャンネル A 用 FDA、及びチャンネル B 用 FDB の高速検出インジケータは、入力の振幅が高速検出上側シュレッショールド・レジスタ 0x47 にプログラムされた値を超えたときにアサートされます。選択されたスレッショールド・レジスタの内容が、ADC の出力での信号振幅と比較されます。

高速上側スレッショールド検出は7クロック・サイクル分の遅延を持っています。上側スレッショールドは次の式で定義される4ビットの値です:

Upper Threshold (% Full Scale) =  $((Register\ 0x47\ value)/8) \times 100\%$

FDインジケータは、信号が下側スレッショールド・レベル以下に低下し、プログラムされたドウェル・タイムの間そのレベル以下に留まるまでクリアされません。下側スレッショールド・レベルは高速検出下側スレッショールド・レジスタ、0x49及び0x4Aでプログラムされます。高速検出下側スレッショールド・レジスタは、ADC出力の信号振幅と比較される15ビットのレジスタです。この比較には、ADCのパイプライン・レイテンシが発生しますが、コンバータ分解能は正確です。下側スレッショールドは次式で定義されています。

Lower Threshold (% Full Scale) = ((Register 0x49/Register 0x4A value)/32767) × 100%

たとえば、フルスケールの 50%を上側スレッショールドに設定し、フルスケールの 40%を下側スレッショールドに設定する場合は、レジスタ 0x49 とレジスタ 0x4A に 0x3333 を書き込みます。ドウェル・タイムは、高速検出ドウェル・タイム・レジスタ、0x4B と 0x4C 内に望みの値を書き込むことによって 1 サンプル・クロック・サイクルから 65,535 サンプル・クロック・サイクルの間でプログラムすることができます(図 66 参照)。.

図 66. FDA 及び FDB 信号に対するスレッショールドの設定

# シリアル・ポート・インタフェース

AD9652 シリアル・ポート・インターフェース(SPI)を使うと、ADC内部に用意されている構造化されたレジスタ・スペースを介してコンバータの特定の機能または動作を設定することができます。SPI は、アプリケーションに応じて、柔軟性とカスタマイゼーションを強化します。シリアル・ポートを介してアドレスがアクセスされ、このポートを介して読み書きすることができます。メモリは、バイトで構成されており、さらにフィールドに分割できます。これらのフィールドについては、Memory Map のセクションに記載します。詳細については、アプリケーション・ノート AN-877、「SPI を使った高速 ADC へのインタフェース」を参照してください。

#### SPI を使う設定

この ADC の SPI は、SCLK ピン、SDIO ピン、CSB ピンの 3本のピンにより定義されます(表 14 参照)。SCLK (シリアル・クロック)ピンは、ADC に対する に対する読み出し/書込みデータの同期に使用されます。SDIO (シリアル・データ入力/出力)ピンは2つの機能で共用されるピンであり、内部 ADC メモリ・マップ・レジスタに対するデータの送受信に使われます。CSB (チップ・セレクト・バー)はアクティブ・ローのコントロール信号であり、書込みサイクルと書込みサイクルをイネーブル/ディスエーブルします。

表 14. シリアル・ポート・インタフェース・ピン

| 双 14. | シリアル・ホード・インダフェ <del>ー</del> ス・ピン |

|-------|----------------------------------|

| ピン    | 機能                               |

| SCLK  | シリアル・クロック。シリアル・インタフェースの読         |

|       | み出し・書き込みを同期させるために用いられるシリ         |

|       | アル・シフト・クロック入力。                   |

| SDIO  | シリアル・データ入力/出力。2つの機能で共有される        |

|       | ピンであり、送られる命令とタイミング・フレーム内         |

|       | の相対位置に依存して、入力ピンまたは出力ピンとし         |

|       | て働きます。                           |

| CSB   | チップ・セレクト・バー。読み出しサイクルと書込み         |

|       | サイクルをゲーティングするアクティブ・ローのコン         |

|       | トロール信号です。パワーアップ中はロジック・ハイ         |

|       | にプルアップする必要があります。                 |

CSB の立ち下がりエッジと SCLK の立ち上がりエッジの組み合わせにより、フレームの開始が指定されます。シリアル・タイミングの例とその定義を表 5 と 図 4 に示します。

CSB ピンを使用するその他のモードもあります。CSB ピンはロー・レベルに固定することができ、これによりデバイスが常時イネーブルされます。これはストリーミングと呼ばれます。

CSBピンをバイト間でハイ・レベルに維持して外部タイミングを延ばすことができます。CSBをハイ・レベルに固定すると、SPI機能は高インピーダンス・モードになります。命令フェーズでは、16ビット命令が送信されます。命令フェーズの後ろにはデータが続き、長さはW0ビットとW1ビットにより指定されます。すべてのデータは8ビット・ワードで構成されます。

シリアル・データの各バイトの先頭ビットは、発行されているのが読み出しコマンドまたは書込みコマンドのいずれであるかを表示します。これにより、シリアル・データ入力/出力(SDIO)ピンが入力と出力との間で方向を変えることができます。

命令フェーズでは、ワード長の他に、シリアル・フレームが読み出し動作または書込み動作のいずれであるかを指定します。 これにより、シリアル・ポートをチップへの書込みまたは 内蔵 メモリ値の読み出しに使うことができます。命令がリードバック動作の場合、リードバックを実行すると、シリアル・データ入力/出力(SDIO/DCS)ピンの方向がシリアル・フレーム内の該当するポイントで入力から出力へ変わります。データは、MSBファースト・モードで送信することができます。MSBファーストはパワーアップ時のデフォルトであり、SPIポート設定レジスタを使って変えることができます。詳細及びその他の機能については、AN-877アプリケーション・ノートを参照してください。

#### ハードウェア・インターフェース

表 14 に記載されているピンは、ユーザー書込みデバイスと AD9652 のシリアル・ポートとの間の物理層インタフェースで す。SCLK ピンと CSB ピンは、SPI インタフェースを使用する ときは入力として機能します。SDIO ピンは双方向で、書込みフ ェーズでは入力として、リードバック時は出力として、それぞ れ機能します。SPIインタフェースは、フィールド・プログラ マブル・グリッド・アレイ (FPGA) またはマイクロコントロー ラから制御できるように十分な柔軟性を持っています。SPI 設 定の一つの方法は、AN-812「Microcontroller-Based Serial Port Interface (SPI) Boot Circuit | に詳細が記載されています。コンバ ータのフル・ダイナミック性能が必要な区間では、SPIポート をアクティブにしないようにしておく必要があります。SCLK 信号、CSB 信号、SDIO 信号は一般に ADC クロックに同期して いるため、これらの信号からのノイズがコンバータ性能を低下 させることがあります。オンボードの SPI バスを他のデバイス に対して使う場合には、このバスと AD9652 との間にバッファ を設けて、クリティカルなサンプリング区間にコンバータ入力 でこれらの信号が変化することを防止することが必要になりま す。

#### SPI を使わない設定

SPI コントロール・レジスタとインタフェースしないアプリケーションでは、SDIO ピンと SCLK ピン は独立した CMOS 互換のコントロール・ピンとして機能します。デバイスがパワーアップすると、ピンは DCS 及び出力データ・フォーマット機能制御用のスタティック・コントロール・ラインとして使用されるものと見なされます。このモードでは、CSB を AVDD に接続する必要があります。この接続により、シリアル・ポート・インタフェースがディスエーブルされます。

表 15. モードの選択

|      | - · · · · · · · · · · · · · · · · · · · |              |

|------|-----------------------------------------|--------------|

| ピン   | 外部電源電圧                                  | コンフィギュレーション  |

| SDIO | AVDD (デフォルト)                            | DCS イネーブル    |

|      | AGND                                    | DCSディスエーブル   |

| SCLK | AVDD                                    | 2の補数有効       |

|      | AGND (デフォルト)                            | オフセット・バイナリ有効 |

|      |                                         |              |

## SPI からアクセス可能な機能

表 16 に、SPI からアクセスできる一般的な機能の簡単な説明を示します。これらの機能の詳細については AN-877 アプリケーション・ノートに記載されています。

### 表 16. SPI を使ってアクセスできる機能

| 機能名          | 説明                                       |

|--------------|------------------------------------------|

| Power Modes  | パワーダウン・モードまたはスタンバイ・モードのいずれかに設定することができます。 |

| Clock        | SPI を介して DCS にアクセスすることができます。             |

| Offset       | コンバータのオフセットをデジタル的に調整します。                 |

| Test I/O     | 既知のデータを出力ビット上に表示させるテスト・モードを設定します。        |

| Output Mode  | 出力モードを設定します。                             |

| Output Phase | 出力クロックの極性を設定します。                         |

| Output Delay | DCO±から出力されるクロックの遅延を変更します。                |

| VREF         | リファレンス電圧を設定します。                          |

# メモリ・マップ

### メモリ・マップ・レジスタ・テーブルの読み出し

メモリ・マップ・レジスタ・テーブル内の各行には 8 ビットのロケーションがあります。メモリ・マップは大まかに、チップ設定レジスタ(アドレス 0x00~アドレス 0x02)、チャンネル・インデックス及び転送レジスタ(アドレス 0x05 とアドレス 0xFF)、及びセットアップ、コントロール、及びテストを含む ADC 機能レジスタ(アドレス 0x08~アドレス 0x4FB)の 3 つのセクションに分かれています。

メモリ・マップ・レジスタ・テーブル(表 17 を参照)には、各 16 進アドレスに対するデフォルトの 16 進値が記載してあります。先頭ビット 7 (MSB)の列は、デフォルト 16 進値の開始になります。たとえば、アドレス 0 x09 のグローバル・クロック・レジスタは、16 進デフォルト値 0 x01 を持ちます。これは、LSB またはビット 0 = 1、残りのビットはすべて 0 であることを意味します。この設定はデフォルトの出力フォーマット値であり、2 の補数です。

レジスタ 0x00~レジスタ 0x17 によって制御される機能の詳細については、AN-877 アプリケーション・ノートを参照してください。このアプリケーション・ノートは、他の残りのレジスタによって制御される機能の詳細も説明しています。

#### 未使用及び予約済みのロケーション

表17に記載されていないすべてのアドレスとビット・ロケーションは、このデバイスではサポートされていないロケーションです。特に指定がない限り、有効アドレス・ロケーションの未使用ビットには0を書き込む必要があります。アドレス・ロケーションの一部が未使用の場合にのみ、これらのロケーションへの書込みが必要です(たとえばアドレス0x18)。アドレス・ロケーション全体がオープン/未使用/未記載の場合(たとえばアドレス0x13)、このアドレス・ロケーションに対しては書込みを行わないでください。

#### デフォルト値

AD9652のリセット後、クリティカルなレジスタにはデフォルト値がロードされます。レジスタのデフォルト値は、メモリ・マップ・レジスタ・テーブ表 17 に記載してあります。

#### ロジック・レベル

ロジック・レベルは次のように定義します。

- 「ビットをセットする」は、「ビットをロジック1に設定する」または「ビットにロジック1を書き込む」と同じ意味です。

- 「ビットをクリアする」は、「ビットをロジック0に設定する」または「ビットにロジック0を書き込む」と同じ意味です。

#### 転送レジスタ・マップ

アドレス 0x08、0x09、0x0B、0x0D、0x0F、0x10、0x14、0x16、0x17、及び 0x30 のレジスタはシャドウされます。これらのアドレスに書込みを行っても、アドレス 0xFFに 0x01 を書き込んで転送コマンドが発行されて、転送ビットがセットされるまで、デバイスの動作に反映されません。この動作により、転送ビットがセットされたときに、これらのレジスタが内部で同時に更新されるようになります。内部更新は転送ビットがセットされたときに実行され、ビットは自動的にクリアされます。

#### チャンネル特有レジスタ

信号モニター・スレッショールドのような幾つかのチャンネ ル・セットアップ機能は、チャンネルごとに異なった値をプロ グラムすることができます。これらの場合、チャンネル・アド レス・ロケーションは、内部で 各チャンネルにコピーされます。 これらのレジスタとビットは、表17でローカルと表示されてい ます。これらのローカル・レジスタとビットをアクセスすると きは、レジスタ 0x05 内の該当するチャンネル A またはチャン ネルBビットをセットします。両ビットがセットされている場 合は、後続の書込みは両チャンネルのレジスタに対して行われ ます。読み出しサイクルでは、チャンネル A またはチャンネル Bの一方のみをセットして、2つのレジスタの内の1つを読み出 します。SPI 読み出しサイクルで両ビットがセットされている と、デバイスはチャンネル A の値を返します。 でグローバル と表示されているレジスタとビットは、デバイス全体またはチ ャンネル間に独立な設定が許容されていないチャンネル機能に 対して有効です。 レジスタ 0x05 内の設定は、グローバルなレ ジスタとビットに影響を与えません。

## メモリ・マップ・レジスタ・テーブル