## MSOP/QFNパッケージを採用した 18ビット1MSPS PulSAR® 7.0mWのADC

**AD7982**

### 特長

ノー・ミッシング・コードの18ビット分解能

スループット:1MSPS

低消費電力

1MSPSで7.0mW

10kSPSで70µW

INL: ±1LSB (typ), ±2LSB (max)

ダイナミック・レンジ:99dB

真の差動アナログ入力範囲: ±V<sub>REF</sub>

$2.5\sim5.0$ VOV<sub>REF</sub> $\ref{C0V}\sim$ V<sub>REF</sub>

任意の入力範囲が可能

ADA4941で簡単に駆動

パイプライン遅延なし

1.8V/2.5V/3V/5Vのロジック・インターフェースで2.5V単電源 動作

SPI®/QSPI™/MICROWIRE™/DSP互換シリアル・インター フェース

複数ADCのデイジーチェーン接続機能とビジー・インジケータ

10ピン・パッケージ:MSOP (MSOP-8) および3mm× 3mmのQFN (LFCSP)、SOT-23サイズ

### アプリケーション

バッテリ駆動の装置

データ・アクイジション・システム

医療用計測器

地震データ・アクイジション・システム

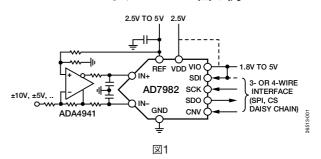

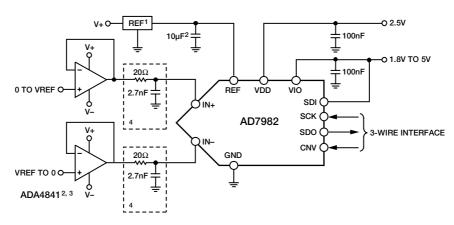

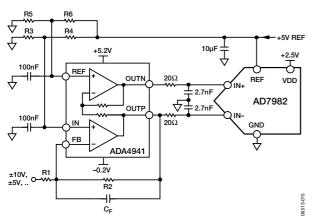

### アプリケーション図の例

### 概要

AD7982は、単電源VDDで動作する18ビット逐次比較型のA/D コンバータ(ADC)です。低消費電力、高速の18ビット・サ ンプリングADCと融通性に優れたシリアル・インターフェー ス・ポートを備えています。CNVの立上がりエッジで、IN+ ピンとIN-ピンの電位差をサンプルします。両ピンの電圧振幅 は、 $0V \sim V_{REF}$ の範囲で逆位相です。リファレンス電圧REFは 外部から供給し、電源電圧VDDと無関係に設定できます。消 費電力はスループットに比例します。

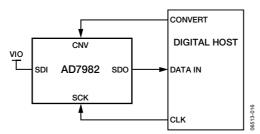

SPI互換シリアル・インターフェースは、SDI入力を使用し、3 線式バスで複数のADCをデイジーチェーン接続することが可能 です。オプションでビジー・インジケータを出力します。別の VIO電源を使用する1.8V、2.5V、3V、5Vロジックと互換性が あります。

AD7982には10ピンMSOPまたは10ピンQFN(LFCSP)パッ ケージがあり、動作は-40~+85℃の温度範囲で規定されてい ます。

表1. MSOP、QFN (LFCSP) パッケージの14/16/18ビットPulSAR® ADC

| Туре                       | 100 kSPS | 250 kSPS | 400 kSPS to 500 kSPS | ≥1000 kSPS | ADC Driver |

|----------------------------|----------|----------|----------------------|------------|------------|

| 18-Bit True Differential   |          | AD7691   | AD7690               | AD7982     | ADA4941    |

|                            |          |          |                      | AD7984     | ADA4841    |

| 16-Bit True Differential   | AD7684   | AD7687   | AD7688               |            | ADA4941    |

|                            |          |          | AD7693               |            | ADA4841    |

| 16-Bit Pseudo Differential | AD7680   | AD7685   | AD7686               | AD7980     | ADA4841    |

|                            | AD7683   | AD7694   |                      |            |            |

| 14-Bit Pseudo Differential | AD7940   | AD7942   | AD7946               |            | ADA4841    |

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の 利用に関して、あるいは利用によって生じる騙こ者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有 に属します。

ートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

© 2007 Analog Devices, Inc. All rights reserved.

REV. A

社/〒105-6891

東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル 電話03 (5402) 8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪MTビル2号 電話06(6350)6868

| 1   |

|-----|

| /K' |

|     |

| 特長           | ドライバ・アンプの選択                           | 14 |

|--------------|---------------------------------------|----|

| アプリケーション1    | シングルエンド/差動変換ドライバ                      |    |

| アプリケーション図の例1 | 電圧リファレンス入力                            | 15 |

| 概要1          | 電源                                    | 15 |

| 改訂履歴2        | デジタル・インターフェース                         | 16 |

| 仕様3          | ビジー・インジケータを使用しない3線式CSモード              | 17 |

| タイミング仕様5     | ビジー・インジケータを使用する3線式 <del>CS</del> モード  | 18 |

| 絶対最大定格6      | ビジー・インジケータを使用しない4線式 <del>CS</del> モード | 19 |

| ESDに関する注意6   | ビジー・インジケータを使用する4線式 <del>CS</del> モード  | 20 |

| ピン配置と機能の説明7  | ビジー・インジケータを使用しないチェーン・モード?             | 21 |

| 用語の説明8       | ビジー・インジケータを使用するチェーン・モード?              | 22 |

| 代表的な性能特性9    | アプリケーションのヒント                          | 23 |

| 動作原理12       | レイアウト                                 | 23 |

| 回路情報12       | AD7982の性能評価                           | 23 |

| コンバータの動作12   | 外形寸法                                  | 24 |

| 代表的な接続図13    | オーダー・ガイド                              | 24 |

| アナログ入力14     |                                       |    |

|              |                                       |    |

# 改訂履歴 10/07—Rev. 0 to Rev. A

| Changes to Table 1 and Layout        |

|--------------------------------------|

| Changes to Table 2                   |

| Changes to Layout                    |

| Changes to Layout                    |

| Changes to Figure 5                  |

| Changes to Figure 18 and Figure 20   |

| Changes to Figure 23                 |

| Changers to Figure 26                |

| Changes to Digital Interface Section |

| Changes to Figure 38                 |

| Changes to Figure 40                 |

| Updated Outline Dimensions           |

| Changes to Ordering Guide            |

|                                      |

### 3/07—Revision 0: Initial Version

## 仕様

特に指定のない限り、VDD=2.5V、VIO=2.3~5.5V、REF=5V、 $T_A$ =-40~+85 ${\mathbb C}_{\circ}$

### 表2

| Parameter                              | Conditions                                                                  | Min                    | Тур                         | Max                           | Unit    |

|----------------------------------------|-----------------------------------------------------------------------------|------------------------|-----------------------------|-------------------------------|---------|

| RESOLUTION                             |                                                                             | 18                     |                             |                               | Bits    |

| ANALOG INPUT                           |                                                                             |                        |                             |                               |         |

| Voltage Range                          | IN+-IN-                                                                     | -V <sub>REF</sub>      |                             | $+V_{REF}$                    | V       |

| Absolute Input Voltage                 | IN+, IN-                                                                    | -0.1                   |                             | $V_{REF} + 0.1$               | V       |

| Common-Mode Input Range                | IN+, IN-                                                                    | $V_{REF} \times 0.475$ | $V_{\text{REF}} \times 0.5$ | $V_{\text{REF}} \times 0.525$ | V       |

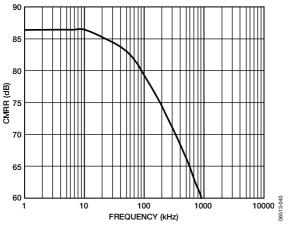

| Analog Input CMRR                      | $f_{IN} = 450 \text{ kHz}$                                                  |                        | 67                          |                               | dB      |

| Leakage Current at 25°C                | Acquisition phase                                                           |                        | 200                         |                               | nA      |

| Input Impedance                        |                                                                             | See the An             | alog Inputs sec             | tion                          |         |

| ACCURACY                               |                                                                             |                        |                             |                               |         |

| No Missing Codes                       |                                                                             | 18                     |                             |                               | Bits    |

| Differential Linearity Error           |                                                                             | -0.85                  | ±0.5                        | +1.5                          | LSB1    |

| Integral Linearity Error               |                                                                             | -2                     | ±1                          | +2                            | LSB1    |

| Transition Noise                       | REF = 5 V                                                                   |                        | 1.05                        |                               | LSB1    |

| Gain Error, $T_{MIN}$ to $T_{MAX}^2$   |                                                                             | -0.023                 | +0.004                      | +0.023                        | % of FS |

| Gain Error Temperature Drift           |                                                                             |                        | ±1                          |                               | ppm/°C  |

| Zero Error, $T_{MIN}$ to $T_{MAX}^2$   |                                                                             |                        | ±100                        | +700                          | μV      |

| Zero Temperature Drift                 |                                                                             |                        | 0.5                         |                               | ppm/°C  |

| Power Supply Rejection Ratio           | $VDD = 2.5 \text{ V} \pm 5\%$                                               |                        | 90                          |                               | dB      |

| THROUGHPUT                             |                                                                             |                        |                             |                               |         |

| Conversion Rate                        |                                                                             | 0                      |                             | 1                             | MSPS    |

| Transient Response                     | Full-scale step                                                             |                        |                             | 290                           | ns      |

| AC ACCURACY                            |                                                                             |                        |                             |                               |         |

| Dynamic Range                          | $V_{REF} = 5 \text{ V}$                                                     | 97                     | 99                          |                               | $dB^3$  |

|                                        | $V_{REF} = 2.5 \text{ V}$                                                   |                        | 93                          |                               | $dB^3$  |

| Oversampled Dynamic Range <sup>4</sup> | $F_0 = 1 \text{ kSPS}$                                                      |                        | 129                         |                               | $dB^3$  |

| Signal-to-Noise                        | $f_{IN} = 1 \text{ kHz}, V_{REF} = 5 \text{ V}, T_A = 25^{\circ}\text{C}$   | 95.5                   | 98                          |                               | $dB^3$  |

|                                        | $f_{IN} = 1 \text{ kHz}, V_{REF} = 2.5 \text{ V}, T_A = 25^{\circ}\text{C}$ |                        | 92.5                        |                               | $dB^3$  |

| Spurious-Free Dynamic Range            | $f_{IN} = 10 \text{ kHz}$                                                   |                        | -115                        |                               | $dB^3$  |

| Total Harmonic Distortion <sup>5</sup> | $f_{IN} = 10 \text{ kHz}$                                                   |                        | -120                        |                               | $dB^3$  |

| Signal-to-(Noise + Distortion)         | $f_{IN} = 1 \text{ kHz}, V_{REF} = 5 \text{ V}, T_A = 25^{\circ}\text{C}$   |                        | 97                          |                               | $dB^3$  |

REV. A -3-

<sup>|</sup> LSBは最下位ビットを意味します。入力範囲が±5Vの場合は、 $1LSB=38.15\mu V$ 。 | 2 「用語の説明」を参照。これらの仕様には全温度範囲での変動が含まれますが、外部リファレンスの誤差分は含まれません。 | 3 個表示の仕様はすべてフルスケール入力 (FSR) を基準とします。特に指定のない限り、フルスケールより0.5dB低い入力信号でテスト。 | 4 ダイナミック・レンジは、スループット $F_s$ で動作するIMSPSのADCをオーバーサンプリングした後に $F_o$ の出力ワードレートを持つポストデジタル・フィルタによる処理を行って取得した値です。 | 5  $f_{IN}=1kHz$ で出荷テスト済み。

特に指定のない限り、VDD=2.5V、VIO=2.3~5.5V、REF=5V、 $T_A$ =-40~+85 ${\mathbb C}_{\circ}$

### 表3

| Parameter                       | Conditions                                        | Min                             | Тур              | Max                           | Unit      |

|---------------------------------|---------------------------------------------------|---------------------------------|------------------|-------------------------------|-----------|

| REFERENCE                       |                                                   |                                 |                  |                               |           |

| Voltage Range                   |                                                   | 2.4                             |                  | 5.1                           | V         |

| Load Current                    | 1 MSPS, REF = $5 \text{ V}$                       |                                 | 350              |                               | μΑ        |

| SAMPLING DYNAMICS               |                                                   |                                 |                  |                               |           |

| -3 dB Input Bandwidth           |                                                   |                                 | 10               |                               | MHz       |

| Aperture Delay                  | VDD = 2.5 V                                       |                                 | 2                |                               | ns        |

| DIGITAL INPUTS                  |                                                   |                                 |                  |                               |           |

| Logic Levels                    |                                                   |                                 |                  |                               |           |

| $ m V_{IL}$                     | VIO > 3 V                                         | -0.3                            |                  | $+0.3 \times VIO$             | V         |

| $ m V_{IH}$                     | VIO > 3 V                                         | 0.7 x VIO                       |                  | VIO + 0.3                     | V         |

| $ m V_{IL}$                     | VIO ≤ 3 V                                         | -0.3                            |                  | $+0.1 \times \text{VIO}$      | V         |

| $ m V_{IH}$                     | VIO ≤ 3 V                                         | 0.9 x VIO                       |                  | VIO + 0.3                     | V         |

| $ m I_{IL}$                     |                                                   | -1                              |                  | +1                            | μA        |

| $I_{IH}$                        |                                                   | -1                              |                  | +1                            | μΑ        |

| DIGITAL OUTPUTS                 |                                                   |                                 |                  |                               |           |

| Data Format                     |                                                   | Serial 18 bits, twos complement |                  |                               |           |

| Pipeline Delay                  |                                                   |                                 | sion results ava | ilable immediately conversion |           |

| $V_{OL}$                        | $I_{SINK} = +500 \mu\text{A}$                     |                                 |                  | 0.4                           | V         |

| $V_{OH}$                        | $I_{SOURCE} = -500 \mu\text{A}$                   | VIO – 0.3                       |                  |                               | V         |

| POWER SUPPLIES                  |                                                   |                                 |                  |                               |           |

| VDD                             |                                                   | 2.375                           | 2.5              | 2.625                         | V         |

| VIO                             | Specified performance                             | 2.3                             |                  | 5.5                           | V         |

| VIO Range                       |                                                   | 1.8                             |                  | 5.5                           | V         |

| Standby Current <sup>1, 2</sup> | VDD and VIO = $2.5 \text{ V}, 25^{\circ}\text{C}$ |                                 | 0.35             |                               | μA        |

| Power Dissipation               | 10 kSPS throughput                                |                                 | 70               | 86                            | μW        |

|                                 | 1 MSPS throughput                                 |                                 | 7.0              | 8.6                           | mW        |

| Energy per Conversion           |                                                   |                                 | 7.0              |                               | nJ/sample |

| TEMPERATURE RANGE <sup>3</sup>  |                                                   |                                 |                  |                               |           |

| Specified Performance           | $T_{MIN}$ to $T_{MAX}$                            | -40                             |                  | +85                           | °C        |

**—4** — REV. A

すべてのデジタル入力は必要に応じてVIOまたはGNDに接続。

アクイジション・フェーズ時。

拡張温度範囲については、代理店および弊社営業部にお問い合わせください。

## タイミング仕様

### 表4

| Parameter                                                                                     | Symbol               | Min  | Тур | Max | Unit |

|-----------------------------------------------------------------------------------------------|----------------------|------|-----|-----|------|

| Conversion Time: CNV Rising Edge to Data Available                                            | t <sub>CONV</sub>    | 500  |     | 710 | ns   |

| Acquisition Time                                                                              | $t_{ACQ}$            | 290  |     |     | ns   |

| Time Between Conversions                                                                      | $t_{CYC}$            | 1000 |     |     | ns   |

| CNV Pulse Width (CS Mode)                                                                     | t <sub>CNVH</sub>    | 10   |     |     | ns   |

| SCK Period (CS Mode)                                                                          | t <sub>SCK</sub>     |      |     |     |      |

| VIO Above 4.5 V                                                                               |                      | 10.5 |     |     | ns   |

| VIO Above 3 V                                                                                 |                      | 12   |     |     | ns   |

| VIO Above 2.7 V                                                                               |                      | 13   |     |     | ns   |

| VIO Above 2.3 V                                                                               |                      | 15   |     |     | ns   |

| SCK Period (Chain Mode)                                                                       | t <sub>SCK</sub>     |      |     |     |      |

| VIO Above 4.5 V                                                                               |                      | 11.5 |     |     | ns   |

| VIO Above 3 V                                                                                 |                      | 13   |     |     | ns   |

| VIO Above 2.7 V                                                                               |                      | 14   |     |     | ns   |

| VIO Above 2.3 V                                                                               |                      | 16   |     |     | ns   |

| SCK Low Time                                                                                  | t <sub>SCKL</sub>    | 4.5  |     |     | ns   |

| SCK High Time                                                                                 | t <sub>SCKH</sub>    | 4.5  |     |     | ns   |

| SCK Falling Edge to Data Remains Valid                                                        | $t_{HSDO}$           | 3    |     |     | ns   |

| SCK Falling Edge to Data Valid Delay                                                          | $t_{DSDO}$           |      |     |     |      |

| VIO Above 4.5 V                                                                               |                      |      |     | 9.5 | ns   |

| VIO Above 3 V                                                                                 |                      |      |     | 11  | ns   |

| VIO Above 2.7 V                                                                               |                      |      |     | 12  | ns   |

| VIO Above 2.3 V                                                                               |                      |      |     | 14  | ns   |

| CNV or SDI Low to SDO D15 MSB Valid (CS Mode)                                                 | $t_{\rm EN}$         |      |     |     |      |

| VIO Above 3 V                                                                                 |                      |      |     | 10  | ns   |

| VIO Above 2.3 V                                                                               |                      |      |     | 15  | ns   |

| CNV or SDI High or Last SCK Falling Edge to SDO High Impedance ( $\overline{\text{CS}}$ Mode) | $t_{DIS}$            |      |     | 20  | ns   |

| SDI Valid Setup Time from CNV Rising Edge                                                     | t <sub>SSDICNV</sub> | 5    |     |     | ns   |

| SDI Valid Hold Time from CNV Rising Edge (CS Mode)                                            | $t_{HSDICNV}$        | 2    |     |     | ns   |

| SDI Valid Hold Time from CNV Rising Edge (Chain Mode)                                         | $t_{HSDICNV}$        | 0    |     |     | ns   |

| SCK Valid Setup Time from CNV Rising Edge (Chain Mode)                                        | t <sub>SSCKCNV</sub> | 5    |     |     | ns   |

| SCK Valid Hold Time from CNV Rising Edge (Chain Mode)                                         | t <sub>HSCKCNV</sub> | 5    |     |     | ns   |

| SDI Valid Setup Time from SCK Falling Edge (Chain Mode)                                       | $t_{SSDISCK}$        | 2    |     |     | ns   |

| SDI Valid Hold Time from SCK Falling Edge (Chain Mode)                                        | t <sub>HSDISCK</sub> | 3    |     |     | ns   |

| SDI High to SDO High (Chain Mode with Busy Indicator)                                         | t <sub>DSDOSDI</sub> |      |     | 15  | ns   |

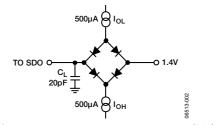

<sup>1</sup> 負荷条件については、図2と図3を参照。

図2. デジタル・インターフェース・タイミング測定時の 負荷回路

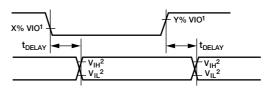

$^1 FOR~VIO \le 3.0V,~X=90,~AND~Y=10;~FOR~VIO > 3.0V,~X=70,~AND~Y=30.$   $^2 MINIMUM~V_{IH}~AND~MAXIMUM~V_{IL}~USED.~SEE~DIGITAL~INPUTS~SPECIFICATIONS~IN~TABLE~3.}$

図3. タイミング測定の電圧レベル

6513-003

## 絶対最大定格

### 表5

| Parameter                              | Rating                                                    |

|----------------------------------------|-----------------------------------------------------------|

| Analog Inputs                          |                                                           |

| IN+, IN- to GND <sup>1</sup>           | $-0.3 \text{ V to V}_{REF} + 0.3 \text{ V or}$<br>±130 mA |

| Supply Voltage                         |                                                           |

| REF, VIO to GND                        | -0.3 V to +6.0 V                                          |

| VDD to GND                             | -0.3 V to +3.0 V                                          |

| VDD to VIO                             | +3 V to -6 V                                              |

| Digital Inputs to GND                  | -0.3 V to VIO + 0.3 V                                     |

| Digital Outputs to GND                 | -0.3 V to VIO + 0.3 V                                     |

| Storage Temperature Range              | -65°C to +150°C                                           |

| Junction Temperature                   | 150°C                                                     |

| $\theta_{\text{JA}}$ Thermal Impedance |                                                           |

| 10-Lead MSOP                           | 200°C/W                                                   |

| 10-Lead QFN (LFCSP_WD)                 | 48.7°C/W                                                  |

| $\theta_{\text{JC}}$ Thermal Impedance |                                                           |

| 10-Lead MSOP                           | 44°C/W                                                    |

| 10-Lead QFN (LFCSP_WD)                 | 2.96°C/W                                                  |

| Lead Temperatures                      |                                                           |

| Vapor Phase (60 sec)                   | 215°C                                                     |

| Infrared (15 sec)                      | 220°C                                                     |

¹ IN+とIN-の説明は、「アナログ入力」を参照してください。

左記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作セクションに記 載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くと、デバイスの 信頼性に影響を与えることがあります。

### ESDに関する注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

—6— REV. A

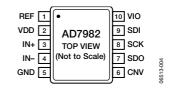

## ピン配置と機能の説明

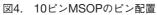

図5 10ピンQFN (LFCFS) のピン配置

### 表6. ピン機能の説明

| ピン |     |      |                                                                                                                                                                                                                                                                                                                                                                          |

|----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号 | 記号  | タイプ¹ | 説明                                                                                                                                                                                                                                                                                                                                                                       |

| 1  | REF | AI   | リファレンス入力電圧。REFの範囲は $2.4\sim5.1$ Vです。このピンはGNDピンを基準としており、 $10\mu$ Fのコンデンサをこのピンの近くに配置してデカップリングしてください。                                                                                                                                                                                                                                                                       |

| 2  | VDD | P    | 電源                                                                                                                                                                                                                                                                                                                                                                       |

| 3  | IN+ | AI   | 正側差動アナログ入力                                                                                                                                                                                                                                                                                                                                                               |

| 4  | IN- | AI   | 負側差動アナログ入力                                                                                                                                                                                                                                                                                                                                                               |

| 5  | GND | P    | 電源グラウンド                                                                                                                                                                                                                                                                                                                                                                  |

| 6  | CNV | DI   | 変換入力。この入力には複数の機能があります。立上がりエッジで変換を開始し、インターフェース・モードとしてチェーン・モードか $\overline{CS}$ モードを選択します。 $\overline{CS}$ モード時は、 $CNV$ がローレベルのときに $SDO$ ピンがイネーブルされます。チェーン・モードでは、 $CNV$ がハイレベルのときにデータを読み出します。                                                                                                                                                                              |

| 7  | SDO | DO   | シリアル・データ出力。変換結果がこのピンに出力されます。これはSCKと同期します。                                                                                                                                                                                                                                                                                                                                |

| 8  | SCK | DI   | シリアル・データ・クロック入力。デバイスが選択されたとき、このクロックによって変換結果<br>がシフト出力されます。                                                                                                                                                                                                                                                                                                               |

| 9  | SDI | DI   | シリアル・データ入力。この入力には複数の機能があります。ADCのインターフェース・モードを次のように選択します。 CNVの立上がりエッジでSDIがローレベルになると、チェーン・モードが選択されます。このモードでは、SDIをデータ入力に使用し、複数のADCの変換結果を1本のSDOラインでデイジーチェーン接続します。SDIのデジタル・データ・レベルは、SCKの18サイクル後にSDO上に出力されます。 CNVの立上がりエッジでSDIがハイレベルのとき、 $\overline{\text{CS}}$ モードが選択されます。このモードでは、SDIまたはCNVがローレベルのときにシリアル出力信号をイネーブルすることができます。変換の終了時にSDIまたはCNVがローレベルのとき、ビジー・インジケータ機能がイネーブルされます。 |

| 10 | VIO | P    | 入力/出力インターフェースのデジタル電源。公称値は、ホスト・インターフェースと同じです $(1.8V, 2.5V, 3V, 5V)$ 。                                                                                                                                                                                                                                                                                                     |

<sup>」</sup>AI=アナログ入力、DI=デジタル入力、DO=デジタル出力、P=電源。

REV. A — 7—

### 用語の説明

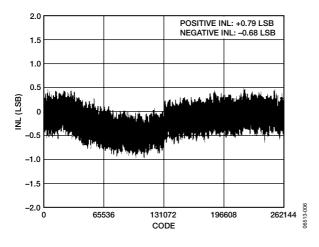

### 積分非直線性誤差 (INL)

INLとは、負側フルスケールと正側フルスケールを結ぶ直線と 実際の各コード出力との差を意味します。負側フルスケールと して使用するポイントは、最初のコード遷移より1/2LSBだけ 下に存在します。正側フルスケールは、最後のコード遷移より 1 1/2LSB高いレベルと定義されます。偏差は各コードの中央と 真の直線との距離として測定されます(図22を参照)。

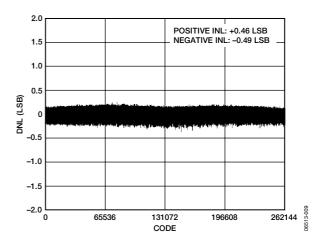

### 微分非直線性誤差 (DNL)

理想的なADCでは、各コード遷移はILSBだけ離れた位置で発生します。DNLとは、この理論値からの最大偏差のことです。通常は、ノー・ミッシング・コードが保証される分解能として規定されることもあります。

#### ゼロ誤差

ゼロ誤差は、理想的なミッドスケール入力電圧 (OV) と、ミッドスケール出力コード (OLSB) を発生する実際の電圧との差を指します。

### ゲイン誤差

最初の遷移(100…00から100…01)は、公称負側フルスケールより1/2LSB高いレベルで発生します( $\pm 5$ V範囲では-4.999981V)。最後の遷移(011…10から011…11)は、公称正側フルスケールより1 1/2LSB低いアナログ電圧で発生します( $\pm 5$ V範囲では+4.999943V)。ゲイン誤差は、最後の遷移の実際のレベルと最初の遷移の実際のレベルとの差と、対応する理論値の差との偏差を表します。

### スプリアスフリー・ダイナミックレンジ (SFDR)

SFDRは、入力信号のRMS振幅値とピーク・スプリアス信号の RMS値との差を意味し、dB値で表します。

### 有効ビット数(ENOB)

ENOBは、サイン波を入力したときの分解能の測定値であり、ビット数で表します。SINADとの関係は次式で表します。

$ENOB = (SINAD_{dB} - 1.76)/6.02$

### ノイズフリー・コード分解能

ノイズフリー・コード分解能は、これを超えると個々のコード を明確に分解することが不可能になるビット数のことです。次 式で計算し、ビット数で表します。

ノイズフリー・コード分解能=  $\log_2(2^N/\ell^2 - 2to)$  ピーク・ノイズ)

#### 有効分解能

有効分解能は次式で計算し、ビット数で表します。

有効分解能= $\log_2(2^N/RMS$ 入力ノイズ)

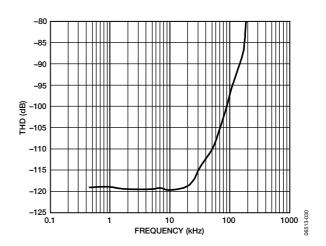

### 高調波歪み (THD)

THDは、最初の5つの高調波成分のRMS値の総和と、フルスケール入力信号のRMS値との比であり、dB値で表します。

### ダイナミック・レンジ

ダイナミック・レンジは、フルスケールのRMS値と、入力を短絡して測定したトータルRMSノイズとの比で、dB値で表します。すべてのノイズ源とDNL成分が含まれるように、-60dBFの信号で測定します。

#### S/N比 (SNR)

SNRは、実際の入力信号のRMS値と、ナイキスト周波数より下の他の全スペクトル成分のRMS値総和から高調波成分とDC成分を除いた値との比であり、dB値で表します。

### 信号/ノイズ&歪み比(SINAD)

SINADは、実際の入力信号のRMS値と、ナイキスト周波数より下の他の全スペクトル成分のRMS値総和(DC以外の高調波成分を含む)との比であり、dB値で表します。

### アパーチャ遅延

アパーチャ遅延は、アクイジション性能を表します。CNV入力の立上がりエッジから、入力信号が変換用にホールドされるまでの時間として測定されます。

### 過渡応答

ADCにフルスケールのステップ関数が入力されてから、ADC がその入力を正確に取得するまでに要する時間です。

## 代表的な性能特性

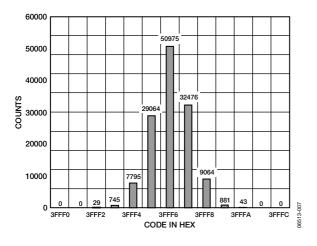

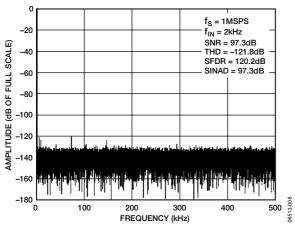

VDD=2.5V, REF=5.0V,  $VIO=3.3V_{\circ}$

図6. コード 対 積分非直線性

図7. コードの中央におけるDC入力の ヒストグラム

図8. FFTプロット

図9. コード 対 微分非直線性

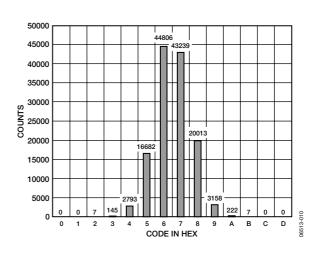

図10. コード遷移時のDC入力のヒストグラム

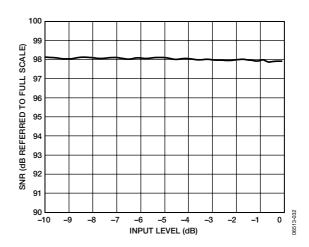

図11. 入力レベル 対 S/N比

REV. A — 9 —

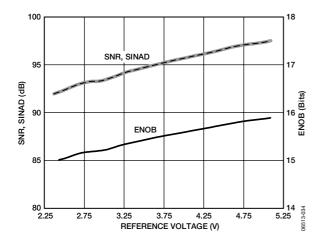

図12. リファレンス電圧 対 S/N比、SINAD、 ENOB

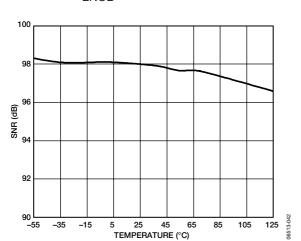

図13. S/N比の温度特性

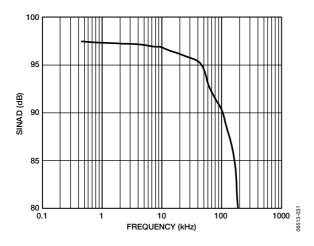

図14. SINADの周波数特性

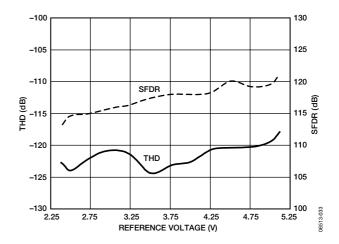

図15. リファレンス電圧 対 THD、SFDR

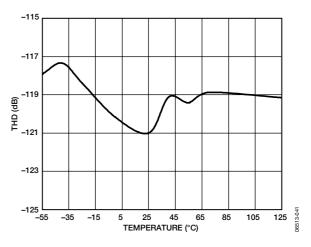

図16. THDの温度特性

図17. THDの周波数特性

— 10 — REV. A

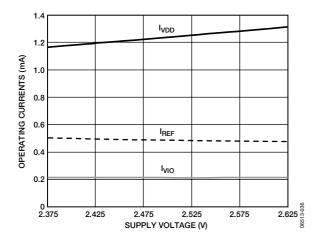

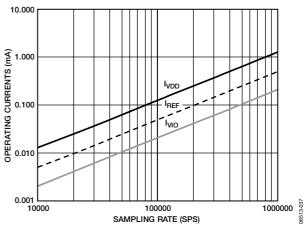

図18. 電源電圧 対 動作電流

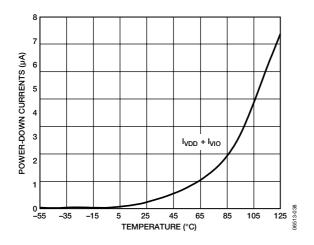

図20. 動作電流の温度特性

図19. パワーダウン電流の温度特性

REV. A — 11 —

### 動作原理

### 回路情報

AD7982は、逐次比較型アーキテクチャを採用した高速、低消費電力、単電源、高精度の18ビットADCです。

AD7982は毎秒100万サンプル(1MSPS)の変換能力を備え、変換終了から次の変換の開始までの間パワーダウンします。たとえば、10kSPSの動作で消費電力がわずか $70\mu W$ (typ)であるため、バッテリ駆動のアプリケーションに最適です。

AD7982はトラック&ホールドを内蔵しており、パイプライン 遅延や待ち時間が生じないため、複数のマルチプレクス・チャンネルのアプリケーションに最適です。

AD7982は、 $1.8\sim5$ Vのデジタル・ロジック・ファミリーのいずれにも接続できます。10ピンMSOPまたは小型の10ピンQFN (LFCSP) パッケージを採用しているため、省スペースの柔軟な構成が可能です。

16ビットのAD7980とピン互換です。

### コンバータの動作

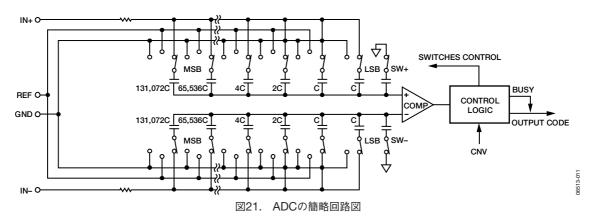

AD7982は、電荷再分配型DACを採用した逐次比較型ADCです。図21に、ADCの簡略回路図を示します。容量性DACは、18個のバイナリ重み付けコンデンサから構成される2個の同一アレイで構成されており、アレイは2個のコンパレータ入力に接続されています。

アクイジション・フェーズで、コンパレータの入力に接続され ているアレイの端子がSW+とSW-を介してGNDに接続され ます。独立した個々のスイッチはすべてアナログ入力に接続さ れます。したがって、コンデンサ・アレイをサンプリング・コ ンデンサとして使用し、IN+とIN-の各入力上のアナログ信号 を取得します。アクイジション・フェーズが終了し、CNV入力 がハイレベルになると、変換フェーズが開始されます。変換 フェーズが開始されると、まずSW+とSW-が開きます。2個 のコンデンサ・アレイが入力から切り離されて、GND入力に 接続されます。これにより、アクイジション・フェーズの終了 時に取得したIN+入力とIN-入力の間の差電圧がコンパレータ に入力され、コンパレータが不平衡状態になります。コンデン サ・アレイの各要素をGNDとREFの間で切り換えると、コン パレータ入力はバイナリ重み付けの電圧ステップ ( $V_{REF}/2$ 、  $V_{REF}$ /4 ...  $V_{REF}$ /262,144) で変化します。コントロール・ロジッ クは、これらのスイッチをMSBから順にトグルさせて、コンパ レータを元の平衡状態に戻すようにします。このプロセスが完 了すると、AD7982はアクイジション・フェーズに戻り、コン トロール・ロジックがADC出力コードとビジー信号インジケー タを発生します。

AD7982には変換クロックが内蔵されているため、変換プロセスでシリアル・クロックSCKは必要ありません。

### 伝達関数

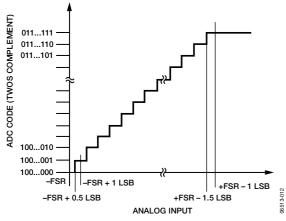

AD7982の理想的な伝達関数を図22と表7に示します。

図22. ADCの理想的な伝達関数

### 表7. 出力コードと理想的な入力電圧

| Description      | Analog Input<br>V <sub>REF</sub> = 5 V | Digital Output<br>Code (Hex) |

|------------------|----------------------------------------|------------------------------|

| FSR – 1 LSB      | +4.999962 V                            | 0x1FFFF¹                     |

| Midscale + 1 LSB | +38.15 μV                              | 0x00001                      |

| Midscale         | 0 V                                    | 0x00000                      |

| Midscale – 1 LSB | -38.15 μV                              | 0x3FFFF                      |

| -FSR + 1 LSB     | -4.999962 V                            | 0x20001                      |

| -FSR             | -5 V                                   | 0x20000 <sup>2</sup>         |

<sup>:</sup> オーバーレンジのアナログ入力  $(V_{\mathrm{IN}^+}-V_{\mathrm{IN}^-}>V_{\mathrm{REF}}-V_{\mathrm{GND}})$  のコード。  $^2$  アンダーレンジのアナログ入力  $(V_{\mathrm{IN}^+}-V_{\mathrm{IN}^-}< V_{\mathrm{GND}})$  のコード。

### 代表的な接続図

図23に、複数の電源を使用するときのAD7982の推奨接続例を 示します。

<sup>1</sup>SEE VOLTAGE REFERENCE INPUT SECTION FOR REFERENCE SELECTION.

<sup>2</sup>C<sub>REF</sub> IS USUALLY A 10µF CERAMIC CAPACITOR (X5R). SEE RECOMMENDED LAYOUT FIGURE 41 AND FIGURE 42.

3SEE DRIVER AMPLIFIER CHOICE SECTION.

<sup>4</sup>OPTIONAL FILTER. SEE ANALOG INPUT SECTION. 図23. 複数の電源を使用する代表的なアプリケーション図

REV. A -13-

### アナログ入力

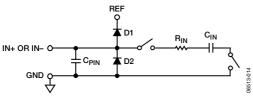

図24にAD7982の入力構造の等価回路を示します。

D1とD2の2個のダイオードが、IN+とIN-のアナログ入力に対するESD保護機能を提供します。アナログ入力信号がリファレンス入力電圧(REF)を0.3V以上超えないように注意してください。アナログ入力信号がこのレベルを超えると、ダイオードが順方向にバイアスされて、電流が流れ始めます。これらのダイオードは、最大130mAの順方向バイアス電流に対応します。ただし、入力バッファの電源(たとえば、図23に示すADA4841の電源)がREFと異なると、アナログ入力信号が最終的に電源レールを0.3V以上超えてしまうことがあります。このような場合には(たとえば入力バッファに短絡回路がある場合)、デバイスを保護するために電流制限機能を使うことができます。

図24. アナログ入力の等価回路

このアナログ入力構造を使うと、IN+とIN-の間の真の差動信号をサンプリングすることができます。これらの差動入力を使用すると、2つの入力に共通する信号が除去されます。

図25. アナログ入力CMRRの周波数特性

アクイジション・フェーズでは、アナログ入力(IN+または IN-)のインピーダンスをコンデンサ $C_{PIN}$ と $R_{IN}$ — $C_{IN}$ 直列接続回路との並列接続としてモデル化できます。 $C_{PIN}$ は主にピン・コンデンサです。 $R_{IN}$ は一般に400 $\Omega$ であり、直列抵抗とスイッチのオン抵抗で構成される集中定数成分です。 $C_{IN}$ は一般に30pFで、主にADCサンプリング・コンデンサとして使用します。

スイッチが閉じるサンプリング・フェーズでは、入力インピーダンスが $C_{PIN}$ に制限されます。 $R_{IN}$ と $C_{IN}$ は単極ローパス・フィルタを構成し、望ましくない折り返し信号の影響を削減し、ノイズを制限します。

駆動回路の信号源インピーダンスが低い場合は、AD7982を直接駆動できます。信号源インピーダンスが大きいと、AC性能、特にTHDに大きく影響します。DC性能は、入力インピーダンスにそれほど影響されません。最大の信号源インピーダンスは、許容できるTHDの値によって異なります。THDの低下は、信号源インピーダンスと最大入力周波数の関数になります。

### ドライバ・アンプの選択

AD7982は簡単に駆動できますが、ドライバ・アンプは次の条件を満たす必要があります。

・ ドライバ・アンプから発生するノイズをできる限り小さくし、AD7982のS/N比および遷移ノイズ性能を維持する必要があります。ドライバ・アンプから発生するノイズは、 $R_{\rm IN}$ と $C_{\rm IN}$ で構成されるAD7982のアナログ入力回路の単極ローパス・フィルタか、あるいは外部フィルタを使用する場合はそのフィルタによって除去することができます。AD7982のノイズは $40\mu V$  rms(typ)であるため、アンプによるS/N比の低下は次式で求めることができます。

$$SNR_{LOSS} = 20 \log \left( \frac{40}{\sqrt{40^2 + \frac{\pi}{2} f_{-3dB} (Ne_N)^2}} \right)$$

ここで、

$f_{-3dB}$ は、AD7982のMHzで表した入力帯域幅(10MHz)または入力フィルタを使用する場合はそのカットオフ周波数。

Nは、アンプのノイズ・ゲイン(たとえば、バッファの場合は1)。

$e_N$ は、オペアンプの等価入力ノイズ電圧  $(nV/\sqrt{Hz})$ 。

- ACアプリケーションの場合は、ドライバがAD7982に釣り合うTHD性能を持っている必要があります。

- マルチチャンネルのマルチプレクス・アプリケーションでは、ドライバ・アンプとAD7982のアナログ入力回路のセトリング時間は、コンデンサ・アレイへのフルスケール・ステップ入力に対して18ビット精度以内(0.0004%、4ppm)に安定する必要があります。アンプのデータシートには、一般に0.1~0.01%以内に安定するセトリング時間が規定されています。これは18ビット精度以内に安定するセトリング時間と大きく異なるため、ドライバを選択する前に確認する必要があります。

表8. 推奨ドライバ・アンプ

| Amplifier      | Typical Application                               |

|----------------|---------------------------------------------------|

| ADA4941        | Very low noise, low power, single to differential |

| ADA4841        | Very low noise, small, and low power              |

| AD8021         | Very low noise and high frequency                 |

| AD8022         | Low noise and high frequency                      |

| OP184          | Low power, low noise, and low frequency           |

| AD8655         | 5 V single supply, low noise                      |

| AD8605, AD8615 | 5 V single supply, low power                      |

### シングルエンド/ 差動変換ドライバ

バイポーラまたはユニポーラのシングルエンドのアナログ信号 を使用するアプリケーションでは、シングルエンド/差動変換 ドライバのADA4941を使用することで差動入力が可能になり ます。図26に回路図を示します。

R1とR2で入力範囲とADC範囲( $V_{REF}$ )の減衰比を設定します。 入力抵抗、信号帯域幅、折り返し防止機能、ノイズ成分により、 R1、R2、 $C_F$ の値を選びます。たとえば、入力範囲が $\pm 10V$ 、 インピーダンスが $4k\Omega$ の場合、 $R2=1k\Omega$ 、 $R1=4k\Omega$ となりま す。

R3とR4でADCのIN-入力の同相電圧を設定し、R5とR6で IN+入力の同相電圧を設定します。同相電圧は $V_{REF}/2$ に近い値 にしてください。たとえば、単電源で入力範囲が±10Vの場合、 R3=8.45kΩ, R4=11.8kΩ, R5=10.5kΩ, R6=9.76kΩ  $\gtrsim t$ ります。

### 電圧リファレンス入力

AD7982の電圧リファレンス入力REFは、ダイナミックな入力 インピーダンスを持つため、「レイアウト」で説明するように REFピンとGNDピンの間で効果的なデカップリングを行い、 低い信号源インピーダンスで駆動する必要があります。

特にインピーダンスが低い信号源(たとえば、AD8031や AD8605を使用するリファレンス・バッファ) でREFを駆動す る場合、最適な性能を得るためには $10\mu F$  (X5R、0805サイズ) のセラミック・チップ・コンデンサの使用が適しています。

バッファなしでリファレンス電圧を使用する場合、デカップリ ングの値は、使用するリファレンスによって異なります。たと えば、温度ドリフトの低いADR43xリファレンスを使用して最 適な性能を得るためには、22μF (X5R、1206サイズ)のセラ ミック・チップ・コンデンサの使用が適しています。

場合によって、2.2µFまでの容量の小さいリファレンス・デ カップリング用コンデンサを使用することで、性能、特にDNL に対する影響を最小限に抑えることができます。

ただし、さらに小さい容量のセラミック・デカップリング用コ ンデンサ (100nFなど) をREFピンとGNDピンの間に追加する 必要はありません。

### 雷源

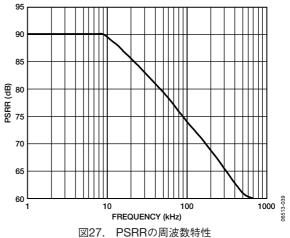

AD7982では、コア電源VDDとデジタル入出力インターフェー ス電源VIOの2本の電源ピンを使用します。VIOは、 $1.8\sim5.5V$ の任意のロジックに直接接続できます。必要な電源の数を少な くするために、VIOピンとVDDピンを相互に接続することがで きます。AD7982は、VIOとVDDの間の電源シーケンシングに は関係ありません。また、図27に示すように、広い周波数範囲 で電源変動の影響を受けません。

最適な性能を得るためには、VDDを電圧リファレンス入力 REFの約半分にしてください。たとえば、REFが5.0Vの場合は、 VDDを2.5V(±5%)に設定します。

各変換フェーズの終わりに、AD7982は自動的にパワーダウン します。したがって、消費電力はサンプリング・レートに正比 例します。このため、このデバイスは低いサンプリング・レー ト(数Hzの場合でも)や低電圧バッテリ駆動のアプリケーショ ンに最適です。

図28. サンプリングレート 対 動作電流

REV. A **— 15 —**

### デジタル・インターフェース

AD7982のピン数は少なくなっていますが、シリアル・インターフェース・モードでは高い柔軟性を提供します。

$\overline{\text{CS}}$ モードでは、SPI、QSPI、デジタル・ホスト、DSPと互換性があります。このモードで、3線式または4線式インターフェースを使用できます。CNV、SCK、SDOの信号を使用する3線式インターフェースは配線数がごくわずかになり、絶縁型のアプリケーションなどに適しています。SDI、CNV、SCK、SDOの信号を使用する4線式インターフェースでは、変換を開始するCNVを読出しタイミング(SDI)と無関係にすることが可能です。これは、ジッタの低いサンプリングまたは同時サンプリングのアプリケーションで便利です。

チェーン・モードでは、SDI入力を使用して、シフト・レジス タと同様に1本のデータ・ラインで複数のADCをカスケード接 続するデイジーチェーン接続が可能です。 AD7982の動作モードは、CNVの立上がりエッジでのSDIのロジックレベルで決定されます。SDIがハイレベルの場合はCSモード、SDIがローレベルの場合はチェーン・モードが選択されます。SDIのホールド時間を、SDIとCNVを接続して設定すると、チェーン・モードが常に選択されるようになります。

いずれのモードでも、AD7982にはデータビットの前にスタートビットを挿入するオプションがあります。このスタートビットをビジー信号インジケータとして使用することで、デジタル・ホストに割込みをかけ、データの読出しをトリガできます。ビジー・インジケータを使用しない場合は、読出しを行う前に最大変換時間の経過を待つ必要があります。

次の場合に、ビジー・インジケータがイネーブルされます。

- CSモードでは、ADCの変換終了時にCNVまたはSDIがローレベルのとき (図32と図36)

- チェーン・モードでは、CNVの立上がりエッジでSCKがハイレベルのとき(図40)

— 16 — REV. A

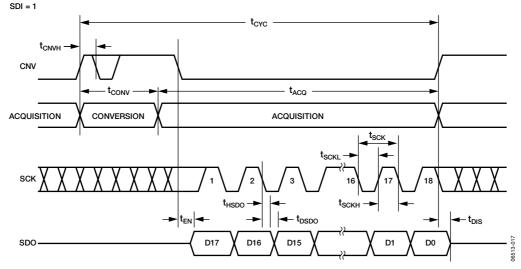

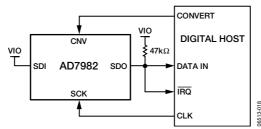

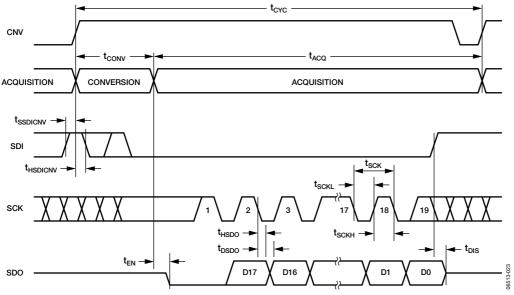

### ビジー・インジケータを使用しない3線式CS モード

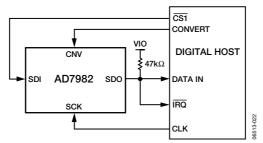

一般に、1個のAD7982をSPI互換のデジタル・ホストに接続するときに使用するモードです。図29に接続図、図30に対応するタイミング図を示します。

SDIをVIOに接続しているときに、CNVの立上がりエッジで変換が開始され、 $\overline{\text{CS}}$ モードが選択され、SDOがハイ・インピーダンスになります。変換が開始されてから終わるまで、CNVの状態に関係なくこれが続きます。これは、たとえばCNVをローレベルに設定して、アナログ・マルチプレクサなどの他のSPIデバイスを選択する場合に便利です。ただし、最小変換時間が経過する前にCNVをハイレベルに復帰させ、変換時間の間、可

能な限り長くハイレベルに保持し、ビジー信号インジケータが発生しないようにする必要があります。変換が完了すると、AD7982はアクイジション・フェーズに入り、パワーダウンします。CNVがローレベルになると、MSBがSDO上に出力されます。残りのデータビットは、その後に続くSCKの立下がりエッジで出力されます。データはSCKの両エッジで有効です。立上がりエッジを使用してデータの取込みが可能ですが、SCKの立下がりエッジを使用するデジタル・ホストでは、ホールド時間が許容される限り、読出し速度を速くすることができます。SCKの18番目の立下がりエッジの後、またはCNVがハイレベルになるときに(いずれか先に発生する方)、SDOはハイ・インピーダンスに戻ります。

図29. ビジー・インジケータを使用しない3線式 $\overline{CS}$ モードの接続図(SDIはハイレベル)

図30. ビジー・インジケータを使用しない3線式OSモードのシリアル・インターフェース・タイミング (SDIはハイレベル)

REV. A — 17 —

### ビジー・インジケータを使用する3線式CS モード

一般に、割込み入力を持つSPI互換のデジタル・ホストに1個のAD7982を接続するときに使用するモードです。

図31に接続図、図32に対応するタイミング図を示します。

SDIをVIOに接続しているときに、CNVの立上がりエッジで変換が開始され、CSモードが選択され、SDOがハイ・インピーダンスになります。SDOはCNVの状態に関係なく、変換が完了するまでハイ・インピーダンスのままです。最小変換時間の前にCNVを使用してアナログ・マルチプレクサなどの他のSPIデバイスを選択できますが、最小変換時間が経過する前にCNVをローレベルに復帰させ、変換時間の間、可能な限り長くローレベルに保持し、ビジー信号インジケータを発生させるようにする必要があります。変換が完了すると、SDOはハイ・インピーダンスからロー・インピーダンスに変わります。SDOライ

ン上のプルアップを使用し、この変化を割込み信号とし、デジタル・ホストが制御するデータ読出しを開始できます。その後、AD7982はアクイジション・フェーズに入り、パワーダウンします。データビットは、後に続くSCKの立下がりエッジによってMSBファーストで出力されます。SCKの両エッジでデータは有効です。立上がりエッジを使用してデータの取込みが可能ですが、SCKの立下がりエッジを使用するデジタル・ホストでは、ホールド時間が許容される限り、読出し速度を速くすることができます。SCKの19番目の立下がりエッジが発生した後、またはCNVがハイレベルになるときに(いずれか先に発生する方)、SDOはハイ・インピーダンスに戻ります。

複数のAD7982を同時に選択する場合は、損傷やラッチアップを生じることなくSDO出力ピンがこの競合を処理します。ただし、消費電力を抑えるために、競合はできる限り短くすることを推奨します。

図31. ビジー・インジケータを使用する3線式 CSモードの接続図(SDIはハイレベル)

図32. ビジー・インジケータを使用する3線式 $\overline{CS}$ モードのシリアル・インターフェース・タイミング(SDIはハイレベル)

### ビジー・インジケータを使用しない4線式CS モード

一般に、複数のAD7982をSPI互換のデジタル・ホストに接続するときに使用するモードです。

図33に2個のAD7982を使用する接続図の例、図34に対応する タイミング図を示します。

SDIがハイレベルのときに、CNVの立上がりエッジで変換が開始され、 $\overline{\text{CS}}$ モードが選択され、SDOがハイ・インピーダンスになります。このモードでは、変換フェーズおよびその後に続くデータ読出し時にCNVをハイレベルに保持する必要があります。(SDIとCNVがローレベルの場合は、SDOがローレベルになります。)最小変換時間の前にSDIを使用して、アナログ・マルチプレクサなどの他のSPIデバイスを選択できますが、最小変換時間が経過する前にSDIをハイレベルに復帰させ、変換時

間の間、可能な限り長くハイレベルに保持し、ビジー信号インジケータが発生しないようにする必要があります。変換が完了すると、AD7982はアクイジション・フェーズに入り、パワーダウンします。SDI入力をローレベルにすることで各ADCの結果が読み出され、これによってMSBがSDO上に出力されます。残りのデータビットは、その後に続くSCKの立下がりエッジで出力されます。SCKの両エッジでデータは有効です。立上がりエッジを使用してデータの取込みが可能ですが、SCKの立下がりエッジを使用するデジタル・ホストでは、ホールド時間が許容される限り、読出し速度を速くすることができます。SCKの18番目の立下がりエッジが発生した後、またはSDIがハイレベルになるときに(いずれか先に発生する方)、SDOがハイ・インピーダンスに戻り、もう1つのAD7982の読出しが可能になります。

図33. ビジー・インジケータを使用しない4線式 $\overline{CS}$ モードの接続図

図34. ビジー・インジケータを使用しない4線式 CSモードのシリアル・インターフェース・タイミング

REV. A — 19 —

### ビジー・インジケータを使用する4線式CS モード

一般に、割込み入力を持つSPI互換のデジタル・ホストに1個のAD7982を接続し、アナログ入力のサンプリングに使用するCNVをデータ読出しの選択に使用する信号とは無関係にしておきたい場合に使用するモードです。この非依存性は、CNVのジッタを低く抑える必要のあるアプリケーションで特に重要です。

図35に接続図、図36に対応するタイミング図を示します。

SDIがハイレベルのときに、CNVの立上がりエッジで変換が開始され、 $\overline{\text{CS}}$ モードが選択され、SDOがハイ・インピーダンスになります。このモードでは、変換フェーズおよびその後に続くデータ読出し時にCNVをハイレベルに保持する必要があります。(SDIとCNVがローレベルの場合は、SDOがローレベルになります。)最小変換時間の前にSDIを使用して、アナログ・マルチプレクサなどの他のSPIデバイスを選択できますが、最小

変換時間が経過する前にSDIをローレベルに復帰させ、変換時 間の間、可能な限り長くローレベルに保持し、ビジー信号イン ジケータを発生させるようにする必要があります。変換が完了 すると、SDOはハイ・インピーダンスからロー・インピーダン スに変化します。SDOライン上のプルアップを使用し、この変 化を割込み信号とし、デジタル・ホストが制御するデータ読出 しを開始できます。その後、AD7982はアクイジション・ フェーズに入り、パワーダウンします。データビットは、後に 続くSCKの立下がりエッジでMSBファーストで出力されます。 SCKの両エッジでデータは有効です。立上がりエッジを使用し てデータの取込みが可能ですが、SCKの立下がりエッジを使用 するデジタル・ホストでは、ホールド時間が許容される限り、 読出し速度を速くすることができます。SCKのオプションの19 番目の立下がりエッジが発生した後、またはSDIがハイレベル になるときに(いずれか先に発生する方)、SDOはハイ・イン ピーダンスに戻ります。

図35. ビジー・インジケータを使用する4線式CSモードの接続図

図36. ビジー・インジケータを使用する4線式 $\overline{\text{CS}}$ モードのシリアル・インターフェース・タイミング

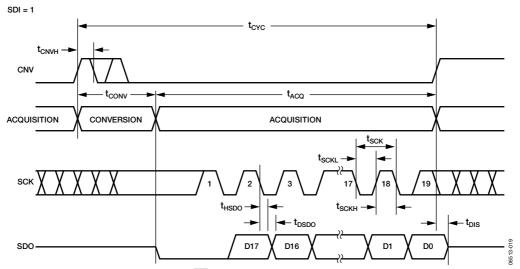

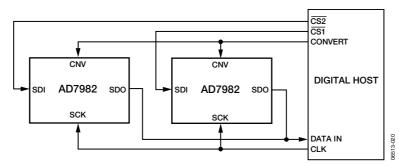

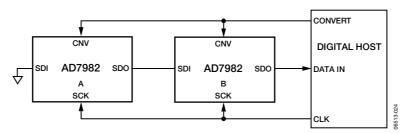

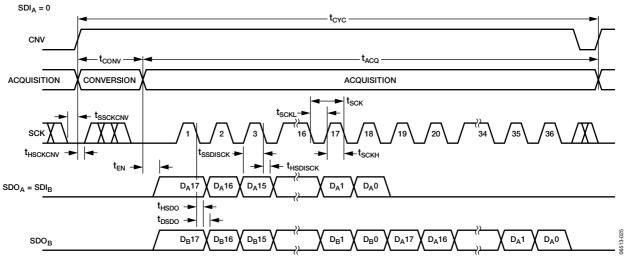

### ビジー・インジケータを使用しないチェーン・ モード

3線式シリアル・インターフェースで複数のAD7982をデイジーチェーン接続するときに、このモードが使用できます。たとえば、絶縁型マルチコンバータ・アプリケーションなど、使用する部品数や配線数を少なくする場合やインターフェース能力が限られているシステムにこの機能が便利です。データの読出しは、シフト・レジスタのクロック動作とほぼ同じです。

図37に2個のAD7982を使用する接続図の例、図38に対応する タイミング図を示します。

SDIとCNVがローレベルのときに、SDOがローレベルになります。SCKがローレベルのときに、CNVの立上がりエッジで変換が開始され、チェーン・モードが選択され、ビジー・インジケータがディセーブルされます。このモードでは、変換フェー

ズおよびその後に続くデータ読出し時に、CNVをハイレベルに保持する必要があります。変換が完了すると、MSBがSDO上に出力され、AD7982はアクイジション・フェーズに入り、パワーダウンします。内部シフト・レジスタに格納されている残りのデータビットは、後に続くSCKの立下がりエッジで出力されます。各ADCでは、SDIが内部シフト・レジスタの入力に接続され、SCKの立下がりエッジで入力されます。チェーン内の各ADCはデータをMSBファーストで出力し、N個のADCのデータを読み出すには18×Nクロックが必要になります。SCKの両エッジでデータは有効です。立上がりエッジを使用してデータの取込みが可能ですが、SCKの立下がりエッジを使用してデータの取込みが可能ですが、SCKの立下がりエッジを使用しるデジタル・ホストでは、ホールド時間が許容される限り読出し速度を速くすることができるため、チェーン内の多くのAD7982の読出しができます。合計読出し時間により、最大変換レートが低下することがあります。

図37. ビジー・インジケータを使用しないチェーン・モードの接続図

図38. ビジー・インジケータを使用しないチェーン・モードのシリアル・インターフェース・タイミング

REV. A — 21 —

### ビジー・インジケータを使用するチェーン・ モード

3線式シリアル・インターフェースで複数のAD7982をデイジーチェーン接続し、ビジー・インジケータを出力する場合に、このモードが使用できます。たとえば、絶縁型マルチコンバータ・アプリケーションなど、使用する部品数や配線数を少なくする場合やインターフェース能力が限られているシステムにこの機能が便利です。データの読出しは、シフト・レジスタのクロック動作とほぼ同じです。

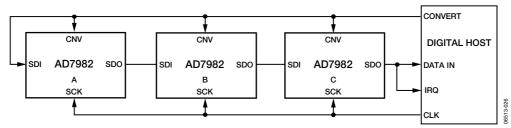

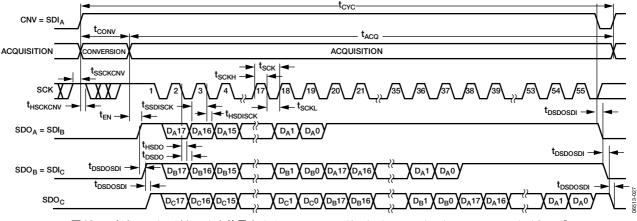

図39に3個のAD7982を使用する接続図の例、図40に対応する タイミング図を示します。

SDIとCNVがローレベルのときに、SDOがローレベルになります。SCKがハイレベルのときに、CNVの立上がりエッジで変換が開始され、チェーン・モードが選択されて、ビジー・インジケータ機能がイネーブルされます。このモードでは、変換フェーズおよびその後に続くデータ読出し時に、CNVをハイレ

ベルに維持する必要があります。チェーン内の全ADCの変換が 完了すると、デジタル・ホストに最も近いADC(図39ではCと 表記されているAD7982 ADC) のSDOピンがハイレベルにな ります。このSDOの変化をビジー・インジケータとし、デジタ ル・ホストが制御するデータ読出しをトリガできます。その後、 AD7982はアクイジション・フェーズに入り、パワーダウンし ます。内部シフト・レジスタに格納されているデータビットは、 後に続くSCKの立下がりエッジで出力されます。各ADCでは、 SDIが内部シフト・レジスタの入力に接続され、SCKの立下が りエッジで入力されます。チェーン内の各ADCはデータを MSBファーストで出力し、N個のADCのデータを読み出すた めには18×N+1クロックが必要になります。立上がりエッジ を使用してデータの取込みが可能ですが、SCKの立下がりエッ ジを使用するデジタル・ホストでは、ホールド時間が許容され る限り読出し速度を速くすることができるため、チェーン内の 多くのAD7982の読出しができます。

図39. ビジー・インジケータを使用するチェーン・モードの接続図

図40. ビジー・インジケータを使用するチェーン・モードのシリアル・インターフェース・タイミング

## アプリケーションのヒント

### レイアウト

AD7982を実装するPCボードは、アナログ部とデジタル部を分離し、ボード内でそれぞれをまとめて配置するように設計してください。アナログ信号をすべて左側、デジタル信号をすべて右側に置くピン配置を採用することによって、このような設計が簡単にできるようになっています。

デバイスの真下にデジタル信号ラインを配置しないようにしてください。そうしないと、AD7982の真下のグラウンド・プレーンがシールドに使われていない限り、チップ上にノイズが混入してしまいます。CNVやクロックなどの高速スイッチング信号がアナログ信号パスの近くを通らないようにします。デジタル信号とアナログ信号は、できるだけ交差しないようにしてください。

少なくともグラウンド・プレーンを1枚使用してください。デジタル部とアナログ部で共通のものにするか、分割することができます。分割する場合は、AD7982の真下で接続してください。

AD7982の電圧リファレンス入力REFには、ダイナミックな入力インピーダンスがあるため、最小の寄生インダクタンスでデカップリングしてください。その際、リファレンス・デカップリング用のセラミック・コンデンサをREFピンとGNDピンのできる限り近く、理想的にはその真上に配置し、低インピーダンスの太いパターンで接続します。

最後に、AD7982の電源VDDとVIOのデカップリングには、一般に100nFのセラミック・コンデンサをAD7982の近くに配置し、接続には短くて太いパターンを使用します。こうすることで、低インピーダンス・パスが得られ、電源ライン上のグリッチの影響を小さくすることができます。

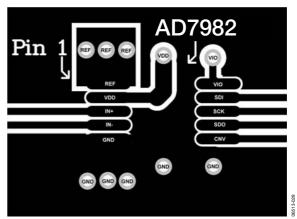

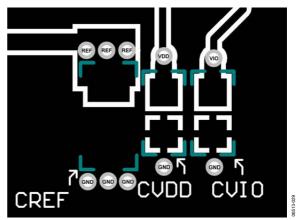

図41と図42に、これらのルールに従ったレイアウトの例を示します。

### AD7982の性能評価

AD7982のその他の推奨レイアウトは、AD7982評価用ボード (EVAL-AD7982CBZ) の説明書に概説されています。この評価用ボード・パッケージには、完全組立てテスト済みの評価用ボード、説明書、EVAL-CONTROL BRD3を使用してPCからボードを制御するためのソフトウェアが含まれています。

図41. AD7982のレイアウト例(上面層)

図42. AD7982のレイアウト例(底面層)

REV. A — 23 —

## 外形寸法

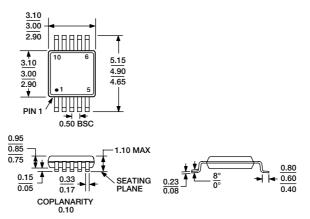

COMPLIANT TO JEDEC STANDARDS MO-187-BA

図43. 10ピン・ミニスモール・アウトライン・パッケージ [MSOP] (RM-10) 寸法単位:mm

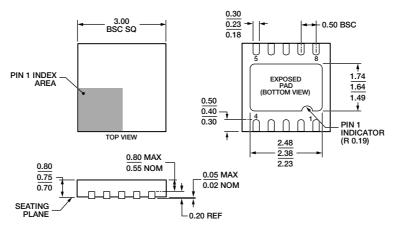

図44. 10ピン・リード・フレーム・チップ・スケール・パッケージ [QFN (LFCSP\_WD)] 3mm×3mmボディ、極薄、デュアル・リード (CP-10-9) 寸法単位:mm

### オーダー・ガイド

| Model                           | Temperature Range | Package Description    | Package<br>Option | Ordering<br>Quantity | Branding |

|---------------------------------|-------------------|------------------------|-------------------|----------------------|----------|

| AD7982BRMZ <sup>1</sup>         | –40°C to +85°C    | 10-Lead MSOP           | RM-10             | Tube, 50             | C5F      |

| AD7982BRMZRL71                  | –40°C to +85°C    | 10-Lead MSOP           | RM-10             | Reel, 1000           | C5F      |

| AD7982BCPZ <sup>1</sup>         | –40°C to +85°C    | 10-Lead QFN (LFCSP_WD) | CP-10-9           | Tube, 75             | C5F      |

| AD7982BCPZ-RL7 <sup>1</sup>     | –40°C to +85°C    | 10-Lead QFN (LFCSP_WD) | CP-10-9           | Reel, 1000           | C5F      |

| AD7982BCPZ-RL <sup>1</sup>      | –40°C to +85°C    | 10-Lead QFN (LFCSP_WD) | CP-10-9           | Reel, 5000           | C5F      |

| EVAL-AD7982CBZ <sup>1, 2</sup>  |                   | Evaluation Board       |                   |                      |          |

| EVAL-CONTROL BRD3Z <sup>3</sup> |                   | Controller Board       |                   |                      |          |

Z=RoHS準拠製品

<sup>2</sup> このボードは、評価/デモンストレーション用に、単独の評価用ボードとして、またはEVAL-CONTROL BRD3と組み合わせて使用することができます。

<sup>3</sup> このボードを使用すると、製品番号末尾にCBが付いたアナログ・デバイセズ製評価用ボード全製品の制御と通信をPCから行うことができます。