# 16ビット、250kSPS PulSAR™ MSOP/QFNパッケージADC

AD7685

#### 特長

ノー・ミスコードの16ビット分解能 スループット・レート: 250kSPS

INL:  $\pm 0.6$ LSB (typ),  $\pm 2$ LSB (max) (FSR $\mathcal{O} \pm 0.003\%$ )

S/(N+D): 93.5dB (@20kHz) THD: -110dB (@20kHz) 疑似差動アナログ入力レンジ:

0V~V<sub>REF</sub>、V<sub>REF</sub>はVDDまで設定可能

パイプライン遅延なし

2.3~5.5Vの単電源動作、1.8~5Vのロジック・インターフェース電源

SPI®/QSPI™/MICROWIRE™/DSP互換のシリアル・イン ターフェース

複数のADCのデイジーチェーン接続、BUSYインジケータ 消費電力

1.35 mW (@2.5V/100kSPS), 4 mW (@5V/100kSPS),  $1.4 \mu W$  (@2.5V/100SPS)

スタンバイ時の消費電流:1nA

10ピン・パッケージ:MSOP(MSOP-8サイズ)および 3mm×3mmのQFN¹(LFCSP)(SOT-23サイズ)

AD7686、AD7687、AD7688と完全にピン互換

#### アプリケーション

バッテリ駆動装置:

医療用計測

移動体通信

携帯情報端末

データ・アクイジション

計測器

プロセス制御

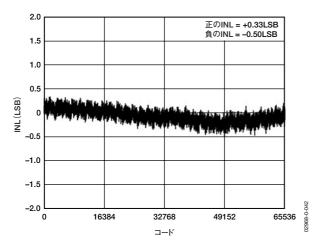

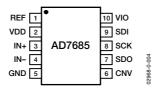

図1. コード 対 積分非直線性

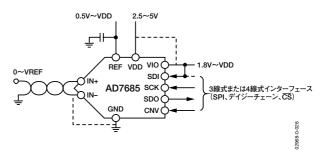

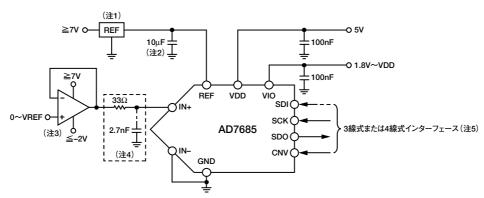

### アプリケーション回路図

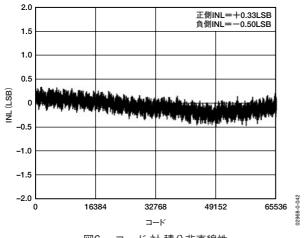

図2

表1. MSOP、QFN (LFCSP)/SOT-23パッケージの 16ビットPulSAR ADC

| タイプ                               | 100kSPS          | 250kSPS                    | 500kSPS          |

|-----------------------------------|------------------|----------------------------|------------------|

| 真の差動<br>疑似差動<br>差動/ユニポーラ<br>ユニポーラ | AD7684<br>AD7683 | AD7687<br>AD7685<br>AD7694 | AD7688<br>AD7686 |

#### 概要

AD7685は、2.3~5.5Vの単電源VDDで動作する16ビット、電荷再分配式の逐次比較型A/Dコンバータ(SAR ADC)です。ノー・ミスコードで低消費電力の高速16ビット・サンプリングADC、内部変換クロック、融通性に優れたシリアル・インターフェース・ポートを内蔵しています。また、低ノイズ、広帯域幅で、アパーチャ遅延の短いトラック&ホールド回路もあります。CNV信号の立上がりエッジで、ADCはグラウンド・センスIN-を基準とする0V~ $V_{REF}$ のアナログ入力IN+をサンプリングします。リファレンス電圧REFは外部から供給し、電源電圧の範囲まで設定できます。

消費電力は、スループットと直線的に比例して変化します。

SPI互換のシリアル・インターフェースでは、SDI入力を使用し、単一の3線バス上で複数のADCをデイジーチェーン接続することができます。また、オプションでBUSYインジケータ信号を供給することもできます。AD7685は、別にVIO電源を使用する1.8V、2.5V、3V、5Vロジックと互換です。

AD7685は10ピンMSOPまたは10ピンQFN(LFCSP)のパッケージで提供しており、 $-40\sim+85$ ℃の温度範囲で仕様が規定されています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。本紙記載の商標および登録商標は、各社の所有に属します。 ※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

© 2004 Analog Devices, Inc. All rights reserved.

REV. 0

本 社/〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル 電話03 (5402) 8200

<sup>1</sup> このパッケージは現在開発中です。QFNパッケージのサンプルと入手については、 弊社までお問い合わせください

## 目次

| 仕様3         | コンバータの動作     | 13 |

|-------------|--------------|----|

| タイミング仕様5    | 代表的な接続図      | 14 |

| 絶対最大定格7     |              |    |

| ESDに関する注意7  | アプリケーションのヒント | 24 |

| ピン配置と機能の説明8 | レイアウト        | 24 |

| 用語の説明9      |              |    |

| 代表的な性能特性10  | 外形寸法         | 25 |

| 回路情報 13     | オーダー・ガイド     | 26 |

## 改訂履歴

4/04-リビジョン0:初版

# 仕様

特に指定のない限り、VDD=2.3~5.5V、VIO=2.3V~VDD、 $V_{REF}$ =VDD、 $T_{A}$ = -40~ +85  $\mathbb C$

#### 表2

|                                                            |                                                         |                     | Bグレー       | · ド                          |      | Cグレ·           | - Ķ1             |                  |

|------------------------------------------------------------|---------------------------------------------------------|---------------------|------------|------------------------------|------|----------------|------------------|------------------|

| パラメータ                                                      | 条件                                                      | Min                 | Тур        | Max                          | Min  | Тур            | Max              | 単位               |

| 分解能                                                        |                                                         | 16                  |            |                              | 16   |                |                  | ビット              |

| アナログ入力                                                     |                                                         |                     |            |                              |      |                |                  |                  |

| 電圧範囲                                                       | IN+-IN-                                                 | 0                   |            | $V_{\scriptscriptstyle REF}$ | 0    |                | $V_{\text{REF}}$ | V                |

| 絶対入力電圧                                                     | IN+                                                     | -0.1                |            | VDD+0.1                      | -0.1 |                | VDD+0.1          | V                |

|                                                            | IN-                                                     | -0.1                |            | 0.1                          | -0.1 |                | 0.1              | V                |

| アナログ入力CMRR                                                 | $f_{IN}=250kHz$                                         |                     | 65         |                              |      | 65             |                  | dB               |

| 漏れ電流(25℃時)<br>入力インピーダンス                                    | アクイジションの実行期間                                            | Г <del>-2</del> .1. | 1          | を参照                          |      | 1              |                  | nA               |

|                                                            |                                                         | 1 / 5               | ロク人刀       | 」を参照                         |      |                |                  |                  |

| 精度                                                         |                                                         |                     |            |                              |      |                |                  |                  |

| ノー・ミスコード                                                   |                                                         | 16                  |            |                              | 16   |                |                  | ビット              |

| 微分直線性誤差(DNL)                                               |                                                         | -1                  | $\pm 0.7$  | 1.2                          | -1   | $\pm 0.5$      | +2               | LSB <sup>2</sup> |

| 積分直線性誤差(INL)<br>遷移ノイズ                                      | REF=VDD=5V                                              | -3                  | ±1<br>0.5  | +3                           | -2   | $\pm 0.6$ 0.45 | +2               | LSB<br>LSB       |

| 透移ノイス<br>ゲイン誤差³(T <sub>MIN</sub> ∼T <sub>MAX</sub> )       | KEF-VDD-3V                                              |                     | ±2         | ±30                          |      | ±2             | ±15              | LSB              |

| ゲイン誤差温度ドリフト                                                |                                                         |                     | $\pm 0.3$  | ±30                          |      | $\pm 0.3$      | ± 13             | ppm/°C           |

| オフセット誤差 <sup>3</sup> (T <sub>MIN</sub> ~T <sub>MAX</sub> ) | VDD=4.5~5.5V                                            |                     | $\pm 0.1$  | ±1.6                         |      | $\pm 0.1$      | ±1.6             | mV               |

| WIN - MAX                                                  | VDD=2.3~4.5V                                            |                     | $\pm 0.7$  | ±3.5                         |      | $\pm 0.7$      | ±3.5             | mV               |

| オフセット温度ドリフト                                                |                                                         |                     | $\pm 0.3$  |                              |      | $\pm 0.3$      |                  | ppm/°C           |

| 電源電圧変動感度                                                   | VDD=5V±5%                                               |                     | $\pm 0.05$ |                              |      | $\pm 0.05$     |                  | LSB              |

| スループット                                                     |                                                         |                     |            |                              |      |                |                  |                  |

| 変換レート                                                      | VDD=4.5∼5.5V                                            | 0                   |            | 250                          | 0    |                | 250              | kSPS             |

|                                                            | VDD=2.3~4.5V                                            | 0                   |            | 200                          | 0    |                | 200              | kSPS             |

| 過渡応答時間                                                     | フルスケール・ステップ                                             |                     |            | 1.8                          |      |                | 1.8              | μs               |

| AC精度                                                       |                                                         |                     |            |                              |      |                |                  |                  |

| 信号対ノイズ比 (S/N比)                                             | $f_{IN}=20kHz$ , $V_{REF}=5V$                           | 90                  | 92         |                              | 92   | 93.5           |                  | $dB^4$           |

|                                                            | $f_{IN}=20kHz$ , $V_{REF}=2.5V$                         | 86                  | 88         |                              | 87.5 | 88.5           |                  | dB               |

| スプリアスフリー・ダイナミック <b>・</b><br>レンジ                            | $f_{IN}=20kHz$                                          |                     | -106       |                              |      | -110           |                  | dB               |

| 全高調波歪み (THD)                                               | $f_{IN}=20kHz$                                          |                     | -106       |                              |      | -110           |                  | dB               |

| 信号/ノイズ&歪み比 (SINAD)                                         | $f_{IN}=20kHz$ , $V_{REF}=5V$                           | 90                  | 92         |                              | 92   | 93.5           |                  | dB               |

|                                                            | f <sub>IN</sub> =20kHz、V <sub>REF</sub> =5V、<br>-60dB入力 |                     | 32         |                              |      | 33.5           |                  | dB               |

|                                                            | $f_{IN}=20kHz$ , $V_{REF}=2.5V$                         | 85.5                | 87.5       |                              | 87   | 88.5           |                  | dB               |

| 相互変調歪み5                                                    |                                                         |                     | -110       |                              |      | -115           |                  | dB               |

REV. 0 -3-

特に指定のない限り、VDD=2.3~5.5V、VIO=2.3V~VDD、 $V_{REF}$ = VDD、 $T_A$ = -40~ +85  $\mathbb C$

#### 表3

| パラメータ                                                           | 条件                                                                                                                                                               | Min                                                           | Тур                          | Max                                                      | 単位                                        |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------|----------------------------------------------------------|-------------------------------------------|

| 電圧リファレンス<br>電圧範囲<br>負荷電流                                        | 250kSPS、REF=5V                                                                                                                                                   | 0.5                                                           | 50                           | VDD+0.3                                                  | V<br>µA                                   |

| サンプリング・ダイナミック特性<br>-3dB入力帯域幅<br>アパーチャ遅延                         | VDD=5V                                                                                                                                                           |                                                               | 2<br>2.5                     |                                                          | MHz<br>ns                                 |

| デジタル入力 $\square$ ジック・レベル $V_{IL}$ $V_{IH}$ $I_{IL}$ $I_{IH}$    |                                                                                                                                                                  | -0.3<br>0.7×VIO<br>-1<br>-1                                   |                              | 0.3×VIO<br>VIO+0.3<br>+1<br>+1                           | V<br>V<br>μA<br>μA                        |

| デジタル出力<br>データ・フォーマット<br>パイプライン遅延<br>$V_{ m OL}$<br>$V_{ m OH}$  | $I_{SINK} = +500\mu A$ $I_{SOURCE} = -500\mu A$                                                                                                                  | シリアル16ビット・ストレート・バイナリ<br>変換終了後直ちに変換結果が得られます。<br>0.4<br>VIO-0.3 |                              |                                                          | V<br>V                                    |

| 電源<br>VDD<br>VIO<br>VIO範囲<br>スタンバイ時の消費電流 <sup>1、2</sup><br>消費電力 | 仕様性能<br>仕様性能<br>VDDとVIO=5V、25℃<br>VDD=2.5V、100SPSのスループット<br>VDD=2.5V、100kSPSのスループット<br>VDD=2.5V、200kSPSのスループット<br>VDD=5V、100kSPSのスループット<br>VDD=5V、250kSPSのスループット | 2.3<br>2.3<br>1.8                                             | 1<br>1.4<br>1.35<br>2.7<br>4 | 5.5<br>VDD+0.3<br>VDD+0.3<br>50<br>2.4<br>4.8<br>6<br>15 | V<br>V<br>V<br>nA<br>μW<br>mW<br>mW<br>mW |

| 温度範囲 <sup>3</sup><br>仕様性能                                       | $T_{MIN} \sim T_{MAX}$                                                                                                                                           | -40                                                           |                              | +85                                                      | $^{\circ}$                                |

すべてのデジタル入力を必要に応じてVIOまたはGNDに強制設定。アクイジションの実行中。拡張温度範囲については、弊社までお問い合わせください。

**—4** — REV. 0

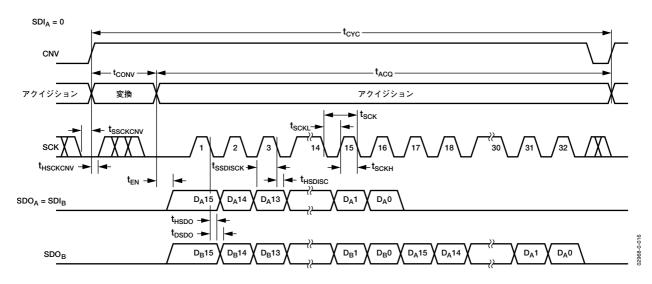

# タイミング仕様

特に指定のない限り、 $-40\sim+85$ °C、 $VIO=2.3\sim5.5$ VまたはVDD+0.3Vのいずれか低い電圧

表4. VDD=4.5~5.5V1

|                                                            | 記号                   | Min | Тур | Max | 単位 |

|------------------------------------------------------------|----------------------|-----|-----|-----|----|

| 変換時間:CNVの立上がりエッジからデータが得られるまでの時間                            | t <sub>CONV</sub>    | 0.5 |     | 2.2 | μs |

| アクイジション時間                                                  | t <sub>ACQ</sub>     | 1.8 |     |     | μs |

| 変換と変換の間隔                                                   | t <sub>CYC</sub>     | 4   |     |     | μs |

| $CNV$ パルス幅( $\overline{CS}$ モード)                           | t <sub>CNVH</sub>    | 10  |     |     | ns |

| $SCK$ サイクル時間( $\overline{CS}$ モード)                         | t <sub>SCK</sub>     | 15  |     |     | ns |

| SCKサイクル時間(チェーン・モード)                                        | t <sub>SCK</sub>     |     |     |     |    |

| VIOが4.5Vを超えるとき                                             |                      | 27  |     |     | ns |

| VIOが3Vを超えるとき                                               |                      | 28  |     |     | ns |

| VIOが2.7Vを超えるとき                                             |                      | 29  |     |     | ns |

| VIOが2.3Vを超えるとき                                             |                      | 30  |     |     | ns |

| SCKのローレベル時間                                                | t <sub>SCKL</sub>    | 7   |     |     | ns |

| SCKのハイレベル時間                                                | t <sub>SCKH</sub>    | 7   |     |     | ns |

| SCKの立下がりエッジからデータの有効性が続く時間                                  | t <sub>HSDO</sub>    | 5   |     |     | ns |

| SCKの立下がりエッジからデータ有効までの遅延                                    | $t_{DSDO}$           |     |     |     |    |

| VIOが4.5Vを超えるとき                                             |                      |     |     | 14  | ns |

| VIOが3Vを超えるとき                                               |                      |     |     | 15  | ns |

| VIOが2.7Vを超えるとき                                             |                      |     |     | 16  | ns |

| VIOが2.3Vを超えるとき                                             |                      |     |     | 17  | ns |

| CNVまたはSDIのローレベルからSDO D15 MSB有効までの時間(CSモード)                 | $t_{\rm EN}$         |     |     |     |    |

| VIOが4.5Vを超えるとき                                             |                      |     |     | 15  | ns |

| VIOが2.7Vを超えるとき                                             |                      |     |     | 18  | ns |

| VIOが2.3Vを超えるとき                                             |                      |     |     | 22  | ns |

| CNVまたはSDIのハイレベルあるいはSCKの最後の立下がりエッジから                        | t <sub>DIS</sub>     |     |     | 25  | ns |

| $SDO$ ハイ・インピーダンスまでの時間( $\overline{CS}$ モード)                |                      |     |     |     |    |

| $CNV$ の立上がりエッジから $SDI$ 有効までのセットアップ時間( $\overline{CS}$ モード) | t <sub>SSDICNV</sub> | 15  |     |     | ns |

| $CNV$ の立上がりエッジから $SDI$ 有効までのホールド時間( $\overline{CS}$ モード)   | t <sub>HSDICNV</sub> | 0   |     |     | ns |

| CNVの立上がりエッジからSCK有効までのセットアップ時間 (チェーン・モード)                   | t <sub>SSCKCNV</sub> | 5   |     |     | ns |

| CNVの立上がりエッジからSCK有効までのホールド時間 (チェーン・モード)                     | t <sub>HSCKCNV</sub> | 5   |     |     | ns |

| SCKの立下がりエッジからSDI有効までのセットアップ時間 (チェーン・モード)                   | t <sub>SSDISCK</sub> | 13  |     |     | ns |

| SCKの立下がりエッジからSDI有効までのホールド時間 (チェーン・モード)                     | t <sub>HSDISCK</sub> | 4   |     |     | ns |

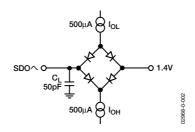

<sup>1</sup> 負荷条件については、図3と図4を参照。

REV. 0 — 5 —

特に指定のない限り、 $-40\sim+85$ ℃、 $VIO=2.3\sim4.5$ VまたはVDD+0.3Vのいずれか低い電圧

表5. VDD=2.3~4.5V1

|                                                                          | 記号                   | Min | Тур | Max | 単位 |

|--------------------------------------------------------------------------|----------------------|-----|-----|-----|----|

| 変換時間:CNVの立上がりエッジからデータが得られるまでの時間                                          | t <sub>CONV</sub>    | 0.7 |     | 3.2 | μs |

| アクイジション時間                                                                | t <sub>ACQ</sub>     | 1.8 |     |     | μs |

| 変換と変換の間隔                                                                 | t <sub>CYC</sub>     | 5   |     |     | μs |

| $CNV$ パルス幅 $(\overline{CS}$ モード)                                         | t <sub>CNVH</sub>    | 10  |     |     | ns |

| $SCK$ サイクル時間( $\overline{CS}$ モード)                                       | t <sub>SCK</sub>     | 25  |     |     | ns |

| SCKサイクル時間 (チェーン・モード)                                                     | t <sub>SCK</sub>     |     |     |     |    |

| VIOが3Vを超えるとき                                                             |                      | 54  |     |     | ns |

| VIOが2.7Vを超えるとき                                                           |                      | 60  |     |     | ns |

| VIOが2.3Vを超えるとき                                                           |                      | 65  |     |     | ns |

| SCKのローレベル時間                                                              | t <sub>SCKL</sub>    | 12  |     |     | ns |

| SCKのハイレベル時間                                                              | t <sub>SCKH</sub>    | 12  |     |     | ns |

| SCKの立下がりエッジからデータの有効性が続く時間                                                | $t_{ m HSDO}$        | 5   |     |     | ns |

| SCKの立下がりエッジからデータ有効までの遅延                                                  | t <sub>DSDO</sub>    |     |     |     |    |

| VIOが3Vを超えるとき                                                             |                      |     |     | 24  | ns |

| VIOが2.7Vを超えるとき                                                           |                      |     |     | 30  | ns |

| VIOが2.3Vを超えるとき                                                           |                      |     |     | 35  | ns |

| $CNV$ または $SDI$ のローレベルから $SDO$ $D15$ $MSB$ 有効までの時間( $\overline{CS}$ モード) | $t_{\rm EN}$         |     |     |     |    |

| VIOが2.7Vを超えるとき                                                           |                      |     |     | 18  | ns |

| VIOが2.3Vを超えるとき                                                           |                      |     |     | 22  | ns |

| CNVまたはSDIのハイレベルあるいはSCKの最後の立下がりエッジから                                      | $t_{ m DIS}$         |     |     | 25  | ns |

| $SDO$ ハイ・インピーダンスまでの時間( $\overline{CS}$ モード)                              |                      |     |     |     |    |

| $CNV$ の立上がりエッジから $SDI$ 有効までのセットアップ時間 ( $\overline{CS}$ モード)              | t <sub>SSDICNV</sub> | 30  |     |     | ns |

| CNVの立上がりエッジからSDI有効までのホールド時間(CSモード)                                       | t <sub>HSDICNV</sub> | 0   |     |     | ns |

| CNVの立上がりエッジからSCK有効までのセットアップ時間 (チェーン・モード)                                 | t <sub>SSCKCNV</sub> | 5   |     |     | ns |

| CNVの立上がりエッジからSCK有効までのホールド時間 (チェーン・モード)                                   | t <sub>HSCKCNV</sub> | 8   |     |     | ns |

| SCKの立下がりエッジからSDI有効までのセットアップ時間 (チェーン・モード)                                 | t <sub>SSDISCK</sub> | 30  |     |     | ns |

| SCKの立下がりエッジからSDI有効までのホールド時間 (チェーン・モード)                                   | t <sub>HSDISCK</sub> | 4   |     |     | ns |

<sup>1</sup> 負荷条件については、図3と図4を参照。

# 絶対最大定格

#### 表6

| パラメータ                                     | 定格值                     |

|-------------------------------------------|-------------------------|

| アナログ入力                                    |                         |

| IN+ <sup>1</sup> , IN- <sup>1</sup> , REF | $GND-0.3V\sim VDD+0.3V$ |

|                                           | または±130mA               |

| 電源電圧                                      |                         |

| GNDに対するVDD、VIO                            | $-0.3 \sim +7 \text{V}$ |

| VIOに対するVDD                                | ±7V                     |

| GNDに対するデジタル入力                             | $-0.3V \sim VIO + 0.3V$ |

| GNDに対するデジタル出力                             | $-0.3V \sim VIO + 0.3V$ |

| 保存温度範囲                                    | -65~150°C               |

| ジャンクション温度                                 | 150℃                    |

| $	heta_{	ext{JA}}$ 熱抵抗                    | 200℃/W (MSOP-10)        |

| $	heta_{ m JC}$ 熱抵抗                       | 44℃/W (MSOP-10)         |

| リードピン温度範囲                                 |                         |

| ベーキング時間(60秒)                              | 215℃                    |

| 赤外線(15秒)                                  | 220℃                    |

絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作に関するセクションに記載されている規定値以上でのデバイス動作を定めたものではありません。長時間デバイスを絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

#### 注意

ESD (静電放電)の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

図3. デジタル・インターフェース・タイミングの負荷回路

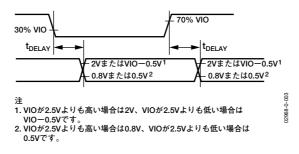

図4. タイミングの電圧レベル

REV. 0 —7—

<sup>1「</sup>アナログ入力」を参照。

# ピン配置と機能の説明

図5. 10ピンのMSOPおよびQFN (LFCSP) のピン配置

表7. ピン機能の説明

| ピン番号 | 記号  | タイプ1 | 機能                                                                                                                                                                                                                                                                                                                                                                                           |

|------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | REF | AI   | リファレンス入力電圧。REFの範囲は $0.5V \sim VDD$ で、GNDピンを基準とします。このピンの近くに $10\mu$ Fのコンデンサを外付けして、デカップリングしてください。                                                                                                                                                                                                                                                                                              |

| 2    | VDD | P    | 電源                                                                                                                                                                                                                                                                                                                                                                                           |

| 3    | IN+ | AI   | アナログ入力。 $IN$ -を基準とします。電圧範囲は $IN$ +と $IN$ -間の差であり、 $0V \sim V_{REF}$ です。                                                                                                                                                                                                                                                                                                                      |

| 4    | IN- | AI   | アナログ入力グラウンド・センス。アナログ・グラウンド・プレーンまたはリモート・センス・グラウンドに接続します。                                                                                                                                                                                                                                                                                                                                      |

| 5    | GND | P    | 電源グラウンド                                                                                                                                                                                                                                                                                                                                                                                      |

| 6    | CNV | DI   | 変換入力。この入力には複数の機能があります。立上がりエッジで変換を開始し、デバイスのインターフェース・モード(チェーン・モードか $\overline{CS}$ モード)を選択します。 $\overline{CS}$ モードでは、CNVがローレベルのときにSDOピンがイネーブルになります。チェーン・モードでは、CNVがハイレベルのときにデータが読み出されます。                                                                                                                                                                                                        |

| 7    | SDO | DO   | シリアル・データ出力。このピンから変換結果を出力します。SCKと同期します。                                                                                                                                                                                                                                                                                                                                                       |

| 8    | SCK | DI   | シリアル・データ・クロック入力。デバイスが選択されるときに、このクロックによって変換<br>結果をシフト出力します。                                                                                                                                                                                                                                                                                                                                   |

| 9    | SDI | DI   | シリアル・データ入力。この入力には複数の機能があります。ADCのインターフェース・モードを次のように選択します。CNVの立上がりエッジのときにSDIがローレベルであれば、チェーン・モードが選択されます。このモードのとき、2個以上のADCの変換結果を1本のSDOライン上にデイジーチェーンするためのデータ入力としてSDIを使用します。SDI上のデジタル・データ・レベルは、16 SCKサイクルの遅延でSDOから出力されます。CNVの立上がりエッジのときにSDIがハイレベルであれば、 $\overline{\text{CS}}$ モードが選択されます。このモードでは、SDIまたはCNVのどちらかがローレベルになるときにシリアル出力信号をイネーブルにできます。変換の終了時にSDIまたはCNVがローレベルであれば、BUSYインジケータ機能がイネーブルになります。 |

| 10   | VIO | P    | 入出力インターフェース用のデジタル電源。公称値は、ホスト・インターフェースと同じ電源<br>電圧(1.8V、2.5V、3V、5V)です。                                                                                                                                                                                                                                                                                                                         |

<sup>」</sup>AI=アナログ入力、DI=デジタル入力、DO=デジタル出力、P=電源

\_8\_ REV. 0

### 用語の説明

#### 積分非直線性誤差(INL)

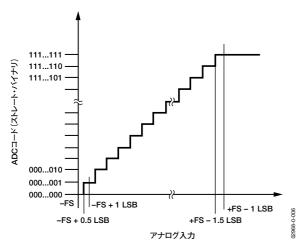

この仕様は、負側のフルスケールと正側のフルスケールを結ぶ 直線と実際の各コード出力との偏差を意味します。負側のフル スケールとして使用するポイントは、最初のコード遷移よりも 1/2LSB下にあります。正側のフルスケールは、最後のコード 遷移よりも1+1/2LSB上のレベルです。偏差とは、各コードの 中心と真の直線との距離の測定値です(図25)。

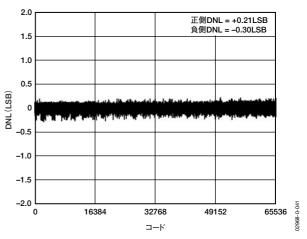

#### 微分非直線性誤差 (DNL)

理想的なADCでは、コード遷移は1LSB離れた位置で発生します。DNLは、この理想値からの最大偏差です。通常は、ノー・ミスコードが保証される分解能で規定します。

#### オフセット誤差

最初の遷移は、アナログ・グラウンドよりも1/2LSB上のレベルで発生します  $(0\sim5V$ で $38.1\mu V)$ 。オフセット誤差とは、そのポイントからの実際の遷移の偏差を意味します。

#### ゲイン誤差

最後の遷移(111…10から111…11)は、公称フルスケールよりも1+1/2LSB下のアナログ電圧で発生します( $0\sim5$ Vで4.999886V)。ゲイン誤差とは、オフセットの調整が終了した後で、最後の遷移の実際のレベルが理想的なレベルと相違する偏差のことです。

#### スプリアスフリー・ダイナミック・レンジ (SFDR)

SFDRとは、入力信号のrms振幅値とピーク・スプリアス信号のrms値の差をデシベル (dB) の単位で表した数値です。

#### 有効ビット数(ENOB)

ENOBとは、正弦波を入力したときの分解能の測定値です。 S/(N+D)に関係し、以下の式で求めます。単位はビットで表します。

$ENOB = (S/[N+D]_{dB} - 1.76)/6.02)$

#### 全高調波歪み(THD)

THDとは、最初の5つの高調波成分のrms値の総和と、フルスケール入力信号のrms値との比であり、dB単位で表します。

#### 信号対ノイズ比(S/N比)

S/N比とは、実際の入力信号のrms値と、ナイキスト周波数よりも下の全スペクトル成分のrms値総和から高調波成分とDC成分を除いた値との比です。dB単位で表します。

#### 信号/ノイズ&歪み(S/[N+D])

S/(N+D)とは、実際の入力信号のrms値と、ナイキスト周波数よりも下の全スペクトル成分のrms値総和(DC以外の高調波成分を含む)との比です。dB単位で表します。

#### アパーチャ遅延

アパーチャ遅延とはアクイジション性能の目安を表す仕様であり、CNV入力の立上がりエッジから入力信号が変換のためにホールドされるまでの時間の測定値です。

#### 過渡応答

過渡応答とは、入力にフルスケール・ステップ関数が与えられてから、AD7685がその入力を高精度に収集するまでに要する時間を表します。

REV. 0 — 9 —

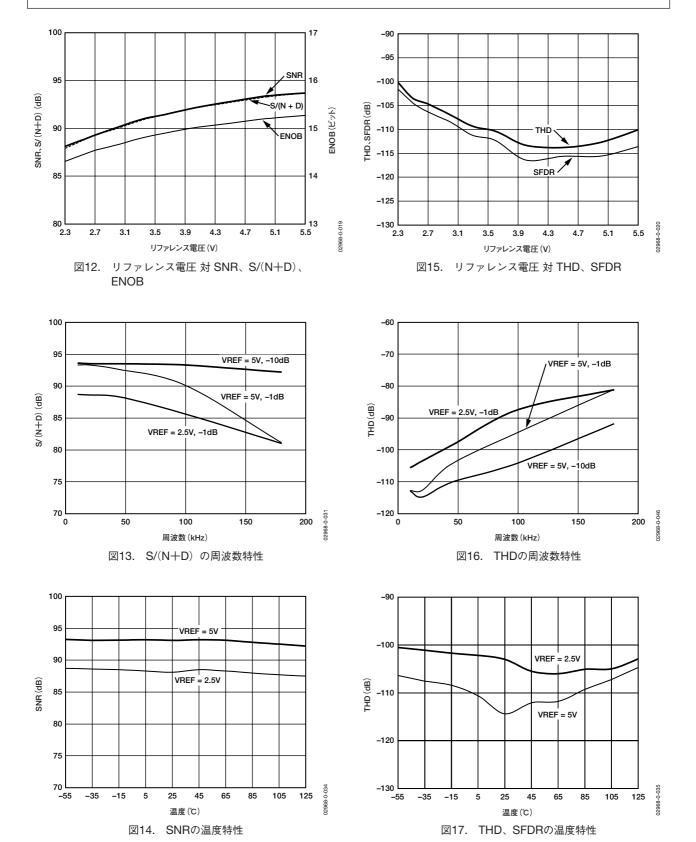

## 代表的な性能特性

図6. コード 対 積分非直線性

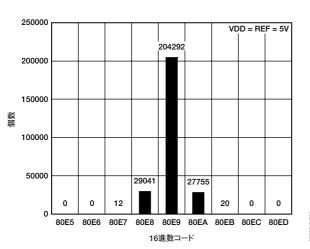

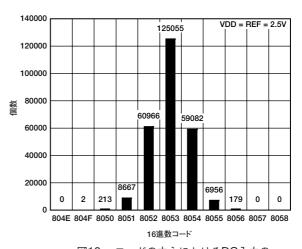

図7. コードの中心におけるDC入力の ヒストグラム

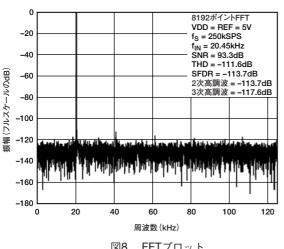

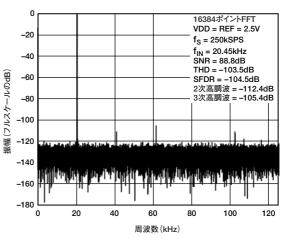

図8. FFTプロット

図9. コード 対 微分非直線性

図10. コードの中心におけるDC入力の ヒストグラム

図11. FFTプロット

— 10 — REV. 0

REV. 0 — 11 —

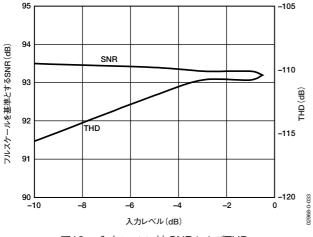

図18. 入力レベル 対 SNRおよびTHD

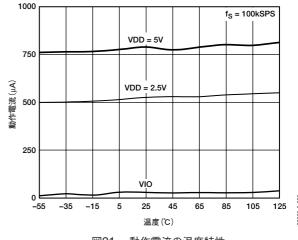

図21. 動作電流の温度特性

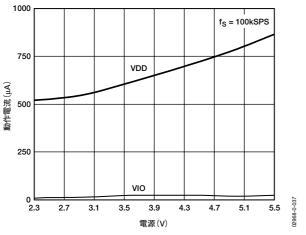

図19. 電源 対 動作電流

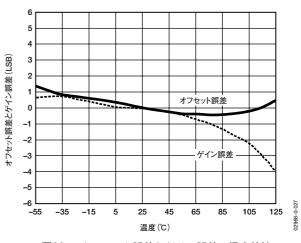

図22. オフセット誤差とゲイン誤差の温度特性

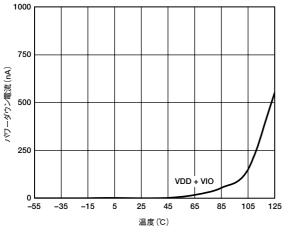

図20. パワーダウン電流の温度特性

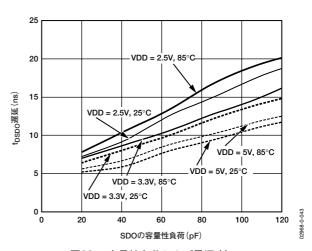

図23. 容量性負荷および電源 対  $t_{DSDO}$

— 12 — REV. 0

#### 回路情報

AD7685は、逐次比較型アーキテクチャを採用する高速、低消 費電力、単電源動作の高精度16ビットADCです。

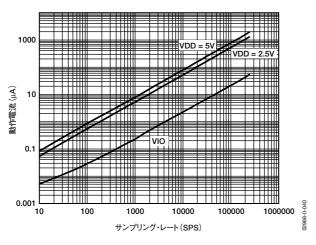

AD7685は1秒あたり25万サンプル(250kSPS)を変換し、変換と変換の間にパワーダウン状態にすることができます。たとえば100SPSで動作するとき、消費電力は2.5Vの電源時でわずか1.35 $\mu W$ (typ)になるため、バッテリ駆動アプリケーションに最適です。

AD7685にはオンチップのトラック&ホールドがあり、パイプライン遅延やレイテンシがまったく発生しないため、マルチプレクサを使用した多チャンネル・アプリケーションに最適です。

AD7685は2.3~5.5Vの電圧範囲の電源動作で仕様が規定されており、1.8~5Vのどんなデジタル・ロジック・ファミリーともインターフェースが可能です。10ピンMSOPまたは小型サイズの10ピンQFN(LFCSP)パッケージの採用によって省スペースを実現し、柔軟な設定が可能になっています。

AD7685は、AD7686、AD7687、AD7688と完全にピン互換です。

#### コンバータの動作

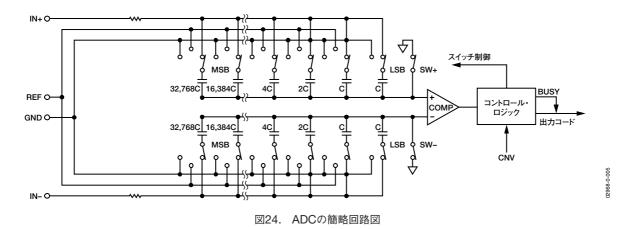

AD7685は、電荷再分配型DACをベースとする逐次比較型ADCです。図24に、このADCの簡略回路図を示します。容量性DACはバイナリの重付けをされた16個のコンデンサから成る2個の同一のアレイで構成され、2つのコンパレータ入力に接続されています。

アクイジション動作の実行中に、コンパレータの入力に接続さ れたアレイの端子がSW+とSW-によってGNDに接続します。 独立したスイッチはすべて、アナログ入力に接続しています。 このようにして、コンデンサ・アレイをサンプリング・コンデン サとして使用し、IN+およびIN-入力上でアナログ信号を取り込 みます。アクイジションが終了して、CNV入力がハイレベルに なると、変換動作を開始します。変換が始まると、最初にSW+ とSW-が開きます。次いで、2個のコンデンサ・アレイが入力か ら切断され、GND入力に接続します。このため、アクイジショ ンの最後に取り込まれた入力IN+とIN-間の差動電圧がコンパ レータの入力に入り、コンパレータが不平衡の状態になります。 コンデンサ・アレイの各エレメントをGNDとREFの間でスイッ チングすることにより、コンパレータ入力がバイナリの重付け をされた電圧ステップ( $V_{\text{REF}}/2$ 、 $V_{\text{REF}}/4$ 、... $V_{\text{REF}}/65536$ )で変 化します。コントロール・ロジックでこれらのスイッチをトグ ルして (MSBファースト)、コンパレータを再び平衡状態に戻 します。このプロセスが終了すると、AD7685はパワーダウン 状態になり、アクイジションの動作に戻り、コントロール・ロ ジックがADCの出力コードとBUSY信号インジケータを生成し ます。

AD7685には変換クロックが内蔵されているため、変換プロセスでシリアル・クロック (SCK) は必要ありません。

REV. 0 — 13 —

#### 伝達関数

AD7685の理想的な伝達特性を図25と表8に示します。

図25. ADCの理想的な伝達関数

#### 表8. 出力コードと理想的な入力電圧

| 説明                       | アナログ入力<br>V <sub>REF</sub> =5V | デジタル出力コード<br>(16進数値)      |

|--------------------------|--------------------------------|---------------------------|

| FSR-1LSB<br>ミッドスケール+1LSB | 4.999924V<br>2.500076V         | FFFF <sup>1</sup><br>8001 |

| ミッドスケール                  | 2.5V                           | 8000                      |

| ミッドスケールー1LSB             | 2.499924V                      | 7FFF                      |

| -FSR+1LSB                | 76.3µV                         | 0001                      |

| -FSR                     | 0V                             | 00002                     |

<sup>」</sup>これは、オーバーレンジのアナログ入力コードでもあります( $V_{\rm IN+}-V_{\rm IN}>V_{\rm REF}-$

$V_{GND}$ )。  $^2$  これは、アンダーレンジのアナログ入力コードでもあります  $(V_{IN^+} - V_{IN} {<} V_{GND})$ 。

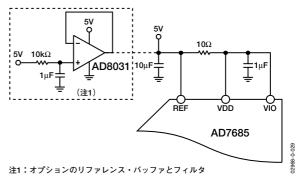

注1:電圧リファレンスの選択については、「電圧リファレンス入力」を参照。

注:C<sub>REF</sub>は通常、10μFのセラミック・コンデンサ (X5R) です。 注3:「ドライバ・アンプの選択」を参照。

注4: オプションのフィルタです。「アナログ入力」を参照。 注5: 最も便利なインターフェース・モードについては、「デジタル・インターフェース」を参照。

図26. 複数の電源を使用する代表的なアプリケーション接続図

代表的な接続図

複数の電源を利用する場合のAD7685の推奨接続図の例を図26 に示します。

-14-REV. 0

#### アナログ入力

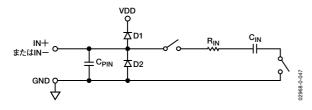

図27は、AD7685の入力構造の等価回路図です。

D1とD2の2個のダイオードが、IN+とIN-の各アナログ入力に対しESD保護を行います。アナログ入力信号が電源電圧範囲を 0.3V以上超えないよう注意する必要があります。この値を超えると、上記のダイオードが順方向にバイアスされて、電流が流れ始めます。ダイオードは、最大130mAの順方向バイアス電流を処理できます。たとえば、入力バッファの(U1)電源が VDDと異なるときに、このような状況が発生する可能性があります。この場合、短絡電流制限機能がある入力バッファを使用してデバイスを保護してください。

図27. アナログ入力等価回路

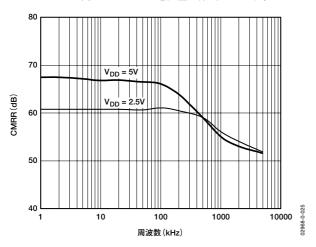

このアナログ入力構造により、IN+とIN-間の差動信号のサンプリングが可能になります。この差動入力を使用することによって、図28に示すように2つの入力に与えられた小さな同期信号が除去されます。図28に、代表的なCMRRの周波数特性を示します。たとえば、IN-入力を使用してリモート信号グラウンドをセンシングすることにより、センサーとADCのローカル・グラウンド間のグラウンド電位差が除去されます。

図28. アナログ入力CMRRの周波数特性

アクイジション動作では、コンデンサ $C_{PIN}$ と $R_{IN}$ および $C_{IN}$ の直列接続によって形成されるネットワークとの並列接続として、アナログ入力(IN+またはIN-)のインピーダンスをモデル化できます。 $C_{PIN}$ は主としてピン容量です。 $R_{IN}$ は通常 $3k\Omega$ で、いくつかの直列抵抗とスイッチのオン抵抗を含みます。 $C_{IN}$ は通常30pFで、主にADCのサンプリング・コンデンサとなります。スイッチが開く変換動作の実行中、入力インピーダンスは $C_{PIN}$ に制限されます。 $R_{IN}$ と $C_{IN}$ は、望ましくない折り返し成分を低減し、ノイズを制限する単極ローパス・フィルタを構成します。

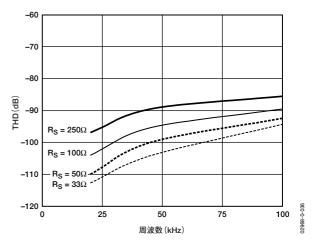

駆動回路の信号源インピーダンスが低いときに、AD7685を直接駆動できます。信号源インピーダンスが大きくなると、AC性能、特に全高調波歪み (THD) 特性に大きな影響を与えます。DC性能のほうは、入力インピーダンスによってそれほど影響を受けません。最大の信号源インピーダンスは、許容可能なTHDの大きさに依存します。図29に示すように、THDは信号源インピーダンスと最大入力周波数に比例して劣化します。

図29. アナログ入力周波数と信号源抵抗値 対 THD

REV. 0 — 15 —

#### ドライバ・アンプの選択

AD7685は簡単に駆動できますが、ドライバ・アンプは次の条件を満たす必要があります。

• AD7685のSNRと遷移ノイズ性能を維持するには、ドライバ・アンプによるノイズを可能な限り低く抑える必要があります。ただし、AD7685のノイズはその他の16ビットADCよりも大幅に低いため、規定のシステム・ノイズ仕様を満たすためにノイズの比較的大きいアンプで駆動することができます。アンプから発生するノイズは、 $R_{IN}$ と $C_{IN}$ で構成されるAD7685のアナログ入力回路のローパス・フィルタや、外部フィルタがあればこれによって除去されます。AD7685のノイズの代表値は $35\mu V$  rmsであることから、次の式によりアンプに起因するSNRの低下を求めることができます。

$$SNR_{LOSS} = 20\log\left(\frac{35}{\sqrt{35^2 + \frac{\pi}{2} f_{-3dB} (Ne_N)^2}}\right)$$

ここで、

$f_{-3dB}$ は、AD7685の-3dB入力帯域幅(2MHz)、または入力フィルタを使用する場合はそのカットオフ周波数です。

Nは、アンプのノイズ・ゲインです(たとえば、バッファ構成の場合は+1)。

$e_N$ は、オペアンプの等価入力ノイズ電圧( $nV/\sqrt{Hz}$ )です。

- ACアプリケーションの場合、ドライバはAD7685に適した THD性能を備えている必要があります。図16に、AD7685 のTHDの周波数特性を示します。

- マルチチャンネルのマルチプレクサ・アプリケーションの 場合、ドライバ・アンプとAD7685のアナログ入力回路は、 コンデンサ・アレイのフルスケール・ステップに対して16 ビット・レベル (0.0015%) でセトリングしなければなり ません。アンプのデータシートでは、一般に0.1~0.01%で のセトリングが規定されています。これは16ビット・レベ ルでのセトリング・タイムと大幅に異なることがあるため、 ドライバを選択する前に確認する必要があります。

表9. 推奨ドライバ・アンプ

| アンプ            | 代表的なアプリケーション    |

|----------------|-----------------|

| AD8021         | きわめて低ノイズで高周波数   |

| AD8022         | 低ノイズで高周波数       |

| OP184          | 低消費電力、低ノイズ、低周波数 |

| AD8605, AD8615 | 5V単電源、低消費電力     |

| AD8519         | 小型、低消費電力、低周波数   |

| AD8031         | 高周波数で低消費電力      |

#### 電圧リファレンス入力

AD7685の電圧リファレンス入力(REF)は変動する入力インピーダンスをもっているため、「レイアウト」で説明するように、低インピーダンスの信号源で駆動し、REFとGNDのピンの間にコンデンサを外付けして、十分にデカップリングを行う必要があります。

AD8031やAD8605を使用するリファレンス・バッファなど、インピーダンスがきわめて低い信号源でREFを駆動するとき、最適な性能を得るためには $10\mu$ F(X5R、0805サイズ)のセラミック・チップ・コンデンサが適切です。

バッファしていないリファレンス電圧を使用する場合、デカップリングの値は、使用するリファレンスによって異なります。たとえば、温度ドリフトの低いリファレンスADR43xを使用する場合は、 $22\mu F$ (X5R、1206 サイズ)のセラミック・チップ・コンデンサによって最適な性能が得られます。

必要に応じて、 $2.2\mu$ Fまでの小さいリファレンス・デカップリング用コンデンサを使用すれば、性能、特にDNLに対する影響を最小にすることができます。

#### 電源

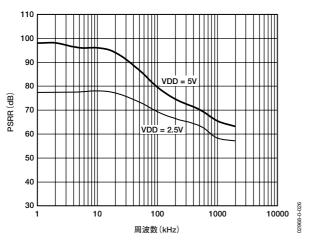

AD7685の仕様は、2.3~5.5Vの広い動作電圧範囲で規定されています。ほかの低電圧コンバータと異なりノイズが低いため、かなり高い性能の16ビット分解能システムを設計することができます。AD7685は、コア電源VDDとデジタル入出力インターフェース電源VIOの2本の電源ピンを使用します。VIOによって、1.8V~VDDの電源で動作するロジックと直接のインターフェースが可能になります。必要な電源の数を減らすために、VIOとVDDを接続することができます。VIOとVDDの電源シーケンスは、どちらが先でもかまいません。さらに、AD7685は、広い周波数範囲で電源変動に対しきわめて高い安定性があります。図30に、PSRRの周波数特性を示します。

図30. PSRRの周波数特性

変換サイクルが終了するごとにAD7685は自動的にパワーダウンするため、図31に示すように消費電力がサンプリング・レートに比例して直線的に変化します。このため、サンプリング・レートが低く(数Hzにも対応)、低消費電力のバッテリ駆動アプリケーションに最適です。

図31. サンプリング・レート 対 動作電流

#### リファレンスからADCへの電源供給

簡単なアプリケーションでは、図32に示すリファレンス回路を使用し、動作電流が低いAD7685に直接電源を供給できます。 リファレンス・ラインは、以下のいずれかによって駆動できます。

- システム電源から直接駆動

- ADR43xなどの高い電流出力能力を備えたリファレンス電圧

- 図32に示すような、システム電源のフィルタ処理機能も備えたAD8031などのリファレンス・バッファ

図32. アプリケーション回路の例

REV. 0 — 17 —

#### デジタル・インターフェース

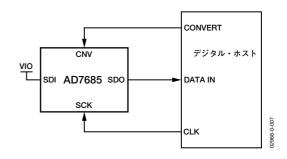

AD7685のピンの数は少ないですが、シリアル・インターフェース・モードによりきわめて高い柔軟性があります。

AD7685は $\overline{\text{CS}}$ モードのときに、SPI、QSPI、デジタル・ホスト、Blackfin®ADSP-BF53xやADSP-219xなどのDSPと互換性があります。このインターフェースは、3線式または4線式のいずれも使用できます。CNV、SCK、SDOの信号を使用する3線式インターフェースでは、配線接続数が少ないため、絶縁アプリケーションなどに向いています。SDI、CNV、SCK、SDOの信号を使用する4線式インターフェースでは、変換を開始するCNV入力を読出しタイミング(SDI)と無関係にすることができます。これは、低ジッタのサンプリングや同時サンプリングのアプリケーションに向いています。

AD7685をチェーン・モードに設定すると、SDI入力を使用し、シフト・レジスタと同じ1本のデータ・ライン上に複数のADCをカスケード接続するデイジーチェーン機能を利用できます。

AD7685の動作モードは、CNVのエッジが立ち上がるときの SDIのレベルによって決まります。SDIがハイレベルのときは  $\overline{\text{CS}}$ モード、SDIがローレベルのときはチェーン・モードが選択 されます。SDIのホールド時間により、SDIとCNVが相互に接 続されているときはチェーン・モードが常に選択されます。

でSモードのときは、オプションとしてデータビットの前に開始 ビットを強制的に設定することもできます。この開始ビットを BUSY信号インジケータとして使用し、デジタル・ホストに割 込みをかけ、データの読出し動作をトリガできます。BUSY信 号インジケータを使用しない場合は、最大変換時間が経過した 後で読出しを行わなければなりません。

BUSYインジケータ機能は、以下の条件のときにイネーブルになります。

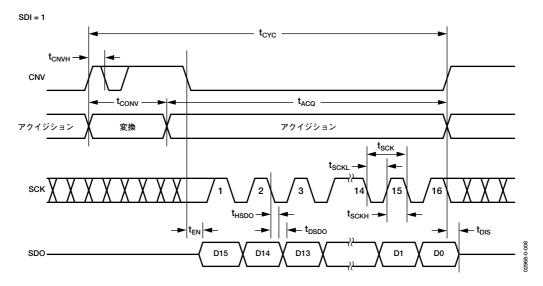

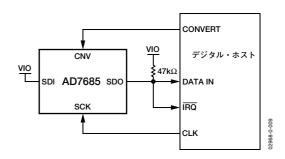

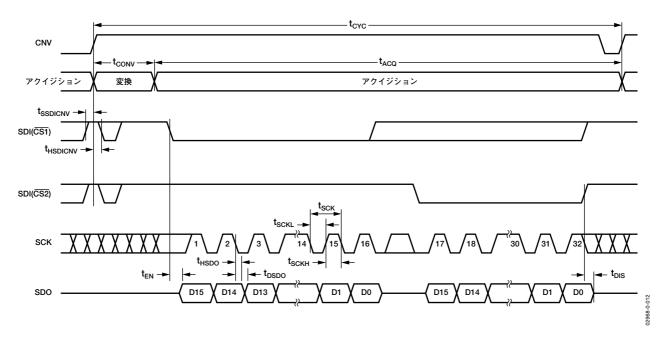

#### BUSYインジケータを使用しない3線式のCSモード

このモードは通常、1個のAD7685をSPI互換のデジタル・ホストに接続するときに使用します。図33にこのモードの接続図、図34にそのタイミング図を示します。

SDIがVIOに接続されているとき、CNVの立上がりエッジで変換を開始し、CSモードが選択され、SDOをハイ・インピーダンスの状態に強制設定します。変換を開始すると、CNVの状態に関係なく変換が完了するまで続けます。このような動作設定は、CNVをローレベルに設定して、たとえばアナログ・マルチプレクサなどのその他のSPIデバイスを選択する場合に便利です。このとき、BUSY信号インジケータが発生しないように、最小変換時間が経過する前にCNVをハイレベルに戻し、最大変換時間が経過するまでCNVをハイレベルに保持する必要があります。変換が終了した時点でAD7685はアクイジション・サイクルに入り、パワーダウンします。CNVがローレベルになると、MSBがSDOに出力されます。残りのデータビットは、その後のSCKの立下がりエッジで順次クロック出力されます。SCKの立上がりと立下がりの両方のエッジでデータが有効になります。立上がりエッジでデータを取り込むことも可能ですが、

SCKの立下がりエッジを使用するデジタル・ホストのほうが、十分なホールド時間があれば、読出しが速くできます。SCKの16番目の立下がりエッジ後、またはCNVがハイレベルになるときのいずれか早いほうの時点で、SDOがハイ・インピーダンスの状態に戻ります。

図33. BUSYインジケータを使用しない3線式OSモードの 接続図(SDIがハイレベル)

図34. BUSYインジケータを使用しない3線式 $\overline{\text{CS}}$ モードのシリアル・インターフェース・タイミング図(SDIがハイレベル)

REV. 0 — 19 —

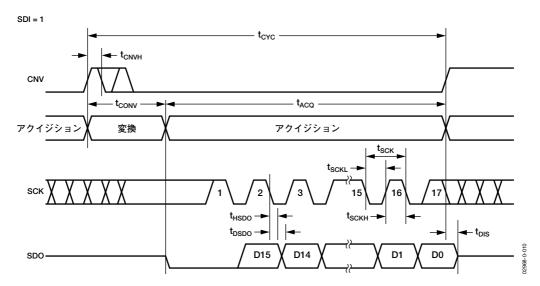

#### BUSYインジケータを使用した3線式のCSモード

このモードは通常、1個のAD7685を割込み入力付きのSPI互換 デジタル・ホストに接続するときに使用します。

図35にこのモードの接続図、図36にそのタイミング図を示します。

SDIがVIOに接続されているとき、CNVの立上がりエッジで変換を開始し、CSモードが選択され、SDOをハイ・インピーダンスの状態に強制設定します。SDOはCNVの状態に関係なく、変換動作が完了するまでハイ・インピーダンスの状態に維持されます。最小変換時間が経過する前にCNVを使用して、アナログ・マルチプレクサなどのその他のSPIデバイスを選択することができます。このとき、BUSY信号インジケータが発生するように、最小変換時間が経過する前にCNVをローレベルに戻し、最大変換時間が経過するまでCNVをローレベルに保持する必要があります。変換が終了した時点で、SDOはハイ・インピーダンスの状態からローレベルに遷移します。SDOライン上のブルアップにより、この遷移を割込み信号として、デジタル・ホストが制御するデータの読出しを開始することができます。その後、AD7685はアクイジション・サイクルに入り、パワーダウンします。データビットは、その後のSCKの立下がりエッジで

MSBファーストで順次クロック出力されます。SCKの立上がりと立下がりの両方のエッジで、データが有効になります。立上がりエッジでデータを取り込むことも可能ですが、SCKの立下がりエッジを使用するデジタル・ホストのほうが、十分なホールド時間があれば、読出し速度が速くなります。オプションの17番目のSCK立下がりエッジ後、またはCNVがハイレベルになるときのいずれか早いほうの時点で、SDOがハイ・インピーダンスの状態に戻ります。

図35. BUSYインジケータを使用した3線式OSモードの 接続図 (SDIがハイレベル)

図36. BUSYインジケータを使用した3線式OSモードのシリアル・インターフェース・タイミング図(SDIがハイレベル)

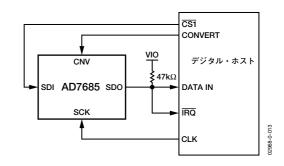

#### BUSYインジケータを使用しない4線式のCSモード

このモードは通常、複数のAD7685をSPI互換のデジタル・ホストに接続するときに使用します。

図37に2個のAD7685を使用する場合の接続図、図38にそのタイミング図を示します。

SDIがハイレベルのとき、CNVの立上がりエッジで変換を開始し、 $\overline{CS}$ モードが選択され、SDOをハイ・インピーダンスの状態に強制設定します。このモードのとき、変換サイクルとその後のデータ読出しの実行中はCNVをハイレベルに保持しなければなりません(SDIとCNVがローレベルであれば、SDOもローレベルに駆動されます)。最小変換時間が経過する前にSDIを使用して、アナログ・マルチプレクサなどのその他のSPIデバイスを選択できます。このとき、BUSY信号インジケータが発生

しないように、最小変換時間が経過する前にSDIをハイレベルに戻し、最大変換時間が経過するまでSDIをハイレベルに保持しなければなりません。変換が終了した時点でAD7685はアクイジション・サイクルに入り、パワーダウンします。SDI入力をローレベルに設定し、MSBをSDOに出力することにより、各ADCの変換結果を読み出すことができます。残りのデータビットは、その後のSCKのエッジで順次クロック出力されます。SCKの立上がりと立下がりの両方のエッジで、データが有効になります。立上がりエッジでデータを取り込むことも可能ですが、SCKの立下がりエッジを使用するデジタル・ホストのほうが、十分なホールド時間があれば、読出し速度が速くなります。SCKの16番目の立下がりエッジ後、またはSDIがハイレベルになるときのいずれか早いほうの時点で、SDOがハイ・インピーダンスの状態に戻り、もう1個のAD7685の読出しができます。

図37. BUSYインジケータを使用しない4線式 CSモードの接続図

図38. BUSYインジケータを使用しない4線式CSモードのシリアル・インターフェース・タイミング図

REV. 0 — 21 —

#### BUSYインジケータを使用した4線式のCSモード

このモードは通常、1個のAD7685を割込み入力付きのSPI互換デジタル・ホストに接続し、アナログ入力のサンプリングに使用するCNV入力をデータ読出しの選択に使用する信号とは無関係に維持したい場合に使用します。これは、CNVに低いジッタが必要なアプリケーションで特に重要な条件となります。

図39にこのモードの接続図、図40にそのタイミング図を示します。

SDIがハイレベルのとき、CNVの立上がりエッジで変換を開始し、 (ST モードが選択され、SDOをハイ・インピーダンスの状態に強制設定します。このモードのとき、変換サイクルとその後のデータ読出しの実行中はCNVをハイレベルに保持しなければなりません(SDIとCNVがローレベルであれば、SDOもローレベルに駆動されます)。最小変換時間が経過する前にSDIを使用して、アナログ・マルチプレクサなどのその他のSPIデバイスを選択できます。このとき、BUSY信号インジケータが発生するように、最小変換時間が経過する前にSDIをローレベルに戻し、最大変換時間が経過する前にSDIをローレベルに戻し、最大変換時間が経過するまでSDIをローレベルに保持しなければなりません。変換が終了した時点で、SDOはハイ・インピーダンスの状態からローレベルに遷移します。SDOライン上のプルアップにより、この遷移を割込み信号として、デジタル・ホストが制御するデータ読出しを開始することができま

す。その後、AD7685はアクイジション・サイクルに入り、パワーダウンします。データビットは、その後のSCKの立下がりエッジでMSBファーストで順次クロック出力されます。SCKの立上がりと立下がりの両方のエッジで、データが有効になります。立上がりエッジでデータを取り込むことも可能ですが、SCKの立下がりエッジを使用するデジタル・ホストのほうが、十分なホールド時間があれば、読出し速度が速くなります。オプションの17番目のSCK立下がりエッジ後、またはSDIがハイレベルになるときのいずれか早いほうの時点で、SDOがハイ・インピーダンスの状態に戻ります。

図39. BUSYインジケータを使用した4線式<del>CS</del>モードの 接続図

図40. BUSYインジケータを使用した4線式 $\overline{\text{CS}}$ モードのシリアル・インターフェース・タイミング図

- 22 - REV. 0

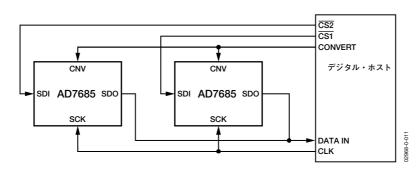

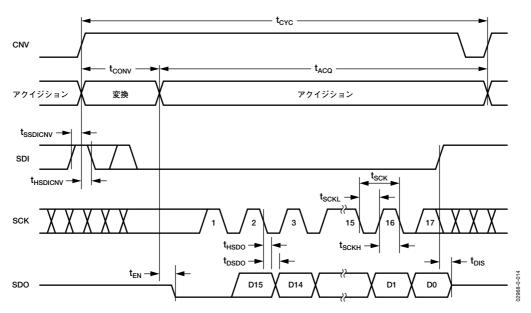

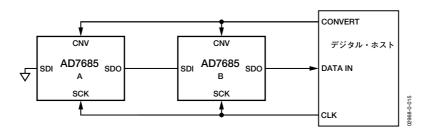

#### チェーン・モード

このモードでは、複数のAD7685を3線式シリアル・インターフェース上でデイジーチェーン接続できます。複数のコンバータを使用する絶縁アプリケーションやインターフェースに限界のあるシステムで部品数と配線数を少なくしなければならない場合に、この機能は便利です。データの読出しは、シフト・レジスタのクロック動作と同じです。

図41に2個のAD7685を使用する場合の接続図、図42にこの場合のタイミング図を示します。

SDIとCNVがローレベルのときに、SDOがローレベルに駆動されます。SCKがローレベルのとき、CNVの立上がりエッジで変換を開始し、チェーン・モードが選択されます。このモードのとき、変換サイクルとその後のデータ読出しの実行中、CNVがハイレベルに保持されます。変換が終了した時点で、MSBがSDOに出力され、AD7685はアクイジション・サイクルに入り、

パワーダウンします。内部シフト・レジスタに格納されている 残りのデータビットは、その後のSCKの立下がりエッジでク ロック出力されます。各ADCで、SDIが内部シフト・レジスタ にデータを入力し、SCKの立下がりエッジでクロック入力され ます。チェーン内の各ADCはデータをMSBファーストで出力 しますが、N個のADCの読出しには16×N個のクロックが必要 です。SCKの立上がりと立下がりの両方のエッジで、データが 有効になります。立上がりエッジでデータを取り込むことも可 能ですが、SCKの立下がりエッジを使用するデジタル・ホスト のほうが、十分なホールド時間があれば、読出し速度が速くな り、その結果多くのAD7685をチェーン内に接続できます。最 大変換レートは、合計読出時間のために低速化することがあり ます。たとえば、デジタル・ホストのセットアップ時間を5ns とし、3Vインターフェースを使用する場合、200kSPSの変換 レートでAD7685を最大5個まで3線ポート上でデイジーチェー ン接続できます。

図41. チェーン・モードの接続図

図42. チェーン・モードのシリアル・インターフェース・タイミング図

REV. 0 — 23 —

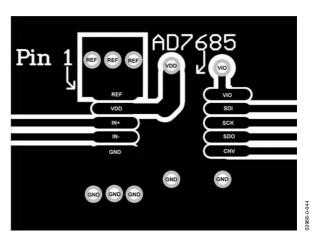

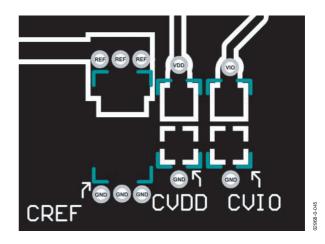

# アプリケーションのヒント

#### レイアウト

AD7685を実装するPCボードは、アナログ回路とデジタル回路を分離し、ボード内にそれぞれをまとめて配置するように設計してください。AD7685のピンはアナログ信号がすべて左側、デジタル信号がすべて右側に配列されているため、このような配置が簡単にできます。

AD7685の真下にシールドとしてグラウンド・プレーンを配置する場合を除き、チップにノイズが結合しないように、デバイスの真下にデジタル・ラインを通さないでください。CNVやクロックなどの高速スイッチング信号がアナログ信号経路の近くを通らないようにします。また、デジタル信号とアナログ信号は交差しないようにしてください。

少なくとも1つのグラウンド・プレーンを使用してください。 共通のグラウンド・プレーンでもよいし、アナログ回路部とデジタル回路部を分離してもよいでしょう。後者の場合は、デジタル・グラウンド・プレーンとアナログ・グラウンド・プレーンをAD7685の真下で接続してください。

AD7685の電圧リファレンス入力REFは、変動する入力インピーダンスをもっているため、デカップリングによって寄生インダクタンスを抑える必要があります。そのために、リファレンスをデカップリングするセラミック・コンデンサをREFピンとGNDピンの近く、理想的には真上に配置して、低インピーダンスの太いパターン配線で接続します。

最後に、VDDとVIOの電源を容量が100nF程度のセラミック・コンデンサでデカップリングしてください。その際、セラミック・コンデンサをAD7685の近くに配置し、太くて短いパターン配線で接続することによって、低インピーダンスの信号経路を作り、電源ラインに対するグリッチの影響を低減する必要があります。

このようなルールに基づくレイアウト例を図43と図44に示します。

#### AD7685の性能評価

AD7685のその他の推奨レイアウトは、AD7685の評価用ボード (EVAL-AD7685) の説明書に記載されています。評価用ボード のパッケージには、組立ておよびテストが完了している評価用ボード、説明書、EVAL-CONTROL BRD2によってPCからボードを制御するためのソフトウェアが同梱されています。

図43. AD7685のレイアウト例(上面層)

図44. AD7685のレイアウト例(底面層)

— 24 — REV. 0

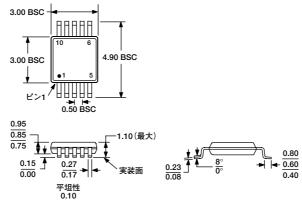

# 外形寸法

JEDEC規格MO-187BAに準拠

図45. 10ピンMSOP (RM-10)

寸法単位:mm

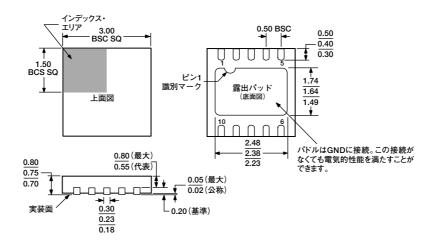

図46. 10ピンQFN (LFCSP) 3mm×3mmのボディー (CP-10-9) 寸法単位:mm

REV. 0 — 25 —

### オーダー・ガイド

| 製品                             | 積分非直線性      | 温度範囲     | パッケージ (オプション) | 出荷形態、数量   | マーキング |

|--------------------------------|-------------|----------|---------------|-----------|-------|

| AD7685BRM                      | ±3LSB (max) | -40~+85℃ | MSOP (RM-10)  | チューブ、50   | C01   |

| AD7685BRMRL7                   | ±3LSB (max) | -40~+85℃ | MSOP (RM-10)  | リール、1,000 | C01   |

| EVAL-AD7685CB <sup>1</sup>     |             |          | 評価用ボード        |           |       |

| EVAL-CONTROL BRD2 <sup>2</sup> |             |          | コントロール・ボード    |           |       |

| EVAL-CONTROL BRD3 <sup>2</sup> |             |          | コントロール・ボード    |           |       |

<sup>」</sup>このボードは単独の評価用ボードとしても、評価/デモンストレーション用にEVAL-CONTROL BRDxと組み合わせて使用することもできます。  $^2$  コントロール・ボードを使用すると、製品名の末尾にCBが付くアナログ・デバイセズの評価用ボードのすべてに対しPCで制御と通信ができます。

REV. 0 — 27 —

D02968-0-4/04(0)-J