2093-00

# 4 チャンネル、I<sup>2</sup>C、超低消費電力、 DEVICES 12 ビットADC、20 ピン LFCSP/TSSOP 採用

AD7091R-5 データシート

#### 特長

I<sup>2</sup>C 互換シリアル・インターフェースは標準モードと高速モード **をサポート**

超低消費電力: 3 V 時、高速モードで 90 µW (typ)

V<sub>DD</sub> = 2.7 V ~ 5.25 V で仕様を規定 s

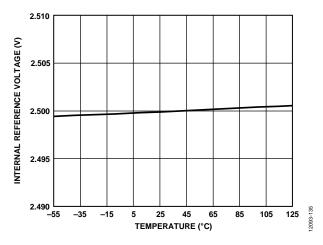

ドリフト 5 ppm/°C(typ)の高精度 2.5 V リファレンスを内蔵 4 つのシングルエンド・アナログ入力チャンネル

アラート機能

ビジー機能

自動サイクル・モード

広い入力帯域幅

入力周波数 1 kHz 時の S/N 比 (SNR) は 68 dB (typ)

柔軟な消費電力/スループット・レート管理

パイプライン遅延なし

パワーダウン・モード

V<sub>DD</sub> = 5.25 V 時 550 nA(typ)

V<sub>DD</sub> = 3 V 時 435 nA(typ)

20 ピン LFCSP / TSSOP パッケージ

動作温度範囲: -40 °C ~ +125 °C

## アプリケーション

バッテリ駆動のシステム

パーソナル・デジタル・アシスタント(PDA)

医用計測機器

モバイル通信

計装システムおよび制御システム

データ・アクイジション・システム

光センサー

診断/モニタリング機能

#### 概要

AD7091R-5は、超低消費電力の12ビット、マルチチャンネル、 逐次比較型 A/D コンバータ (ADC) です。AD7091R-5 は 2.7 V ~5.25 Vの単電源で動作し、高速モードの場合、3 V時の消費 電流はわずか 24 μA (typ) です。

AD7091R-5 は、I<sup>2</sup>C インターフェースと互換性のある 2 線式シ リアル・インターフェースを備えています。変換プロセス は、CONVST/GPO<sub>1</sub>ピン経由でのサンプル・モード、ソフトウェ ア制御を通じて選択する自動サイクル・モード、または I<sup>2</sup>C の 書き込み動作によって変換が行われるコマンド・モードで制御 できます。

デバイスは、最大 1.5 MHz の入力周波数を処理できる広帯域ト ラック&ホールド・アンプを内蔵しています。AD7091R-5 は、 内蔵変換クロック、高精度 2.5 V 内部リファレンス電圧、プロ グラマブルな範囲外ユーザー・アラート機能も備えています。

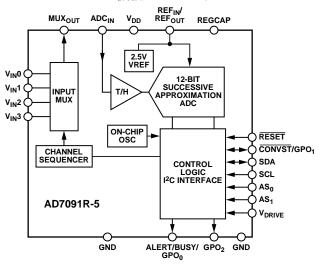

#### 機能ブロック図

図 1.

AD7091R-5 には、チャンネル・シーケンサ付きの 4 つのシン グルエンド・アナログ入力があり、順次変換するチャンネルを 事前にプログラムで選択できます。

AD7091R-5 は、高度な設計技法を採用しているので、性能を 損なうことなく超低消費電力を実現できます。また、柔軟なパ ワー・マネージメントのオプションも備えています。内蔵され ている設定レジスタにより、さまざまな動作状態を設定できま す。これらの設定には、パワー・マネージメント、アラート機 能、ビジー表示、チャンネル・シーケンシング、汎用出力ピン が含まれます。MUXouT ピンと ADCIN ピンを使用することで、 ADC によるアクイジションの前に、マルチプレクサ出力のシ グナル・コンディショニングを実行できます。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標 は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2016 Analog Devices, Inc. All rights reserved.

Rev. 0

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03(5402)8200

大阪営業所/〒532-0003

# AD7091R-5

# 目次 <sub>特長</sub>

| 符長                         | 1  |

|----------------------------|----|

| アプリケーション                   | 1  |

| 機能ブロック図                    | 1  |

| 概要                         | 1  |

| 仕様                         | 3  |

| I <sup>2</sup> C タイミング仕様   | 5  |

| 絶対最大定格                     | 6  |

| 熱抵抗                        | 6  |

| ESD に関する注意                 | 6  |

| ピン配置およびピン機能の説明             | 7  |

| 代表的な性能特性                   | 9  |

| 用語                         | 14 |

| 動作原理                       | 15 |

| 回路説明                       | 15 |

| コンバータの動作                   | 15 |

| ADC の伝達関数                  | 15 |

| リファレンス                     | 15 |

| 電源                         | 16 |

| デバイスのリセット                  | 16 |

| アナログ入力                     | 16 |

| ドライバ・アンプの選択                | 17 |

| 代表的な接続図                    | 17 |

| I <sup>2</sup> C レジスタ      | 19 |

| レジスタのアドレス指定                | 19 |

| スレーブ・アドレス                  | 19 |

| I <sup>2</sup> C レジスタ・アクセス | 19 |

| 変換結果レジスタ20                       |

|----------------------------------|

| チャンネル・レジスタ21                     |

| 設定レジスタ22                         |

| アラート表示レジスタ24                     |

| チャンネル x ロー・リミット・レジスタ26           |

| チャンネル x リミット・レジスタ2ε              |

| チャンネル x ヒステリシス・レジスタ2ε            |

| I <sup>2</sup> C インターフェース        |

| シリアル・バスのアドレス・バイト27               |

| 一般的な PC のタイミング27                 |

| AD7091R-5 への書込み                  |

| 16 ビット・レジスタに対する 2 バイト・データの書込み 28 |

| 複数のレジスタへの書込み28                   |

| AD7091R-5 からのデータの読出し29           |

| 16 ビット・レジスタからの 2 バイト・データの読出し 29  |

| 動作モード30                          |

| サンプル・モード30                       |

| コマンド・モード30                       |

| 自動サイクル・モード32                     |

| パワーダウン・モード32                     |

| アラート33                           |

| ビジー33                            |

| チャンネル・シーケンサ33                    |

| 外形寸法                             |

| オーダー・ガイド34                       |

## 改訂履歴

7/15—Revision 0:初版

# 仕様

特に指定のない限り、 $V_{DD}$  = 2.7 V  $\sim$  5.25 V、 $V_{DRIVE}$  = 1.8 V  $\sim$  5.25 V、 $f_{SCL}$  = 400 kHz、高速 SCL モード、 $V_{REF}$  = 2.5 V 内部/外部、 $T_A$  = -40 °C  $\sim$  +125 °C。

表 1.

| Parameter                                       | Test Conditions/Comments                          | Min                    | Тур        | Max                    | Unit   |

|-------------------------------------------------|---------------------------------------------------|------------------------|------------|------------------------|--------|

| DYNAMIC PERFORMANCE                             | $f_{IN} = 1$ kHz sine wave                        |                        |            |                        |        |

| Signal-to-Noise Ratio (SNR)                     |                                                   |                        | 68         |                        | dB     |

| Signal-to-Noise-and-Distortion Ratio (SINAD)    |                                                   |                        | 67         |                        | dB     |

| Total Harmonic Distortion (THD)                 |                                                   |                        | -80        |                        | dB     |

| Spurious-Free Dynamic Range (SFDR)              |                                                   |                        | -81        |                        | dB     |

| Channel to Channel Isolation                    |                                                   |                        | -105       |                        | dB     |

| Aperture Delay                                  |                                                   |                        | 5          |                        | ns     |

| Aperture Jitter                                 |                                                   |                        | 40         |                        | ps     |

| Full Power Bandwidth                            | At -3 dB                                          |                        | 1.5        |                        | MHz    |

|                                                 | At -0.1 dB                                        |                        | 1.2        |                        | MHz    |

| DC ACCURACY                                     |                                                   |                        |            |                        |        |

| Resolution                                      |                                                   | 12                     |            |                        | Bits   |

| Integral Nonlinearity (INL)                     |                                                   | -1.25                  | $\pm 0.8$  | +1.25                  | LSB    |

| Differential Nonlinearity (DNL)                 | Guaranteed no missing codes to 12 bits            | -0.9                   | ±0.3       | +0.9                   | LSB    |

| Offset Error                                    | $T_A = 25^{\circ}C$                               | -1.5                   | ±0.3       | +1.5                   | mV     |

| Offset Error Matching                           | $T_A = 25^{\circ}C$                               | -1.5                   | ±0.3       | +1.5                   | mV     |

| Offset Error Drift                              |                                                   |                        | 2          |                        | ppm/°C |

| Gain Error                                      | $T_A = 25^{\circ}C$                               | -0.1                   | 0.0        | +0.1                   | % FS   |

| Gain Error Matching                             | $T_A = 25$ °C                                     | -0.1                   | 0.0        | +0.1                   | % FS   |

| Gain Error Drift                                | -                                                 |                        | 1          |                        | ppm/°C |

| ANALOG INPUT                                    |                                                   |                        |            |                        | II.    |

| Input Voltage Range <sup>1</sup>                | At ADC <sub>IN</sub>                              | 0                      |            | $V_{ m REF}$           | V      |

| DC Leakage Current                              | TICTID ON                                         | -1                     |            | +1                     | μA     |

| Input Capacitance <sup>2</sup>                  | During acquisition phase                          |                        | 10         |                        | pF     |

| input cupucitance                               | Outside acquisition phase                         |                        | 1.5        |                        | pF     |

| Multiplexer On Resistance                       | $V_{DD} = 5.0 \text{ V}$                          |                        | 50         |                        | Ω      |

| Wattiplexer on Resistance                       | $V_{DD} = 3.5 \text{ V}$ $V_{DD} = 2.5 \text{ V}$ |                        | 100        |                        | Ω      |

| VOLTAGE REFERENCE INPUT/OUTPUT                  | ▼ DD = 2.3 ▼                                      |                        | 100        |                        | 32     |

| REF <sub>OUT</sub> <sup>3</sup>                 | Internal reference output, T <sub>A</sub> = 25°C  | 2.49                   | 2.5        | 2.51                   | V      |

| $REF_{IN}^{3}$                                  | External reference input                          | 1.0                    | 2.3        | $V_{DD}$               | v      |

| Drift                                           | External reference input                          | 1.0                    | 5          | ▼ DD                   | ppm/°C |

| Power-On Time                                   | $C_{REF} = 2.2 \mu F$                             |                        | 50         |                        | ms     |

| LOGIC INPUTS                                    | CREF - 2.2 μ1                                     |                        | 30         |                        | 1115   |

| Input Voltage                                   |                                                   |                        |            |                        |        |

| High ( $V_{IH}$ )                               |                                                   | $0.7 \times V_{DRIVE}$ |            |                        | V      |

| $Low(V_{IL})$                                   |                                                   | 0.7 × V DRIVE          |            | $0.3 \times V_{DRIVE}$ | V      |

|                                                 | V = 0 V or V                                      | -1                     | 0.01       | +1                     |        |

| Input Current (I <sub>IN</sub> )  LOGIC OUTPUTS | $V_{IN} = 0 \text{ V or } V_{DRIVE}$              | -1                     | 0.01       | Τ1                     | μA     |

|                                                 |                                                   |                        |            |                        |        |

| Output Voltage                                  | J 200 A                                           | 17 0.2                 |            |                        |        |

| High (V <sub>OH</sub> )                         | $I_{\text{SOURCE}} = 200 \mu\text{A}$             | $V_{DRIVE} - 0.2$      |            | 0.4                    | V      |

| Low (V <sub>OL</sub> )                          | $I_{SINK} = 200 \mu A$                            |                        |            | 0.4                    | V      |

| Floating State Leakage Current                  |                                                   | -1                     | 1          | +1                     | μΑ     |

| Output Coding                                   |                                                   | Straig                 | ht (natura | I) binary              |        |

| Parameter                            | Test Conditions/Comments                                                                                                                                    | Min | Тур       | Max      | Unit |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|----------|------|

| CONVERSION RATE                      |                                                                                                                                                             |     |           |          |      |

| Conversion Time                      |                                                                                                                                                             |     | 550       |          | ns   |

| Update Rate                          |                                                                                                                                                             |     |           |          |      |

| Autocycle Setting 00                 |                                                                                                                                                             | 90  | 100       | 110      | μs   |

| Autocycle Setting 01                 |                                                                                                                                                             | 180 | 200       | 220      | μs   |

| Autocycle Setting 10                 |                                                                                                                                                             | 360 | 400       | 440      | μs   |

| Autocycle Setting 11                 |                                                                                                                                                             | 720 | 800       | 880      | μs   |

| Throughput Rate                      | $f_{SCL} = 400 \text{ kHz}$ , command mode                                                                                                                  |     |           | 22.22    | kSPS |

| POWER REQUIREMENTS                   |                                                                                                                                                             |     |           |          |      |

| $V_{ m DD}$                          |                                                                                                                                                             | 2.7 |           | 5.25     | V    |

| V <sub>DRIVE</sub> Range             |                                                                                                                                                             | 1.8 |           | 5.25     | V    |

| I <sub>DD</sub>                      | $V_{IN} = 0 V$                                                                                                                                              |     |           |          |      |

| Normal Mode—Static                   | $V_{DD} = 5.25 \text{ V}$                                                                                                                                   |     | 22        | 50       | μA   |

|                                      | $V_{DD} = 3 \text{ V}$                                                                                                                                      |     | 21.6      | 46       | μΑ   |

| Normal Mode—Operational              | $V_{DD} = 5.25 \text{ V}, f_{SCL} = 400 \text{ kHz}$                                                                                                        |     | 26        | 55       | μΑ   |

| Tromai Mode operational              | $V_{DD} = 3 \text{ V}, f_{SCL} = 400 \text{ kHz}$                                                                                                           |     | 24        | 52       | μΑ   |

|                                      | $V_{DD} = 5.25 \text{ V}, f_{SCL} = 100 \text{ kHz}$                                                                                                        |     | 25        | 54       | μΑ   |

|                                      | $V_{DD} = 3 \text{ V}, f_{SCL} = 100 \text{ kHz}$                                                                                                           |     | 23        | 51       | μΑ   |

|                                      | $V_{DD} = 3 \text{ V}$ , autocycle mode                                                                                                                     |     | 70        | 105      | μΑ   |

| Power-Down Mode                      | $V_{DD} = 5.25 \text{ V}$                                                                                                                                   |     | 0.550     | 17       | μΑ   |

| Tower Bown Mode                      | $V_{DD} = 5.25 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                                |     | 0.550     | 8        | μΑ   |

|                                      | $V_{DD} = 3 \text{ V}$                                                                                                                                      |     | 0.435     | 15       | μΑ   |

| $I_{DRIVE}$                          | $V_{IN} = 0 \text{ V}$                                                                                                                                      |     | 0.133     | 15       | μ.1  |

| Normal Mode—Static                   | $V_{DRIVE} = 5.25 \text{ V}$                                                                                                                                |     | 2         | 4        | μA   |

| Tromai Prode State                   | $V_{DRIVE} = 3.23 \text{ V}$ $V_{DRIVE} = 3 \text{ V}$                                                                                                      |     | 1         | 3.5      | μΑ   |

| Normal Mode—Operational              | $V_{DRIVE} = 5.25 \text{ V}, f_{SCL} = 400 \text{ kHz}$                                                                                                     |     | 6         | 15       | μΑ   |

| Normal Wode Operational              | $V_{DRIVE} = 3.23 \text{ V}, f_{SCL} = 400 \text{ kHz}$<br>$V_{DRIVE} = 3 \text{ V}, f_{SCL} = 400 \text{ kHz}$                                             |     | 5         | 14       | μΑ   |

|                                      | $V_{DRIVE} = 5 \text{ V}, f_{SCL} = 400 \text{ kHz}$<br>$V_{DRIVE} = 5.25 \text{ V}, f_{SCL} = 100 \text{ kHz}$                                             |     | 5         | 14       | μΑ   |

|                                      | $V_{DRIVE} = 3.23 \text{ V}, f_{SCL} = 100 \text{ kHz}$<br>$V_{DRIVE} = 3 \text{ V}, f_{SCL} = 100 \text{ kHz}$                                             |     | 4         | 13       | μΑ   |

| Total Power Dissipation <sup>4</sup> | $V_{\text{DRIVE}} = 3$ $V_{\text{NSCL}} = 100$ kHz $V_{\text{IN}} = 0$ V                                                                                    |     | 7         | 13       | μΑ   |

| Normal Mode—Static                   | $V_{DD} = V_{DRIVE} = 5.25 \text{ V}$                                                                                                                       |     | 130       | 290      | μW   |

| Normal Wode—Static                   | $V_{DD} = V_{DRIVE} = 3.23 \text{ V}$ $V_{DD} = V_{DRIVE} = 3 \text{ V}$                                                                                    |     | 70        | 150      | μW   |

| Normal Mode—Operational              | $V_{DD} = V_{DRIVE} = 5.25 \text{ V}, f_{SCL} = 400 \text{ kHz}$                                                                                            |     | 170       | 370      | μW   |

| Normai wiode—Operational             | $V_{DD} = V_{DRIVE} = 3.23 \text{ V, } I_{SCL} = 400 \text{ kHz}$<br>$V_{DD} = V_{DRIVE} = 3 \text{ V, } I_{SCL} = 400 \text{ kHz}$                         |     | 90        | 200      | μW   |

|                                      | $V_{DD} = V_{DRIVE} = 3 \text{ V}, 1_{SCL} = 400 \text{ kHz}$<br>$V_{DD} = V_{DRIVE} = 5.25 \text{ V}, f_{SCL} = 100 \text{ kHz}$                           |     | 160       | 360      | 1 -  |

|                                      | $V_{DD} = V_{DRIVE} = 3.23 \text{ V, } I_{SCL} = 100 \text{ kHz}$<br>$V_{DD} = V_{DRIVE} = 3 \text{ V, } I_{SCL} = 100 \text{ kHz}$                         |     | 85        | 195      | μW   |

|                                      |                                                                                                                                                             |     | 85<br>210 |          | μW   |

| Dorriga Dorriga M J                  | $V_{DD} = V_{DRIVE} = 3 \text{ V, autocycle mode}$                                                                                                          |     |           | 315      | μW   |

| Power-Down Mode                      | $V_{DD} = 5.25 \text{ V}$ |     | 3         | 95<br>22 | μW   |

|                                      | $V_{DD} = 5.25 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                                |     | 3         | 33       | μW   |

|                                      | $V_{DD} = V_{DRIVE} = 3 \text{ V}$                                                                                                                          |     | 1.4       | 50       | μW   |

<sup>「</sup>マルチプレクサの入力電圧は、 $V_{DD}$  を超えてはいけません。 <sup>2</sup> 初期リリース時にサンプル・テストにより適合性を保証。 <sup>3</sup> パラメータの説明で、多機能ピンの特定の機能について示している箇所では、仕様に関係するピン名のみを示しています。多機能ピンのすべてのピン名について は、Pin Configurations and Function Descriptions のセクションを参照してください。

$<sup>^4</sup>$ 総消費電力には、 $V_{DD}$ 、 $V_{DRIVE}$ 、 $REF_{IN}$  の消費電力が含まれます (注  $^3$ を参照)。

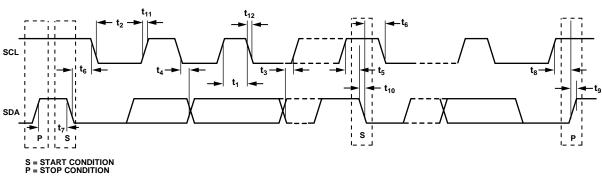

### I<sup>2</sup>C タイミング仕様

これらの値はすべて、入力フィルタがイネーブルの状態で測定したものです。 $C_B$  は、バス・ラインに容量性負荷が存在することを表し、立上がり時間と立下がり時間は  $0.3 \times V_{DRIVE} \sim 0.7 \times V_{DRIVE}$  で測定した値です(Figure 2 を参照)。特に指定のない限り、 $V_{DD}$  = 2.7  $V \sim 5.25 \, V$ 、 $V_{DRIVE}$  =  $1.8 \, V \sim 5.25 \, V$ 、 $V_{REF}$  =  $2.5 \, V$  内部/外部、 $T_{A}$  =  $T_{MIN} \sim T_{MAX}$ 。

表 2.

| Limit at T <sub>MIN</sub> , T <sub>MAX</sub> |                       |     |         |                                                                                    |  |  |  |

|----------------------------------------------|-----------------------|-----|---------|------------------------------------------------------------------------------------|--|--|--|

| Parameter                                    | Parameter Min Typ Max |     | ax Unit | Description                                                                        |  |  |  |

| $f_{SCL}$                                    |                       | 10  | 00 kHz  | Serial clock frequency, standard mode                                              |  |  |  |

|                                              |                       | 40  | 00 kHz  | Fast mode                                                                          |  |  |  |

| $t_1$                                        | 4                     |     | μs      | SCL high time, standard mode                                                       |  |  |  |

|                                              | 0.6                   |     | μs      | Fast mode                                                                          |  |  |  |

| $t_2$                                        | 4.7                   |     | μs      | SCL low time, standard mode                                                        |  |  |  |

|                                              | 1.3                   |     | μs      | Fast mode                                                                          |  |  |  |

| $t_3$                                        | 250                   |     | ns      | Data setup time, standard mode                                                     |  |  |  |

|                                              | 100                   |     | ns      | Fast mode                                                                          |  |  |  |

| $t_4^{\ 1}$                                  | 0                     | 3.4 | 45 μs   | Data hold time, standard mode                                                      |  |  |  |

|                                              | 0                     | 0.9 | 9 μs    | Fast mode                                                                          |  |  |  |

| $t_5$                                        | 4.7                   |     | μs      | Setup time for a repeated start condition, standard mode                           |  |  |  |

|                                              | 0.6                   |     | μs      | Fast mode                                                                          |  |  |  |

| $t_6$                                        | 4                     |     | μs      | Hold time for a repeated start condition, standard mode                            |  |  |  |

|                                              | 0.6                   |     | μs      | Fast mode                                                                          |  |  |  |

| $\mathbf{t}_7$                               | 4.7                   |     | μs      | Bus-free time between a stop and a start condition, standard mode                  |  |  |  |

|                                              | 1.3                   |     | μs      | Fast mode                                                                          |  |  |  |

| $t_8$                                        | 4                     |     | μs      | Setup time for a stop condition, standard mode                                     |  |  |  |

|                                              | 0.6                   |     | μs      | Fast mode                                                                          |  |  |  |

| t <sub>9</sub>                               |                       | 10  | 000 ns  | Rise time of the SDA signal, standard mode                                         |  |  |  |

|                                              | $20 + 0.1C_{B}$       | 30  | 00 ns   | Fast mode                                                                          |  |  |  |

| $t_{10}$                                     |                       | 30  | 00 ns   | Fall time of the SDA signal, standard mode                                         |  |  |  |

|                                              | $20 + 0.1C_{B}$       | 30  | 00 ns   | Fast mode                                                                          |  |  |  |

| t <sub>11</sub>                              |                       | 10  | 000 ns  | Rise time of the SCL signal, standard mode                                         |  |  |  |

|                                              | $20 + 0.1C_{B}$       | 30  | 00 ns   | Fast mode                                                                          |  |  |  |

| $t_{11A}$                                    |                       | 10  | 000 ns  | Rise time of the SCL signal after a repeated; not shown in Figure 2, standard mode |  |  |  |

|                                              | $20 + 0.1C_{B}$       | 30  | 00 ns   | Start condition and after an acknowledge bit, fast mode                            |  |  |  |

| $t_{12}$                                     |                       | 30  | 00 ns   | Fall time of the SCL signal, standard mode                                         |  |  |  |

|                                              | $20 + 0.1C_B$         | 30  |         | Fast mode                                                                          |  |  |  |

| $t_{SP}$                                     | 0                     | 50  | ns      | Pulse width of the suppressed spike; not shown in Figure 2, fast mode              |  |  |  |

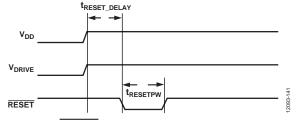

| $t_{RESETPW}$                                | 10                    |     | ns      | RESET pulse width (see Figure 35)                                                  |  |  |  |

| $t_{RESET\_DELAY}$                           | 50                    |     | ns      | RESET pulse delay upon power-up (see Figure 35)                                    |  |  |  |

$<sup>^{\</sup>rm I}$  SCL 立下がりエッジの不定領域をブリッジするには、デバイスは SDA のデータ・ホールド時間を提供する必要があります。

図 2.2 線式シリアル・インターフェースのタイミング図

# 絶対最大定格

特に指定のない限り、 $T_A = 25$ °C。

#### 表 3

| <b>1</b> 人 3.                                         |                                               |

|-------------------------------------------------------|-----------------------------------------------|

| Parameter                                             | Rating                                        |

| V <sub>DD</sub> to GND                                | -0.3 V to +7 V                                |

| $V_{ m DRIVE}$ to GND                                 | -0.3 V to +7 V                                |

| Analog Input Voltage to GND                           | $-0.3 \text{ V to V}_{REF} + 0.3 \text{ V}$   |

| Digital Input <sup>1</sup> Voltage to GND             | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$ |

| Digital Output <sup>2</sup> Voltage to GND            | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$ |

| Input Current to Any Pin Except Supplies <sup>3</sup> | ±10 mA                                        |

| Operating Temperature Range                           | −40°C to +125°C                               |

| Storage Temperature Range                             | −65°C to +150°C                               |

| Junction Temperature                                  | 150°C                                         |

| ESD                                                   |                                               |

| Human Body Model (HBM)                                | 1.5 kV                                        |

| Field Induced Charged Device Model (FICDM)            | 500 V                                         |

$<sup>^1</sup>$  デジタル入力ピンには、 $AS_0$ 、 $\overline{RESET}$ 、 $AS_1$ 、SCL、SDA、 $\overline{CONVST}/GPO_1$  が 含まれます。

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。製品を長時間絶対最大定格状態に置くと、製品の信頼性 に影響を与えることがあります。

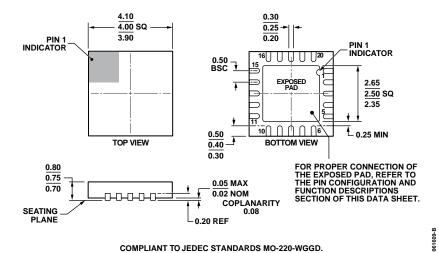

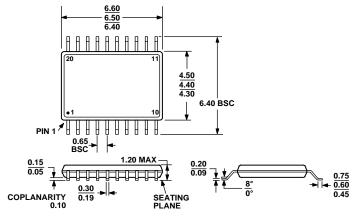

#### 熱抵抗

θ<sub>JA</sub>は最悪の条件、すなわち、回路基板に表面実装パッケージ をハンダ付けした状態で規定しています。

表 4. 熱抵抗

| Package Type     | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|------------------|-----------------|-----------------|------|

| 20-Lead LFCSP_WQ | 52              | 6.5             | °C/W |

| 20-Lead TSSOP    | 84.3            | 18.4            | °C/W |

## ESD に関する注意

ESD (静電放電)の影響を受けやすいデバイスです。 電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

$<sup>^2</sup>$  デジタル出力ピンには、ALERT/BUSY/GPO<sub>0</sub>、GPO<sub>2</sub>、SDA が含まれます。

<sup>3</sup>最大 100 mA までの過渡電流では、SCR ラッチ・アップは生じません。

# ピン配置およびピン機能の説明

18 V<sub>DRIVE</sub> 20 RESET 19 AS<sub>0</sub> 00015 SDA V<sub>DD</sub> 1 REGCAP 2 14 AS<sub>1</sub> AD7091R-5 REF<sub>IN</sub>/REF<sub>OUT</sub> 3 13 GND TOP VIEW (Not to Scale) GND 4 12 ADC<sub>IN</sub> 11 V<sub>IN</sub>1 MUX<sub>OUT</sub> 5 GPO<sub>2</sub> 9 V<sub>IN</sub>3 10 ALERT/BUSY/GPO<sub>0</sub> 8 V N V

図 3. 20 ピン TSSOP のピン配置

NOTES

1. EXPOSED PAD. THE EXPOSED PAD IS NOT CONNECTED INTERNALLY. IT IS RECOMMENDED THAT THE PAD BE SOLDERED TO GND.

図 4. 20 ピン LFCSP のピン配置

表 5. ピン機能の説明

| ピン番号  |       |                                       |                                                                                                                                                                                |

|-------|-------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | LFCSP | 記号                                    | 説明                                                                                                                                                                             |

| 1     | 19    | $AS_0$                                | $I^2C$ アドレス・ビット $0$ 。このピンと $AS_1$ のロジック状態により、 $AD7091R-5$ の固有の $I^2C$ アドレスが選択されます。デバイスのアドレスは、これらのピンのロジック状態に依存します。                                                              |

| 2     | 20    | RESET                                 | リセット。ロジック入力。このピンをロー・レベルにプルダウンすると、デバイスがリセットされます。                                                                                                                                |

| 3     | 1     | $V_{DD}$                              | 電源入力。 $V_{DD}$ 範囲は $2.7~V\sim5.25~V$ 。この電源ピンは GND ヘデカップリングします。                                                                                                                 |

| 4     | 2     | REGCAP                                | 内蔵レギュレータの電圧出力に対するデカップリング・コンデンサ・ピン。2.2 μF のコンデンサを使用して、この出力ピンを GND ヘデカップリングします。                                                                                                  |

| 5     | 3     | REF <sub>IN</sub> /REF <sub>OUT</sub> | 電圧リファレンス出力は $2.5V$ 。このピンは GND ヘデカップリングします。推奨デカップリング・コンデンサ値は $2.2\mu F$ です。 $2.5V$ 内部リファレンスを使用するか、このピンに加える電圧で内部リファレンス電圧をオーバードライブすることができます。外付けリファレンスの電圧範囲は $1.0V\sim V_{DD}$ です。 |

| 6, 15 | 4, 13 | GND                                   | チップのグラウンド・ピン。これらのピンは、AD7091R-5 の全回路に対するグラウンド基準ポイントです。                                                                                                                          |

| 7     | 5     | MUX <sub>OUT</sub>                    | マルチプレクサ出力。マルチプレクサの出力がこのピンに現れます。外部フィルタリングまたは<br>バッファリングが不要な場合は、このピンを ADC <sub>IN</sub> ピンに直接接続します。あるいは、コンディ<br>ショニング・ネットワークの出力を ADC <sub>IN</sub> ピンに接続します。                     |

| 8     | 6     | $V_{IN}0$                             | チャンネル $0$ のアナログ入力。シングルエンド・アナログ入力。アナログ入力範囲は $0  V \sim V_{REF}$ 。                                                                                                               |

| 9     | 7     | $V_{IN}2$                             | チャンネル $2$ のアナログ入力。シングルエンド・アナログ入力。アナログ入力範囲は $0  V \sim V_{REF}$ 。                                                                                                               |

| 10    | 8     | ALERT/BUSY/GPO <sub>0</sub>           | このピンは多機能ピンで、設定レジスタによって機能が決定されます。                                                                                                                                               |

|       |       |                                       | アラート出力ピン(ALERT)。このピンは ALERT として機能する場合、変換結果がレジスタ設定の制限値外になったことを示すロジック出力です。                                                                                                       |

|       |       |                                       | ビジー出力(BUSY)。BUSY ピンは、変換が実行されていることを示します。                                                                                                                                        |

|       |       |                                       | 汎用デジタル出力 0 (GPO <sub>0</sub> ) 。                                                                                                                                               |

| 11    | 9     | $GPO_2$                               | 汎用デジタル出力 2。                                                                                                                                                                    |

| 12    | 10    | $V_{IN}3$                             | チャンネル $3$ のアナログ入力。シングルエンド・アナログ入力。アナログ入力範囲は $0  V \sim V_{REF}$ 。                                                                                                               |

| 13    | 11    | $V_{IN}1$                             | チャンネル $1$ のアナログ入力。シングルエンド・アナログ入力。アナログ入力範囲は $0  V \sim V_{REF}$ 。                                                                                                               |

| 14    | 12    | ADC <sub>IN</sub>                     | ADC 入力。このピンを使用すれば、ADC に直接アクセスできます。外部フィルタリングまたはバッファリングが不要な場合は、このピンを MUX <sub>OUT</sub> ピンに直接接続します。あるいは、コンディショニング・ネットワークの入力を MUX <sub>OUT</sub> ピンに接続します。                        |

| ピン番号<br>TSSOP LFCSP |    |                         |                                                                                                                                                                                                                                                                                                              |

|---------------------|----|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |    | 記号                      | 説明                                                                                                                                                                                                                                                                                                           |

| 16                  | 14 | AS <sub>1</sub>         | $I^2C$ アドレス・ビット 1。このピンと $AS_0$ のロジック状態により、 $AD7091R-5$ の固有の $I^2C$ アドレスが選択されます。デバイスのアドレスは、これらのピンのロジック状態に依存します。                                                                                                                                                                                               |

| 17                  | 15 | SDA                     | シリアル・データ入力/出力。このオープンドレイン出力には、プルアップ抵抗が必要です。電<br>圧チャンネルの出力コーディングはストレート・バイナリです。                                                                                                                                                                                                                                 |

| 18                  | 16 | SCL                     | デジタル入力シリアル $I^2$ C バス・クロック。この入力には、プルアップ抵抗が必要です。 $I^2$ C モードでのデータ転送レートは、 $100\mathrm{kHz}$ (標準モード)と $400\mathrm{kHz}$ (高速モード)の両方の動作モードと互換性があります。                                                                                                                                                              |

| 19                  | 17 | CONVST/GPO <sub>1</sub> | このピンは多機能ピンで、設定レジスタと変換モードによって機能が決定されます。 変換開始の入力信号( $\overline{\text{CONVST}}$ )。エッジ・トリガ・ロジック入力。 $\overline{\text{CONVST}}$ の立下がりエッジ で ADC がホールド・モードになり、変換が開始されます。EOC での $\overline{\text{CONVST}}$ のロジック・レベルが AD7091R-5 の消費電力モードを制御します。 汎用デジタル出力 1( $\overline{\text{GPO}_1}$ )。コマンド・モードまたは自動サイクル・モードの場合、このピン |

| 20                  | 18 | $V_{ m DRIVE}$          | は汎用デジタル出力として機能できます。 ロジック電源入力。このピンに供給される電圧により、インターフェースの動作電圧が決定されます。 $V_{DRIVE}$ と GND の間にデカップリング・コンデンサを接続します。推奨値は $10\mu\text{F}$ と $0.1\mu\text{F}$ です。このピンの電圧範囲は $1.8\text{V}\sim5.25\text{V}$ であり、 $V_{DD}$ の電圧範囲と異なってもかまいませんが、 $V_{DD}$ 値を上回る場合は相違が $0.3\text{V}$ を超えてはいけません。                             |

| N/A1                | 21 | EPAD                    | 露出パッド。露出パッドは内部で接続されていません。パッドを GND にハンダ付けすることが<br>推奨されます。                                                                                                                                                                                                                                                     |

<sup>「</sup>N/Aは該当なしを意味します。

# 代表的な性能特性

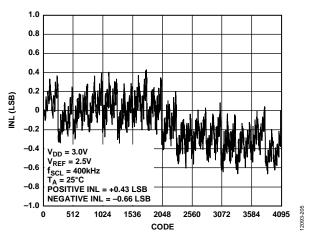

図 5. 積分非直線性とコードの関係

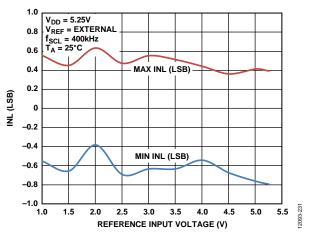

図 6. 最小/最大 INL と外部リファレンス入力電圧の関係

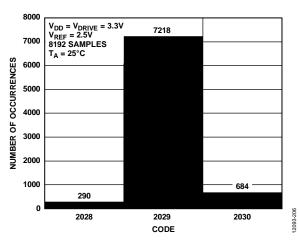

図 7. コード中心での DC 入力のヒストグラム

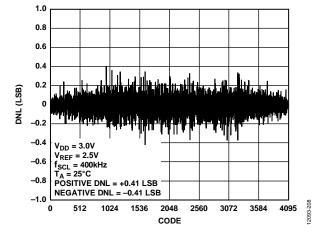

図 8. 微分非直線性とコードの関係

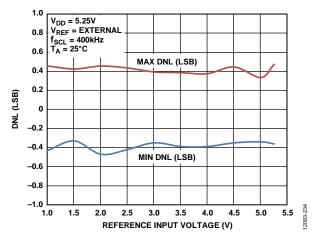

図 9. 最小/最大 DNL と外部リファレンス入力電圧の関係

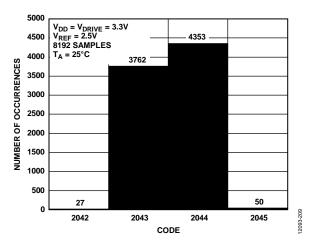

図 10. コード遷移での DC 入力のヒストグラム

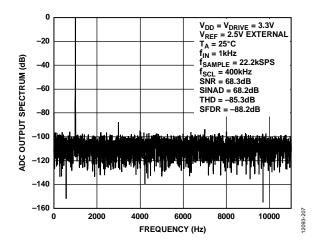

図 11. 10 kHz FFT、V<sub>DD</sub> = 3.0 V、V<sub>REF</sub> = 2.5 V 外部

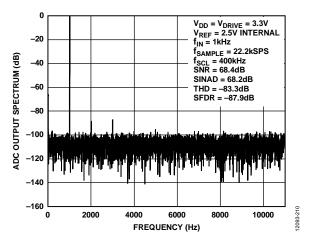

図 12. 10 kHz FFT、 $V_{DD}$  = 3.0 V、 $V_{REF}$  = 2.5 V 内部

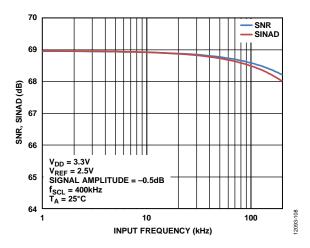

図 13. SNR、SINAD と入力周波数の関係

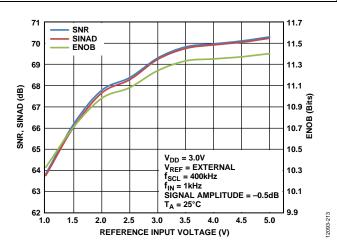

図 14. SNR、SINAD、ENOB とリファレンス入力電圧の関係

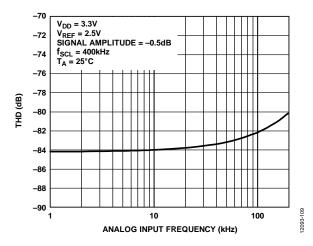

図 15. THD とアナログ入力周波数の関係

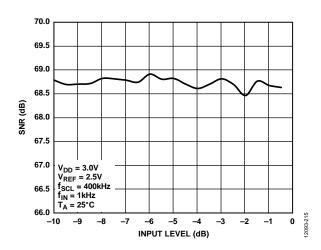

図 16. SNR と入力レベルの関係

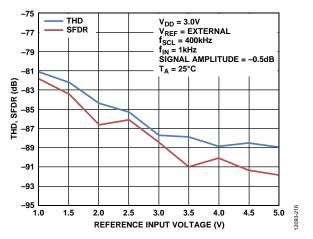

図 17. THD、SFDR とリファレンス入力電圧の関係

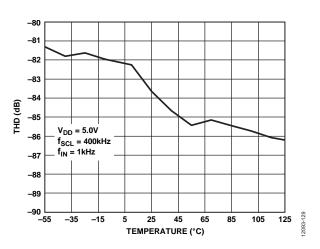

図 18. THD と温度の関係

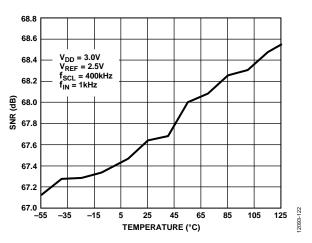

図 19. SNR と温度の関係

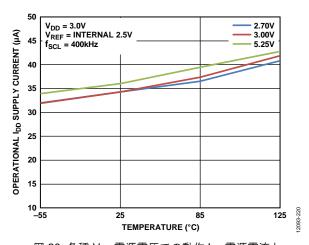

図 20. 各種 V<sub>DD</sub> 電源電圧での動作 I<sub>DD</sub> 電源電流と 温度の関係

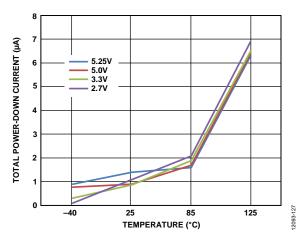

図 21. 各種 VDD 電源電圧での合計パワーダウン電流と温度の 関係

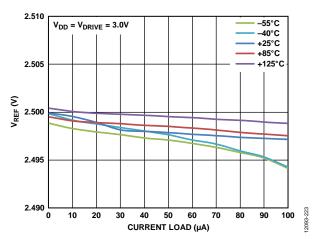

図 22. 各種温度でのリファレンス電圧出力(V<sub>REF</sub>)と 電流負荷の関係

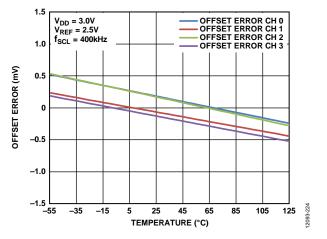

図 23. オフセット誤差と温度の関係

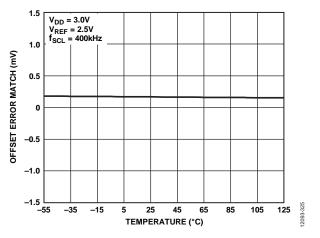

図 24. オフセット誤差整合と温度の関係

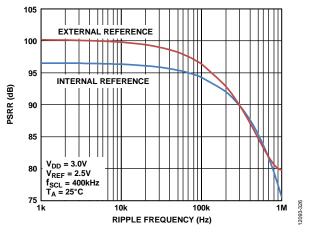

図 25. PSRR とリップル周波数の関係

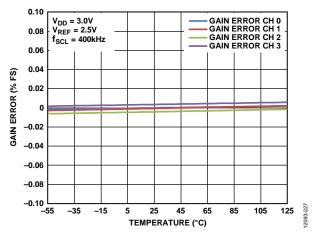

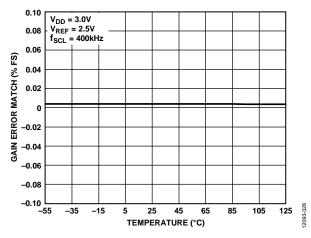

図 26. ゲイン誤差と温度の関係

図 27. ゲイン誤差整合と温度の関係

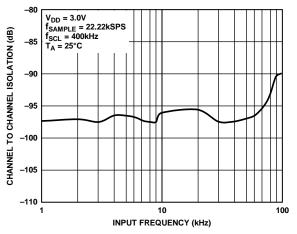

図 28. チャンネル間絶縁と入力周波数の関係

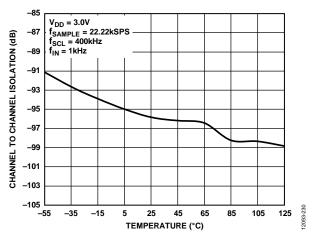

図 29. チャンネル間絶縁と温度の関係

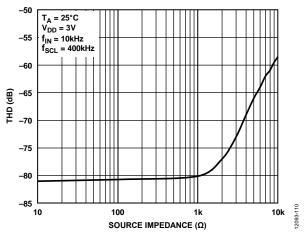

図 30. THD と信号源インピーダンスの関係

図 31. 内部リファレンス電圧と温度の関係

# 用語

#### 積分非直線性 (INL)

ADC 伝達関数の両端を結ぶ直線からの最大許容誤差です。 AD7091R-5 の場合、伝達関数の両端は、ゼロ・スケール(最初のコード遷移より % LSB 下のポイント)とフルスケール(最後のコード遷移より % LSB 上のポイント)に相当します。

#### 微分非直線性 (DNL)

ADC の 2 つの隣接コード間における 1 LSB 変化の測定値と理論値の差です。

#### オフセット誤差

オフセット誤差は、最初のコード遷移(00...000から00...001) と理想的な遷移(GND+0.5 LSB など)との偏差です。

#### オフセット誤差整合

オフセット誤差整合は、任意の2つの入力チャンネル間のオフセット誤差の差です。

#### ゲイン誤差

AD7091R-5 の場合、ゲイン誤差は、オフセット誤差を調整した後の最後のコード遷移( $111 \cdots 110$  から  $111 \cdots 111$ )と理想的な遷移( $V_{REF} - 1.5$  LSB など)の間の偏差です。

#### ゲイン誤差整合

ゲイン誤差整合は、任意の2つの入力チャンネル間のゲイン誤差の差です。

#### 過渡応答時間

変換終了後、トラック&ホールド・アンプはトラック・モードに戻ります。トラック&ホールド・アクイジション時間は、変換終了後にトラック&ホールド・アンプの出力が最終値の  $\pm 0.5$  LSB 以内に収まるまでに要する時間です。詳細については、 $\Gamma$ C Interface のセクションを参照してください。

#### 信号/ノイズ+歪み (SINAD)

SINAD は、ADC 出力で信号/ノイズ+歪みの測定値です。信号は基本波の rms 振幅で表します。ノイズは 1/2 サンプリング周波数 (fs/2) までの非基本波の総和で表します (DC を除く)。

この比はデジタル化処理の量子化レベル数に依存し、レベル数が大きいほど、量子化ノイズは小さくなります。サイン波入力を持つ理想的なNビット・コンバータの理論的なSINADは次式で求めます。

信号/ (ノイズ+歪み) = (6.02N + 1.76) (dB)

したがって、12 ビット・コンバータの場合、SINAD は 74 dB になります。

#### チャンネル間絶縁

チャンネル間絶縁とは、選択したチャンネルとその他のすべてのチャンネル間のクロストーク・レベルの測定値です。この値を測定するには、非選択入力チャンネルのすべてにフルスケールの10 kHz のサイン波信号を入力し、その信号の減衰量を DC信号が入力されている選択されたチャンネルで調べます。Figure 28 に、AD7091R-5 のすべてのチャンネル間での最悪の条件を示します。

#### 全高調波歪み (THD)

THD は高調波の rms 値の総和と基本波の比です。AD7091R-5 の場合、この値は次のように定義されます。

$$THD(dB) = 20\log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_4}$$

ここで、

V<sub>1</sub> は基本波の rms 振幅。

$V_2$ 、 $V_3$ 、 $V_4$ 、 $V_5$ 、 $V_6$  は、2 次 ~ 6 次の高調波の rms 振幅。

#### ピーク高調波またはスプリアス・ノイズ

ピーク高調波またはスプリアス・ノイズは、基本波 rms 値に対する ADC 出力スペクトル内の(DC を除いて fs/2 まで)次に大きい成分の rms 値の比として定義されます。一般に、この仕様の値はスペクトル内の最大の高調波により決定されますが、高調波がノイズ・フロアに埋めこまれている ADC の場合はノイズ・ピークになります。

# 動作原理

#### 回路説明

AD7091R-5 は、超低消費電力の 12 ビット単電源 ADC です。 デバイスは  $2.7 \, \text{V} \sim 5.25 \, \text{V}$  の電源で動作します。AD7091R-5 は、標準  $1^{2}\text{C}$  動作モードと高速  $1^{2}\text{C}$  動作モードの両方で機能することができます。

AD7091R-5 は、4:1 マルチプレクサと内蔵トラック&ホールド・アンプを備えていて、20 ピン LFCSP パッケージまたは 20 ピン TSSOP パッケージに収められています。これらのパッケージは、代替ソリューションに比べて大幅に優れた省スペース性を発揮します。このデバイスからのデータにアクセスするには、シリアル・クロック入力を使用します。逐次比較型 ADC を制御するための内部発生クロックが実装されています。AD7091R-5のリファレンス電圧は、外部から提供されるか、高精度内蔵リファレンス・ソースにより内部で発生されます。AD7091R-5のアナログ入力範囲は  $0\,V \sim V_{REF}$  です。

AD7091R-5 はパワーダウン・オプションを備えているため、変換の間で消費電力を節約できます。パワーダウン機能には、標準のシリアル・インターフェースを通じてアクセスします (Modes of Operation のセクションを参照)。

#### コンパータの動作

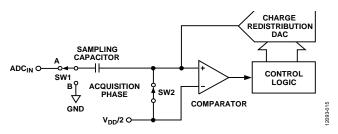

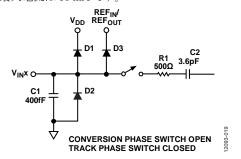

AD7091R-5 は、電荷再配分式 D/A コンバータ(DAC)を採用した逐次比較型 ADC です。Figure 32 と Figure 33 に、ADC の簡略化した回路図を示します。Figure 32 に、アクイジション・フェーズにある ADC を示します。スイッチ 2(SW2)が閉じていて、スイッチ 1(SW1)が位置 A にある場合、コンパレータは平衡状態に保持されて、サンプリング・コンデンサは ADC<sub>IN</sub>上の信号を取得します。

図 32. ADC アクイジション・フェーズ

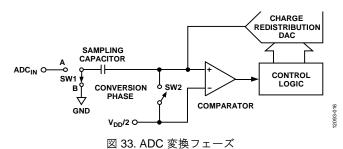

ADC が変換を開始すると、SW2 が開いて、SW1 が位置 B に移動し、コンパレータが非平衡状態になります(Figure 33 を参照)。 コントロール・ロジックと電荷再配分式 DAC を使用して、サンプリング・コンデンサに対して一定量の電荷を加算および減算し、コンパレータを平衡状態に戻すようにします。 SAR の判定が行われると、コンパレータの入力が平衡状態に戻ります。 これらの SAR の判定から、コントロール・ロジックは ADC 出力コードを生成します。

#### ADC の伝達関数

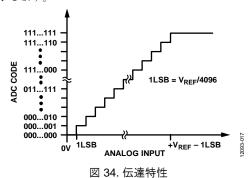

AD7091R-5の出力コーディングはストレート・バイナリです。 設計上のコード遷移は LSB の連続する整数値の中間(% LSB、1% LSB など)で発生します。AD7091R-5の LSB サイズは  $V_{REF}/4096$  になります。AD7091R-5の理論上の伝達特性を Figure 34に示します。

リファレンス

AD7091R-5 は、2.5 V の内部リファレンスまたは外付けリファレンスで動作できます。設定レジスタの P\_DOWN LSB ビットのロジック状態により、内部リファレンスが使用されるかどうかが決まります。P\_DOWN LSB ビットを 1 に設定すると、ADCの内部リファレンスが選択されます。

P\_DOWN LSB ビットを 0 に設定した場合は、REF<sub>IN</sub>/REF<sub>OUT</sub> ピンを通じて 2.5 V  $\sim$  V<sub>DD</sub> の外部リファレンスを供給します。パワーアップ時に、内部リファレンスはデフォルトでディスエーブルになります。

内部リファレンス回路は、2.5 V バンド・ギャップ・リファレンスとリファレンス・バッファで構成されています。AD7091R-5 を内部リファレンス・モードで動作させる場合、2.5 V の内部 リファレンスは  $REF_{IN}/REF_{OUT}$  ピンに出力されます。通常、このピンは 2.2  $\mu F$  のコンデンサを使用して GND にデカップリングします。内部リファレンスをシステムの他の部分に適用する場合は、内部リファレンスをバッファした後に適用することが推奨されます。

リファレンス・バッファがパワーアップしてから 2.2 μF デカップリング・コンデンサを充電するまで 50 ms かかります。

#### 電源

AD7091R-5 は、コア電源 ( $V_{DD}$ ) とデジタル入出力インターフェース電源 ( $V_{DRIVE}$ ) の 2 つの電源ピンを使用します。 $V_{DRIVE}$  では、  $1.8\,V\sim5.25\,V$  のあらゆるロジックと直接インターフェースすることができます。システムのロジック・レベルに応じて  $V_{DRIVE}$  と  $V_{DD}$  を接続して、必要に応じて電源の数を削減できます。 AD7091R-5 は、 $V_{DRIVE}$  と  $V_{DD}$  間の電源シーケンスに依存しません。さらに、 AD7091R-5 は、広い周波数範囲にわたって電源の変動による影響を受けません(Figure 25 を参照)。

AD7091R-5 は各変換フェーズの終わりに自動的にパワーダウンします。このため、消費電力はサンプリング・レートに直線的に比例します。AD7091R-5 は自動パワーダウン機能を備えているので、低サンプリング・レートのアプリケーション(数Hz のものを含む)やバッテリ駆動のアプリケーションに最適なデバイスとなっています。

表 6. 推奨パワー・マネジメント・デバイス 1

| Product | Description                                       |

|---------|---------------------------------------------------|

| ADP7102 | 20 V, 300 mA, low noise, CMOS LDO                 |

| ADM7160 | Ultralow noise, 200 mA linear regulator           |

| ADP162  | Ultralow quiescent current, CMOS linear regulator |

<sup>&</sup>lt;sup>1</sup>最新の推奨されるパワー・マネージメント・デバイスについては、AD7091R-5 製品ページを参照してください。

#### デバイスのリセット

パワーアップ時には、デバイスが正常に初期化されるように  $\overline{RESET}$  ピンに少なくとも 10 ns のパルス幅のリセット・パルスを供給する必要があります。リセット・パルスを供給しないと、デバイスが誤動作することがあります。電源の確立に関するリセット・パルスのタイミングについては、Figure 35 を参照してください。

RESET ピンは、いつでもデバイスとすべての内部レジスタ(コマンド・レジスタを含む)の内容をデフォルト状態にリセットできます。リセット動作をアクティブにするには、RESET ピンが SCL 信号に同期されていない間、このピンを 10 ns 以上ロー・レベルに設定します。通常動作を確保するには、RESET ピンを常に安定したロジック・レベルに保持する必要があります。

図 35. RESET ピンのパワーアップのタイミング

#### アナログ入力

Figure 36 に、AD7091R-5 のアナログ入力構造の等価回路を示します。D1 と D2 のダイオードにより、アナログ入力の ESD 保護機能が実現します。アナログ入力信号が電源レールを上回る場合は相違が 300 mV を超えないようにしてください。300 mV を超えると、ダイオードが順方向にバイアスされて、基板に電流が流れます。各ダイオードがデバイスに損傷を与えずに許容できる最大電流は 10 mA です。

図 36. アナログ入力の等価回路

図 36 に示す C1 コンデンサは約 400 fF(typ)で、主にピン容量に起因します。R1 抵抗はスイッチのオン抵抗で構成される集中定数コンポーネントです。この抵抗は約 500  $\Omega$ (typ)です。C2 コンデンサは ADC のサンプリング・コンデンサで、容量は 3.6 pF(typ)です。

高調波歪みと S/N 比が重視されるアプリケーションでは、低インピーダンスのソースからアナログ入力を駆動してください。信号源インピーダンスが大きいと、ADC の AC 性能に重大な影響を与えます。このため、Figure 37 に示す入力バッファ・アンプが必要になることもあります。オペ・アンプの選択は、アプリケーションに依存します。

アナログ入力を駆動するアンプが存在しない場合は、信号源インピーダンスを低い値に制限します。最大信号源インピーダンスは、許容可能な全高調波歪み(THD)の大きさに依存します。信号源インピーダンスが増加すると THD が大きくなるため、性能が低下します。

仕様規定された性能を実現するには、AD7091R-5  $V_{INX}$  ピンへのアナログ入力信号経路で外付けフィルタを使用します。このフィルタには、1 極のローパス RC フィルタまたは同等のフィルタを使用できます。

$MUX_{OUT}$  ピンを  $ADC_N$  ピンに直接接続します。必要に応じて、バッファ・アンプを経路に挿入します。チャンネルをシーケンシングする場合、バッファへの入力と  $MUX_{OUT}$  の間にフィルタを配置しないでください。フィルタを配置すると、クロストークが発生します。バッファを実装しない場合、チャンネルをシーケンシングするときに  $MUX_{OUT}$  と  $ADC_N$  の間にフィルタを配置しないでください。フィルタを配置すると、クロストークが発生します。

#### ドライバ・アンプの選択

AD7091R-5 は簡単に駆動できますが、ドライバ・アンプは次の条件を満たす必要があります。

AD7091R-5のSNRと遷移ノイズ性能を維持するには、ドライバ・アンプによって生成されるノイズをできるだけ低く抑える必要があります。ドライバから発生するノイズは、AD7091R-5アナログ入力回路のR1とC2から構成される1極ローパス・フィルタ、または外付けフィルタ(使用した場合)により除去されます。AD7091R-5のノイズは350μVrms(typ)であるため、アンプに起因するSNRの性能低下は、次式で与えられます。

$$SNR_{LOSS} = 20 \log \left( \frac{350}{\sqrt{350^2 + \frac{\pi}{2} f_{-3dB} (Ne_N)^2}} \right)$$

ここで、

$f_{3dB}$  は AD7091R-5(1.5 MHz)の入力帯域幅(MHz)、または入力フィルタのカットオフ周波数(使用する場合)。 N はアンプのノイズ・ゲイン(例えば、バッファ構成ではゲイン = 1。 Figure 37 を参照)。

eNは、オペ・アンプの等価入力ノイズ電圧(nV/√Hz)。

- AC アプリケーションの場合、ドライバは AD7091R-5 に 見合う THD 性能を備えている必要があります。

- MUXour と ADCIN の間にバッファを配置する場合、ドライバ・アンプと AD7091R-5 アナログ入力回路は、コンデンサ・アレイへのフル・スケール・ステップに対して 12 ビット・レベル (0.0244 %、244 ppm) でセトリングする必要があります。アンプのデータシートでは、一般に 0.1% ~ 0.01% でのセトリングが仕様規定されていて、12 ビット・レベルでのセトリング時間とは大幅に異なることがあります。ドライバを選択する前に、アンプのセトリング時間を確認してください。

表 7. 推奨ドライバ・アンプ

| X.1.1EX.1.2.1 |                                                  |  |  |  |  |

|---------------|--------------------------------------------------|--|--|--|--|

| Product       | Description <sup>1</sup>                         |  |  |  |  |

| ADA4805-1     | Low noise, low power, wide bandwidth amplifier   |  |  |  |  |

| AD8031        | Low voltage, low power, single channel amplifier |  |  |  |  |

| AD8032        | Low voltage, low power, dual channel amplifier   |  |  |  |  |

| AD8615        | Low frequency, low voltage amplifier             |  |  |  |  |

<sup>&</sup>lt;sup>1</sup> 最新の推奨される ADC ドライバ製品については、AD7091R-5 製品ページを参照してください。

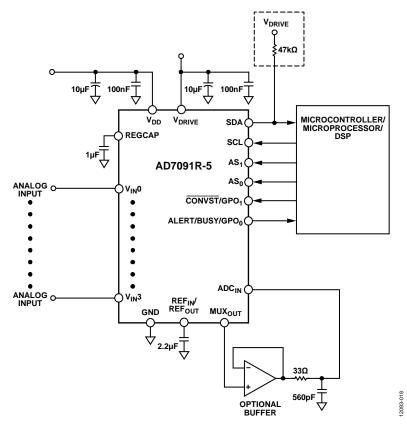

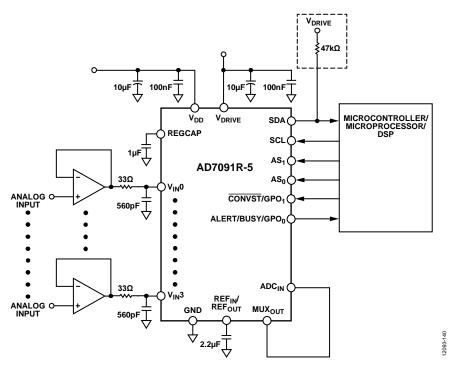

#### 代表的な接続図

図 37 と図 38 に、AD7091R-5 の一般的な接続図を示します。

$2.7\,\mathrm{V}\sim5.25\,\mathrm{V}$  の範囲の正電源を  $V_{DD}$  ピンに接続します。  $V_{DD}$  デカップリング・コンデンサの代表値は、 $100\,\mathrm{nF}$  と  $10\,\mathrm{\mu F}$  です。これらのコンデンサはデバイス・ピンのできるだけ近く配置してください。規定の性能を達成するため、REF $_{\mathrm{IN}}$ /REF $_{\mathrm{OUT}}$  ピンをデカップリングしてください。REF $_{\mathrm{IN}}$ /REF $_{\mathrm{OUT}}$  コンデンサの代表値は  $2.2\,\mathrm{\mu F}$  で、これは  $0\,\mathrm{V}\sim\mathrm{V}_{\mathrm{REF}}$  のアナログ入力範囲を提供します。レギュレータ・バイパス(REGCAP)デカップリング・コンデンサの代表値は  $1\,\mathrm{\mu F}$  です。  $V_{\mathrm{DRIVE}}$  入力へ加えられる電圧が、シリアル・インターフェースの電圧を制御します。このため、このピンをマイクロプロセッサの電源に接続してください。  $V_{\mathrm{DRIVE}}$  を  $1.8\,\mathrm{V}\sim5.25\,\mathrm{V}$  の範囲に設定します。  $V_{\mathrm{DRIVE}}$  デカップリング・コンデンサの代表値は、 $100\,\mathrm{nF}$  と  $10\,\mathrm{\mu F}$  です。  $16\,\mathrm{U}$  ット変換結果( $3\,\mathrm{F}$  ドレス・ビット、 $1\,\mathrm{F}$  アラート・ビット、 $12\,\mathrm{F}$  ータ・ビット)は $2\,\mathrm{F}$  バイトで出力され、最上位バイト (MSB) が最初に示されます。

外付けリファレンスが必要な場合は、設定レジスタを使用して内部リファレンスをディスエーブルにします。外付けリファレンス電圧を $1.0\,\mathrm{V}\sim5.25\,\mathrm{V}$ の範囲で選択して、 $\mathrm{REF}_{\mathrm{IN}}/\mathrm{REF}_{\mathrm{OUT}}$ ピンに接続します。

消費電力が問題となるアプリケーションの場合は、ADC のパワーダウン・モードを使用して消費電力性能を向上させます。 詳細については、Modes of Operation のセクションを参照してください。

図 37. オプションのバッファ使用時の代表的な接続図

図 38. オプションのバッファ未使用時の代表的な接続図

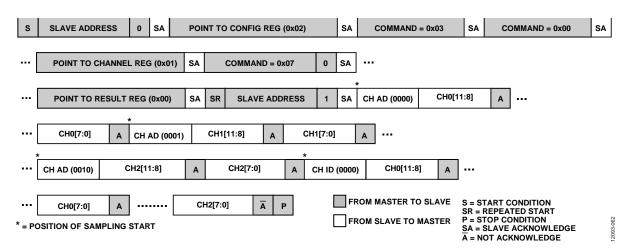

# I2C レジスタ

AD7091R-5 には、複数のユーザープログラマブル・レジスタ があります。Table 9 に、レジスタの完全なリストを示します。

このレジスタは、リード/ライト(R/W)または読出し専用(R)です。リード/ライト・レジスタでは、データの書込みと読出しを行えます。読出し専用レジスタでは、データの読出しのみを行えます。読出し専用レジスタまたは未実装レジスタ・アドレスへの書込みは、NOP(無動作)コマンドとみなされます。この $I^2C$ コマンドは、AD709IR-5によって無視されます。読出し専用レジスタに書込みを行うと、次の $I^2C$ フレームの前に変換を実行しない限り、後続の $I^2C$ フレームへの出力はすべてゼロになります。同様に、未実装レジスタの読出しを行うと、ゼロが出力されます。

#### レジスタのアドレス指定

AD7091R-5 でのシリアル転送は、9 つの SCL サイクルで構成されます。データは9ビット(トランスミッタからの8ビットのデータと後続のレシーバからのアクノレッジ・ビット)のグループとしてシリアル・バスを介して転送されます。SDAラインでのデータ遷移は、クロック信号のロー期間に発生し、ハイ期間中は安定している必要があります。レシーバは、アクノレッジ・ビット中に SDAラインをロー・レベルにプルダウンして、先行バイトが正常に受信されたことを通知します。そうでない場合は、このトランザクションをキャンセルします。マスターが送信する先頭バイトは、7ビットのスレーブ・アドレスと後続のデータ方向ビットで構成されている必要があります。バス上の各デバイスは固有のスレーブ・アドレスを持っているため、先頭バイトによりトランザクション時に1つのスレーブ・デバイスとの交信がセットアップされます。

このトランザクションは、スレーブ・デバイスへの書込み(データ方向ビット=0) またはスレーブ・デバイスからのデータの 読出し (データ方向ビット=1) に使用できます。 読出しトランザクションの場合、(別の書込みトランザクションで)スレーブ・デバイスに最初に書込みを行った後、どのレジスタから読み出すかを通知する必要があります。 読出しと書込みを1つのトランザクション内で行うことはできません。

トランザクションが完了すると、マスターはバスの制御を維持して、次のスタート・ビットを発生させて新しいトランザクションを開始できます(SCLがハイ・レベルになっているときの SDAでのハイ・レベルからロー・レベルへの遷移)。この動作は反復開始と呼ばれます。代わりに、SCLラインを解放した後、SDAラインを解放することにより、バスを放棄することもできます。 SCLがハイ・レベルになっている間、SDAでのロー・レベルからハイ・レベルへの遷移をストップ・ビット (P) と呼びます。これにより、 $\Gamma C$  バスはアイドル状態のままになります(バスによって電流は消費されません)。

#### スレーブ・アドレス

デバイスに書き込む先頭バイトは、スレーブ・アドレス・バイトです。AD7091R-5には、7ビット・スレーブ・アドレスがあります。AD7091R-5では、7ビット・スレーブ・アドレスの3個のMSBは3'b010に固定されています。4個のLSBは、外部ピンを使用してユーザーが設定します。各デバイスに2個のアドレス選択ピンがあり、各ピンでハイ、ロー、または未使用を検出できます。結果として9個の組み合わせが可能です。

Table 8 に、アドレス選択ピンの各種構成での AD7091R-5 のスレーブ・アドレスの 4 個の LSB を示します。

表 8. スレーブ・アドレス

| <u> </u>                     |                              |    |    |    |    |  |  |

|------------------------------|------------------------------|----|----|----|----|--|--|

| AS <sub>1</sub> <sup>1</sup> | AS <sub>0</sub> <sup>1</sup> | A3 | A2 | A1 | A0 |  |  |

| $V_{ m DD}$                  | $V_{DD}$                     | 0  | 0  | 0  | 0  |  |  |

| $V_{\mathrm{DD}}$            | NC                           | 0  | 0  | 1  | 0  |  |  |

| $V_{\mathrm{DD}}$            | GND                          | 0  | 0  | 1  | 1  |  |  |

| NC                           | $V_{DD}$                     | 1  | 0  | 0  | 0  |  |  |

| NC                           | NC                           | 1  | 0  | 1  | 0  |  |  |

| NC                           | GND                          | 1  | 0  | 1  | 1  |  |  |

| GND                          | $V_{DD}$                     | 1  | 1  | 0  | 0  |  |  |

| GND                          | NC                           | 1  | 1  | 1  | 0  |  |  |

| GND                          | GND                          | 1  | 1  | 1  | 1  |  |  |

$<sup>^1</sup>$  NC は AS<sub>x</sub> ピンをフロート状態のままにすることを意味し、 $V_{DD}$  はハイ・レベルへプルアップすることを意味し、GND はロー・レベルへプルダウンすることを意味します。

#### I2C レジスタ・アクセス

表 9. レジスタの説明

| Address | Register Name        | Default | Access |

|---------|----------------------|---------|--------|

| 0x00    | Conversion result    | 0x0000  | R      |

| 0x01    | Channel              | 0x0000  | R/W    |

| 0x02    | Configuration        | 0x00C0  | R/W    |

| 0x03    | Alert indication     | 0x0000  | R      |

| 0x04    | Channel 0 low limit  | 0x0000  | R/W    |

| 0x05    | Channel 0 high limit | 0x01FF  | R/W    |

| 0x06    | Channel 0 hysteresis | 0x01FF  | R/W    |

| 0x07    | Channel 1 low limit  | 0x0000  | R/W    |

| 0x08    | Channel 1 high limit | 0x01FF  | R/W    |

| 0x09    | Channel 1 hysteresis | 0x01FF  | R/W    |

| 0x0A    | Channel 2 low limit  | 0x0000  | R/W    |

| 0x0B    | Channel 2 high limit | 0x01FF  | R/W    |

| 0x0C    | Channel 2 hysteresis | 0x01FF  | R/W    |

| 0x0D    | Channel 3 low limit  | 0x0000  | R/W    |

| 0x0E    | Channel 3 high limit | 0x01FF  | R/W    |

| 0x0F    | Channel 3 hysteresis | 0x01FF  | R/W    |

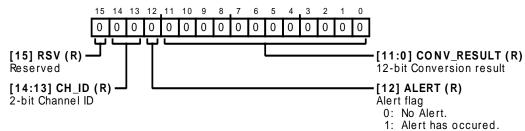

#### 変換結果レジスタ

変換結果レジスタは、16ビットの読出し専用レジスタです。ここには、最新のADC変換結果がストレート・バイナリ・フォーマットで格納されます。変換されたチャンネルのチャンネルIDとアラート・ステータスも、このレジスタに含まれます。

表 10. 変換結果ビット・マップ

LSB MSB **B15 B14 B13 B12** B11 **B10 B9 B8 B7** В6 **B5 B4 B3** B2 **B**1 **B0** RSV CH\_ID ALERT CONV\_RESULT

表 11. 変換結果レジスタのビットの説明

| ビット     | 名前 RSV CH_ID  ALERT    | 説明     | •                      | リセット           | アクセス  |             |

|---------|------------------------|--------|------------------------|----------------|-------|-------------|

| 15      | RSV                    | 予約済み   | ب                      |                | 0x0   | R           |

| [14:13] | CH_ID                  | 変換した   | こチャンネル                 | の2ビット・チャンネル ID | 0x0   | R           |

|         | RSV 13] CH_ID  ALERT   | B14    | B13                    | アナログ入力チャンネル    |       |             |

|         |                        | 0      | 0                      | チャンネル 0        |       |             |

|         |                        | 0      | 1                      | チャンネル 1        |       |             |

|         |                        | 1      | 0                      | チャンネル 2        |       |             |

|         |                        | 1      | 1                      | チャンネル 3        |       |             |

| 12      | ALERT                  | アラー    | ・・フラグ                  |                | 0x0   | R           |

|         |                        | 0: アラー | - ト未発生                 |                |       |             |

|         |                        | 1: アラー | ートが発生                  |                |       |             |

| [11:0]  | CONV_RESULT 12 ビット変換結果 |        | CONV_RESULT 12 ビット変換結果 |                | 0x000 | x0 R R x0 R |

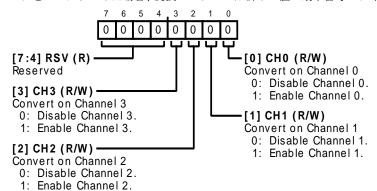

#### チャンネル・レジスタ

AD7091R-5のチャンネル・レジスタは8ビットのリード/ライト・レジスタです。4個の各アナログ入力チャンネルには、チャンネル・レジスタの対応するビットが1個あります。チャンネル変換シーケンスに含めるチャンネルを選択するには、チャンネル・レジスタの対応するチャンネル・ビットを1に設定します。1つの変換による遅延の後に、チャンネル変換シーケンスが更新されます。新しい値を使用してチャンネル・レジスタをプログラムした場合、変換シーケンスは新しい値の最小番号のチャンネルにリセットされます。

表 12. チャンネル・ビット・マップ

MSB

LSB

B7

B6

B5

B4

B3

B2

B1

B0

RSV

CH3

CH2

CH1

CH0

表 13. チャンネル・レジスタのビットの説明

| ビット   | 名前  | 説明                 | リセット | アクセス |

|-------|-----|--------------------|------|------|

| [7:4] | RSV | 予約済み               | 0x00 | R    |

| 3     | CH3 | チャンネル3で変換          | 0x0  | R/W  |

|       |     | 0: チャンネル 3 ディスエーブル |      |      |

|       |     | 1: チャンネル 3 イネーブル   |      |      |

| 2     | CH2 | チャンネル 2 で変換        | 0x0  | R/W  |

|       |     | 0: チャンネル 2 ディスエーブル |      |      |

|       |     | 1: チャンネル 2 イネーブル   |      |      |

| 1     | CH1 | チャンネル1で変換          | 0x0  | R/W  |

|       |     | 0: チャンネル1ディスエーブル   |      |      |

|       |     | 1: チャンネル 1 イネーブル   |      |      |

| 0     | CH0 | チャンネル 0 で変換        | 0x0  | R/W  |

|       |     | 0: チャンネル 0 ディスエーブル |      |      |

|       |     | 1: チャンネル 0 イネーブル   |      |      |

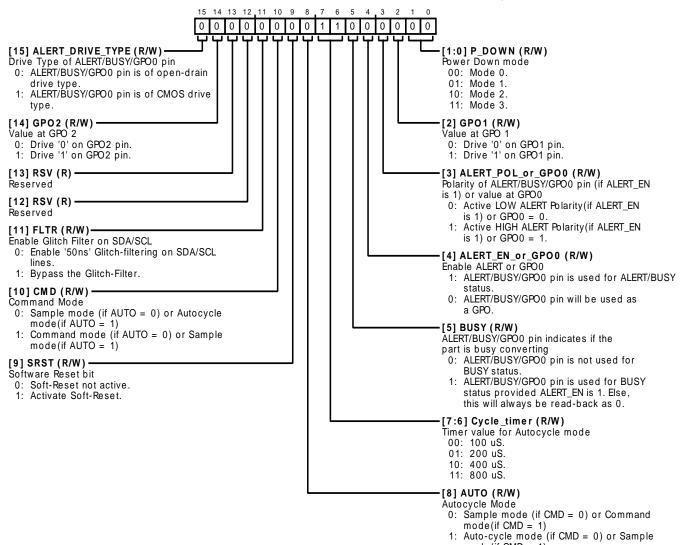

#### 設定レジスタ

設定レジスタは、AD7091R-5の動作モードを設定する16ビットのリード/ライト・レジスタです。

表 14. 設定ビット・マップ

**MSB LSB**

| B15                      | B14  | B13 | B12 | B11  | B10 | В9   | B8   | B7  | В6 | B5       | B4                       | B3                        | B2   | B1    | B0 |

|--------------------------|------|-----|-----|------|-----|------|------|-----|----|----------|--------------------------|---------------------------|------|-------|----|

| ALERT_<br>DRIVE_<br>TYPE | GPO2 | RSV | RSV | FLTR | CMD | SRST | AUTO | CYC | _  | BUS<br>Y | ALERT_<br>EN_OR_G<br>PO0 | ALERT_<br>POL_OR_<br>GPO0 | GPO1 | P_DOV | VN |

mode(if CMD = 1)

#### 表 15. 設定レジスタのビットの説明 1

| ピット | 名前               | 説明                                                    | リセット | アクセス |

|-----|------------------|-------------------------------------------------------|------|------|

| 15  | ALERT_DRIVE_TYPE | ALERT/BUSY/GPO <sub>0</sub> ピンのドライブ・タイプ。              | 0x0  | RW   |

|     |                  | 0: ALERT/BUSY/GPO <sub>0</sub> ピンは、オープンドレイン・ドライブ・タイプ。 |      |      |

|     |                  | 1: ALERT/BUSY/GPO₀ ピンは、CMOS ドライブ・タイプ。                 |      |      |

| 14  | GPO2             | GPO <sub>2</sub> の値。                                  | 0x0  | RW   |

|     |                  | 0: GPO <sub>2</sub> ピンを 0 にドライブ。                      |      |      |

|     |                  | 1: GPO <sub>2</sub> ピンを 1 にドライブ。                      |      |      |

| 13  | RSV              | 予約済み。                                                 | 0x00 | R    |

| 12  | RSV              | 予約済み。                                                 | 0x00 | R    |

| ビット   | 名前                | 説明                                                        |                                                   |                                                                                      |                      |                    | リセット | アクセス |  |  |

|-------|-------------------|-----------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------|----------------------|--------------------|------|------|--|--|

| 11    | FLTR              | SDA/SCL                                                   | でグリッラ                                             | チ・フィルタをイネーブルレ                                                                        | こします。                |                    | 0x0  | RW   |  |  |

|       |                   | 0: SDA/SO                                                 | CL ラインで                                           | で 50 ns のグリッチ・フィル                                                                    | タリングをイネー             | ーブルにします。           |      |      |  |  |

|       |                   | 1: グリッ                                                    | チ・フィル                                             | <i>、</i> タをバイパスします。                                                                  |                      |                    |      |      |  |  |

| 10    | CMD               | コマンド                                                      | ・モード。                                             |                                                                                      |                      |                    | 0x0  | RW   |  |  |

|       |                   | 0: サンプ<br>1 の場合)                                          |                                                   | (AUTO=0の場合) またば                                                                      | 自動サイクル・コ             | モード(AUTO=          |      |      |  |  |

|       |                   | 1: コマン<br>場合)。                                            | ド・モード                                             | (AUTO=0の場合)またに                                                                       | はサンプル・モー             | ド(AUTO=1の          |      |      |  |  |

| 9     | SRST              | コントロ・<br>レジスタ:<br>れません。<br>0: ソフト                         | ール・ロジ<br>がリセット<br>。このビッ<br>・リセット                  | ット・ビット。このビット<br>ジック・レジスタ、変換結果<br>されますが、他のメモリマ<br>トは、次のクロック・サイ<br>が非アクティブ。<br>がアクティブ。 | レジスタ、および<br>ップド・レジスク | バアラート表示<br>タはリセットさ | 0x0  | RWAC |  |  |

| 8     | AUTO              |                                                           | クル・モー                                             |                                                                                      |                      |                    | 0x0  | RW   |  |  |

| o     | ACTO              | ,                                                         |                                                   | : (CMD = 0 の場合) または                                                                  | コマンド・モー              | ド (CMD = 1 の       | OXO  | KW   |  |  |

|       |                   |                                                           | 1:自動サイクル・モード (CMD=0 の場合) またはサンプル・モード (CMD=1 の場合)。 |                                                                                      |                      |                    |      |      |  |  |

| [7:6] | CYCLE_TIMER       | 自動サイ                                                      | クル・モー                                             | ・ドのタイマー値。                                                                            |                      |                    | 0x3  | RW   |  |  |

|       |                   | 00:100 μs <sub>c</sub>                                    |                                                   |                                                                                      |                      |                    |      |      |  |  |

|       |                   | 01:200 μs <sub>c</sub>                                    | )                                                 |                                                                                      |                      |                    |      |      |  |  |

|       |                   | 10:400 μs <sub>c</sub>                                    | )                                                 |                                                                                      |                      |                    |      |      |  |  |

|       |                   | 11:800 μs <sub>c</sub>                                    |                                                   |                                                                                      |                      |                    |      |      |  |  |

| 5     | BUSY              | SY ALERT/BUSY/GPO <sub>0</sub> ピンは、デバイスが変換中であるかどうかを示します。  |                                                   |                                                                                      |                      |                    |      |      |  |  |

|       |                   | 0: ALERT                                                  |                                                   |                                                                                      |                      |                    |      |      |  |  |

|       |                   | 1: ALERT<br>タスに使<br>クされま                                  |                                                   |                                                                                      |                      |                    |      |      |  |  |

| 4     | ALERT_EN_OR_GPO0  | ALERT/B                                                   | USY/GPO <sub>0</sub>                              | ピンまたは GPO0 をイネー                                                                      | ブルにします。              |                    | 0x0  | RW   |  |  |

|       |                   | 1: ALERT                                                  | BUSY/GP                                           | O <sub>0</sub> ピンは ALERT/BUSY ス                                                      | テータスに使用さ             | れます。               |      |      |  |  |

|       |                   | 0: ALERT                                                  | BUSY/GP                                           | O <sub>0</sub> ピンは GPO として使用:                                                        | されます。                |                    |      |      |  |  |

| 3     | ALERT_POL_OR_GPO0 | ALERT/B<br>の値。                                            | USY/GPO <sub>0</sub>                              | ピンの極性(ALERT_EN_O                                                                     | R_GPO0が1の場           | 合)またはGPO0          | 0x0  | RW   |  |  |

|       |                   |                                                           | ィブ・ロー<br>は GPO0 =                                 | - ALERT/BUSY/GPO <sub>0</sub> 極性<br>0。                                               | (ALERT_EN_OR_        | _GPO0 が 1 の場       |      |      |  |  |

|       |                   |                                                           | ィブ・ハイ<br>は GPO0 =                                 | ALERT/BUSY/GPO <sub>0</sub> 極性<br>1。                                                 | (ALERT_EN_OR_        | _GPO0 が 1 の場       |      |      |  |  |

| 2     | GPO1              | GPO <sub>1</sub> の値                                       | 1.                                                |                                                                                      |                      |                    | 0x0  | RW   |  |  |

|       |                   | $0: \overline{\text{CONVST}}/\text{GPO}_1$ ピンを $0$ にドライブ。 |                                                   |                                                                                      |                      |                    |      |      |  |  |

|       |                   | 1: CONVS                                                  | T/GPO₁ ピ                                          | ンを1にドライブ。                                                                            |                      |                    |      |      |  |  |

| [1:0] | P_DOWN            | パワーダ                                                      |                                                   | 0x0                                                                                  | R/W                  |                    |      |      |  |  |

|       |                   | 設定                                                        | モード                                               | スリープ・モード <i>/</i><br>バイアス・ジェネレータ                                                     | 内部リフ                 | ァレンス               |      |      |  |  |

|       |                   | 00                                                        | モード0                                              | オフ                                                                                   | オフ                   |                    |      |      |  |  |

|       |                   | 01                                                        | モード1                                              | オフ                                                                                   | オン                   |                    |      |      |  |  |

|       |                   | 10                                                        | モード2                                              | オン                                                                                   | オフ                   |                    |      |      |  |  |

|       |                   | 11                                                        | モード3                                              |                                                                                      | オン                   |                    |      |      |  |  |

<sup>&</sup>lt;sup>1</sup> AD7091R-5 は、FC 標準グリッチ・フィルタをサポートしていますが、クロック・ストレッチングや一般的なコール・アドレス指定はサポートしていません。

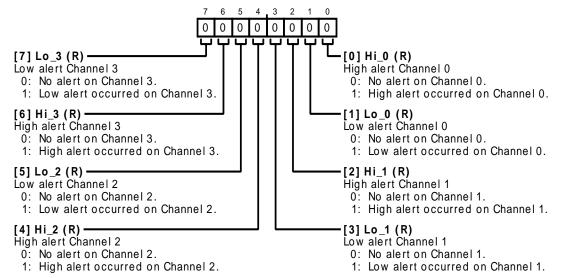

#### アラート表示レジスタ

8 ビット・アラート表示レジスタは、アラート・イベントの情報を提供する読出し専用レジスタです。Channel x Low Limit Register の セクションと Channel x High Limit Register のセクションで説明したように、変換結果により ALERT/BUSY/GPO $_0$  ピンがアクティブに なった場合、アラート・レジスタを読み出してアラートの発生源を判断します。このレジスタには、チャンネルあたり 2 つのステータス・ビットがあり、1 つは上限、もう 1 つは下限に対応しています。ステータスが1のビットは、どこで(どのチャンネルで)超過 が発生したか示し、上限または下限のどちらで超過が発生したかを示します。最初のアラートの受信とアラート・レジスタの問い合わせの間に別のチャンネルで 2 番目のアラート・イベントが発生した場合、そのアラート・イベントに対応するビットもセットされます。

アラート表示レジスタの内容は、読み出すとリセットされます。AD7091R-5 が  $I^2$ C インターフェースを使用してアラート表示レジスタを読み出すと、このレジスタはバイトの4番目の SCLクロックでリセットされます。このときまで、このレジスタのデータは  $I^2$ C シフト・レジスタに移動されます。

未実装チャンネルのアラート・ビットは、常にゼロを返します。

表 16. アラート表示ビット・マップ

| MSB  |      |      |      |      |      |      | LSB  |

|------|------|------|------|------|------|------|------|

| B7   | B6   | B5   | B4   | B3   | B2   | B1   | В0   |

| LO_3 | HI_3 | LO_2 | HI_2 | LO_1 | HI_1 | LO_0 | HI_0 |

#### 表 17.アラート表示レジスタのビットの説明

| ビット | ビット名 | 説明                     | リセット | アクセス |

|-----|------|------------------------|------|------|

| 7   | LO_3 | チャンネル3ロー・アラート・ステータス    | 0x0  | R    |

|     |      | 0: チャンネル 3 にアラートなし     |      |      |

|     |      | 1: チャンネル3でロー・アラートが発生   |      |      |

| 6   | HI_3 | チャンネル 3 ハイ・アラート・ステータス  | 0x0  | R    |

|     |      | 0: チャンネル 3 にアラートなし     |      |      |

|     |      | 1: チャンネル 3 でハイ・アラートが発生 |      |      |

| 5   | LO_2 | チャンネル2ロー・アラート・ステータス    | 0x0  | R    |

|     |      | 0: チャンネル 2 にアラートなし     |      |      |

|     |      | 1: チャンネル 2 でロー・アラートが発生 |      |      |

| 4   | HI_2 | チャンネル 2 ハイ・アラート・ステータス  | 0x0  | R    |

|     |      | 0: チャンネル 2 にアラートなし     |      |      |

|     |      | 1: チャンネル2でハイ・アラートが発生   |      |      |

| 3   | LO_1 | チャンネル1ロー・アラート・ステータス    | 0x0  | R    |

|     |      | 0: チャンネル 1 にアラートなし     |      |      |

|     |      | 1: チャンネル 1 でロー・アラートが発生 |      |      |

| ビット | ビット名 | 説明                     | リセット | アクセス |

|-----|------|------------------------|------|------|

| 2   | HI_1 | チャンネル1ハイ・アラート・ステータス    | 0x0  | R    |

|     |      | 0: チャンネル1にアラートなし       |      |      |

|     |      | 1: チャンネル 1 でハイ・アラートが発生 |      |      |

| 1   | LO_0 | チャンネル 0 ロー・アラート・ステータス  | 0x0  | R    |

|     |      | 0: チャンネル 0 にアラートなし     |      |      |

|     |      | 1: チャンネル 0 でロー・アラートが発生 |      |      |

| 0   | HI_0 | チャンネル 0 ハイ・アラート・ステータス  | 0x0  | R    |

|     |      | 0: チャンネル 0 にアラートなし     |      |      |

|     |      | 1: チャンネル 0 でハイ・アラートが発生 |      |      |

#### チャンネル X ロー・リミット・レジスタ

AD7091R-5 の各アナログ入力チャンネルには、独自のロー・リミット・レジスタがあります。ロー・リミット・レジスタは16 ビットのリード/ライト・レジスタです。レジスタ・アドレスについては、Table 9 を参照してください。ロー・リミット・レジスタは、ALERT 出力をアクティブにする変換値の下限を格納します。

16 ビットのうち、ビット B11 ~ ビット B0 の 12 個の最下位ビット (LSB) のみが使用されます。 ビット B15 ~ ビット B12 は 使用されません。

#### チャンネル X リミット・レジスタ

AD7091R-5 の各アナログ入力チャンネルには、独自のリミット・レジスタがあります。リミット・レジスタは 16 ビットのリード/ライト・レジスタです。レジスタ・アドレスについては、Table 9 を参照してください。リミット・レジスタは、ALERT出力をアクティブにする変換値の上限を格納します。

表 18. チャンネル x ロー・リミット・ビット・マップ

16 ビットのうち、ビット $B11 \sim$  ビットB0 の 12 個の最下位ビット (LSB) のみが使用されます。ビット $B15 \sim$  ビットB12 は使用されません。

#### チャンネル X ヒステリシス・レジスタ

AD7091R-5 の各アナログ入力チャンネルには、独自のヒステリシス・レジスタがあります。ヒステリシス・レジスタは 16 ビットのリード/ライト・レジスタです。レジスタ・アドレスについては、Table 9 を参照してください。ヒステリシス・レジスタは、リミット・レジスタを使用しているときにヒステリシス値(N)を格納します。ヒステリシス値は、リミットを超過した場合の ALERT/ BUSY/GPO $_0$  ピンのリセット・ポイントを決定します。

16 ビットのうち、ビット B11 ~ ビット B0 の 12 個の最下位ビット (LSB) のみが使用されます。 ビット B15 ~ ビット B12 は 使用されません。

| MSB |     |     |     |     |     |    |    |    |        |         |    |    |    |    | LSB |

|-----|-----|-----|-----|-----|-----|----|----|----|--------|---------|----|----|----|----|-----|

| B15 | B14 | B13 | B12 | B11 | B10 | В9 | B8 | B7 | B6     | B5      | B4 | В3 | B2 | B1 | В0  |

|     | R.S | SV  |     |     |     |    |    |    | CHx LO | W LIMIT |    |    |    |    |     |

表 19. チャンネル x ロー・リミット・レジスタのビットの説明

| ビット     | ビット名          | 説明                | リセット  | アクセス |

|---------|---------------|-------------------|-------|------|

| [15:12] | RSV           | 予約済み              | 0x00  | R    |

| [11:0]  | CHx LOW LIMIT | チャンネル x のロー・リミット値 | 0x000 | R/W  |

#### 表 20. チャンネル x 上限ビット・マップ

|   | MSB |     |     |     |     |     |    |    |    |         |         |    |    |    |    | LSB |

|---|-----|-----|-----|-----|-----|-----|----|----|----|---------|---------|----|----|----|----|-----|

| ĺ | B15 | B14 | B13 | B12 | B11 | B10 | В9 | B8 | B7 | B6      | B5      | B4 | В3 | B2 | B1 | В0  |

| ĺ |     | R.  | SV  |     |     |     |    |    |    | CHx HIG | H LIMIT |    |    |    |    |     |

#### 表 21. チャンネル x リミット・レジスタのビットの説明

| ビット     | ビット名           | 説明             | リセット  | アクセス |

|---------|----------------|----------------|-------|------|

| [15:12] | RSV            | 予約済み           | 0x00  | R    |

| [11:0]  | CHx HIGH LIMIT | チャンネル x のリミット値 | 0xFFF | R/W  |

#### 表 22. チャンネル x ヒステリシス・ビット・マップ

| MSB |                    |     |     |     |     |    |    |    |    |                |    |    |    |    | LSB |

|-----|--------------------|-----|-----|-----|-----|----|----|----|----|----------------|----|----|----|----|-----|

| B15 | B14                | B13 | B12 | B11 | B10 | В9 | B8 | В7 | В6 | B <sub>5</sub> | В4 | В3 | B2 | B1 | Во  |

|     | RSV CHX HYSTERISIS |     |     |     |     |    |    |    |    |                |    |    |    |    |     |

## 表 23. チャンネル x ヒステリシス・レジスタのビットの説明

| ビット ビット名 |                | 説明               | リセット  | アクセス |

|----------|----------------|------------------|-------|------|

| [15:12]  | RSV            | 予約済み             | 0x00  | R    |

| [11:0]   | CHx HYSTERISIS | チャンネル x のヒステリシス値 | 0xFFF | R/W  |

-タシート AD7091R-5

# I<sup>2</sup>C インターフェース

AD7091R-5 の制御はI<sup>2</sup>C 互換シリアル・バスを使用して実行し ます。AD7091R-5 は、プロセッサなどのマスター・デバイス の制御下にあるスレーブ・デバイスとしてこのバスに接続され ます。

#### シリアル・バスのアドレス・バイト

デバイスに書き込む先頭バイトは、スレーブ・アドレス・バイ トです。すべての I<sup>2</sup>C 互換デバイスと同様、AD7091R-5 には7 ビットのシリアル・アドレスがあります。-このアドレスの3個 の MSB は 010 に設定されています。4 個の LSB は、3 ステー ト入力ピン ASo および ASI を使用してプログラムすることがで きます(Table 24 を参照)。

Table 24 で High はピンを VDRIVE に接続することを意味し、Low はピンを GND に接続することを意味します。NC はピンをフ ロート状態のままにすることを意味します。NC の場合、ピン の浮遊容量は30 pF以下にしてフローティング状態を正しく検 出できるようにする必要があります。このため、 PCB パター ンはできるだけ短くする必要があります。

表 24.3 ステート入力ピンを使用したスレーブ・アドレスの制御

|                 |                 | Slave Address (A6 to A0) |      |  |  |  |  |  |

|-----------------|-----------------|--------------------------|------|--|--|--|--|--|

| AS <sub>1</sub> | AS <sub>0</sub> | Binary                   | Hex  |  |  |  |  |  |

| High            | High            | 010 0000                 | 0x20 |  |  |  |  |  |

| High            | NC              | 010 0010                 | 0x22 |  |  |  |  |  |

| High            | Low             | 010 0011                 | 0x23 |  |  |  |  |  |

| NC              | Н               | 010 1000                 | 0x28 |  |  |  |  |  |

| NC              | NC              | 010 1010                 | 0x2A |  |  |  |  |  |

| NC              | Low             | 010 1011                 | 0x2B |  |  |  |  |  |

| Low             | High            | 010 1100                 | 0x2C |  |  |  |  |  |

| Low             | NC              | 010 1110                 | 0x2E |  |  |  |  |  |

| Low             | Low             | 010 1111                 | 0x2F |  |  |  |  |  |

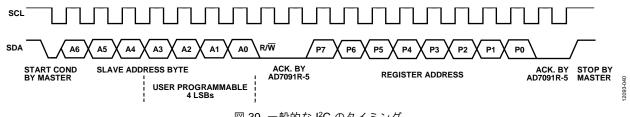

#### 一般的な I<sup>2</sup>C のタイミング

図39に、I2C準拠のインターフェースを使用した一般的な読出 し動作と書込み動作のタイミング図を示します。

バスを駆動するデバイスが存在しないときは、SCL と SDA は ハイ・レベルになります。これはアイドル状態と呼ばれます。 バスがアイドル状態のとき、マスターは、シリアル・クロック・ ライン (SCL) がハイ・レベルになっている間にシリアル・デー

タ・ライン (SDA) がハイ・レベルからロー・レベルに遷移す ることによる開始条件を確立してデータ転送を開始します。こ れは、データ・ストリームが後続することを示します。マスター・ デバイスは、クロックを生成する必要があります。

データは9ビット(トランスミッタからの8ビットのデータと 後続のレシーバからのアクノレッジ・ビット(ACK))のグルー プとしてシリアル・バスを介して転送されます。SDA ライン でのデータ遷移は、クロック信号のロー期間中に発生し、ハイ 期間中は安定している必要があります。レシーバは、アクノレッ ジ・ビット中にSDA ラインをロー・レベルにプルダウンして、 先行バイトが正常に受信されたことを通知する必要があります。 そうでない場合は、このトランザクションをキャンセルします。