# 120 mA電流シンク 10ビットI<sup>2</sup>C DAC

# AD5821A

## 特長

電流シンク: 120 mA 3×3アレイの WLCSP パッケージを採用 2線式(I<sup>2</sup>C 互換) 1.8 V シリアル・インターフェースを内蔵 10 ビット分解能 電流検出抵抗を内蔵 電源電圧範囲: 2.7 V~5.5 V すべてのコードで単調性を保証 パワーダウン電流: 0.5 µA (typ) リファレンス電圧を内蔵 超低ノイズのプリアンプを内蔵 パワーダウン機能 パワーオン・リセット

### アプリケーション

民牛用

レンズのオートフォーカス 手振れ補正 光学ズーム シャッタ 絞り/露光 ニュートラル・フィルタ レンズ・カバー カメラ付き携帯電話 デジタル静止画カメラ カメラ・モジュール デジタル・ビデオ・カメラ/ビデオ・カメラ カメラ付きデバイス セキュリティ・カメラ Web/PC カメラ

### 工業用

ヒーター制御 ファン制御 クーラー(ペルチェ)制御 ソレノイド・コントロール バルブ制御 リニア・アクチュエータ制御 光制御 電流ループ制御

### 概要

AD5821Aは、出力電流シンク能力 120 mAの 10 ビット・シング ル D/A コンバータ(DAC)です。リファレンス電圧を内蔵し、2.7 V~5.5 V の単電源で動作します。この DAC は、最大 400 kHz の クロック・レートで動作する 2 線式 I<sup>2</sup>C®互換シリアル・インタ ーフェースを経由して制御されます。

AD5821A はパワーオン・リセット回路を採用しているため、 DAC 出力をゼロにしてパワーアップし、有効な書き込みがある までこの出力状態を維持します。また、デバイスの消費電流を1 μA (最大)に削減するパワーダウン機能も内蔵しています。

AD5821A は、カメラ付き携帯電話、デジタル静止画カメラ、ビ デオ・カメラでのオートフォーカス、手振れ補正、光ズーム・ アプリケーション向けにデザインされています。

また、AD5821A は、温度、光、移動を-30°C~+85°C の温度範 囲で性能低下なしで制御するなどの、多くの工業用アプリケー ションにも適しています。

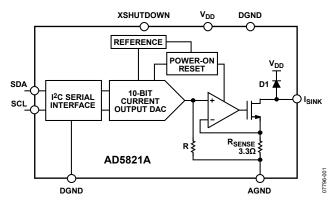

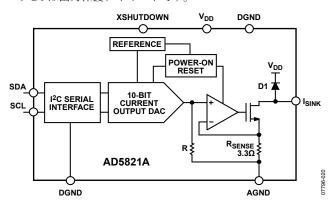

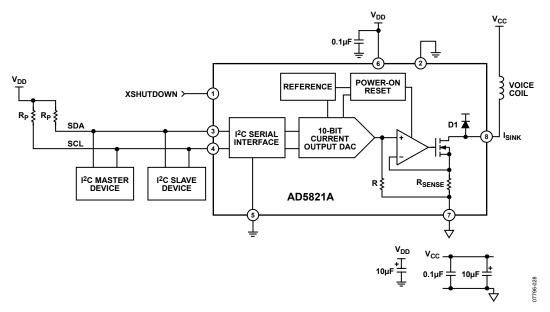

## 機能ブロック図

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に 関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、 アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様 予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。 本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2008 Analog Devices, Inc. All rights reserved.

Rev. 0

本 社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03 (5402) 8200

# AD5821A

# 目次

| 符長                   | l |

|----------------------|---|

| アプリケーション             |   |

| 概要                   |   |

| <del>ん</del> 機能ブロック図 |   |

| 改訂履歴                 |   |

| 仕様                   |   |

| AC 仕様                |   |

| タイミング仕様              |   |

| 絶対最大定格               |   |

| ピン配置およびピン機能説明        |   |

|                      |   |

| 代表的な性能特性               | 7   |

|------------------------|-----|

| 用語                     | 10  |

| 動作原理                   | 11  |

| シリアル・インターフェース          | 11  |

| I <sup>2</sup> C バスの動作 | 11  |

| データ・フォーマット             | 11  |

| 電源のバイパスとグラウンド接続        | 12  |

| アプリケーション情報             | 14  |

| 外形寸法                   | 15  |

| ナーガー・ガノド               | 1.5 |

## 改訂履歴

10/08—Revision 0: Initial Version

# 仕様

$V_{DD}$  = 2.7 V  $\sim$  5.5 V、AGND = DGND = 0 V、負荷抵抗( $R_L$ ) = 25  $\Omega$  ( $V_{DD}$   $\sim$  接続)。特に指定のない限り、すへての仕様は  $T_{MIN}$   $\sim$   $T_{MAX}$  で規定。表 1.

|                                                |                        | B Versio | n <sup>1</sup> |          |                                                                                    |

|------------------------------------------------|------------------------|----------|----------------|----------|------------------------------------------------------------------------------------|

| Parameter                                      | Min                    | Typ      | Max            | Unit     | Test Conditions/Comments                                                           |

| DC PERFORMANCE                                 |                        |          |                |          | $V_{DD} = 3.6 \text{ V}$ to 4.5 V; device operates over 2.7 V to 5.5 V             |

|                                                |                        |          |                |          | with reduced performance                                                           |

| Resolution                                     |                        | 10       |                | Bits     | 117 μA/LSB                                                                         |

| Relative Accuracy <sup>2</sup>                 |                        | ±1.5     | ±4             | LSB      |                                                                                    |

| Differential Nonlinearity <sup>2, 3</sup>      |                        |          | ±1             | LSB      | Guaranteed monotonic over all codes                                                |

| Zero-Code Error <sup>2, 4</sup>                | 0                      | 0.5      | 1              | mA       | All 0s loaded to DAC                                                               |

| Offset Error @ Code 16 <sup>2</sup>            |                        | 0.5      |                | mA       |                                                                                    |

| Gain Error <sup>2</sup>                        |                        |          | ±0.6           | % of FSR | at 25°C                                                                            |

| Offset Error Drift <sup>4, 5</sup>             |                        | 10       |                | μA/°C    |                                                                                    |

| Gain Error Drift <sup>2, 5</sup>               |                        | ±0.2     | ±0.5           | LSB/°C   |                                                                                    |

| OUTPUT CHARACTERISTICS                         |                        |          |                |          |                                                                                    |

| Minimum Sink Current <sup>4</sup>              |                        | 3        |                | mA       |                                                                                    |

| Maximum Sink Current                           |                        | 120      |                | mA       |                                                                                    |

| Output Current During XSHUTDOWN <sup>5</sup>   |                        | 80       |                | nA       | XSHUTDOWN = 0                                                                      |

| Output Compliance <sup>5</sup>                 | 0.6                    |          | $V_{DD}$       | V        | Output voltage range over which maximum 120 mA sink current is available           |

| Output Compliance <sup>5</sup>                 | 0.48                   |          | $V_{DD}$       | V        | Output voltage range over which 90 mA sink current is available                    |

| Power-Up Time <sup>5</sup>                     |                        | 20       |                | μs       | To 10% of FS, coming out of power-down mode; $V_{DD} = 5 \text{ V}$                |

| LOGIC INPUTS (XSHUTDOWN) <sup>5</sup>          |                        |          |                |          |                                                                                    |

| Input Current                                  |                        |          | ±1             | μΑ       |                                                                                    |

| Input Low Voltage, V <sub>INL</sub>            |                        |          | 0.54           | V        | $V_{\rm DD} = 2.7 \text{ V to } 5.5 \text{ V}$                                     |

| Input High Voltage, V <sub>INH</sub>           | 1.26                   |          |                | V        | $V_{\rm DD} = 2.7 \text{ V to } 5.5 \text{ V}$                                     |

| Pin Capacitance                                |                        | 3        |                | pF       |                                                                                    |

| LOGIC INPUTS (SCL, SDA) <sup>5</sup>           |                        |          |                |          |                                                                                    |

| Input Low Voltage, V <sub>INL</sub>            | -0.3                   |          | +0.54          | V        | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$                                         |

| Input High Voltage, V <sub>INH</sub>           | 1.26                   |          | $V_{DD} + 0.3$ | V        | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$                                         |

| Input Low Voltage, V <sub>INL</sub>            | -0.3                   |          | +0.54          | V        | $V_{\rm DD} = 3.6 \text{ V to } 5.5 \text{ V}$                                     |

| Input High Voltage, V <sub>INH</sub>           | 1.4                    |          | $V_{DD} + 0.3$ | V        | $V_{\rm DD} = 3.6 \text{ V to } 5.5 \text{ V}$                                     |

| Input Leakage Current, IIN                     |                        |          | ±1             | μA       | $V_{IN} = 0 \text{ V to } V_{DD}$                                                  |

| Input Hysteresis, V <sub>HYST</sub>            | $0.05~\mathrm{V_{DD}}$ |          |                | V        |                                                                                    |

| Digital Input Capacitance, C <sub>IN</sub>     |                        | 6        |                | pF       |                                                                                    |

| Glitch Rejection <sup>6</sup>                  |                        |          | 50             | ns       | Pulse width of spike suppressed                                                    |

| POWER REQUIREMENTS                             |                        |          |                |          |                                                                                    |

| $ m V_{DD}$                                    | 2.7                    |          | 5.5            | V        |                                                                                    |

| I <sub>DD</sub> (Normal Mode)                  |                        | 0.5      | 1              | mA       | I <sub>DD</sub> specification is valid for all DAC codes;                          |

| ,                                              |                        |          |                |          | $V_{INH} = 1.8 \text{ V}, V_{INL} = GND, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ |

| I <sub>DD</sub> (Power-Down Mode) <sup>7</sup> |                        | 0.5      |                | μΑ       | $V_{INH} = 1.8 \text{ V}, V_{INL} = GND, V_{DD} = 3 \text{ V}$                     |

<sup>&</sup>lt;sup>1</sup>Bバージョンの温度範囲は-30°C~+85°C。

$<sup>^2</sup>$ 用語のセクション参照。

$<sup>^3</sup>$  直線性はコード範囲を縮小してテスト(コード 32~1023)。

<sup>4</sup>ゼロに近い出力電流を実現するときは、パワーダウン機能を使ってください。

<sup>&</sup>lt;sup>5</sup> デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。XSHUTDOWN はアクティブ・ローです。SDA と SCL のプルアップ抵抗は 1.8 V に接続されています。

<sup>&</sup>lt;sup>6</sup> SCL と SDA の入力フィルタリングにより、ノイズ・スパイクを 50 ns 以下に抑圧。

$<sup>^7</sup>$  XSHUTDOWN はアクティブ・ローです。

## AC 仕様

特に指定がない限り、 $V_{DD}$  = 2.7 V ~ 5.5 V、AGND = DGND = 0 V、 $R_L$  = 25  $\Omega$  ( $V_{DD}$  ~ 接続)。

### 表 2.

|                                     | B Version <sup>1, 2</sup> |      |     |        |                                                                                                                                                             |  |  |  |  |  |

|-------------------------------------|---------------------------|------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Parameter Min                       |                           | Typ  | Max | Unit   | Test Conditions/Comments                                                                                                                                    |  |  |  |  |  |

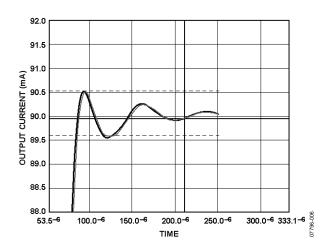

| Output Current Settling Time        |                           | 250  |     | μs     | $V_{DD} = 3.6 \text{ V}, R_L = 25 \Omega, L_L = 680 \mu\text{H}, \frac{1}{4} \text{ scale to } \frac{3}{4} \text{ scale change } (0x100 \text{ to } 0x300)$ |  |  |  |  |  |

| Slew Rate                           |                           | 0.3  |     | mA/μs  |                                                                                                                                                             |  |  |  |  |  |

| Major Code Change Glitch<br>Impulse |                           | 0.15 |     | nA-sec | 1 LSB change around major carry                                                                                                                             |  |  |  |  |  |

| Digital Feedthrough <sup>3</sup>    |                           | 0.06 |     | nA-sec |                                                                                                                                                             |  |  |  |  |  |

<sup>&</sup>lt;sup>1</sup>Bバージョンの温度範囲は-40℃~+85℃。

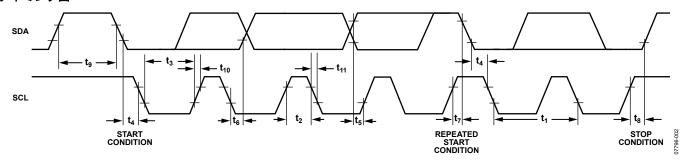

## タイミング仕様

$V_{DD}$  = 2.7 V  $\sim$  3.6 V。特に指定がない限り、すべての仕様は  $T_{MIN}$   $\sim$   $T_{MAX}$  で規定。

### 表 3.

|                        | B Version                                    |         |                                                                                 |

|------------------------|----------------------------------------------|---------|---------------------------------------------------------------------------------|

| Parameter <sup>1</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    | Description                                                                     |

| $f_{SCL}$              | 400                                          | kHz max | SCL clock frequency                                                             |

| $t_1$                  | 2.5                                          | μs min  | SCL cycle time                                                                  |

| $t_2$                  | 0.6                                          | μs min  | t <sub>HIGH</sub> , SCL high time                                               |

| $t_3$                  | 1.3                                          | μs min  | t <sub>LOW</sub> , SCL low time                                                 |

| $t_4$                  | 0.6                                          | μs min  | t <sub>HD, STA</sub> , start/repeated start condition hold time                 |

| $t_5$                  | 100                                          | ns min  | t <sub>SU, DAT</sub> , data setup time                                          |

| ${t_6}^2$              | 0.9                                          | μs max  | t <sub>HD, DAT</sub> , data hold time                                           |

|                        | 0                                            | μs min  |                                                                                 |

| $t_7$                  | 0.6                                          | μs min  | t <sub>SU, STA</sub> , setup time for repeated start                            |

| $t_8$                  | 0.6                                          | μs min  | t <sub>SU, STO</sub> , stop condition setup time                                |

| $t_9$                  | 1.3                                          | μs min  | t <sub>BUF</sub> , bus free time between a stop condition and a start condition |

| $t_{10}$               | 300                                          | ns max  | t <sub>R</sub> , rise time of both SCL and SDA when receiving                   |

|                        | 0                                            | ns min  | Can be CMOS driven                                                              |

| $t_{11}$               | 250                                          | ns max  | t <sub>F</sub> , fall time of SDA when receiving                                |

|                        | 300                                          | ns max  | t <sub>F</sub> , fall time of both SCL and SDA when transmitting                |

|                        | $20 + 0.1  C_B^{\ 3}$                        | ns min  |                                                                                 |

| $C_B$                  | 400                                          | pF max  | Capacitive load for each bus line                                               |

<sup>「</sup>デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

### タイミング図

図 2.2 線式シリアル・インターフェースのタイミング図

Rev. 0 — 4/15 —

$<sup>^2</sup>$ デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

<sup>3</sup> 用語のセクションを参照。

$<sup>^2</sup>$  SCL の立ち下がりエッジの不定領域を避けるため、マスター・デバイスは、SDA 信号に対して最小 300 ns のホールド・タイムを保証する必要があります (SCL 信号の  $V_{\text{INH MIN}}$  を基準として)。

$<sup>^3</sup>$   $C_B$  は 1 本のバス・ラインの合計容量(pF)です。 $t_R$  と  $t_F$  は、0.3  $V_{DD}$  と 0.7  $V_{DD}$  との間で測定。

# 絶対最大定格

特に指定のない限り、T<sub>A</sub>=25℃。

表 4.

| Parameter                                    | Rating                                     |

|----------------------------------------------|--------------------------------------------|

| V <sub>DD</sub> to AGND                      | -0.3 V to +5.5 V                           |

| $V_{DD}$ to DGND                             | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| AGND to DGND                                 | -0.3 V to +0.3 V                           |

| SCL, SDA to DGND                             | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| XSHUTDOWN to DGND                            | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| I <sub>SINK</sub> to AGND                    | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Operating Temperature Range                  |                                            |

| Industrial (B Version)                       | −30°C to +85°C                             |

| Storage Temperature Range                    | −65°C to +150°C                            |

| Junction Temperature (T <sub>J MAX</sub> )   | 150°C                                      |

| WLCSP Power Dissipation                      | $(T_{J MAX} - T_A)/\theta_{JA}$            |

| $\theta_{JA}$ Thermal Impedance <sup>1</sup> |                                            |

| Mounted on 4-Layer Board                     | 95°C/W                                     |

| Lead Temperature, Soldering                  |                                            |

| Maximum Peak Reflow Temperature <sup>2</sup> | 260°C (±5°C)                               |

$<sup>^1</sup>$  最適  $\theta_{JA}$ を実現するためには、AD5821A を 4 層ボードにハンダ付けすることが推奨されます。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒 久的な損傷を与えることがあります。この規定はストレス定格 の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものでは ありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### ESD の注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. 0 - 5/15 -

$<sup>^2</sup>$  JEDEC J-STD-020C に準拠。

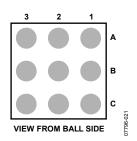

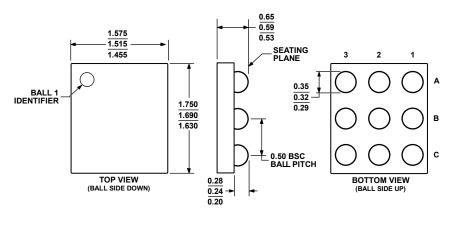

# ピン配置およびピン機能説明

図 3.ピン配置

### 表 5.ピン機能の説明

| ピン番号 | 記号                | 説明                           |

|------|-------------------|------------------------------|

| A1   | I <sub>SINK</sub> | 出力電流シンク。                     |

| A2   | NC                | 未接続。                         |

| A3   | XSHUTDOWN         | パワーダウン。非同期パワーダウン信号、アクティブ・ロー。 |

| B1   | AGND              | アナログ・グラウンド・ピン。               |

| B2   | DGND              | デジタル・グラウンド・ピン。               |

| В3   | SDA               | I <sup>2</sup> Cインターフェース信号。  |

| C1   | DGND              | デジタル・グラウンド・ピン。               |

| C2   | $V_{DD}$          | デジタル電源電圧。                    |

| C3   | SCL               | I <sup>2</sup> Cインターフェース信号。  |

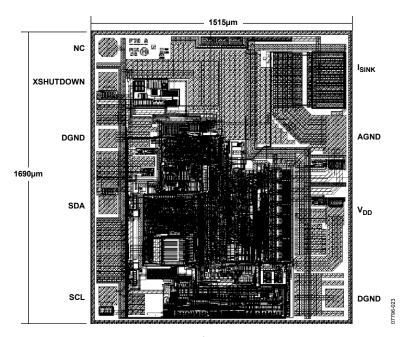

図 4.パターン図 寸法表示: ミクロン(µm)

Rev. 0 — 6/15 —

# 代表的な性能特性

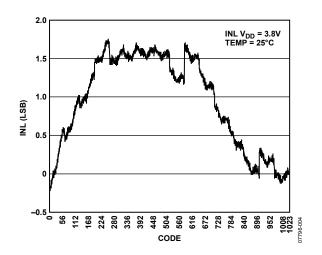

図 5. INL (typ)対コードのプロット

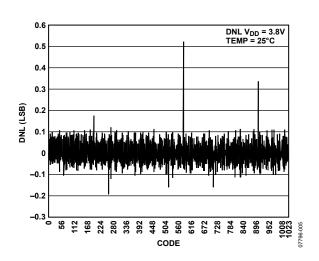

図 6.DNL (typ)対コードのプロット

図 7. $\frac{1}{2}$ から $\frac{3}{2}$ スケールへのセトリング・タイム( $V_{DD}$  = 3.6 V)

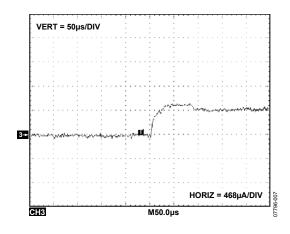

図 8. 4LSB ステップに対するセトリング・タイム( $V_{DD}$  = 3.6 V)

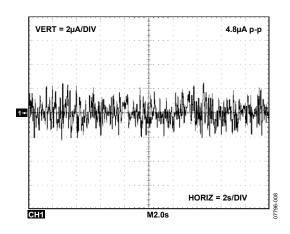

図 9.0.1 Hz~10 Hz のノイズ・プロット(V<sub>DD</sub> = 3.6 V)

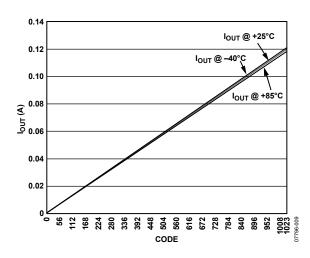

図 10.シンク電流対コード対温度(V<sub>DD</sub> = 3.6 V)

Rev. 0 - 7/15 -

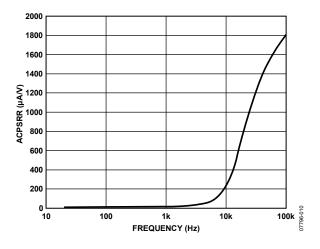

図 11.AC 電源除去比(V<sub>DD</sub> = 3.6 V)

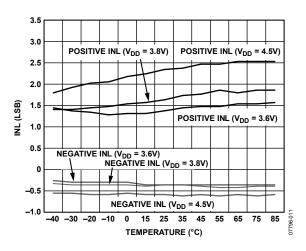

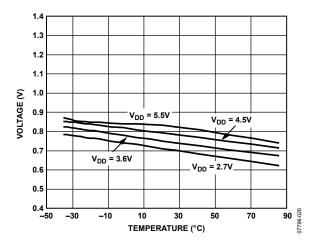

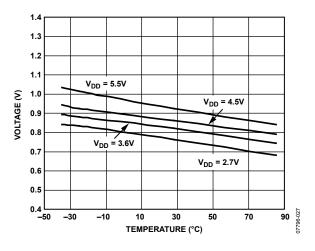

図 12.INL 対温度対電源電圧

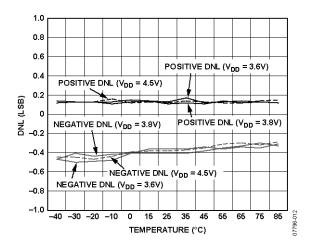

図 13.DNL 対温度対電源電圧

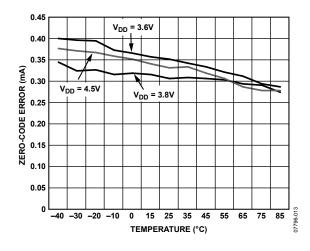

図 14.ゼロ・コード誤差対温度対電源電圧

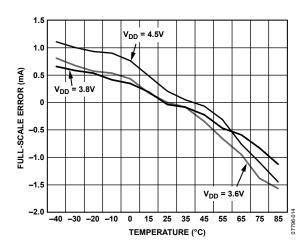

図 15.フル・スケール誤差対温度対電源電圧

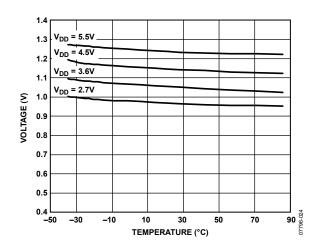

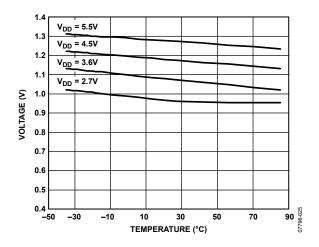

図 16.SCL および SDA のロジック・ハイ・レベル $(V_{INH})$ 対温度および電源電圧

Rev. 0 — 8/15 —

# AD5821A

図 17.SCL および SDA のロジック・ロー・レベル( $V_{INL}$ )対温度および電源電圧

図 18.XSHUTDOWN のロジック・ハイ・レベル(V<sub>INH</sub>)対温度および 電源電圧

図 19.DNL 対 XSHUTDOWN のロジック・ロー・レベル(V<sub>INL</sub>)対温度 および電源電圧

Rev. 0 — 9/15 —

## 用語

#### 相対精度

DAC の場合、相対精度すなわち積分非直線性(INL)は、DAC 伝達関数の上下両端を結ぶ直線からの最大乖離(LSB 数で表示)を表します。INL(typ)対コードのプロットを図 5 に示します。

### 微分非直線性(DNL)

微分非直線性(DNL)は、隣接する2つのコードの間における測定された変化と理論的な1LSB変化との差をいいます。最大1LSBの微分非直線性の仕様は、単調性を保証するものです。このDACはデザインにより単調性を保証しています。DNL(typ)対コードのプロットを図6に示します。

### ゼロ・コード誤差

ゼロ・コード誤差は、ゼロ・コード(0x0000)を DAC レジスタに ロードしたときの出力として測定されます。理論的には出力は 0 mA です。 AD5821A では DAC 出力が 0 mA を下回ることができないため、ゼロ・コード誤差は常に正です。これは、DAC と 出力アンプのオフセット誤差の組み合わせによりゼロ・コード 誤差が発生するためです。ゼロ・コード誤差は mA で表します。

### ゲイン誤差

ゲイン誤差は、DAC 振幅誤差の測定値です。理論値からの実際の DAC 伝達特性の傾きの差をフル・スケール範囲のパーセント値で表したものです。

#### ゲイン誤差ドリフト

ゲイン誤差ドリフトは、温度変化によるゲイン誤差の変化を表し、LSB/°Cで表されます。

#### デジタルからアナログへのグリッチ・インパルス

これは、DAC レジスタ内のコード状態が変化したときに、アナログ出力に混入されるインパルスを意味します。通常、nA-secで表すグリッチの面積として規定され、主要キャリ変化時に、デジタル・コードが 1 LSB だけ変化したときに測定されます。

#### デジタル・フィードスルー

デジタル・フイードスルーは、DAC 出力の更新が行われていないときに、DAC のデジタル入力から DAC のアナログ出力に注入されるインパルスを表します。nA-sec で規定され、データ・バス上でのフル・スケール変化時、すなわち全ビット 0 から全ビット 1 への変化、またはその逆の変化のときに測定されます。

#### オフセット誤差

オフセット誤差は、伝達関数の直線領域での  $I_{SINK}$ (実測値)と  $I_{OUT}$ (理論値)の差を表し、mA で表示されます。オフセット誤差は、AD5821A の DAC レジスタにコード 16 をロードして測定されています。

### オフセット誤差ドリフト

オフセット誤差ドリフトは、温度変化によるオフセット誤差の変化を表し、μV/°Cで表されます。

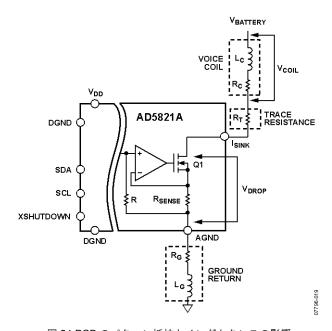

## 動作原理

AD5821A は、120 mA の出力電流シンク能力を持つ 10 ビット DAC です。このデバイスは、レンズのオートフォーカス、手振れ補正、光ズームのようなアプリケーションでボイス・コイル・アクチュエータを駆動することを目的としています。 回路 図を図 20 に示します。 10 ビットの電流出力 DAC と抵抗 R の組み合わせにより、オペアンプの非反転入力を駆動する電圧を発生します。また、この電圧は  $R_{\rm SENSE}$  抵抗の両端にも現れて、ボイス・コイルの駆動に必要なシンク電流も発生します。

抵抗 R と抵抗  $R_{SENSE}$  は、インターリーブされているため互いに一致しています。このため、温度係数と非直線性は全温度で一致し、温度に対する出力ドリフトは最小になっています。ダイオード D1 は出力保護ダイオードです。

図 20.ボイス・コイルへの接続を示すブロック図

### シリアル・インターフェース

AD5821A は、業界標準の  $I^2C$  2 線式シリアル・プロトコルを使って制御されます。DAC に対するデータの読み書きは、最大 400 kHz のデータ・レートで行うことができます。読み出し動作の後、入力レジスタ値は全ビット 0 にリセットされます。

### I<sup>2</sup>C バスの動作

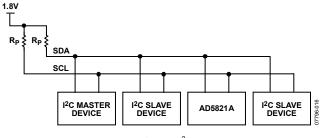

$\Gamma^2$ C バスは、シリアル・クロック(SCL)を発生する 1 個以上のマスター・デバイスと接続して動作し、AD5821A のようなスレーブ・デバイスに対して、シリアル・データ・ライン(SDA)を使ってデータを読み書きします。 $\Gamma^2$ C バス上のすべてのデバイスでは、SDA ピンを SDA ラインに、SCL ピンをマスター・デバイスの SCL ラインに、それぞれ接続します。 $\Gamma^2$ C デバイスではバス・ラインをロー・レベルすることだけが可能です。ハイ・レベルはプルアップ抵抗  $\Gamma^2$ R によるプルアップで実現されます。 $\Gamma^2$ R の値は、データ・レート、バス容量、 $\Gamma^2$ C デバイスがシンクできる最大負荷電流(標準デバイスでは 3 mA)に依存します。

図 21.一般的な I<sup>2</sup>C バス

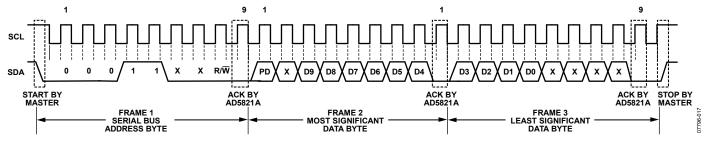

バスがアイドル状態のとき、SCL と SDA はハイ・レベルです。マスターはスタート条件を設定してデータ転送を開始します。このスタート条件は、SCL がハイ・レベルの間の、SDA 上のハイ・レベルからロー・レベルへの変化として定義されています。バスに接続されているすべてのスレーブ・デバイスはスタート条件に応答して、シリアル・クロックを使って次の 8 ビットのデータをシフト入力します。

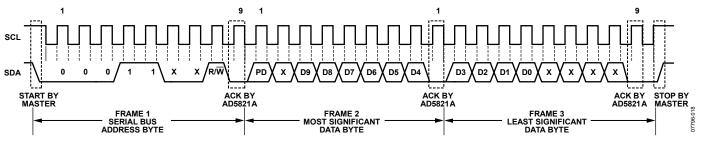

これら $\underline{0}$ 8 データ・ビットは、7 ビットのアドレスとリード/ライト(R/W)ビットから構成されています。R/Wビットは、デバイスへのデータの書き込みでは 0 に、デバイスからのデータの読み出しでは 1 に、それぞれ設定されます。 $I^2C$  バス上の各スレーブ・デバイスは、独自のアドレスを使って識別されます。AD5821A のアドレスは 0001100 ですが、最後の 2 ビットが未使用/don't care であるため、0001101、0001110、0001111 もデバイスのアドレスに使うことができます(図 22 と図 23 参照)。アドレスと R/Wビットの組み合わせとデータは常に 8 ビット長であるため、AD5821A の書き込みアドレスは 00011000 (0x18)、読み出しアドレスは 00011001 (0x19)になります(図 22 と図 23 参照)。

アドレス・データの終わりに(R/Wビットの後ろ)、自分のアドレスを検出したスレーブ・デバイスは、アクノリッジ(ACK)条件を発生して応答します。この ACK は、SCLのロー・レベル中に9番目のクロック・パルスの前にスレーブ・デバイスが SDA をロー・レベルにし、9番目のクロック・パルス中そのロー・レベルを維持することとして定義されます。マスター・デバイスはACKを受信すると、書き込み動作ではクロックを出力してデータを AD5821A に書き込むことができ、読み出し動作ではクロックを出力してデータを協力してデータを読み出すことができます。データ・フォーマットのセクションで説明するように、データはクロックのロー・レベル区間中に(ハイ・レベル区間での SDA 変化はスタート条件の定義に使用しているため)、またはストップ条件時に変化する必要があります。

I<sup>2</sup>C データは 8 ビットのブロックに分割されるため、スレーブは各ブロックの終わりで ACK を発生します。AD5821A は 10 ビットのデータを必要とするため、書き込み動作では 2 データ・ワードを書き込み、読み出し動作では 2 データ・ワードを読み出す必要があります。読み出し動作または書き込み動作の終わりに、AD5821A は 2番目のデータ・バイトをアクノリッジします。マスターはストップ条件を発生します。ストップ条件は、SCLのハイ・レベル中の、SDAのロー・レベルからハイ・レベルへの変化として定義され、トランザクションを終了させます。

### データ・フォーマット

データは上位バイト先頭(MSBファースト)で AD5821A に書き込まれ、16 ビット入力レジスタにシフト入力されます。 すべての データがシフト入力されると、データは入力レジスタから DAC レジスタへ転送されます。

DAC は 10 ビットのデータだけを必要とするため、入力レジスタ・データのすべてのビットを使いません。MSB は、アクティブ・ハイのソフトウェア制御パワーダウン機能として予約されています。

データ・フォーマットを表 6に示します。この表では、ビット 14 が未使用、ビット 13~ビット 4 は DAC データ・ビット(D9~D0)に対応、ビット 3~ビット 0 は未使用であることに注意してください。

読み出し動作では、データは同じビット順で読み出されます。

図 22.書き込み動作

図 23.読み出し動作

表 6.データ・フォーマット

| Serial Data-        | High Byte              |        |        |        |        |        |       |       | Low Byte |       |       |       |       |       |       |       |

|---------------------|------------------------|--------|--------|--------|--------|--------|-------|-------|----------|-------|-------|-------|-------|-------|-------|-------|

| Words               | Bit 15                 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Serial Data<br>Bits | SD7                    | SD6    | SD5    | SD4    | SD3    | SD2    | SD1   | SD0   | SD7      | SD6   | SD5   | SD4   | SD3   | SD2   | SD1   | SD0   |

| Input Register      | R15                    | R14    | R13    | R12    | R11    | R10    | R9    | R8    | R7       | R6    | R5    | R4    | R3    | R2    | R1    | R0    |

| Function            | XSHUTDOWN <sup>1</sup> | X      | D9     | D8     | D7     | D6     | D5    | D4    | D3       | D2    | D1    | D0    | X     | X     | X     | X     |

<sup>&</sup>lt;sup>1</sup> XSHUTDOWN =ソフト・パワーダウン、X =未使用/don't care、D9~D0 = DAC データ。

### 電源のバイパスとグラウンド接続

高精度が重要な回路では、PCB上の電源とグラウンド・リターンのレイアウトを注意深く行うことが役立ちます。AD5821Aを実装する PCBは、アナログ部とデジタル部を分離する必要があります。AGNDと DGNDが共用される場合には、グラウンドの接続はAD5821Aにできるだけ近い1ヵ所で行う必要があります。

AGNDのリターン・パスのレイアウトには特に注意し、これをボイス・コイル・モーターと $I_{SINK}$ との間に配置して、直列抵抗を小さくする必要があります。図24に、AD5821Aの出力電流シンクを示し、AGNDの実効直列インピーダンスおよびモーターと $I_{SINK}$ との間のパターン抵抗を小さくすることの重要性を示します。ボイス・コイルは、インダクタ $I_{CC}$ と抵抗 $I_{CC}$ を使ってモデル化してあります。ボイス・コイルを流れる電流は実質的にDC電流であり、AD5821Aが電流をシンクするとき電圧降下 $I_{COII}$ を発生させます。直列インダクタンスの影響は小さくなっています。

図 24.PCB のパターン抵抗とインダクタンスの影響

120 mAの最大電流をシンクするとき、 $R_{SENSE}$ に許容できる最大電圧降下は400 mVであり、Q1のドレイン—ソース間最小電圧は200 mVです。これは、AD5821A出力が600 mVのコンプライアンス電圧を持つことを意味します。 $V_{DROP}$ が600 mVを下回ると、出力トランジスタQ1は正常に動作できなくなるため、 $I_{SINK}$ を一定に維持できなくなります。

90 mA の電流をシンクするとき、 $R_{SENSE}$  に許容できる最大電圧降下は 300 mV であり、Q1 のドレイン—ソース間最小電圧は 180 mV です。これは、AD5821A 出力が 480 mV のコンプライアンス電圧を持つことを意味します。 $V_{DROP}$  が 480 mV を下回ると、出力トランジスタ Q1 は正常に動作できなくなるため、 $I_{SINK}$  を一定に維持できなくなります。 $I_{SINK}$  が減少すると、トランジスタ Q1 に加わる電圧も減少するため、ボイス・コイル・モーターに使用できる電源も低くなります。

ボイス・コイルを流れる電流が 120~mA に増加すると、 $V_{COIL}$  が増加します。 $V_{DROP}$  が減少して、最後に 600~mV ( $I_{SINK}=90~mA$  の場合は 480~mV)の最小規定コンプライアンス電圧に到達します。グラウンド・リターン・パスは、 $R_G$  と  $L_G$  でモデル化します。ボイス・コイルと AD5821A との間のパターン抵抗は、 $R_T$  でモデル化します。 $L_G$  の誘導性効果は  $R_{SENSE}$  と  $R_C$  に等しく影響を与え、電流が一定に維持されるため、グラウンド・リターン・パスの純抵抗成分ほど重要ではありません。最大シンク電流がモーターに流れると、抵抗成分  $R_T$  と  $R_G$  が Q1 の電圧ヘッドルームに影響を与えます。このため、電圧コンプライアンスの理由で、 $R_C$  の最大値が制限されることがあります。

たとえば、

$V_{BAT} = 3.6 \text{ V}$

$R_G = 0.5 \Omega$

$R_T = 0.5 \Omega$

$I_{SINK} = 120 \text{ mA}$

$V_{DROP}$  = 600 mV (コンプライアンス電圧)

の場合、ボイス・コイルの最大抵抗値Rcは、

$$R_C = \frac{V_{BAT} - [V_{DROP} + (I_{SINK} \times R_T) + (I_{SINK} \times R_G)]}{I_{SINK}} =$$

$$\frac{3.6 \text{ V} - [600 \text{ mV} + 2 \times (120 \text{ mA} \times 0.5 \Omega)]}{120 \text{ mA}} = 24 \Omega$$

もう1つ別の例をあげると、

$V_{BAT} = 3.6 \text{ V}$

$R_G = 0.5 \Omega$

$R_T = 0.5 \Omega$

$I_{SINK} = 90 \text{ mA}$

$V_{DROP}$  = 480 mV (90 mA でのコンプライアンス電圧仕様)

の場合、ボイス・コイルの最大抵抗値 $R_C$ は、

$$R_C = \frac{V_{BAT} - [V_{DROP} + (I_{SINK} \times R_T) + (I_{SINK} \times R_G)]}{I_{SINK}} =$$

$$\frac{3.6 \text{ V} - [480 \text{ mV} + 2 \times (90 \text{ mA} \times 0.5 \Omega)]}{90 \text{ mA}} = 33.66 \Omega$$

この理由のため、AD5821Aとモーターとの間のグラウンド・リターン・パスと相互接続の直列インピーダンスを小さくすることが重要です。また、 $I_{SINK}$ が小さくなるほど、出力ステージのコンプライアンス電圧も小さくなることに注意することも重要です。この減少により、高抵抗値を持つボイス・コイル・モーターを使うか、あるいはボイス・コイル・モーターの電源電圧を小さくすることが必要になります。 $I_{SINK}$ 電流が減少すると、コンプライアンス電圧が減少します。

AD5821A の電源、または AD5821A の電源として使うレギュレータはデカップリングする必要があります。電源を  $10~\mu F$  のコンデンサでデカップリングすることが推奨されます。この  $10~\mu F$  コンデンサをタンタル・ビーズ・タイプと理想的ですが、電源またはレギュレータ電源のレギュレーションが優れている場合には、このようなデカップリングが不要であることもあります。AD5821A は局所的に  $0.1~\mu F$  のセラミック・コンデンサでデカップリングし、この  $0.1~\mu F$  のコンデンサはできるだけ  $V_{DD}$  ピンの近くに配置する必要があります。 $0.1~\mu F$  のコンデンサは、実効直列抵抗と実効直列インダクタンスが小さいセラミックである必要があります。 $0.1~\mu F$  のコンデンサは、大きな過渡電流に対してグラウンドへの低インピーダンス・パスを提供します。

電源ラインはできるだけ太いパターンにしてインピーダンスを小さくし、電源ライン上のグリッチによる影響を軽減させるようにします。クロックとその他の高速スイッチング・デジタル信号は、デジタル・グラウンドを使ってボード上の他の部分からシールドする必要があります。デジタル信号とアナログ信号の交差は、できるだけ回避する必要があります。ボードの反対側のパターンは、互いに右角度となるように配置してボードを通過するフィードスルー効果を減少させます。最適なボード・レイアウト技術は、ボードの部品側をグラウンド・プレーン専用として使い、信号パターンはハンダ面に配置するマイクロストリップ技術ですが、2層ボードでは常に可能とは限りません。

# アプリケーション情報

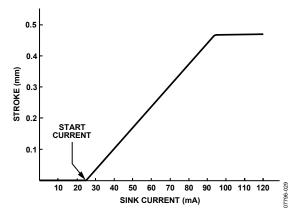

AD5821A は、レンズ・オートフォーカス、手振れ補正、または 光ズームのようなアプリケーションで使用されるスプリング付きまたはスプリングのないリニア・モーターを駆動するために デザインされています。スプリング付きモーターの動作原理は、ボイス・コイルとスプリングのバランスによりレンズ位置が制御 されることです。図 25 に、オートフォーカス用の代表的なスプリング付きリニア・モーターの伝達カーブを示します。この伝達関数の要点は変位すなわちストロークであり、実際のレンズ 移動距離を mm で表したもので、モーターを流れる電流は mA で表します。

スタート電流はスプリング付きリニア・モーターに固有であり、レンズが移動したとき超える必要のあるスレッショールド電流になります。スタート電流は通常20~mA以上であり、定格ストロークすなわち変位は通常 $0.25~mm\sim0.4~mm$ で、伝達カーブの傾きは約 $10~\mu m/mA$ 以下です。

AD5821A は最大 120 mA をシンクするようにデザインされており、市販のリニア・モーターまたはボイス・コイルには十分な能力です。これらのアプリケーションに対して AD5821A を最適なソリューションにしているもう 1 つの要因は、デバイスの単調性であり、与えられたデジタル・ワードに対してレンズ位置の再現性が保証されることです。

図 26 に、AD5821A の一般的なアプリケーション回路を示します。

図 25.スプリング付きボイス・コイルのストローク対シンク電流

図 26.代表的なアプリケーション回路

091306-B

# 外形寸法

図 27.9 ボール・ウェハー・レベル・チップ・スケール・パッケージ[WLCSP] (CB-9-1) 寸法: mm

## オーダー・ガイド

| Model                          | Temperature Range | Package Description                           | Package Option | Branding |

|--------------------------------|-------------------|-----------------------------------------------|----------------|----------|

| AD5821ABCBZ-REEL7 <sup>1</sup> | −30°C to +85°C    | 9-Ball Wafer Level Chip Scale Package (WLCSP) | CB-9-1         | 1X       |

| AD5821ABCBZ-REEL <sup>1</sup>  | −30°C to +85°C    | 9-Ball Wafer Level Chip Scale Package (WLCSP) | CB-9-1         | 1X       |

| AD5821A-WAFER                  | −40°C to +85°C    | Bare Die Wafer                                |                |          |

| AD5821AD-WAFER                 | −40°C to +85°C    | Bare Die Wafer on Film                        |                |          |

| EVAL-AD5821AEBZ <sup>1</sup>   |                   | Evaluation Board                              |                |          |

$<sup>^{1}</sup>$  Z = RoHS 準拠製品

ライセンスを受けたアナログ・テバイセズまたはサブライセンスを受けた関連会社の 1 つから  $I^2C$  部品を購入すると、Phillips 社の制定する  $I^2C$  標準仕様にシステムが準拠している場合、 $I^2C$  システム内でこれらのテバイスを使うための Phillips 社の  $I^2C$  特許権のもとにライセンスが購入者に移転されます。