## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2015年5月26日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2015年5月26日

製品名：AD5761/AD5721

対象となるデータシートのリビジョン(Rev)：Rev.0

・訂正箇所①：P.1 左の段 特長欄 上から5行目

誤：「16ビット精度：±2LSB（最大）」

正：「16ビット分解能：INL誤差±2LSB（最大）」

・訂正箇所②：P.1 右の段 「概要」の項 8行目

誤：「・・・7.5μsのセトリング・タイムを保証します。」

正：「・・・7.5μsのセトリング・タイムを規定します。」

・訂正箇所③：P.1 右の段 概要欄 上から2行目以降

誤：「この高精度 16/12 ビット DAC に必要な外付け部品は、電源ピンのデカップリング・コンデンサと電源電圧だけです。」

正：「この高精度 16/12 ビット DAC に必要な外付け部品は、電源ピンのデカップリング・コンデンサと電源電圧、基準電圧源（リファレンス）です。」

・訂正箇所④：P.30 左の段 上から5行目

誤：「AD5761/AD5721 はリファレンス電圧とリファレンス・バッファを内蔵しているため、外付けバイポーラ・リファレンスとそれに対応するバッファが不要になり、コストとボーダー・スペースの削減が可能です。」

正：上記の文を削除

・訂正箇所⑤：P.30 左の段 「高精度リファレンス電圧の選択」の項 最初の文

誤：「フル動作温度範囲で AD5761/AD5721 の最適性能を実現するためには、外付けリファレンスの使用を必要とするアプリケーションがあります。」

正：「フル動作温度範囲で AD5761/AD5721 の最適性能を実現するためには、外付けリファレンスの選択に注意する必要があります。」

・訂正箇所：P.30 右の段 「電源の注意事項」の項 最初の文

誤：「・・・V<sub>DD</sub> = 11 V、V<sub>SS</sub> = -21 V、DV<sub>CC</sub> = 5 V・・・」

正：「・・・V<sub>DD</sub> = 21 V、V<sub>SS</sub> = -11 V、DV<sub>CC</sub> = 5 V・・・」

アナログ・デバイセズ株式会社

本社／〒105-6891 東京都港区海岸1-16-1

ニューピア竹芝サウスタワーB

電話 03 (5402) 8200

大阪営業所／〒532-0003 大阪府大阪市淀川区富原3-5-36

新大阪トラストタワー

電話 06 (6350) 6868

# 複数レンジ、16/12ビット バイポーラ／ユニポーラ、電圧出力DAC

## データシート

## AD5761/AD5721

### 特長

ソフトウェアから設定可能な8種類の出力レンジ: 0 V~5 V、0 V~

~10 V、0 V~16 V、0 V~20 V、±3 V、±5 V、±10 V、-2.5

V~+7.5 V; 5% オーバーレンジ

総合未調整誤差(TUE): 0.1% FSR (最大)

16ビット精度: ±2 LSB (最大)

単調性保証: DNL 誤差 ±1 LSB (最大)

1チャンネルの16/12ビットDAC

セトリング・タイム: 7.5 μs (typ)

リファレンス・バッファを内蔵

低ノイズ: 35 nV/√Hz

低グリッチ: 1 nV-sec

1.8 V ロジックと互換

LDACによる非同期更新

ゼロスケール／ミッドスケールへの非同期RESET

DSP/マイクロコントローラ互換のシリアル・インターフェース

4 kV の強固なHBM ESD 定格

動作温度範囲: -40°C~+125°C

### アプリケーション

工業用オートメーション

計装/データ・アクイジション機器

オープン/クローズド・ループ・サーボ制御、プロセス制御

プログラマブルなロジック・コントローラ

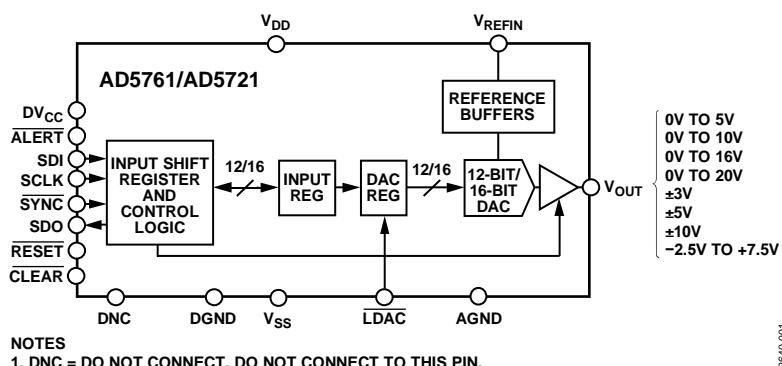

### 概要

AD5761/AD5721 は、1 チャンネル、16/12 ビット・シリアル入力、電圧出力 D/A コンバータ (DAC) で、4.75 V~30 V の単電源または  $V_{SS} = -16.5 \text{ V} \sim 0 \text{ V}$  および  $V_{DD} = 4.75 \text{ V} \sim 16.5 \text{ V}$  の両電源で動作します。出力アンプとリファレンス・バッファを内蔵しているため、非常に使い易い汎用ソリューションを提供します。

単調性、最大 ±2 LSB の積分非直線性(INL)を保証し、35 nV/√Hz のノイズ、いくつかの例外のレンジを除いて 7.5 μs のセトリング・タイムを保証しています。

AD5761/AD5721 は、最大 50 MHz のクロック・レートで動作し、DSP およびマイクロコントローラ・インターフェース規格と互換性を持つシリアル・インターフェースを採用しています。ダブル・バッファリングを採用しているため、DAC 出力の非同期更新が可能です。入力コードのフォーマットとしては、2 の補数またはストレート・バイナリを選択することができます。非同期リセット機能は、すべてのレジスタをデフォルト状態へリセットします。出力レンジは、コントロール・レジスタの RA[2:0] ビットで選択することができます。

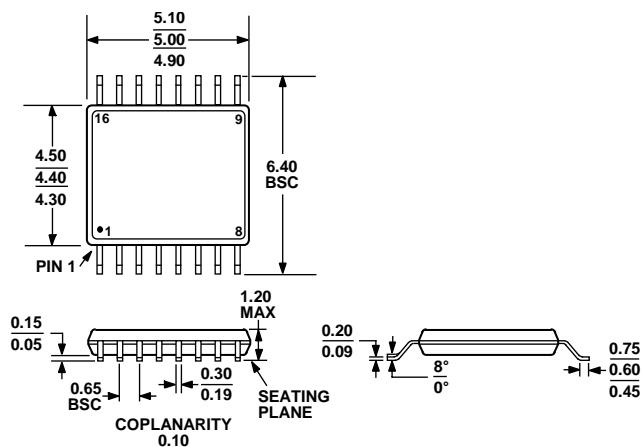

これらのデバイスは 16 ピン TSSOP パッケージを採用し、-40°C~+125°C の工業温度範囲で仕様を保証します。

表 1. ピン互換デバイス

| Device          | Description                           |

|-----------------|---------------------------------------|

| AD5761R/AD5721R | AD5761/AD5721 with internal reference |

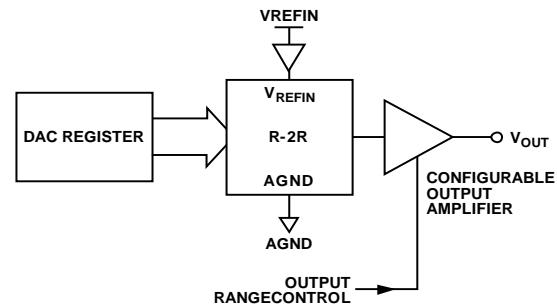

### 機能ブロック図

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                  |    |                      |    |

|------------------|----|----------------------|----|

| 特長               | 1  | レジスタの詳細              | 25 |

| アプリケーション         | 1  | 入力シフトレジスタ            | 25 |

| 概要               | 1  | コントロール・レジスタ          | 25 |

| 機能ブロック図          | 1  | コントロール・レジスタのリードバック   | 27 |

| 改訂履歴             | 2  | 入力レジスタから DAC レジスタを更新 | 27 |

| 仕様               | 3  | DAC レジスタのリードバック      | 27 |

| AC 性能特性          | 5  | DAC レジスタの書き込みと更新     | 28 |

| タイミング特性          | 6  | 入力レジスタのリードバック        | 28 |

| 絶対最大定格           | 8  | ディスエーブル・ディジーチェーン機能   | 28 |

| ESD の注意          | 8  | ソフトウェア・データ・リセット      | 29 |

| ピン配置およびピン機能説明    | 9  | ソフトウェア・フル・リセット       | 29 |

| 代表的な性能特性         | 10 | NOP レジスタ             | 29 |

| 用語               | 20 | アプリケーション情報           | 30 |

| 動作原理             | 22 | 代表的な動作回路             | 30 |

| D/A コンバータ        | 22 | 電源の注意事項              | 30 |

| 伝達関数             | 22 | 評価用ボード               | 30 |

| DAC アーキテクチャ      | 22 | 外形寸法                 | 32 |

| シリアル・インターフェース    | 23 | オーダー・ガイド             | 32 |

| ハードウェア・コントロール・ピン | 23 |                      |    |

## 改訂履歴

1/15—Revision 0: Initial Version

## 仕様

特に指定がない限り、 $V_{DD}^1 = 4.75\text{ V} \sim 30\text{ V}$ 、 $V_{SS}^1 = -16.5\text{ V} \sim 0\text{ V}$ 、 $AGND = DGND = 0\text{ V}$ 、 $V_{REFIN} = 2.5\text{ V}$  外付け、 $DV_{CC} = 1.7\text{ V} \sim 5.5\text{ V}$ 、 $0\text{ V} \sim 16\text{ V}$  および  $0\text{ V} \sim 20\text{ V}$  レンジでは  $R_{LOAD} = 2\text{ k}\Omega$ ；その他のすべてのレンジで  $R_{LOAD} = 1\text{ k}\Omega$ 、 $C_{LOAD} = 200\text{ pF}$ 、すべての仕様は  $T_{MIN} \sim T_{MAX}$  で規定。

表 2.

| Parameter <sup>2</sup>                               | Min        | Typ       | Max        | Unit                         | Test Conditions/Comments                                                                     |

|------------------------------------------------------|------------|-----------|------------|------------------------------|----------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE                                   |            |           |            |                              |                                                                                              |

| Programmable Output Ranges                           | 0          | 5         |            | V                            | External reference <sup>3</sup> , outputs unloaded                                           |

|                                                      | 0          | 10        |            | V                            |                                                                                              |

|                                                      | 0          | 16        |            | V                            |                                                                                              |

|                                                      | 0          | 20        |            | V                            |                                                                                              |

|                                                      | -2.5       | +7.5      |            | V                            |                                                                                              |

|                                                      | -3         | +3        |            | V                            |                                                                                              |

|                                                      | -5         | +5        |            | V                            |                                                                                              |

|                                                      | -10        | +10       |            | V                            |                                                                                              |

| AD5761                                               |            |           |            |                              |                                                                                              |

| Resolution                                           | 16         |           |            | Bits                         |                                                                                              |

| Relative Accuracy, INL                               |            |           |            |                              |                                                                                              |

| B Grade <sup>4</sup>                                 | -2         | +2        |            | LSB                          | All ranges except 0 V to 16 V and 0 V to 20 V, $V_{REFIN} = 2.5\text{ V}$ external reference |

| Differential Nonlinearity, DNL                       | -1         | +1        |            | LSB                          |                                                                                              |

| AD5721                                               |            |           |            |                              |                                                                                              |

| Resolution                                           | 12         |           |            | Bits                         |                                                                                              |

| Relative Accuracy, INL                               |            |           |            |                              |                                                                                              |

| B Grade                                              | -0.5       | +0.5      |            | LSB                          | External reference <sup>3</sup>                                                              |

| Differential Nonlinearity, DNL                       | -0.5       | +0.5      |            | LSB                          |                                                                                              |

| Zero-Scale Error                                     | -6         | +6        |            | mV                           | All ranges except $\pm 10\text{ V}$ and 0 V to 20 V, external reference <sup>3</sup>         |

|                                                      | -10        | +10       |            | mV                           | 0 V to 20 V, $\pm 10\text{ V}$ ranges, external reference <sup>3</sup>                       |

| Zero-Scale Temperature Coefficient (TC) <sup>5</sup> |            | $\pm 5$   |            | $\mu\text{V}/^\circ\text{C}$ | Unipolar ranges, external reference <sup>3</sup>                                             |

|                                                      |            | $\pm 15$  |            | $\mu\text{V}/^\circ\text{C}$ | Bipolar ranges, external reference <sup>3</sup>                                              |

| Bipolar Zero Error                                   | -5         | +5        |            | mV                           | All bipolar ranges except $\pm 10\text{ V}$                                                  |

|                                                      | -7         | +7        |            | mV                           | $\pm 10\text{ V}$ output range                                                               |

| Bipolar Zero TC <sup>5</sup>                         |            | $\pm 2$   |            | $\mu\text{V}/^\circ\text{C}$ | $\pm 3\text{ V}$ range, external reference <sup>3</sup>                                      |

|                                                      |            | $\pm 5$   |            | $\mu\text{V}/^\circ\text{C}$ | All bipolar ranges except $\pm 3\text{ V}$ , external reference <sup>3</sup>                 |

| Offset Error                                         | -6         | +6        |            | mV                           | All ranges except $\pm 10\text{ V}$ and 0 V to 20 V, external reference <sup>3</sup>         |

|                                                      | -10        | +10       |            | mV                           | 0 V to 20 V, $\pm 10\text{ V}$ ranges; external reference <sup>3</sup>                       |

| Offset Error TC <sup>5</sup>                         |            | $\pm 5$   |            | $\mu\text{V}/^\circ\text{C}$ | Unipolar ranges, external reference <sup>3</sup>                                             |

|                                                      |            | $\pm 15$  |            | $\mu\text{V}/^\circ\text{C}$ | Bipolar ranges, external reference <sup>3</sup>                                              |

| Gain Error                                           | -0.1       | +0.1      |            | % FSR                        | External reference <sup>3</sup>                                                              |

| Gain Error TC <sup>5</sup>                           |            | $\pm 1.5$ |            | ppm FSR/°C                   | External reference <sup>3</sup>                                                              |

| Total Unadjusted Error (TUE)                         | -0.1       | +0.1      |            | % FSR                        | External reference <sup>3</sup>                                                              |

| REFERENCE INPUT <sup>5</sup>                         |            |           |            |                              |                                                                                              |

| Reference Input Voltage ( $V_{REF}$ )                |            | 2.5       |            | V                            | $\pm 1\%$ for specified performance                                                          |

| Input Current                                        | -2         | $\pm 0.5$ | +2         | $\mu\text{A}$                |                                                                                              |

| Reference Range                                      | 2          |           | 3          | V                            |                                                                                              |

| OUTPUT CHARACTERISTICS <sup>5</sup>                  |            |           |            |                              |                                                                                              |

| Output Voltage Range                                 | $-V_{OUT}$ |           | $+V_{OUT}$ |                              | Refer to Table 7 for the different output voltage ranges available                           |

|                                                      | -10        |           | +10        | V                            | $V_{DD}/V_{SS} = \pm 11\text{ V}$ , $\pm 10\text{ V}$ output range                           |

|                                                      | -10.5      |           | +10.5      | V                            | $V_{DD}/V_{SS} = \pm 11\text{ V}$ , $\pm 10\text{ V}$ output range with 5% overrange         |

| Capacitive Load Stability                            |            |           | 1          | nF                           |                                                                                              |

| Parameter <sup>2</sup>                                       | Min                  | Typ                  | Max | Unit                  | Test Conditions/Comments                                                                                                   |

|--------------------------------------------------------------|----------------------|----------------------|-----|-----------------------|----------------------------------------------------------------------------------------------------------------------------|

| Headroom                                                     |                      | 0.5                  | 1   | V                     | $R_{LOAD} = 1 \text{ k}\Omega$ for all ranges except 0 V to 16 V and 0 V to 20 V ranges ( $R_{LOAD} = 2 \text{ k}\Omega$ ) |

| Output Voltage TC                                            |                      | $\pm 3$              |     | ppm FSR/°C            | $\pm 10$ V range, external reference                                                                                       |

| Short-Circuit Current                                        |                      | 25                   |     | mA                    | Short on the $V_{OUT}$ pin                                                                                                 |

| Resistive Load                                               |                      |                      | 1   | $\text{k}\Omega$      | All ranges except 0 V to 16 V and 0 V to 20 V                                                                              |

|                                                              |                      |                      | 2   | $\text{k}\Omega$      | 0 V to 16 V, 0 V to 20 V ranges                                                                                            |

| Load Regulation                                              |                      | 0.3                  |     | $\text{mV}/\text{mA}$ | Outputs unloaded                                                                                                           |

| DC Output Impedance                                          |                      | 0.5                  |     | $\Omega$              | Outputs unloaded                                                                                                           |

| LOGIC INPUTS <sup>5</sup>                                    |                      |                      |     |                       | $DV_{CC} = 1.7$ V to 5.5 V, JEDEC compliant                                                                                |

| Input Voltage                                                |                      |                      |     |                       |                                                                                                                            |

| High, $V_{IH}$                                               | 0.7 $\times DV_{CC}$ |                      |     | V                     |                                                                                                                            |

| Low, $V_{IL}$                                                |                      | 0.3 $\times DV_{CC}$ |     | V                     |                                                                                                                            |

| Input Current                                                |                      |                      |     |                       |                                                                                                                            |

| Leakage Current                                              |                      |                      |     | $\mu\text{A}$         | SDI, SCLK, $\overline{\text{SYNC}}$                                                                                        |

|                                                              | -1                   | +1                   |     | $\mu\text{A}$         | $\overline{\text{LDAC}}, \overline{\text{CLEAR}}, \overline{\text{RESET}}$ pins held high                                  |

|                                                              | -1                   | +1                   |     | $\mu\text{A}$         | $\overline{\text{LDAC}}, \overline{\text{CLEAR}}, \overline{\text{RESET}}$ pins held low                                   |

| Pin Capacitance                                              |                      | 5                    |     | pF                    | Per pin, outputs unloaded                                                                                                  |

| LOGIC OUTPUTS (SDO, $\overline{\text{ALERT}}$ ) <sup>5</sup> |                      |                      |     |                       |                                                                                                                            |

| Output Voltage                                               |                      |                      |     |                       |                                                                                                                            |

| Low, $V_{OL}$                                                |                      | 0.4                  |     | V                     | $DV_{CC} = 1.7$ V to 5.5 V, sinking 200 $\mu\text{A}$                                                                      |

| High, $V_{OH}$                                               | $DV_{CC} - 0.5$      |                      |     | V                     | $DV_{CC} = 1.7$ V to 5.5 V, sourcing 200 $\mu\text{A}$                                                                     |

| High Impedance, SDO Pin                                      |                      |                      |     |                       |                                                                                                                            |

| Leakage Current                                              |                      |                      |     | $\mu\text{A}$         |                                                                                                                            |

| Pin Capacitance                                              |                      | 5                    |     | pF                    |                                                                                                                            |

| POWER REQUIREMENTS                                           |                      |                      |     |                       |                                                                                                                            |

| $V_{DD}$                                                     | 4.75                 | 30                   |     | V                     |                                                                                                                            |

| $V_{SS}$                                                     | -16.5                | 0                    |     | V                     |                                                                                                                            |

| $DV_{CC}$                                                    | 1.7                  | 5.5                  |     | V                     |                                                                                                                            |

| $I_{DD}$                                                     |                      | 5.1                  | 6.5 | mA                    | Outputs unloaded, external reference                                                                                       |

| $I_{SS}$                                                     |                      | 1                    | 3   | mA                    | Outputs unloaded                                                                                                           |

| $DI_{CC}$                                                    |                      | 0.005                | 1   | $\mu\text{A}$         | $V_{IH} = DV_{CC}, V_{IL} = DGND$                                                                                          |

| Power Dissipation                                            |                      | 67.1                 |     | mW                    | $\pm 11$ V operation, outputs unloaded                                                                                     |

| DC Power Supply Rejection Ratio (PSRR) <sup>5</sup>          |                      | 0.1                  |     | $\text{mV}/\text{V}$  | $V_{DD} \pm 10\%, V_{SS} = -15$ V                                                                                          |

| AC PSRR <sup>5</sup>                                         |                      | 0.1                  |     | $\text{mV}/\text{V}$  | $V_{SS} \pm 10\%, V_{DD} = +15$ V                                                                                          |

|                                                              | 80                   |                      |     | dB                    | $V_{DD} \pm 200$ mV, 50 Hz/60 Hz, $V_{SS} = -15$ V; external reference; $C_{LOAD}$ = unloaded                              |

|                                                              | 80                   |                      |     | dB                    | $V_{SS} \pm 200$ mV, 50 Hz/60 Hz, $V_{DD} = +15$ V; external reference; $C_{LOAD}$ = unloaded                              |

<sup>1</sup> 規定性能に対して、ヘッドルーム条件は 1 V。<sup>2</sup> 温度範囲は-40 °C～+125°C です。typ 値は+25°C の値です。<sup>3</sup> 外部リファレンスは、オーバーレンジありで 2 V～2.85 V を、オーバーレンジなしで 2 V～3 V を、それぞれ意味します。<sup>4</sup> 積分非直線性誤差は、 $V_{REFIN} = 2.5$  V の外付けリファレンスを使用し、0 V～16 V と 0 V～20 V のレンジに対して $\pm 4$  LSB (最小/最大)で規定し、オーバーレンジありで  $V_{REFIN} = 2$  V～2.85 V を使用し、およびオーバーレンジなしで 2 V～3 V を使用して全レンジに対して規定します。<sup>5</sup> デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

## AC 性能特性

特に指定がない限り、 $V_{DD}^1 = 4.75\text{ V} \sim 30\text{ V}$ 、 $V_{SS}^1 = -16.5\text{ V} \sim 0\text{ V}$ 、 $AGND = DGND = 0\text{ V}$ 、 $V_{REFIN} = 2.5\text{ V}$  外付け、 $DV_{CC} = 1.7\text{ V} \sim 5.5\text{ V}$ 、 $0\text{ V} \sim 16\text{ V}$  および $0\text{ V} \sim 20\text{ V}$  レンジでは  $R_{LOAD} = 2\text{ k}\Omega$ ；その他のすべてのレンジで  $R_{LOAD} = 1\text{ k}\Omega$ 、 $C_{LOAD} = 200\text{ pF}$ 、すべての仕様は  $T_{MIN} \sim T_{MAX}$  で規定。

表 3.

| Parameter <sup>2</sup>                       | Min | Typ  | Max | Unit   | Test Conditions/Comments                                                    |

|----------------------------------------------|-----|------|-----|--------|-----------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE <sup>3</sup>             |     |      |     |        |                                                                             |

| Output Voltage Settling Time                 | 9   | 12.5 |     | μs     | 20 V step to 1 LSB at 16-bit resolution                                     |

|                                              | 7.5 | 8.5  |     | μs     | 10 V step to 1 LSB at 16-bit resolution                                     |

|                                              |     | 5    |     | μs     | 512 LSB step to 1 LSB at 16-bit resolution                                  |

| Digital-to-Analog Glitch Impulse             | 8   |      |     | nV·sec | ±10 V range                                                                 |

|                                              | 1   |      |     | nV·sec | 0 V to 5 V range                                                            |

| Glitch Impulse Peak Amplitude                | 15  |      |     | mV     | ±10 V range                                                                 |

|                                              | 10  |      |     | mV     | 0 V to 5 V range                                                            |

| Power-On Glitch                              | 100 |      |     | mV p-p |                                                                             |

| Digital Feedthrough                          | 0.6 |      |     | nV·sec |                                                                             |

| Output Noise                                 |     |      |     |        |                                                                             |

| 0.1 Hz to 10 Hz Bandwidth (BW)               | 15  |      |     | μV p-p |                                                                             |

| 100 kHz BW                                   | 45  |      |     | μV rms | 0 V to 20 V and 0 V to 16 V ranges, 2.5 V external reference                |

|                                              | 35  |      |     | μV rms | 0 V to 10 V, ±10 V, -2.5 V to +7.5 V ranges, 2.5 V external reference       |

|                                              | 25  |      |     | μV rms | ±5 V range, 2.5 V external reference                                        |

|                                              | 15  |      |     | μV rms | +5 V, ±3 V ranges; 2.5 V external reference                                 |

| Output Noise Spectral Density (at 10 kHz)    | 80  |      |     | nV/√Hz | ±10 V range, 2.5 V external reference                                       |

|                                              | 35  |      |     | nV/√Hz | ±3 V range, 2.5 V external reference                                        |

|                                              | 70  |      |     | nV/√Hz | ±5 V, 0 V to 10 V, and -2.5 V to +7.5 V ranges; 2.5 V external reference    |

|                                              | 110 |      |     | nV/√Hz | 0 V to 20 V range, 2.5 V external reference                                 |

|                                              | 90  |      |     | nV/√Hz | 0 V to 16 V range, 2.5 V external reference                                 |

|                                              | 45  |      |     | nV/√Hz | 0 V to 5 V range, 2.5 V external reference                                  |

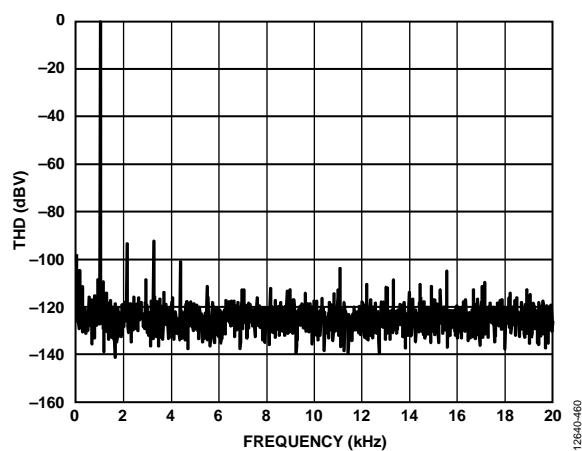

| Total Harmonic Distortion (THD) <sup>4</sup> | -87 |      |     | dB     | 2.5 V external reference, 1 kHz tone                                        |

| Signal-to-Noise Ratio (SNR)                  | 92  |      |     | dB     | At ambient, 2.5 V external reference, BW = 20 kHz, $f_{OUT} = 1\text{ kHz}$ |

| Peak Harmonic or Spurious Noise (SFDR)       | 92  |      |     | dB     | At ambient, 2.5 V external reference, BW = 20 kHz, $f_{OUT} = 1\text{ kHz}$ |

| Signal-to-Noise-and-Distortion (SINAD) Ratio | 85  |      |     | dB     | At ambient, 2.5 V external reference, BW = 20 kHz, $f_{OUT} = 1\text{ kHz}$ |

<sup>1</sup> 標定性能に対して、ヘッドルーム条件は 1 V。

<sup>2</sup> 温度範囲は-40 °C～+125°C です。typ 値は+25°C の値です。

<sup>3</sup> 設計とキャリクタライゼーションにより保証しますが、出荷テストは行いません。

<sup>4</sup> デジタル的に発生した 1 kHz の正弦波。

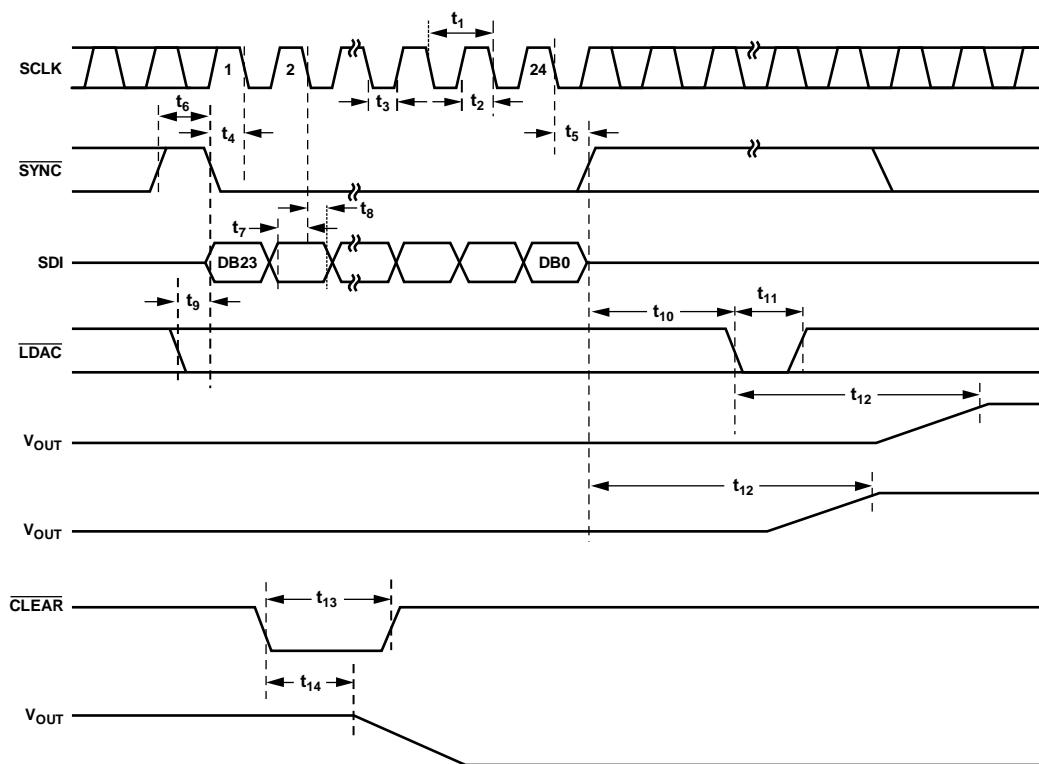

## タイミング特性

特に指定がない限り、 $DV_{CC} = 1.7 \text{ V} \sim 5.5 \text{ V}$ 、すべての仕様は  $T_{MIN} \sim T_{MAX}$  で規定。

表 4.

| Parameter | Limit at $T_{MIN}$ to $T_{MAX}$ | Unit   | Description                                                                                                                 |

|-----------|---------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| $t_1^1$   | 20                              | ns min | SCLK cycle time                                                                                                             |

| $t_2$     | 10                              | ns min | SCLK high time                                                                                                              |

| $t_3$     | 10                              | ns min | SCLK low time                                                                                                               |

| $t_4$     | 15                              | ns min | SYNC falling edge to SCLK falling edge setup time                                                                           |

| $t_5$     | 10                              | ns min | SCLK falling edge to SYNC rising edge time                                                                                  |

| $t_6$     | 20                              | ns min | Minimum SYNC high time (write mode)                                                                                         |

| $t_7$     | 5                               | ns min | Data setup time                                                                                                             |

| $t_8$     | 5                               | ns min | Data hold time                                                                                                              |

| $t_9$     | 10                              | ns min | LDAC falling edge to SYNC falling edge                                                                                      |

| $t_{10}$  | 20                              | ns min | SYNC rising edge to LDAC falling edge                                                                                       |

| $t_{11}$  | 20                              | ns min | LDAC pulse width low                                                                                                        |

| $t_{12}$  | 9                               | μs typ | DAC output settling time, 20 V step to 1 LSB at 16-bit resolution (see Table 3)                                             |

|           | 7.5                             | μs typ | DAC output settling time, 10 V step to 1 LSB at 16-bit resolution                                                           |

| $t_{13}$  | 20                              | ns min | CLEAR pulse width low                                                                                                       |

| $t_{14}$  | 200                             | ns typ | CLEAR pulse activation time                                                                                                 |

| $t_{15}$  | 10                              | ns min | SYNC rising edge to SCLK falling edge                                                                                       |

| $t_{16}$  | 40                              | ns max | SCLK rising edge to SDO valid ( $C_{L\_SDO} = 15 \text{ pF}$ , where $C_{L\_SDO}$ is the capacitive load on the SDO output) |

| $t_{17}$  | 50                              | ns min | Minimum SYNC high time (readback/daisy-chain mode)                                                                          |

<sup>1</sup> 最大 SCLK 周波数は、書込モードでは 50 MHz に、リードバック・モードでは 33 MHz に、それぞれなります。

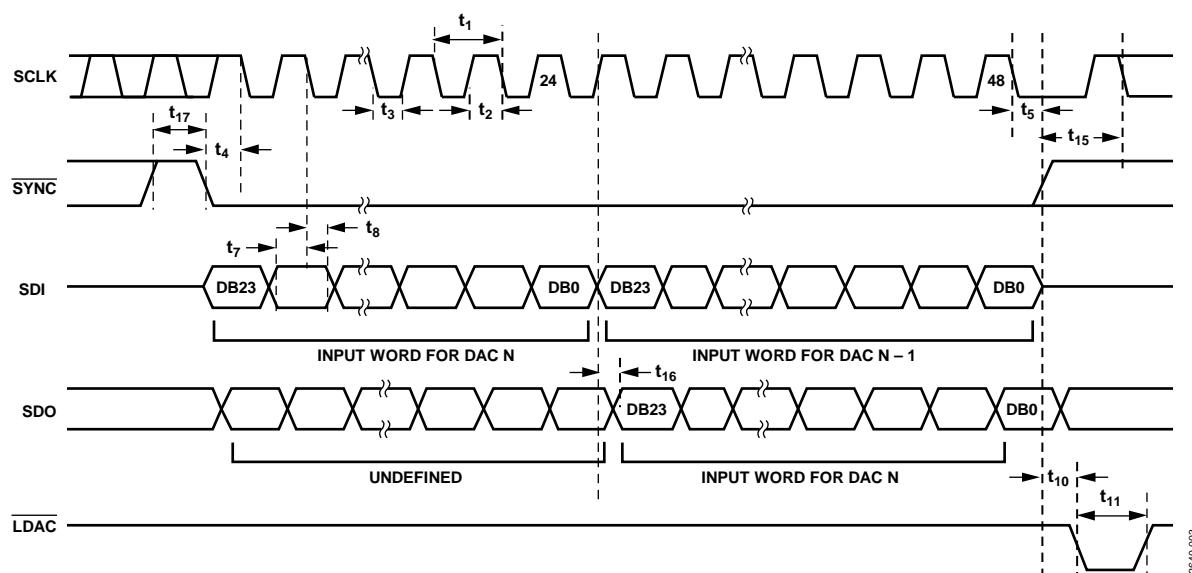

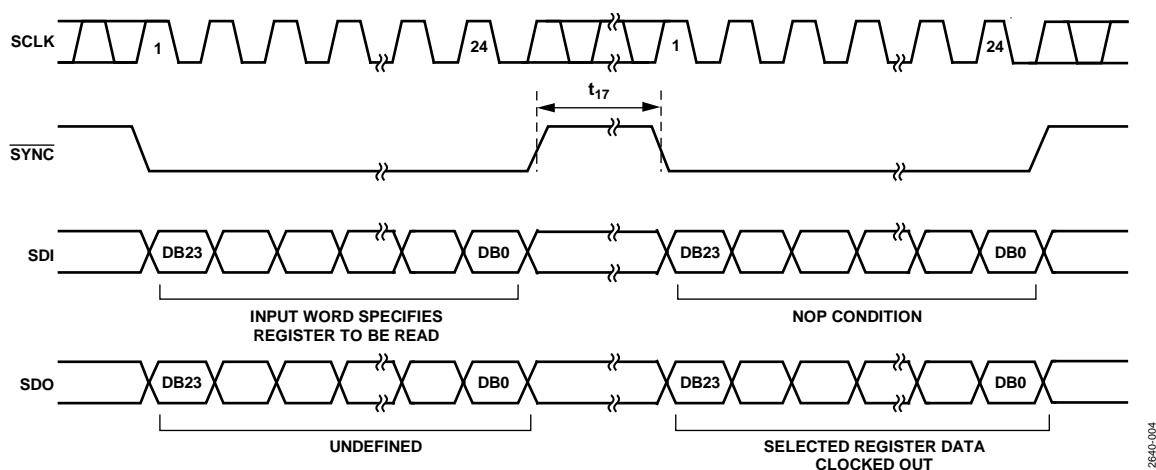

## タイミング図

1284D-002

図 2. シリアル・インターフェースのタイミング図

図3.デイジーチェーン・タイミング図

図4.リードバックのタイミング図

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。最大 200 mA までの過渡電流では SCR ラッチ・アップは生じません。

表 5.

| Parameter                                    | Rating                                                 |

|----------------------------------------------|--------------------------------------------------------|

| $V_{DD}$ to AGND                             | -0.3 V to +34 V                                        |

| $V_{SS}$ to AGND                             | +0.3 V to -17 V                                        |

| $V_{DD}$ to $V_{SS}$                         | -0.3 V to +34 V                                        |

| $DV_{CC}$ to DGND                            | -0.3 V to +7 V                                         |

| Digital Inputs <sup>1</sup> to DGND          | -0.3 V to $DV_{CC} + 0.3$ V or 7 V (whichever is less) |

| Digital Outputs <sup>2</sup> to DGND         | -0.3 V to $DV_{CC} + 0.3$ V or 7 V (whichever is less) |

| $V_{REFIN}$ to DGND                          | -0.3 V to +7 V                                         |

| $V_{OUT}$ to AGND                            | $V_{SS}$ to $V_{DD}$                                   |

| AGND to DGND                                 | -0.3 V to +0.3 V                                       |

| Operating Temperature Range, TA Industrial   | -40°C to +125°C                                        |

| Storage Temperature Range                    | -65°C to +150°C                                        |

| Junction Temperature, $T_{J\text{ MAX}}$     | 150°C                                                  |

| 16-Lead TSSOP Package                        |                                                        |

| $\theta_{JA}$ Thermal Impedance <sup>3</sup> | 113°C/W                                                |

| $\theta_{JC}$ Thermal Impedance              | 28°C/W                                                 |

| Power Dissipation                            | $(T_{J\text{ MAX}} - T_A)/\theta_{JA}$                 |

| Lead Temperature                             | JEDEC industry standard                                |

| Soldering                                    | J-STD-020                                              |

| ESD (Human Body Model)                       | 4 kV                                                   |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上での製品動作を定めたものではありません。製品を長時間絶対最大定格状態に置くと製品の信頼性に影響を与えます。

### ESD の注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

<sup>1</sup> デジタル入力には、CLEAR、RESET、SCLK、SYNC、SDI、LDACが含まれます。

<sup>2</sup> デジタル出力には、ALERTとSDOが含まれます。

<sup>3</sup> JEDEC 2S2P テスト・ボード、自然空冷(0 m/sec の空気流)。

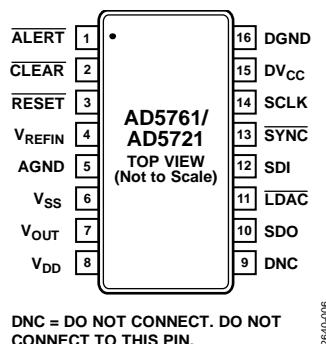

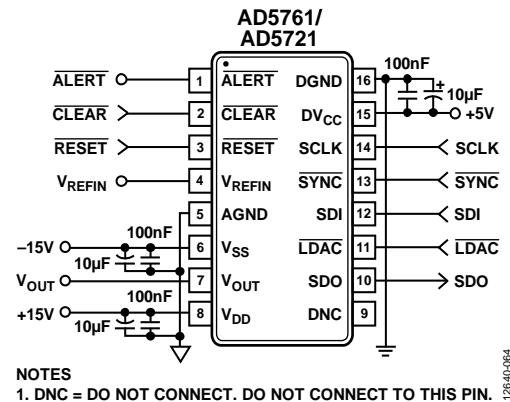

## ピン配置およびピン機能説明

図 5. ピン配置

表 6. ピンの機能説明

| ピン番号 | 記号               | 説明                                                                                                                                                                                                                             |

|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ALERT            | アクティブ・ローのアラート信号。チップ温度が約 150°C を超えるか、あるいは出力の短絡または電源電圧の低下が発生すると、このピンがロー・レベルになります。また、パワーアップ時、フル・ソフトウェア・リセット時、またはハードウェア・リセット時にも、このピンはロー・レベルになります。これに対して、コントロール・レジスタへ書き込みを行うと、このピンはハイ・レベルになります。                                     |

| 2    | CLEAR            | 立下がりエッジのクリア入力。このピンをアサートすると、DAC レジスタがゼロスケール、ミッドスケール、またはフルスケール・コード(ユーザー選択可能)に設定されて、DAC 出力が更新されます。このピンにはプルアップ抵抗が内蔵されているため、フローティングのままにすることができます。                                                                                   |

| 3    | RESET            | アクティブ・ローのリセット入力。このピンをアサートすると、AD5761/AD5721 はデフォルトのパワーオン状態に戻り、出力がグラウンドにクランプされ、出力バッファはパワーダウンします。このピンにはプルアップ抵抗が内蔵されているため、フローティングのままにすることができます。                                                                                    |

| 4    | VREFIN           | 外部リファレンス電圧入力。性能は、 $V_{REFIN} = 2.5\text{ V}$ で規定されています。                                                                                                                                                                        |

| 5    | AGND             | アナログ回路のグラウンド基準。                                                                                                                                                                                                                |

| 6    | V <sub>SS</sub>  | 負のアナログ電源接続。-16.5 V~0 V の電圧レンジをこのピンへ接続することができます。ユニポーラ出力レンジの場合は、このピンを 0 V に接続します。V <sub>SS</sub> は AGND へデカッピングする必要があります。                                                                                                        |

| 7    | V <sub>OUT</sub> | DAC のアナログ出力電圧。出力アンプは、2 kΩ、1 nF の負荷を直接駆動することができます。                                                                                                                                                                              |

| 8    | V <sub>DD</sub>  | 正のアナログ電源接続。ユニポーラ出力レンジの場合、4.75 V~30 V の電圧をこのピンに接続することができます。バイポーラ出力レンジの場合、4.75 V~16.5 V の電圧をこのピンに接続することができます。V <sub>DD</sub> は AGND へデカッピングする必要があります。                                                                            |

| 9    | DNC              | 接続なし。このピンは接続しないでください。                                                                                                                                                                                                          |

| 10   | SDO              | シリアル・データ出力。このピンは、デイジーチェーン・モードまたはリードバック・モードでシリアル・レジスタからのデータを駆動するときに使います。データは SCLK の立ち上がりエッジで出力され、SCLK の立下がりエッジで有効。                                                                                                              |

| 11   | LDAC             | DAC のロード。このロジック入力は DAC レジスタを更新し、したがってアナログ出力を更新します。ロー・レベルに固定すると、入力レジスタが更新されたとき DAC レジスタが更新されます。入力レジスタへの書き込み時に LDAC をハイ・レベルに維持すると、DAC 出力レジスタは更新されず、LDAC の立下がりエッジまで DAC 出力の更新が待たれます。このピンにはプルアップ抵抗が内蔵されているため、フローティングのままにすることができます。 |

| 12   | SDI              | シリアル・データ入力。データは、SCLK の立下がりエッジで有効である必要があります。                                                                                                                                                                                    |

| 13   | SYNC             | アクティブ・ローの同期入力。このピンは、シリアル・インターフェースのフレーム同期信号です。SYNC がロー・レベルのとき、データは SCLK の立下がりエッジで転送されます。データは、SYNC の立上がりエッジでラッチされます。                                                                                                             |

| 14   | SCLK             | シリアル・クロック入力。データは、SCLK の立下がりエッジで入力シフトレジスタに入力されます。このピンは最大 50 MHz のクロック速度で動作します。                                                                                                                                                  |

| 15   | DV <sub>CC</sub> | デジタル電源。電圧範囲は 1.7 V~5.5 V です。ここに加えた電圧により、デジタル・インターフェースが動作する電圧が設定されます。                                                                                                                                                           |

| 16   | DGND             | デジタル・グラウンド。                                                                                                                                                                                                                    |

## 代表的な性能特性

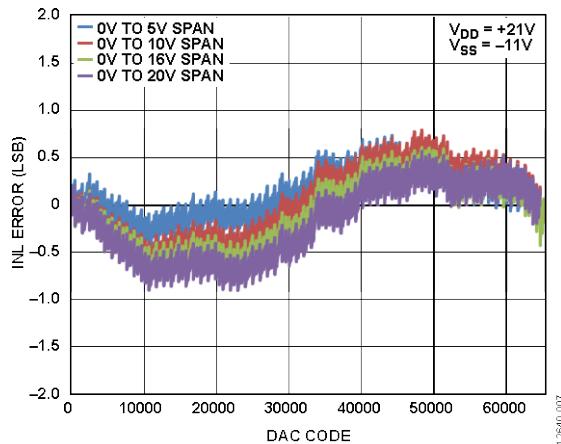

図 6. AD5761 の DAC コード対 INL 誤差、ユニポーラ出力

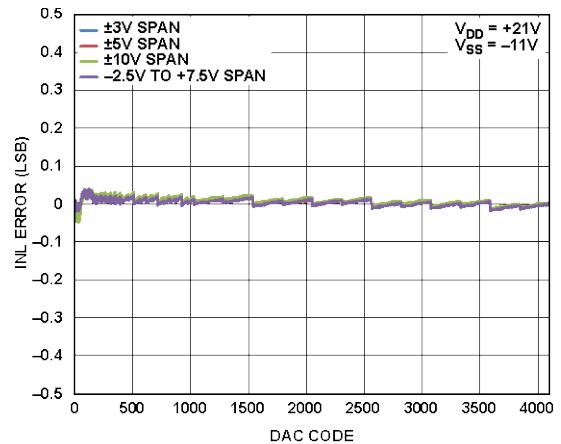

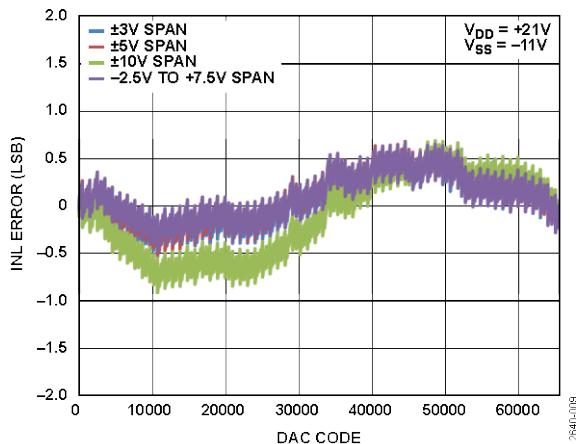

図 9. AD5721 の DAC コード対 INL 誤差、バイポーラ出力

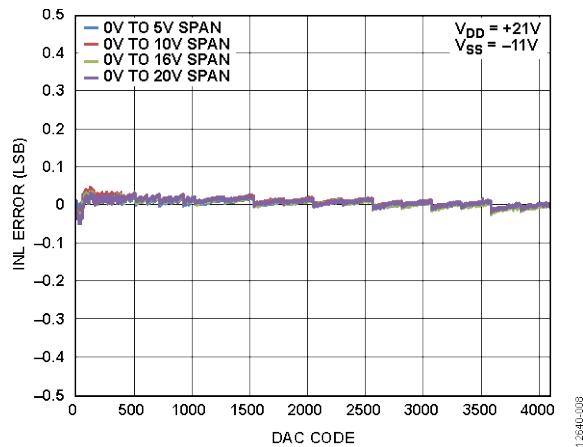

図 7. AD5721 の DAC コード対 INL 誤差、ユニポーラ出力

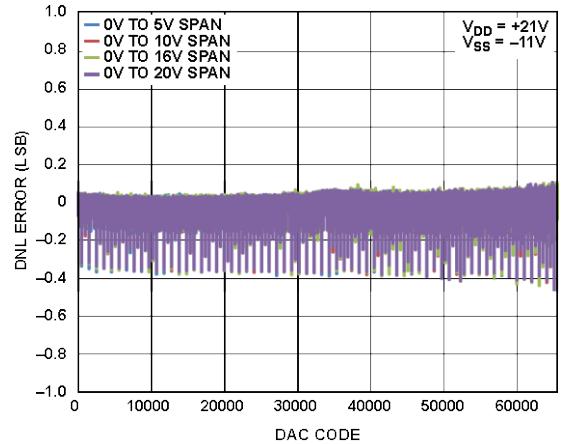

図 10. AD5761 の DAC コード対 DNL 誤差、ユニポーラ出力

図 8. AD5761 の DAC コード対 INL 誤差、バイポーラ出力

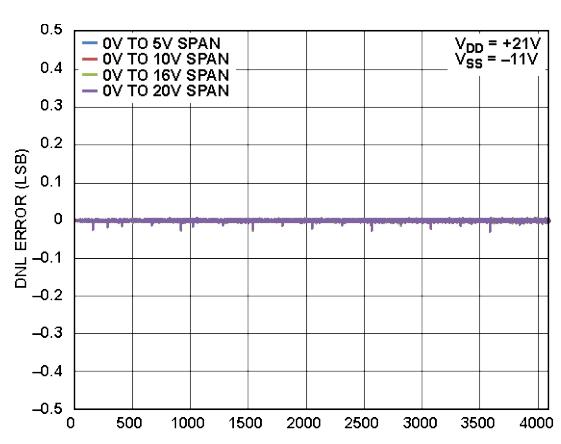

図 11. AD5721 の DAC コード対 DNL 誤差、ユニポーラ出力

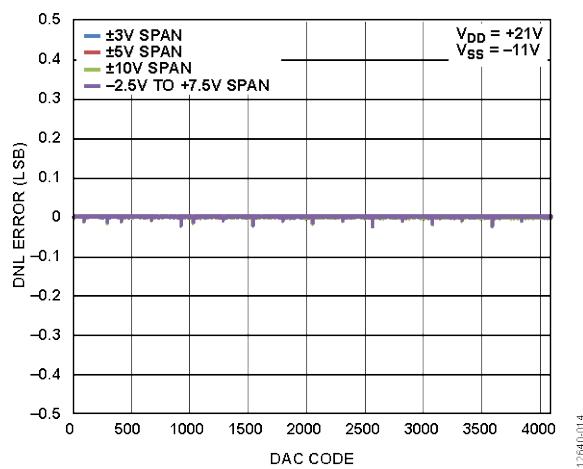

図 12. AD5761 の DAC コード対 DNL 誤差、バイポーラ出力

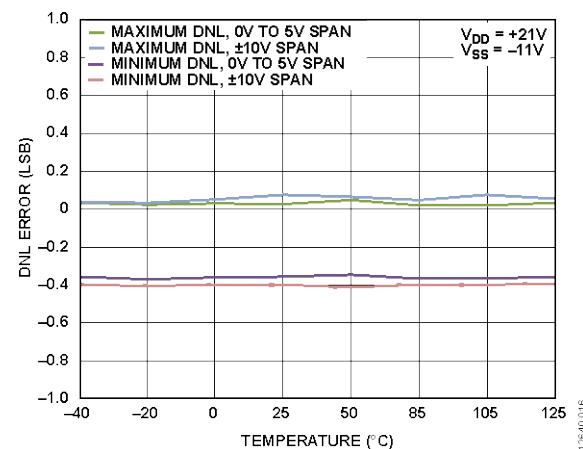

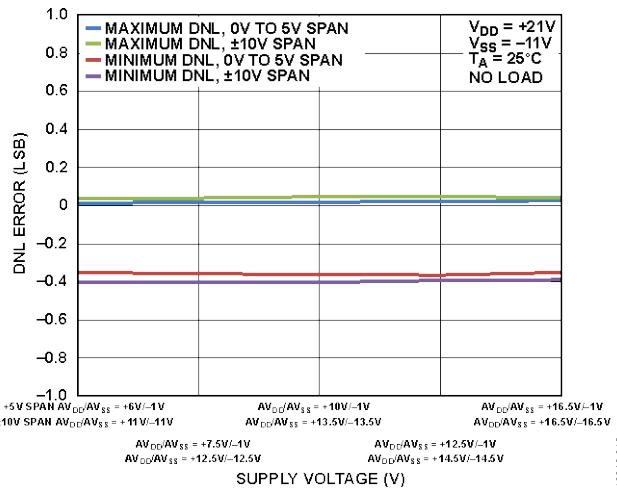

図 15. DNL 誤差の温度特性

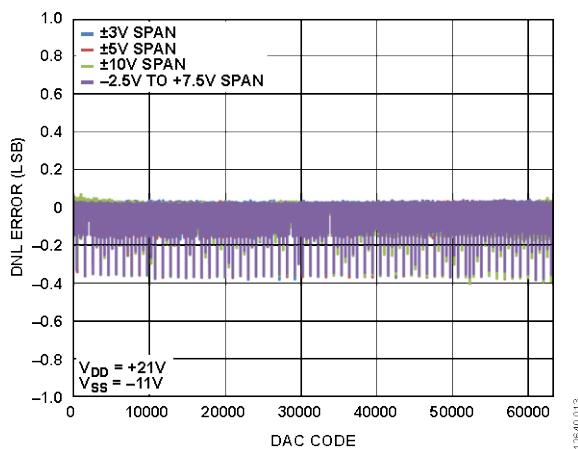

図 13. AD5721 の DAC コード対 DNL 誤差、バイポーラ出力

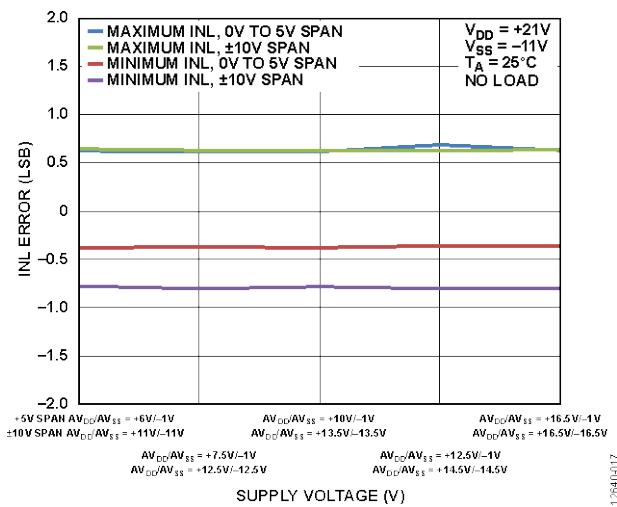

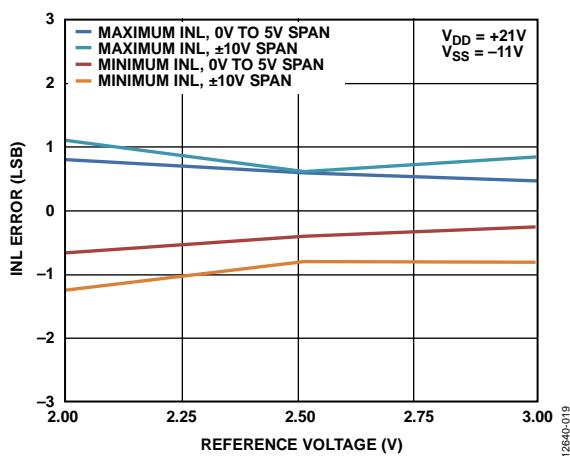

図 16. 電源電圧対 INL 誤差

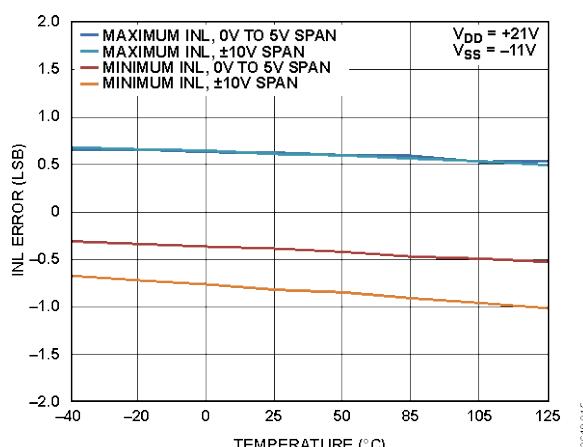

図 14. INL 誤差の温度特性

図 17. 電源電圧対 DNL 誤差

図 18. リファレンス電圧対 INL 誤差

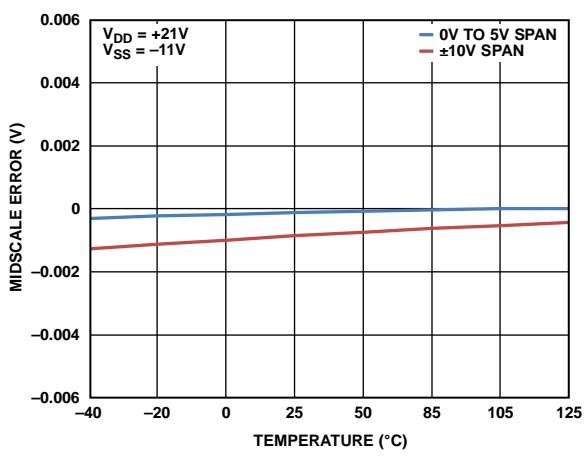

図 21. ミッドスケール誤差の温度特性

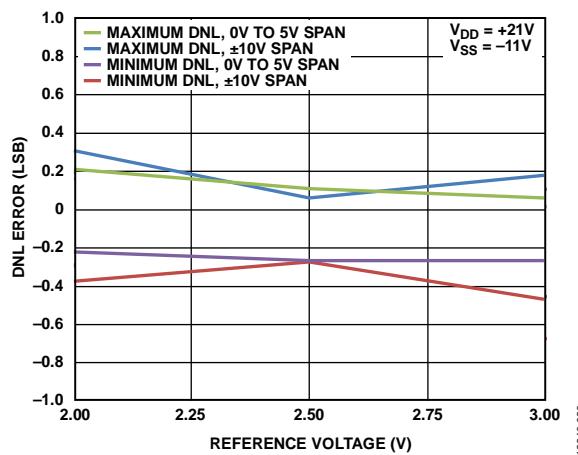

図 19. リファレンス電圧対 DNL 誤差

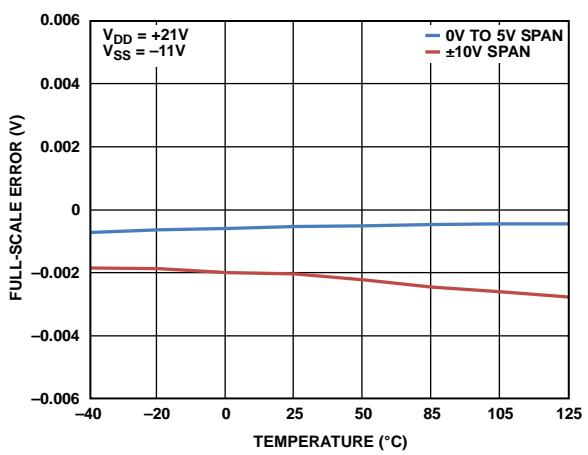

図 22. フルスケール誤差の温度特性

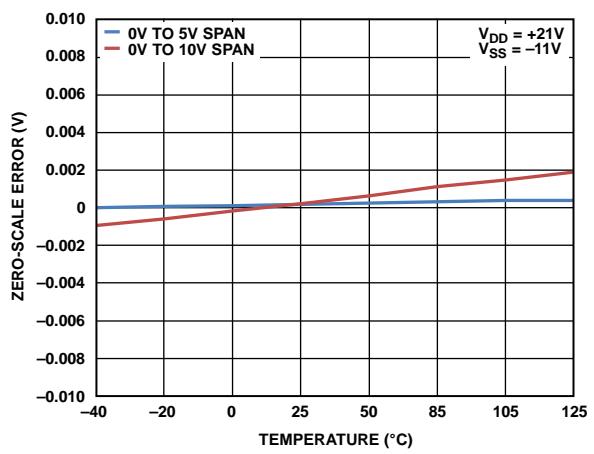

図 20. ゼロスケール誤差の温度特性

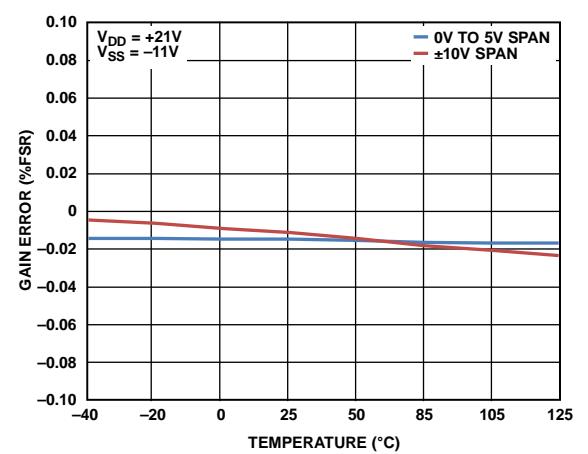

図 23. ゲイン誤差の温度特性

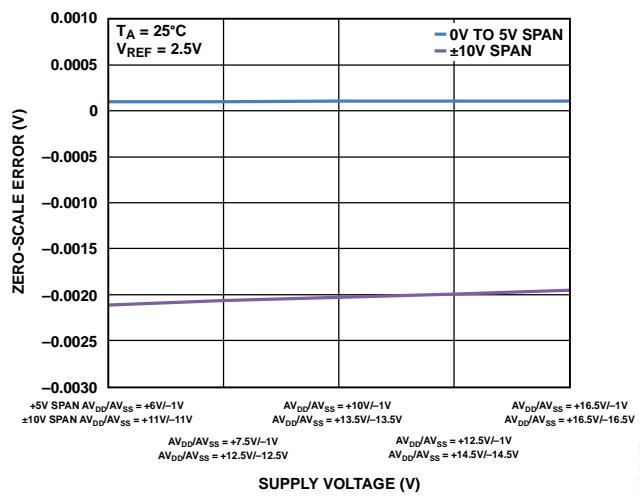

図 24. 電源電圧対ゼロスケール誤差

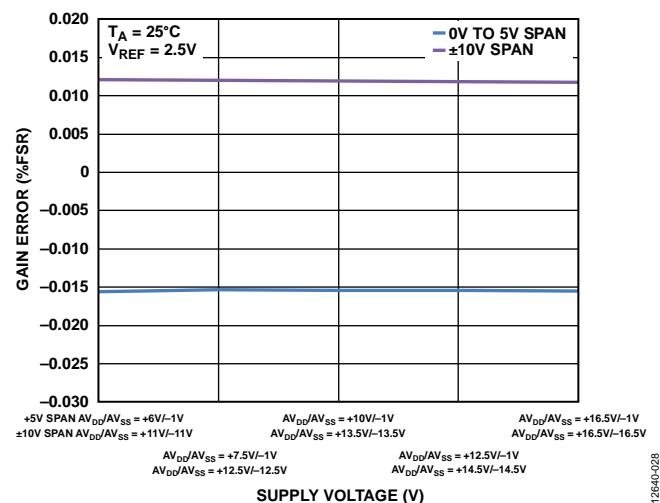

図 27. 電源電圧対ゲイン誤差

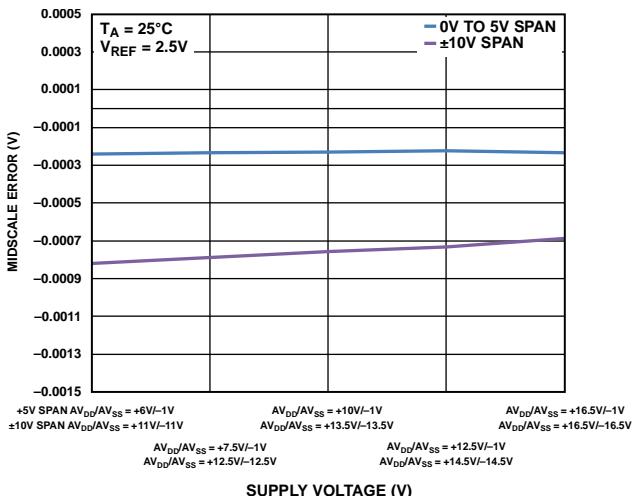

図 25. 電源電圧対ミッドスケール誤差

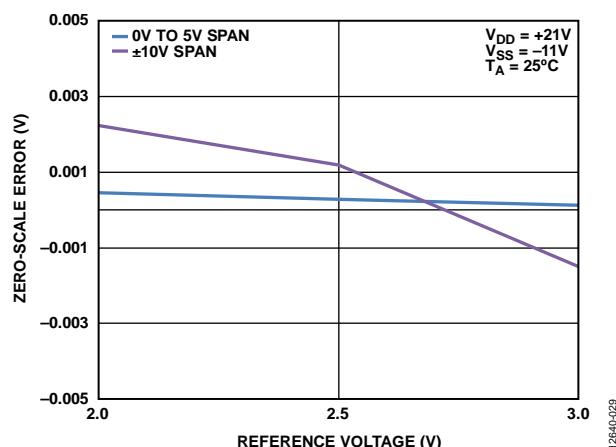

図 28. リファレンス電圧対ゼロスケール誤差

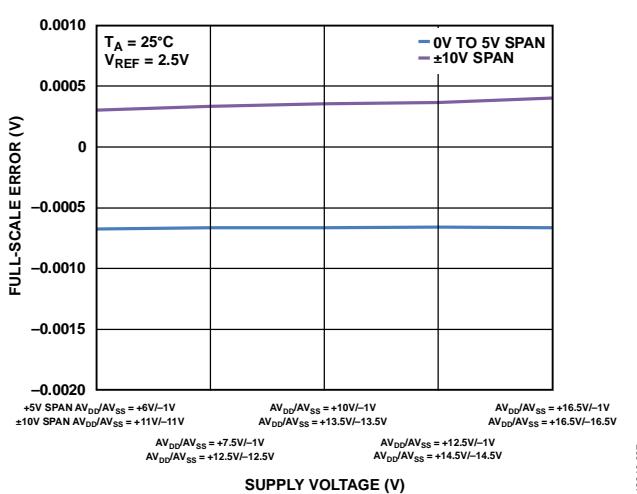

図 26. 電源電圧対フルスケール誤差

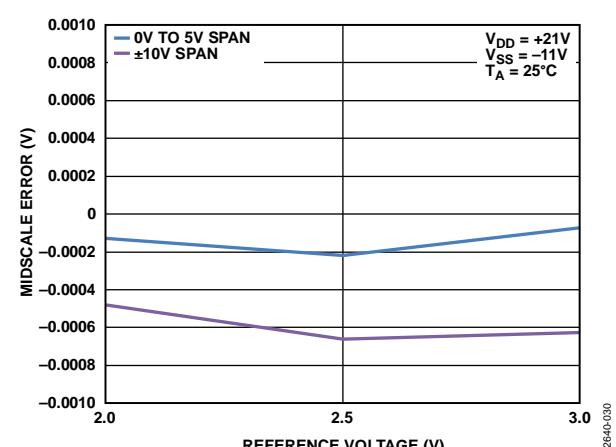

図 29. リファレンス電圧対ミッドスケール誤差

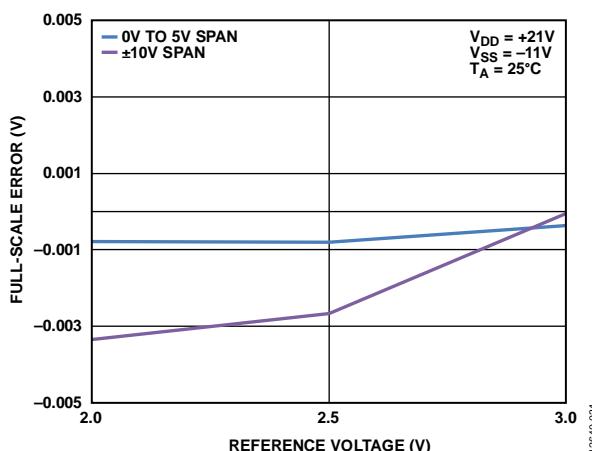

図 30. リファレンス電圧対フルスケール誤差

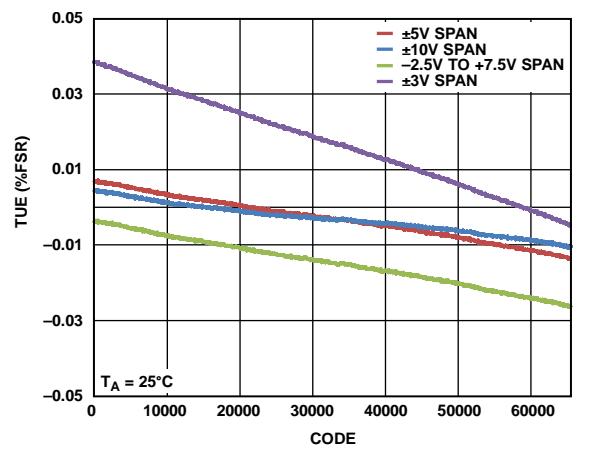

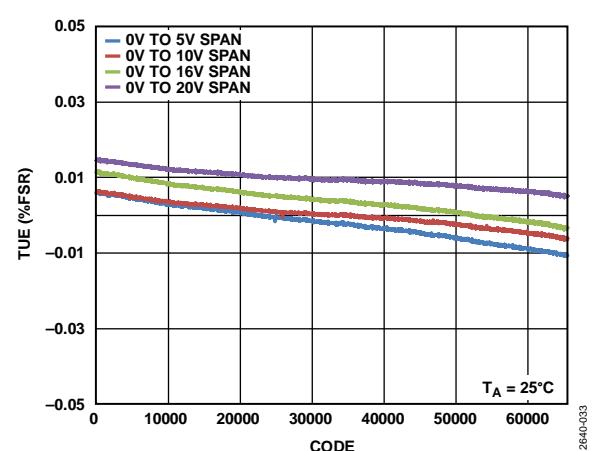

図 33. コード対 TUE、バイポーラ出力

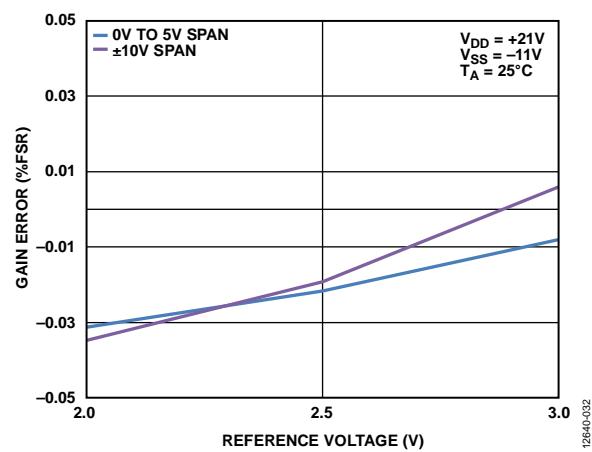

図 31. リファレンス電圧対ゲイン誤差

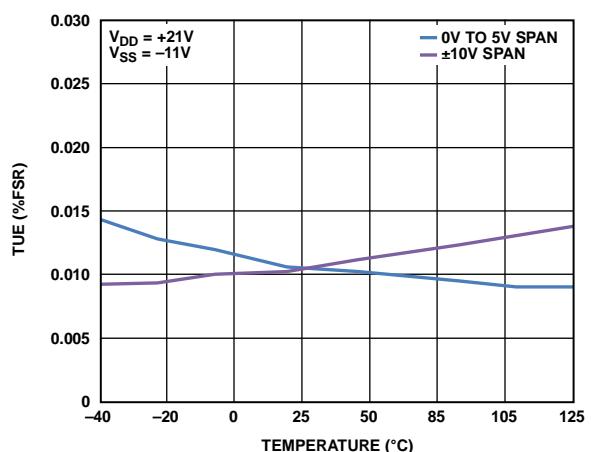

図 34. TUE の温度特性

図 32. コード対 TUE、ユニポーラ出力

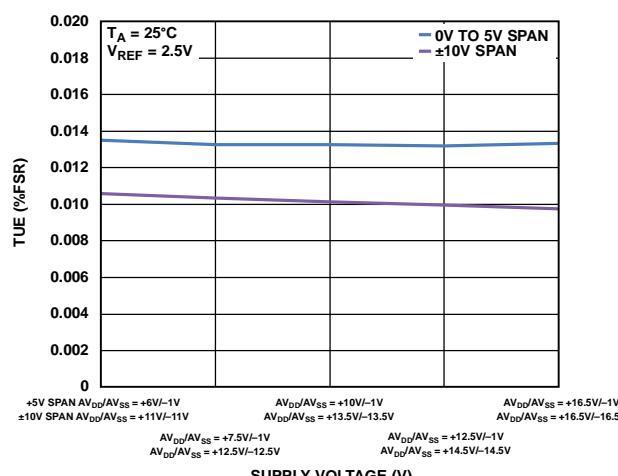

図 35. 電源電圧対 TUE

12640-143

12640-144

12640-051

12640-052

12640-050

12640-053

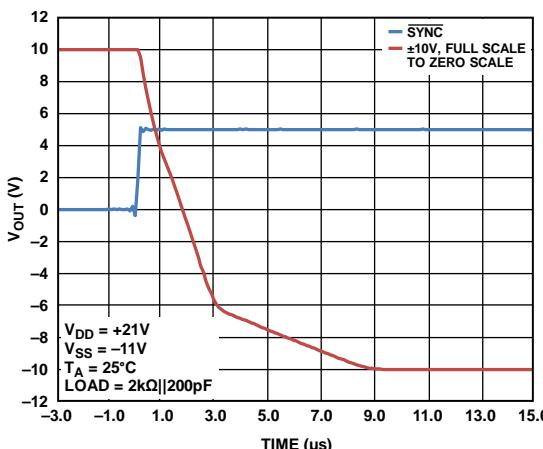

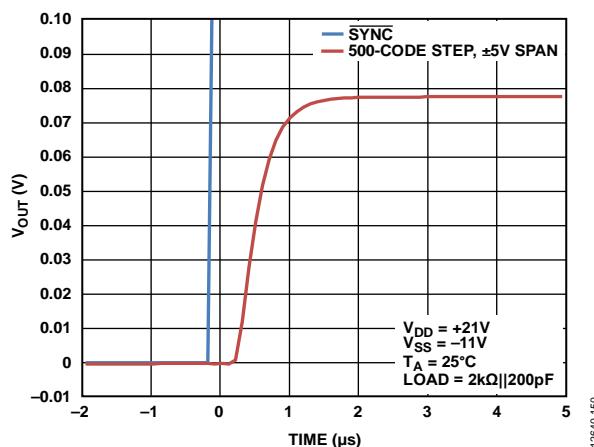

図 42. 500 コード・ステップのセッティング・タイム

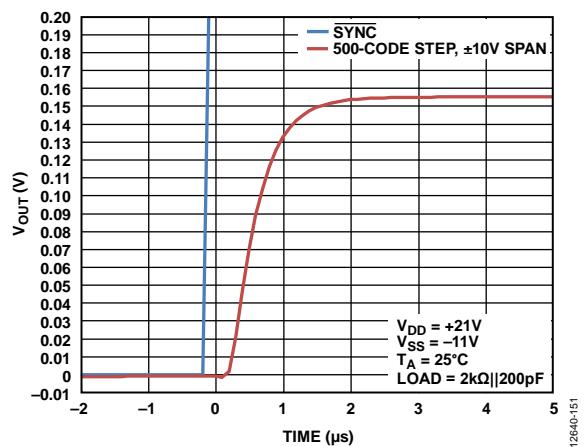

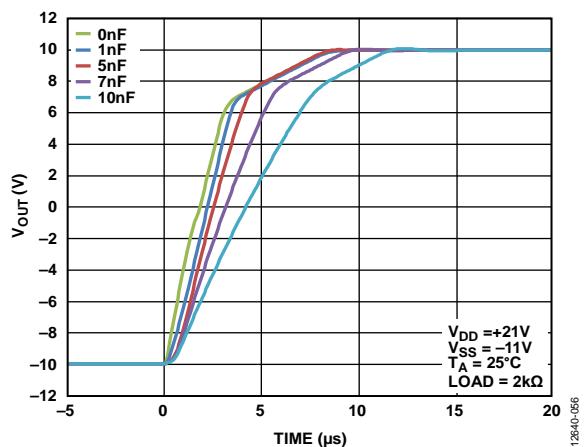

±5 V レンジ図 45. 容量負荷対セッティング・タイム

0 V~5 V レンジ図 43. 500 コード・ステップのセッティング・タイム

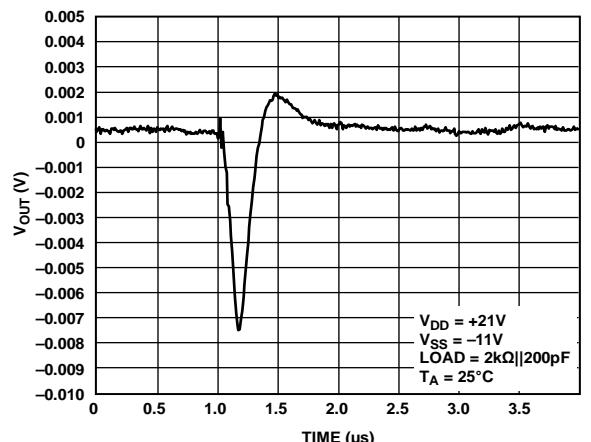

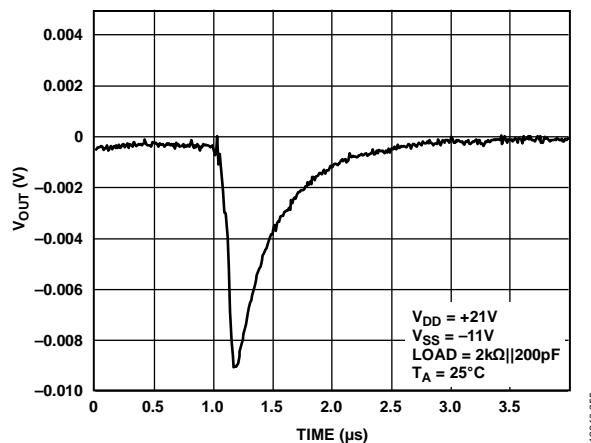

±10 V レンジ図 46. D/A グリッチ・エネルギー

0 V~5 V レンジ

図 44. 容量負荷対セッティング・タイム、±10 V レンジ

図 47. D/A グリッチ・エネルギー、±10 V レンジ

図 48. パワーアップ・グリッチ

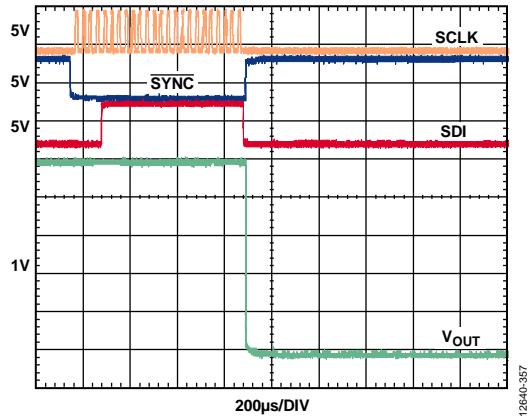

図 51. ゼロスケールからのソフトウェア・フル・リセット・グリッチ、出力負荷あり、0 V~5 V レンジ

図 49. フルスケールからのソフトウェア・フル・リセット・グリッチ、出力負荷あり、0 V~5 V レンジ

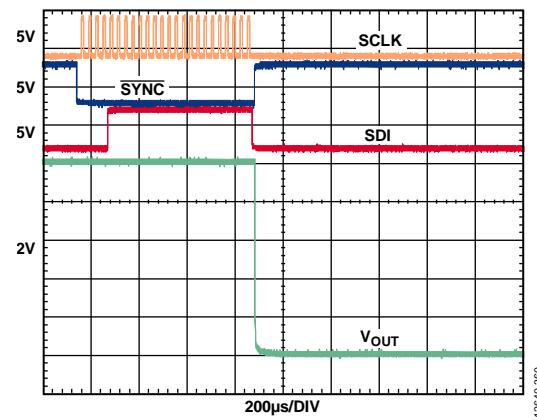

図 52. フルスケールからのソフトウェア・フル・リセット・グリッチ、出力負荷あり、±10 V レンジ

図 50. ミッドスケールからのソフトウェア・フル・リセット・グリッチ、出力負荷あり、0 V~5 V レンジ

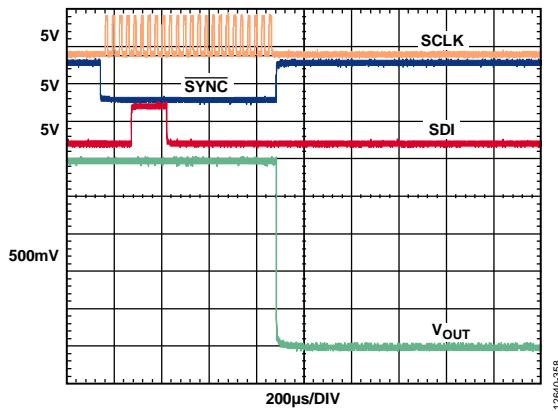

図 53. ミッドスケールからのソフトウェア・フル・リセット・グリッチ、出力負荷あり、±10 V レンジ

図 54. ゼロスケールからのソフトウェア・フル・リセット・グリッチ、出力負荷あり、 $\pm 10\text{ V}$  レンジ

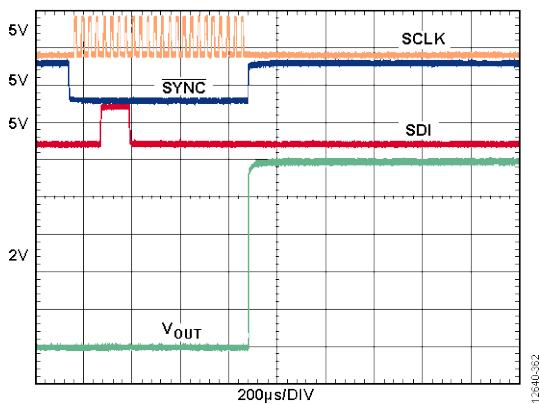

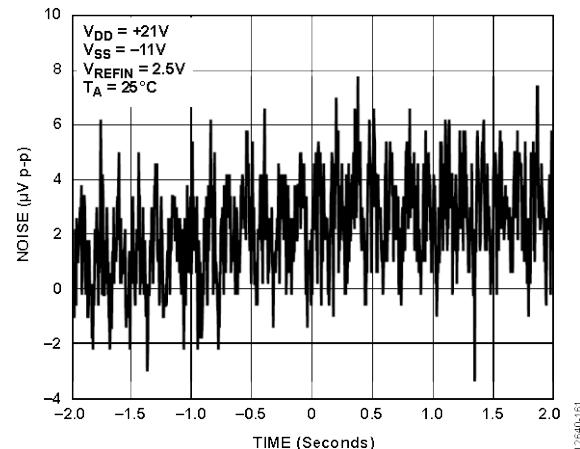

図 57. ピーク to ピーク・ノイズ(電圧出力ノイズ)

0.1 Hz～10 Hz 帯域幅

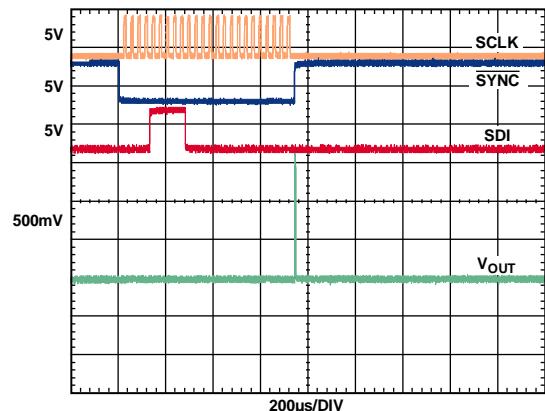

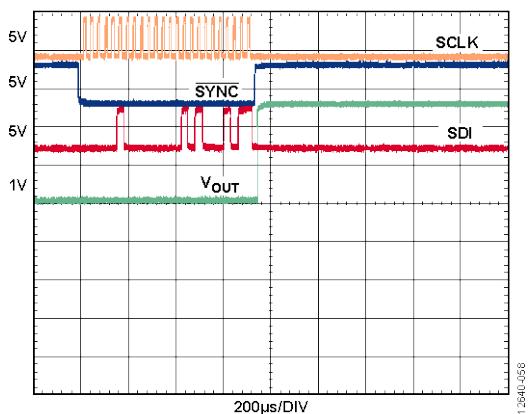

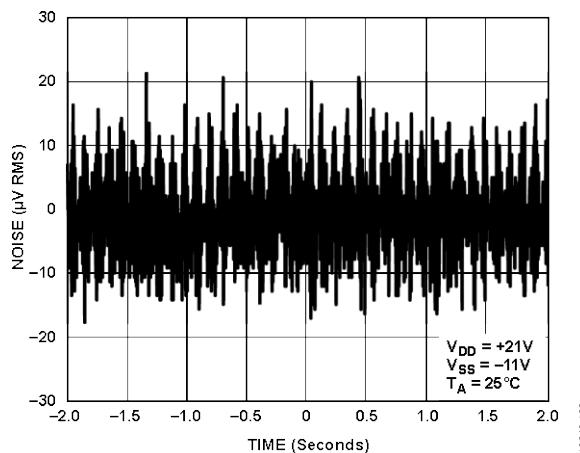

図 55. 出力レンジ変化グリッチ、0 V～5 V レンジ

図 58. ピーク to ピーク・ノイズ(電圧出力ノイズ)

100 kHz 帯域幅

図 56. 出力レンジ変化グリッチ、 $\pm 10\text{ V}$  レンジ

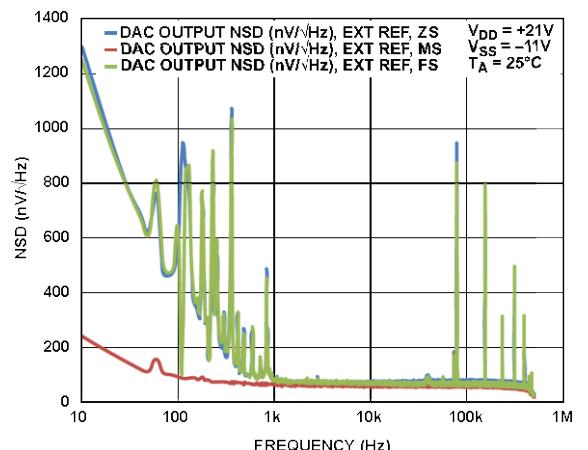

図 59. DAC 出力ノイズ・スペクトル密度の周波数特性

$\pm 10\text{ V}$  レンジ

図 60. 全高調波歪み、1 kHz

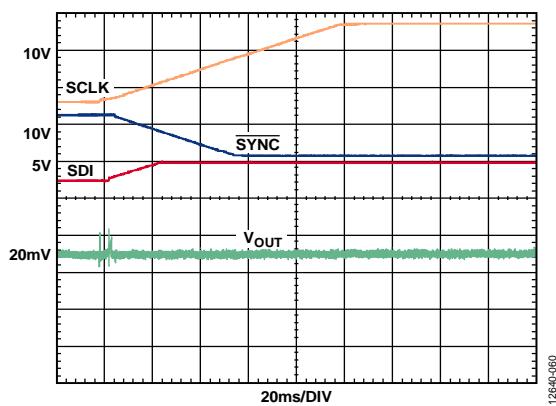

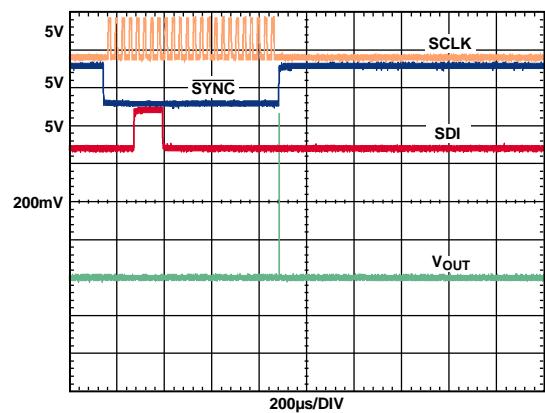

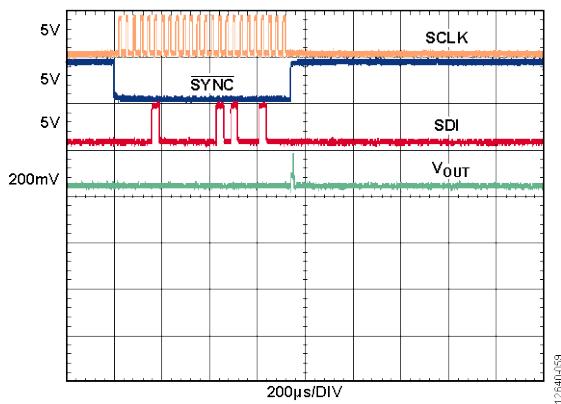

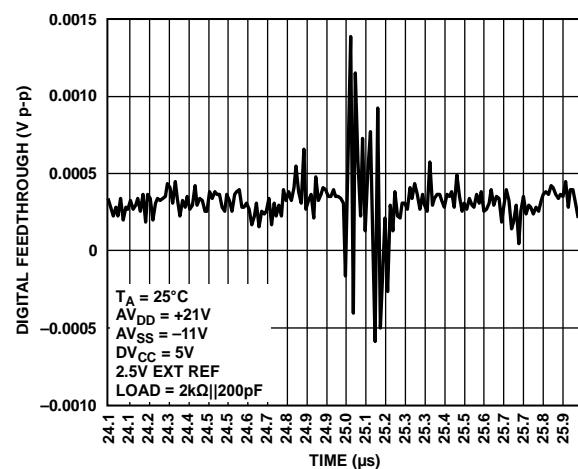

図 61. デジタル・フィードスルー

## 用語

### 総合未調整誤差(TUE)

総合未調整誤差は、種々の誤差(電源、温度、時間に対する INL 誤差、オフセット誤差、ゲイン誤差、出力ドリフト)をすべて考慮した出力誤差を表し、% FSR で表されます。

### 相対精度または積分非直線性(INL)

DAC の場合、相対精度すなわち積分非直線性は、DAC 伝達関数の上下両端を結ぶ直線からの最大偏差(LSB 数で表示)を表します。INL 誤差(typ)対 DAC コードのプロットを図 6 に示します。

### 微分非直線性(DNL)

微分非直線性(DNL)は、隣接する 2 つのコードの間における測定された変化と理論的な 1 LSB 变化との誤差です。最大 $\pm 1$  LSB の微分非直線性の規定により、単調性が保証されます。この DAC は単調性が保証されています。DNL 誤差(typ)対コードのプロットを図 10 に示します。

### 単調性

デジタル入力コードを増加させたとき、出力が増加するか不变である場合に、DAC は単調であるといいます。AD5761/AD5721 は全動作温度範囲で単調性を維持しています。

### バイポーラ・ゼロ誤差

バイポーラ・ゼロ誤差は、AD5761/AD5721 の DAC レジスタに 0x8000(ストレート・バイナリ・コーディング)または 0x0000(2 の補数コーディング)をロードしたときの、0 V の理論ハーフスケール出力からのアナログ出力の差を表します。

### バイポーラ・ゼロ温度係数(TC)

バイポーラ・ゼロ TC は、温度変化に対するバイポーラ・ゼロ誤差の変化を表し、 $\mu\text{V}/^\circ\text{C}$  で表されます。

### ゼロスケール誤差

ゼロスケール誤差は、0x0000(ストレート・バイナリ・コーディング)または 0x8000(2 の補数コーディング)を DAC レジスタにロードしたときの、DAC 出力電圧の誤差を意味します。理論的には、出力電圧は負のフルスケールになります。ゼロスケール誤差の温度特性を図 20 に示します。

### ゼロスケール誤差温度係数(TC)

ゼロスケール誤差 TC は、温度変化に対するゼロスケール誤差の変化を表し、 $\mu\text{V}/^\circ\text{C}$  で表されます。

### オフセット誤差

オフセット誤差は、伝達関数の直線領域での  $\text{V}_{\text{OUT}}$ (実測値)と  $\text{V}_{\text{OUT}}$ (理論値)の差を表し、mV で表示されます。

### オフセット誤差温度係数(TC)

オフセット誤差 TC は、温度変化によるオフセット誤差の変化を表し、 $\mu\text{V}/^\circ\text{C}$  で表されます。

### ゲイン誤差

ゲイン誤差は DAC のスパン誤差を表します。理論 DAC 伝達特性傾斜からの変位を表し、DAC 出力の%FSR で表示されます。ゲイン誤差の温度特性を図 23 に示します。

### ゲイン誤差温度係数(TC)

ゲイン誤差 TC は、温度変化によるゲイン誤差の変化を表し、 $\text{ppm FSR}/^\circ\text{C}$  で表されます。

### DC 電源除去比(DC PSRR)

DC 電源除去比は、DAC へ加えた電源の DC 変化に対応する出力電圧の除去能力を表します。電源電圧の与えられた DC 変化に対して測定され、mV/V で表されます。

### AC 電源除去比(AC PSRR)

AC 電源除去比は、DAC へ加えた電源の AC 変化に対応する出力電圧の除去能力を表します。電源電圧の与えられた振幅と周波数の変化に対して測定され、デシベルで表されます。

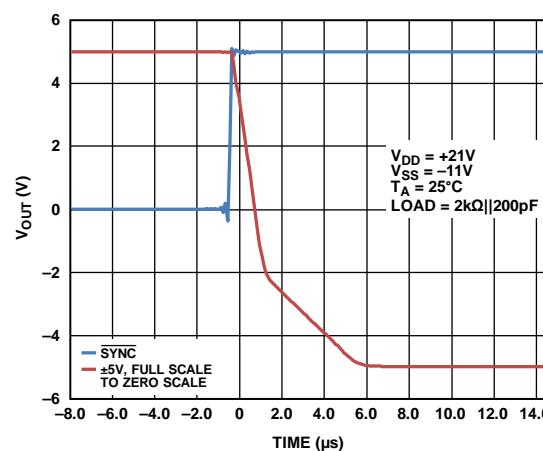

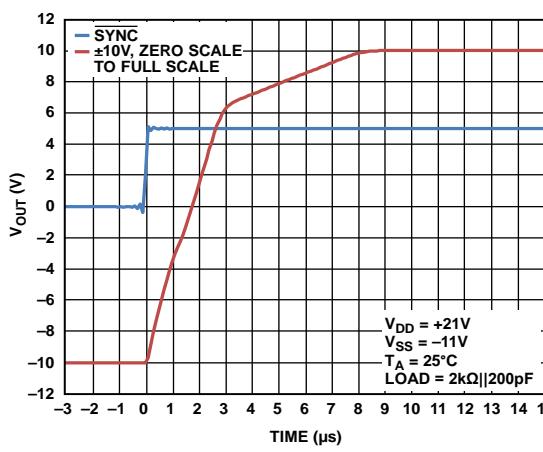

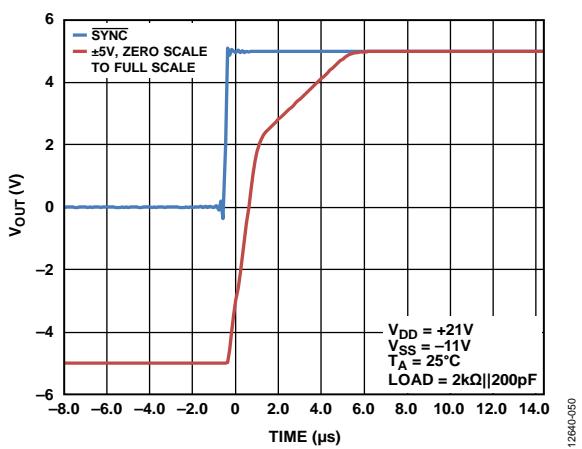

### 出力電圧セトリング・タイム

フルスケール入力変化に対して、出力が規定のレベルまでに安定するため必要とする時間を表します。フルスケール・セトリング・タイムを図 38~図 41 に示します。

### デジタルからアナログへのグリッチ・インパルス

デジタルからアナログへのグリッチ・インパルスは、DAC レジスタ内の入力コードが変化したときに、アナログ出力に混入するインパルス・ノイズを表します。通常これは  $\text{nV}\cdot\text{sec}$  で表すグリッチの面積として規定され、メジャー・キャリー変化時に、デジタル入力コードが 1 LSB だけ変化したときに測定されます(図 46 と図 47 参照)。

### グリッチ・インパルスのピーク振幅

DAC レジスタ内の入力コードが変化したときに、アナログ出力に混入するインパルスのピーク振幅を表します。これは mV で表すグリッチの大きさとして規定され、メジャー・キャリー変化時に、デジタル入力コードが 1 LSB だけ変化したときに測定されます。

### デジタル・フィードスルー

デジタル・フィードスルーは、DAC 出力の更新が行われていないときに、DAC のデジタル入力から DAC のアナログ出力に注入されるインパルスを表します。 $\text{nV}\cdot\text{sec}$  で規定され、データ・バス上のフルスケール・コード変化を使って測定されます。

### ノイズ・スペクトル密度

ノイズ・スペクトル密度は、スペクトル密度( $\text{nV}/\sqrt{\text{Hz}}$ )としてキャラクタライズされる内部発生ランダム・ノイズを表します。DAC にフルスケールを入力し、出力のノイズを測定し、 $\text{nV}/\sqrt{\text{Hz}}$  で表します。ノイズ・スペクトル密度のプロットを図 59 に示します。

**全高調波歪み(THD)**

THD は高調波の rms 値総和と基本波の比です。

AD5761/AD5721 の場合、次式で与えられます。

$$THD \text{ (dB)} = 20 \times \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

ここで、

$V_1$  は基本波の rms 振幅。

$V_2$ 、 $V_3$ 、 $V_4$ 、 $V_5$ 、 $V_6$  は、2 次～6 次の高調波の rms 振幅。

## 動作原理

### D/A コンバータ

AD5761/AD5721 は、1 チャンネル、16/12 ビット電圧出力 D/A コンバータ (DAC) です。AD5761/AD5721 の出力レンジはソフトウェアから選択可能で、次のように設定することができます。

- ユニポーラ出力電圧: 0 V~5 V、0 V~10 V、0 V~16 V、0 V~20 V

- バイポーラ出力電圧: -2.5 V~+7.5 V、±3 V、±5 V、±10 V

データは、シリアル・ペリフェラル・インターフェース (SPI) 互換の 4 線式デジタル・インターフェースを使って 24 ビット・ワード・フォーマットで AD5761/AD5721 に書込まれます。このデバイスには、デイジーチェーン接続およびリードバックを可能にする SDO ピンもあります。

### 伝達関数

DAC 入力コーディングは、ストレート・バイナリまたは 2 の補数 (バイポーラ・レンジのみ) が可能です。伝達関数は次式で与えられます。

$$V_{OUT} = V_{REF} \times \left[ \left( M \times \frac{D}{65,536} \right) - C \right]$$

ここで、

$V_{REF}$  は 2.5 V。

$M$  は与えられた出力レンジのゲイン (表 7 参照)。

$D$  は DAC レジスタにロードされるコードの 10 進数表示です。

12 ビット・デバイスの場合 0~4095。

16 ビット・デバイスの場合 0~65,535。

$C$  は与えられた出力レンジのオフセット (表 7 参照)。

表 7. 様々な出力レンジに対する  $M$  と  $C$  の値

| Range            | M   | C   |

|------------------|-----|-----|

| ±10 V            | 8   | 4   |

| ±5 V             | 4   | 2   |

| ±3 V             | 2.4 | 1.2 |

| -2.5 V to +7.5 V | 4   | 1   |

| 0 V to 20 V      | 8   | 0   |

| 0 V to 16 V      | 6.4 | 0   |

| 0 V to 10 V      | 4   | 0   |

| 0 V to 5 V       | 2   | 0   |

### DAC アーキテクチャ (回路原理)

DAC アーキテクチャは、R/2R レジスタ・ネットワーク DAC とそれに続く出力バッファ・アンプから構成されています。図 62 に、DAC アーキテクチャのブロック図を示します。リファレンス電圧入力はアンプでバッファされた後に DAC に加えられます。

設定可能な出力アンプの出力電圧レンジは、コントロール・レジスタの下位 3 ビット (RA[2:0]) へ書込みを行って選択されます。

図 62. DAC アーキテクチャ

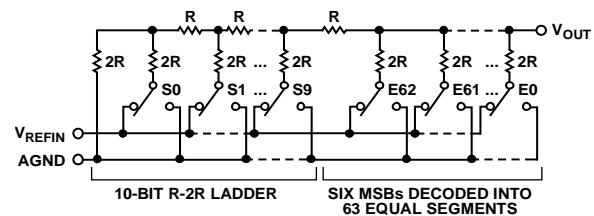

### R/2R レジスタ・ネットワーク DAC

AD5761/AD5721 のアーキテクチャは、2 つの特性が良くマッチングした DAC セクションから構成されています。簡略化した回路図を図 63 に示します。16 ビット・データワードの上位 6 ビットがデコードされて 63 個のスイッチ E0~E62 を駆動します。データワードの下位の 10 ビットは 10 ビット電圧モード R/2R 抵抗ラダー回路のスイッチ S0~S9 を駆動します。

DAC レジスタにロードされるコードにより、 $V_{REFIN}$  とグラウンド (AGND) の間で切り替えられるラダー回路のスイッチ位置が決定されます。ラダーの終わりから出力電圧が得られ、増幅されて選択された出力電圧になります。

図 63. DAC ラダーの構造

### リファレンス・バッファ

AD5761/AD5721 は、外付けのリファレンスを使用して動作します。リファレンスの入力レンジは 2 V~3 V で、仕様性能は 2.5 V で規定しています。この入力電圧は、内部でバッファされた後に DAC コアに加えられます。

### DAC 出力アンプ

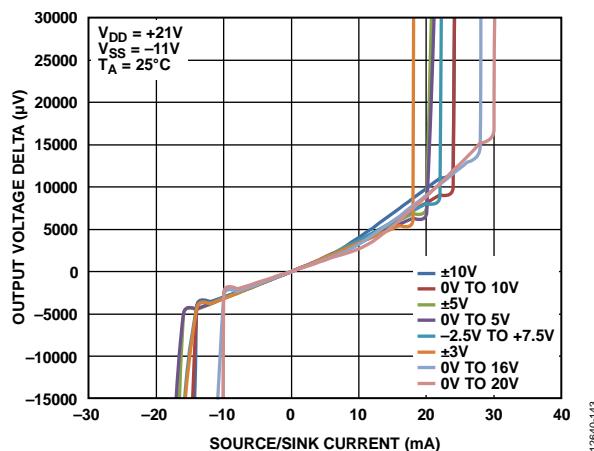

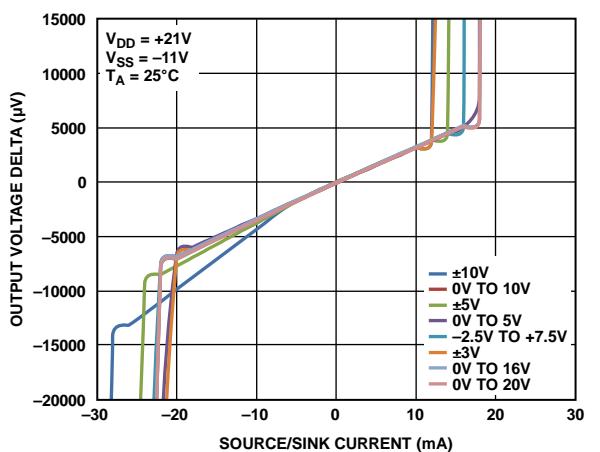

出力アンプは、ユニポーラとバイポーラの出力電圧を発生することができます。AGND に接続された  $2 \text{ k}\Omega$  負荷と、これに並列接続された  $1 \text{ nF}$  の容量負荷を駆動することができます。図 36 に、出力アンプのソース能力とシンク能力を示します。

## シリアル・インターフェース

AD5761/AD5721 の 4 線式 (SYNC, SCLK, SDI, SDO) デジタル・インターフェースは SPI 互換です。書込みシーケンスは SYNC ラインをロー・レベルにすると開始され、SDI ピンからデータワード全体がロードされるまで、このラインをロー・レベルに維持しなければなりません。データは SCLK の立ち下がりエッジ変化で取り込まれます (図 2 参照)。SYNCをハイ・レベルに戻すと、シリアル・データワードが表 10 に示す命令に従ってデコードされます。AD5761/AD5721 には、複数デバイスのデイジーチェーン接続またはレジスタ値のリードバックを可能にする SDO ピンがあります。

### スタンダードアロン動作

このシリアル・インターフェースは、連続および非連続シリアル・クロックで動作します。ただし正しいクロック・サイクル数の間だけ、SYNCをロー・レベルに維持することが可能な場合にのみ、連続 SCLK ソースを使用することができます。

ゲーティド・クロック・モードでは、所定数のクロック・サイクルを含むバースト・クロックを使い、最終クロックの後に SYNCをハイ・レベルにしてデータをラッチする必要があります。SYNCの最初の立ち下がりエッジで書込みサイクルが開始されます。SYNCをハイ・レベルに戻す前に、24 個の立ち下がりクロック・エッジを SCLK に入力する必要があります。24 番目の立ち下がり SCLK エッジの前に SYNCをハイ・レベルにすると、それまで書込まれたデータは無効になります。SYNCをハイ・レベルにする前に、24 個より多くの立ち下がり SCLK エッジを入力した場合も、入力データは無効になります。

入力シフトレジスタは、SYNCの立ち上がりエッジで更新されます。次のシリアル転送を行うときは、SYNCをロー・レベルに戻す必要があります。シリアル・データ転送の終了後、データは自動的に入力シフトレジスタからアドレス指定されたレジスタへ転送されます。書込みサイクルが完了した後、SYNCがハイ・レベルの間に LDACをロー・レベルにすることにより、出力を更新することができます。

### リードバック動作

入力、DAC、コントロールの各レジスタ値は、SDO ピンを使ってリードバックすることができます。図 4 に、レジスタのデコード方法を示します。読み出すレジスタのアドレスを指定すると、次の 24 クロック・サイクルでデータが SDO ピンに出力されます。クロックは、SYNCがロー・レベルの間に入力する必要があります。SYNCがハイ・レベルに戻ると、SDO ピンはハイ・インピーダンス(HiZ)になります。1 個のレジスタを読み出すときは、データ出力時のクロック・タイミングでは NOP コマンドを入力します。複数のレジスタを読み出す場合、アドレス指定された最初のレジスタのデータを出力するクロックのタイミングで、2 番目に読み出すレジスタのアドレス指定を入力することができます。リードバック動作を完了させるためには SDO ピンをイネーブルする必要があります。SDO ピンはデフォルトでイネーブルされています。

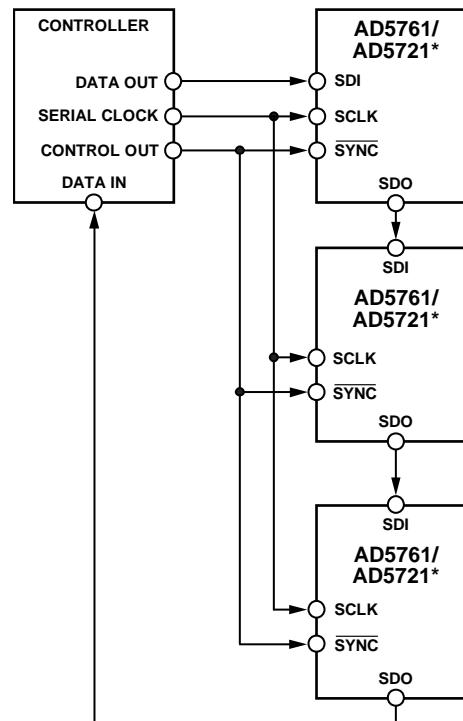

### デイジーチェーン動作

複数のデバイスを使うシステムでは、SDO ピンを使って複数のデバイスをデイジーチェーン接続することができます。このデイジーチェーン・モードは、システム診断とシリアル・インターフェースのライン数の削減に有効です。SYNCの最初の立ち下がりエッジで書込みサイクルが開始されます。SCLK は SYNCがロー・レベルのとき、連続的に入力シフトレジスタのクロックとして入力されます。24 個を超えるクロック・パルスが入力されると、データはシフトレジスタからはみ出して、SDO ピンに出力されます。データは SCLK の立ち上がりエッジ

で出力され、SCLK の立ち下がりエッジで有効になります。

最初のデバイスの SDO をチェーン内にある次のデバイスの SDI 入力に接続すると、複数デバイスの共用インターフェースが構成されます。システム内の各デバイスは、24 個のクロック・パルスを必要とします。したがって、必要な合計クロック・サイクル数は  $24 \times N$  になります。ここで、N はチェーン内の AD5761/AD5721 の合計デバイス数です。すべてのデバイスへのシリアル転送が完了すると、SYNCがハイ・レベルになり、デイジーチェーン内にある各デバイス内の入力データがラッチされて、入力シフトレジスタにさらにデータが入力されるのを防止します。

\*ADDITIONAL PINS OMITTED FOR CLARITY.

12640963

図 64. デイジーチェーンのブロック図

## ハードウェア・コントロール・ピン

### リード DAC 機能(LDAC)

データが DAC の入力レジスタへ転送された後、DAC レジスタと DAC 出力を更新する方法は 2 つあります。SYNCと LDAC の状態に応じて、同期 DAC 更新または非同期 DAC 更新を選択することができます。

#### 同期 DAC 更新

この同期 DAC 更新モードでは、データを入力シフトレジスタへ入力中に LDACをロー・レベルにします。こうすると DAC 出力は、SYNCの立ち上がりエッジで更新されます。

### 非同期 DAC 更新

この非同期 DAC 更新モードでは、データを入力シフトレジスタへ入力中に LDACをハイ・レベルにします。SYNCをハイ・レベルにした後に LDACをロー・レベルにすることにより、DAC 出力が非同期に更新されます。更新は、LDACの立ち下がりエッジで行われるようになります。

### リセット機能(RESET)

AD5761/AD5721 をパワーオン・デフォルト状態にリセットするときは、RESETエラー! ブックマークが定義されていません。ピンをトグルするか、またはソフトウェア・フル・リセット・レジスタを使います(表 26 参照)。

### 非同期クリア機能(CLEAR)

CLEARピンは立ち下がりエッジで駆動する入力で、このピンを使って出力をユーザー設定値にクリアすることができます。コントロール・レジスタのビット 10 とビット 9 に書き込みを行って、あらかじめクリアコード値を設定します(表 11 と表 12 参照)。動作を完了するためには、CLEARを最小時間ロー・レベルに維持する必要があります(図 2 参照)。CLEAR信号がハイ・レベルに戻っても、新しい値が DAC レジスタにロードされるまで出力はクリア値を維持します。

### アラート機能(ALERT)

ALERT ピンがロー・レベルの場合（異状状態の発生）、短絡または停電のいずれが発生したかを知るために、コントロール・レジスタのリードバックが必要で、その中のビット 12 (SC ビット)とビット 11 (BO ビット)の値に応じて判断します(表 15 と表 16 参照)。これらの状態が発生していない場合は、温度が約 150°C を超えていることを示します。

パワーアップ時、ソフトウェア・フル・リセット時、またはハードウェア・リセット時に、ALERT ピンはロー・レベルになります。コントロール・レジスタへ書き込みを行って DAC を設定すると、ALERT ピンはハイ・レベルになります。

チップ温度が約 150°C を超えると、ALERT ピンがロー・レベルになり、ETS ビット値によりデバイスのデジタル電源状態、すなわち内部デジタル電源のパワーオン／パワーダウン状態が表されます。ETS ビットに 0 を設定すると、内部チップ温度が約 150°C を超えても、内部デジタル電源がパワーオンのままであります。ETS ビットに 1 を設定すると、内部チップ温度が約 150°C を超えてデバイスが機能しなくなったり、内部デジタル電源がパワーダウンします(表 11 と表 12 参照)。

デバイスの正常動作のためには、パワーアップ時の AD5761/AD5721 温度は 150°C 未満である必要があります。

## レジスタの詳細

### 入力シフトレジスタ

入力シフトレジスタは24ビット幅です。データは、シリアル・クロック入力 SCLK (最大 50 MHz)の制御のもとで24ビット・ワードとしてMSBが先頭でデバイスに入力されます。入力シフトレジスタは、3ビットのdon't careビット、1ビットの固定値ビット (DB20 = 0)、4ビットのアドレス・ビット、16ビットまたは12ビットのデータワード(それぞれ表8と表9参照)から構成されています。

表 8. AD5761 の 16 ビット入力シフトレジスタ・フォーマット

| MSB            |                |                |      |                  |      |      |      |               | LSB |

|----------------|----------------|----------------|------|------------------|------|------|------|---------------|-----|

| DB23           | DB22           | DB21           | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB0   |     |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | Register address |      |      |      | Register data |     |

<sup>1</sup> X は don't care。

表 9. AD5721 の 12 ビット入力シフトレジスタ・フォーマット

| MSB            |                |                |      |                  |      |      |      |               | LSB               |

|----------------|----------------|----------------|------|------------------|------|------|------|---------------|-------------------|

| DB23           | DB22           | DB21           | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB4   | DB3 to DB0        |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | Register address |      |      |      | Register data | XXXX <sup>1</sup> |

<sup>1</sup> X は don't care。

表 10. 入力シフトレジスタ・コマンド

| Register Address |      |      |      | Command                    |

|------------------|------|------|------|----------------------------|

| DB19             | DB18 | DB17 | DB16 |                            |

| 0                | 0    | 0    | 0    | No operation               |

| 0                | 0    | 0    | 1    | 入力レジスタへ書き込み(更新は無し)         |

| 0                | 0    | 1    | 0    | 入力レジスタから DAC レジスタへデータ転送、更新 |

| 0                | 0    | 1    | 1    | DAC レジスタへ書き込み、更新           |

| 0                | 1    | 0    | 0    | コントロール・レジスタへ書き込み           |

| 0                | 1    | 0    | 1    | No operation               |

| 0                | 1    | 1    | 0    | No operation               |

| 0                | 1    | 1    | 1    | ソフトウェア・データ・リセット            |

| 1                | 0    | 0    | 0    | 予約済みアドレス                   |

| 1                | 0    | 0    | 1    | デイジーチェーン機能の有効／無効           |

| 1                | 0    | 1    | 0    | 入力レジスタのリードバック(読み出し)        |

| 1                | 0    | 1    | 1    | DAC レジスタのリードバック(読み出し)      |

| 1                | 1    | 0    | 0    | コントロール・リードバック(読み出し)        |

| 1                | 1    | 0    | 1    | No operation               |

| 1                | 1    | 1    | 0    | No operation               |

| 1                | 1    | 1    | 1    | ソフトウェア・フル・リセット             |

### コントロール・レジスタ

コントロール・レジスタは、AD5761/AD5721 の動作モードを制御します。表 11 と表 12 に、コントロール・レジスタ・オプションを示します。

パワーアップ時、フル・リセット後、またはハードウェア・リセット後、DAC 出力は  $1\text{ k}\Omega$  の抵抗を介してグラウンドへクランプされ、出力バッファはパワーダウン・モードに入ります。デバイスの設定、グラウンドへのクランプの解除、出力バッファのパワーアップには、コントロール・レジスタへの書き込みが必要です。

動作中に DAC 出力レンジを再設定する場合、デバイスへソフトウェア・フル・リセット・コマンド(表 26)を書込んだ後にコントロール・レジスタへ書き込みを行う必要があります。

表 11. コントロール・レジスタへの書き込み

| MSB              |      |                  |                   |          |     |     |     |     |         |         | LSB |  |  |

|------------------|------|------------------|-------------------|----------|-----|-----|-----|-----|---------|---------|-----|--|--|

| DB[23:21]        | DB20 | DB[19:16]        | DB[15:11]         | DB[10:9] | DB8 | DB7 | DB6 | DB5 | DB[4:3] | DB[2:0] |     |  |  |

| XXX <sup>1</sup> | 0    | Register address | Register data     |          |     |     |     |     |         |         |     |  |  |

| XXX <sup>1</sup> | 0    | 0100             | XXXX <sup>1</sup> | CV[1:0]  | OVR | B2C | ETS | 0   | PV[1:0] | RA[2:0] |     |  |  |

<sup>1</sup> X は don't care。

表 12. コントロール・レジスタの機能

| Bit Name | Description                                                                                                                                                                                      |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CV[1:0]  | CLEAR 時の電圧選択。<br>00: ゼロスケール。<br>01: ミッドスケール。<br>10, 11: フルスケール。                                                                                                                                  |

| OVR      | 5% オーバーレンジのオン／オフ。<br>0: 5% オーバーレンジ出力をディスエーブル。<br>1: 5% オーバーレンジ出力をイネーブル。                                                                                                                          |

| B2C      | バイポーラ・レンジの入力コード。<br>0: バイポーラ出力レンジに対する DAC 入力をストレート・バイナリ・コードとする。<br>1: バイポーラ出力レンジに対する DAC 入力を 2 の補数コードとする。                                                                                        |

| ETS      | サーマル・シャットダウン・アラート。ただし約 150°C (デバイスの最大定格)を上回る温度でデバイスがパワーオンするとアラート機能が正常に動作しないことがあります。<br>0: チップ温度が 150°C を超えて、内部デジタル電源はパワーダウンしない。<br>1: チップ温度が 150°C を超えた場合、内部デジタル電源はパワーダウンする。                     |

| PV[1:0]  | パワーアップ時の出力電圧。<br>00: ゼロスケール。<br>01: ミッドスケール。<br>10, 11: フルスケール。                                                                                                                                  |

| RA[2:0]  | 出力レンジの選択。出力レンジの設定後、デバイスをリセットする必要があります。<br>000: -10 V～+10 V。<br>001: 0 V～+10 V。<br>010: -5 V～+5 V。<br>011: 0 V～5 V。<br>100: -2.5 V～+7.5 V。<br>101: -3 V～+3 V。<br>110: 0 V～16 V。<br>111: 0 V～20 V。 |

表 13. バイポーラ出力レンジで可能なコード

| Straight Binary | Decimal Code | Twos Complement |

|-----------------|--------------|-----------------|

| 1111            | +7           | 0111            |

| 1110            | +6           | 0110            |

| 1101            | +5           | 0101            |

| 1100            | +4           | 0100            |

| 1011            | +3           | 0011            |

| 1010            | +2           | 0010            |

| 1001            | +1           | 0001            |

| 1000            | 0            | 0000            |

| 0111            | -1           | 1111            |

| 0110            | -2           | 1110            |

| 0101            | -3           | 1101            |

| 0100            | -4           | 1100            |

| 0011            | -5           | 1011            |

| 0010            | -6           | 1010            |

| 0001            | -7           | 1001            |

| 0000            | -8           | 1000            |

## コントロール・レジスタのリードバック（レジスタの読み出し）

コントロール・レジスタのリードバック動作では、レジスタ・アドレスを 1100 に設定することにより、コントロール・レジスタ値が取得されます。表 14 に、このコマンドの 24 ビット・シフトレジスタを示します。後側の 16 ビットは don't care ビットです。

次のコマンド・サイクルで、コントロール・レジスタ値が MSB を先頭にして SDO ピンからシフト出力されます。表 15 に SDO ピンからの 24 ビット・データ読み出しのフォームを示します。DB23 が最初にシフト出力されるビットです。

表 14. コントロール・レジスタのリードバック、24 ビット・シフトレジスタから SDI ピンへ

| MSB              |      |                  |           | LSB       |      |               |           |

|------------------|------|------------------|-----------|-----------|------|---------------|-----------|

| DB[23:21]        | DB20 | DB[19:16]        | DB[15:10] | DB[23:21] | DB20 | DB[19:16]     | DB[15:10] |

| XXX <sup>1</sup> | 0    | Register address |           |           |      | Register data |           |

| XXX <sup>1</sup> | 0    | 1100             |           |           |      | Don't care    |           |

<sup>1</sup> X は don't care。

表 15. コントロール・レジスタのリードバック、SDO ピンからの 24 ビット・データ読み出し

| MSB              |      |                  |                  |      |      |          |     |     |     |                |         |         |               | LSB |  |

|------------------|------|------------------|------------------|------|------|----------|-----|-----|-----|----------------|---------|---------|---------------|-----|--|

| DB[23:21]        | DB20 | DB[19:16]        | DB[15:13]        | DB12 | DB11 | DB[10:9] | DB8 | DB7 | DB6 | DB5            | DB[4:3] | DB[2:0] |               |     |  |

| XXX <sup>1</sup> | 0    | Register address |                  |      |      |          |     |     |     |                |         |         | Register data |     |  |

| XXX <sup>1</sup> | 0    | 1100             | XXX <sup>1</sup> | SC   | BO   | CV[1:0]  | OVR | B2C | ETS | X <sup>1</sup> | PV[1:0] | RA[2:0] |               |     |  |

<sup>1</sup> X は don't care。

表 16. リードバック・コントロール・レジスタのビット説明

| Bit Name | Description                                                                          |

|----------|--------------------------------------------------------------------------------------|

| SC       | 短絡状態。SC ビットは、各コントロール・レジスタへの書き込みでリセットされます。<br>0: 短絡状態は検出されていません。<br>1: 短絡状態が検出されています。 |

| BO       | 停電状態。BO ビットは、各コントロール・レジスタへの書き込みでリセットされます。<br>0: 停電状態が検出されていません。<br>1: 停電状態が検出されています。 |

## 入力レジスタから DAC レジスタを更新

DAC レジスタ更新機能は、DAC レジスタに入力レジスタに保存されたデータを転送し、DAC 出力電圧を更新します。この動作は、ソフトウェア LDAC と同じです。表 17 に、データを DAC レジスタへ書き込む方法を示します。

表 17. 入力レジスタから DAC レジスタを更新

| MSB            |                |                |      |                  |      |      |      | LSB         |               |

|----------------|----------------|----------------|------|------------------|------|------|------|-------------|---------------|

| DB23           | DB22           | DB21           | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB0 |               |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | Register address |      |      |      |             | Register data |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | 0010             |      |      |      |             | Don't care    |

<sup>1</sup> X は don't care。

## DAC レジスタのリードバック

DAC レジスタのリードバック動作では、レジスタ・アドレスを 1011 に設定することにより、DAC レジスタ値が取得されます。表 18 に、このコマンドに対する 24 ビット・シフトレジスタを示します。次のコマンド・サイクルで、DAC レジスタ値が MSB ファーストで SDO ピンからシフト出力されます。表 19 に SDO ピンからの 24 ビット・データ読み出しを示します。DB23 が最初にシフト出力されるビットです。

表 18. DAC レジスタのリードバック、24 ビット・シフトレジスタから SDI ピンへ

| MSB            |                |                |      |                  |      |      |      | LSB         |               |

|----------------|----------------|----------------|------|------------------|------|------|------|-------------|---------------|

| DB23           | DB22           | DB21           | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB0 |               |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | Register address |      |      |      |             | Register data |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | 1011             |      |      |      |             | Don't care    |

<sup>1</sup> X は don't care。

表 19. DAC レジスタのリードバック、SDO ピンからの 24 ビット・データ読出し

| MSB            |                |                |      |                  |      |      |      | LSB         |

|----------------|----------------|----------------|------|------------------|------|------|------|-------------|

| DB23           | DB22           | DB21           | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB0 |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | Register address |      |      |      |             |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | 1011             |      |      |      |             |

<sup>1</sup> X は don't care。

## DAC レジスタの書き込みと更新

DAC レジスタ (レジスタ・アドレス 0011) の書き込みと更新では、LDAC の状態と無関係に、入力レジスタと DAC レジスタを入力シフトレジスタから入力されたデータワードで更新します。

レジスタ・アドレスを 0001 に設定すると、入力レジスタに入力シフトレジスタからのデータが書き込まれます。SDI ピンからは MSB ファーストで入力されます。

表 20. DAC レジスタの書き込みと更新

| MSB            |                |                |      |                  |      |      |      | LSB         |

|----------------|----------------|----------------|------|------------------|------|------|------|-------------|

| DB23           | DB22           | DB21           | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB0 |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | Register address |      |      |      |             |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | 0001             |      |      |      |             |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | 0011             |      |      |      |             |

<sup>1</sup> X は don't care。

## 入力レジスタのリードバック

入力レジスタのリードバック動作では、レジスタ・アドレスを 1010 に設定することにより、入力レジスタ値が取得されます。表 21 に、このコマンドに対する 24 ビット・シフトレジスタを示します。次のコマンド・サイクルで、入力レジスタ値が MSB を先頭にして SDO ピンからシフト出力されます。表 22 に SDO ピンからの 24 ビット・データ読出しを示します。DB23 が最初にシフト出力されるビットです。

表 21. 入力レジスタのリードバック、24 ビット・シフトレジスタから SDI ピンへ

| MSB            |                |                |      |                  |      |      |      | LSB         |

|----------------|----------------|----------------|------|------------------|------|------|------|-------------|

| DB23           | DB22           | DB21           | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB0 |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | Register address |      |      |      |             |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | 1010             |      |      |      |             |

<sup>1</sup> X は don't care。

表 22. 入力レジスタのリードバック、SDO ピンからの 24 ビット・データ読出し

| MSB            |                |                |      |                  |      |      |      | LSB         |

|----------------|----------------|----------------|------|------------------|------|------|------|-------------|

| DB23           | DB22           | DB21           | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB0 |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | Register address |      |      |      |             |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | 1010             |      |      |      |             |

<sup>1</sup> X は don't care。

## ディスエーブル・デイジーチェーン機能

この機能が不要な場合、SDO バッファの消費電力を節約するためデイジーチェーン機能をディスエーブルすることができます(表 23 参照)。ディスエーブルすると、SDO ピンがスリーステートになるためリードバック要求は受け付けません。

表 23. ディスエーブル・デイジーチェーン機能レジスタ

| MSB            |                |                |      |                  |      |      |      | LSB         |               |

|----------------|----------------|----------------|------|------------------|------|------|------|-------------|---------------|

| DB23           | DB22           | DB21           | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB1 | DB0           |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    | Register address |      |      |      |             | Register data |

|                |                |                |   |      |            |     |

|----------------|----------------|----------------|---|------|------------|-----|

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0 | 1001 | Don't care | DDC |

|----------------|----------------|----------------|---|------|------------|-----|

<sup>1</sup> X は don't care。

表 24. ディスエーブル・デイジーチェーンのビット説明

| Bit Name | Description                                                                                                                               |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| DDC      | DDC は、デバイスのデイジーチェーン機能をイネーブルするかディスエーブルするかを決定します。デフォルトで、デイジーチェーン機能はイネーブルされています。<br>0: デバイスのデイジーチェーン機能をイネーブル。<br>1: デバイスのデイジーチェーン機能をディスエーブル。 |

## ソフトウェア・データ・リセット

AD5761/AD5721 はソフトウェアからゼロスケール、ミッドスケール、またはフルスケールにリセットすることができます (表 25 参照)。デバイスをリセットする値は、PV1 ビットと PV0 ビットで指定されます。これらのビットはコントロール・レジスタ・コマンドへの書き込みで設定されます (表 11 と表 12 参照)。

表 25. ソフトウェア・データ・リセット・レジスタ

| MSB            | DB23           | DB22           | DB21 | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB0   | LSB |

|----------------|----------------|----------------|------|------|------------------|------|------|------|---------------|-----|

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    |      | Register address |      |      |      | Register data |     |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    |      | 0111             |      |      |      | Don't care    |     |

<sup>1</sup> X は don't care。

## ソフトウェア・フル・リセット

デバイスは、ソフトウェアから完全にリセットすることもできます (表 26 参照)。レジスタ・アドレスを 1111 に設定すると、デバイスはパワーアップのデフォルト状態で動作し、出力が AGND にクランプされ、出力バッファがパワーダウンします。デバイスの設定、グラウンドへの 1 kΩ 抵抗クランプの解除、出力バッファのパワーアップには、コントロール・レジスタへの書き込みが必要です。

通常動作で DAC 出力レンジを再設定すると、ソフトウェア・フル・リセット・コマンドも発行されます。

表 26. ソフトウェア・フル・リセット・レジスタ

| MSB            | DB23           | DB22           | DB21 | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 to DB0   | LSB |

|----------------|----------------|----------------|------|------|------------------|------|------|------|---------------|-----|

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    |      | Register address |      |      |      | Register data |     |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    |      | 1111             |      |      |      | Don't care    |     |

<sup>1</sup> X は don't care。

## NOP レジスタ

NOP レジスタは無視され、デバイス状態は変化しません (表 27 参照)。

表 27. NOP レジスタ

| MSB            | DB23           | DB22           | DB21 | DB20 | DB19                     | DB18 | DB17 | DB16 | DB15 to DB0   | LSB |

|----------------|----------------|----------------|------|------|--------------------------|------|------|------|---------------|-----|

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    |      | Register address         |      |      |      | Register data |     |

| X <sup>1</sup> | X <sup>1</sup> | X <sup>1</sup> | 0    |      | 0000/0101/0110/1101/1110 |      |      |      | Don't care    |     |

<sup>1</sup> X は don't care。

## アプリケーション情報

### 代表的な動作回路

図 65 に、AD5761/AD5721 の代表的な動作回路を示します。この高精度 16/12 ビット DAC に必要な外付け部品は、電源ピンのデカッピング・コンデンサと電源電圧だけです。AD5761/AD5721 はリファレンス電圧とリファレンス・バッファを内蔵しているため、外付けバイポーラ・リファレンスとそれに対応するバッファが不要になり、コストとボード・スペースの削減が可能です。

図 65 では、 $V_{DD}$  は 15 V に、 $V_{SS}$  は -15 V に、それぞれ接続されていますが、 $V_{DD}$  と  $V_{SS}$  はそれぞれ 4.75 V~30 V および -16.5 V~0 V の電源で動作することができます。

### 高精度リファレンス電圧の選択

フル動作温度範囲で AD5761/AD5721 の最適性能を実現するためには、外付けリファレンスの使用を必要とするアプリケーションがあります。リファレンス電圧の誤差はデバイス出力に影響を与えるため同じ選択を行うように注意する必要があります。

高精度アプリケーションに対するリファレンス電圧の選択で考慮すべき誤差原因としては、初期精度、出力電圧の温度係数、長時間ドリフト、出力電圧ノイズの 4 つがあります。

外付けリファレンスの出力電圧の初期精度誤差により、DAC 内でフルスケール誤差が発生します。これらの誤差を小さくするため、初期精度誤差の小さいリファレンス電圧の使用が望まれます。ADR421 のような出力調整機能を持つリファレンス電圧を選択すると、リファレンス電圧を公称値以外の電圧に設定することにより、システム誤差を調節することができます。この調整機能は、誤差をなくすため室温で使用することもできます。

長時間ドリフトは、リファレンス出力電圧の時間的なドリフトの大きさを表します。厳しい長時間ドリフト仕様を持つリファレンス電圧を使うと、ソリューション全体が製品寿命を通して比較的安定します。

リファレンス出力電圧の温度係数は、ゲイン誤差と TUE に影響を与えます。DAC 出力電圧の周囲状態に対する温度依存性を小さくするためには、厳しい温度係数仕様を持つリファレンス電圧を選択する必要があります。

比較的低いノイズが要求される高精度アプリケーションでは、リファレンス電圧の出力ノイズを考慮する必要があります。必要とされるシステム分解能に対して実用的な程度に出力ノイズ電圧が小さいリファレンス電圧を選択することは重要です。ADR4525 のような高精度リファレンス電圧は、0.1~10 Hz の領域で低い出力ノイズ・レベルを持っています。ただし、回路帯域幅が広くなると、出力ノイズを小さくするために、リファレンス出力にフィルタが必要になることがあります。

NOTES

1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

図 65. 代表的な動作回路

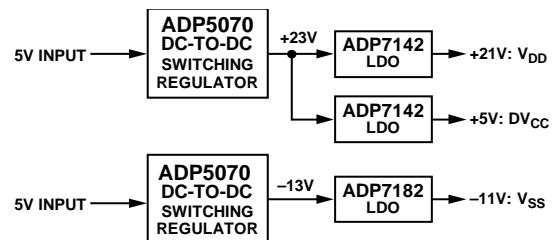

### 電源の注意事項

AD5761/AD5721 には、DAC で 8 種類の出力電圧レンジを使用できるようにするために、 $V_{DD} = 11$  V、 $V_{SS} = -21$  V、 $DV_{CC} = 5$  V の 3 種類の電源を供給する必要があります。

最適な電源効率と低ノイズ性能を必要とするアプリケーションに対しては、5 V 入力レールを 2 種類の中間電源 (+23 V と -13 V) に変換する ADP5070 スイッチング・レギュレータの使用が推奨されます。これらの中間電源は、非常に低いノイズの低ドロップアウト (LDO) レギュレータ (ADP7142 と ADP7182) でさらにレギュレーションされます。図 66 に推奨方法を示します。

図 66. ADP7142 と ADP7182 によるポスト・レギュレーション

### 評価用ボード

デバイスの高性能を最小の労力で評価することを支援するためには AD5761R の評価用ボードを提供しています。この評価用ボードは AD5761/AD5721 の評価に使用することができます。AD5761R 評価キットには、実装/テスト済みの AD5761R プリント回路ボード (PCB) が含まれています。評価用ボードは、PC の USB ポートにインターフェースされます。評価用ボードでは、AD5761R の設定を容易にするソフトウェアを使うことができます。評価用ボードの動作を詳しく説明する EVAL-AD5761RSDZ ユーザー・ガイドを提供しています。

表 28. AD5761/AD5721 と組み合わせて使用する推奨高精度リファレンス

| Part No. | Initial Accuracy<br>(mV Maximum) | Long-Term Drift (ppm<br>Typical) | Temperature Drift<br>(ppm/°C Maximum) | 0.1 Hz to 10 Hz Noise<br>( $\mu$ V p-p Typical) |

|----------|----------------------------------|----------------------------------|---------------------------------------|-------------------------------------------------|

| ADR03    | $\pm 2.5$                        | 50                               | 3                                     | 6                                               |

| ADR421   | $\pm 1$                          | 50                               | 3                                     | 1.75                                            |

| ADR431   | $\pm 1$                          | 40                               | 3                                     | 3.5                                             |

| ADR441   | $\pm 1$                          | 50                               | 3                                     | 1.2                                             |

| ADR4525  | 1                                | 25                               | 2                                     | 1.25                                            |

## 外形寸法

COMPLIANT TO JEDEC STANDARDS MO-153-AB

図 67. 16 ピン薄型シルリンク・スモール・アウトライン・パッケージ[TSSOP]

(RU-16)

寸法: mm

## オーダー・ガイド

| Model <sup>1</sup> | Resolution (Bits) | Temperature Range | INL (LSB) | Package Description | Package Option |

|--------------------|-------------------|-------------------|-----------|---------------------|----------------|

| AD5721BRUZ         | 12                | -40°C to +125°C   | ±0.5      | 16-Lead TSSOP       | RU-16          |

| AD5721BRUZ-RL7     | 12                | -40°C to +125°C   | ±0.5      | 16-Lead TSSOP       | RU-16          |

| AD5761BRUZ         | 16                | -40°C to +125°C   | ±2        | 16-Lead TSSOP       | RU-16          |

| AD5761BRUZ-RL7     | 16                | -40°C to +125°C   | ±2        | 16-Lead TSSOP       | RU-16          |

<sup>1</sup> Z = RoHS 準拠製品。