# シリアル・インターフェース、12ビット 高帯域幅乗算DAC

**AD5444**

### 特長

INL: ±0.5LSB

動作電源電圧: 2.5~5.5V リファレンス入力: ±10V

拡張工業用温度範囲(3):-40~+125℃

パッケージ:10ピンMSOP

ピン・コンパチブルな12ビット電流出力DAC

50MHzのシリアル・インターフェース

単調増加性を保証

4象限乗算機能

電圧低下検出機能付きのパワーオン・リセット

消費電流:0.4 μ A以下(typ)

### アプリケーション

携帯型バッテリ駆動のアプリケーション

波形発生器

アナログ信号処理

計測器

プログラマブルなアンプおよび減衰器デジタル制御によるキャリブレーション

プログラマブルなフィルタおよび発振器

コンポジット・ビデオ

超音波機器

ゲイン、オフセット、電圧のトリミング

車載レーダー

### 概要

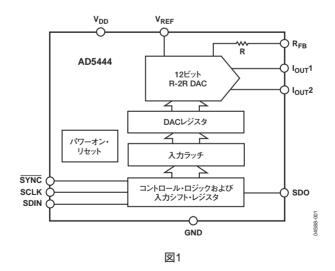

AD5444<sup>1</sup>は、CMOS 12ビットの電流出力D/Aコンバータです。2.5~5.5Vの電源で動作するため、バッテリ駆動のアプリケーションなどに適しています。

このDACは、SPI®、QSPI™、MICROWIRE™、大部分のDSPインターフェース規格と互換性を持つダブル・バッファ付き3線式シリアル・インターフェースを採用しています。パワーアップ時には、内部のシフト・レジスタとラッチにゼロが設定され、DAC出力はゼロスケールになります。CMOSサブミクロン・プロセスで製造されているため、優れた4象限乗算機能を提供します。

フルスケール出力電流は、外部リファレンス入力電圧 ( $V_{REF}$ )により決定されます。2.5~5.5Vの単電源で動作するにもかかわらず、リファレンスとして $\pm 10V$ を入力することができます。内蔵の帰還抵抗 ( $R_{FB}$ )を外付けの電流/電圧 (I/V) 変換用高精度アンプと組み合わせて使用すると、温度トラッキング機能とフルスケール電圧出力が可能になります。AD5444 DACは 小型の 10ピン MSOPパッケージを採用しており、AD5425/AD5432/AD5443ファミリーのDACとピン・コンパチブルです。

### 機能ブロック図

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関いて、あるいはその利用によって生じる第三者の特許やその他の権利の侵害に関いて一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。日本語データシートは、REVISIONが古い場合があります。最新の内容については、英語版をご参照ください。 ©2005 Analog Devices, Inc. All rights reserved.

REV.0

| 本 社 / 東京都港区海岸1-16-1 電話03(5402)8200 〒105-6891 ニューピア竹芝サウスタワービル

大阪営業所 / 大阪府大阪市淀川区宮原3-5-36 電話0( 6350 )6868(代) 〒532-0003 新大阪MTビル2号

<sup>1</sup>米国特許番号5,689,257

## 目次

| 仕様3                  | DACをデバイダまたはプログラマブル・ゲイン素子として     |

|----------------------|---------------------------------|

| タイミング仕様 ・・・・・・5      | 使用する場合・・・・・・16                  |

| 絶対最大定格 · · · · · · 6 | アンプの選択・・・・・・17                  |

| ESDに関する注意 ······6    | リファレンスの選択・・・・・・17               |

| ピン配置および機能の説明 ・・・・・・7 | シリアル・インターフェース・・・・・・19           |

| 用語の説明 ・・・・・・8        | マイクロプロセッサとのインターフェース・・・・・・・20    |

| 代表的な性能特性 ・・・・・・9     | PCボードのレイアウトと電源デカップリング ······22  |

| 機能の説明・・・・・・14        | DAC用評価用ボード · · · · · · · · · 22 |

| DAC部 · · · · · · 14  | 評価用ボードの電源・・・・・・22               |

| 回路動作・・・・・・14         | AD54xxシリーズのラインアップ ・・・・・・26      |

| 単電源アプリケーション・・・・・・16  | 外形寸法・・・・・・27                    |

| ゲインの増加・・・・・・16       | オーダー・ガイド・・・・・・27                |

2

### 改訂履歴

10/04—Revision 0: Initial Version

# 仕様

Yバージョンの温度範囲:-40~+125℃。

特に指定のない限り、 $V_{DD}$ =2.5~5.5V、 $V_{REF}$ =10V、 $I_{OUT}$ 2=0V。すべての仕様は $T_{MIN}$ ~ $T_{MAX}$ で規定。特に指定のない限り、DC性能はOP177を、AC性能はAD8038を使用して測定。

#### 表1

| パラメータ                                   | Min            | Тур        | Max       | 単位         | 条件                                                                        |

|-----------------------------------------|----------------|------------|-----------|------------|---------------------------------------------------------------------------|

| 静的性能                                    |                |            |           |            |                                                                           |

| 分解能                                     |                |            | 12        | ビット        |                                                                           |

| 相対精度                                    |                |            | ±0.5      | LSB        |                                                                           |

| 微分非直線性(INL)                             |                |            | ±1        | LSB        | 単調増加性を保証                                                                  |

| 総合未調整誤差(TUE)                            |                |            | ±1        | LSB        | THE PRINCE OF THE                                                         |

| ゲイン誤差                                   |                |            | $\pm 0.5$ | LSB        |                                                                           |

| ゲイン誤差温度係数                               |                | ±5         | ±0.5      |            |                                                                           |

|                                         |                | ±3         | ±1        | ppm FSR/°C | = 7-00000 T −25°C I 1                                                     |

| 出力リーク電流                                 |                |            |           | nA         | データ=0x0000、T <sub>A</sub> =25℃、I <sub>OUT</sub> 1                         |

|                                         |                |            | $\pm 10$  | nA         | データ= $0x0000$ 、 $T_A=-40~+125$ °C、                                        |

|                                         |                |            |           |            | I <sub>OUT</sub> 1                                                        |

| リファレンス入力範囲                              |                | <b>⊥10</b> |           | V          |                                                                           |

|                                         |                | ±10        |           |            | 1 + 1 + 1 + ma                                                            |

| V <sub>REF</sub> 入力抵抗                   | 7              | 9          | 11        | kΩ         | 入力抵抗TC=−50ppm/℃                                                           |

| R <sub>FB</sub> 帰還抵抗                    | 7              | 9          | 11        | kΩ         | 入力抵抗TC=−50ppm/℃                                                           |

| 入力容量                                    |                |            |           |            |                                                                           |

| ゼロスケール・コード                              |                | 18         | 22        | pF         |                                                                           |

| フルスケール・コード                              |                | 18         | 22        | pF         |                                                                           |

| デジタル入出力1                                |                |            |           |            |                                                                           |

| 入力ハイレベル電圧 $(V_{ m IH})$                 | 2.0            |            |           | V          | $V_{DD}=3.6\sim5V$                                                        |

|                                         | 1.7            |            |           | V          | $V_{DD} = 2.5 \sim 3.6 V$                                                 |

| 入力ローレベル電圧 $(\mathbf{V}_{\mathrm{IL}})$  |                |            | 0.8       | V          | $V_{DD} = 2.7 \sim 5.5 V$                                                 |

|                                         |                |            | 0.7       | V          | $V_{DD} = 2.5 \sim 2.7 V$                                                 |

| 出力ハイレベル電圧(V <sub>OH</sub> )             | $V_{DD}-1$     |            |           | V          | $V_{DD}$ =4.5V $\sim$ 5V, $I_{SOURCE}$ =200 $\mu$ A                       |

|                                         | $V_{DD} = 0.5$ | 5          |           | V          | $V_{DD} = 2.5 \text{V} \sim 3.6 \text{V}, I_{SOURCE} = 200 \mu \text{ A}$ |

| 出力ローレベル電圧 $(V_{OL})$                    |                |            | 0.4       | V          | $V_{DD} = 4.5 \text{V} \sim 5 \text{V}, I_{SINK} = 200 \mu \text{ A}$     |

|                                         |                |            | 0.4       | V          | $V_{DD} = 2.5 V \sim 3.6 V$ , $I_{SINK} = 200 \mu A$                      |

| 入力リーク電流 (I <sub>IL</sub> )              |                |            | $\pm 1$   | nA         | $T_A=25$ °C                                                               |

|                                         |                |            | $\pm 10$  | nA         | $T_{A} = -40 \sim +125 ^{\circ} \text{C}$                                 |

| 入力容量                                    |                |            | 10        | pF         | The state of                                                              |

| 動的性能1                                   |                |            | -         | r          |                                                                           |

| リファレンス入力帯域幅                             | 10             |            |           | MHz        | V <sub>REF</sub> =±3.5V、DACに全ビット「1」をロート                                   |

| 出力電圧セトリング時間                             |                |            |           | 11111      | V <sub>REF</sub> =10V, R <sub>LOAD</sub> =100Ω, DACラッチ                    |

| 四万电压工厂,不可同                              |                |            |           |            | に全ビット「0」と「1」を交互にロード                                                       |

| フルスケールの±1mV以内                           |                | 100        | 110       | ns         | に至られて切られると大型にロート                                                          |

| フルスケールの±4mV以内                           |                | 24         | 40        |            |                                                                           |

|                                         |                |            |           | ns         |                                                                           |

| フルスケールの±16mV以内                          |                | 16         | 33        | ns         | た。カーコーコン同7式II土田                                                           |

| デジタル遅延                                  |                | 20         | 40        | ns         | インターフェース遅延時間                                                              |

| 10%から90%へのセトリング時間                       |                | 10         | 30        | ns         | 立上がりおよび立下がり時間、VREF=10V                                                    |

| ~ · · · · · · · · · · · · · · · · · · · |                | 2          |           |            | $R_{LOAD}=100\Omega$                                                      |

| デジタルからアナログへのグリッチ・                       |                | 2          |           | nV-s       | メジャー・キャリー付近での1 LSB変化、                                                     |

| インパルス                                   |                |            |           |            | V <sub>REF</sub> =0V                                                      |

| 出力容量                                    |                |            |           |            |                                                                           |

| $I_{OUT}1$                              |                | 13         |           | pF         | DACラッチに全ビット「0」をロード                                                        |

|                                         |                | 28         |           | pF         | DACラッチに全ビット「1」をロード                                                        |

| $I_{OUT}2$                              |                | 18         |           | pF         | DACラッチに全ビット「0」をロード                                                        |

|                                         |                | 5          |           | pF         | DACラッチに全ビット「1」をロード                                                        |

| デジタル・フィードスルー                            |                | 0.5        |           | nV-s       | <del>CS</del> がハイレベルで、全ビット「0」と全ビット                                        |

|                                         |                |            |           |            | 「1」を交互にロードしたときのDAC出力へ                                                     |

|                                         |                |            |           |            | のフィードスルー                                                                  |

| パラメータ                              | Min | Тур | Max   | 単位      | 条件                                                       |

|------------------------------------|-----|-----|-------|---------|----------------------------------------------------------|

| アナログTHD                            |     | 83  |       | dB      | $V_{REF}$ =3.5 $V_p$ - $p$ 、全ビット $\lceil 1 \rceil$ をロード、 |

|                                    |     |     |       |         | f=1kHz                                                   |

| デジタルTHD                            |     |     |       |         | クロック=1MHz、V <sub>REF</sub> =3.5V                         |

| 50kHz f <sub>OUT</sub>             |     | 71  |       | dB      |                                                          |

| 20kHz f <sub>OUT</sub>             |     | 77  |       | dB      |                                                          |

| 出力ノイズ・スペクトル密度                      |     | 25  |       | nV/√Hz  | @ 1kHz                                                   |

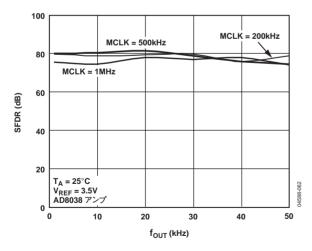

| SFDR性能(ワイドバンド)                     |     |     |       |         | クロック=10MHz、V <sub>REF</sub> =3.5V                        |

| 50kHz f <sub>OUT</sub>             |     | 78  |       | dB      |                                                          |

| 20kHz f <sub>OUT</sub>             |     | 74  |       | dB      |                                                          |

| SFDR性能(ナローバンド)                     |     |     |       |         | クロック=1MHz、V <sub>REF</sub> =3.5V                         |

| $50 \mathrm{kHz}~\mathrm{f_{OUT}}$ |     | 87  |       | dB      |                                                          |

| 20kHz f <sub>OUT</sub>             |     | 85  |       | dB      |                                                          |

| 相互変調歪み                             |     | 79  |       | dB      | $f_1$ =20kHz、 $f_2$ =25kHz、クロック=1MHz                     |

|                                    |     |     |       |         | $V_{REF}=3.5V$                                           |

| 電源条件                               |     |     |       |         |                                                          |

| 電源電圧範囲                             | 2.5 |     | 5.5   | V       |                                                          |

| $I_{DD}$                           |     | 0.4 | 10    | $\mu$ A | T <sub>A</sub> =-40~+125°C、ロジック入力=0V                     |

|                                    |     |     |       |         | またはV <sub>DD</sub>                                       |

|                                    |     |     | 0.6   | μΑ      | $T_A=25$ ℃、ロジック入力 $=0$ Vまたは $V_{DD}$                     |

| 電源電圧変動感度1                          |     |     | 0.001 | %/%     | $\Delta V_{DD} = \pm 5\%$                                |

<sup>「</sup>設計および特性評価により保証。出荷テストは実施していません。

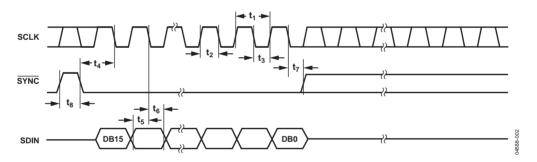

## タイミング特性

Yバージョンの温度範囲:-40~+125℃(図2参照)

設計および特性評価により保証。出荷テストは実施していません。

すべての入力信号は $tr=tf=1ns(V_{DD}$ の $10\sim90\%)$ で規定し、 $(V_{IL}+V_{IH})/2$ の電圧レベルからの時間とします。

$V_{REF}=5V$ ,  $I_{OUT}2=0V$

特に指定のない限り、すべての仕様はT<sub>MIN</sub>~T<sub>MAX</sub>で規定。

#### 表2

| パラメータ             | V <sub>DD</sub> =4.5~5.5V | V <sub>DD</sub> =2.5~5.5V | 単位        | 条件/コメント                    |

|-------------------|---------------------------|---------------------------|-----------|----------------------------|

| f <sub>SCLK</sub> | 50                        | 50                        | MHz (max) | 最大クロック周波数                  |

| $t_1$             | 20                        | 20                        | ns (min)  | SCLKサイクル時間                 |

| $t_2$             | 8                         | 8                         | ns (min)  | SCLKのハイレベル時間               |

| $t_3$             | 8                         | 8                         | ns (min)  | SCLKのローレベル時間               |

| $t_4$             | 8                         | 8                         | ns (min)  | SYNC の立下がりエッジからSCLKのアクティブ・ |

|                   |                           |                           |           | エッジまでのセットアップ時間             |

| t <sub>5</sub>    | 5                         | 5                         | ns (min)  | データのセットアップ時間               |

| $t_6$             | 4.5                       | 4.5                       | ns (min)  | データのホールド時間                 |

| $t_7$             | 5                         | 5                         | ns (min)  | SYNC の立上がりエッジからSCLKのアクティブ・ |

|                   |                           |                           |           | エッジまで                      |

| $t_8$             | 30                        | 30                        | ns (min)  | SYNC の最小ハイレベル時間            |

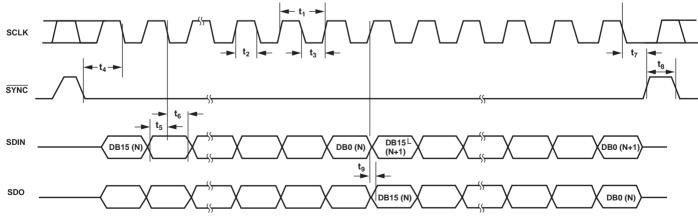

| t9                | 23                        | 30                        | ns (min)  | SCLKのアクティブ・エッジからSDOの有効まで   |

図2. スタンドアロン・タイミング図

代わりに、コントロール・ビットの指定により、SCLKの立上がリエッジでデータを入力シフト・レジスタに入力できます。この場合、データはSCLKの立下がリエッジでSDOから出力されます。上記のSCLKを反転した場合のタイミング。

図3. デイジーチェーン・タイミング図

4588.003

### 絶対最大定格

特に指定のない限り、T<sub>A</sub>=25℃。 100mAまでの過渡電流ではSCRラッチ・アップは生じません。

#### 表3

| パラメータ                          | 定格                         |

|--------------------------------|----------------------------|

| GNDに対するVDD                     | -0.3~+7V                   |

| GNDに対する $V_{REF}$ 、 $R_{FB}$   | −12~+12V                   |

| GNDに対するIout1、Iout2             | −0.3∼+7V                   |

| ロジック入力および出力「                   | $-0.3 \sim V_{DD} + 0.3 V$ |

| 電源ピン以外の全ピンの入力電流                | ±10mA                      |

| 動作温度範囲                         |                            |

| 拡張工業用(Yバージョン)                  | -40∼+125°C                 |

| 保存温度範囲                         | -65~+150°C                 |

| ジャンクション温度                      | 150℃                       |

| $10$ ピンMSOPの $\theta_{JA}$ 熱抵抗 | 206℃/W                     |

| リードピン温度(ハンダ処理、10秒)             | 300℃                       |

| 赤外線リフロー時のピーク温度(20秒以下)          | 235℃                       |

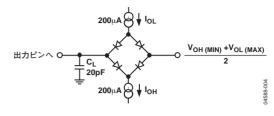

図4. SDOタイミング仕様に対する負荷回路

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。1つのパラメータでも絶対最大定格を超えると、デバイスに影響を与えます。

#### 注意

ESD(静電放電)の影響を受けやすいデバイスです。人体や試験機器には4,000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣下や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

REV.0

6

$<sup>^1</sup>$  SCLK、 $\overline{\text{SYNC}}$ 、DINでの過電圧は、内部ダイオードでクランプされます。

## ピン配置および機能の説明

図5. MSOP(RM-10)のピン配置

#### 表4. ピン機能の説明

| ピン番号 | 記号                 | 機能                                                         |

|------|--------------------|------------------------------------------------------------|

| 1    | I <sub>OUT</sub> 1 | DACの電流出力                                                   |

| 2    | I <sub>OUT</sub> 2 | DACのアナログ・グラウンド。このピンは通常、システムのアナログ・グラウンドに接続されます。             |

| 3    | GND                | グラウンド・ピン                                                   |

| 4    | SCLK               | シリアル・クロック入力。デフォルトでは、データはシリアル・クロック入力の立下がりエッジでシフト・レジスタに入力され  |

|      |                    | ます。代わりに、シリアル・コントロール・ビットを使って、SCLKの立上がりエッジでデータがシフト・レジスタに入力され |

|      |                    | るように、デバイスを設定することもできます。                                     |

| 5    | SDIN               | シリアル・データ入力。データはシリアル・クロック入力のアクティブ・エッジで16ビット入力レジスタに入力されます。パ  |

|      |                    | ワーアップ時、デフォルトでは、データはSCLKの立下がりエッジでシフト・レジスタに入力されます。コントロール・ビッ  |

|      |                    | トを使って、アクティブ・エッジを立上がりエッジに変更することができます。                       |

| 6    | SYNC               | コントロール入力(アクティブ・ロー)。これは、入力データに対するフレーム同期信号です。 SYNC をローレベルにす  |

|      |                    | ると、次のクロックのアクティブ・エッジでデータがシフト・レジスタにロードされます。出力データは、SYNCの立上がり  |

|      |                    | エッジで更新されます。                                                |

| 7    | SDO                | シリアル・データ出力。このピンを使うと、複数デバイスをデイジーチェーン接続することができます。デフォルトでは、    |

|      |                    | データはSCLKの立下がりエッジでシフト・レジスタに入力され、SCLKの立上がりエッジでSDOから出力されます。デ  |

|      |                    | ータは常に、データをシフト・レジスタにローディングするエッジと反対のエッジで出力されます。              |

| 8    | $V_{DD}$           | 正側電源入力。このデバイスは2.5~5.5Vの電源で動作します。                           |

| 9    | V <sub>REF</sub>   | DACのリファレンス電圧入力                                             |

| 10   | $R_{FB}$           | DACの帰還抵抗。外付けアンプの出力に接続して、DACの電流出力を電圧に変換します。                 |

### 用語の説明

#### 相対精度(積分非直線性、INL)

相対精度またはエンドポイント非直線性とは、DAC伝達関数の両端を結ぶ直線からの最大偏差を表します。ゼロスケールおよびフルスケールの調節後に測定し、一般にLSB単位またはフルスケールのパーセント値で表します。

#### 微分非直線性(DNL)

微分非直線性とは、隣接する2つのコードの間における測定された変化と理論的な1LSB変化との差を表します。微分非直線性の仕様が全動作温度範囲で±1LSB以内の場合、単調増加性が保証されます。

#### ゲイン誤差

ゲイン誤差またはフルスケール誤差とは、DACの理論出力値とデバイスの実際の出力との間の出力誤差を表します。このDACでは、理論最大出力はV<sub>REF</sub>-1LSBになります。DACのゲイン誤差は、外付け抵抗を使って0に調整できます。

#### 出力リーク電流

出力リーク電流は、DACのラダー・スイッチがオフのときに、これらのスイッチに流入する電流を表します。IouT1ピンの場合は、全ビット「0」をDACにロードしてIouT1電流を測定します。DACに全ビット「1」をロードすると、IouT2ラインに流入する電流が最小になります。

#### 出力容量

IOUT1またはIOUT2とAGNDとの間の容量。

#### 出力電流セトリング時間

フルスケールの入力変化に対して、出力が規定のレベルに安定するまでの時間を表します。このデバイスの場合、 $100\Omega$ の抵抗をグラウンドに接続して規定しています。セトリング時間仕様には、 $\overline{\text{SYNC}}$ の立上がりエッジからフルスケール出力変化までのデジタル遅延が含まれます。

#### デジタルからアナログへのグリッチ・インパルス

入力によって状態が変化したとき、デジタル入力からアナログ出力に注入される電荷の量。通常、グリッチの面積として規定され、グリッチが電流信号と電圧信号のどちらで測定されるかに応じて、それぞれpA-secまたはnV-secで表します。

#### デジタル・フィードスルー

デバイスが選択されていないにもかかわらず、デバイスのデジタル入力上の高周波ロジック動作がデバイスを通して容量的に結合され、Iourピンと後段の回路にノイズとして現れます。このノイズがデジタル・フィードスルーです。

#### 乗算フィードスルー誤差

DACに全ビット「0」をロードしたときの、DACのリファレンス入力からDACのIour1ピンへの容量性フィードスルーに起因する誤差を表します。

#### 全高調波歪み(THD)

このDACは、ACリファレンス駆動が可能です。THDは、DAC出力の各高調波のrms和と基本波の比を表します。次に示すように、一般に2~5次高調波のみで表されます。

$$THD = 20\log \frac{\sqrt{{V_2}^2 + {V_3}^2 + {V_4}^2 + {V_5}^2}}{V_1}$$

#### デジタル相互変調歪み(IMD)

2次相互変調歪み(IMD)は、DACでデジタル的に発生したfaとfbの2トーンと、2fa-fbと2fb-faに発生する2次の歪みとの相対振幅になります。

#### コンプライアンス電圧範囲

デバイスが仕様規定しているピン電圧(出力)の最大範囲を表します。

#### スプリアス・フリー・ダイナミック・レンジ(SFDR)

基本波信号がスプリアス・ノイズの干渉または歪みを受けなくてすむ、DACで使用できるダイナミック・レンジをいいます。SFDRは、DCからナイキスト周波数(DACサンプリング・レートの1/2、すなわちf<sub>8</sub>/2)までの高調波または非高調波の最大のスプリアスと基本波との間の振幅差として表されます。ナローバンドのSFDRは、任意のウインドウ・サイズ(この場合、基本波の50%)で測定したSFDRをいいます。デジタルSFDRは、信号がデジタル的に生成された正弦波の場合に、DACが使用できるダイナミック・レンジです。

REV.0

8

### 代表的な性能特性

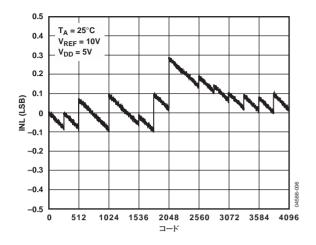

図6. コード 対 INL

図7. コード 対 DNL

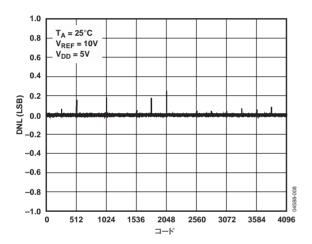

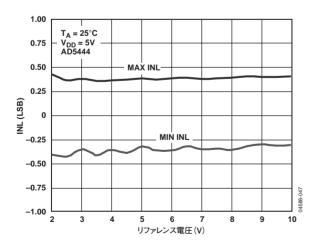

図8. リファレンス電圧対 INL

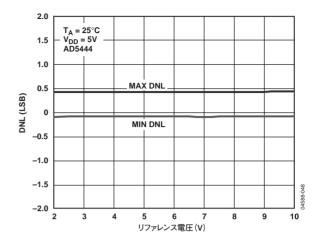

図9. リファレンス電圧対 DNL

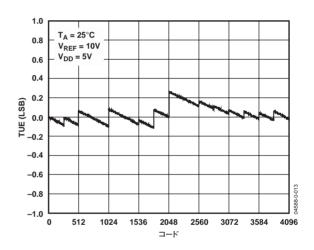

図10. コード 対 TUE

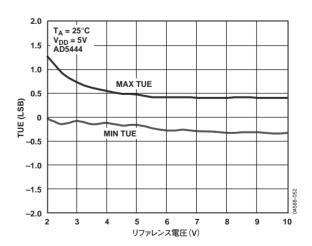

図11. リファレンス電圧 対 TUE

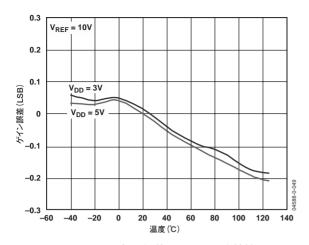

図12. ゲイン誤差(LSB)の温度特性

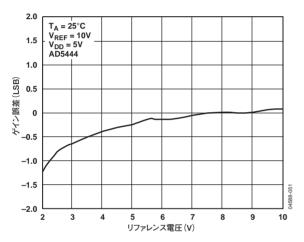

図13. リファレンス電圧対 ゲイン誤差(LSB)

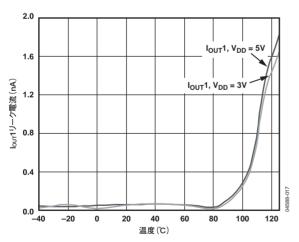

図14. I<sub>OUT</sub>1リーク電流の温度特性

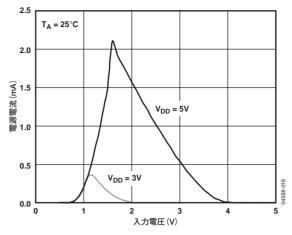

図15. ロジック入力電圧 対電源電流

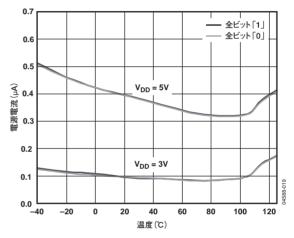

図16. 電源電流の温度特性

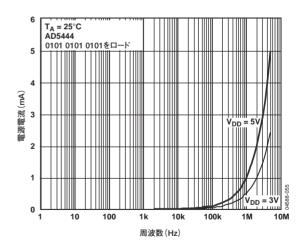

図17. 更新レート対電源電流

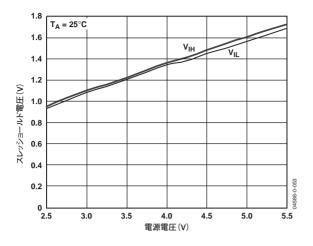

図18. 電源電圧対 スレッショールド電圧

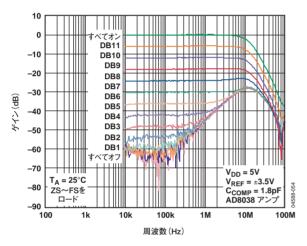

図19. 各コードに対するリファレンス乗算帯域幅の周波数特性

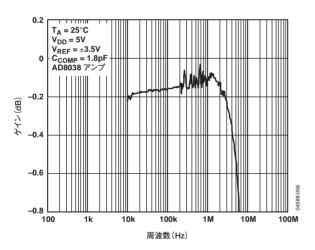

図20. リファレンス乗算帯域幅(全ビット「1」をロード)

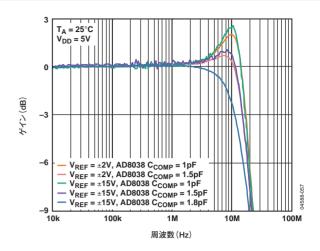

図21. 各補償コンデンサに対するリファレンス乗算帯域幅の 周波数特性

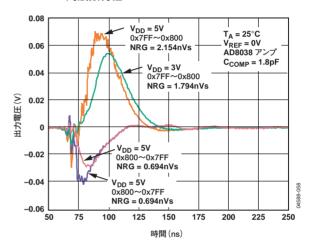

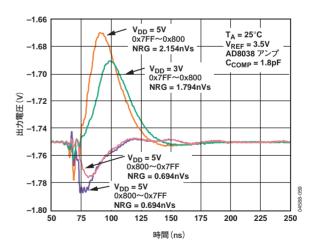

図22. ミッドスケール遷移(VREF = 0V)

図23. ミッドスケール遷移(VREF = 3.5V)

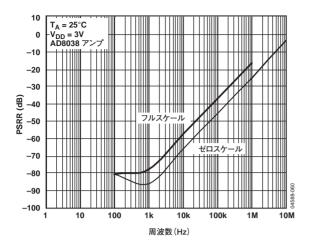

図24. 電源電圧変動除去比の周波数特性

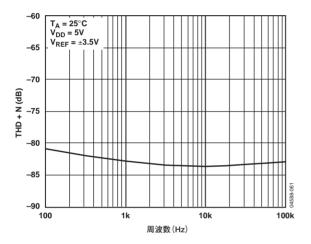

図25. THD + ノイズの周波数特性

図26. fout周波数 対 ワイドバンドSFDR

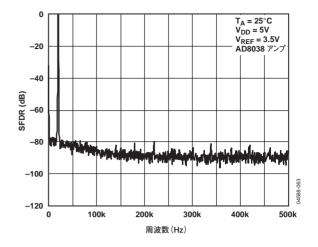

図27. ワイドバンドSFDR(fout = 20kHz、クロック = 1MHz)

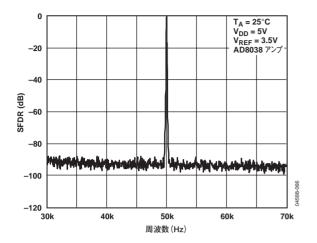

図28. ワイドバンドSFDR(fout = 50kHz、クロック = 1MHz)

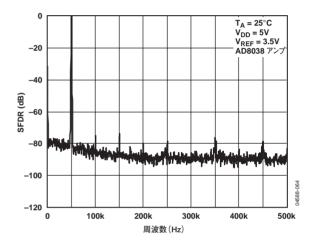

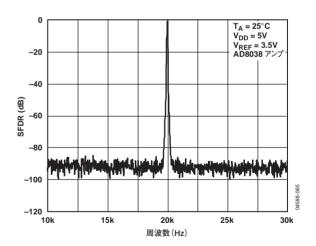

図29. ナローバンドSFDR(fout = 20kHz、クロック = 1MHz)

図30. ナローバンドSFDR(fout = 50kHz、クロック = 1MHz)

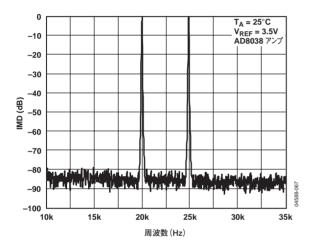

図31. ナローバンドIMD( fout = 20kHz、25kHz、クロック = 1MHz )

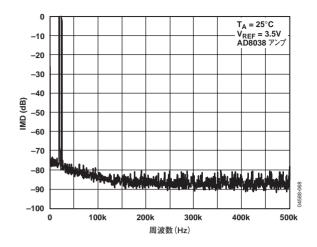

図32. ワイドバンドIMD(fout = 20kHz、25kHz、クロック = 1MHz)

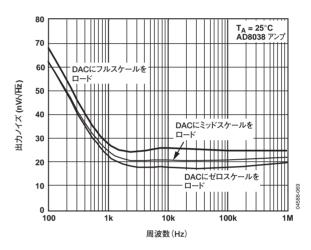

図33. 出力ノイズ・スペクトル密度

### 機能の説明

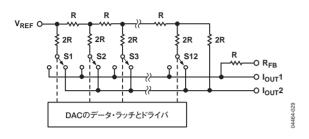

#### DAC部

AD5444は12ビットの電流出力DACで、4ビット単位でセグメント化された反転R-2Rラダーで構成されています。図34に、12ビットAD5444の簡略回路図を示します。

図34. 簡略回路図

帰還抵抗 $R_{FB}$ はRと同じ値です。Rの値は通常、 $9k\Omega$  (最小 $7k\Omega$ 、最大  $11k\Omega$ )です。 $I_{OUT}$ 1がGNDと同電位に保持されると、デジタル入力コードに関係なく、一定の電流が各ラダーに流入します。したがって、 $V_{REF}$ の入力抵抗は常に一定で公称値Rとなります。DAC出力 ( $I_{OUT}$ )はコードに依存し、さまざまな抵抗値と容量値を生成します。外付けアンプを選択する際には、アンプ反転入力ノードで生じるインピーダンスの変動を考慮する必要があります。

DACには $V_{REF}$ 、 $R_{FB}$ 、 $I_{OUT}$ の各ピンが用意してあるためきわめて汎用性が高く、たとえば、ユニポーラ出力、バイポーラ・モードでの4象限乗算などの複数の動作モードの設定が可能です。内蔵の $R_{FB}$ 帰還抵抗に対して直列にマッチング・スイッチが使用されていることに注意してください。 $R_{FB}$ を測定する際には、 $V_{DD}$ に電源を接続して連続性を維持する必要があります。

#### 回路動作

#### ユニポーラ・モード

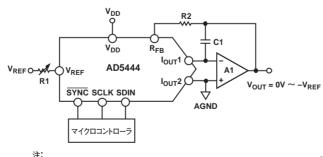

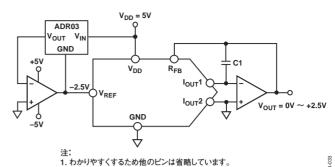

オペアンプを1個使うと、図35に示す2象限乗算動作またはユニポーラ 出力電圧振幅をもつようにデバイスを容易に構成できます。 出力アンプをユニポーラ・モードで接続した場合、出力電圧は次式で得られます。

$$V_{OUT} = -\frac{D}{2^n} \times V_{REF}$$

ここで、

DはDACにロードされるデジタル値(デシマル)で、nはDACの分解能です。

$$D = 0 \sim 4095$$

なお、出力電圧の極性は、DCリファレンス電圧のV<sub>REF</sub>極性と反対になります。

このDACは、負または正のリファレンス電圧で動作するように設計されています。 $V_{DD}$ 電源ピンは、内部デジタル・ロジックがDACスイッチのオン状態とオフ状態を駆動するときにのみ使います。このDACには、-10~+10Vの範囲のACリファレンス信号も入力できるように設計されています。リファレンス電圧が10Vに固定されている場合、図35の回路は0~-10Vのユニポーラ出力電圧振幅になります。 $V_{IN}$ がAC信号の場合、この回路は2象限乗算を実行します。

表5に、ユニポーラ動作におけるデジタル・コードと予測される出力電圧との関係を示します。

表5. ユニポーラ・コード表

| デジタル入力         | アナログ出力(V)                          |

|----------------|------------------------------------|

| 1111 1111 1111 | -V <sub>REF</sub> (4095/4096)      |

| 1000 0000 0000 | $-V_{REF}(2048/4096) = -V_{REF}/2$ |

| 0000 0000 0001 | -V <sub>REF</sub> (1/4096)         |

| 0000 0000 0000 | $-V_{REF}(0/4096) = 0$             |

注:

1. R1とR2は、ゲイン調整が必要な場合のみ使用。

2. A1が高速アンプの場合、位相補償のC1 (1~2pF) が必要になることもあります。

図35. ユニポーラ動作

14

#### バイポーラ動作

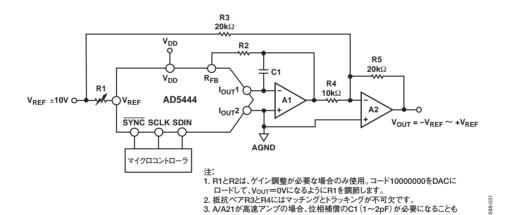

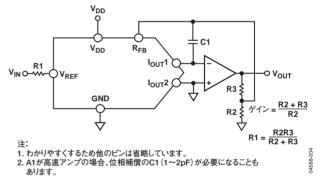

アプリケーションによっては、フル4象限乗算機能またはバイポーラ出力振幅が必要となることがあります。これは、外付けアンプをもう1個と外付け抵抗をいくつか追加することにより容易に実現できます(図36)。この回路では、2つめのアンプA2がゲイン2を提供します。リファレンス電圧からのオフセットを使って外付けアンプをバイアスすると、4象限乗算動作が得られます。この回路の伝達関数は、入力データ(D)がコード・ゼロ( $V_{OUT}$ = $V_{REF}$ ) →ミッドスケール( $V_{OUT}$ = $V_{REF}$ )にインクリメントするのに対応して、負と正の両出力電圧が発生することを示しています。

$$V_{OUT} = \left(V_{REF} \times \frac{D}{2^{n-1}}\right) - V_{REF}$$

ここで、

Dは、DACにロードされるデジタル値(デシマル)で、nはDACの分解能です。

$$D = 0 \sim 4095$$

V<sub>IN</sub>がAC信号の場合、この回路は4象限乗算を実行します。

表6に、バイポーラ動作におけるデジタル・コードと予測される出力電圧との関係を示します。

表6. バイポーラ・コード表

| デジタル入力         | アナログ出力(V)                     |

|----------------|-------------------------------|

| 1111 1111 1111 | +V <sub>REF</sub> (2047/2048) |

| 1000 0000 0000 | 0                             |

| 0000 0000 0001 | -V <sub>REF</sub> (2047/2048) |

| 0000 0000 0000 | -V <sub>REF</sub> (0/2048)    |

#### 安定性

I/V変換の構成では、DACのI<sub>OUT</sub>とオペアンプの反転ノードをできるだけ 短い配線で接続する必要があるため、適確なPCボードのレイアウトが必 要です。各コード変化はステップ関数に対応するため、オペアンプのゲ イン帯域幅積(GB積)が制限されていて反転ノードの寄生容量が大き い場合に、ゲイン・ピーキングが発生することがあります。この寄生容量 によりオープン・ループ応答に極が生じるため、クローズド・ループ・アプ リケーション回路でリンギングが発生したり、回路が不安定になったりす ることがあります。

安定性を得るために、オプションで補償コンデンサC1を $R_{FB}$ と並列に接続することもできます(図35と図36)。C1が小さ過ぎると出力でリンギングが発生し、大き過ぎるとセトリング時間に悪影響を与えます。C1は経験的に得られますが、一般に1 $\sim$ 2pFで十分に補償できます。

図36. バイポーラ動作(4象限乗算)

#### 単電源アプリケーション

#### 電圧スイッチング動作モード

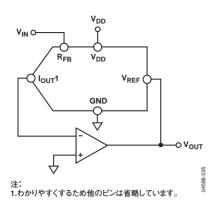

図37に、電圧スイッチング・モードで動作するDACを示します。リファレンス電圧V<sub>IN</sub>はI<sub>OUT</sub>1ピンに、I<sub>OUT</sub>2はAGNDにそれぞれ接続され、出力電圧はV<sub>REF</sub>ピンから得られます。この構成では、正のリファレンス電圧から正の出力電圧が得られ、単電源動作が可能となります。DACの出力は一定インピーダンス(DACラダー抵抗)をもつ電圧であり、オペアンプによって出力電圧をバッファリングする必要があります。リファレンス入力のインピーダンスは一定でなく、コードに依存して変化します。したがって、電圧入力は低インピーダンス信号源から駆動する必要があります。

図37. 単電源の電圧スイッチング・モード

DACラダー内のスイッチは同じソース-ドレイン電圧をもたなくなるので、 $V_{\rm IN}$ が低電圧に制限されることに注意してください。その結果、それらのオン抵抗が異なり、DACの積分直線性が損なわれます。また、 $V_{\rm IN}$ は-0.3V以下にならないようにする必要があります。そうしないと、内部ダイオードがオンになり、デバイスの最大定格を超えてしまいます。このタイプのアプリケーションでは、乗算機能が失われます。

#### 正の出力電圧

出力電圧の極性は、DCリファレンス電圧のVREF極性と反対になります。 正の電圧出力を得るには、抵抗値の誤差の影響を受けやすい反転アンプを使った出力の反転より、DACの入力に負のリファレンス電圧を接続したほうがよいでしょう。負のリファレンス電圧を生成するには、リファレンス回路のVourピンが仮想グラウンド、GNDピンが-2.5Vになるように、オペアンプを使ってリファレンスをレベル・シフトできます(図38)。

2. A1が高速アンプの場合、位相補償のC1 (1~2pF) が必要になることもあります。

図38. 最小の部品による正の電圧出力

#### ゲインの追加

VINより大きい出力電圧が必要なアプリケーションでは、外付けアンプを追加してゲインを増やすか、あるいは1段でゲインの増加を行います。DACの薄膜抵抗の温度係数の影響を考慮することは重要です。単にRFB抵抗に直列に抵抗を接続するだけでは温度係数のミスマッチが生じて、ゲイン温度係数誤差が大きくなります。代わりに、図39に示す回路を使用して、回路のゲインを増やすことを推奨します。R1、R2、R3はすべて同じ温度係数をもつ必要がありますが、DACの温度係数に一致させる必要はありません。この方法は、1より大きいゲインを必要とする回路に推奨されます。

図39. 電流出力DACゲインの増加

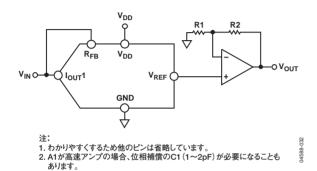

### DACをデバイダまたはプログラマブル・ゲイン素子 として使用する場合

電流切替え型のDACは非常に柔軟であるため、さまざまなアプリケーションに適しています。図40に示すように、このタイプのDACをオペアンプの帰還素子として接続し、 $R_{FB}$ を入力抵抗として使用する場合、出力電圧はデジタル入力値Dに反比例します。

$D=1-2^{-n}$ の場合、出力電圧は、

$$V_{OUT} = -V_{IN}/D = -V_{IN}/(1-2^{-n})$$

図40. デバイダまたはプログラマブルなゲイン素子として 使用した電流切替え型DAC

Dが減少すると、出力電圧が増加します。デジタル値 Dが小さい場合は、アンプが飽和しないようにして必要な精度を満たすことが大切です。たとえば、図40の回路でバイナリ・コード0x10 (00010000)、すなわち10 進数の16で駆動する8ビットDACでは、出力電圧が16×VINになります。しかし、DACに $\pm 0.5$ LSBの直線性がある場合、実際にはDの重みは $15.5/256 \sim 16.5/256$ の範囲になるため、可能な出力電圧は15.5VIN の範囲になります。つまり、たとえDACそのものの最大誤差が0.2%であっても、誤差は3%になります。

DACのリーク電流も、デバイダ回路における誤差源になります。リーク電流は、DACを介してオペアンプから供給される逆向きの電流により相殺する必要があります。 $V_{REF}$ ピンはDに依存する電流だけが $I_{OUT}$ 1ピンに流れるため、出力電圧は次のように変化します。

DACのリーク電流に起因する出力誤差電圧=(リーク電流×R)/D

ここで、Rは $V_{REF}$ ピンでのDAC抵抗。

10nAのDACリーク電流、 $R=10k\Omega$ 、ゲイン=16(すなわち1/D)に対して、誤差電圧は1.6mVになります。

#### アンプの選択

電流切替えモードに対する基本的な条件は、入力バイアス電流と入力オフセット電圧が小さいアンプを使うことです。オペアンプの入力オフセット電圧は、回路の可変ゲイン(コードに依存するDAC出力抵抗によりゲインが変化)で乗算されます。隣接する2つのデジタル値の間でこのノイズ・ゲインが変化すると、アンプの入力オフセット電圧により出力電圧にステップ変化が生じます。この出力電圧変化が2つのコード間の出力の変化に重畳され、微分直線性誤差を発生させます。この誤差がかなり大きいと、DACの単調増加性が失われます。

オペアンプの入力バイアス電流も、帰還抵抗R<sub>FB</sub>にバイアス電流が流入する結果、電圧出力にオフセットを発生させます。しかし、ほとんどのオペアンプは入力バイアス電流が十分に低いので、12ビット・アプリケーションで大きな誤差を発生させることはありません。

電圧スイッチング回路では、回路の電圧出力でコード依存誤差が発生することから、オペアンプの同相ノイズ除去性能が重要となります。ほとんどのオペアンプは、8/10/12ビット分解能での使用に適した十分な同相ノイズ除去性能があります。

DACスイッチがワイドバンドの低インピーダンス信号源(V<sub>IN</sub>とAGND)から駆動される場合、セトリング時間は短くなります。したがって、電圧スイッチングDAC回路のスルーレートとセトリング時間は、主として出力オペアンプによって決まります。この構成で最小のセトリング時間を実現するには、DACのV<sub>REF</sub>ノード(このアプリケーションでは電圧出力ノード)の容量を可能な限り小さくすることが重要です。そのためには、低入力容量をもつバッファ・アンプを使用するとともに、ボードの設計に注意する必要があります。

ほとんどの単電源回路ではグラウンドがアナログ信号の範囲に含まれますが、そのためにはレールtoレール信号を処理できるアンプが必要となります。アナログ・デバイセズでは、広範囲の単電源アンプを提供しています。

#### リファレンスの選択

AD5444電流出力DACで使用するリファレンス電圧を選択する際には、リファレンス出力電圧温度係数の仕様に注意する必要があります。このパラメータはフルスケール誤差に影響するだけでなく、直線性性能(INLとDNL)にも影響することがあります。リファレンス電圧の温度係数は、システム精度仕様に一致させる必要があります。たとえば、0~50℃の温度範囲で全体仕様を1LSB以内に維持しなければならない8ビット・システムでは、システムの最大温度ドリフトは78ppm/℃未満にする必要があります。

同じ温度範囲で全体仕様を2LSB未満にしなければならない12ビット・システムでは、最大ドリフトは10ppm/でにする必要があります。この誤差源を最小に抑えるには低出力温度係数の高精度リファレンスを選択してください。表7に、この範囲の電流出力DACに使用できるアナログ・デバイセズのリファレンス製品を示します。

### 表7. 推奨するADIの高精度リファレンス電圧

| リファレンス | 出力電圧(V) | 初期精度(%) | 温度ドリフト(ppm/°C) | 0.1~10Hzのノイズ(μVp-p) | パッケージ            |

|--------|---------|---------|----------------|---------------------|------------------|

| ADR01  | 10      | 0.1     | 3              | 20                  | SC70, TSOT, SOIC |

| ADR02  | 5       | 0.1     | 3              | 10                  | SC70、TSOT、SOIC   |

| ADR03  | 2.5     | 0.2     | 3              | 10                  | SC70、TSOT、SOIC   |

| ADR425 | 5       | 0.04    | 3              | 3.4                 | MSOP, SOIC       |

#### 表8. 推奨するADIの高精度オペアンプ

| 製品番号   | 最大電源電圧(V) | V <sub>0S</sub> (max)(μV) | I <sub>B</sub> (max)(nA) | GB積(MHz) | スルーレート(V/μs) |

|--------|-----------|---------------------------|--------------------------|----------|--------------|

| OP97   | ±20       | 25                        | 0.1                      | 0.9      | 0.2          |

| OP1177 | ±18       | 60                        | 2                        | 1.3      | 0.7          |

| AD8551 | 6         | 5                         | 0.05                     | 1.5      | 0.4          |

### 表9. 推奨するADIの高速オペアンプ

| 製品番号   | 最大電源電圧(V) | V <sub>OS</sub> (max)(μV) | I <sub>B</sub> (max)(nA) | BW@A <sub>CL</sub> (MHz) | スルーレート(V/μs) |

|--------|-----------|---------------------------|--------------------------|--------------------------|--------------|

| AD8065 | ±12       | 1500                      | 0.01                     | 145                      | 180          |

| AD8021 | ±12       | 1000                      | 1000                     | 200                      | 100          |

| AD8038 | ±5        | 3000                      | 0.75                     | 350                      | 425          |

| AD9631 | ±5        | 10000                     | 7000                     | 320                      | 1300         |

### シリアル・インターフェース

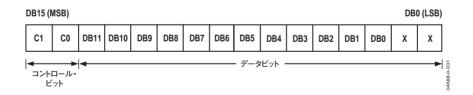

AD5444は、SPI/QSPI/MICROWIREおよびDSPの各インターフェース規格と互換性を持ち、かつ使いやすい3線式インターフェースを内蔵しています。データは、16ビットワードでデバイスに書き込まれます。この16ビットワードは、2ビットのコントロール・ビットと12ビットのデータビットにより構成されます(図41)。AD5444は12ビットがデータビットで、下位2ビットはドント・ケアです。

#### DACコントロール・ビット:C1、CO

コントロール・ビットC1とC0を使うと、新しいDACコードのロードと更新、およびアクティブ・クロック・エッジの変更を行うことができます。デフォルトでは、データはSCLKの立下がりエッジでシフト・レジスタに入力されますが、コントロール・ビットを使ってこれを変えることができます。変更した場合、DACコアは次のデータ・フレームまで動作しません。電源の再投入時に、これはデフォルト状態にリセットされます。内蔵のパワーオン・リセット回路により、DACレジスタとIourピンにゼロスケールがロードされた状態でデバイスが立ち上がるようになっています。

表10. DACコントロール・ビット

| C1 | CO | 制御機能                    |

|----|----|-------------------------|

| 0  | 0  | ロードおよび更新(パワーオン・デフォルト)   |

| 0  | 1  | SDOをディスエーブル             |

| 1  | 0  | 動作なし                    |

| 1  | 1  | 立上がりエッジでデータをシフト・レジスタに入力 |

#### SYNC機能

$\overline{SYNC}$  は、フレーム同期信号として機能するエッジ・トリガ入力です。データは、 $\overline{SYNC}$  がローレベルのときにのみデバイスに転送できます。シリアル・データ転送を開始するときは、 $\overline{SYNC}$  をローレベルにして、 $\overline{SYNC}$  の立下がりからSCLKの立下がりエッジまでの最小セットアップ・タイム( $t_4$ )を確保します。デバイスの消費電力を最小限に抑えるために、デバイスに書込みを行うときだけ、すなわち  $\overline{SYNC}$  の立下がりエッジでのみインターフェースをパワーアップさせます。

SCLK入力バッファとSDIN入力バッファは、SYNC の立上がりエッジでパワーダウンされます。

SCLKパルスの16番目の立下がりエッジの後に、SYNCをハイレベルにすると、データが入力シフト・レジスタからDACへ転送されます。

#### デイジーチェーン・モード

デイジーチェーン・モードはデフォルトでパワーオン時にイネーブルになります。デイジーチェーン機能をディスエーブルにするときは、コントロール・ワードに「01」を書き込みます。デイジーチェーン・モードでは、SCLKの内部ゲーティングがディスエーブルになります。SCLKは SYNC がローレベルのとき、入力シフト・レジスタに連続的に入力されます。16個を超えるクロック・パルスが入力されると、データはシフト・レジスタからはみ出して、SDOピンに出力されます。このデータはSCLKの立上がりエッジで出力され(これはデフォルトですが、コントロール・ワードでアクティブ・エッジを変更可能)、次のデバイスでは立下がりエッジで有効になります(デフォルト)。このピンをチェーン内の次のデバイスのSDIN入力に接続すると、複数デバイスのインターフェースを構成できます。システム内の各デバイスには、16個のクロック・パルスが必要です。したがって、必要な合計クロック・サイクル数は16 N(Nはチェーン内の合計デバイス数)になります。

すべてのデバイスに対するシリアル転送が完了したら、SYNCをハイレベルにします。これにより、入力シフト・レジスタに余分なデータが入力されるのを防止します。必要なクロック・サイクル数を含むバースト・クロックを使うことができ、そのしばらく後でSYNCをハイレベルにします。SYNCの立上がりエッジの後に、データは各デバイスの入力レジスタからアドレス指定されたDACに自動的に転送されます。

コントロール・ビット=10のとき、デバイスは無動作モードになります。デイジーチェーン・アプリケーションで、チェーン内の特定のDACの設定を変更したくない場合には、この機能が便利です。DACのコントロール・ビットに「10 |を書き込むだけで、後続のデータビットが無視されます。

図41. AD5444の12ビット入力シフト・レジスタ

#### マイクロプロセッサとのインターフェース

マイクロプロセッサとAD5444 DACとのインターフェースは、マイクロコントローラとDSPプロセッサに対して互換性を持つ標準プロトコルを使うシリアル・バスを介して行います。この通信チャンネルは、クロック信号、データ信号、同期信号から構成される3線式インターフェースです。AD5444では16ビット・ワードを使い、デフォルトではSCLKの立下がりエッジでデータが有効になりますが、データワード内のコントロール・ビットを使ってこれを変更することもできます。

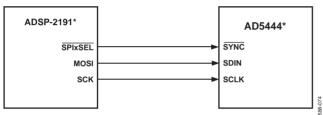

#### ADSP-21xxとAD5444とのインターフェース

ADSP-21xxファミリーのDSPは、外付けロジックの追加なしに容易に AD5444 DACにインターフェースできます。図42に、DACとADSP-2191MのSPIインターフェースの例を示します。DSPのSCKがシリアル・データ・ラインSDINを駆動します。 $\overline{\text{SYNC}}$ は、ポート・ライン(この場合 SPIxSEL)から駆動されます。

\*わかりやすくするため他のピンは省略しています。

図42. ADSP-2191のSPIとAD5444とのインターフェース

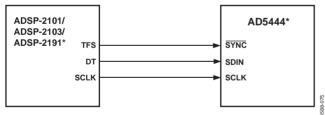

図43に、DACとDSP SPORTとの間のシリアル・インターフェースを示します。この例では、SPORT0を使って、DACシフト・レジスタへデータを転送します。送信は、SPORTをイネーブルにした後に、Txレジスタにワードを書きこむことにより、起動されます。書込みシーケンスでは、データはDSPのシリアル・クロックの各立上がりエッジで出力され、SCLKの立下がりエッジでDACシフト・レジスタに入力されます。DAC出力の更新は、SYNC信号の立上がりエッジで行われます。

\*わかりやすくするため他のピンは省略しています。

図43. ADSP-2101/ADSP-2103/ADSP-2191のSPORTと AD5444とのインターフェース

フレーム同期遅延、フレーム同期のセットアップ時間とホールド時間、データ遅延、データのセットアップ時間とホールド時間、SCLK幅の仕様に互換性がある場合、2個のデバイス間で一定のクロック速度での通信が可能です。DACインターフェースは、最小13nsのt4(SYNCの立下がりエッジからSCLKの立下がりエッジまでのセットアップ時間)を想定しています。SPORTレジスタのクロック周波数とフレーム同期周波数については、『ADSP-21xxユーザ・マニュアル』を参照してください。

表11に、SPORTコントロール・レジスタの設定を示します。

表11. SPORTコントロール・レジスタの設定

| 名称     | 設定   | 説明              |

|--------|------|-----------------|

| TFSW   | 1    | オルタネート・フレーミング   |

| INVTFS | 1    | アクティブ・ローのフレーム信号 |

| DTYPE  | 00   | データ右詰め          |

| ISCLK  | 1    | 内部シリアル・クロック     |

| TFSR   | 1    | ワードごとのフレーム      |

| ITFS   | 1    | 内部フレーミング信号      |

| SLEN   | 1111 | 16ビット・データワード    |

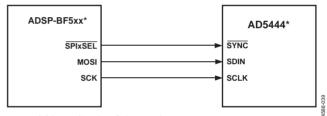

#### ADSP-BF5xxとAD5444とのインターフェース

ADSP-BF5xxファミリーのプロセッサは、SPI互換デバイスとの通信を可能にするSPI互換ポートを内蔵しています。図46に、ADSP-BF5xxとAD5444 DACとの間のシリアル・インターフェースを示します。この構成では、MOSIピン(マスター出力/スレーブ入力ピン)を使ってデータが転送されます。 SYNC は、再設定可能なフラグ・ピンであるSPIチップ・セレクト・ピンから駆動されます。

\*わかりやすくするため他のピンは省略しています。

図44. ADSP-BF5xxとAD5444とのインターフェース

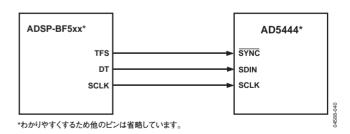

ADSP-BF5xxプロセッサは、チャンネル同期シリアル・ポート(SPORT)を内蔵しています。図46に、DACとDSP SPORTとの間のシリアル・インターフェースを示します。SPORTをイネーブルにして、Txレジスタにワードを書き込むと、送信が起動されます。データは、DSPのシリアル・クロックの各立上がりエッジで出力され、SCLKの立下がりエッジでDACシフト・レジスタに入力されます。送信フレーム同期(TFS)ラインをSYNC信号として使うと、DAC出力が更新されます。

図45. ADSP-BF5xxとAD5444とのインターフェース

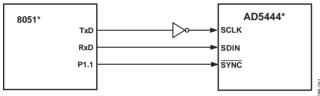

#### 80C51/80L51とAD5444とのインターフェース

図46に、DACと80C51/80L51との間のシリアル・インターフェースを示します。80C51/80L51のTxDがDACシリアル・インターフェースのSCLKを駆動し、RxDがシリアル・データ・ラインSDINを駆動します。P1.1は、シリアル・ボートのビット・プログラマブル・ピンであり、SYNCの駆動に使用します。データがスイッチに転送されると、P1.1はローレベルになります。80C51/80L51はデータを8ビットのバイトとしてのみ転送するため、送信サイクル内には立下がりクロック・エッジが8個しかありません。データをDACにロードするには、最初の8ビットが転送された後もP1.1をローレベルのままにして、2番目の書込みサイクルを実行すると、データの2番目のバイトの転送が開始されます。

RxD上のデータはTxDの立上がりエッジでマイクロコントローラから出力され、立下がりエッジで有効になります。そのため、DACとマイクロコントローラ・インターフェースとの間に外付けロジックは不要となります。このサイクルの完了後にP1.1をハイレベルにします。80C51/80L51は、データ・ストリームの先頭ビットとしてSBUFレジスタのLSBを出力します。DACの入力レジスタは、MSBファーストでデータを受け取る必要があります。送信ルーチンは、このことを考慮に入れる必要があります。

\*わかりやすくするため他のピンは省略しています。

図46. 80C51/80L51とAD5444とのインターフェース

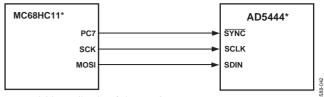

#### MC68HC11とAD5444とのインターフェース

図47に、DACとMC68HC11マイクロコントローラとのシリアル・インターフェースの例を示します。MC68HC11のシリアル・ペリフェラル・インターフェース (SPI) は、マスター・モード (MSTR) = 1、クロック極性ビット (CPOL) = 0、クロック位相ビット (CPHA) = 1に設定します。SPIは、SPIコントロール・レジスタ (SPCR) に書込みを行って設定します。『68HC11ユーザ・マニュアル』を参照してください。68HC11のSCKがDACインターフェースのSCLKを駆動し、MOSI出力がAD5444のシリアル・データ・ライン (SDIN)を駆動します。

SYNC 信号は、ポート・ライン (PC7) から引き出されます。データをAD5444に転送するときは、SYNC ラインをローレベルにします (PC7)。MOSIに出力されるデータは、SCKの立下がりエッジで有効になります。シリアル・データは68HC11から8ビットのバイトで転送され、送信サイクル内には立下がりクロック・エッジが8個しかありません。データはMSBファーストで転送されます。データをDACにロードするときは、最初の8ビットが転送された後もPC7をローレベルのままにして、DACに対して2番目のシリアル書込み動作を実行します。この手順の終わりに、PC7をハイレベルにします。

\*わかりやすくするため他のピンは省略しています。

図47. 68HC11/68L11とAD5444とのインターフェース

入力シフト・レジスタに以前書き込まれたデータを確認する場合は、SDO ラインをMC68HC11のMISOに接続して、SYNC をローレベルにすると、SCLKの立上がりエッジでデータがシフト・レジスタから出力されます。

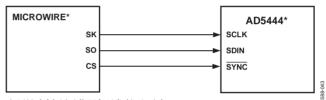

#### MICROWIREとAD5444とのインターフェース

図48に、DACと任意のMICROWIRE互換デバイスとのインターフェースを示します。シリアル・データはシリアル・クロックSKの立下がりエッジで出力され、SKの立上がりエッジでDACの入力シフト・レジスタに入力されます。このSKの立上がりエッジは、DACのSCLKの立下がりエッジに対応します。

\*わかりやすくするため他のピンは省略しています。

図48. MICROWIREとAD5444とのインターフェース

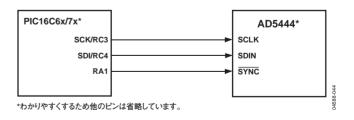

#### PIC16C6x/7xとAD5444とのインターフェース

PIC16C6x/7xの同期シリアル・ポート(SSP)をSPIマスターに設定します (クロック極性ビット=0)。これは、同期シリアル・ポート・コントロール・レ ジスタ(SSPCON)に書込みによって行います。『PIC16/17マイクロコントローラ・ユーザ・マニュアル』を参照してください。

この例では、I/OポートRA1を使ってSYNCパルスを発生させ、DACのシリアル・ポートをイネーブルにしています。このマイクロコントローラは、各シリアル転送動作でデータを8ビットだけ転送します。したがって、書込み動作を2回続けて行う必要があります。図49に接続図を示します。

図49. PIC16C6x/7xとAD5444とのインターフェース

### PCボードのレイアウトと電源デカップリング

精度が重要な回路では、定格の性能を得るために電源とグラウンド・リターンのレイアウトに注意する必要があります。AD5444を実装するプリント回路ボードは、アナログ部分とデジタル部分を分離し、ボード内でそれぞれまとめて配置するように設計してください。複数のデバイスがAGNDとDGNDの接続を必要とするシステムでDACを使用する場合は、この接続は1ヵ所のみで行います。できるだけデバイスの近くにスター結線してください。

このDACでは、パッケージのできるだけ近いところ(理想的にはデバイスの真上)に $10\mu$  Fと $0.1\mu$  Fのコンデンサを並列接続することにより十分な電源バイパスを持たせてください。 $0.1\mu$  Fコンデンサは、高周波でグラウンドに低インピーダンス・パスを提供するセラミック型のような等価直列抵抗(ESR)が小さく、かつ等価直列インダクタンス(ESL)が小さいものを使って、内部ロジックのスイッチングに起因する過渡電流を処理する必要があります。ESRが小さい $1\sim10\mu$  Fのタンタル・コンデンサまたは電解コンデンサも電源に接続して、過渡電圧を抑え、かつ低周波リップルを除去する必要があります。

クロックなどの高速スイッチング信号はデジタル・グラウンドでシールドして、ボード上の他の部品へノイズを放出しないようにし、リファレンス入力の近くを通らないようにします。

デジタル信号とアナログ信号は交差しないようにしてください。ボードの 反対側のパターンは、互いに直角になるように配置します。これにより、ボードを通過するフィードスルーの影響を削減できます。マイクロストリップ技術は最適なソリューションですが、両面ボードでは必ずしも使用できるとは限りません。この技術では、ボードの部品面をグラウンド・プレーン専用にし、信号パターンはハンダ面に配置します。

レイアウトは、リード長をできるだけ短くしたコンパクトな設計を推奨します。入力までの配線はできるだけ短くして、IR電圧降下と浮遊インダクタンスを小さくする必要があります。

V<sub>REF</sub>とR<sub>FB</sub>の間のPCボードのメタル・パターンも、ゲイン誤差を小さくするためにマッチングさせる必要があります。最大の高周波性能を得るには、I/Vアンプをできるだけデバイスの近くに配置する必要があります。

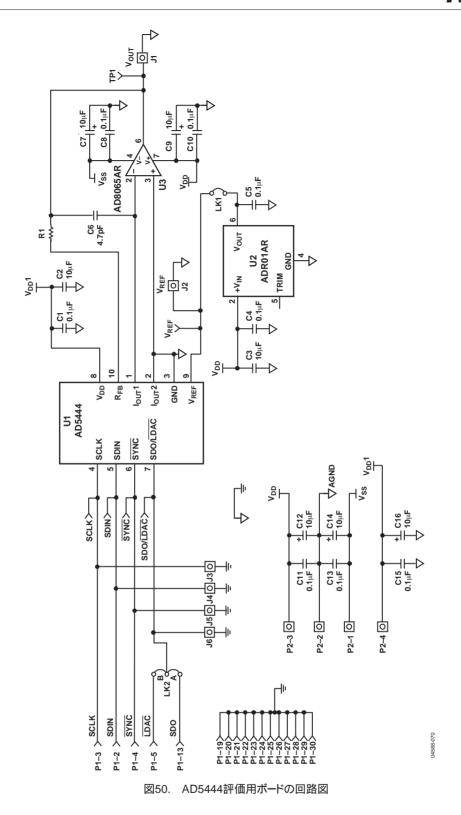

#### DAC用評価用ボード

評価用ボードは、AD5444 DACと電流/電圧変換アンプ「AD8065」で構成されています。評価用ボードには、10Vリファレンス電圧「ADR01」が実装されていますが、外付けのリファレンス電圧もSMB入力に接続できます。

この評価用キットには、DACを制御するPCソフトウェアのCD-ROMが含まれています。このソフトウェアを使うと、デバイスへのコードの書込みを容易に行うことができます。

#### 評価用ボードの電源

このボードには $\pm 12$ Vと+5Vの電源が必要です。+12Vの $V_{DD}$ と $V_{SS}$ は出力アンプの電源として、+5VはDAC( $V_{DDI}$ )とトランシーバ( $V_{CC}$ )の電源として使います。

両電源は、 $10 \mu$  Fのタンタル・コンデンサと $0.1 \mu$  Fのセラミック・コンデンサでそれぞれのグラウンド・プレーンにデカップリングされています。

REV.0 23

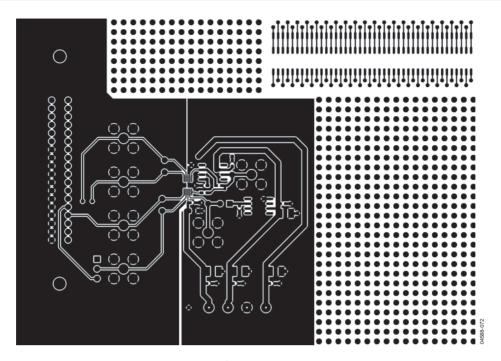

図51. 部品面のアートワーク

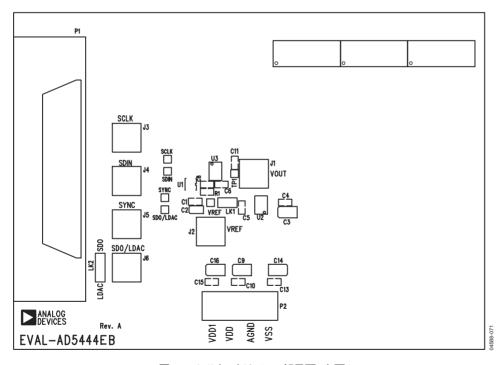

図52. シルクスクリーン 部品面(上面)

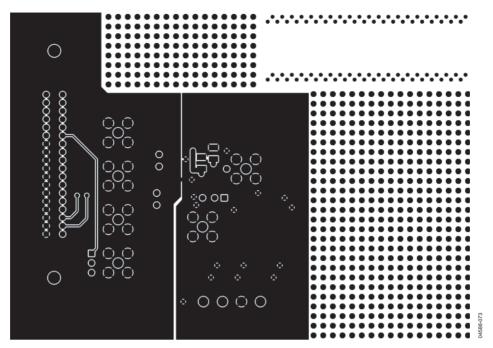

図53. ハンダ面のアートワーク

# AD54xxシリーズのラインアップ

表12

| 製品番号   | 分解能 | DAC数 | INL(LSB) | インターフェース | パッケージ        | 特長                                        |  |

|--------|-----|------|----------|----------|--------------|-------------------------------------------|--|

| AD5424 | 8   | 1    | ±0.25    | パラレル     | RU-16, CP-20 | 10MHz BW、17ns $\overline{\text{CS}}$ パルス幅 |  |

| AD5426 | 8   | 1    | ±0.25    | シリアル     | RM-10        | 10MHz BW、50MHzシリアル                        |  |

| AD5428 | 8   | 2    | ±0.25    | パラレル     | RU-20        | 10MHz BW、17ns CSパルス幅                      |  |

| AD5429 | 8   | 2    | ±0.25    | シリアル     | RU-10        | 10MHz BW、50MHzシリアル                        |  |

| AD5450 | 8   | 1    | ±0.25    | シリアル     | RJ-8         | 10MHz BW、50MHzシリアル                        |  |

| AD5432 | 10  | 1    | ±0.5     | シリアル     | RM-10        | 10MHz BW、50MHzシリアル                        |  |

| AD5433 | 10  | 1    | ±0.5     | パラレル     | RU-20, CP-20 | 10MHz BW、17ns CSパルス幅                      |  |

| AD5439 | 10  | 2    | ±0.5     | シリアル     | RU-16        | 10MHz BW、50MHzシリアル                        |  |

| AD5440 | 10  | 2    | ±0.5     | パラレル     | RU-24        | 10MHz BW、17ns <del>CS</del> パルス幅          |  |

| AD5451 | 10  | 1    | ±0.25    | シリアル     | RJ-8         | 10MHz BW、50MHzシリアル                        |  |

| AD5443 | 12  | 1    | ±1       | シリアル     | RM-10        | 10MHz BW、50MHzシリアル                        |  |

| AD5444 | 12  | 1    | ±0.5     | シリアル     | RM-8         | 50MHzのシリアル・インターフェース                       |  |

| AD5415 | 12  | 2    | ±1       | シリアル     | RU-24        | 10MHz BW、58MHzシリアル                        |  |

| AD5445 | 12  | 2    | ±1       | パラレル     | RU-20, CP-20 | 10MHz BW、17ns $\overline{\text{CS}}$ パルス幅 |  |

| AD5447 | 12  | 2    | ±1       | パラレル     | RU-24        | 10MHz BW、17ns CSパルス幅                      |  |

| AD5449 | 12  | 2    | ±1       | シリアル     | RU-16        | 10MHz BW、50MHzシリアル                        |  |

| AD5452 | 12  | 1    | ±0.5     | シリアル     | RJ-8、RM-8    | 10MHz BW、50MHzシリアル                        |  |

| AD5446 | 14  | 1    | ±1       | シリアル     | RM-8         | 10MHz BW、50MHzシリアル                        |  |

| AD5453 | 14  | 1    | ±2       | シリアル     | UJ-8、RM-8    | 10MHz BW、50MHzシリアル                        |  |

| AD5553 | 14  | 1    | ±1       | シリアル     | RM-8         | 4MHz BW、50MHzシリアル・クロック                    |  |

| AD5556 | 14  | 1    | ±1       | パラレル     | RU-28        | 4MHz BW、20ns WR パルス幅                      |  |

| AD5555 | 14  | 2    | ±1       | シリアル     | RM-8         | 4MHz BW、50MHzシリアル・クロック                    |  |

| AD5557 | 14  | 2    | ±1       | パラレル     | RU-38        | 4MHz BW、20ns WR パルス幅                      |  |

| AD5543 | 16  | 1    | ±2       | シリアル     | RM-8         | 4MHz BW、50MHzシリアル・クロック                    |  |

| AD5546 | 16  | 1    | ±2       | パラレル     | RU-28        | 4MHz BW、20ns WR パルス幅                      |  |

| AD5545 | 16  | 2    | ±2       | シリアル     | RU-16        | 4MHz BW、50MHzシリアル・クロック                    |  |

| AD5547 | 16  | 2    | ±2       | パラレル     | RU-38        | 4MHz BW、20ns WR パルス幅                      |  |

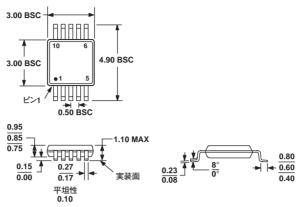

## 外形寸法

JEDEC規格MO-187BAに準拠

### オーダー・ガイド

| 製品モデル           | 分解能 | INL  | 温度範囲       | パッケージ  | パッケージ・<br>オプション | マーキング |

|-----------------|-----|------|------------|--------|-----------------|-------|

| AD5444YRM       | 12  | ±0.5 | -40~+125℃  | MSOP   | RM-10           | D27   |

| AD5444YRM-REEL  | 12  | ±0.5 | -40~+125℃  | MSOP   | RM-10           | D27   |

| AD5444YRM-REEL7 | 12  | ±0.5 | -40∼+125°C | MSOP   | RM-10           | D27   |

| EVAL-AD5444EB   |     |      |            | 評価用ボード |                 |       |