# 4/6チャンネル、 デジタル・ポテンショメータ

# AD5204/AD5206

## 特長

256ポジション

独立プログラマブル・マルチ・チャンネル

AD5204:4チャンネル AD5206:6チャンネル ポテンショメータ置換部品 10kΩ、50kΩ、100kΩ

3線SPIコンパチブル・シリアル・データ入力 単電源: +2.7~5.5V、デュアル電源: ±2.7V動作

パワー・オンによる中間スケール回帰動作

## アプリケーション

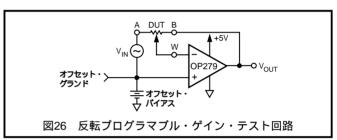

機械式ポテンショメーターの置換部品計装:ゲイン、オフセット調整プログラマブル電圧/電流変換プログラマブル・フィルタ、遅延、時定数ライン・インピーダンス・マッチング

## 概要

AD5204/AD5206は、4/6チャンネル、256ポジション、デジタル制御の可変抵抗器 (VR)を構成し、ポテンショメータや可変抵抗器と同様な電子的調整機能を提供します。AD5204/AD5206の各チャンネルは、ワイパー接点を持った固定抵抗器を備えており、SPIコンパチブルのシリアル入力レジスタに設定されたデジタル・コードの値に従って固定抵抗器にタップを設定します。ワイパーと固定抵抗器の両端の抵抗値は、VRラッチに転送されるデジタルコードに従って直線的に変化します。このように構成される可変抵抗器では、A端子とワイパーおよびB端子とワイパーの抵抗値を完全にプログラマブルな形で変化させることができます。A-B端子間の固定抵抗値は10k $\Omega$ 、50k $\Omega$ 、100k $\Omega$ で、公称温度係数は700ppm/°Cとなっています。

両モデルとも、個別にプログラムされた抵抗値を保持するVRラッチが設けられています。VRラッチは、標準3線シリアル入力デジタル・インターフェースからの値をロードする内部シリアル/パラレル・シフトレジスタによって更新されます。シリアル入力レジスタにクロックに従って入力されるデータ・ワードは、11のデータ・ビットによって構成されます。でSストローブがロジック・ハイに戻ったときに最初の3ビットがデコードされて、残りの8ビットのデータ・ワードをロードするVRラッチを指定します。シリアル・レジスタの反対側の端にあるシリアル・データ出力ピン(SDO、AD5204のみ)により、マルチVRのアプリケーションでも、外部デコード・ロジック回

機能ブロック図 AD5204  $\Diamond V_{DD}$  $\overline{cs}$ Δ1 ΕN Ժա₁ RDAC ) B1 #1 SDO ( シリアル レジスタ ∖ w₄ **RDAC** SDI DI D0 SHDN パワー・  $v_{ss}$ DD リセット AD5206 ρv<sup>DD</sup> cs Α1 FN ጎw1 RDAC ) R1 A1 A0 D7 レジスタ 5 W6 RDAC D0 SDI C DI В6 パワー オン・ GND C Vss

路を付加することなく、デージー・チェーンを簡単に構成することができます。

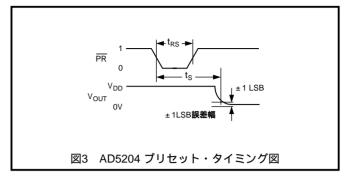

オプションのリセット  $(\overline{PR})$ は、VRラッチに $80_H$ を負荷することによって、AD5204のすべてのワイパーを強制的に中間スケールの位置に戻します。

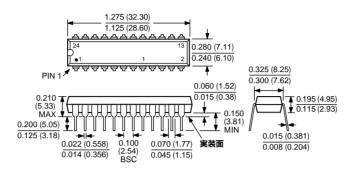

AD5204/AD5206は、表面実装型(SOL-24)、TSSOP-24および24 ピンのプラスチックDIPパッケージで供給されます。拡張工業温 度範囲の-40~+85℃で動作が保証されています。

1、2および4チャンネルのデバイスについては、AD8400/AD8402/AD8403の資料をご覧ください。

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、その情報の利用または利用したことにより引き起こされる第3者の特許または権利の侵害に関して、当社はいっさいの責任を負いません。さらに、アナログ・デバイセズ社の特許または特許の権利の使用を許諾するものでもありません。

REV.0

本 社/東京都港区海岸1-16-1 電話03(5402)8200 〒105-6891 ニューピア竹芝サウスタワービル

大阪営業所/大阪市淀川区宮原3-5-36 電話06(6350)6868(代) 〒532-0003 新大阪第二森ビル

**AD5204/AD5206 - 仕様** 電気的特性(特に指示のない限り、V<sub>DD</sub>= + 5V ± 10% または + 3V ± 10%、Vss=0V、V<sub>A</sub>= + V<sub>DD</sub>、V<sub>B</sub>=0V、 - 40 <T<sub>A</sub>< + 85 )

| パラメータ                                          | 記号                               | 条件                                                    | Min     | Typ¹   | Max      | 単位             |

|------------------------------------------------|----------------------------------|-------------------------------------------------------|---------|--------|----------|----------------|

| すべてのVRに適用される加減抵抗器モード                           |                                  |                                                       |         |        |          |                |

| 抵抗值差分NL <sup>2</sup>                           | R-DNL                            | R <sub>WB</sub> , V <sub>A</sub> = 無接続                | -1      | ± 1/4  | +1       | LSB            |

| 抵抗値非直線性誤差 <sup>2</sup>                         | R-INL                            | R <sub>WB</sub> , V <sub>A</sub> = 無接続                | -2      | ± 1/2  | +2       | LSB            |

| 公称抵抗值許容誤差3                                     | R <sub>AB</sub>                  | T <sub>A</sub> = + 25                                 | -30     |        | +30      | %              |

| 抵抗值温度係数                                        | R <sub>AB</sub> / T              | V <sub>AB</sub> =V <sub>DD</sub> ,ワイパー無接続             |         | 700    |          | ppm/           |

| 公称抵抗値マッチ                                       | R/R <sub>AB</sub>                | CH1から2,3,4または5,6;V <sub>AB</sub> =V <sub>DD</sub>     |         | 0.25   | 1.5      | %              |

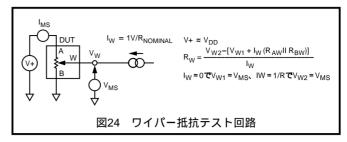

| ワイパー抵抗値                                        | R <sub>W</sub>                   | I <sub>w</sub> =1 V/R,V <sub>DD</sub> = +5V           |         | 50     | 100      | 70             |

| すべてのVR <b>に適用されるポテンショメータ</b> :                 |                                  |                                                       |         |        | 100      |                |

| 解像度                                            | N                                |                                                       | 8       |        |          | Bits           |

| 微分非直線性4                                        | DNL                              |                                                       | -1      | ± 1/4  | +1       | LSB            |

| 積分非直線性 <sup>4</sup>                            | INL                              |                                                       | -2      | ± 1/2  | +2       | LSB            |

| 分圧器温度係数                                        | V <sub>w</sub> / T               | Code=40 <sub>H</sub>                                  | -       | 15     | '-       | ppm/           |

| フルスケール誤差                                       | V <sub>WFSE</sub>                | Code=76H                                              | -2      | -1     | 0        | LSB            |

| ゼロスケール誤差                                       | V <sub>WZSE</sub>                | Code=00 <sub>H</sub>                                  | 0       | +1     | +2       | LSB            |

| でロスケール <u>鉄差</u><br>抵抗器端子                      | V WZSE                           | Code=oo <sub>H</sub>                                  | 0       | TI     | +2       | LOD            |

| 電圧範囲5                                          | W W W                            |                                                       | Vss     |        | \/       | V              |

|                                                | $V_A, V_B, V_W$                  | f 1MUz ガランドに対して測字 Code 40                             | V SS    | 15     | $V_{DD}$ |                |

| 容量 <sup>6</sup> A <sub>X</sub> ,B <sub>X</sub> | $C_A, C_B$                       | f=1MHz,グランドに対して測定、Code=40 <sub>H</sub>                |         | 45     |          | pF             |

| 容量 <sup>6</sup> W <sub>X</sub>                 | Cw                               | f=1MHz,グランドに対して測定、Code=40 <sub>H</sub>                |         | 60     | _        | pF             |

| シャットダウン電流で                                     | I <sub>A_SD</sub>                | ., ., ., ., .,                                        |         | 0.01   | 5        | μΑ             |

| 同相モード漏洩電流                                      | Ісм                              | $V_A = V_B = V_W = 0, V_{DD} = +2.7V, V_{SS} = -2.5V$ |         | 1      |          | nA             |

| デジタル入/出力                                       | 1                                | Lea                                                   | 1 .     |        |          | 1              |

| 入力ロジック・ハイ                                      | V <sub>IH</sub>                  | $V_{DD}=+5V/+3V$                                      | 2.4/2.1 |        |          | V              |

| 入力ロジック・ロー                                      | V <sub>IL</sub>                  | V <sub>DD</sub> =+5V/+3V                              |         |        | 0.8/0.6  | V              |

| 出力ロジック・ハイ                                      | V <sub>OH</sub>                  | +5Vに対しR <sub>PULL-UP</sub> =1k                        | 4.9     |        |          | V              |

| 出力ロジック・ロー                                      | V <sub>OL</sub>                  | $I_{OL}$ =1.6mA, $V_{LOGIC}$ =+5 $V$                  |         |        | 0.4      | V              |

| 入力電流                                           | I <sub>IL</sub>                  | V <sub>IN</sub> =0Vまたは+5V                             |         |        | ± 1      | μΑ             |

| 入力容量 <sup>6</sup>                              | C <sub>IL</sub>                  |                                                       |         | 5      |          | pF             |

| 電源                                             |                                  |                                                       |         |        |          | 1              |

| 単電源入力範囲                                        | V <sub>DD</sub> Range            | V <sub>SS</sub> =0V                                   | 2.7     |        | 5.5      | V              |

| デュアル電源入力範囲                                     | V <sub>DD/SS</sub> Range         |                                                       | ± 2.3   |        | ± 2.7    | V              |

| 正極性電源電流                                        | I <sub>DD</sub>                  | V <sub>IH</sub> =+5VまたはV <sub>IL</sub> =0V            |         | 12     | 60       | μΑ             |

| 負極性電源電流                                        | I <sub>SS</sub>                  | $V_{SS}$ =-2.5 $V$ , $V_{DD}$ =+2.7 $V$               |         | 12     | 60       | μΑ             |

| 消費電力 <sup>8</sup>                              | P <sub>DISS</sub>                | V <sub>IH</sub> =+5VまたはV <sub>IL</sub> =0V            |         |        | 0.3      | mW             |

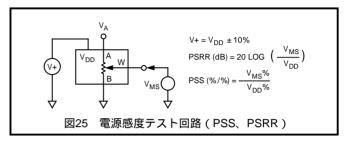

| 電源感度                                           | Pss                              | $V_{DD} = +5V \pm 10\%$                               |         | 0.0002 | 0.005    | %/%            |

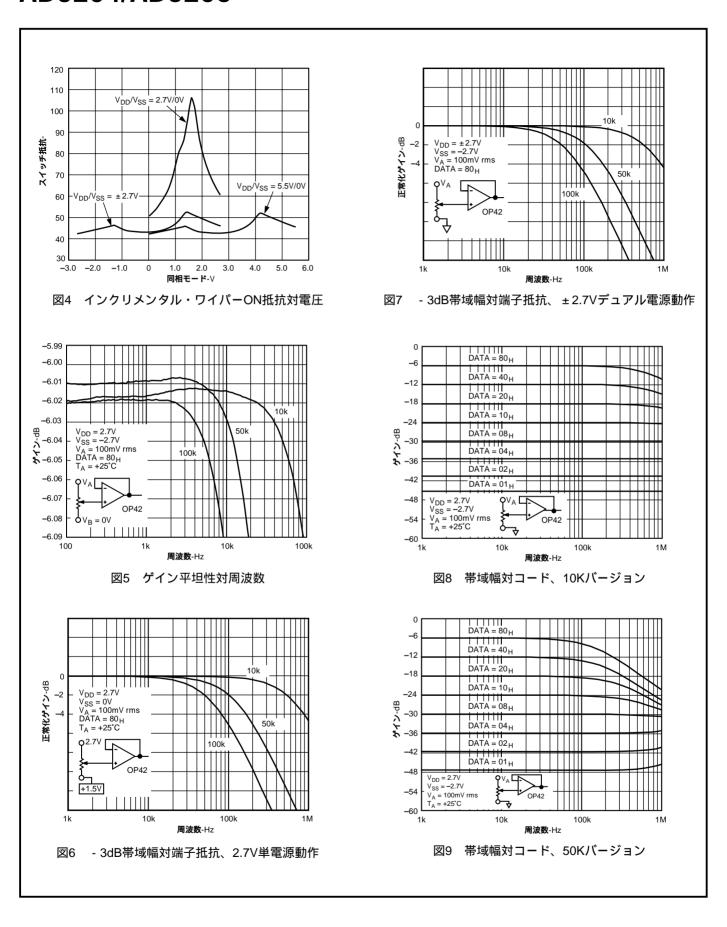

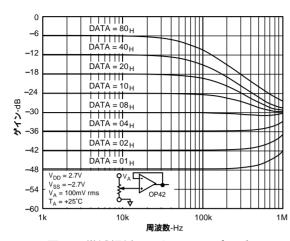

| ダイナミック特性 <sup>6,9</sup>                        | •                                |                                                       |         |        |          | •              |

| - 3dB帯域幅                                       | BW_10K                           | R <sub>AB</sub> =10k                                  |         | 721    |          | kHz            |

|                                                | BW_50K                           | R <sub>AB</sub> =50k                                  |         | 137    |          | kHz            |

|                                                | BW_100K                          | R <sub>AB</sub> =100k                                 |         | 69     |          | kHz            |

| 全高調波歪み                                         | THD <sub>w</sub>                 | $V_A=1.414V$ rms, $V_B=0V$ DC, $f=1$ kHz              |         | 0.004  |          | %              |

| Vwセトリング・タイム(10K/50K/100K)                      | ts                               | V <sub>A</sub> =5V,V <sub>B</sub> =0V,±1LSBエラー帯域      |         | 2/9/18 |          | μs             |

| 抵抗器ノイズ電圧                                       | e <sub>N_WB</sub>                | R <sub>WB</sub> =5k ,f=1kHz,PR=0                      |         | 9      |          | nV/√F          |

| 全体に適用されるインターフェース・タイミ                           |                                  | 1                                                     |         |        |          | , ,,           |

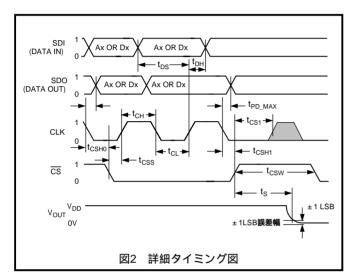

| 入力クロック・パルス幅                                    | t <sub>CH</sub> ,t <sub>CL</sub> | クロック・レベル・ハイまたはロー                                      | 20      |        |          | ns             |

| データ・セットアップ・タイム                                 | t <sub>DS</sub>                  | ) I ) ) V / V I & / C I & I                           | 5       |        |          | ns             |

| データ・ホールド・タイム                                   | t <sub>DH</sub>                  |                                                       | 5       |        |          | ns             |

| CLK対SDO伝達遅延 <sup>11</sup>                      |                                  | R <sub>L</sub> =2k ,C <sub>L</sub> <20pF              | 1       |        | 150      | ns             |

| CSセットアップ・タイム                                   | t <sub>PD</sub>                  | Ν2κ ,Ο_\20μι                                          |         |        | 100      |                |

| いヒットアッノ・ツイム                                    | t <sub>CSS</sub>                 |                                                       | 15      |        |          | ns             |

| <u>で</u> ハイ・パルフ恒                               | t <sub>CSW</sub>                 |                                                       | 40      |        |          | ns             |

| CSハイ・パルス幅                                      |                                  |                                                       | 00      |        |          |                |

| リセット・パルス幅                                      | t <sub>RS</sub>                  |                                                       | 90      |        |          | ns             |

|                                                |                                  |                                                       | 90 0    |        |          | ns<br>ns<br>ns |

2

<sup>1.</sup>代表値は + 25 およびV<sub>DD</sub> = + 5Vの場合の平均的読み出し値を表します。

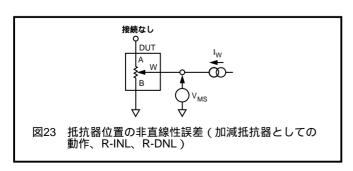

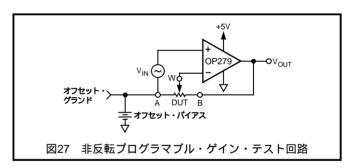

<sup>2.</sup>抵抗器のポジション非直線性誤差R-INLは、最大抵抗および最低抵抗に対するワイパーのポジション間で計測した場合の理想値からの偏差を表します。R-DNLは、隣接するタップのポジション間におけ る理想値からの相対的なステップの変化を計測したものです。各部分について単調性が保証されています。図23のテスト回路をご覧ください。 $V_{DD}$  = +3V または $V_{DD}$  = +5V の両方に対して $I_{W=}$   $V_{DD}$  /Rとな ります。

3.V<sub>AB</sub> = V<sub>DD</sub>,ワイパー (V<sub>w</sub>) = 無接続。

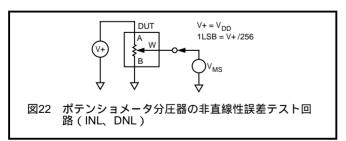

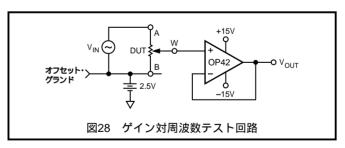

- 4.INLおよびDNLは、RDACを電圧出力D/Aコンパータのようなポテンショメータ分圧器として設定し、 $V_W$ で測定したものです。 $V_A = V_{DD}$ および $V_B = 0V$ です。DNLの仕様の最大  $\pm$  1LSBの誤差は、保証された単調性のある動作条件です。図22のテスト回路をご覧ください。

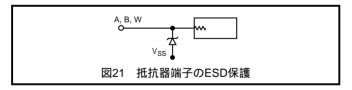

- 5.抵抗器の端子A,B,Wは相互の関係において、極性の制約がありません。

- 6.設計によって保証されていますが、製造テストには適用されません。

- 7.Ax端子における測定値です。すべてのAx端子は、シャットダウン・モードにおいて開放状態となります。

- $8.P_{DISS}$ は、( $I_{DIS} \times V_{DD}$ ) の算式により算出されたものです。 CMOSのロジック・レベル入力を使用することにより、消費電力を最小限に抑えることができます。

- 9.ダイナミック特性は、すべて $V_{DD}$  = +5Vです。

- 11.伝達遅延は、V<sub>DD</sub>,R<sub>L</sub>,C<sub>L</sub>の値に依存します。「動作」の項をご覧ください。

仕様は予告なく変更されることがあります。

| 絶対最大定格*                                              |                  | ピン温度(ハンダ付け、10秒)                                          | + 30            | 00   |

|------------------------------------------------------|------------------|----------------------------------------------------------|-----------------|------|

| (特に注記のない限り、TA = +25 )                                |                  | パッケージ消費電力                                                | $(T_JMAX-T_A)$  | / JA |

| V <sub>DD</sub> ~グランド                                | - 0.3V, +7V      | 熱抵抗 JA                                                   |                 |      |

| V <sub>SS</sub> ~グランド                                | 0V, - 7V         | P-DIP(N-24)                                              | 63              | /W   |

| V <sub>DD</sub> ~グランド                                | + 7V             | SOIC(SOL-24)                                             | 70              | /W   |

| V <sub>A</sub> ,V <sub>B</sub> ,V <sub>W</sub> ~グランド | $V_{SS}, V_{DD}$ | TSSOP-24                                                 | 143             | /W   |

| Ax-Bx,Ax-Wx,Bx-Wx                                    | ± 20mA           |                                                          |                 |      |

| デジタル入 / 出力電圧 ~ グランド                                  | 0V, +7V          | 注記                                                       |                 |      |

| 動作温度範囲                                               | - 40 ~ + 85      | * 上記の絶対最大定格を超えるストレスを加えると、デル<br>ります。この定格はストレス定格の規定のみを目的とす |                 |      |

| 最大接合温度(T₃MAX)                                        | + 150            | ョンに記載する規定値以上でのデバイス動作を定めたも                                | 5のではありません。デバイスを |      |

| 保管温度                                                 | - 65 ~ + 150     | 絶対最大定格条件に置くと、デバイスの信頼度に影響を                                | 5与えることかめります。    |      |

#### 注意

ESD(静電放電)の影響を受けやすいデバイスです。4000Vもの高圧の静電気が人体やテスト装置に容易に帯電し、 検知されることなく放電されることがあります。AD5204/AD5206は当社独自のESD保護回路を備えていますが、高 エネルギーの静電放電を受けたデバイスには回復不可能な損傷が発生することがあります。このため、性能低下や 機能喪失を回避するために、適切なESD予防措置をとるようお奨めします。

オーダー・ガイド

| 型番           | k   | 温度範囲        | パッケージ                          | パッケージ・オプション |

|--------------|-----|-------------|--------------------------------|-------------|

| AD5204BN10   | 10  | - 40 ~ + 85 | 24ピンNarrow Body(PDIP)          | N-24        |

| AD5204BR10   | 10  | - 40 ~ + 85 | 24ピンWide Body(SOIC)            | R-24/SOL-24 |

| AD5204BRU10  | 10  | - 40 ~ + 85 | 24ピンThin Shrink SOパッケージ(TSSOP) | RU-24       |

| AD5204BN50   | 50  | - 40 ~ +85  | 24ピンNarrow Body(PDIP)          | N-24        |

| AD5204BR50   | 50  | - 40 ~ + 85 | 24ピンWide Body(SOIC)            | R-24/SOL-24 |

| AD5204BRU50  | 50  | - 40 ~ + 85 | 24ピンThin Shrink SOパッケージ(TSSOP) | RU-24       |

| AD5204BN100  | 100 | - 40 ~ + 85 | 24ピンNarrow Body(PDIP)          | N-24        |

| AD5204BR100  | 100 | - 40 ~ + 85 | 24ピンWide Body(SOIC)            | R-24/SOL-24 |

| AD5204BRU100 | 100 | - 40 ~ + 85 | 24ピンThin Shrink SOパッケージ(TSSOP) | RU-24       |

| AD5206BN10   | 10  | - 40 ~ + 85 | 24ピンNarrow Body(PDIP)          | N-24        |

| AD5206BR10   | 10  | - 40 ~ + 85 | 24ピンWide Body(SOIC)            | R-24/SOL-24 |

| AD5206BRU10  | 10  | - 40 ~ + 85 | 24ピンThin Shrink SOパッケージ(TSSOP) | RU-24       |

| AD5206BN50   | 50  | - 40 ~ + 85 | 24ピンNarrow Body(PDIP)          | N-24        |

| AD5206BR50   | 50  | - 40 ~ + 85 | 24ピンWide Body(SOIC)            | R-24/SOL-24 |

| AD5206BRU50  | 50  | - 40 ~ + 85 | 24ピンThin Shrink SOパッケージ(TSSOP) | RU-24       |

| AD5206BN100  | 100 | - 40 ~ + 85 | 24ピンNarrow Body(PDIP)          | N-24        |

| AD5206BR100  | 100 | - 40 ~ + 85 | 24ピンWide Body(SOIC)            | R-24/SOL-24 |

| AD5206BRU100 | 100 | - 40 ~ + 85 | 24ピンThin Shrink SOパッケージ(TSSOP) | RU-24       |

AD5204/AD5206は5,925個のトランジスタによって構成されています。ダイサイズは、92mil×114mil、10,488平方milです。

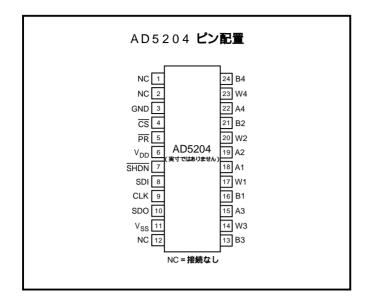

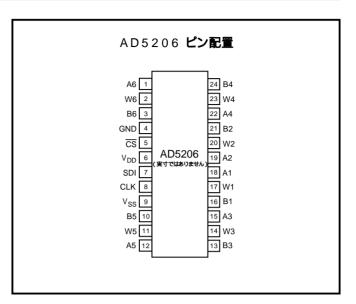

|        | Α               | D5204 <b>ピン機能説明</b>                                     | AD5206 <b>ピン機能説明</b> |                 |                                                         |  |

|--------|-----------------|---------------------------------------------------------|----------------------|-----------------|---------------------------------------------------------|--|

| ピン番号   | 記号              | 機能                                                      | ピン番号                 | 記号              | 機能                                                      |  |

| 1,2,12 | NC              | 無接続。                                                    | 1                    | A6              | A端子RDAC#6。                                              |  |

| 3      | GND             | グランド。                                                   | 2                    | W6              | ワイパーRDAC#6。addr=101B。                                   |  |

| 4      | CS              | アクティブ・ローのチップ・セレクト入                                      | 3                    | B6              | B端子RDAC#6。                                              |  |

|        |                 | 力。CSがハイに戻ると、シリアル入力レ                                     | 4                    | GND             | グランド                                                    |  |

|        |                 | ジスタにあるデータがアドレス・ビットに                                     | 5                    | CS              | アクティブ・ローのチップ・セレクト入                                      |  |

|        |                 | 応じてデコードされ、ターゲットのRDAC                                    |                      |                 | 力。CSがハイに戻ると、シリアル入力レ                                     |  |

|        |                 | ラッチへロードされます。                                            |                      |                 | ジスタにあるデータがアドレス・ビットに                                     |  |

| 5      | PR              | アクティブ・ローの中間スケールへのプリセ                                    |                      |                 | 応じてデコードされ、ターゲットのRDAC                                    |  |

|        |                 | ット。RDACレジスタを80⊣にセットします。                                 |                      |                 | ラッチへロードされます。                                            |  |

| 6      | $V_{DD}$        | 正極性の電源。 + 3Vと + 5Vの両方での動                                | 6                    | $V_{DD}$        | 正極性の電源。 + 3Vと + 5Vの両方での動                                |  |

|        |                 | 作が可能です。( IV <sub>DD</sub> I + IV <sub>SS</sub> I<5.5V ) |                      |                 | 作が可能です。( IV <sub>DD</sub> I + IV <sub>SS</sub> I<5.5V ) |  |

| 7      | SHDN            | アクティブ・ロー入力。端子Aは開放。可                                     | 7                    | SDI             | シリアル・データ入力。MSBファースト                                     |  |

|        |                 | 変抵抗#1~#4のシャットダウン制御。                                     |                      |                 | で入力します。                                                 |  |

| 8      | SDI             | シリアル・データ入力。MSBファースト                                     | 8                    | CLK             | シリアル・クロック入力。立上がりエッジ                                     |  |

|        |                 | で入力します。                                                 |                      |                 | によってトリガされます。                                            |  |

| 9      | CLK             | シリアル・クロック入力。立上がりエッジ                                     | 9                    | V <sub>SS</sub> | 負極性の電源。0Vと-2.7Vの両方での動作                                  |  |

|        |                 | によってトリガされます。                                            |                      |                 | が可能です。( IV <sub>DD</sub> I + IV <sub>SS</sub> I<5.5V )  |  |

| 10     | SDO             | シリアル・データ出力。 オープン・ドレイン・                                  | 10                   | B5              | B端子RDAC#5。                                              |  |

|        |                 | トランジスタにプルアップ抵抗が必要です。                                    | 11                   | W5              | ワイパーRDAC#5。addr=100B。                                   |  |

| 11     | V <sub>SS</sub> | 負極性の電源。0Vと - 2.7Vの両方での動                                 | 12                   | A5              | A端子RDAC#5。                                              |  |

|        |                 | 作が可能です。( IV <sub>DD</sub> I + IV <sub>SS</sub> I<5.5V ) | 13                   | B3              | B端子RDAC#3。                                              |  |

| 13     | B3              | B端子RDAC#3。                                              | 14                   | W3              | ワイパーRDAC#3。addr=010B。                                   |  |

| 14     | W3              | ワイパーRDAC#3。addr=010B                                    | 15                   | A3              | A端子RDAC#3。                                              |  |

| 15     | A3              | A端子RDAC#3。                                              | 16                   | B1              | B端子RDAC#1。                                              |  |

| 16     | B1              | B端子RDAC#1。                                              | 17                   | W1              | ワイパーRDAC#1。addr=000B。                                   |  |

| 17     | W1              | ワイパーRDAC#1。addr=000B                                    | 18                   | A1              | A端子RDAC#1。                                              |  |

| 18     | A1              | A端子RDAC#1。                                              | 19                   | A2              | A端子RDAC#2。                                              |  |

| 19     | A2              | A端子RDAC#2。                                              | 20                   | W2              | ワイパーRDAC#2。addr=001B。                                   |  |

| 20     | W2              | ワイパーRDAC#2。addr=001B。                                   | 21                   | B2              | B端子RDAC#2。                                              |  |

| 21     | B2              | B端子RDAC#2。                                              | 22                   | A4              | A端子RDAC#4。                                              |  |

| 22     | A4              | A端子RDAC#4。                                              | 23                   | W4              | ワイパーRDAC#4。addr=011B。                                   |  |

| 23     | W4              | ワイパーRDAC#4。addr=011B                                    | 24                   | B4              | B端子RDAC#4。                                              |  |

| 24     | B4              | B端子RDAC#4。                                              |                      |                 |                                                         |  |

図10 帯域幅対コード、100Kバージョン

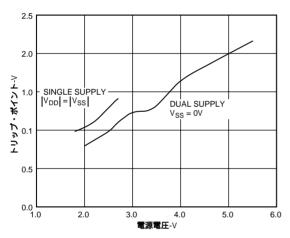

図11 デジタル入力トリップ・ポイント対電源電圧

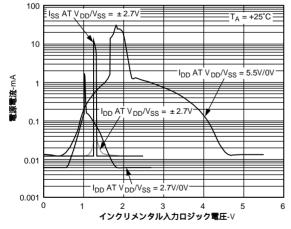

図12 電源電流対入力ロジック電圧

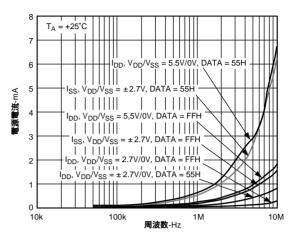

図13 電源電流対クロック周波数

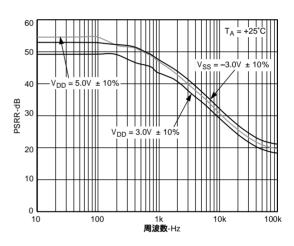

図14 電源変動除去対周波数

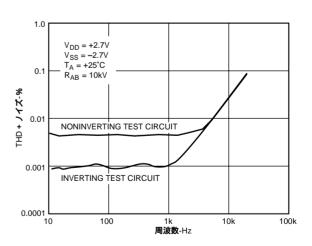

図15 全高調波歪みパルス・ノイズ対周波数

#### 動作

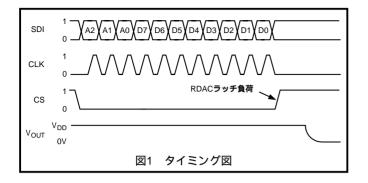

AD5204/AD5206は、4/6チャンネル、256ポジション、デジタル制御の可変抵抗器(VR)を提供します。プログラムされたVRの設定は、11ビット・シリアル・データ・ワードをSDI(シリアル・データ入力)ピンにクロック入力することで変更できます。データ・ワードのフォーマットは、MSBファーストの3つのアドレス・ビットと、これに続くMSBファーストの8ビットのデータビットという構成です。表Iに、シリアル・レジスタのデータ・ワードのフォーマットを示します。

表 ... シリアル・データのワード・フォーマット

| アドレ | ス  |                       | デー  | タ   |     |     |    |    |     |     |

|-----|----|-----------------------|-----|-----|-----|-----|----|----|-----|-----|

| B10 | В9 | В8                    | B 7 | B 6 | B 5 | B 4 | В3 | В2 | B 1 | B 0 |

| A2  | A1 | A0                    | D7  | D6  | D5  | D4  | D3 | D2 | D1  | D0  |

| MSB |    | LSB                   | MSE | 3   |     |     |    |    |     | LSB |

| 210 |    | <b>2</b> <sup>8</sup> | 27  |     |     |     |    |    |     | 20  |

AD5204/AD5206でのシリアル・レジスタ・データのB7からB0までを受信するVRラッチのアドレス割り当てについては、表Vをご覧ください。VRの出力は、ランダムのシーケンスにおいて一度に1つだけ変更することができます。AD5204のプリセットでは、PRピンをアサートすることによって中間スケールに戻すことができ、パワー・オンの時点でのフォールト状態からの回復を簡略化しています。両モデルとも、パワー・オンの時点で、予め定められた中間スケールの位置にワイパーを戻すパワー・オン・プリセット機能を内蔵しています。さらに、AD5204では、パワーのシャットダウンのためのSHDNピンを備えており、RDACを消費電力ゼロの状態とし、端子Axを開放状態、ワイパーをBxに接続することで、VRでリーク電流のみが消費される状態とすることができます。シャットダウン・モードでは、VRラッチの設定は保持されるため、パワー・シャットダウンから動作状態に復帰する場合でも、VRの設定はシャットダウン前の抵抗値に対応したものとなります。

## 可変抵抗器のプログラミング

#### 加減抵抗器動作

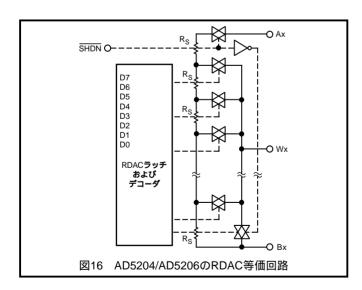

端子AとBの間の公称抵抗値は、10k 、50k 、100k のものが 用意されています。製品の型番の最後の桁が、例えば10k = 10、100k = 100のように、この公称抵抗を表しています。VRの 公称抵抗(RAB)には、ワイパー端子によってアクセスできる256の接点位置と、B端子接点があります。RDACラッチの8ビットのデータ・ワードはデコードされて、256の設定のうちの1つを選択します。ワイパーの最初の接続は、データ00Hに対応するB端子から始まります。このB端子との接続では、ワイパーの接触抵抗である45 が含まれます。2番目の接続(10k の場合)では、データ01Hに対する84 [= RBA (公称抵抗)/256 + Rw = 39 + 45 ]の位置となります。3番目の接続は、データ02Hに対する78 + 45 = 123 の位置となります。LSBに1が加算されるごとに、ワイパーは抵抗値の上がる方向に進められ、最後のタップでは抵抗値は10006 となります。ワイパーは、直接A端子に接続されることはありません。簡略化されたRDACの等価回路については、図16をご覧ください。

WxとBxの間においてデジタル的にプログラムされる出力抵抗の一般的な計算式は、以下のようになります。

$$R_{WB}(Dx) = (Dx)/256 \times R_{BA} + R_{W}$$

(1)

Dxは8ビットのRDACxラッチに保持された値であり、 $R_{BA}$ は端子間の公称抵抗値です。

例えば、 $V_B = 0$ VでA端子が開放の状態では、次のRDACラッチのコードに対して次の出力抵抗値が設定されます (10kのポテンショメータに対する値です)。

表II

| D(10 <b>進</b> ) | R <sub>WB</sub> - | 出力状態                |

|-----------------|-------------------|---------------------|

| 255             |                   | フル・スケール             |

| 128             | 5045              | 中間スケール ( PR = 0状態 ) |

| 1               | 84                | 1LSB                |

| 0               | 45                | ゼロ・スケール(ワイパーの接触抵抗)  |

ゼロ・スケール状態でも一定のワイパー抵抗値45 があることに ご注意ください。特性の劣化や内部スイッチの接点の破壊を防止するために、WとBの間での電流を最大値である20mA以内と するように注意してください。

RDACによって置き換えられる機械式ポテンショメータ同様、完全に対称な構成となっています。ワイパーWと端子Aの抵抗によって、デジタル的に制御される抵抗R<sub>WA</sub>が得られます。この端子を使うときは、必ずB端子をワイパーに接続します。R<sub>WA</sub>への抵抗値の設定により、最大の抵抗値からスタートし、ラッチにロードされるデータの値が増加するにつれ減少します。この動作の一般的な計算式は、次の通りです。

$$R_{WA}(Dx) = (256 - Dx)/256 \times R_{BA} + R_{W}$$

(2)

Dxは8ビットのRDACxラッチに保持された値であり、 $R_{BA}$ は端子間の公称抵抗値です。例えば、 $V_A=0V$ でB端子がワイパーWに接続された状態では、次のRDACラッチのコードに対して次の出力抵抗値が設定されます。

表III

|         |                   | 54                  |

|---------|-------------------|---------------------|

| D (10進) | R <sub>WA</sub> - | 出力状態                |

| 255     | 84                | フル・スケール             |

| 128     | 5045              | 中間スケール ( PR = 0状態 ) |

| 1       | 10006             | 1LSB                |

| 0       | 10045             | ゼロ・スケール             |

8

RBAの代表的な分布は、チャンネル間で±1%以内となっています。しかしながら、デバイス間での差異は製造ロットに依存し、±30%程度の違いがあります。RBAの温度による変化については、温度係数が700ppm/となっています。

## ポテンショメータの分圧器のプログラム

#### 電圧出力動作

デジタルのポテンショメータを使用すれば、任意の端子に対して印加された入力電圧に比例する出力電圧が簡単に得られます。例えば、A端子を5Vに、B端子をグランドに接続した場合には、ワイパーにおける出力電圧を0Vから、+5Vより1LSB分だけ低い電圧の間の、任意の値に変化させることができます。各LSBに対応する電圧は、ポテンショメータの分圧器の端子AB間に印加された電圧を接触位置の数である256で割った値に等しくなります。端子AB間に印加される任意の入力電圧について、グランドに対する出力電圧を算出する一般的な計算式は、以下のようになります。

$$V_W(Dx) = Dx/256 \times V_{AB} + V_B \tag{3}$$

デジタル・ポテンショメータを分圧器モードで動作させると、温度変化に対する精度がさらに向上します。ここで、出力電圧は内部の抵抗器の分圧の比に依存し、絶対的な抵抗値とは関係がありません。このため、温度によるドリフトは15ppm/まで向上します。

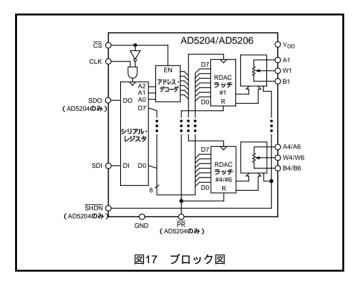

### デジタル・インターフェース

AD5204/AD5206には、標準の3線シリアル入力制御インターフェースが備えられています。3つの入力とは、クロッグ(CLK)でいた。シリアル・データ入力(SDI)です。立上がリエッジを基準とする CLK入力は、シリアル入力レジスタに誤ったデータを入力しないように、遷移の波形が整ったものでなければなりません。標準のロジック・ファミリーによって良好に動作します。製品の評価のために機械的なスイッチを使用する場合には、フリップ・フロップや他の適当な手段によって信号のバウンドを防止する必要があります。図17は、内部デジタル回路をさらに詳細に示したものです。でSがアクティブ・ローの状態に保たれているときに、表IVに示すように、クロックの立上がリエッジによって、データがシリアル・レジスタにロードされます。正極性(VDD)と負極性(VSS)の電源を使用する場合にも、ロジック・レベルはデジタル・グランド(GND)を基準として

判断されます。

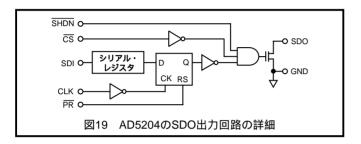

シリアル・データ出力(SDO)ピンには、オープン・ドレインのNチャ ンネルFETを用いています。この出力でデータを次のパッケージ のSDIピンに転送するためには、プルアップ抵抗が必要です。プ ルアップ抵抗の終端電圧は、AD5204のSDO出力デバイスのVDD より高い電圧でもかまいません。例えば、AD5204をVDD = 3.3V の電圧で動作させ、次のデバイスとのインターフェースのためのプ ルアップ電圧を+5/とすることができます。これにより、1つのプロ セッサのシリアル・データ・ラインから、いくつかのRDACをデージ ー・チェーン接続することが可能となります。SDIピンにプルアップ 抵抗を接続して次のデバイスと直列に接続する場合には、クロッ ク周期を長くする必要があります。データ転送を確実にするには、 デバイス間のデージー・チェーンのノードであるSDO-SDIの容量 性負荷を考慮する必要あります。デージー・チェーンを使う場合に は、各パッケージのすべてのビットがそれぞれのシリアル・レジス タに転送されるまでの間、CSをローに保って、アドレス・ビットとデ ータ・ビットが適正なデコードの位置に置かれるようにする必要が あります。2つのAD5204の4つのチャンネルのRDACがデージー・ チェーンされる場合には、表」に示すワード・フォーマットに従った 22ビットのアドレスおよびデータが必要となります。シャットダウン (SHDN)の間、SDO出力ピンは、プルアップ抵抗での電力消費 をなくすために強制的にオフ(ロジック・レベル・ハイの状態)にさ れます。図19に、SDO出力回路の等価回路を示します。

表 IV 入力ロジック制御真偽表

| CLK | CS  | PR  | SHDN | レジスタの動作                                   |

|-----|-----|-----|------|-------------------------------------------|

| L   | L   | Н   | Н    | SR動作せず、SDOピン・イネーブル。                       |

| Р   | L   | Н   | Н    | SDIピンから1ビットをシフト入力。                        |

|     |     |     |      | 入力されているビットの11番目が                          |

| X   | P   | Н   | н    | SDOからシフト出力される。<br> A2.A1.A0のデコード結果に応じて    |

| ^   |     | 111 | 11   | SRデータをRDACラッチにロード                         |

|     |     |     |      | (表V参照)。                                   |

| X   | Н   | Н   | Н    | ノー・オペレーション                                |

| X   | X   | L   | Н    | すべてのRDACラッチを中間スケー                         |

|     |     |     |      | ルに設定、ワイパーが中央に設定さ                          |

| Х   | н   | Р   | Н    | │れSDOラッチがクリアされる。<br>│すべてのRDACラッチに80μをラッチ。 |

|     | • • |     | 1    |                                           |

| Χ   | Н   | Н   | L    | すべての抵抗器のA端子を開放状態                          |

|     |     |     |      | │とし、WをBに接続し、SDOの出力<br>│トランジスタをオフとする。      |

|     |     |     |      | 「フンノハノでガノこりる。                             |

注:P=立上がりエッジ、X=任意、SR=シフト・レジスタ

表∨ アドレス・デコード・テーブル

| A 2 | A 1 | A 0 | デコードされるラッチ      |

|-----|-----|-----|-----------------|

| 0   | 0   | 0   | RDAC#1          |

| 0   | 0   | 1   | RDAC#2          |

| 0   | 1   | 0   | RDAC#3          |

| 0   | 1   | 1   | RDAC#4          |

| 1   | 0   | 0   | RDAC#5、AD5206のみ |

| 1   | 0   | 1   | RDAC#6、AD5206のみ |

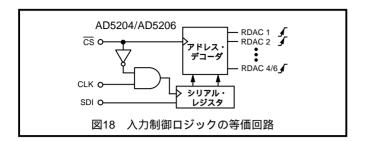

仕様の表に示すデータ・セットアップ・タイムとデータ・ホールド・タイムは、データの有効期間の条件を示します。シリアル・レジスタに入力された最後の11ビットは、CSがハイに戻るときに保持されます。また、CSがハイになるときに、アドレス・デコーダをゲートして、立上がリエッジによってトリガされる4または6のうちの1つのRDACラッチをイネーブルします。詳しくは図18をご覧ください。

ターゲットのRDACラッチにシリアル・データ・ワードの最後の8ビットがロードされ、1回のDACの更新が完了します。4つの独立した8ビットのデータ・ワードをクロックに従って入力し、4つのVRの設定のすべてを変更する必要があります。

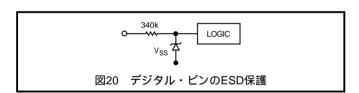

図20に示すように、すべてのデジタル・ピンは直列に接続された 入力抵抗と並列に挿入されたツェナーESDの構造によって保護 されています。この構成は、デジタル・ピンのCS、SDI、SDO、PR、 SHDN、CLKで採用されています。

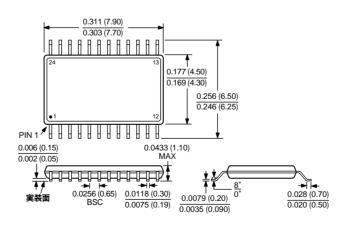

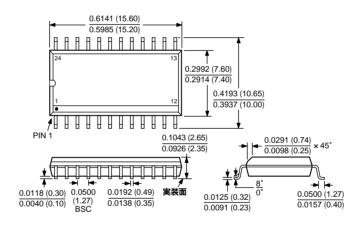

## 外形寸法

サイズはインチと (mm) で示します。

### 24ピン Narrow Body PDIP (N-24)

### 24 L'> SOIC (R-24/SOL-24)

### 24 L'> Thin Shrink SO Package (TSSOP) (RU-24)