UG-1295

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### Hardware Reference Manual for the ADRV9008-1, ADRV9008-2, and ADRV9009

### INTRODUCTION

This hardware reference manual serves as the main source of information for system engineers and software developers using the ADRV9008-1 receiver (Rx), ADRV9008-2 transmitter (Tx) and observation receiver (ORx), and the ADRV9009 transceiver.

# UG-1295

# ADRV9008-1/ADRV9008-2/ADRV9009 Hardware Reference Manual

# TABLE OF CONTENTS

| Introduction 1                                         |

|--------------------------------------------------------|

| Revision History                                       |

| System Overview                                        |

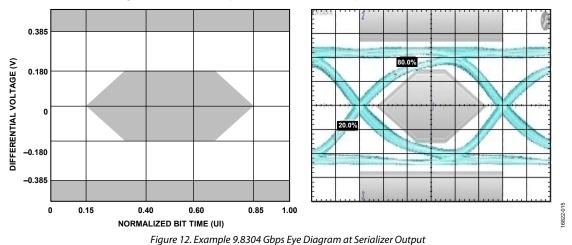

| System Architecture Description                        |

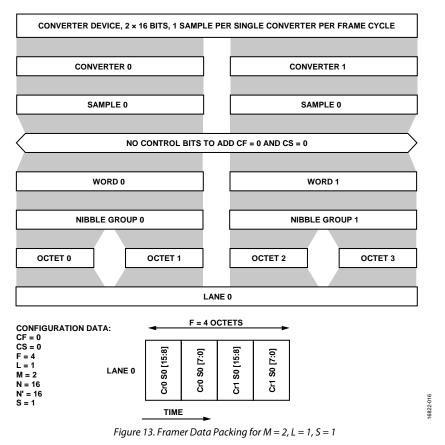

| Software Architecture                                  |

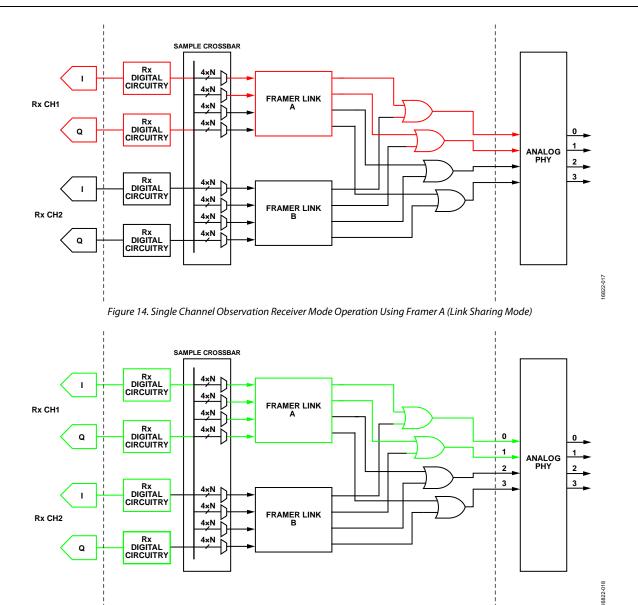

| Folder Structure                                       |

| Private vs. Public API Functions                       |

| Hardware Abstraction Layer (HAL)7                      |

| HAL Interface Definition                               |

| Data Types and Enumerations9                           |

| Detailed Hal Function Definitions10                    |

| Software Integration                                   |

| Implementing Hardware Abstraction Interface            |

| Developing the Application20                           |

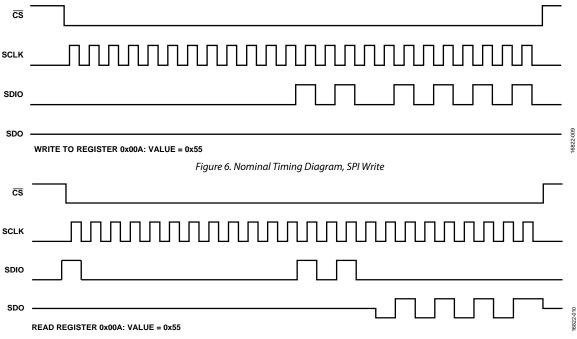

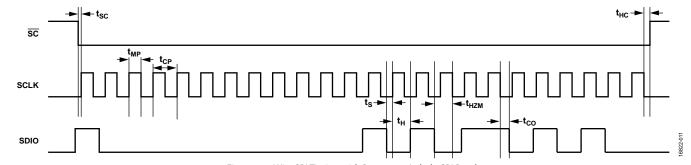

| SPI                                                    |

| SPI Configuration Using API Function                   |

| SPI Bus Signals                                        |

| SPI Data Transfer Protocol                             |

| Timing Diagrams                                        |

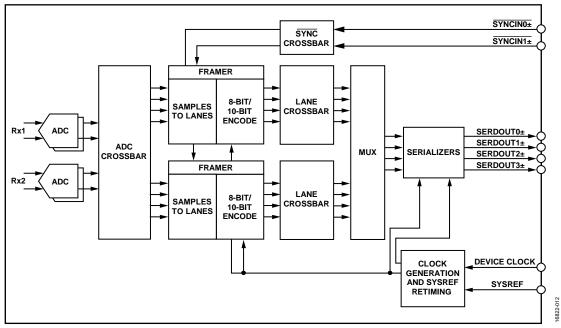

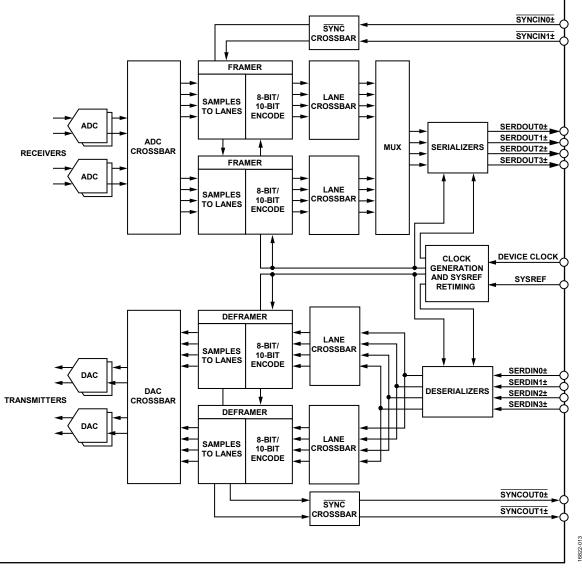

| JESD204B Interface                                     |

| Receiver (ADC) Datapath                                |

| Transmitters (DAC) Datapath 46                         |

| Multichip Synchronization54                            |

| Link Establishment55                                   |

| Compatibility with Xilinx JESD204B FPGA IP 57          |

| Link Sharing in TDD Mode57                             |

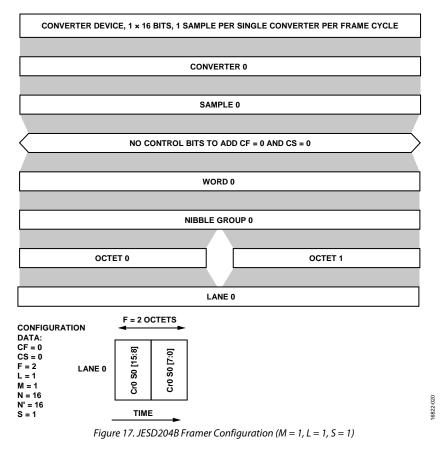

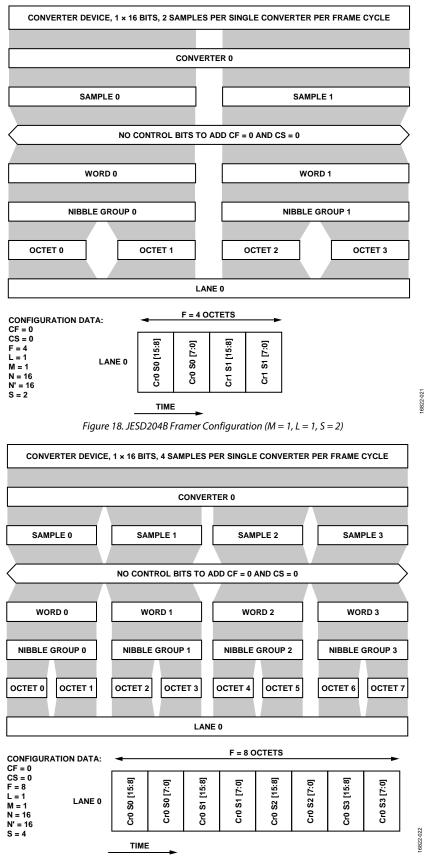

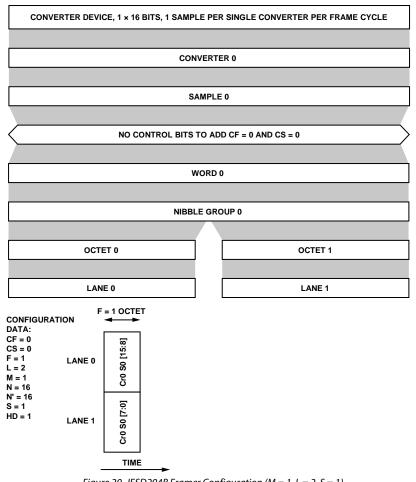

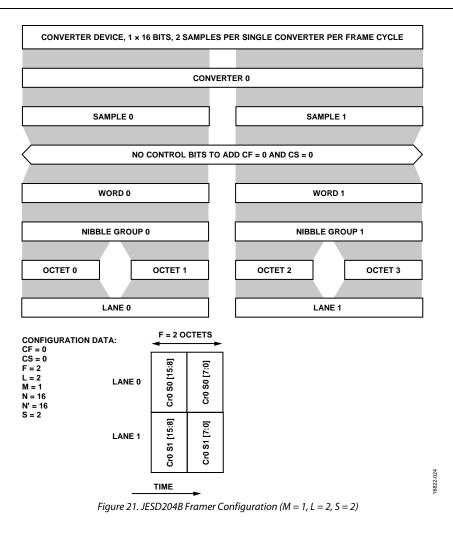

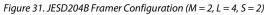

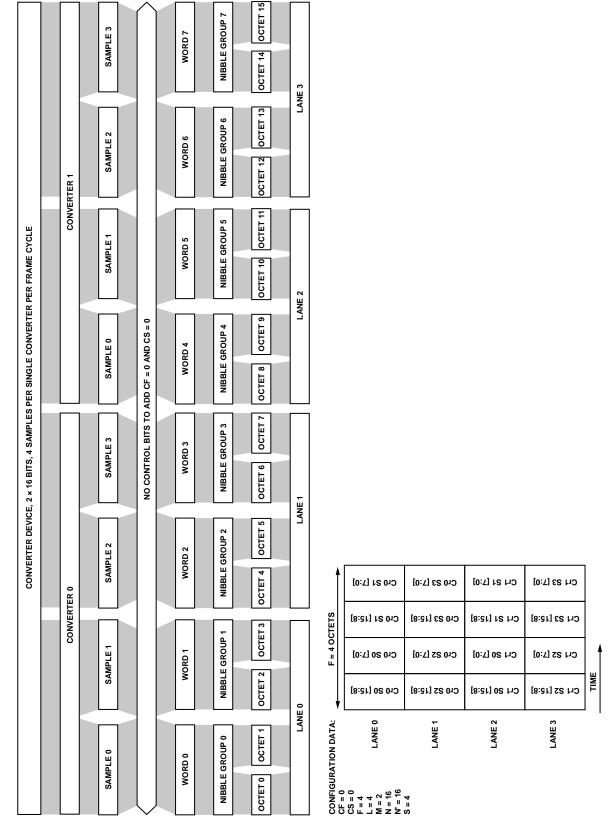

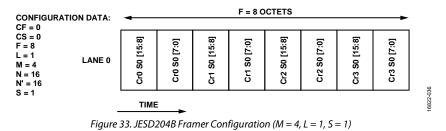

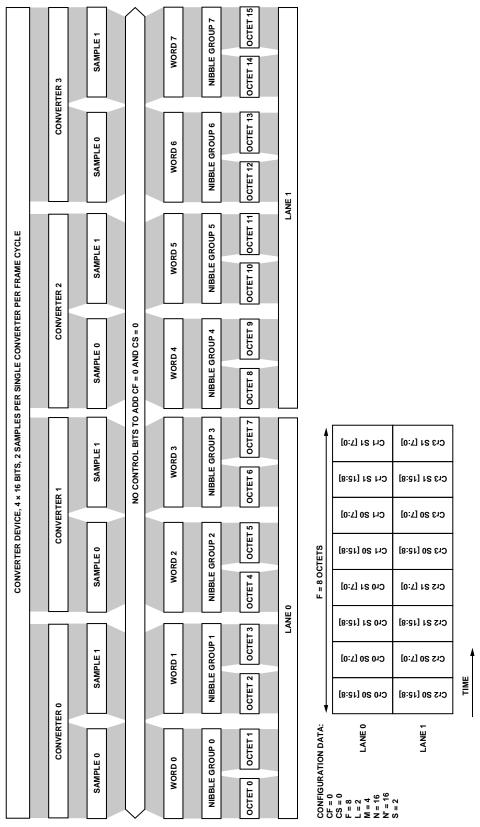

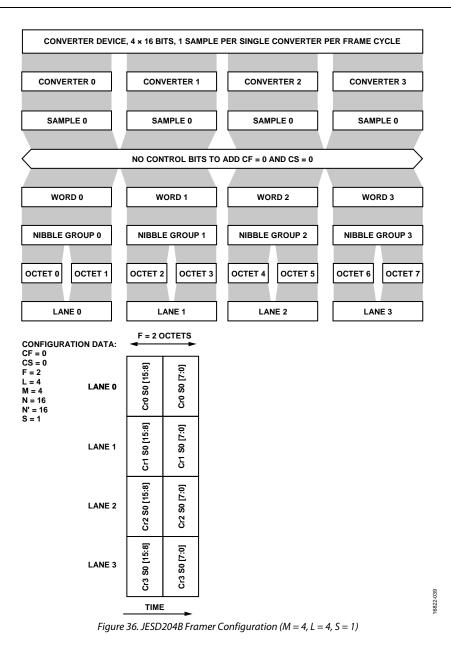

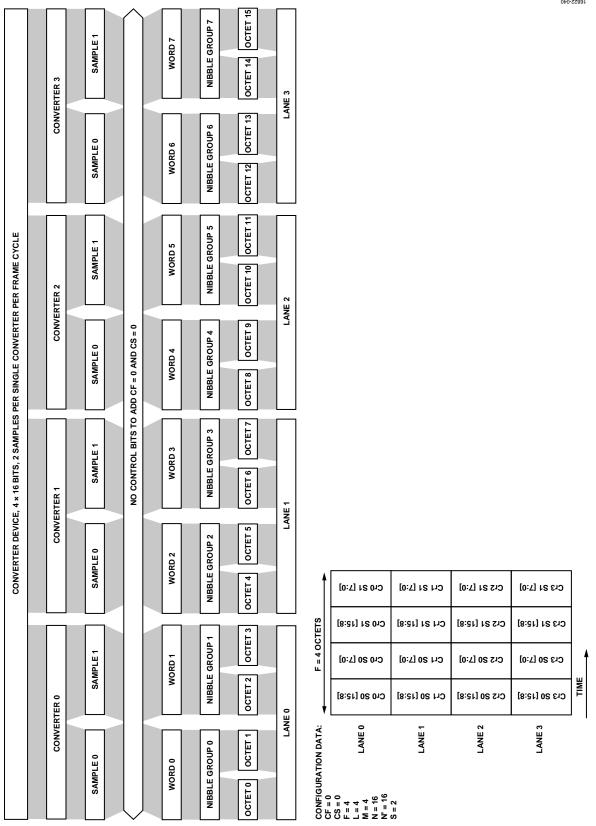

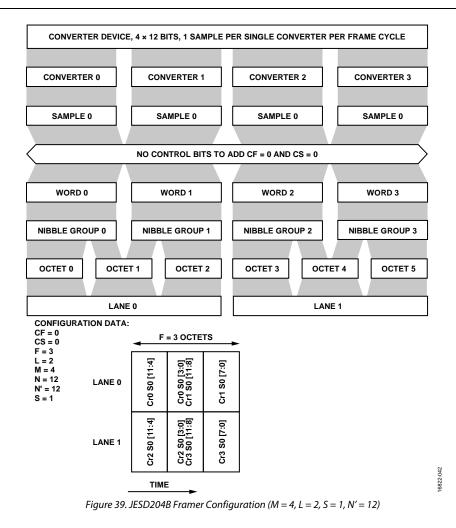

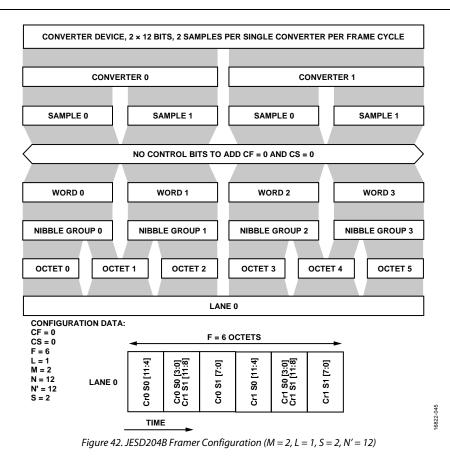

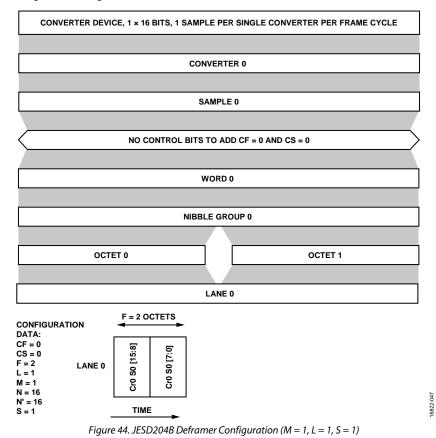

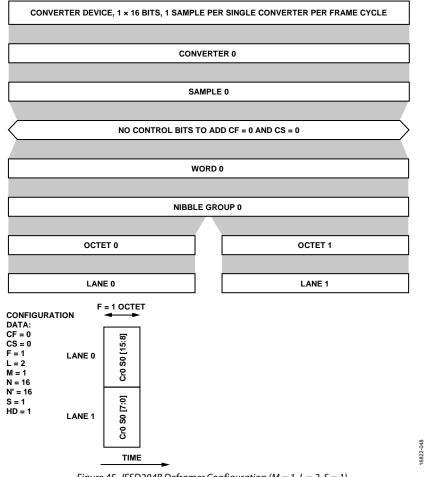

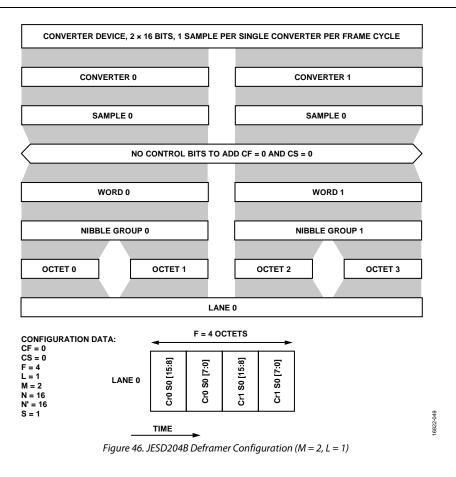

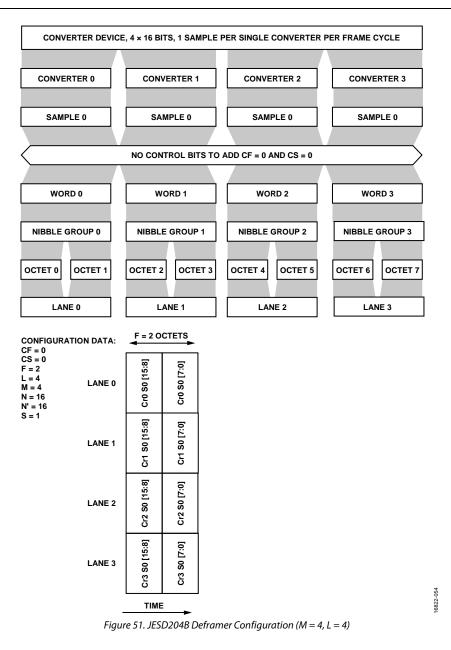

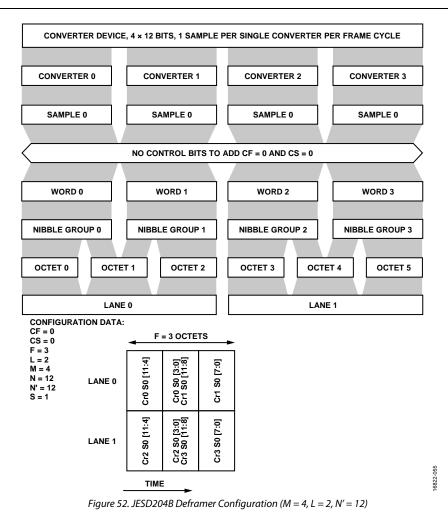

| JESD204B Configuration Diagrams 59                     |

| System Initialization                                  |

| Device Initialization Sequence93                       |

| Device Initialization Example Code                     |

| System Shutdown94                                      |

| Device Shutdown Sequence94                             |

| Stream Processor and System Control                    |

| Stream Processor95                                     |

| System Control95                                       |

| Use Cases                                              |

| GSM Use Cases 101                                      |

| GSM 1800 Digital Cellular System (DCS) Band101         |

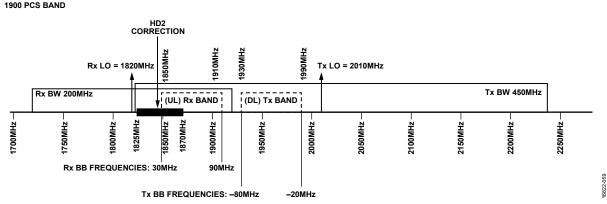

| GSM 1900 Personal Communications Service (PCS) Band101 |

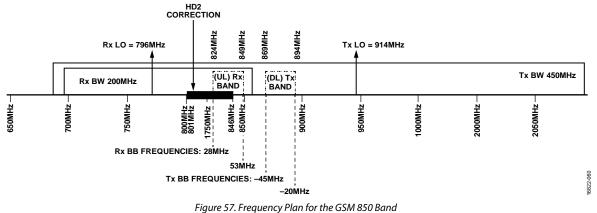

| GSM 850 Band 102                                       |

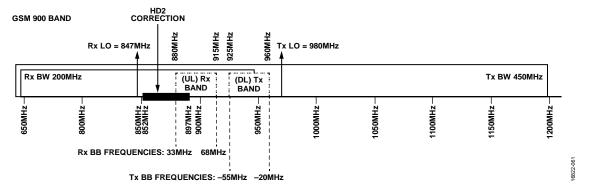

| GSM 900 Band                                                           | 102   |

|------------------------------------------------------------------------|-------|

| Synthesizer Configuration                                              | 103   |

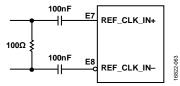

| Connections for External Clock (REF_CLK_IN± Pins)                      | 104   |

| REF_CLK_IN± Signal Phase Noise Requirements                            | 104   |

| Synthesizer Software Configuration                                     | 105   |

| RF PLL Frequency Change Procedure                                      | 107   |

| RF PLL Loop Filter Recommendations                                     | 110   |

| RF PLL Loop Filter Change Procedure                                    | 110   |

| RF PLL Resolution                                                      | 111   |

| RF PLL Lock Status                                                     | 112   |

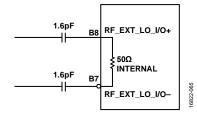

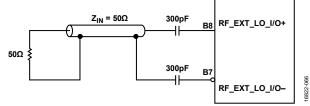

| Connections for External LO                                            | 113   |

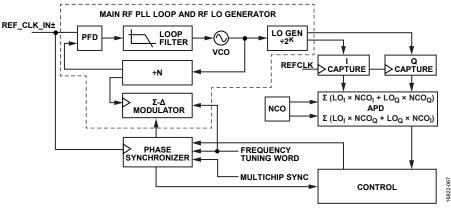

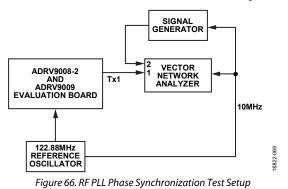

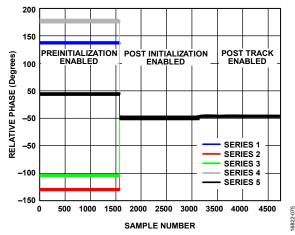

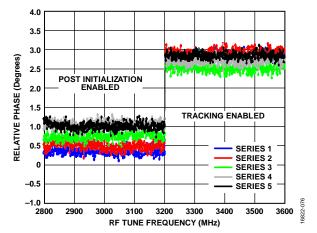

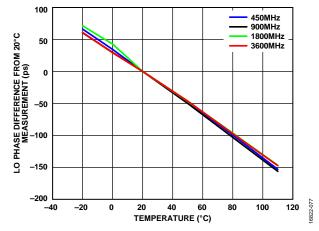

| RF PLL Phase Synchronization                                           | 114   |

| RF PLL Frequency Hopping                                               | 121   |

| Receiver Gain Control                                                  | 125   |

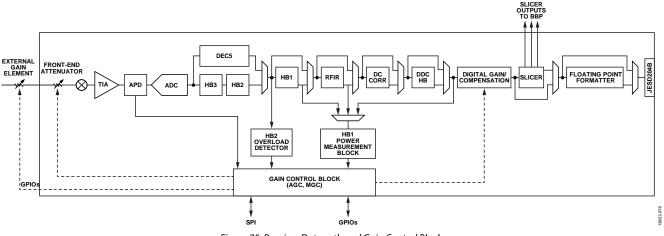

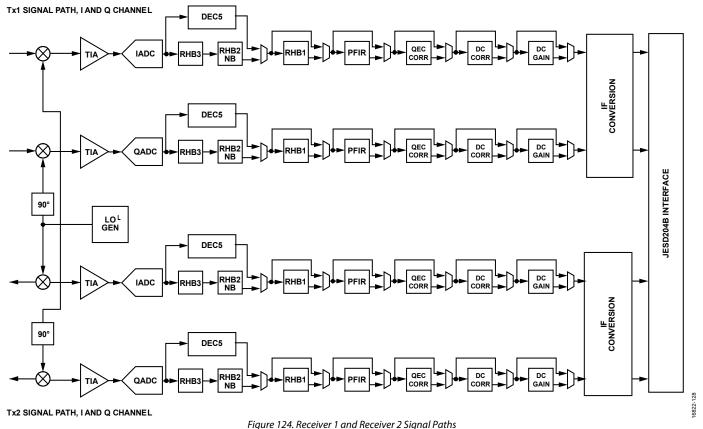

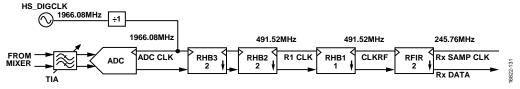

| Receiver Datapath                                                      | 125   |

| Gain Control Modes                                                     | 127   |

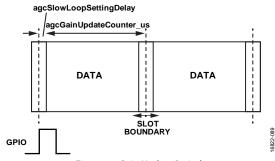

| AGC Clock and Gain Block Timing                                        | 134   |

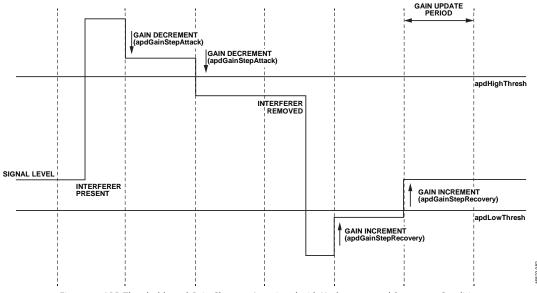

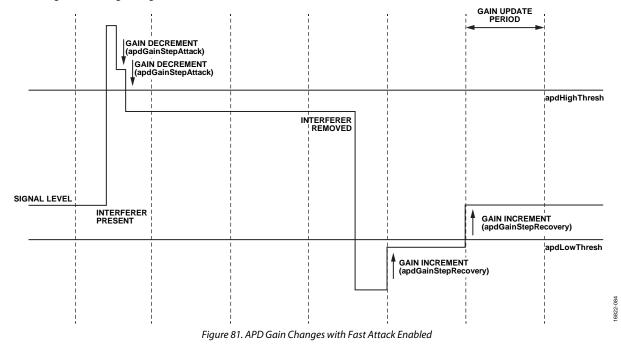

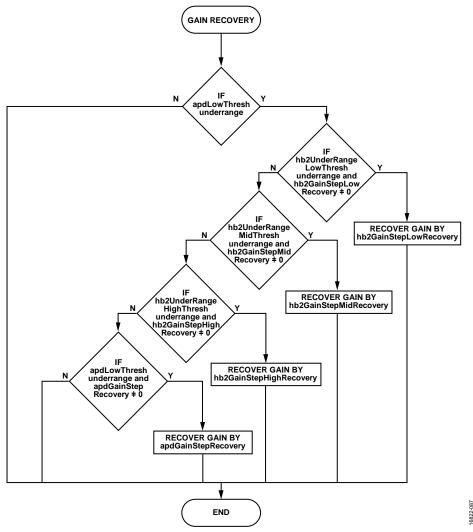

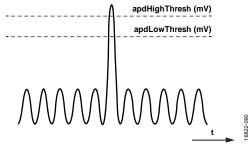

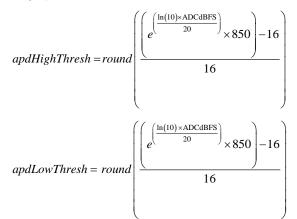

| APD                                                                    | 135   |

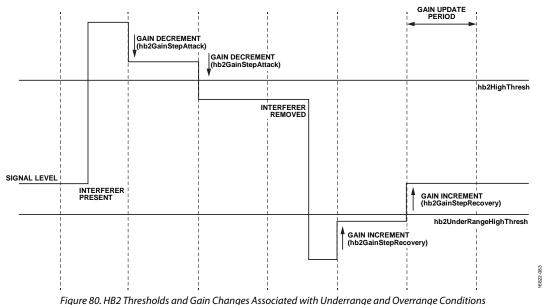

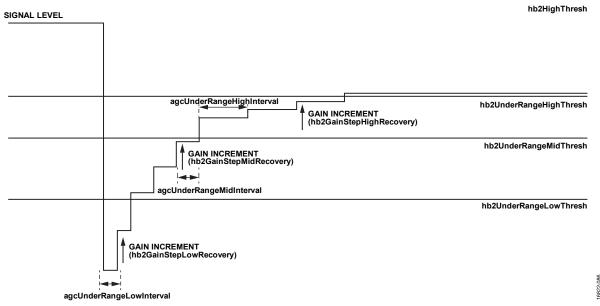

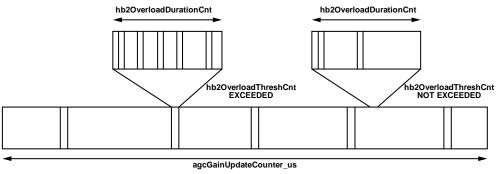

| HB2 Peak Detector                                                      | 136   |

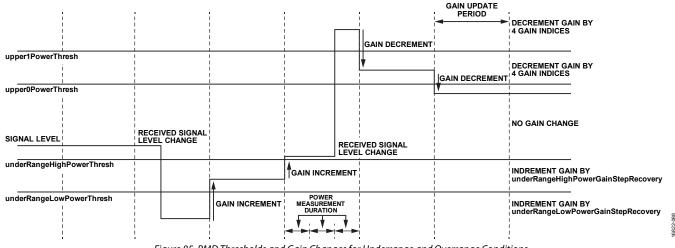

| Power Detector                                                         | 138   |

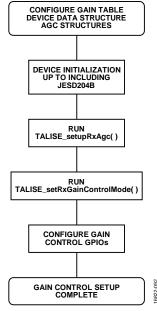

| Gain Control API Programming                                           | 138   |

| Gain Control Data Structures                                           | 139   |

| Sample Python Scripts                                                  | 144   |

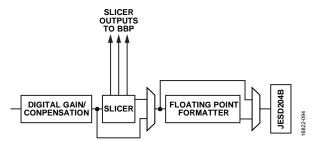

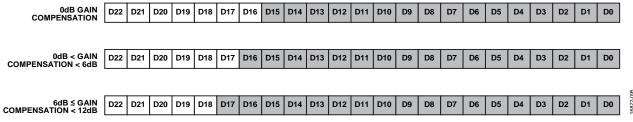

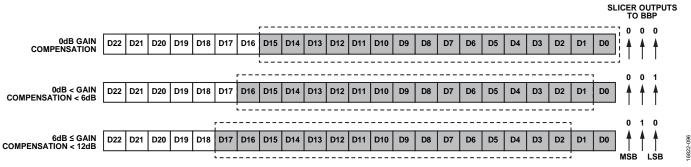

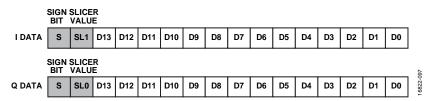

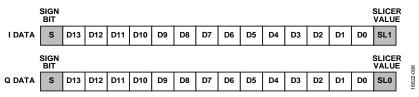

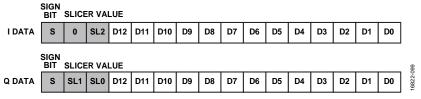

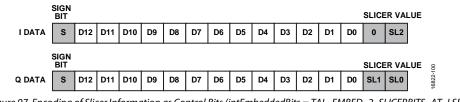

| Gain Compensation, Floating Point Formatter, and Slice                 | r 149 |

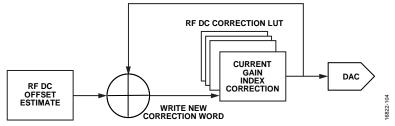

| Receiver DC Offset Calibration                                         | 158   |

| Receiver DC Offset Correction Circuitry                                | 158   |

| QEC, Calibration, and Arm Configuration                                | 161   |

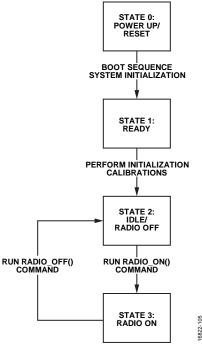

| Arm State Machine Overview                                             | 161   |

| Loading the Arm Processor                                              | 162   |

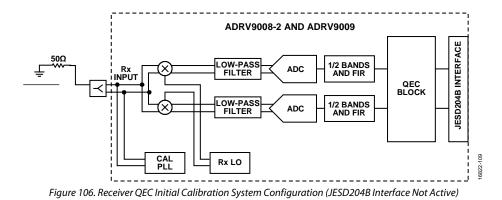

| ADRV9008-1, ADRV9008-2, and ADRV9009 Initial Calibrations              | 162   |

| ADRV9008-1, ADRV9008-2, and ADRV9009 Tracking                          | 102   |

| Calibrations                                                           | 164   |

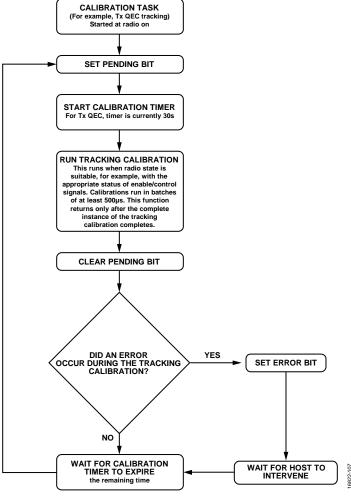

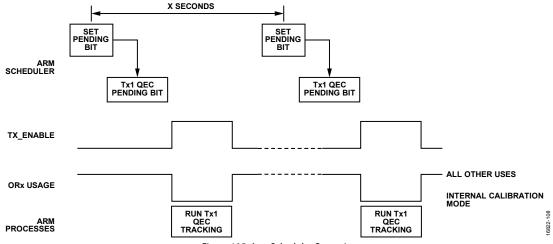

| ADRV9008-1, ADRV9008-2, and ADRV9009 Tracking<br>Calibration Scheduler | 165   |

| System Considerations for Arm Calibrations                             | 169   |

| Arm GPIO Pins                                                          | 181   |

| Initialization Calibration Errors                                      | 187   |

| Tracking Calibration Monitoring                                        | 190   |

| Reading the Arm Version                                                | 193   |

| Performing an Arm Memory Dump                                          | 193   |

|                                                                        |       |

| Filter Configuration                               |

|----------------------------------------------------|

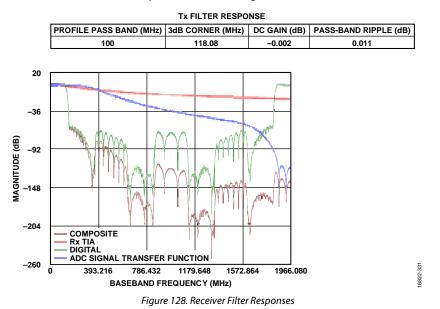

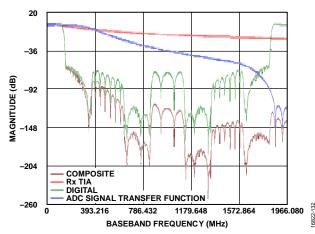

| Receiver Signal Path                               |

| Receiver Transimpedance Amplifier (TIA) 196        |

| Receive DEC5 197                                   |

| Receive Half-Band 3 (RHB3) Filter 197              |

| Receive Half-Band 2, Narrow-Band (RHB2) Filter 197 |

| Receive Half-Band 1 (RHB1) Filter 197              |

| Receiver Finite Impulse Response (RFIR) Filter 197 |

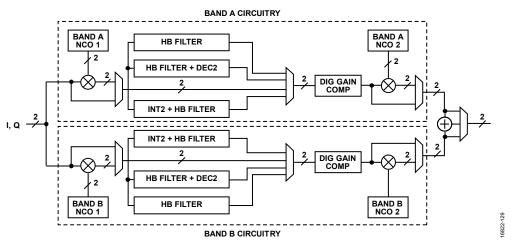

| Receiver IF Conversion 197                         |

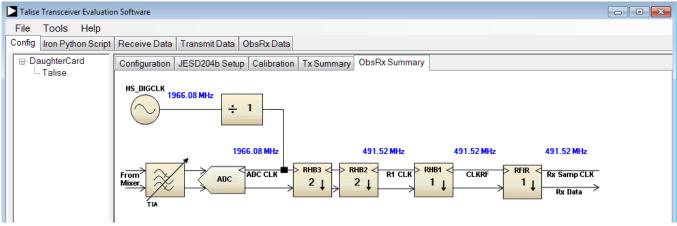

| Receiver Signal Path Example 199                   |

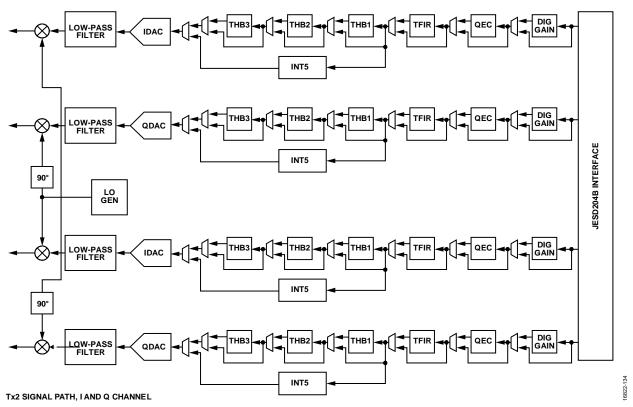

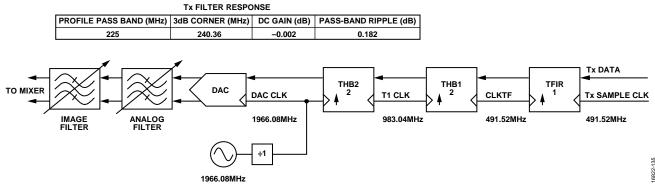

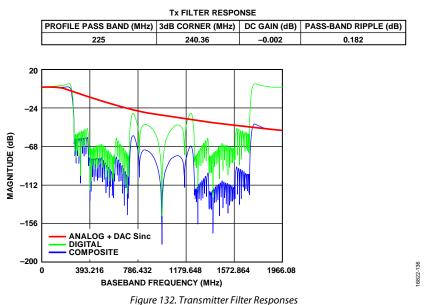

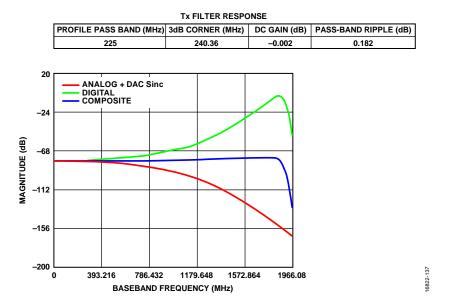

| Transmitter Signal Path 202                        |

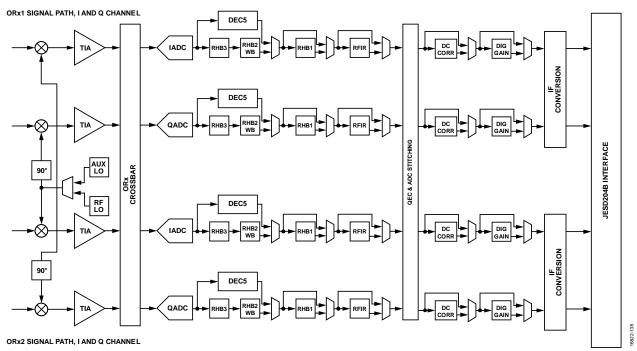

| Observation Receivers Signal Path 205              |

| Filter Configuration API Functions 208             |

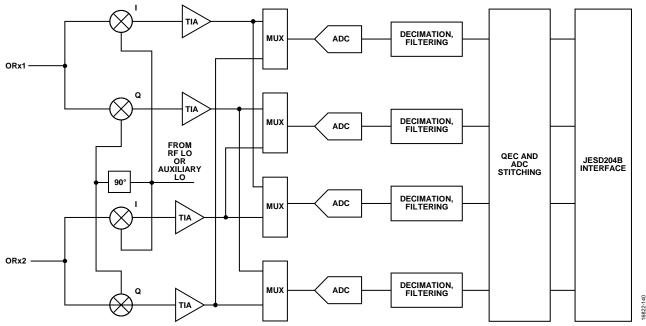

| Observation Receiver                               |

| Observation Receiver API Structure 209             |

| Observation Channel Control 210                    |

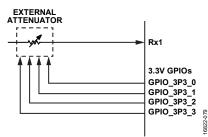

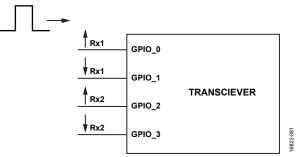

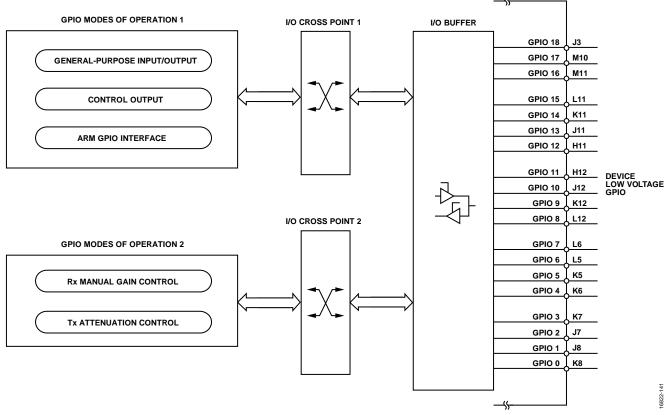

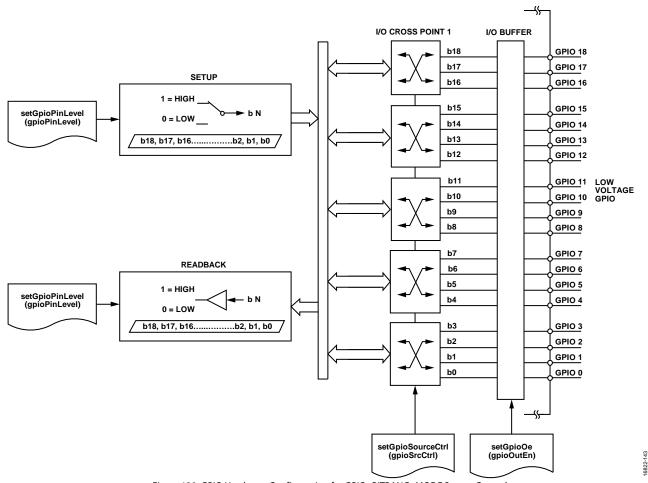

| GPIO Configuration 211                             |

| Low Voltage GPIO Operation 212                     |

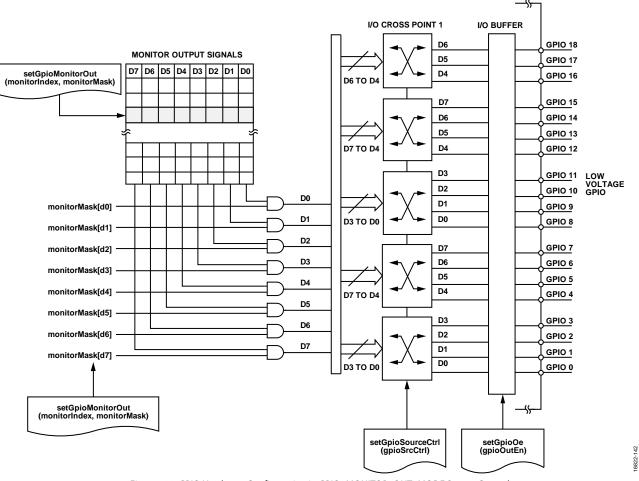

| GPIO Monitor Mode Output 213                       |

| GPIO Bitbang Mode 215                              |

| GPIO Arm Output Operation 215                      |

| GPIO Slicer Features                               |

| <b>REVISION H</b> | IISTORY |

|-------------------|---------|

|-------------------|---------|

9/2018—Revision 0: Initial Version

| GPIO For Receiver Manual Gain Control Mode  |     |

|---------------------------------------------|-----|

| Pin Control                                 |     |

| Transmitter Attenuation Control, SPI2 Port  |     |

| Low Voltage GPIO API Functions              |     |

| General-Purpose Interrupt Operation         |     |

| GP_INTERRUPT Pin API Functions              | 224 |

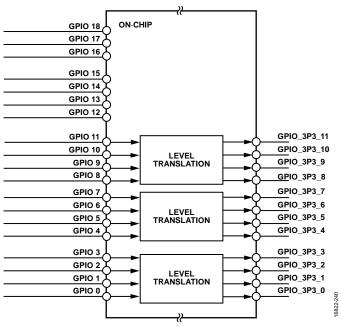

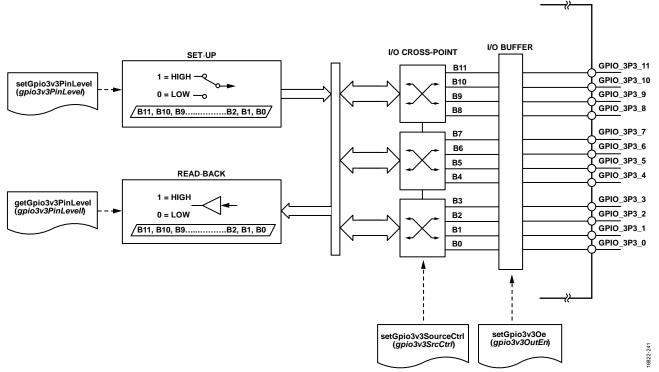

| 3.3 V GPIO Operation                        |     |

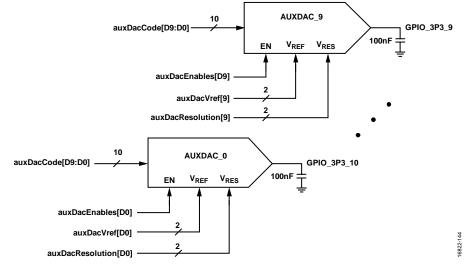

| Auxiliary Converters and Temperature Sensor | 230 |

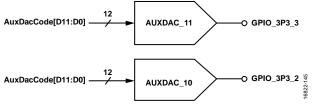

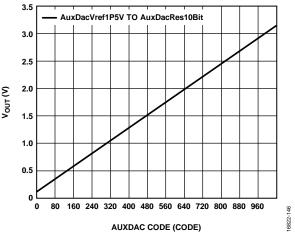

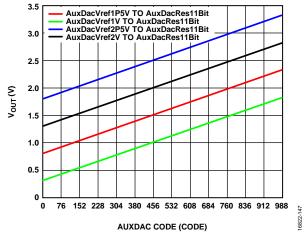

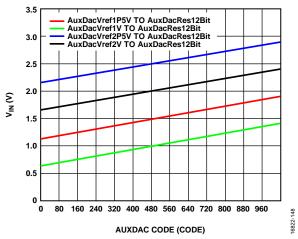

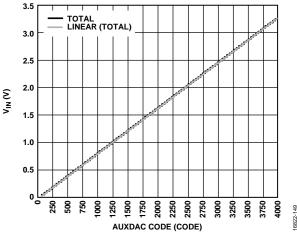

| Auxilary DAC (AUXDAC)                       | 230 |

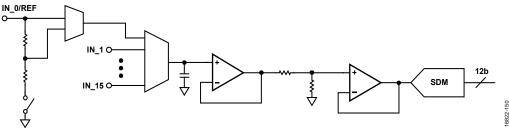

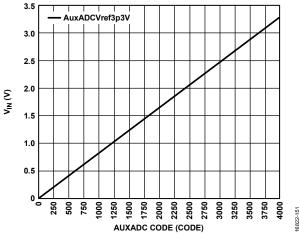

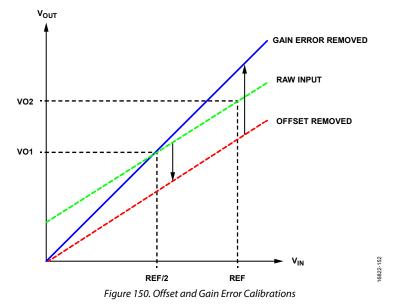

| Auxiliary ADC (AUXADC)                      | 234 |

| Temperature Sensor                          | 239 |

| Transmitter Attenuation                     | 240 |

| API Functions for Transmitter Attenuation   | 240 |

| Transmitter NCO Internal Signal Source      | 241 |

| Transmitter NCO API Functions               | 241 |

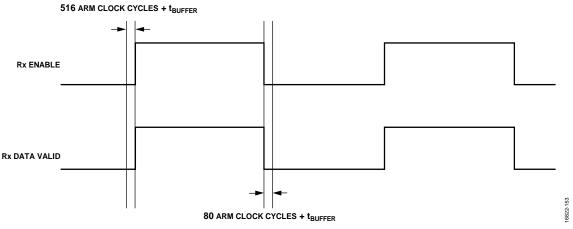

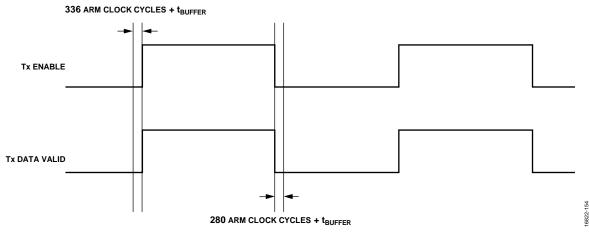

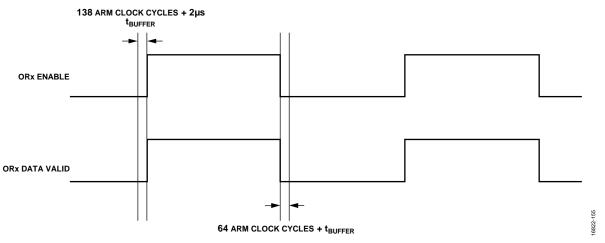

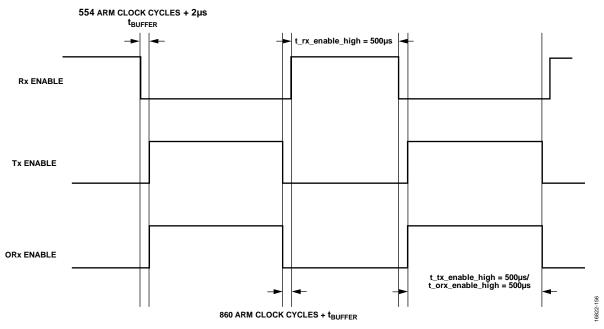

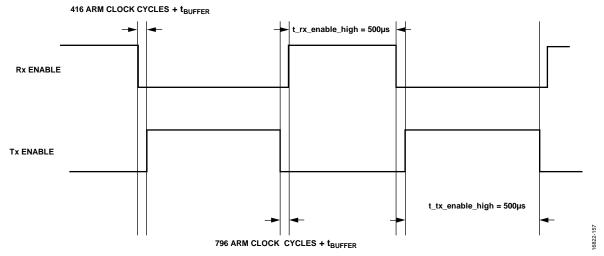

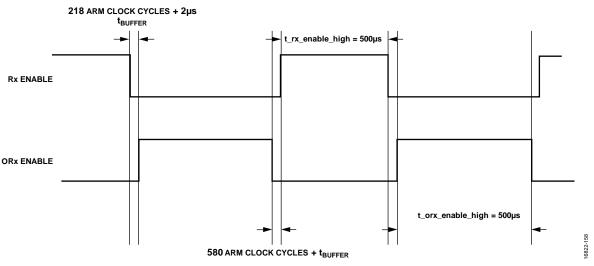

| Minimum Switching Times for the ADRV9008-1, |     |

| ADRV9008-2, and ADRV9009                    |     |

| Elemental Times for the Stream              |     |

| Minimum Switching Times for the ADRV9008-1  |     |

| Minimum Switching Times for the ADRV9008-2  |     |

| Minimum Switching Times for the ADRV9009    | 244 |

|                                             |     |

UG-1295

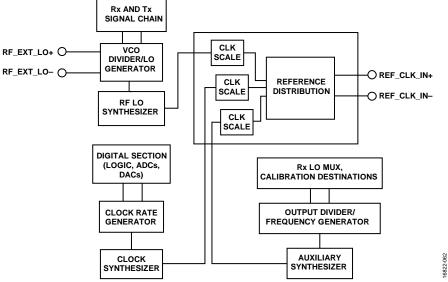

### SYSTEM OVERVIEW

The device consist of three highly integrated, radio frequency (RF) devices.

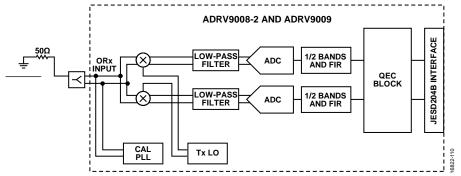

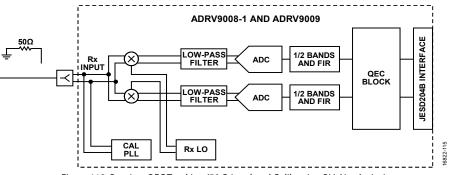

The ADRV9008-1 is a dual-channel RF receiver that operates over a frequency range of 75 MHz to 6 GHz. The ADRV9008-1 supports a receiver bandwidth of 200 MHz and supports multicarrier, global systems for mobile communications (GSM) cellular phone standards. Data transfer is accomplished using four JESD204B dedicated, high speed, serial interface lanes. See the ADRV9008-1 data sheet for a block diagram of the device.

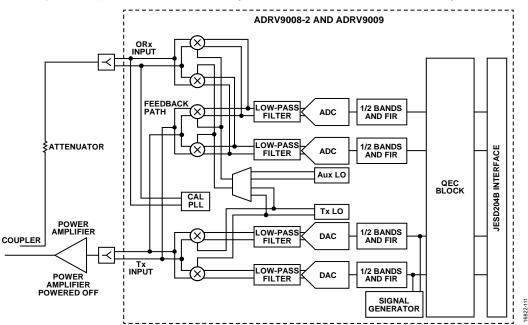

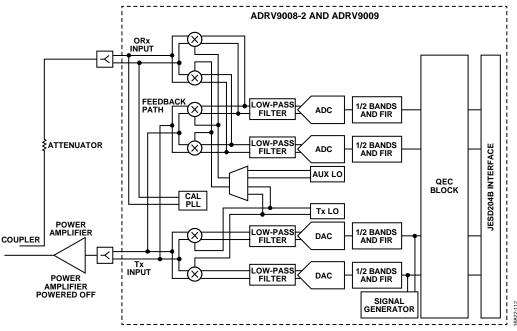

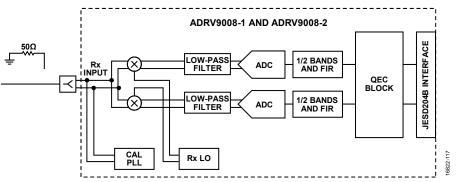

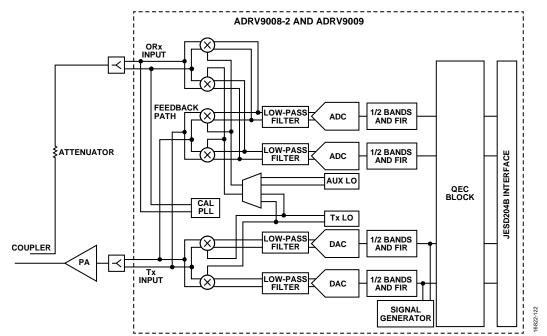

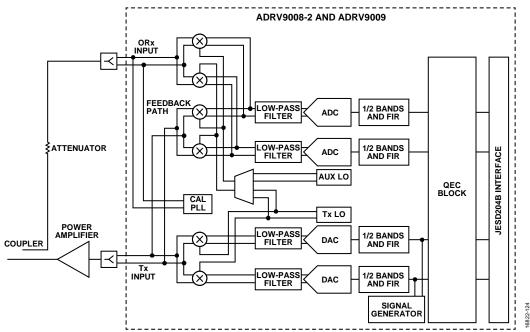

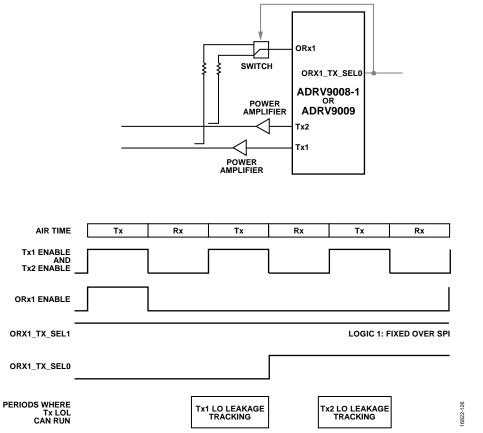

The ADRV9008-2 is a dual-channel RF transmitter and observation receiver that operates over a frequency range of 75 MHz to 6 GHz. The ADRV9008-2 supports up to 450 MHz of transmitter bandwidth and supports multicarrier GSM. The device includes a pair of observation receivers. Only one channel can be operational at any given time. This pair of channels supports the same frequency range and bandwidth of the transmitter channels. Data transfer is accomplished through eight JESD204B dedicated, high speed interface lanes. There are four lanes each for the transfer of transmitter data and observation receiver data. See the ADRV9008-2 data sheet for a block diagram of the device.

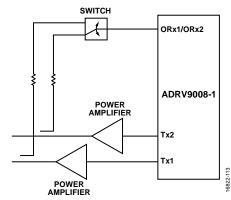

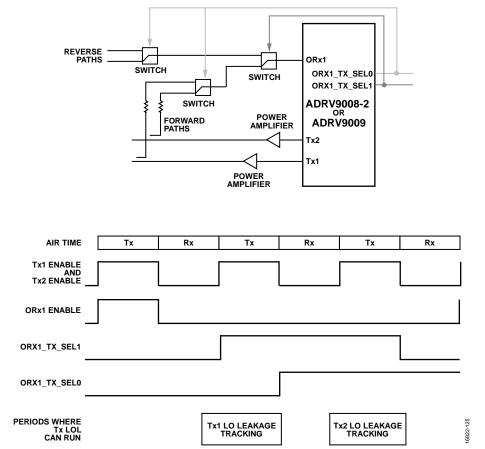

The ADRV9009 is a dual-channel RF transmitter and receiver with an observation receiver. The ADRV9009 operates over a frequency range of 75 MHz to 6 GHz. The device supports up to 450 MHz of synthesis bandwidth on its transmitters. The receiver portion of the device can operate either as a dual-channel receiver that supports bandwidths up to 200 MHz or as a single-channel observation receiver that supports bandwidths up to 450 MHz. The receiver portion is switched between single-channel and dual-channel mode in time division duplex (TDD) operation, utilizing the dual-channel receiver mode during receiver slots and utilizing the single-channel observation receiver can select either of the ORX1\_IN+/ORX1\_IN- or ORX2\_IN+/ORX2\_IN- RF inputs. Data transfer is accomplished through eight JESD204B dedicated, high speed interface lanes. There are four interface lanes each for the transfer of transmitter data and main receiver/observation receiver data. See the ADRV9009 data sheet for a block diagram of the device.

A serial peripheral interface (SPI) transmits and receives control information between the devices and a baseband processor (BBP). All software control is communicated via the SPI. The devices include a control interface that utilizes GPIO lines to provide hardware control to and from the devices. These GPIOs can be configured to provide dedicated sets of functions for different application scenarios. Some GPIO are intended for digital control and others are supplied by a 3.3 V analog supply to control external analog components. The devices also include a set of four low speed auxiliary ADCs that can be used to monitor external voltages of interest to system operation.

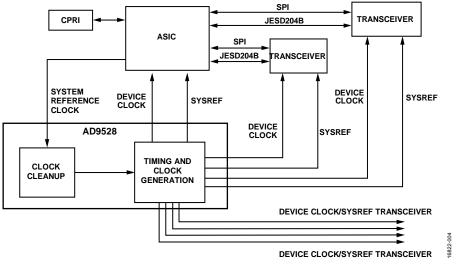

The AD9528 is a good choice for systems and is used on the Analog Devices, Inc., evaluation platform because the AD9528 provides a two-stage PLL with multiple outputs, along with an integrated JESD204B SYSREF generator for multiple device synchronization.

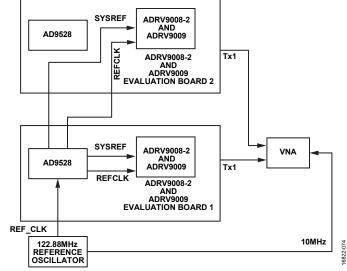

Figure 1. Mutiple Device System Example

### SYSTEM ARCHITECTURE DESCRIPTION

This reference manual provides information about the application programming interface (API) software, developed by Analog Devices for the ADRV9008-1, ADRV9008-2, and ADRV9009. This document outlines the overall architecture, folder structure, and methods for using API software on any platform. This reference manual does not explain the API library functions. Detailed information regarding the API functions is in the device API doxygen document (**Talise.chm**) located at /**src/doc.** This file can also be viewed in the **Help** tab on the Talise transceiver evaluation software (TTES) that controls the evaluation platform.

### SOFTWARE ARCHITECTURE

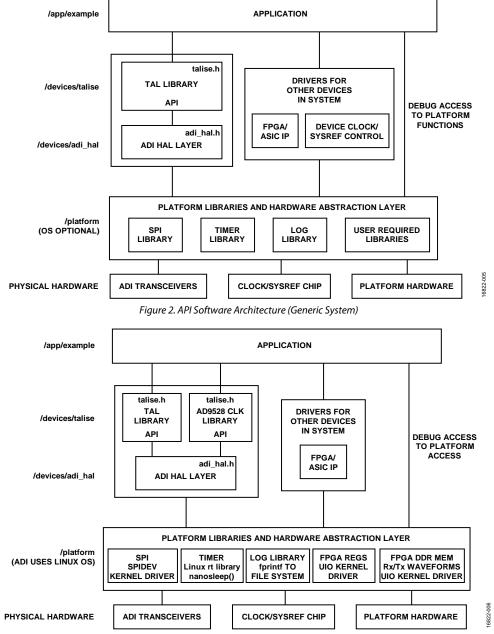

Figure 2 and Figure 3 illustrate the software architecture for a generic system and for the Analog Devices evaluation platform, respectively.

Figure 3. API Software Architecture (Analog Devices Evaluation Platform)

### FOLDER STRUCTURE

Source files are provided by Analog Devices in the folder structure shown in Figure 4. Analog Devices understands that the developer may desire to use a different folder structure. Analog Devices provides the API source code releases in the folder structure shown in Figure 4, and the developer may organize the API into a custom folder organization if required. The developer is not permitted to to modify the content of the API source code. Modifying the content of each API source file prevents updates to future API code releases.

### /src/app/example Folder

The /src/app/example folder contains a simple example application layer program. The headless.c file has the top level main function that demonstrates the sequence of the API function calls to initialize the device. Software developers can use this example code as a starting point to begin development on a custom application layer program. The /src/app/example folder also contains the talise\_config.c file. The talise\_config.c file holds the initialization and run-time data structures used by the API. The TTES can generate the initialization and run-time data structures for the API. Generating the talise\_config.c file from the evaluation software allows the user to create the structures with custom values selected by the graphical user interface (GUI) configuration pages.

### /src/devices Folder

The /**src/devices** folder includes the main API code for the transmitter (/**src/devices/talise**). The /**talise** folder contains the high level function prototypes, data types, macros, and source code that are used to build the final user software system. The user is strictly forbidden from modifying the files contained in the /**talise** folder because the code is maintained by Analog Devices. The only exception to this restriction is that the developer can modify the /**talise/talise\_user.c** file, which contains receiver gain tables and user selectable define macros, for example, TALISE\_VERBOSE mode, which enables and disables certain API messages to the log.

The /**adi\_hal** folder provides the means for a developer to insert custom platform hardware driver code for system integration with the API. It is important that the function prototypes in the **adi\_hal.c** file do not change. The developer is responsible for implementing the code inside each **adi\_hal.c** function to ensure that the correct hardware drivers are called for the platform hardware. In the example code provided in the **adi\_hal.c** file, the functions are generic wrappers that call hardware layer functions, devices, and resources for the Xilinx\* Zynq\*-7000 SoC ZC706 platform. Analog Devices API implementation attempts to keep the **adi\_hal.c** implementation generic to allow simplified platform swapping.

### /src/doc Folder

The /src/doc folder contains the device API doxygen (Talise.chm) file for user reference. This file is in compressed HTML format. For security reasons, .chm files can only be opened from a local drive. Attempting to open these files from a network drive can result in a file that appears empty.

### **PRIVATE vs. PUBLIC API FUNCTIONS**

The API is made up of multiple .c and .h files. The functionality of the API is broken into modular pieces to help organize the API functions. Because the API is written in C, there are no language modifiers to identify a function as private or public, as commonly done in object oriented languages. Public API functions are denoted by the function name prepended with TALISE\_functionName(). The application layer is free to use any API function that is prepended with the TALISE\_ naming. Private helper functions lack the TALISE\_ prefix. It is not intended that the private helper functions add any value to the application layer.

Most functions in the API are prefixed with TALISE\_ and are for public use. Many of these functions are never called directly from the application layer. For this reason, the majority of the initialization and other helper functions are separated from the top level **talise.c/talise.h** files to help the developer focus on the functions that are most commonly and widely used by the application layer program.

# UG-1295

### HARDWARE ABSTRACTION LAYER (HAL)

The HAL interface is a library of functions that the transceiver APIs uses when the API must access the target platform hardware. The HAL is defined by **adi\_hal.h**; however, the implementation of this interface is platform dependent and is implemented by the end user in the **adi\_hal.c** file. This architecture is depicted in Figure 2.

The HAL is a collection of APIs, macros, and defines that are designed to make the upper layers (libraries and application) as platform independent as possible. This reference manual describes those HAL components.

The Analog Devices source code has a subfolder under the /**adi\_hal** folder in the /**device** folder. The **adi\_hal.h** header file details the HAL interface and functions. The **adi\_hal.c** provides details of the Analog Devices platform specific implementation of the Analog Devices HAL (ADIHAL) interface. The **adi\_hal.c** file can be used as an example by the end user when developing the HAL function implementation for a custom platform.

### Hardware Functions

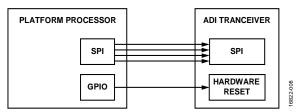

The transceiver API requires a library of functions that facilitate access to the hardware interfaces on the target platform (see Figure 5).

Figure 5. Hardware Controls Required by HAL Interface Functions

Access to the SPI controller that communicates with the transmitter is required. The SPI Interface details are illustrated in the SPI section. In addition, control of the hardware reset signal that controls the RESET pin of the Analog Devices transceiver is required. This hardware reset signal is usually implemented by a platform processor GPIO. Refer to the ADRV9008-1, ADRV9008-2, and ADRV9009 data sheets for full details on the RESET pin. Figure 5 shows a short overview of the required HAL functions. Full details are provided in the Hardware Abstraction Layer (HAL) section of this document.

### **Logging Functions**

The API provides a simple logging feature function that can be enabled for debugging purposes. This feature requires an implementation for the ADIHAL\_writeToLog function. The APIs optionally call to send debug information to the system via the HAL. The ADIHAL\_setLogLevel function can be used to configure HAL flags, and the HAL flags configure how the HAL processes the various message types from the API layer. The Analog Devices transceiver open hardware function TALISE\_openHw calls this function to set the desired logging operation.

### **Multidevice Support**

For applications with multiple transceivers, the HAL layer requires a reference to the targeted device and its hardware particulars, for example, the SPI chip select and reset signal. The first parameter of the HAL function prototype, void\* devHalInfo, acts as the device reference for the HAL functions.

Note that for Analog Devices transceiver APIs, it is required that only one thread can control and configure a particular device at any given time.

### devHalInfo Pointer Parameter

To transfer the target device information from the application to the HAL functions, the API layer transfers a void pointer parameter, devHalInfo, from the application to all HAL functions. This void pointer acts as a state container for the relevant hardware information for a particular device.

The API user must define this state container as per system HAL implementation requirements. The user can implement any structure to transfer any hardware configuration information that the hardware requires between the application layer and the platform layer. This state container can be used to transfer device reference information in multithreaded and multitransceiver systems.

The application transfers the device state container, devHalInfo, via the API transceiver device structure, for example, taliseDevice\_t. The API function does not read or write the (void \*) devHalInfo but transfers the state container as a parameter to all HAL function calls.

### UG-1295

```

Pseudo Code Example Use of devHalInfo

The device structure is as follows:

typedef struct

{

void

*devHalInfo;

/*HAL layer State Container*/

void

*devStateInfo;

/*API internal State Container*/

} taliseDevice_t;

The example target system HAL device state container is as follows:

typedef struct

{

/*Device Reference*/

uint8_t devIndex

zynqSpiSettings_t *spiSettings;

/*Platform SPI controller settings*/

/*Timeout limit for HAL function

uint16_t wait_timeout;

Completion*/

} zynqcAdiDev_t;

The example API call on the target system application is as follows:

zynqAdiDev_tTaliseDev1 {...};

taliseDevice_t device = {&TaslieDev1....} ;

Talise_initialize(&device) ;

retval = TALISE_openHw (device-> devHalInfo);

The example target system HAL function implementation is as follows:

ADIHAL_openHw(void * device) {

zynqAdiDev_t *talDev = device->devHalInfo;

```

### }

### **HAL Functions Timeout**

For systems where HAL resources are shared, it is possible that HAL functions block and must wait for resources to complete the hardware operation. The HAL timeout variable, set by the API, instructs the HAL implementation with how long each function can take to try to complete the operation. If the operation fails to complete within this time interval, the HAL function must return indicating that the function timed out. See the adiHalErr\_t section for details.

This timeout value is set by the API at HAL initialization via the ADIHAL\_openHW function. Additionally, the API can update the timeout requirement by calling the HAL function ADIHAL\_setTimeout from the API layer for operations that may have different time constraints.

It is expected that the HAL implementation of the end user captures and maintains the timeout value to implement the timeout feature for all subsequent HAL function calls. The HAL implementation can use the HAL device state container, devHalInfo, to maintain this timeout value.

### HAL INTERFACE DEFINITION

This section describes the Hardware Application Layer (HAL) Interface.

### DATA TYPES AND ENUMERATIONS

The following data types and enumerations are used by the HAL.

### adiHalErr\_t

adiHalErr\_t is an enumerated data type that lists the error types returned by the Analog Devices HAL interface function. These error types include errors that the HAL implementation may detect and return to the transceiver API. The transceiver API reports any HAL layer error detected to the application. The transceiver API can fail due to a HAL error and then recommend a recovery action to the application. The recovery action recommended depends on the stage of API execution during which the error occurs, as well as the function of the API. Refer to the API documentation for more details.

#### adiHalErr\_t Synopsis

The synopsis for adiHalErr\_t is as follows:

```

typedef enum

{

ADIHAL_OK=0,

ADIHAL_SPI_FAIL,

ADIHAL_GPIO_FAIL,

ADIHAL_TIMER_FAIL,

ADIHAL_WAIT_TIMEOUT,

ADIHAL_GEN_SW,

ADIHAL_WARNING

```

} adiHalErr\_t;

### adiHalErr\_t Enumerators

The enumerators for adiHalErr\_t are as follows:

- ADIHAL\_OK. This enumerator indicates that the HAL function completed successfully and that no errors are detected.

- ADIHAL\_SPI\_FAIL. This enumerator indicates that HAL SPI operation is unable to complete. The SPI controller may not be accessible due to a fatal error. The API fails and directly passes the error to the application.

- ADIHAL\_GPIO\_FAIL. This enumerator indicates that HAL operations that require a system GPIO, such as ADIHAL\_resetHW, are unable to complete. The system GPIO may not be accessible due to a fatal error. The API fails and passes the error to the application.

- ADIHAL\_TIMER\_FAIL. This enumerator indicates that HAL operations that require delays and sleeps, such as ADIHAL\_wait\_us, are unable to complete. System timers or time functions may not be accessible due to a fatal error. The API fails and passes the error to the application.

- ADIHAL\_WAIT\_TIMEOUT. This enumerator indicates that HAL operations that cannot complete within the interval set by the API return this error. This timeout may be due to the required hardware (SPI controller, GPIO, and so on) being temporarily unavailable. The timeout value is passed to the HAL layer by the API with the ADIHAL\_openHW HAL initialization function and/or at any other time with the ADIHAL\_setTimeout function. The API can fail depending on the function of the API and at what stage of execution of the API the error is detected. The error is passed directly to the API.

- ADIHAL\_GEN\_SW. This enumerator indicates that the HAL functions detect a general software error during execution. This error type includes, but is not limited to, open hardware or closed hardware failures, the device state container being a NULL pointer, an unknown chip select, or the device being already open. The API fails and passes the error to the application.

- ADIHAL\_WARNING. This enumerator indicates that the HAL functions detect an error that does not affect operation. This error acts as a warning that such an error occurred. The API reports this error to the application, but does not take any action or indicate a failure.

### adiLogLevel\_t

adilogLevel\_t is an enumerated data type in bit mask format that lists the log message type received by the HAL layer from the API via the ADIHAL\_writeToLog function.

### adiLogLevel\_t Synopsis

The synopsis for adiLogLevel\_t is as follows:

typedef enum

{

| ADIHAL_LOG_NONE | = | 0x0, |  |

|-----------------|---|------|--|

| ADIHAL_LOG_MSG  | = | 0x1, |  |

| ADIHAL_LOG_WARN | = | 0x2, |  |

| ADIHAL_LOG_ERR  | = | 0x4, |  |

| ADIHAL_LOG_SPI  | = | 0x8, |  |

| ADIHAL_LOG_ALL  | = | 0xF  |  |

|                 |   |      |  |

} adiLogLevel\_t;

#### adiLogLevel\_t Enumerators

The enumerators for adiLogLevel\_t are as follows:

- ADIHAL\_LOG\_NONE. This enumerator indicates that the mask for no logging is enabled. This function can be optionally used by the ADIHAL\_writeToLog implementation to ignore all error types. This function is not used by the API as an error category, but can be used by ADIHAL\_setLogLevel.

- ADIHAL\_LOG\_MSG. This enumerator indicates the mask for a log message or warning. This enumerator does not indicate an error.

- ADIHAL\_LOG\_ERR. This enumerator indicates the mask for error message.

- ADIHAL\_LOG\_SPI. This enumerator indicates the mask error message related to SPI operation.

- ADIHAL\_LOG\_ALL. This enumerator indicates that the mask for all logging is enabled. This function can be optionally used by the ADIHAL\_writeToLog implementation to represent all error types. This function is not used by the API as an error category, but can be used by ADIHAL\_setLogLevel.

### **DETAILED HAL FUNCTION DEFINITIONS**

The following sections describe the detailed HAL function definitions.

### ADIHAL\_openHW

The ADIHAL\_openHW HAL function performs a platform hardware initialization for device. This function initializes all external hardware components required by the device and the HAL functions for correct functionality, such as SPI drivers, GPIOs, clocks (if necessary), as per the target platform and the target device requirements. At a minimum, any SPI driver for the device is initialized within this function for the SPI writes within the API to function.

The hardware initialize API calls the ADIHAL\_openHW HAL function. For example, for the ADRV9008-1, ADRV9008-2, and ADRV9009 devices, the API calls the TALISE\_openHw API. This API is called before any other API.

Based on the required operation, the API sets the value of the timeout parameter. After this value is set, the value serves as the timeout requirement for all HAL operations. It is the responsibility of the HAL implementation to maintain this timeout value as a reference. The HAL implementation must use this value to ensure the HAL function does not block longer than this time interval. Refer to the HAL Functions Timeout section for details.

ADIHAL\_openHW must be called before calling any other HAL functions.

### ADIHAL\_openHW Synopsis

The synopsis for the ADIHAL\_openHW function is as follows:

adiHalErr\_t ADIHIAL\_openHw(void \*devHalInfo, uint32\_t timeout\_ms)

Parameters include the following:

- void\*devHalInfo. This parameter is a void pointer to the targeted device state container. Refer to the devHalInfo Pointer Parameter section for details.

- uint32\_t timeout\_ms. This parameter is a positive integer representing the time interval (in ms) in which the HAL functions can block before returning. The HAL functions may not block indefinitely. The API provides this time value to the HAL.

Refer to the HAL Functions Timeout section for details.

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application. Refer to the adiHalErr\_t section for details.

Dependencies: the ADIHAL\_openHW HAL function is dependent on application and platform specific modules.

### ADIHAL\_openHW Remarks

Although ADIHIAL\_openHw initially sets the timeout value for HAL functions, the API may modify the timeout value by calling ADIHAL\_setTimeout for any time sensitive operations.

For Analog Devices transceiver APIs, there is a requirement that only one thread can control and configure a particular device at any given time. For this reason, ADIHIAL\_OPENHW may flag an ADIHAL\_GEN\_SW error to the API and application if the device targeted by the \*devHalInfo parameter is already initialized.

#### ADIHAL\_closeHW

The ADIHAL\_closeHW HAL function performs a platform hardware shutdown for the device. This function shuts down all external hardware resources and peripherals required by the device for correct functionality, such as SPI drivers, GPIOs, clocks (as per the targeted platform), and the target device. The ADIHAL\_closeHW HAL function closes and frees any resources assigned in the ADIHAL\_openHw API.

The hardware shutdown API calls the ADIHAL\_closeHW HAL function. For example, for the ADRV9008-1, ADRV9008-2, and ADRV9009 devices, the TALISE\_closeHw API calls this function.

### ADIHAL\_closeHW Synopsis

The synopsis for the ADIHAL\_closeHW function is as follows:

adiHalErr\_t ADIHAL\_closeHw(void \*devHalInfo)

Parameter: void\*devHalInfo. This parameter is a void pointer to the targeted device state container. Refer to the devHalInfo Pointer Parameter section for details.

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application. Refer to the adiHalErr\_t section for details.

Dependencies: the ADIHAL\_closeHW HAL function is dependent on application and platform specific modules, as well as ADIHAL\_openHW.

### ADIHAL\_closeHW Remarks

For Analog Devices transceiver APIs, there is a requirement that only one thread can control and configure a particular device at any given time. For this reason, ADIHAL\_closeHw may flag an ADIHAL\_GEN\_SW error to the API and application if the device targeted by the \*devHalInfo parameter is already closed.

### ADIHAL\_resetHW

Toggle the active low hardware reset pin,  $\overline{\text{RESET}}$ , of the device. To ensure a successful hardware reset of the device, pull the targeted device  $\overline{\text{RESET}}$  pin low for period of at least 1 ms and then pull  $\overline{\text{RESET}}$  high again. In general, for Analog Devices transceiver devices, low = 0 V and high = the VDD\_INTERFACE value. The exact reset procedure is described in the data sheet of the targeted Analog Devices device data sheet.

### ADIHAL\_resetHW Synopsis

The synopsis for the ADIHAL\_resetHW function is as follows:

adiHalErr\_t ADIHAL\_resetHw(void \*devHalInfo)

Parameter: void\*devHalInfo. This parameter is a void pointer to the targeted device state container. Refer to the devHalInfo Pointer Parameter section for details.

Return value: an error of type adiHalErr\_t , ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application. Refer to the adiHalErr\_t section for details

Dependencies: the ADIHAL\_resetHW HAL function is dependent on application and platform specific modules, as well as ADIHAL\_openHW and ADIHAL\_closeHW. In general, it is expected that ADIHAL\_openHW initializes all hardware resources for the transceiver. This function depends on the GPIO. Therefore, it is expected that the required GPIO is initialized in ADIHAL\_openHW. Do not call ADIHAL\_resetHW before ADIHAL\_openHW and not call ADIHAL\_resetHW after ADIHAL\_closeHW.

### ADIHAL\_resetHW Remarks

For the ADIHAL\_resetHW function, devHalInfo contains information to determine which reference to a specific device on the platform is to be reset and any additional platform information required to toggle the RESET pin.

Do not make any communication attempts to the device for 100  $\mu$ s following the toggle of the RESET pin. In general, a call to this function is followed by call to ADIHAL\_wait\_us by the API.

### ADIHAL\_setTimeout

The ADIHAL\_setTimeout HAL function sets the timeout duration for the HAL functions. This function sets the timeout duration for the HAL functions. If the HAL operation exceeds this time, the function returns with the ADIHAL\_WAIT\_TIMEOUT error.

Based on the required operation, the API sets this timeout value. After this value is set, it serves as the timeout requirement for all HAL operations. The HAL implementation must maintain this timeout value as a reference and ensure that the HAL function does not block longer than this time interval.

### ADIHAL\_setTimeout Synopsis

The synopsis for the ADIHAL\_setTimeout function is as follows:

```

adiHalErr_t ADIHAL_setTimeout(void *devHalInfo, uint32_t timeout_ms);

```

### Parameters:

- void\*devHalInfo. This parameter is a void pointer to the targeted device state container. Refer to the devHalInfo Pointer Parameter section for details.

- uint32\_t timeout\_ms. This parameter is a positive integer representing the time interval (in ms) in which the HAL functions can block before returning. The HAL functions cannot block indefinitely. The API provides this value to the HAL.

Refer to the HAL Functions Timeout section for details.

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application. Refer to the adiHalErr\_t section for details.

Dependencies: the ADIHAL\_setTimeout HAL function is dependent on application and platform specific modules.

### ADIHAL\_setTimeout Remarks

The ADIHAL\_setTimeout function is required for system environments in which HAL resources are shared and in cases where resources, such as the SPI, are functional but not available due to these resources being used by another device.

### ADIHAL\_spiWriteByte

The ADIHAL\_spiWriteByte function performs a single SPI write to a device. Using the SPI interface protocol, write a single byte to a specified address within a specific device. The state container maintains the SPI chip select value to specify the target device and any other platform specific settings required for the platforms SPI controller, such as write bit polarity and a long instruction word.

The SPI write implementation must support 15-bit addressing and 8-bit data bytes. Full details of the SPI protocol required for SPI communication with the transceiver is described in the SPI section.

The ADIHAL\_spiWriteByte HAL function is used by transceiver APIs. Therefore, any necessary SPI drivers or resources are expected to be already opened by the ADIHAL\_openHw() function call.

### ADIHAL\_spiWriteByte Synopsis

The synopsis for the ADIHAL\_spiWriteByte function is as follows:

adiHalErr\_t ADIHAL\_spiWriteByte(void \*devHalInfo, uint16\_t addr, uint8\_t data);

Parameters inlcude the following:

- void\*devHalInfo. This parameter is a void pointer to the targeted device state container. The device state provides the SPI device chip select information.

- addr. This parameter provides an SPI register address in which to perform an SPI write. The address value must not exceed 15-bits because the MSB bit is used for a read/write bit in the SPI implementation.

- data. This parameter provides an 8-bit data value to write to the specified SPI address.

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application. Refer to the adiHalErr\_t section for details.

Dependencies: the ADIHAL\_spiWriteByte HAL function is dependent on application and platform specific modules, as well as ADIHAL\_openHW and ADIHAL\_closeHW. In general, it is expected that ADIHAL\_openHW initializes all hardware resources for the transceiver. This function depends on the SPI. Therefore, it is expected that the required SPI is initialized in ADIHAL\_openHW. Do not call ADIHAL\_spiWriteByte before ADIHAL\_openHW and not call ADIHAL\_spiWriteByte after ADIHAL\_closeHW.

### ADIHAL\_spiWriteByte Remarks

Analog Devices devices support various modes of the SPI protocol, such as 3-wire or 4-wire mode (see the SPI Data Transfer Protocol section). The HAL can implement any of the supported modes. However, the transceiver must be configured to the same mode as the HAL implementation. The SPI mode configuration of the transceiver is set by the initialization API and the desired SPI mode defined by taliseSpiSettings\_t of the initialization parameter.

### ADIHAL\_spiReadByte

The ADIHAL\_spiReadByte HAL function performs a single SPI read to a device. Using the SPI interface protocol, read a single byte from a specified address within a specific device. The state container maintains the SPI chip select value to specify the target device and any other platform specific settings required for the SPI controller, such as writ bit polarity and a long instruction word.

The SPI read implementation must support 15-bit addressing and 8-bit data bytes. Full details of the SPI protocol required for SPI communication with the transceiver is described in the SPI Data Transfer Protocol section.

This HAL function is used by most transceiver APIs. Therefore, any necessary SPI drivers or resources are expected to be already opened by the ADIHAL\_openHw() function call.

### ADIHAL\_spiReadByte Synopsis

The synopsis for the ADIHAL\_spiReadByte function is as follows:

adiHalErr\_t ADIHAL\_spiReadByte(void \*devHalInfo, uint16\_t addr, uint8\_t \*readdata);

Parameters include the following:

- void\*devHalInfo. This parameter is a void pointer to the targeted device state container. The device state provides the SPI device chip select information.

- addr. This parameter provides an SPI register address on which to perform an SPI read. The address value must not exceed 15-bits because the MSB is used for a read/write bit in the SPI implementation.

- \*readdata. This parameter is a pointer to the 8-bit variable to be updated with the value read from the SPI register address. The API layer allocates the memory for this pointer.

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application. Refer to the adiHalErr\_t section for details.

Dependencies: the ADIHAL\_spiReadByte HAL function is dependent on application and platform specific modules, as well asADIHAL\_openHW and ADIHAL\_closeHW. In general, it is expected that ADIHAL\_openHW initializes all hardware resources for the transceiver. This function depends on the SPI. Therefore, it is expected that the required SPI is initialized in ADIHAL\_openHW. Do not call ADIHAL\_spiReadByte before ADIHAL\_openHW and do not call ADIHAL\_spiReadByte after ADIHAL\_closeHW.

### ADIHAL\_spiReadByte Remarks

Analog Devices devices support various modes of the SPI protocol, such as 3-wire or 4-wire mode (see the SPI Data Transfer Protocol section). The HAL can implement any of the supported modes. However, the transceiver must be configured to the same mode as the HAL implementation. The SPI mode configuration of the transceiver is set by the initialization API and the desired SPI mode defined by taliseSpiSettings\_t of the initialization parameter.

### ADIHAL\_spiWriteBytes

The ADIHAL\_spiWriteBytes HAL function performs a set of SPI writes to a device. A list of SPI addresses is passed to this function with a corresponding list of values to be written to these addresses. The ADIHAL\_spiWriteBytes function performs an SPI write to the targeted device for each member in the arrays. Each address element corresponds to the same index element in the data array.

For example, Address 0 is the SPI address for Data 0, Address 1 is the SPI add for Data 1, and so on.

If the platform layer SPI driver has no way to write an array to the SPI driver, set this function to call ADIHAL\_spiWriteByte in for a loop.

The HAL\_SPIWRITEARRAY\_BUFFERSIZE macro in **adi\_hal.h** must be set to the maximum number of SPI transactions supported by the HAL implementation of ADIHAL\_spiWriteBytes. The API layer references this macro when creating buffers of data to write with ADIHAL\_spiWriteBytes.

### ADIHAL\_spiWriteBytes Synopsis

The synopsis for the ADIHAL\_spiWriteBytes function is as follows:

adiHalErr\_t ADIHAL\_spiWriteBytes(void \*devHalInfo, uint16\_t \*addr, uint8\_t \*data, uint32\_t

count);

Parameters include the following:

- void\*devHalInfo. This parameter is a void pointer to the targeted device state container. The device state provides the SPI device chip select information.

- \*addr. This parameter provides an array of addresses of SPI registers to write (15-bit SPI register addresses, the MSB in the SPI implementation sets the read/write bit).

- \*readdata. This parameter provides an array of 8-bit data values to write to the SPI addresses listed in the address array.

- count. This parameter provides the number of registers on which to perform SPI writes (the size of the address and read data arrays).

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value represents an error code to be returned to the application. Refer to the adiHalErr\_t section for details.

Dependencies: the ADIHAL\_spiWriteBytes HAL function is dependent on application and platform specific modules, as well as ADIHAL\_openHW and ADIHAL\_closeHW. In general, it is expected that ADIHAL\_openHW initializes all hardware resources for the transceiver. This function depends on the SPI. Therefore, it is expected that the required SPI is initialized in ADIHAL\_openHW. Do not call ADIHAL\_spiWriteBytes before ADIHAL\_openHW and do not call ADIHAL\_spiWriteBytes after ADIHAL\_closeHW.

### ADIHAL\_spiWriteBytes Remarks

Analog Devices devices support various modes of the SPI protocol, such as 3-wire or 4-wire mode (see the SPI Data Transfer Protocol section). The HAL can implement any of the supported modes. However, the transceiver must be configured to the same mode as the HAL implementation. The SPI mode configuration of the transceiver is set by the initialization API and the desired SPI mode defined by taliseSpiSettings\_t of the initialization parameter.

### ADIHAL\_spiReadBytes

The ADIHAL\_spiReadBytes function performs a set of SPI reads from a device. A list of SPI addresses is passed to this function with a data array pointer to store the data read back from the list of SPI addresses. This function performs an SPI read from the list of SPI addresses in the targeted device. Each address element has a corresponding index in the data array.

For example, readdata[0] stores the data from the SPI address from dataarray[0].

If the platform layer SPI driver has no way to read an array from the SPI driver, set this function to call ADIHAL\_spiReadByte in for a loop.

### ADIHAL\_spiReadBytes Synopsis

The synopsis for the ADIHAL\_spiReadBytes function is as follows:

adiHalErr\_t ADIHAL\_spiReadBytes(void \*devHalInfo, uint16\_t \*addr, uint8\_t \*data, uint32\_t

count);

Parameters include the following:

- void\*devHalInfo. This parameter is a void pointer to the targeted device state container. The device state provides the SPI device chip select information.

- \*addr. This parameter provides an array of addresses of SPI register to read (15-bit SPI register addresses, the MSB in SPI implementation sets the read/write bit).

- \*readdata. This parameter provides an array of 8-bit data values to store the data read from the SPI addresses listed in the address array. The API layer allocates the memory for this pointer.

- count. This parameter provides the number of registers on which to perform the SPI reads (the size of the address and read data arrays).

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application. Refer to the adiHalErr\_t section for details.

Dependencies: the ADIHAL\_spiReadBytes HAL function is dependent on application and platform specific modules, as well as ADIHAL\_openHW and ADIHAL\_closeHW.

In general, it is expected that ADIHAL\_openHW initializes all hardware resources for the transceiver. This function depends on the SPI. Therefore, it is expected that the required SPI is initialized in ADIHAL\_openHW. Do not call ADIHAL\_spiReadBytes before ADIHAL\_openHW and not call ADIHAL\_spiReadBytes after ADIHAL\_closeHW.

### ADIHAL\_spiReadBytes Remarks

Analog Devices devices support various modes of the SPI protocol, such as 3-wire or 4-wire mode (see the SPI Data Transfer Protocol section). The HAL can implement any of the supported modes. However, the transceiver must be configured to the same mode as the HAL implementation. The SPI mode configuration of the transceiver is set by the initialization API and the desired SPI mode defined by taliseSpiSettings\_t of the initialization parameter.

### ADIHAL\_spiWriteField

The ADIHAL\_spiWriteField HAL function performs a write to a specific field within an SPI register. This function performs a read/modify/write operation on a single SPI register. This function implements an SPI read of all 8-bit bits in the register, modifies the bits of a specific field, and writes the new value back to the same SPI register in the device.

The mask and startBit parameters specify the field of bits within the register to be modified. The mask is expected to be applied to the 8-bit value read back from register. The startBit parameter specifies the start bit of targeted field within the register. The value of startBit is used to shift the fieldVal parameter to the correct starting bit in the SPI register.

An example of pseudo code is as follows:

```

/*Read a specific register*/

spiRead(regAddr, &regVal);

```

```

/* Modify specific field*/

regVal = regVal & ~mask) | ((fieldVal << startBit) & mask);</pre>

```

/\*Write the modified value back to the SPI register\*/

spiWrite(regAddr, regVal);

The SPI write/read implementations must support 15-bit addressing and 8-bit data bytes. Full details of the SPI protocol required for SPI communication with the transceiver is described in the SPI Data Transfer Protocol section.

This HAL function is used by most transceiver APIs. Therefore, any necessary SPI drivers or resources are expected to be already opened by the ADIHAL\_openHw() function call.

### ADIHAL\_spiWriteField Synopsis

The synopsis for the ADIHAL\_spiWriteField HAL is as follows:

adiHalErr\_t ADIHAL\_spiWriteField(void \*devHalInfo, uint16\_t addr, uint8\_t fieldVal, uint8\_t

mask, uint8\_t startBit);

Parameters include the following

- void\*devHalInfo. This parameter is a void pointer to the targeted device state container. The device state provides the SPI device chip select information.

- addr. This parameter provides the SPI register address on which to perform an SPI read. The address value must not exceed 15 bits because the MSB bit is used for the read/write bit in the SPI implementation.

- fieldVal. This parameter provides the desired new value for the targeted field within the register specified by addr parameter.

- mask. Field mask, describing the targeted bits within the register specified by addr parameter.

- startBit. This parameter provides the field LSB position in the register (0 to 7).

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates a successful operation. Any other value may represent an error code to be returned to the application. Refer to the adiHalErr\_t section for details.

Dependencies: the ADIHAL\_spiWriteField HAL function is dependent on application and platform specific modules, as well as ADIHAL\_openHW and ADIHAL\_closeHW. In general, it is expected that ADIHAL\_openHW initializes all hardware resources for the transceiver. This function depends on the SPI. Therefore, it is expected that the required SPI is initialized in ADIHAL\_openHW. Do not call ADIHAL\_spiWriteField before ADIHAL\_openHW and not call ADIHAL\_spiWriteField after ADIHAL\_closeHW.

### ADIHAL\_spiWriteField Remarks

Analog Devices devices support various modes of the SPI protocol, such as 3-wire or 4-wire mode (see the SPI Data Transfer Protocol section). The HAL can implement any of the supported modes. However, the transceiver must be configured to the same mode as the HAL implementation. The SPI mode configuration of the transceiver is set by the initialization API and the desired SPI mode defined by taliseSpiSettings\_t of the initialization parameter.

### ADIHAL\_spiReadField

The ADIHAL\_spiReadField HAL function performs a read to a specific field within an SPI register. This function performs a read operation on a single SPI register.

The mask and startBit parameters specify the field of bits within the register to be read. The mask is expected to be applied to the 8-bit value read back from register. The startBit startBit specifies the LSB of the targeted field within the register, which is used to shift the desired field value down to the Bit 0 position.

An example of pseudo code is as follows:

```

/*Read a specific register*/

spiRead(regAddr, &regVal);

*fieldVal = ((regVal & mask) >> startBit);

```

The SPI read/write implementations must support 15-bit addressing and 8-bit data bytes. Full details of the SPI protocol required for SPI communication with the transceiver is described in the SPI section and the HAL Interface Definition section.

This HAL function is used by most transceiver APIs. Therefore, any necessary SPI drivers or resources are expected to be already opened by the ADIHAL\_openHw() function call.

### ADIHAL\_spiReadField Synopsis

The synopsis for ADIHAL\_spiReadField is as follows:

adiHalErr\_t ADIHAL\_spiReadField(void \*devHalInfo, uint16\_t addr, uint8\_t \*fieldVal, uint8\_t

mask, uint8\_t startBit);

Parameters include the following:

- void\*devHalInfo. This parameter is a void pointer to the targeted device state container. The device state provides the SPI device chip select information.

- addr. This parameter provides an SPI register address on which to perform an SPI read. The address value must not exceed 15 bits because the MSB is used for the read/write bit in the SPI implementation.

- fieldVal. This parameter is a pointer variable to return the value of the desired field specified by the mask parameter.

- mask. Field mask, describing the targeted bits within the register specified by addr parameter.

- startBit. Field LSB bit position in the register (0 to 7).

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application. Refer to the adiHalErr\_t section for details.

Dependencies: the ADIHAL\_spiReadField HAL function is dependent on application and platform specific modules, as well as ADIHAL\_openHW and ADIHAL\_closeHW. In general, it is expected that ADIHAL\_openHW initializes all hardware resources for the transceiver. This function depends on the SPI. Therefore, it is expected that the required SPI is initialized in ADIHAL\_openHW. Do not call ADIHAL\_spiReadField before ADIHAL\_openHW and not call ADIHAL\_spiReadField after ADIHAL\_closeHW.

#### ADIHAL\_spiReadField Remarks

Analog Devices devices support various modes of the SPI protocol, such as 3-wire or 4-wire mode (see the SPI Data Transfer Protocol section). The HAL can implement any of the supported modes. However, the transceiver must be configured to the same mode as the HAL implementation. The SPI mode configuration of the transceiver is set by the initialization API and the desired SPI mode defined by taliseSpiSettings\_t of the initialization parameter.

#### ADIHAL\_wait\_us

The ADIHAL\_wait\_us HAL function performs a thread blocking/sleeping delay of the specified time in milliseconds. This function must wait for this specified amount of time, at least.

#### ADIHAL\_wait\_us Synopsis

The synopsis for ADIHAL\_wait\_us is as follows:

uint32\_t ADIHAL\_wait\_us(void \*devHalInfo, uint32\_t time\_us);

Parameters include the following:

- void\*devHalInfo is a void pointer to the targeted device state container. The device state provides details of the targeted device.

- uint32\_t time\_us is the desired amount of time in (in ms) for which the function blocks or thread sleeps.

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application.

Dependencies: the ADIHAL\_wait\_us HAL function is dependent on application and platform specific modules

#### ADIHAL\_wait\_us Remarks

The ADIHAL\_wait\_us HAL function is used for delay/sleep between checking status events.

### ADIHAL\_writeToLog

The ADIHAL\_writeToLog HAL function writes a message to a log file for debugging purposes. This function uses the logLevel parameter to specify what type of message, warning, or error to write to the log file. The API functions call this function to log errors detected during the execution of the transceiver API. Logging and file details are platform specific and the devHalInfo parameter is expected to provide this information.

### ADIHAL\_writeToLog Synopsis

**UG-1295**

The synopsis for ADIHAL\_writeToLog is as follows:

adiHalErr\_t ADIHAL\_writeToLog(void \*devHalInfo, adiLogLevel\_t logLevel,

uint32\_t errorCode, const char \*comment);

#### Parameters include the following:

- void\*devHalInfo is a void pointer to the targeted device state container. The device state provides details of the targeted device.

- adiLogLevel\_t logLevel is an enumerated value to specify the type of log message being logged. The value is one of the following adiLogLevel\_t enumerator types:

- ADIHAL\_LOG\_MSG

- ADIHAL\_LOG\_WARN

- ADIHAL LOG ERR

- ADIHAL LOG\_SPI; refer to adiLogLevel\_t section for details

- uint32\_t errorCode is a 32-bit integer value representing the API error code reference for the error being logged.

- const char \*comment is a character array that holds the desired comment to represent the error.

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application.

Dependencies: the ADIHAL\_writeToLog HAL function is dependent on application and platform specific modules

#### ADIHAL\_writeToLog Remarks

This function is used to write a message to a log file for debugging purposes.

#### ADIHAL\_setLogLevel

The ADIHAL\_setLogLevel HAL function sets the HAL logging options for the device. This function sets the desired logging options for the logging feature. The device API calls this function based on the logging options set by the API user in the API layer. The HAL implementation maintains this logging option and defines its use with the ADIHAL\_writeToLog function. Logging and file details are platform specific and the devHallnfo parameter is expected to provide this information. The devHallnfo parameter can be used to maintain the logging options for a particular device.

#### ADIHAL\_setLogLevel Synopsis

The synopsis for ADIHAL\_setLogLevel is as follows:

adiHalErr\_t ADIHAL\_setLogLevel(void \*devHalInfo, uint16\_t halLogLevel)

Parameters inlcude the following:

- void\*devHalInfo is a void pointer to the targeted device state container. The device state provides details of the targeted device.

- uint16\_t logLevel is a bit mask to indicate the desired logging options. The value is one of the following adiLogLevel\_t enumerator types:

- ADIHAL\_LOG\_NONE

- ADIHAL\_LOG\_MSG

- ADIHAL\_LOG\_WARN

- ADIHAL\_LOG\_ERR

- ADIHAL\_LOG\_ALL

- uint32\_t errorCode is a 32-bit integer value representing the API error code reference for the error being logged.

- const char \*comment is a character array that holds the desired comment to represent the error.

Return value: an error of type adiHalErr\_t, ADIHAL\_OK indicates successful operation. Any other value may represent an error code to be returned to the application.

Dependencies: the ADIHAL\_setLogLevel HAL function is dependent on application and platform specific modules

### ADIHAL\_setLogLevel Remarks

See the adiLogLevel\_t and ADIHAL\_writeToLog sections.

### **SOFTWARE INTEGRATION**

The API package was developed on a Xilinx Zynq ZC706 reference platform and utilizes a Cortex\*-A9 processor that runs a Linux variant. Using the provided API in a custom hardware and software environment is readily accomplished because the API was developed abiding by ANSI C constructs and maintaining Linux system call transparency. The ANSI C standard was followed to ensure agnostic processor and operating system integration with the API code.

### IMPLEMENTING HARDWARE ABSTRACTION INTERFACE

Users develop code to target custom hardware platforms and therefore use different drivers for the peripherals, for example, SPI and GPIO, in comparison to the drivers chosen for the Analog Devices evaluation platform. The HAL interface is a library of functions that the API uses when the API must access the target platform hardware. The HAL is defined by **adi\_hal.h**. The implementation of this interface is platform dependent and is implemented by the developer in the **adi\_hal.c** file. The prototypes of the required functions defined in the **adi\_hal.h** file must not be modified because doing so breaks the API.

Table 1 lists the functions required by the HAL interface for integration. For full details on the definition and required operation of these functions, see the Hardware Abstraction Layer section and the HAL Interface Definition section.

### Table 1. HAL Interface Functions for User Integration

| Function Name        | Function Description                                                                                                    |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|

| ADIHAL_openHw        | Open and initialize all platform drivers/resources and peripherals required to control the device (SPI, timer, logging) |

| ADIHAL_closeHw       | Close any resources opened by ADIHAL_openHw                                                                             |

| ADIHAL_resetHw       | Toggle the hardware reset signal for the device                                                                         |

| ADIHAL_setTimeout    | Set the maximum time in which the API expects the HAL functions to complete and return                                  |

| ADIHAL_spiWriteByte  | Write a single byte of data to a 15-bit register address on the targeted SPI device                                     |

| ADIHAL_spiReadByte   | Read a single byte of data from a 15-bit register address on the targeted SPI device                                    |

| ADIHAL_spiWriteBytes | Write an array of data bytes to an array of register addresses on the targeted SPI device                               |

| ADIHAL_spiReadBytes  | Read an array of data bytes from an array of register addresses on the targeted SPI device                              |

| ADIHAL_spiWriteField | Perform a read/modify/write to a bit field in a particular SPI register                                                 |

| ADIHAL_spiReadField  | Read a particular bit field of data from a SPI register                                                                 |

| ADIHAL_wait_us       | Perform a wait/thread/sleep operation in units of µs                                                                    |

| ADIHAL_setLogLevel   | Mask to set the severity of information to write to the log (error/warning/message)                                     |

| ADIHAL_writeToLog    | Log a debug message (message/warning/error) from the API to the platform log                                            |

### **DEVELOPING THE APPLICATION**

The /src/app/example/headless.c file provides a user example demonstrating top level configuration and control. The example application was written to support the control of one device. The API was written to support the control of multiple devices. Because the API is written in C, a pointer to a taliseDevice\_t data structure is used to describe or point to a particular device. To support multiple devices, the application layer code must instantiate multiple taliseDevice\_t structures to describe each physical device. Many initialization settings also have data structures that are defined by the API.

### **Include Files**

The API has multiple **.h** header files. For core API functionality, Table 2 shows the mandatory **.h** header files that must be included in the application layer program. Optional add on API functions can be included if the application requires those features as shown in Table 3. Note that the places typedef definitions in files with **\_types** suffixes, for example, **talise\_types.h**. These **\_types.h** files are included within their corresponding **.h** files and do no need to be manually included in the application layer code.

| Mandatory Include Files | Description                          |

|-------------------------|--------------------------------------|

| talise.h                | Core run-time functions              |

| talise_error.h          | Core error handling functions        |

| talise_arm.h            | Arm related functions                |

| talise_cals.h           | Calibration related functions        |

| talise_gpio.h           | GPIO related functions               |

| talise_jesd204.h        | JESD204B interface related functions |

| talise_radioctrl.h      | Functions for controlling the radio  |

| talise_rx.h             | Receiver related functions           |

| talise_tx.h             | Transmitter related functions        |

Table 2. Mandatory .h Header Files for the Application Layer

#### Table 3. Optional .h Header Files for the Application Layer

| Optional (Add On) Include Files | Description                                                |

|---------------------------------|------------------------------------------------------------|

| talise_agc.h                    | Add on receiver automatic gain control (AGC) functionality |

The **talise\_reg\_addr\_macros.h** and **talise\_arm\_macros.h** files are not needed by the application layer and are only used directly by the API. The **talise\_user.h** file does not need to be included in the application layer unless the application layer is required to access the exported variables contained in the file (receiver gain tables).

Note that the **talise\_user.h** and **talise\_user.c** files contain the default gain table as well as defines for API timeouts and SPI read intervals, which can be set as needed by the baseband integrated circuit (BBIC). The **talise\_user.h** files are the only API files that the developer has permission to change.

### **API Data Structures**

There are two top level data structures used by the API to allow multiple device support: the taliseDevice\_t structure and the taliseInit\_t structure. The taliseDevice\_t structure identifies each instance of a physical device. The taliseDevice\_t structure has two members: devHalInfo and devStateInfo.

The data structure is as follows:

```

typedef struct

{

void *devHalInfo; /*!< ADI_HAL Hardware layer settings pointer specific to this

Talise instance */

taliseInfo_t devStateInfo; /*!< Talise runtime state container */</pre>

```

#### } taliseDevice\_t;

The devHalInfo member is defined as a void pointer and allows the user to define and pass any platform hardware settings to the platform HAL layer functions. For example, the devHalInfo member can contain information, such as which SPI chip select must be used for the physical device. The API does not use the devHalInfo member, and therefore does not define what information it should contain. Note that the API functions are shared across all instances of physical devices. The devHalInfo structure defined by the developer identifies which physical device is targeted (SPI chip select) when a particular API function is called. It can be necessary for the developer to store other hardware information unique to a particular device in this structure, for example, timer instances and log file information, to allow for multithreading. It is expected that only one thread use the API to a particular device.

The devStateInfo member of the taliseDevice\_t structure is a run-time state container for the API. The application layer must allocate memory for this structure, but only the API writes to the structure. The application layer allocates the devStateInfo member with all zeroes. The API uses the devStateInfo member to keep up with the current state of the API (if has it been initialized or if the Arm loaded), as well as a debug store for any run-time data, such as error codes and error sources. It is not intended for the application layer to directly access the devStateInfo member, as the API functions are provided to access the last error code and source information.

The taliseInit\_t structure is the second important top level structure. The core initialization settings to configure a device are stored in this structure and passed to the API initialization functions during the initialization phase. This structure contains the receiver/ transmitter/observation receiver profile settings, system clock settings, JESD204B settings, and specific SPI controller settings. The application layer passes a pointer to an instance of the taliseInit\_t structure for a particular device to the TALISE\_initialize() API function to handle the majority of the device initialization. After initialization is complete, the taliseInit\_t structure can be disposed of or deallocated.

The data structure is as follows:

```

typedef struct

```

```

{

```

```

taliseSpiSettings_t spiSettings; /*!< SPI settings data structure */

taliseRxSettings_t rx; /*!< Rx settings data structure */

taliseObsRxSettings_t tx; /*!< Tx settings data structure */

taliseDigClocks_t clocks; /*!< Holds settings for CLKPLL and reference clock */

taliseJesdSettings_t jesd204Settings; /*!< Holds the JESD204B data link settings */</pre>

```

### } taliseInit\_t;

### Receiver, Transmitter, and Observation Receiver API Profiles

The API is designed to be configured using a use case profile of settings for the receiver, transmitter, and observation receiver. The taliseInit\_t structure shown in the API Data Structures section holds the profile information, which is used during initialization to configure the device. The same API is used to support the receiver only device as is used to support the transmitter and observation receiver devices and TDD devices in the family of transceivers. The API can be used for a receiver only configuration, as well as for a transmitter and observation receiver configuration. It is not possible to use a transmitter profile only, because the observation receiver configuration is necessary for the transmitter initialization and tracking calibrations to run properly.

For a receiver only device, the receiver member in the taliseInit\_t structure must be initialized with a valid receiver profile. The transmitter and observation receiver members of the taliseInit\_t structure are allocated, but these members can be initialized to all zeros if unused. Additionally, for a transceiver and observation receiver device, the receiver member can be initialized to zeros, and the transceiver and observation receiver must be initialized with a valid use case profile. The TALISE\_initialized API function determines which profiles are valid based on a non-zero I/Q data rate and if the channels are enabled.

For example, init->tx.txChannels, init->obsRx.obsRxChannelsEnable, and init->rx.rxChannels members are used by the API to identify which profiles to verify and use during initialization. The profiles are verified by ensuring that the I/Q data rates for each enabled profile can be accomplished by the common digital clocks available to the datapath. If the profiles are not possible due to inconsistency in the necessary shared clocks, the API returns an error during initialization.

Because the profiles share common digital clock settings, the taliseInit\_t structure has a single clock member to describe the clock PLL and digital clock information. The JESD204B framer and deframer settings are shared as well, and these settings are pulled out to the taliseJesdSettings\_t member. The receiver and observation receiver member structures contain a member that allows each profile to select which framer to use.

The latest supported profiles can be obtained from the latest TTES. The profile information is stored in a file called **ProfileLUT.txt** that ships with the software. The software is capable of generating the C code for the initialization structure necessary for the settings chosen in the evaluation software. The autogenerated initialization structure provides the developer a with low risk path to creating a correct initialization structure that works on the Analog Devices evaluation platform with the API.

### Initialization Data Structures

The API functions use a specific set of data structures. The application layer code is responsible for initializing these data structures. All API functions use a pointer to a taliseDevice\_t structure to describe the device of interest, which allows the application layer to control multiple devices in a system using the same API library. It is imperative that structure initialization is complete before attempting system operation. The file /src/app/example/talise\_config.c illustrates structure initialization. Explanations for each data structure can be found in the talise.chm document. Table 4 contains a list of the initialization structures used by the API.

| Data Structure      | Location                            | Description                                                                                                        |

|---------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| taliselnit_t        | /src/devices /talise/talise_types.h | Top level initialization structure.                                                                                |

| taliseSpiSettings_t | /src/devices/talise/talise_types.h  | This contains the SPI controller configuration, which is typically a subset of the platform hardware SPI settings. |

| taliseFir_t         | /src/devices/talise/talise_types.h  | Data structure to specify finite infinite response (FIR) filter settings.                                          |

| taliseRxSettings_t  | /src/devices/talise/talise_types.h  | Data structure to specify receiver datapath settings.                                                              |

| taliseRxProfile_t   | /src/devices/talise/talise_types.h  | Data structure to specify settings for the current receiver specific use case profile.                             |

| Table 4. Initialization | Data Structures | Used in the API |

|-------------------------|-----------------|-----------------|

|-------------------------|-----------------|-----------------|

| Data Structure                 | Location                                   | Description                                                                               |

|--------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|

| taliseRxGainControl_t          | /src/devices/talise/talise_types.h         | Data structure to hold receiver gain control settings for initialization.                 |

| taliseTxSettings_t             | /src/devices/talise/talise_types.h         | Data structure to specify transceiver datapath settings.                                  |

| taliseTxProfile_t              | /src/devices/talise/talise_types.h         | Data structure to specify settings for the current transceiver specific use case profile. |

| taliseObsRxSettings_t          | /src/devices/talise/talise_types.h         | Data structure to specify observation receiver datapath settings.                         |

| taliseORxGainControl_t         | /src/devices/talise/talise_types.h         | Data structure to specify observation receiver gain control settings for initialization.  |

| taliseJesdSettings_t           | /src/devices/talise/talise_jesd204_types.h | Data structure to specify JESD204B framer and deframer configuration information.         |

| taliseJesd204bDeframerConfig_t | /src/devices/talise/talise_jesd204_types.h | Data structure to specify the settings for the deserializer and deframer configuration.   |

| taliseJesd204bFramerConfig_t   | /src/devices/talise/talise_jesd204_types.h | Data structure to specify JESD204B framer configuration settings.                         |

| taliseDigClocks_t              | /src/devices/talise/talise_types.h         | Data structure to specify digital clock settings.                                         |

| taliseAgcCfg_t                 | /src/devices/talise/talise_agc_types.h     | Data structure to specify AGC settings for AGC initialization.                            |

Note that the taliseAgcCfg\_t structure is not part of the taliseInit\_t structure. The AGC configuration requires a large memory footprint for its initialization structure. Because the AGC may not be used for every use case, it is not required to allocate memory for the structure unless the AGC feature is used. If the AGC feature is desired for the main receiver datapath, allocate the taliseAgcCfg\_t structure and pass a pointer to the structure to the TALISE\_setupRxAgc API function.

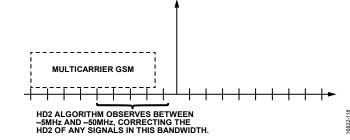

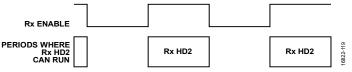

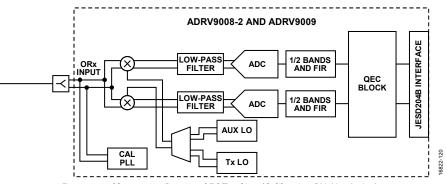

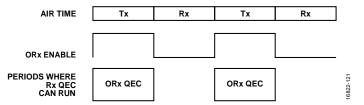

### API Error Handling and Debug