# ADuCM4050 User Guide

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### How to Set Up and Use the ADuCM4050

#### **FEATURES**

Up to 52 MHz ARM Cortex-M4F processor

512 kB of embedded flash memory with ECC

Optional 4 kB cache for lower active power

128 kB system SRAM with parity

Power management unit

Multilayer advanced microcontroller bus architecture bus matrix

Central DMA controller

Beeper interface

SPORT, SPI, I<sup>2</sup>C, and UART peripheral interfaces

Cryptographic hardware support with AES-128, AES-256 along ECB mode, CBC mode, CTR mode, CCM mode, modified CCM mode, and SHA-256

Protected key storage with key wrap and unwrap

2 RTCs

3 general-purpose timers

1 watchdog timer

RGB timer for driving RGB LED

Programmable GPIO pins

Keyed HMAC with key unwrap

Hardware CRC calculator with programmable generator polynomial Power-on reset and power supply monitor

12-bit successive approximation register ADC

True random number generator

#### **GENERAL DESCRIPTION**

This user guide provides detailed information on the ADuCM4050 microcontroller functionality and features. Each section describes a different feature.

The ADuCM4050 processor is an ultra low power, integrated, mixed-signal, microcontroller system used for processing, control, and connectivity. The microcontroller unit (MCU) subsystem is based on the ARM\* Cortex-M4F processor, a collection of digital peripherals, cache embedded static random access memory (SRAM) and flash memory, and an analog subsystem that provides clocking, reset, and power management capabilities along with the analog-to-digital converter (ADC).

The ADuCM4050 processor provides a collection of power modes and features, such as dynamic and software controlled clock gating and power gating, to support extremely low dynamic and hibernate power management.

Full specifications on the ADuCM4050 are available in the product data sheet and the ADuCM4050 Ultra Low Power ARM Cortex-M4F MCU with Integrated Power Management Hardware Reference Manual.

## ADuCM4050 User Guide

## UG-1160

## **TABLE OF CONTENTS**

| Features                                       | 1  |

|------------------------------------------------|----|

| General Description                            | 1  |

| Revision History                               | 2  |

| Getting Started                                | 3  |

| Software Installation                          | 4  |

| IAR Embedded Workbench Configuration           | 5  |

| Power Optimization for the ADuCM4050 Processor | 7  |

| ADuCM4050 Processor Power Management           | 7  |

| ADuCM4050 Processor Power Modes                | 7  |

| Fast Wake Up from Hibernate Mode               | 13 |

| Flash Memory and Instruction SRAM              | 13 |

| Normal Wake Up                                 | 13 |

| Fast Wake Up                                   | 13 |

| Using the ADuCM4050 Processor Boot Kernel      | 17 |

| Device Information Space Overview              | 17 |

| Boot Kernel Overview                           | 17 |

| UART Downloader                                | 20 |

| Read Protection Key and Hashing                | 24 |

| Memory Configuration                           | 25 |

| Handling CRC in the IAR Workbench              | 26 |

| CrossCore Serial Flash Programmer              | 26 |

| Cache Memory in the ADuCM4050                  | 28 |

| Storage and Access Ecosystem Block Diagram     | 28 |

| Flack Controller                               | 20 |

| Effects of Cache                             | 28 |

|----------------------------------------------|----|

| Current Consumption Comparison               | 30 |

| Dual RTC Feature in the ADuCM4050            | 31 |

| Comparison of the RTC Features               | 31 |

| Power Considerations                         | 31 |

| Conclusion                                   | 31 |

| Benefits of ADuCM4050 the DC-to-DC Converter | 32 |

| DC-to-DC Basics                              | 32 |

| Capacitors vs. Inductor Converters           | 34 |

| Conclusions                                  | 35 |

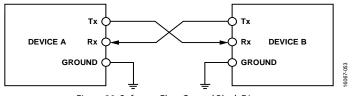

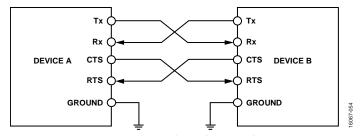

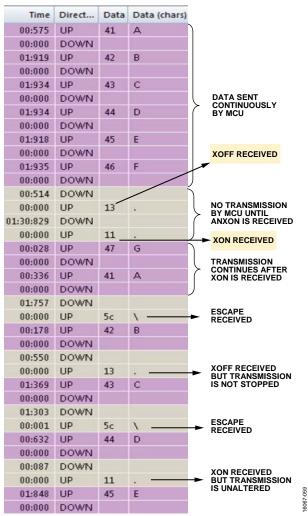

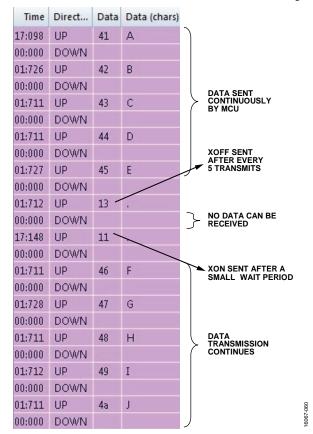

| UART Software Flow Control                   | 36 |

| UART Flow Control                            | 36 |

| System Description                           | 37 |

| Data Capture                                 | 40 |

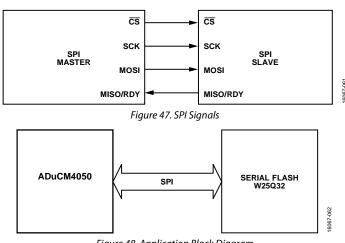

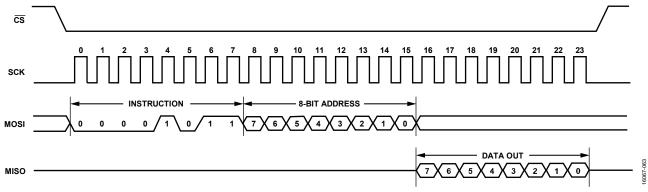

| SPI Flow Control Methods                     | 41 |

| SPI Read Command Mode                        | 41 |

| Flow Control Modes                           | 43 |

| Conclusions                                  | 44 |

| Sleep on Exit                                | 46 |

| Benefits                                     | 46 |

| Enabling the Sleep on Exit Feature           | 46 |

| System Control Register in the ADuCM4050     | 47 |

#### **REVISION HISTORY**

6/2018—Revision A: Initial Version

## **GETTING STARTED**

This section introduces the tools and support packages required to develop an application for the ADuCM4050 microcontroller. This section describes how to download, install, and configure the files that program the ADuCM4050.

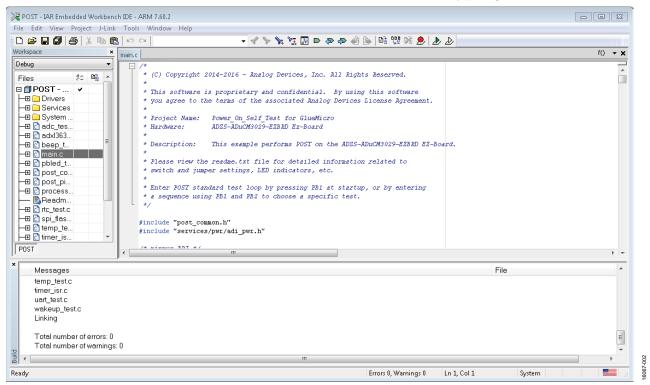

This section describes different steps in developing an application by using the IAR Embedded Workbench\* as an integrated development environment (IDE). This section also describes how to download and run sample codes provided with the device family package (DFP) drivers.

Figure 1. IAR Embedded Workbench

#### **SOFTWARE INSTALLATION**

The software tools required to develop applications with the ADuCM4050 are available for download on the EV-COG-AD4050 page.

**Table 1. Required Software Tools**

| Tool                                          | Functions                                                                                                      |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| IAR Embedded<br>Workbench                     | Used for compiling, debugging, and code development                                                            |

| Cross Core<br>Embedded<br>Studio              | Used for compiling, debugging, and code development                                                            |

| Segger J-Link<br>Software                     | J-Link software and documentation pack that includes USB drivers for the emulator, J-Link commander, and so on |

| ADuCM4050<br>Device<br>Family Pack<br>Drivers | Includes ADuCM4050 peripheral drivers and libraries, IAR configuration files, and the source and header files  |

#### Installing the Segger J-Link Driver

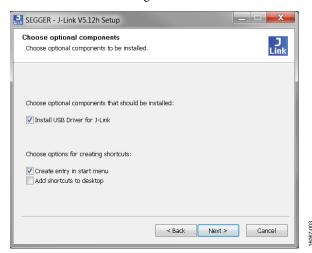

The Segger J-Link USB driver must be installed before using a serial wire interface, such as the interface of the IAR Embedded Workbench, to download and debug code.

Use the following procedure to install the J-Link USB driver:

- Download the latest Segger J-Link software and documentation pack from the Segger website.

- 2. Run the executable software installer within the download directory.

- Follow the on-screen instructions to complete the installation.

Ensure the Install USB Driver for J-Link option is checked, as shown in Figure 2.

Figure 2. Segger J-Link Driver Installation Options

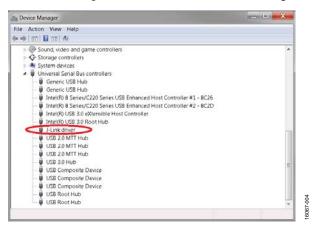

- 4. Plug in the J-Link emulator board, and open the **Device Manager**.

- Check that the emulator board appears in the Windows\*

Device Manager in the USB controllers lists (see Figure 3).

Figure 3. Device Manager

After following the software installation procedures, the USB driver for the J-Link is installed and verified.

#### IAR Tools Installation

The IAR Embedded Workbench and the included IAR C/C++ Compiler generates the fastest performing, most compact code in the industry for ARM-based applications. Therefore, Analog Devices, Inc., created the DFP drivers for the ADuCM4050 for the IAR Embedded Workbench.

The KickStart edition is a free starter kit and evaluation version of IAR. This edition has limitations, both in code size (32 kB) and in the service and support provided.

The IAR KickStart software is available as a free trial to download on the IAR website.

For a detailed procedure on installing the IAR Embedded Workbench and adding license details, if required, refer to the *Installation and Licensing Guide for IAR Embedded Workbench*, which is available on the IAR website.

The DFP examples are for the IAR Embedded Workbench Version 8.20.1 or later. Project compatibility issues may occur when using different versions. ADuCM4050 User Guide UG-1160

#### **ADuCM4050** Device Family Pack (DFP)

The ADuCM4050 DFP provides the configuration, support files, and components required to ease the development of the ADuCM4050.

The contents of the DFP are as follows:

- Source files for the device drivers and services for use on the ADuCM4050 processor

- Tool chain support. These components are installed in the IAR Embedded Workbench workspace to configure the tool chain to recognize the ADuCM4050

- Documentation containing details about the present version of DFP

The IAR Embedded Workbench must be installed before installing the DFP.

Use the following procedure to install the DFP:

- Download the ADuCM4050 DFP on the EV-COG-AD4050 page.

- Select the ADuCM4x50 Device Family Pack, which leads you to the page to download the latest version of the DFP. This is a CMSIS pack file that must be installed in IAR Embedded Workbench Version 8.11.3 and above.

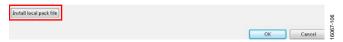

- Open the IAR Embedded Workbench IDE and select the CMSIS Pack Installer, as shown in Figure 4.

Figure 4. CMSIS Pack Installer

4. Click **Install local pack file** in the window that is shown in Figure 5, and browse to the DFP CMSIS pack file downloaded to install it.

Figure 5. Install Local Pack File Button

After installation completes, the DFP displays installed (see Figure 6).

Figure 6. Completed Installation of the DFP

#### IAR EMBEDDED WORKBENCH CONFIGURATION

This section describes the IAR Embedded Workbench configuration procedure for proper operation of the ADuCM4050. Only the sections that must be modified from the default values are described.

Take the following steps to configure the IAR:

In Options, ensure the Analog Devices ADuCM4050 device option is selected as the target.

- 2. Go to C/C++ Compiler > Optimizations, select from the different optimization options for speed, code size, balance, and so on, depending on your application needs. Sometimes, the compiler identifies the writes of a register as eligible to be optimized, which may cause unexpected behavior. In such situations, it is recommended to protect configuration functions from being optimized by using the following code:

- #pragma optimize=none

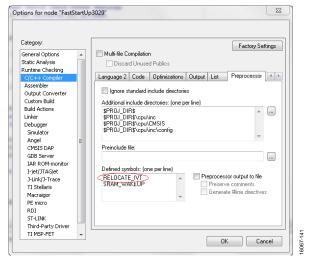

- Go to C/C++ Compiler > Preprocessor and include the path of the included directories, depending on the code to be run.

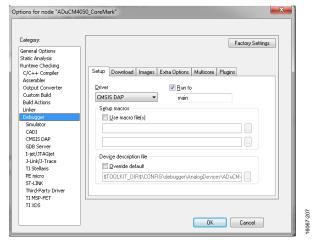

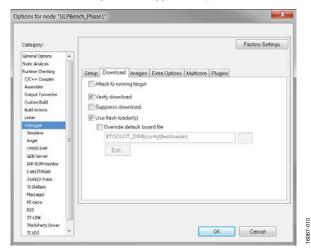

- 4. Go to Debugger and select CMSIS DAP as the debugger within the Driver dropdown menu (see Figure 7). Verify that both the Verify download and Use flash loader(s) boxes are checked in the Debugger > Download menu, as shown in Figure 8.

Figure 7. Debugger > Setup Tab

Figure 8. **Debugger** > **Download** Tab

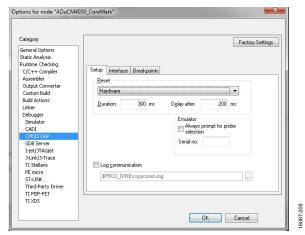

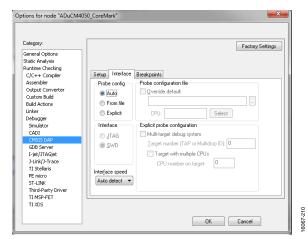

Figure 9 shows the CMSIS DAP > Setup configuration. Be sure to use the Hardware target reset strategy under the Reset dropdown menu. Figure 10 shows the CMSIS DAP > Interface configuration

Figure 9. CMSIS DAP > Setup Configuration Tab

Figure 10. CMSIS DAP > Interface Configuration Tab

## POWER OPTIMIZATION FOR THE ADuCM4050 PROCESSOR

Choosing a low power MCU is a difficult task because it involves reviewing data sheets to analyze electrical specifications. It is often difficult to relate these specifications to applicable, system level use cases.

Evaluating various power modes while considering peripheral operations emulating real use case scenarios is an essential step in choosing the right MCU for a power sensitive application. Key aspects to evaluate when choosing an MCU for low power applications include the following:

- Availability of low power modes and the impact of these modes on the ability to retain the contents of the SRAM.

- Power consumption with the real-time clock (RTC) running while the rest of the system is in low power mode.

- Wake-up times from low power modes.

- Supply voltage range from an application standpoint. The designer can adjust and select the system supply voltage, depending on the component requirements.

- Power consumption in active mode.

- Core activity—example algorithm processing.

- Peripheral activity—direct memory access (DMA) operations.

- Simultaneous core and peripheral activity.

- Flexibility in choosing core and peripheral clock frequencies that meet system requirements while keeping the power consumption low.

- Hardware DMA blocks that enable the CPU to be in low power mode during peripheral activity.

The ADuCM4050 processor is an ultra low power, integrated, mixed-signal, MCU system for processing, control, and connectivity. The MCU system is based on an ARM Cortex-M4F processor, offering 1.25 DMIPS per MHz of performance running up to 52 MHz, combined with a collection of digital peripherals, embedded SRAM and flash memories, and an analog subsystem that provides clocking, reset, and power management capabilities in addition to an ADC subsystem.

The ADuCM4050 processor is one of the few ultra low power MCUs on the market that offers a cache controller. Programs that repeatedly access the same data or instructions make

effective use of cache memory, thereby reducing overall power consumption.

The power consumption of an MCU largely depends on two factors: the operating voltage and the frequency at which the system operates. The ADuCM4050 processor incorporates several power modes that are useful in building battery-powered or self-powered (energy harvesting) applications.

This section discusses the power modes of the ADuCM4050 processors in detail and provides example power measurements for several scenarios, to help developers choose power modes that best fit low power application requirements.

#### **ADUCM4050 PROCESSOR POWER MANAGEMENT**

The ADuCM4050 processor incorporates a highly customizable power management and clocking system that offers application developers the flexibility to balance power and performance. The power management blocks consist of integrated regulators, a clock gating scheme, and switches applicable to numerous application scenarios

The power management system features are as follows:

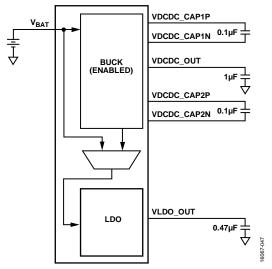

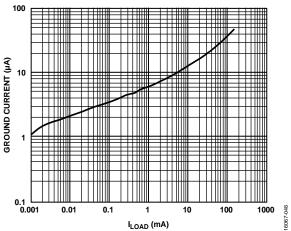

- An integrated 1.2 V low dropout (LDO) regulator and an optional capacitive buck regulator.

- Integrated power switches for low standby current in hibernate mode.

- Power gating to reduce leakage in sleep modes.

- A power supply monitor with a selectable voltage range.

#### **ADUCM4050 PROCESSOR POWER MODES**

The power management system provides the following low power modes:

- Active mode with customized clock gating features.

- Flexi mode with smart peripherals.

- Hibernate mode with optional SRAM retention capability.

- Shutdown mode without SRAM retention.

- Shutdown fast mode without SRAM retention.

Each mode provides a low power benefit with potential functionality trade-offs.

## **UG-1160**

Table 2 summarizes the status of the system blocks in each low power mode.

Table 2. Power Mode System Block Status

| Functional Block      | ARM Cortex-M4F Core | Buck              | Peripheral/DMA    | HFXTAL            | HFOSC             | LFXTAL            | PLL               | LFOSC | RTC0              | RTC1              | ADC               | SRAM            | Flash |

|-----------------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|-------------------|-------------------|-------------------|-----------------|-------|

| Active Mode           | On                  | User <sup>1</sup> | On    | User <sup>1</sup> | User <sup>1</sup> | User <sup>1</sup> | On              | On    |

| Flexi Mode            | Off                 | User <sup>1</sup> | On    | User <sup>1</sup> | User <sup>1</sup> | User <sup>1</sup> | On              | On    |

| Hibernate<br>Mode     | Off                 | Off               | Off               | Off               | Off               | User              | Off               | On    | User <sup>1</sup> | User <sup>1</sup> | Off               | On <sup>2</sup> | Off   |

| Shutdown<br>Mode      | Off                 | Off               | Off               | Off               | Off               | User              | Off               | Off   | User <sup>1</sup> | Off               | Off               | Off             | Off   |

| Shutdown<br>Fast Mode | Off                 | Off               | Off               | Off               | Off               | User              | Off               | Off   | User <sup>1</sup> | Off               | Off               | Off             | Off   |

<sup>&</sup>lt;sup>1</sup> In the user application code, this functional block can be configured on or off.

#### **Active Mode**

In active mode (also called full on mode), the ARM Cortex-M4F is active and executes instructions from flash memory and/or SRAM. All peripherals can be enabled or disabled at the discretion of the user, and active mode power can be enhanced by optimized clock management.

Several power saving options are available in active mode:

- Using the buck converter.

- Enabling the cache.

- Using dynamic clock scaling.

- Using clock gating.

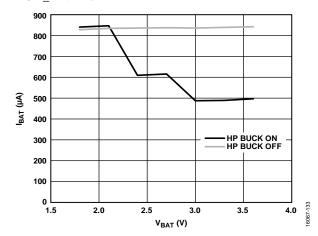

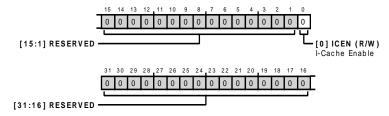

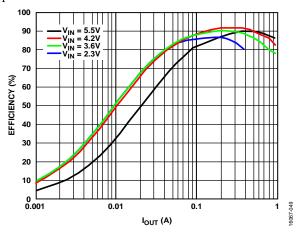

#### **Buck Converter**

The optional integrated buck converter feature saves power in active mode. The buck converter powers the linear regulator, which powers the digital core domain. The buck converter enters bypass mode after the battery voltage ( $V_{BAT}$ ) falls below ~2.3 V. After entering bypass mode, the buck converter output follows the input.

For designs in which the optional buck converter is not used, the VDCDC\_CAP1P, VDCDC\_CAP1N, VDCDC\_OUT, VDCDC\_CAP2P, and VDCDC\_CAP2N pins must be left unconnected.

The buck converter is solely for processor usage. An external load cannot be connected to the buck converter output.

Enable the buck converter by setting the HPBUCKEN bit in the CTL1 register per the following code:

\*pREG\_PMG0\_CTL1 |= (1<<BITP\_PMG\_CTL1\_HPBUCKEN);

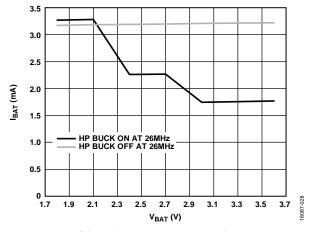

Figure 11 compares the power consumption of the ADuCM4050 processor when computing prime numbers with the following conditions:

- $V_{RAT} = 3.0 \text{ V}$

- HCLK = PCLK = 26 MHz

- Cache memory disabled

The buck converter impacts current consumption positively at higher  $V_{BAT}$  values. Specifically, there is roughly a 50% decrease in the active current when  $V_{BAT} \ge 3 \text{ V}$ .

Figure 11. Impact of the Buck Converter on Active Mode Power Consumption

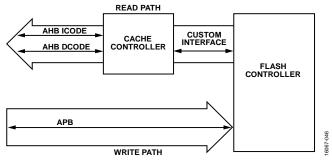

#### **Enabling Cache Memory**

Cache memory reduces the average time to access data from flash memory. For scenarios in which the CPU is required to run an algorithm or the same data must be accessed repeatedly, cacheable memory can reduce the power consumption because execution is from the internal instruction SRAM. When the cache controller is enabled, 4 kB of instruction SRAM is reserved as cache memory.

Cache memory is disabled at startup by default. Use the following procedure to enable the cache memory:

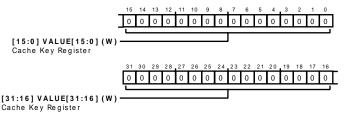

- Read the cache enable status bit (Bit 0 in the FLCC\_CACHE\_ STAT register) to ensure cache memory is disabled. Poll this bit until it clears.

- 2. Write the user key to the FLCC0\_CACHE\_KEY register.

```

*pREG_FLCCO_CACHE_KEY = 0xF123F456;

```

Set the instruction cache enable bit (ICEN in the FLCC0\_ CACHE\_SETUP register) as follows:

```

*preg_flcc0_cache_setup |= (1 << bitp_flcc_cache_setup_icen);

```

<sup>&</sup>lt;sup>2</sup> The retainable SRAM size is configurable.

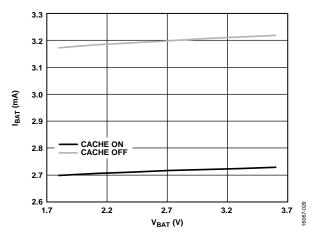

Figure 12 compares the power consumption of the ADuCM4050 processors when computing prime numbers with the following conditions:

- $V_{BAT} = 3.0 \text{ V}$

- HCLK = PCLK = 26 MHz

- Buck converter disabled

Figure 12. Impact of Cache Memory on Active Mode Power Consumption

Enabling the cache memory reduces the average active current consumption by  $\sim$ 15%.

#### **Dynamic Clock Scaling**

Dynamic clock and/or frequency scaling is a proven method to reduce power consumption. The ADuCM4050 processors have a flexible clock architecture that allows dynamic modification of the CPU and peripheral clock frequencies. A combination of clock dividers and a phase-locked loop (PLL) provides flexibility in deriving an optimum system clock frequency that guarantees system performance while keeping the power consumption low, as compared to a fixed clock scheme. Programmable clock dividers are available to generate the clocks in the system, and the divisors can be configured while the code is running.

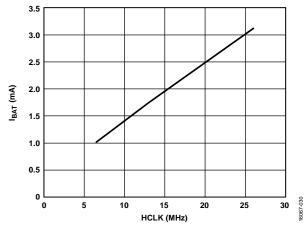

Figure 13 plots the power consumption of the ADuCM4050 processors when computing prime numbers with the following conditions:

- $V_{BAT} = 3.0 \text{ V}$

- HCLK = PCLK (the source of the root clock is HFOSC)

- Buck converter disabled

- Cache disabled

Figure 13. Impact of Core Clock Frequency on Active Mode Power Consumption

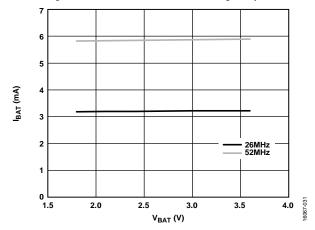

Figure 14 plots the power consumption of the ADuCM4050 processors when computing prime numbers with the following conditions:

- $V_{BAT} = 3.0 \text{ V}$

- HCLK = PCLK (the source of the root clock is XTAL)

- Two wait state on the flash

- Buck converter disabled

- Cache disabled

Power dissipation decreases as core clock frequency decreases.

Figure 14. Impact of Core Clock Frequency on Active Mode Power Consumption with the PLL

#### **Clock Gating**

The system is heavily clock gated and uses automatic clock gating techniques. Most peripherals are automatically clock gated when the peripheral is disabled, such that the clock runs only when the peripheral is enabled. The exceptions are I²C, general-purpose input/output (GPIO), and the general-purpose timer (GPTMR). These blocks must be manually clock gated using the CLKCON5 register. Gate the peripheral clock completely by setting the CLKG\_CLK\_CTL5 bit. Any access to the clock gated peripherals overrides the clock gate settings in the CLKCON5 register.

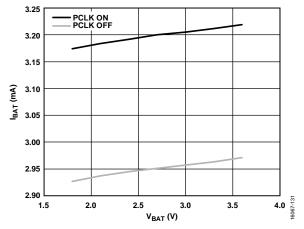

For application scenarios in which the core is processing data and no peripheral activity is desired, the peripheral clock (PCLK) can be turned off to save power. Figure 15 shows the power consumption of the ADuCM4050 processors when computing prime numbers with the following conditions:

- $V_{BAT} = 3.0 \text{ V}$

- Buck converter disabled

- Cache memory disabled

- HCLK = PCLK = 26 MHz

Figure 15. Impact of Peripheral Clock Gating on Active Mode Power Consumption

As shown in Figure 15, a ~0.2 mA reduction in the active current is observed when the peripheral clock is gated.

In active mode, the four techniques described in this section can be combined to achieve maximum power savings.

#### Flexi Mode

Flexi mode is a flexible sleep mode useful in scenarios in which the core must wait for a peripheral data transfer to complete before it can start processing. In flexi mode, the core is clock gated, and the remainder of the system is active. Flexi mode substantially reduces active power when low speed activity is expected to complete (for example, reading a certain number of bytes from a sensor) before the processor must be woken up to process the data.

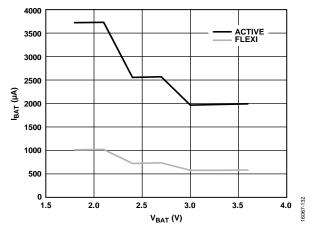

Consider a scenario in which the CPU configures a serial peripheral interface (SPI) DMA and must wait for the DMA to complete. Figure 16 shows the power consumption of the ADuCM4050 processors transferring data over the SPI using DMA accesses with the following conditions:

- $V_{BAT} = 3.0 \text{ V}$

- Buck converter enabled

- Cache disabled

- PCLK = 26 MHz

- SPI\_DIV = 49

Figure 16. Impact of Flexi Mode on Power Consumption

As shown in Figure 16, there is nearly a 71% savings in power when flexi mode is used while the DMA is ongoing, rather than keeping the core in active mode.

A number of wake-up sources that exit flexi mode (for example, DMA interrupts, external interrupts, timer interrupts, and so on), and it typically takes only one CPU clock cycle to exit.

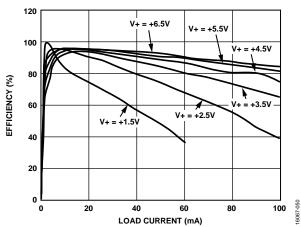

The buck converter can also be enabled in flexi mode to save additional power. Figure 17 shows the power consumption of the ADuCM4050 processor across  $V_{\text{BAT}}$  in flexi mode with the buck converter on while transferring data over the SPI using DMA accesses with the following conditions:

- $V_{BAT} = 3.0 \text{ V}$

- Cache memory disabled

- PCLK = 26 MHz

- SPI DIV = 49

Figure 17. Impact of the Buck Converter on Flexi Mode Power Consumption

As seen in Figure 17, a similar power improvement pattern to the impact of the buck converter in active mode is shown in Figure 11. Specifically, when  $V_{BAT} \geq 3$  V, a 50% improvement in power is observed.

ADuCM4050 User Guide UG-1160

#### Hibernate Mode

In hibernate mode, the ARM Cortex-M4F core and all digital peripherals are off with configurable SRAM retention, port pin retention, a limited number of wake-up interrupts, and, optionally, an active RTC. All GPIO pin states are retained in hibernate mode. The ADuCM4050 processor also incorporates the SensorStrobe™ mechanism in the RTC1 block, which enables ultra low power sensor data measurement.

Before entering hibernate mode, most of the enabled peripherals must be programmed to undergo a specific sequence to properly enter or exit hibernate mode, and several system memory map registers (MMRs) and peripheral registers are retained while in hibernate mode. For more details, refer to the relevant peripheral information in the ADuCM4050 Ultra Low Power ARM Cortex-M4F MCU with Integrated Power Management Hardware Reference Manual.

#### **Configurable Retainable SRAM**

The ADuCM4050 processor supports SRAM partitioned in 32 kB blocks. Several memory sizes can be retained from 16 kB (default) up to 124 kB while in hibernate mode. The more SRAM that must be retained, the higher the power consumption in hibernate mode, as shown in Figure 18.

Figure 18. Current on the V<sub>BAT</sub> Supply Pin (I<sub>BAT</sub>) for Various Retained SRAM Values

The SRAM retention size can be configured by setting the appropriate bits in the PMG0\_SRAMRET register. For example, to enable 124 kB of SRAM to be retained while in hibernate mode, use the following code in the PMG0\_SRAMRET register:

```

*pREG_PMG_PWRKEY = 0x4859;

*pREG_PMG_SRAMRET |=

((1 << BITP_PMG_SRAMRET_SRAM_RET1_EN)|

(1 << BITP_PMG_SRAMRET_SRAM_RET2_EN)|

(1 << BITP_PMG_SRAMRET_SRAM_RET3_EN)|

(1 << BITP_PMG_SRAMRET_SRAM_RET4_EN));

```

If parity is enabled, initialization of nonretained SRAM regions may be required upon waking from hibernate mode.

#### Wake-Up Sources

The following events are capable of waking the device up from hibernate mode:

- External Interrupt 0 to External Interrupt 3

- RTC0 and RTC1 interrupt

- Battery voltage range interrupt

- Universal asynchronous receiver/transmitter (UART) receiver (Rx) pin activity

Of the two real-time clocks, RTC1 is the recommended wake-up source from hibernate mode because it consumes less power than RTC0, and it provides more functionality. In an application where both hibernate mode and shutdown mode must be used, only RTC0 can be used. RTC0 is the only real-time clock that can be used for exiting shutdown mode. See the Dual RTC Feature in the ADuCM4050 section for more information.

The wake-up time from hibernate mode from any of these events is  $\sim \! 10$   $\mu s$  when executing from flash and  $\sim \! 5$   $\mu s$  when executing from SRAM.

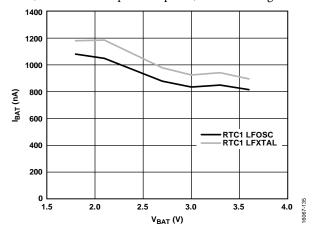

#### **RTC Clock Sources**

The ADuCM4050 processor offers two clock choices for the RTC1 block:

- A low power internal RC oscillator (LFOSC).

- An external crystal oscillator (LFXTAL).

Consider that the input clock for RTC1 is LFMUX. Therefore, the decision of choosing between LFOSC and LFXTAL must be made while taking into account the requirements for the other peripherals clocked by LFMUX.

Choosing to implement either LFOSC or LFXTAL is a trade-off between accuracy and power consumption. LFXTAL is more accurate (depending on the crystal manufacturer) compared to the LFOSC, but LFOSC dissipates less power, as shown in Figure 19.

Figure 19. Hibernate Current with RTC1 as the Wake-Up Source (LFOSC vs. LFXTAL)

#### SensorStrobe

The SensorStrobe mechanism allows the ADuCM4050 processor to be used as a programmable clock generator in all power modes, except in shutdown and shutdown fast modes. In this way, the external sensors have their timing domains mastered by the ADuCM4050 processors because the SensorStrobe output is a programmable divider from RTC1, which can operate up to a resolution of 30.7  $\mu s$ . The sensors and microcontroller are synchronous, which removes the need for additional resampling of data to time align the microcontrollers and the sensors.

#### Shutdown Mode

Shutdown mode is the deepest sleep mode in which digital and analog circuits are powered down. The state of the digital core and the SRAM memory content is not retained. However, the state of the pads is preserved, as is the wake-up interrupt configuration.

The configuration of the pads is preserved and locked after waking up from shutdown mode. The user must unlock the state of the pads by writing 0x58FA to the PGM\_TST\_CLR\_LATCH\_GPIOS register, preferably inside the interrupt service routine (ISR) routine:

\*preg\_PMG0\_TST\_CLR\_LATCH\_GPIOS = 0x58FA;

Additionally, the user must configure the appropriate wake-up source, choosing from the following options:

- External Interrupt 0 to External Interrupt 2

- External reset

- Battery falling below 1.6 V

- RTC0 timer

The RTC0 block can optionally be enabled in this mode, which allows the processor to be periodically woken up by the RTC0 interrupt.

The clock source for RTC0 must be LFXTAL because LFOSC is disabled in shutdown mode.

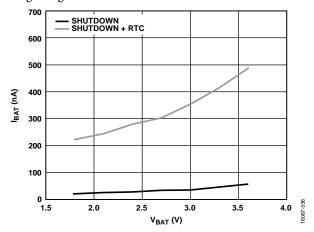

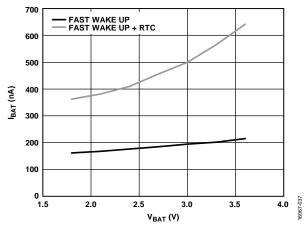

Because the RTC0 block must be powered to serve as a wake-up source, it adds to the power dissipation while in shutdown mode, as shown in Figure 20.

When the device wakes up from shutdown mode, the power-on reset (POR) sequence is followed, and code execution starts from the beginning.

Figure 20. Shutdown Mode Current (External Sources vs. RTCO)

#### Shutdown Mode—Fast Wake Up

Fast wake up mode has exactly the same behavior as the mode described in the Shutdown Mode section, except for the faster wake-up time at the expense of higher power consumption.

Figure 21 shows the power consumption in this power mode. As shown, enabling the RTC0 adds extra power dissipation.

Figure 21. Shutdown Mode Current (External Sources vs. RTC0)

## FAST WAKE UP FROM HIBERNATE MODE FLASH MEMORY AND INSTRUCTION SRAM

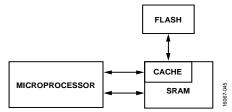

Flash memory is the long-term storage medium for any microcontroller. Because the flash memory is nonvolatile, it is used for the storage of constant data and program code of the microcontroller. Due to the nature of flash memories, memory access is slow compared to SRAM, cache, and other registers. The latency takes effect during the execution of a looping code that performs real-time calculations.

The ADuCM4050 microcontroller has the capacity to execute instructions in SRAM. Instruction SRAM (iSRAM) is a portion of the ADuCM4050 microcontroller dedicated to be a temporary program code and instruction storage. It is used when the program must execute a looping code faster and does not want the flash latency to affect the execution. The iSRAM is small (up to 32 kB) compared to the 512 kB flash memory. Therefore, only important code and instructions must use the iSRAM.

#### **NORMAL WAKE UP**

Cortex-M4F core and all the digital peripherals (except some user-selectable SRAM blocks) are turned off during hibernate mode. The RTC can be configured by the user program to turn off during hibernate. (RTC0 and/or RTC1 might be on depending on the user configuration). Registers of the digital peripherals are also turned off. This is to ensure the low current consumption of the microcontroller during hibernate mode, although some registers are retained to allow the device to wake up in the same status it was in when it went to sleep.

An interrupt from one of the allowed wake-up sources boots the microcontroller from hibernate to active mode to service the interrupt. Refer to the ADuCM4050 Ultra Low Power ARM Cortex-M4F MCU with Integrated Power Management Hardware Reference Manual document for further information about the possible interrupt wake-up sources. During the transition from hibernate to active mode, the microcontroller reinitializes the digital peripherals that are off during hibernate before it executes the first instruction on the ISR.

The flash memory, where the program code is located, is also off during hibernate mode. Upon microcontroller wake up, the core turns on the flash memory. The flash memory initialization is slow, and it takes about  $5.7~\mu s$  to complete before it can take commands from the controller.

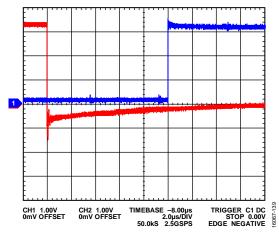

Figure 22 shows the delay time from triggering an external wake-up signal to microcontroller response by lighting up a light emitting diode. The red trace is the signal from the push button that triggers an external interrupt signal to wake up the microcontroller. The blue trace is the GPIO toggling indicating that the microcontroller is awake, that is, the first instruction executed is a GPIO toggle (GPIO\_TGL). The entire wake-up process takes around 10  $\mu s$  to complete.

Figure 22. Normal Wake Up from Hibernate Mode Response

#### **FAST WAKE UP**

One way to wake up from hibernate faster is to move the required functions and instructions to iSRAM. The microcontroller code starts earlier because the code must not wait for the completion of the flash memory initialization.

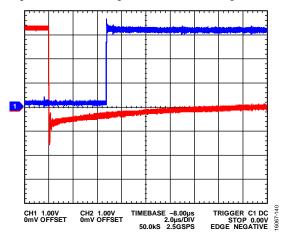

Figure 23 shows the delay time from triggering an external wake-up signal to microcontroller response with the fast wake-up procedure. The red trace is the signal from the push button, and the blue trace is the GPIO toggled as first instruction after waking up.

The wake-up time is reduced to around 4.5  $\mu$ s. This time assumes a 50% improvement with respect to normal wake up.

Figure 23. Fast Wake Up from Hibernate Mode Response

Table 3. Wake-Up Times with Different Peripherals

| ADuCM4050 Peripheral Activity                | Normal Wake-Up Time (μs) | Fast Wake-Up Time (μs) |

|----------------------------------------------|--------------------------|------------------------|

| Pin Toggle (Lighting an LED)                 | 9.7                      | 4.4                    |

| I <sup>2</sup> C Clock (First Edge, 400 kHz) | 12.3                     | 7.0                    |

| SPI Clock (First Edge, 400 kHz)              | 12.5                     | 7.2                    |

Table 3 shows a comparison of the wake-up times to different peripherals. The wake-up time is measured from the falling edge of the external wake-up signal to the first rising edge of the serial clocks (as for I<sup>2</sup>C and SPI) or the rising edge of the pin connected to the light emitting diode.

To perform fast wake up from hibernate mode, use the following procedure:

- 1. Initialize the iSRAM.

- 2. Modify the linker script to add sections for the functions and to remap the addresses.

- Relocate the interrupt vector table (VTOR) from flash to SRAM.

- Place the required functions and interrupt handlers in iSRAM.

#### Initialization of the iSRAM

To use the iSRAM, take the following steps:

- 1. Enable the iSRAM bank by asserting the INSTREN bit field in the PMG\_TST\_SRAM\_CTL register.

- 2. Retain the half of the iSRAM by asserting the BNK2EN bit in the PMG\_TST\_SRAM\_CTL register.

#### **Modification of the Linker Script**

Modify the linker script to help the linker place the code in the correct place in the memory map. Remap the addresses, and add the required sections for the location of the program code and interrupt handlers to iSRAM.

If using the IAR Embedded Workbench, apply the following changes to the linker script:

1. Remap the SRAM addresses. Search for the following line in the linker script:

```

define symbol USER_SRAM_MODE = 0;

```

Change the value of the USER\_SRAM\_MODE to 0 or 1.

Add sections for iSRAM. Search the linker script for the following lines:

```

// iSRAM section for placing code in

SRAM

place in iRAM {section ISRAM_REGION };

initialize by copy {section ISRAM_REGION

};

```

Modify the lines to include the .textrw section. IAR linker places the instructions for SRAM in the .textrw section.

```

// ISRAM section for placing code in SRAM

place in iRAM {section ISRAM_REGION,

section .textrw};

```

initialize by copy {section ISRAM\_REGION,

section .textrw};

#### **Interrupt Vector Table Relocation**

The interrupt vector table (IVT) lists the different interrupt sources for the ADuCM4050 microcontroller. The following events are capable of waking the MCU up from hibernate mode:

- External Interrupt 0 to External Interrupt 3

- RTC0 and RTC1 interrupt

- Battery voltage range interrupt

- UART receiver (Rx) pin activity

For fast wake up, move the IVT from flash to SRAM. In this way, the microcontroller does not need to wait for the flash initialization to check the location of the interrupt handler of the wake-up source.

Copy the IVT to SRAM and update the SCB register to the VTOR of the address of the interrupt vector in SRAM.

The file system\_ADuCM4050.c must be modified as follows:

1. Add multiple definitions before the SystemInit function

```

#ifdef RELOCATE_IVT

#include <assert.h>

#ifdef __GNUC_

#define ATTRIBUTE_INTERRUPT

_attribute___((__interrupt___))

#define KEEP_VAR(var) var

_attribute__((used))

#define WEAK_PROTO(proto)

__attribute__((weak)) proto

#define WEAK_FUNC(func)

__attribute__((weak)) func

#define VECTOR_SECTION

".isr_vector"

#define SECTION_PLACE(def,sectionname)

__attribute__ ((section(sectionname))) def

#define RESET_EXCPT_HNDLR ResetISR

#define COMPILER NAME

"GNUC"

#endif // __GNUC__

#ifdef USER_SPECIFIED_RTOS

#include <user_rtos_support.h>

#endif

#ifdef __ARMCC_VERSION

#define ATTRIBUTE_INTERRUPT

```

ADuCM4050 User Guide UG-1160

```

#define KEEP_VAR(var) var

_align(RELOCATION_ALIGNMENT)

/* Keil */

__attribute__((used))

#define WEAK_PROTO(proto) proto

__attribute__((weak))

#pragma message("WARNING: NO ALIGHMENT

#define WEAK FUNC(func) func

DEFINED FOR IVT RELOCATION")

#define VECTOR_SECTION "RESET"

#define SECTION_PLACE(def,sectionname)

/* reserve no-init aligned IVT space at top

__attribute__ ((section(sectionname))) def

of RAM */

#define RESET_EXCPT_HNDLR

SECTION_PLACE(KEEP_VAR(__no_init void *

__main

_relocated_vector_table[LENGTHOF_IVT]),

RELOCATION_ADDRESS);

#define COMPILER_NAME

#endif

"ARMCC"

#endif // __ARMCC_VERSION

2. Replace this line

SCB->VTOR = (uint32_t) &__Vectors;

#ifdef ___ICCARM___

with these lines

#ifdef RELOCATE_IVT

/* Copy the IVT (avoid use of memcpy

* Pm154 (rule 19.10): in the definition of a

here so it does not become locked into

function-like macro, each instance of a

flash), */

parameter shall be enclosed in parentheses.

size t i;

The parameters in the following macros

cannot be enclosed in parentheses.

//assert(

sizeof(__relocated_vector_table) ==

___Vectors_Size);

#pragma diag_suppress=Pm154

for (i = 0u; i < LENGTHOF_IVT; i++) {

_relocated_vector_table[i] =

#define ATTRIBUTE_INTERRUPT

__Vectors[i];

#define KEEP_VAR(var)

__root var

}

#define WEAK_PROTO(proto)

__weak proto

SCB->VTOR = (uint32_t)

#define WEAK_FUNC(func)

__weak func

&__relocated_vector_table;

#define VECTOR SECTION

".intvec"

/* Set the vector table address */

#define SECTION_PLACE(def,sectionname) def @

sectionname

SCB->VTOR = (uint32_t) &__Vectors;

#define RESET_EXCPT_HNDLR

#endif

__iar_program_start

3. Replace this line

#define COMPILER_NAME

"ICCARM"

extern uint32_t __Vectors;

with these lines

#endif /* ___ICCARM___ */

#ifdef RELOCATE_IVT

extern void* __Vectors[];

extern uint32_t ___Vectors_Size;

#else

#define RELOCATION_ADDRESS

(0x20000000)

extern uint32_t __Vectors;

#define RELOCATION ALIGNMENT

(0x200)

#endif

#define LENGTHOF_IVT (88u)

#if defined ( __ICCARM___ )

data_alignment=RELOCATION_ALIGNMENT /* IAR

#elif defined (__CC_ARM)

```

UG-1160 ADuCM4050 User Guide

Finally, it is necessary to declare the define RELOCATE\_IVT by adding it to the **C/C++ Compiler/Preprocessor** tab (see Figure 24) to activate the relocation code built in the evaluation board support package.

Figure 24. IAR **C/C++Compiler** Options—**RELOCATE\_IVT** Directive in the Defined Symbols Textbox

#### **Placement of Program Code to SRAM**

The procedure of placing the program code to SRAM is dependent on the compiler used.

For most compilers, use the following line before the function definition to tell the location of the defined function:

```

#pragma location="<linker section>"

```

For the IAR Embedded Workbench, use the \_\_ramfunc keyword before the function (see Figure 25).

```

__ramfunc void Ext_IntO_Handler(void) {

__disable_irq();

// write to spi tx registers

*((volatile uint32_t *) REG_SPI2_CTL) = spi_con_buff;

*[(volatile uint32_t *) REG_SPI2_TX] = 0x48;

*((volatile uint32_t *) REG_SPI2_TX) = 0x88;

*((volatile uint32_t *) REG_SPI2_TX) = 0x88;

*((volatile uint32_t *) REG_GPI00_0UT) = (1 << 13);

*((volatile uint32_t *) REG_XINTO_CLR) |= 1;

SCB->SCR &= ~(lu << 1);

</pre>

```

Figure 25. Sample for Appending \_\_ramfunc Directive to a Function

The amount of iSRAM retained depends on the PMG0\_ SRAMRET register configuration. The RET1 bit field enables the retention of the 12 kB in the range of  $0x1000\_0000$  to  $0x1000\_2$ FFF. The RET2 bit field enables the retention of the 16 kB in the range of  $0x1000\_3000$  to  $0x1000\_6$ FFFF. Be sure that the location of the code is in the retained region.

## USING THE ADUCM4050 PROCESSOR BOOT KERNEL

The ADuCM4050 processor features integrated flash memory that contains the user application code (user space) and a dedicated 4 kB bank of memory, with the information space arranged as shown in Figure 26. The total device storage is generally described as the size of the user space.

|                            | 0x80FFF | DEVICE INFORMATION       |  |

|----------------------------|---------|--------------------------|--|

| INFORMATION SPACE<br>(4kB) |         | BOOT KERNEL              |  |

|                            | 0x80000 |                          |  |

|                            | 0x7FFFF |                          |  |

| USER SPACE<br>(512kB)      |         | USER APPLICATION<br>CODE |  |

|                            | 0x00000 |                          |  |

Figure 26. Flash Information Memory Space

The ADuCM4050 processor features 512 kB of user space.

As shown in Figure 26, the information space block is further broken down into the boot kernel, residing in the upper 4 kB of flash memory, and the device information space. The boot kernel is responsible for implementing a secure environment, where the user application code can optionally be read and/or write protected, and executes the application from flash memory on reset. The boot kernel also provides a mechanism to upgrade the firmware through a UART downloader.

This section describes the information space region of the onchip flash memory, as well as both the boot process and how to use the UART downloader to perform field upgrades to the processor firmware.

#### **DEVICE INFORMATION SPACE OVERVIEW**

The device information space is reserved for use by Analog Devices and stores several trim and calibration values and other device specific metadata. The 256 bytes of device information space in Address 0x0008\_0F00 to Address 0x0008\_0FFF are protected and cannot be read by user code (attempted reads return bus error). The 32 bytes of device information space in Address 0x0008\_0EE0 to Address 0x0008\_0EFF can be read by user code and Table 4 summarizes the information stored therein. None of the device information space can be programmed or erased by the user.

**Table 4. List of User Accessible Parameters in Device Information Space**

| Address Range                 | Size                   | Description               |

|-------------------------------|------------------------|---------------------------|

| 0x0008_0EF0 to<br>0x0008_0EFF | 128 bits<br>(16 bytes) | Unique ID                 |

| 0x0008_0EE4 to<br>0x0008_0EEF | 96 bits<br>(12 bytes)  | Manufacturer ID           |

| 0x0008_0EE0 to<br>0x0008_0EE3 | 32 bits<br>(4 bytes)   | Revision number of kernel |

#### **BOOT KERNEL OVERVIEW**

The boot kernel switches to the user application after performing certain checks (including the CRC integrity of the user application), or the boot kernel enters UART downloader mode to upgrade the user application in flash memory, depending on the SYS\_BMODE0 boot mode pin state at reset.

The boot kernel supports in field updates to the user application through the UART port. For security reasons, the boot kernel itself does not provide the flash programming feature. However, it allows the firmware update code, which has flash driver code for updating the user flash, to be downloaded to the device over the UART port. This code is referred to as a second stage loader (SSL) and is run from SRAM. The SSL must be authenticated before it can be provided run access. The security scheme implemented is discussed in the Read Protection Key Hash section and the Key Hash CRC section, describing the critical part of the kernel to provide the secure environment in which the user code can be read and/or write protected, allowing intellectual property security.

The serial download capability allows developers to reprogram the device while it is soldered directly onto the target system, avoiding the need for an external device programmer and removing the need to swap the device out of the system. The serial download feature also enables system upgrades to be performed in the field, provided the hardware infrastructure involving the SYS\_BMODE0 pin and the UART port are implemented on the target board.

#### **Configuring Security Options**

The boot kernel provides the flexibility to configure the security options of the device by allowing the user to program certain keys and parameters in predefined locations in Page 0 of the user flash memory. The kernel provides the user code security and integrity, which depends on the number of user defined parameters in the first page of the user flash memory. Table 5 summarizes the list of keys and parameters, as well as their locations in the user flash memory.

Table 5. List of Keys and Parameters

| Addre | ss Range            | Size                   | Description                                                                                  |  |  |  |  |  |

|-------|---------------------|------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | 0_0180 to<br>0_018F | 128 bits<br>(16 bytes) | Read protection key hash                                                                     |  |  |  |  |  |

|       | 0_0190 to<br>0_0193 | 32 bits<br>(4 bytes)   | CRC of read protection key hash                                                              |  |  |  |  |  |

|       | 0_0194 to<br>0_0197 | 32 bits<br>(4 bytes)   | Length of user boot loader or<br>entire user code (used for CRC<br>verification before boot) |  |  |  |  |  |

|       | 0_0198 to<br>0_019B | 32-bit<br>word         | In circuit write protection if set to no write (NOWR)                                        |  |  |  |  |  |

|       | 0_019C to<br>0_019F | 32-bit<br>word         | CPU write protection of individual flash blocks                                              |  |  |  |  |  |

## **UG-1160**

#### **Read Protection Key Hash**

Program the 128-bit read protection key hash at Address 0x00000180 in the first page of the user flash memory. The value of this hash depends on the kind of security desired in the system, because this security defines the read accessibility to the device. The key hash defines the state of the serial wire debugger (SWD), as well as the access permission of the SSL downloaded for upgrades via the UART.

The reset state of the flash memory of all logic high memory cells (along with a valid key hash CRC) indicates that the user does not desire read protection. In this case, the SWD interface is automatically enabled during booting.

Any nonreset value results in the SWD being locked. Therefore, there is no SWD access to the device.

The key hash is the 128-bit, truncated secure hash algorithm (SHA-256) of the user key (which is 128 bits in length), which can be sent along with the SSL during the UART download phase. If the user key is valid, and the hash of the received key matches the key hash stored, the SSL runs with all permissions. If the user key fails the key hash check, the SSL only has write permission to the user flash.

#### **Key Hash CRC**

The key hash has a 32-bit CRC checksum stored at Address 0x00000190. The key hash is valid only if the associated 4-byte checksum is valid. The key hash has a separate key hash to protect it against flash tempering attacks. The user must ensure a valid CRC for the key hash is stored along with the key hash itself.

#### In Circuit Write Protect Key

The 32-bit in circuit write protect key at Address 0x00000198 of the user flash memory prevents in circuit programming of the device. To disable in circuit reprogramming, program the hexadecimal value of the NoWr ASCII string (without the terminating null character) to this address. In this case, SWD access to the device is locked, and the only way to update the device code is via the UART downloader.

Use in circuit write protection along with read protection (providing both read and write protection). In circuit write protection alone does not have any significance.

#### **Write Protection**

Pages can be locked to prevent code from accidentally erasing and reprogramming critical flash memory blocks (such as the user code boot loader). There is a hardware register in the flash controller that disables the programming of pages grouped into blocks. This register is not automatically loaded via the hardware. Rather, this register is written to via the kernel. The kernel reads the write protection word from the user flash address, Address 0x0000019C, and writes it to the write protection register in the flash controller. The user can write the appropriate word to this location, depending on the pages intended to be protected against accidental writes. The pages are protected in groups of

four, with each bit in the 32-bit word corresponding to four continuous flash pages. Refer to the ADuCM4050 Ultra Low Power ARM Cortex-M4F MCU with Integrated Power Management Hardware Reference Manual for details.

#### **User Code Length**

There is a 32-bit value stored at a flash memory address, Address 0x00000194, that defines the CRC protected user code length. The value programmed in this field defines the page number of the user flash memory up to which the CRC protection is desired by the user. The value of N means that CRC protection is desired from Page 0 to Page N of the flash memory, protecting a total of N + 1 pages.

Valid values for the field in Address 0x00000194 are 0 to 255 for the 512 kB ADuCM4050 processor. Any value outside this range is treated as invalid and results in a CRC check failure.

#### User Code CRC

The user code CRC is stored at the end of Page N. The 32-bit CRC (MSB first) with a polynomial of 0x4C11DB7 is expected by the kernel. If the page number is N, the CRC is expected to reside at flash memory address  $(N \times 0x800) + 0x7FC$ . For example, if N = 5, a total of six pages are CRC protected, and the CRC is stored at Address 0x2FFC. There is an option to disable the CRC check by programming 0xFFFFFFFFF to the expected CRC location. After the kernel sees this value in the CRC location, it skips the CRC check.

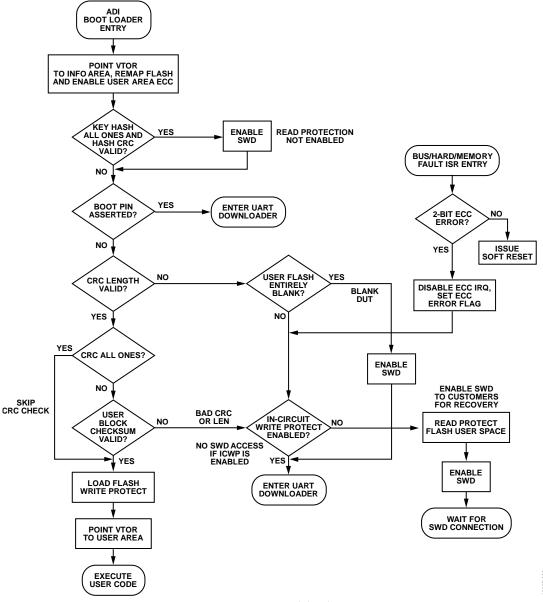

#### **Boot Code Flow**

This section describes how the kernel operates, based on the user programmable parameters described in the Read Protection Key Hash section through the User Code CRC section. Figure 27 shows a flowchart of the boot code.

After reset, the boot kernel inspects all the parameters stored in Page 0 of the user flash memory. The user has not requested the read protection if the user read protection key hash is not programmed (meaning that it is set to all FFs) and the key hash CRC is valid. As such, the SWD is enabled. However, flash access may be protected, depending on the state of the user code CRC.

If the CRC is valid, access to user flash memory is unrestricted.

If the user disables the CRC by programming 0xFFFFFFFF to the CRC location, access to the user flash memory is also unrestricted.

If the CRC is invalid, the user flash memory is protected with no read or write access allowed. Only the flash mass erase command is allowed. In this case, user code execution is not allowed.

Take care to program a valid CRC (or 0xFFFFFFFF) in the defined CRC location. Otherwise, the user flash memory is read protected by the kernel. In this case, flash-based applications fail to load unless the user flash memory is mass erased.

If the user read protection key hash is programmed with a nonreset value, meaning that the read protection is enabled, or if the key

ADuCM4050 User Guide UG-1160

hash CRC is invalid, the SWD is disabled by the kernel and SWD access to the device is not possible. Perform this programming only after product development is complete and SWD access is not intended in the field. However, when read protection is enabled, the SWD is opened only if CRC protection is enabled and the CRC is corrupted, which allows device recovery when the CRC is accidentally corrupted. In this case, the SWD opens, but the user flash memory is protected with no read, write, or page erase accessibility (to maintain the user code confidentiality while allowing device recovery). However, mass erase is still possible, which results in the user flash memory being open again (with read and write access).

The user flash memory (user space) is completely blank when shipped. Therefore, none of the security keys and parameters are programmed. Most of the parameters, such as the key hash CRC and the user code length, have invalid values, meaning the parameters are all set to 0xFF. In this case, the kernel performs a check of the user flash memory to identify if it is blank or completely unprogrammed. If the user flash is blank, the kernel

skips all the checks and opens the SWD. In addition to opening the SWD, which allows users to connect to the device through SWD for their development, the boot kernel also enters the UART downloader mode and awaits reception of the SSL.

After the device is programmed via the SWD, the user flash memory is no longer blank, and the kernel relies on the state of the SYS\_BMODE0 pin to decide if the user code must be executed after performing all the checks explained in the Boot Code Flow section, or if the boot kernel must enter the UART downloader mode.

If the SYS\_BMODE0 pin is asserted low, the kernel enters the UART downloader and waits for the SSL to download.

If the SYS\_BMODE0 pin is deasserted high, the kernel jumps to the user reset vector in the user flash memory after performing all security checks.

The only case where the kernel enters the UART download mode without sampling the SYS\_BMODE0 pin is when the user flash memory is blank.

Figure 27. Boot Kernel Flowchart

SSL code downloaded over the UART must be mapped to the SRAM. In UART downloader mode, the SSL is loaded to the SRAM and has flash programming capabilities. The kernel authenticates the SSL and allows execution only if authentication is successful. This code is responsible for downloading and upgrading the actual firmware (for example, the user application) in the user flash memory. The kernel does not support direct updates to the user flash memory. Therefore, the SSL is required to perform such actions.

The kernel follows a specific protocol to download the SSL to the processor, which must be adhered to by the transmitting host. If the SSL follows the same packet protocol as the kernel, the host interface is simplified (for example, communication with the kernel and the SSL is uniform). The details of the protocol are discussed in the Protocol section.

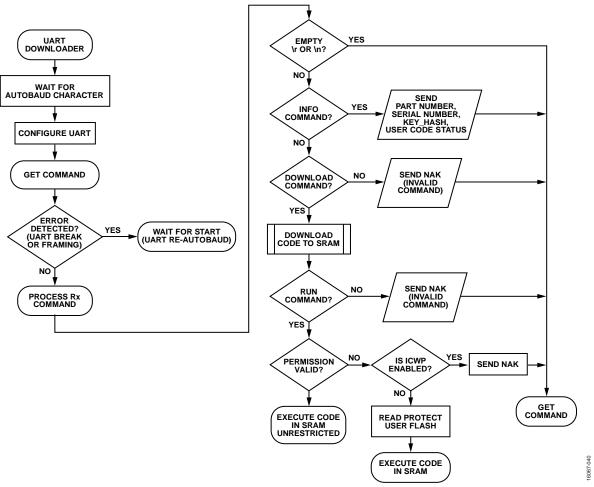

#### **UART DOWNLOADER**

The ADuCM4050 processors enter UART downloader mode if the SYS\_BMODE0 pin (GPIO17) is pulled low. If this condition is detected by the device at power-on or hard reset, the device enters serial download mode. In this mode, an on-chip loader routine in the kernel is initiated, which configures the UART port of the device and, via a specific serial download protocol, communicates with a host to manage the firmware upgrade process. Figure 28 shows the UART downloader flow.

ADuCM4050 User Guide UG-1160

Figure 28. UART Downloader Flowchart

## **UG-1160**

#### **Protocol**

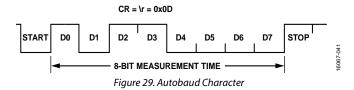

After the serial downloader is triggered by asserting the SYS\_BMODE0 pin, the kernel waits for the host to send a carriage return character (ASCII 0x0D, as shown in Figure 29) to initiate the UART autobaud process.

The kernel makes use of the UART autobaud feature to detect the baud rate of the host and to subsequently configure the UART port to transmit or receive, at the baud rate of the host, with eight data bits and no parity. Due to the 6.5 MHz reset peripheral clock (PCLK), the UART can be configured by the kernel to support baud rates up to 230,400 bps. Baud rates greater than this value contain more errors and may result in an unreliable data transfer. However, after loading the SSL, higher baud rates are possible if the SSL increases the PCLK (up to 52 MHz) and performs a second autobaud detection via the UART.

After receiving the autobaud character, the kernel calculates the required clock divisor values and configures the UART, at which point the kernel sends the device information as part of a 57-byte ID data packet, as shown in Figure 29, to acknowledge that the autobaud detection process is successful.

#### **Packet Structure**

In addition to indicating to the host that the processor is now ready to communicate, the autobaud acknowledgement also contains information about the device, the state of the user flash memory, and security restrictions. After the autobaud acknowledgement, the data transfer itself can begin, as governed by the communications data transport packet format shown in Table 16.

#### Packet Start ID Field, ID0 and ID1

The first transfer field is the 2-byte packet start ID field (ID0 and ID1), comprised of two start characters (0x07 for ID0 and 0x0E for ID1). These bytes are constant and are used by the loader to detect the beginning of a valid data packet.

#### Number of Data Bytes Field

The next transfer field is the total number of data bytes field, which includes the 1-byte command (CMD), the 4-byte address (value), and the remaining payload (data). The minimum number of data bytes is five, which corresponds to a command and address only. The maximum number of data bytes is 255, supporting a command, an address, and up to 250 bytes of data.

#### Command Function Field (CMD), Data Byte 1

The command function field describes the function of the data packet. Three commands are supported by the kernel, represented in ASCII format:

- W (0x57)—write command

- R (0x52)—run command

- I (0x45)—information command

Table 6. Autobaud Response

| 1 4010 011 | Tutobudu Neopolise                                                                                                             |

|------------|--------------------------------------------------------------------------------------------------------------------------------|

| Bytes      | Contents                                                                                                                       |

| 1 to 15    | Product identifier: ADuCM4050 and six spaces                                                                                   |

| 16 to 18   | Hardware and firmware version numbers                                                                                          |

| 19         | User code blank; x means the code to execute, and a dash (-) means the user code is blank                                      |

| 20         | User code checksum; P means that the checksum passed, and F means that the checksum failed                                     |

| 21         | Write protection enabled; W means that write protection is disabled, and a dash (-) means that the write protection is enabled |

| 22         | Read protection enabled; R means that read protection is disabled, and a dash (-) means that read protection is enabled        |

| 23         | Space                                                                                                                          |

| 24 to 55   | 128-bit serial number, as a 32-digit uppercase hexadecimal number (for example, 0123456789ABCDEF0123456789ABCDEF)              |

| 56         | Line feed                                                                                                                      |

| 57         | Carriage return                                                                                                                |

**Table 7. UART Packet Structure**

| ID0  | ID1  | Number of Data Bytes | CMD        | Value      | Data | Checksum |

|------|------|----------------------|------------|------------|------|----------|

| 0x07 | 0x0E | 5 to 255             | W, R, or I | h, u, m, l | XX   | CS       |

#### Write Command

The write command packet shown in Table 8 includes the number of data bytes (5 + n), where n is the payload size in bytes), the write command (W), the 32-bit start address to write to, and the n data bytes in the payload.

When a write command packet is received by the kernel, the payload bytes are placed sequentially in the SRAM as they arrive, beginning at the start address. The kernel sends a no acknowledge command if the checksum is incorrect or if the received address is out of range. If the host receives a no acknowledge from the loader, abort and restart the download process.

#### **Run Command**

After the host transmits all the data packets to the kernel, it can send a final packet instructing the kernel to start executing code.

This final packet is achieved by sending the run command packet, which is comprised of the run command (R) and the 32-bit address to begin running from, as shown in Table 9.

When the kernel receives a run command packet, it jumps to the address supplied in the packet only after the permission checks pass.

#### **Information Command**

The host can send the information command packet shown in Table 10 at any time. This packet is comprised of the command (I) and a 32-bit address. Though the value field is required for the packet to be properly received by the kernel, the content of the value field is irrelevant.

When the kernel receives the information command packet, it responds with the 57-byte ID packet (see Table 6).

**Table 8. Write Command Packet**

| ID0  | ID1  | Number of Data Bytes | CMD      | Value         | Data    | Checksum |

|------|------|----------------------|----------|---------------|---------|----------|

| 0x07 | 0x0E | 5 + n                | W (0x57) | Start address | n bytes | CS       |

#### **Table 9. Run Command Packet**

| ID0  | ID1  | Number of Data Bytes | CMD      | Value         | Checksum |

|------|------|----------------------|----------|---------------|----------|

| 0x07 | 0x0E | 5                    | R (0x52) | Start address | CS       |

#### **Table 10. Information Command Packet**

| ID0  | ID1  | Number of Data Bytes | CMD      | Value     | Checksum |

|------|------|----------------------|----------|-----------|----------|

| 0x07 | 0x0E | 5                    | I (0x52) | 0xXXXXXXX | CS       |

## **UG-1160**

#### Value Field (Data Byte 2 to Data Byte 5)

The value field contains a 32-bit address that includes h, u, m, and locations. The MSB is in the h location (Data Byte 2), and the LSB is in the l location (Data Byte 5).

The significance of the packets associated are as follows:

- In a write command packet, the value field indicates the start address in memory to which the data payload is written.

- In a run command packet, the value field indicates the address in SRAM where the SSL code begins.

- In an information command packet, the value field has no meaning.

#### Data Field (Data Byte 6 to Data Byte 255)

User code is downloaded one byte at a time, and the data field can contain a maximum of 250 bytes. The data is normally stripped out of the Intel\* HEX extended 16-byte record format, reassembled by the host, and then sent in packet form using a series of write command packets to the ADuCM4050 processor.

#### Checksum Field (CS)

The data packet checksum is written to the checksum field. This twos complement checksum is calculated from the summation of the hexadecimal values that span the number of bytes field to the end of the data field. Thus, the 8-bit LSB of the sum of all the bytes in the packet from the number of data bytes field, up to and including the checksum field, is 0.

#### Acknowledge of Command

The loader routine issues a no acknowledge command (0x07) as a negative response, or an acknowledge command (0x06) as a positive response to each data packet received.

The loader transmits a no acknowledge if it meets any of following conditions:

- The loader receives an incorrect checksum.

- A UART framing or break error occurs (this error may not reach the host if the UART link is invalid).

- The SRAM code verification fails.

If any one of these conditions is met, it is required to reset the target and restart the firmware upgrade process. If none of these conditions are met, an acknowledge command is transmitted.

#### **READ PROTECTION KEY AND HASHING**

The read protection key allows access to the device during failure analysis. If the device is read protected and failure analysis of the current flash memory content is necessary, enable the SWD interface by sending the key corresponding to the hash stored in the user flash memory. It is recommended that the key be unique to the device and be based on the unique identifier of the device (for example, the serial number stored in the information space).

A hash is stored in the user flash memory after the interrupt vectors. This is the hash of a secret customer key. It is strongly recommended that this key be unique to the device for security reasons, and that the unlock key is valid for that one specific device. To maintain a unique key per device, there must be a device identifier to associate which key belongs to a particular device. For simple key management, it is advised to make the key a hash of a master secret and the device identifier.

Read Protection Key = Hash (Master Secret || Unique Device Identifier)

*Key Hash* = *Hash* (*Read Protection Key*)

When the kernel is in UART loader mode, it can accept the read protection key. Then, the boot loader performs a hash of the read protection key and compares it to the stored key hash. On a successful match, the bootloader permits the downloaded SSL code in the SRAM to be executed with all the permissions enabled. If the key hash check fails, then the kernel checks the ICWP key in the user flash memory. If ICWP is turned off by the user by programming any value to Address 0x00000198 other than the hexadecimal equivalent of the NoWr ASCII string, then the SSL is allowed to run after protecting the flash against read and write accesses. In this case, the SSL must first issue a mass erase of the user flash memory before attempting to perform any access to the user flash memory space. If ICWP is also enabled by the user, then the SSL is not granted permission to run unless the key hash authentication passes.

The 128-bit read protection key is passed as a part of the SRAM code. This key must be stored in big endian format in the SRAM as a data payload starting at Address 0x20000180 and must be oriented is a specific fashion in the memory for the kernel to parse it correctly. Specifically, if the read protection key is represented as ABCDEFGHIJKLMNOP, where each letter represents one byte (with A being the first byte and P being the last byte), the required arrangement of the bytes in memory is shown in Table 11.

Table 11. Read Protection in SRAM

| _ *** * - * - * * * * - * * * - * - |        |        |        |        |  |  |  |

|-------------------------------------|--------|--------|--------|--------|--|--|--|

| Address                             | Byte 0 | Byte 1 | Byte 2 | Byte 3 |  |  |  |

| 0x20000180                          | D      | C      | В      | A      |  |  |  |

| 0x20000184                          | Н      | G      | F      | E      |  |  |  |

| 0x20000188                          | L      | K      | J      | 1      |  |  |  |

| 0x2000018C                          | Р      | 0      | N      | М      |  |  |  |

For example, if the read protection key is 0x00010203040506070-8090A0B0C0D0E0F, then Table 12 shows how the memory must be written.

**Table 12. Example Read Protection Key in SRAM**

| Address    | Byte 0 | Byte 1 | Byte 2 | Byte 3 |  |  |  |

|------------|--------|--------|--------|--------|--|--|--|

| 0x20000180 | 0x03   | 0x02   | 0x01   | 0x00   |  |  |  |

| 0x20000184 | 0x07   | 0x06   | 0x05   | 0x04   |  |  |  |

| 0x20000188 | 0x0B   | 0x0A   | 0x09   | 0x08   |  |  |  |

| 0x2000018C | 0x0F   | 0x0E   | 0x0D   | 0x0C   |  |  |  |

ADuCM4050 User Guide UG-1160

The kernel computes the SHA-256 hash of this key, truncates it to a 128-bit hash, and then compares it to the hash stored in Page 0 of the user flash memory at Address 0x00000180. The user must store the 128-bit truncated hash of the key to the flash memory using a similar pattern. The SHA-256 hash for the example key shown in Table 12 is 0xBE45CB2605BF36BEBDE68-4841A28F0FD43C69850A3DCE5FEDBA69928EE3A8991, which means the 128-bit truncated hash that must be stored properly to the user flash memory space is 0x43C69850A3DCE-5FEDBA69928EE3A8991, arranged as shown in Table 13.

Table 13. Example Read Protection Key Hash in Flash Memory

| Address    | Byte 0 | Byte 1 | Byte 2 | Byte 3 |

|------------|--------|--------|--------|--------|

| 0x00000180 | 0x50   | 0x98   | 0xC6   | 0x00   |

| 0x00000184 | 0xFE   | 0xE5   | 0xDC   | 0xA3   |

| 0x00000188 | 0x28   | 0x99   | 0xA6   | 0xDB   |

| 0x0000018C | 0x91   | 0x89   | 0x3A   | 0xEE   |

The CRC32 of the key hash is calculated with a polynomial of 0x04C11DB7 and a seed value of 0xFFFFFFFF, and it is stored in LSB format in the flash memory space at Address 0x000000190.

#### **MEMORY CONFIGURATION**

Table 14 summarizes the different keys and parameters stored in Page 0 of the user flash memory, the associated addresses, and the values programmed to Page 0 when creating a project with the default start-up file.

Table 14. Page 0 Memory Configuration

|                                  | Address Range |             |              |                            |                                                                   |  |

|----------------------------------|---------------|-------------|--------------|----------------------------|-------------------------------------------------------------------|--|

| Content                          | Start Address | End Address | Size (Bytes) | Section Name               | <b>Default Content</b>                                            |  |

| Vector Table                     | 0x0000_0000   | 0x0000_017F | 384          | .intvec                    | Vector table                                                      |  |

| Read Protection Key Hash         | 0x0000_0180   | 0x0000_018F | 16           | ReadProtection KeyHash     | 0xFFFFFFF                                                         |  |

|                                  |               |             |              |                            | 0xFFFFFFF                                                         |  |

|                                  |               |             |              |                            | 0xFFFFFFF                                                         |  |

|                                  |               |             |              |                            | 0xFFFFFFF                                                         |  |

| CRC of Read Protection Key       | 0x0000_0190   | 0x0000_0193 | 4            | CRC_ReadProtection KeyHash | 0xA79C3203                                                        |  |

| Number of Pages the CRC Computes | 0x0000_0194   | 0x0000_0197 | 4            | NumCRCPages                | 0                                                                 |  |

| Checksum                         | 0x0000_07FC   | 0x0000_07FF | 4            | Checksum                   | Checksum of 0 to<br>0x7FB (if enabled<br>in tools by the<br>user) |  |

| Page 0 User Memory               | 0x0000_01A0   | 0x0000_07FC | 1628         | Page0_region               | User application                                                  |  |

#### HANDLING CRC IN THE IAR WORKBENCH

Calculate the CRC from part of the application image to be loaded into the first several pages of the flash memory. Store the page number of the last page involved in the CRC calculation at Address 0x194 as a 32-bit integer. For example, if only Page 0 is involved in the CRC calculation, store the value of 0x00 at Address 0x194. If the CRC is calculated for the first three pages, the value must be 0x02.

When the CRC is calculated, the last four bytes of the last page included in the CRC calculation are excluded. These four bytes are used for storing the CRC value itself. For example, if the last page is Page 0, the CRC is calculated from Address 0x000 up to and including Address 0x7FB. The tool stores the calculated CRC value at Address 0x7FC as a 32-bit integer.

The standard CRC calculation is CRC32 with a polynomial of 0x04C11DB7, stored in MSB first format, with an initial value of 0xFFFFFFFF. The unit size is 32 bits, which means the tool must read 32 bits at one time from the image when calculating the CRC.

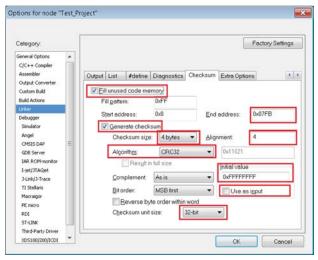

#### **Checksum Tab**

There is a **Checksum** tab under the **Linker** category in the IAR tools, which generates the CRC of the user application code. To store the correct CRC, the following settings must be used (see Figure 30):

- Check the **Fill unused code memory** box.

- Set the **End address:** field to 0x7FB (this value changes depending on the page number).

- Check the **Generate checksum** box.

- Select the 4 bytes option from the Checksum size: pulldown menu

- Set the **Alignment:** field to 4 (which indicates 4 bytes).

- Select the CRC32 option from the Algorithm: pull-down menu.

- Set the **Initial value** field to 0xFFFFFFF and ensure the **Use as input** box is not checked.

- Select the **32-bit** option from the **Checksum unit size**: pull-down menu.

Figure 30. Checksum Settings

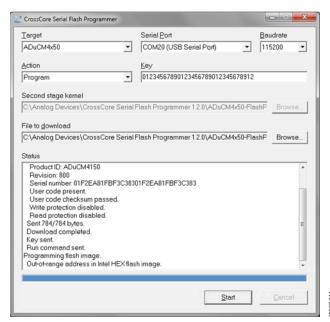

#### **CROSSCORE SERIAL FLASH PROGRAMMER**

The CrossCore\* Serial Flash Programmer (CCSFP) is a PC-based host utility, provided by Analog Devices that upgrades the user code over the UART port. CCSFP provides a graphical user interface (GUI) to provide the following options for the UART upgrade:

- Target processor

- UART PC port number

- Baud rate

- SSL hexadecimal file to be used for the upgrade

- User application hexadecimal file to be upgraded

- Key to authenticate the SSL

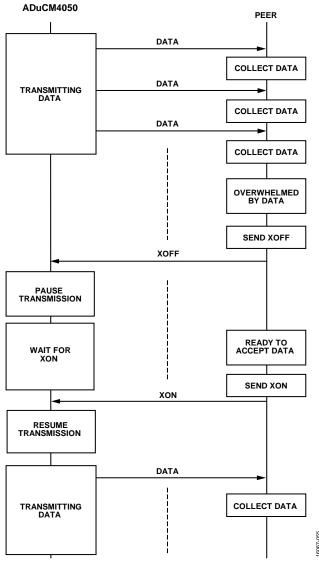

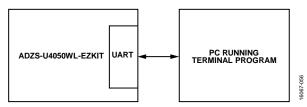

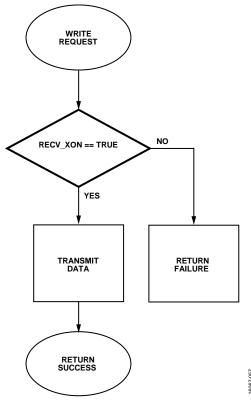

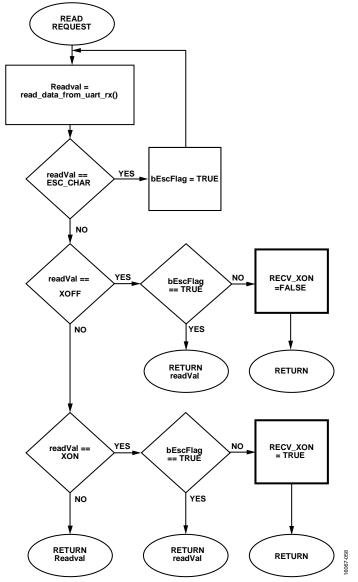

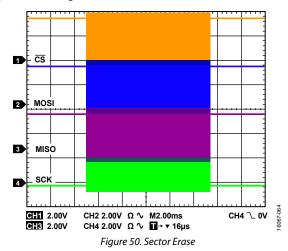

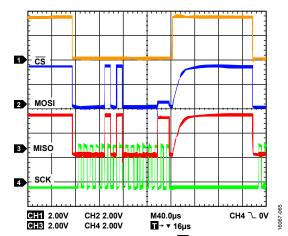

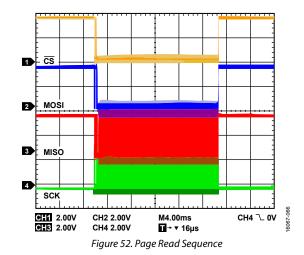

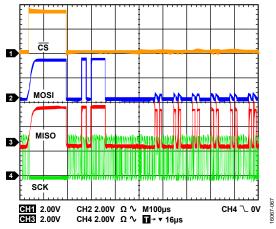

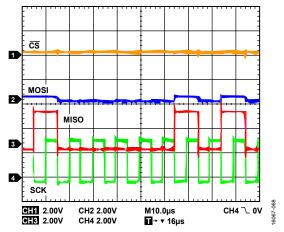

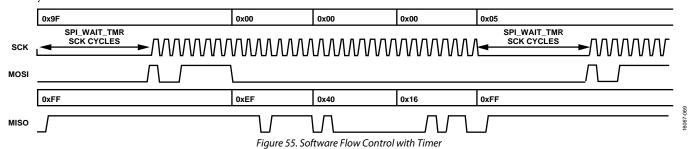

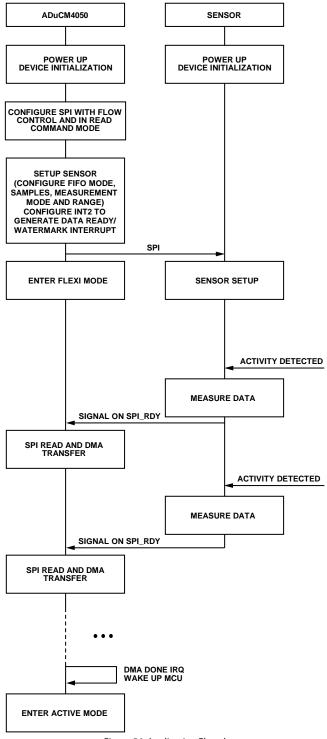

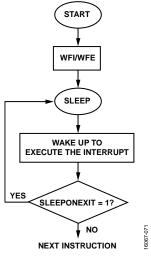

ADuCM4050 User Guide UG-1160