# I<sup>2</sup>C Quick Guide

## I<sup>2</sup>C Standard

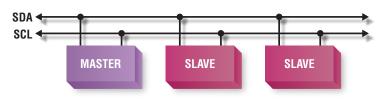

The  $I^2C$  (inter-IC) bus is a 2-wire, multi-drop, digital communications link for ICs that has become the defacto standard for many embedded applications. Serial, 8-bit, bidirectional data transfer can occur at speeds up to 3.4Mbps, though 400kHz is usually sufficient. Since only two bus lines are required, a serial data line (SDA) and serial clock line (SCL), building a system with multiple master or slave devices is relatively simple. The number of  $I^2C$  devices that can be connected to a single  $I^2C$  bus segment is limited only by a maximum bus capacitance (400pF) and address space.

### I<sup>2</sup>C vs SMBus vs PMBus

| Specification |                                                  |                                   | SMBus                           |           |                                |  |

|---------------|--------------------------------------------------|-----------------------------------|---------------------------------|-----------|--------------------------------|--|

|               |                                                  | I <sup>2</sup> C                  | High Power                      | Low Power | PMBus                          |  |

|               | Packet Error Checking (Optional)                 | -                                 | •                               |           |                                |  |

| Signaling     | SMBALERT (Optional)                              | _                                 | •                               |           |                                |  |

|               | Block Size Limit                                 | -                                 | 32 bytes 255 bytes              |           |                                |  |

| Timing        | Data Rate (Standard Mode)                        |                                   | 100kbps                         |           |                                |  |

|               | Data Rate (Fast Mode)                            | 400kbps                           | -                               | _         | 400kbps                        |  |

|               | Data Rate (Fast Mode Plus)                       | 1Mbps                             | -                               | _         | -                              |  |

|               | Data Rate (High Speed Mode)                      | 3.4Mbps                           | -                               | -         | -                              |  |

|               | Clock Speed                                      | 0Hz to 3.4MHz                     | 10kHz to 100kHz 10kHz to 400kHz |           |                                |  |

|               | Bus Timeout                                      | -                                 | 25ms to 35ms                    |           |                                |  |

|               | Bus Master Request Delay (Min)                   | -                                 | 50µs                            |           |                                |  |

|               | SCL Hold Time (Max)                              | -                                 | 2ms                             |           |                                |  |

|               | Data Hold Time (Min)                             | -                                 | 300ns                           |           |                                |  |

| Electrical    | Capacitance Load per Bus Segment (Max)           | 400pF                             |                                 | _         | 400pF                          |  |

|               | Rise Time (Max)                                  | 1µs at 100kHz, 300ns at 400kHz    | 1µs                             |           | 1µs at 100kHz, 300ns at 400kHz |  |

|               | Pull-Up Current at 0.4V (Max)                    | 3mA (Standard Mode and Fast Mode) | 4mA                             | 350μΑ     | 4mA                            |  |

|               | Leakage Current per Device (Max)                 | ±10µA                             | ±5µA                            |           | ±10μA                          |  |

|               | V <sub>IL</sub> Input Logic Low Threshold (Max)  | 0.3V <sub>DD</sub> or 1.5V        | 0.8V                            |           |                                |  |

|               | V <sub>IH</sub> Input Logic High Threshold (Min) | 0.7V <sub>DD</sub> or 3V          | 2.1V                            |           |                                |  |

|               | V <sub>OL</sub> Output Logic Low Threshold (Max) |                                   | 0.4V                            |           |                                |  |

### Frequently Asked Questions

#### Q1) How are I<sup>2</sup>C, SMBus and PMBus related?

Answer: Originally developed to facilitate battery management systems, SMBus uses I<sup>2</sup>C hardware but adds second-level software, which ultimately allows devices to be hot swapped without restarting the system. PMBus extends SMBus by defining a set of device commands specifically designed to manage power converters, exposing device attributes such as measured voltage, current, temperature and more. In general, I<sup>2</sup>C, SMBus and PMBus devices can share a bus without any major issues.

#### Q2) How do I build a large system and still meet bus capacitance and rise time specifications?

Answer: Linear Technology's bus buffers resolve common electrical limitations posed by specifications, thereby allowing more devices to be added to the bus. These devices break up large busses into several smaller I<sup>2</sup>C compliant (<400pF) pieces, while still providing simultaneous communications to all bus segments and optionally injecting a boosted pull-up current during positive bus transitions to quickly slew large bus capacitances.

#### Q3) How do I resolve a stuck bus?

Answer: Other than having a host try to manually fix a bus stuck low, Linear Technology's bus buffers provide stuck bus protection which recovers a stuck bus by automatically generating pulses on SCLOUT in an attempt to unstick the bus. Otherwise, a hard reset is required.

#### Q4) How do I increase the number of I<sup>2</sup>C addresses available?

Answer: Linear Technology's address translators and software or hardware controlled I<sup>2</sup>C multiplexers provide the ability to address one of multiple identical devices or simply increase fan-out, thus resolving address conflict issues, while also providing Hot Swap capabilities, bus buffering, rise time acceleration and stuck bus protection.

Linear Technology provides a comprehensive family of I<sup>2</sup>C-enabled devices for a variety of applications. From Hot Swap controllers to bus isolators, these devices provide on-the-fly adjustability, enhance I<sup>2</sup>C performance or simply enable designers to easily manage key system parameters.

#### Hot Swap Controller

- Control inrush current on a live backplane, while monitoring current, voltage, power and energy

- Record past and present fault conditions and configure latchoff or auto-restart

## Power Supply/LED Driver

Control power-on/-off or dimming and configure mode of operation, output voltage, sequencing and slew rate for single- or multi-topology converters

## Power System Management Controller

- Control, monitor, supervise, sequence and margin multiple power supplies

- Access EEPROM for user configuration, fault logging and telemetry

## Power/Energy Monitor

Monitor current, voltage, average power, charge and energy, while minimizing software polling with min/max registers and configurable alerts

#### **Temperature Monitor**

- Measure combinations of voltage, current and internal or external temperature

- Trigger single or repeated measurements and change formats (Celsius or Kelvin)

I<sup>2</sup>C

Bus

## Bus Buffer/Multiplexer/Address Translator/Rise Time Accelerator

Break up bus capacitance, increase fan-out, level shift busses, decrease rise times and nest addresses while providing Hot Swap capabilities and stuck bus protection

#### Bus Isolator

Break ground loops and isolate logic level interfaces, while also providing Hot Swap capabilities or adjustable isolated power to neighboring components

#### Power over Ethernet Power Sourcing Equipment (PSE)

• Efficiently source up to 90W of power, while configuring PSE mode of operation and monitoring per port status, current, MOSFET health and die temperature

## Battery Charger/Gas Gauge

Adjust charge current, float voltage and charge termination, while monitoring status, charge, current, voltage or temperature of battery, USB or wall sources

#### ADC/DAC

Write to or read from data converters with no latency, and select input or output data formats and use of internal or external reference

#### Silicon Oscillator

Enable and program clock frequency with 0.1% resolution, as well as instantaneously change octaves using DACs with 10-bit monotonicity and less than 1% nonlinearity