# **Data Sheet**

# HMC7043

# High Performance, 3.2 GHz, 14-Output Clock Distributor with JESD204B/C Support

# **FEATURES**

- ▶ JEDEC JESD204B and JESD204C support

- ▶ Low additive jitter: <15 fs rms at 2457.6 MHz (12 kHz to 20 MHz)

- ▶ Very low noise floor: -155.2 dBc/Hz at 983.04 MHz

- ▶ Up to 14 LVDS, LVPECL, or CML type device clocks (DCLKs)

- Maximum CLKOUTx/CLKOUTx and SCLKOUTx/SCLKOUTx frequency of 3200 MHz

- JESD204B and JESD204C compatible system reference (SYSREF) pulses

- 25 ps analog and ½ clock input cycle digital delay independently programmable on each of 14 clock output channels

- ▶ SPI-programmable adjustable noise floor vs. power consumption

- ► SYSREF valid interrupt to simplify JESD204B synchronization

- Supports deterministic synchronization of multiple HMC7043 devices

- RFSYNCIN pin or SPI-controlled SYNC trigger for output synchronization of JESD204B/C

- ▶ GPIO alarm/status indicator to determine system health

- Clock input to support up to 6 GHz

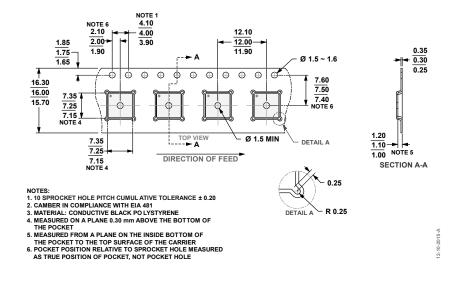

- ▶ 48-lead, 7 mm × 7 mm LFCSP package

## **APPLICATIONS**

- ▶ JESD204B and JESD204C clock generation

- Cellular infrastructure (multicarrier GSM, LTE, W-CDMA)

- Data converter clocking

- Phase array reference distribution

- Microwave baseband cards

## **GENERAL DESCRIPTION**

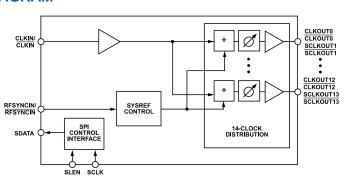

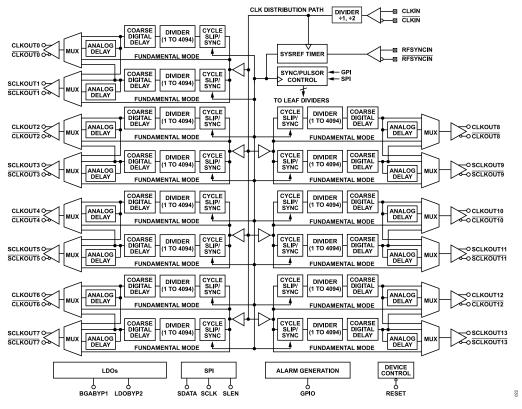

The HMC7043 is a high performance clock buffer for the distribution of ultralow phase noise references for high speed data converters with either parallel or serial (JESD204B/C types) interfaces. **FUNCTIONAL BLOCK DIAGRAM**  The HMC7043 is designed to meet the requirements of multicarrier GSM and LTE base station designs, and offers a wide range of clock management and distribution features to simplify baseband and radio card clock tree designs.

The HMC7043 provides 14 low noise and configurable outputs to offer flexibility in interfacing with many different components in a base transceiver station (BTS) system, such as data converters, local oscillators, transmit/receive modules, field programmable gate arrays (FPGAs), and digital front-end ASICs. The HMC7043 can generate up to seven DCLK and SYSREF clock pairs per the JESD204B/C interface requirements.

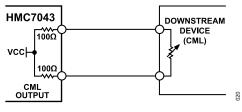

The system designer can generate a lower number of DCLK and SYSREF pairs, and configure the remaining output signal paths for independent phase and frequency. Both the DCLK and SYSREF clock outputs can be configured to support different signaling standards, including CML, LVDS, LVPECL, and LVCMOS, and different bias conditions to adjust for varying board insertion losses.

One of the unique features of the HMC7043 is the independent flexible phase management of each of the 14 channels. All 14 channels feature both frequency and phase adjustment. The outputs can also be programmed for 50  $\Omega$  or 100  $\Omega$  internal and external termination options.

The HMC7043 device features an RF SYNC feature that synchronizes multiple HMC7043 devices deterministically, that is, ensures that all clock outputs start with the same edge. This operation is achieved by rephasing the nested HMC7043 or SYSREF control unit/divider, deterministically, and then restarting the output dividers with this new phase.

The HMC7043 is offered in a 48-lead, 7 mm × 7 mm LFCSP package with an exposed pad connected to ground.

Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                    | 1    |

|---------------------------------------------|------|

| Applications                                | 1    |

| General Description                         | 1    |

| Functional Block Diagram                    | 1    |

| Specifications                              | 4    |

| Conditions                                  | 4    |

| Supply Current                              | 4    |

| Digital Input/Output (I/O) Electrical       |      |

| Specifications                              | 5    |

| Input Path Specifications                   | 5    |

| Additive Jitter and Phase Noise             |      |

| Characteristics                             | 6    |

| Clock Output Distribution Specifications    | 6    |

| Clock Output Driver Characteristics         | 7    |

| Absolute Maximum Ratings                    | 9    |

| Thermal Resistance                          | 9    |

| ESD Caution                                 | 9    |

| Pin Configuration and Function Descriptions | . 10 |

| Typical Performance Characteristics         | . 12 |

| Typical Application Circuits                | .14  |

| Terminology                            | 15 |

|----------------------------------------|----|

| Theory of Operation                    | 16 |

| Detailed Block Diagram                 |    |

| Clock Input Network                    | 17 |

| Clock Output Network                   | 18 |

| Phase Behavior of Synchronized Divided |    |

| Clocks                                 | 24 |

| Typical Programming Sequence           | 24 |

| Power Supply Considerations            | 25 |

| Serial Control Port                    | 28 |

| Serial Port Interface (SPI) Control    | 28 |

| Control Registers                      |    |

| Control Register Map                   | 29 |

| Control Register Map Bit Descriptions  | 34 |

| Applications Information               | 43 |

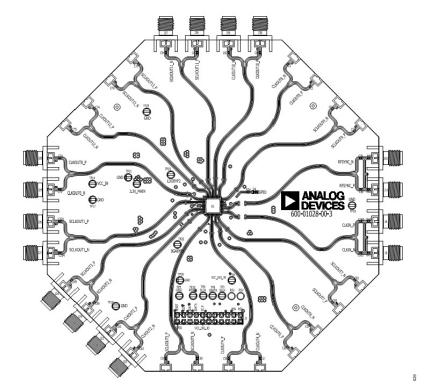

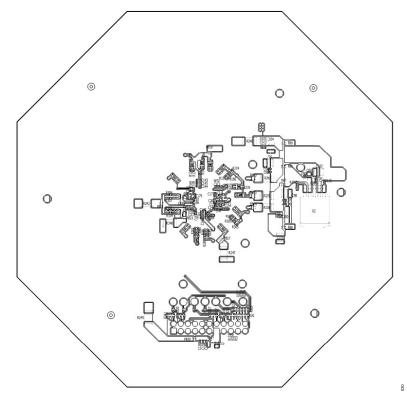

| Evaluation PCB and Schematic           | 43 |

| Outline Dimensions                     | 45 |

| Ordering Guide                         | 45 |

| Lead Finish and MSL Rating Options     | 45 |

| Evaluation Boards                      | 45 |

|                                        |    |

# **REVISION HISTORY**

| 12/2024—Rev. C to Rev. D                                                                        |    |

|-------------------------------------------------------------------------------------------------|----|

| Changes to Table 4                                                                              | 5  |

| Changed Output Behavior with Pulse Generation Request Section to Phase Behavior of Synchronized |    |

| Divided Clocks Section                                                                          | 24 |

| Changes to Phase Behavior of Synchronized Divided Clocks Section                                |    |

| Changes to Typical Read Cycle Section                                                           |    |

| 6/2024—Rev. B to Rev. C                                                                         |    |

| Changes to Data Sheet Title                                                                     | 1  |

| Changed Master to Main and Slave to Node (Throughout)                                           |    |

| Changes to Features Section                                                                     |    |

| Changes to Applications Section                                                                 |    |

| Changes to General Description Section                                                          |    |

| Changed Clock Input Path Specifications Section to Input Path Specifications Section            |    |

| Changes to Table 4                                                                              |    |

| Changes to Clock Output Skew Parameter, Table 6                                                 |    |

| Added Note 2, Table 7                                                                           | 0  |

| Changes to Table 8                                                                              |    |

| Added Thermal Resistance Section and Table 9, Renumbered Sequentially                           |    |

|                                                                                                 |    |

| Changes to Figure 15 and Figure 23                                                              |    |

| Added Figure 18 and Figure 24; Renumbered Sequentially                                          |    |

| Changes to Theory of Operation Section.                                                         |    |

| Changes to Clock Output Network Section                                                         |    |

| Changes to SYSREF Valid Interrupt Section.                                                      |    |

| Added Output Behavior with Pulse Generation Request Section and Figure 31                       |    |

| Changes to Typical Programming Sequence Section                                                 | 24 |

# TABLE OF CONTENTS

| Changes to Table 18 Title                | 25 |

|------------------------------------------|----|

| Changes to Table 19 Title                | 26 |

| Changes to Typical Read Cycle Section    |    |

| Changes to Typical Write Cycle Section   |    |

| Changes to Table 21                      |    |

| Added Note 1 and Note 2, Table 32        | 37 |

| Changes to Table 42                      |    |

| Added Lead Finish and MSL Rating Options |    |

| 5 1                                      | -  |

$V_{CC}$  = 3.3 V ± 5%, and  $T_A$  = 25°C, unless otherwise noted. Minimum and maximum values are given over the full  $V_{CC}$  and  $T_A$  (-40°C to +85°C) variation, as listed in Table 1.

### CONDITIONS

| Table 1.                                  |       |     |       |      |                                                                                                                           |

|-------------------------------------------|-------|-----|-------|------|---------------------------------------------------------------------------------------------------------------------------|

| Parameter <sup>1</sup>                    | Min   | Тур | Max   | Unit | Test Conditions/Comments                                                                                                  |

| SUPPLY VOLTAGE, V <sub>CC</sub>           |       |     |       |      |                                                                                                                           |

| VCC1_CLKDIST                              | 3.135 | 3.3 | 3.465 | V    | 3.3 V ± 5%, supply voltage for CLK distribution                                                                           |

| VCC2_OUT                                  | 3.135 | 3.3 | 3.465 | V    | 3.3 V ± 5%, supply voltage for Output Channel 2 and Output Channel 3                                                      |

| VCC3_OUT                                  | 3.135 | 3.3 | 3.465 | V    | 3.3 V ± 5%, supply voltage for Output Channel 4, Output Channel 5, Output Channel 6, and Output Channel 7                 |

| VCC4_CLKIN                                | 3.135 | 3.3 | 3.465 | V    | 3.3 V ± 5%, supply voltage for the clock input path                                                                       |

| VCC5_SYSREF                               | 3.135 | 3.3 | 3.465 | V    | 3.3 V ± 5%, supply voltage for the common SYSREF divider                                                                  |

| VCC6_OUT                                  | 3.135 | 3.3 | 3.465 | V    | $3.3 \text{ V} \pm 5\%$ , supply voltage for Output Channel 8, Output Channel 9, Output Channel 10, and Output Channel 11 |

| VCC7_OUT                                  | 3.135 | 3.3 | 3.465 | V    | 3.3 V $\pm$ 5%, supply voltage for Output Channel 0, Output Channel 1, Output Channel 12, and Output Channel 13           |

| TEMPERATURE                               |       |     |       |      |                                                                                                                           |

| Ambient Temperature Range, T <sub>A</sub> | -40   | +25 | +85   | °C   |                                                                                                                           |

<sup>1</sup> Maximum values are guaranteed by design and characterization.

# SUPPLY CURRENT

For detailed test conditions, see Table 18 and Table 19.

#### Table 2.

| Parameter <sup>1, 2</sup>        | Min | Тур | Max | Unit | Test Conditions/Comments                                                                                                                          |

|----------------------------------|-----|-----|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| CURRENT CONSUMPTION <sup>3</sup> |     |     |     |      |                                                                                                                                                   |

| VCC1_CLKDIST                     |     | 87  | 125 | mA   |                                                                                                                                                   |

| VCC2_OUT <sup>4</sup>            |     | 90  | 250 | mA   | Typical value is given at $T_A = 25^{\circ}C$ with two LVDS clocks at divide by 8                                                                 |

| VCC3_OUT <sup>4</sup>            |     | 52  | 500 | mA   | Typical value is given at 25°C with two LVDS high performance clocks, fundamental frequency of the clock input ( $f_0$ ), two SYSREF clocks (off) |

| VCC4_CLKIN                       |     | 16  | 25  | mA   | Typical value is given at T <sub>A</sub> = 25°C with RF synchronization (RFSYNC) input buffer off                                                 |

| VCC5_SYSREF                      |     | 23  | 35  | mA   | Typical value is given at $T_A = 25^{\circ}C$ with internal RF SYNC path off                                                                      |

| VCC6_OUT <sup>4</sup>            |     | 90  | 500 | mA   | Typical value is given at 25°C with two LVDS high performance clocks at divide by 2, two SYSREF clocks (off)                                      |

| VCC7_OUT <sup>4</sup>            |     | 100 | 500 | mA   | Typical value is given at 25°C with two LVDS clocks at divide by 8, two SYSREF clocks (off)                                                       |

| Total Current                    |     | 458 |     | mA   |                                                                                                                                                   |

<sup>1</sup> Maximum values are guaranteed by design and characterization.

<sup>2</sup> Currents include LVDS termination currents.

<sup>3</sup> Maximum values are for all circuits enabled in their worst case power consumption mode, PVT variations, and accounting for peak current draw during temporary synchronization events.

<sup>4</sup> Typical specification applies to a normal usage profile (Profile 1 in Table 18) but very low duty cycle currents (sync events) and some optional features are disabled. This specification assumes output configurations as described in the test conditions/comments column.

# DIGITAL INPUT/OUTPUT (I/O) ELECTRICAL SPECIFICATIONS

| Table | 3. |

|-------|----|

| Parameter                                                                  | Min  | Тур                          | Max             | Unit | Test Conditions/Comments                                                                       |

|----------------------------------------------------------------------------|------|------------------------------|-----------------|------|------------------------------------------------------------------------------------------------|

| DIGITAL INPUT SIGNALS (RESET, SLEN, SCLK)                                  |      |                              |                 |      |                                                                                                |

| Safe Input Voltage Range                                                   | -0.1 |                              | +3.6            | V    |                                                                                                |

| Input Load                                                                 |      | 0.3                          |                 | pF   |                                                                                                |

| Input Voltage                                                              |      |                              |                 |      |                                                                                                |

| Input Logic High                                                           | 1.2  |                              | V <sub>CC</sub> | V    |                                                                                                |

| Input Logic Low                                                            | 0    |                              | 0.5             | V    |                                                                                                |

| SPI Bus Frequency                                                          |      |                              | 10              | MHz  |                                                                                                |

| DIGITAL BIDIRECTIONAL SIGNALS CONFIGURED AS INPUTS (SDATA, GPIO)           |      |                              |                 |      |                                                                                                |

| Safe Input Voltage Range                                                   | -0.1 |                              | +3.6            | V    |                                                                                                |

| Input Capacitance                                                          |      | 0.4                          |                 | pF   |                                                                                                |

| Input Resistance                                                           |      | 50                           |                 | GΩ   |                                                                                                |

| Input Voltage                                                              |      |                              |                 |      |                                                                                                |

| Input Logic High                                                           | 1.22 |                              | $V_{CC}$        | V    |                                                                                                |

| Input Logic Low                                                            | 0    |                              | 0.24            | V    |                                                                                                |

| Input Hysteresis                                                           |      | 0.2                          |                 | V    | Occurs around 0.85 V                                                                           |

| GPIO ALARM MUXING/DELAY                                                    |      |                              |                 |      |                                                                                                |

| Delay from Internal Alarm/Signal to General-Purpose<br>Output (GPO) Driver |      | 2                            |                 | ns   | Does not include t <sub>DGPO</sub>                                                             |

| DIGITAL BIDIRECTIONAL SIGNALS CONFIFURED AS OUTPUTS (SDATA, GPIO)          |      |                              |                 |      |                                                                                                |

| CMOS Mode                                                                  |      |                              |                 |      |                                                                                                |

| Logic 1 Level                                                              | 1.6  | 1.9                          | 2.2             | V    |                                                                                                |

| Logic 0 Level                                                              |      | 0                            | 0.1             | V    |                                                                                                |

| Output Drive Resistance (R <sub>DRIVE</sub> )                              |      | 50                           |                 | Ω    |                                                                                                |

| Output Driver Delay (t <sub>DGPO</sub> )                                   |      | 1.5 + 42 × C <sub>LOAD</sub> |                 | ns   | Approximately 1.5 ns + 0.69 × R <sub>DRIVE</sub> × C <sub>LOAD</sub> (C <sub>LOAD</sub> in nF) |

| Maximum Supported DC Current <sup>1</sup>                                  |      |                              | 0.6             | mA   |                                                                                                |

| Open-Drain Mode                                                            |      |                              |                 |      | External 1 kΩ pull-up resistor                                                                 |

| Logic 1 Level                                                              |      |                              | 3.6             | V    | 3.6 V maximum permitted; specifications set by external supply                                 |

| Logic 0 Level                                                              |      | 0.13                         | 0.28            | V    | Against a 1 k $\Omega$ external pull-up resistor to 3.3 V                                      |

| Pull-Down Impedance                                                        |      | 60                           |                 | Ω    |                                                                                                |

| Maximum Supported Sink Current <sup>1</sup>                                |      |                              | 5               | mA   |                                                                                                |

<sup>1</sup> Guaranteed by design and characterization for long-term reliability.

# INPUT PATH SPECIFICATIONS

| Table 4.                                    |     |     | 1   | 1    |                                                                                                                                                                     |

|---------------------------------------------|-----|-----|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                   | Min | Тур | Мах | Unit | Test Conditions/Comments                                                                                                                                            |

| CLOCK INPUT (CLKIN)                         |     |     |     |      |                                                                                                                                                                     |

| Recommended Input Power, AC-Coupled         |     |     |     |      |                                                                                                                                                                     |

| Differential                                | -6  |     | +8  | dBm  |                                                                                                                                                                     |

| Single-Ended <sup>1</sup>                   | -10 |     | +6  | dBm  | Noise floor degrade by 3 dB at f <sub>CLKIN</sub> = 2400 MHz                                                                                                        |

| Return Loss                                 |     | -12 |     | dB   | When terminated with 100 $\Omega$ differential                                                                                                                      |

| Clock Input Frequency (f <sub>CLKIN</sub> ) | 200 |     |     | MHz  | When all channel dividers are equal to one or channels are in the fundamental mode. If <1 GHz, set the low frequency external VCO path bit (Register 0x0064, Bit 0) |

### Table 4. (Continued)

| Parameter          | Min T | 'yp Max      | Unit  | Test Conditions/Comments                                                         |

|--------------------|-------|--------------|-------|----------------------------------------------------------------------------------|

|                    | 450   |              | MHz   | When channel dividers are larger than 1 and synchronization is needed            |

|                    |       | 3200         | MHz   | Clock Input Divider is disabled. Register 0x0064[1] = 0                          |

|                    |       | 6000         | MHz   | Clock Input Divider is enabled. Register 0x0064[1] = 1                           |

| Common-Mode Range  | 0.4   | 2.4          | V     |                                                                                  |

| RFSYNC INPUT       |       |              |       |                                                                                  |

| Differential Swing | 0.375 | 1.4          | V р-р | Differential, keep signal at reference input pin <2.8 V, measured at 800 MHz     |

| Single-Ended Swing | 0.375 | 1.4          | V p-p | Keep signal at reference input pin <2.8 V                                        |

| Common Mode Range  | 0.4   | 2.4          | V     | If user supplied, on-chip $V_{CM}$ is approximately 2.1 V. DC coupling preferred |

| Input Impedance    |       | 00 to<br>000 | Ω     | User selectable; differential                                                    |

| Return Loss        | -     | 12           | dB    | When terminated with 100 $\Omega$ differential                                   |

| Setup/Hold Time    | 4     | 0            | ps    | V <sub>CM</sub> set to self bias voltage                                         |

<sup>1</sup> Guaranteed by design and characterization.

# ADDITIVE JITTER AND PHASE NOISE CHARACTERISTICS

| Table 5.                 |     |        |     |        |                                                                                                                           |

|--------------------------|-----|--------|-----|--------|---------------------------------------------------------------------------------------------------------------------------|

| Parameter <sup>1</sup>   | Min | Тур    | Мах | Unit   | Test Conditions/Comments                                                                                                  |

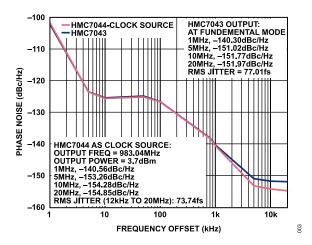

| ADDITIVE JITTER          |     |        |     |        | HMC7044 used as a clock source (see Figure 3)                                                                             |

| RMS Additive Jitter      |     | <30    |     | fs rms | Clock output frequency ( $f_{CLKOUT}$ ) = 983.04 MHz, BW = 12 kHz to 20 MHz, clock input slew rate $\ge$ 8 ns             |

|                          |     | <15    |     | fs rms | f <sub>CLKOUT</sub> = 2457.6 MHz, BW = 12 kHz to 20 MHz, clock input slew rate ≥ 4 ns                                     |

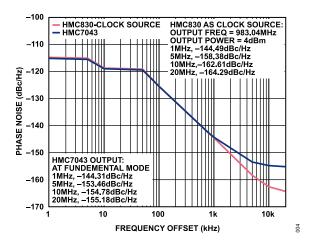

| CLOCK OUTPUT PHASE NOISE |     |        |     |        | HMC830 used as a clock source and configured to produce 983.04 MHz at the output (see Figure 4), input slew rate > 1 V/ns |

| Absolute Phase Noise     |     |        |     |        |                                                                                                                           |

| Offset = 1 MHz           |     | -144.3 |     | dBc/Hz | f <sub>CLKOUT</sub> = 983.04 MHz, f <sub>CLKOUT</sub> = 983.04 MHz, divide by 1 at the output                             |

| Offset = 10 MHz          |     | -154.8 |     | dBc/Hz | f <sub>CLKOUT</sub> = 983.04 MHz, f <sub>CLKOUT</sub> = 2949.12 MHz, divide by 3 at the output                            |

| Offset = 20 MHz          |     | -155.2 |     | dBc/Hz | $f_{CLKOUT}$ = 983.04 MHz, $f_{CLKOUT}$ = 983.04 MHz, divide by 1 at the output                                           |

<sup>1</sup> Guaranteed by design and characterization.

# **CLOCK OUTPUT DISTRIBUTION SPECIFICATIONS**

### Table 6.

| Parameter                                                                 | Min | Тур | Max  | Unit | Test Conditions/Comments                                                                                                  |

|---------------------------------------------------------------------------|-----|-----|------|------|---------------------------------------------------------------------------------------------------------------------------|

| CLOCK OUTPUT SKEW                                                         |     |     |      |      | Please refer to the Phase Behavior of<br>Synchronized Divided Clocks section for the<br>skew behavior of pulse generation |

| CLKOUTx/CLKOUTx to SCLKOUTx/SCLKOUTx Skew Within<br>One Clock Output Pair |     | 15  |      | ps   | Same pair, same type termination and configuration                                                                        |

| Any CLKOUTx/CLKOUTx to Any SCLKOUTx/SCLKOUTx                              |     | 30  |      | ps   | Any pair, same type termination and<br>configuration                                                                      |

| PROPAGATION DELAY CLKIN to CLKOUTx and SCLKOUTx <sup>1</sup>              | 770 | 820 | 870  | ps   | $\rm f_{CLKIN}$ = 983.04 MHz, all V <sub>CC</sub> set to 3.3 V                                                            |

| CLOCK OUTPUT DIVIDER CHARACTERISTICS                                      |     |     |      |      |                                                                                                                           |

| 12-Bit Divider Range                                                      | 1   |     | 4094 |      | 1, 3, 5, and all even numbers up to 4094                                                                                  |

| SYSREF CLOCK OUTPUT DIVIDER CHARACTERISTICS                               |     |     |      |      |                                                                                                                           |

# Table 6. (Continued)

| Parameter                                   | Min | Тур    | Max  | Unit             | Test Conditions/Comments                                                                                    |

|---------------------------------------------|-----|--------|------|------------------|-------------------------------------------------------------------------------------------------------------|

| 12-Bit Divider Range                        | 1   |        | 4094 |                  | 1, 3, 5, and all even numbers up to 4094; pulse generator behavior is only supported for divide ratios ≥ 32 |

| CLOCK OUTPUT ANALOG FINE DELAY              |     |        |      |                  |                                                                                                             |

| Analog Fine Delay                           |     |        |      |                  |                                                                                                             |

| Adjustment Range <sup>1</sup>               | 135 |        | 670  | ps               | 24 delay steps, f <sub>CLKOUT</sub> = 983.04 MHz                                                            |

| Resolution                                  |     | 25     |      | ps               | f <sub>CLKOUT</sub> = 983.04 MHz (2949.12 MHz/3)                                                            |

| Maximum Analog Fine Delay Frequency         |     | 1600   |      | MHz              |                                                                                                             |

| CLOCK OUTPUT COARSE DELAY (FLIP FLOP BASED) |     |        |      |                  |                                                                                                             |

| Coarse Delay Adjustment Range               | 0   |        | 17   | 1/2 CLKIN period | 17 delay steps                                                                                              |

| Coarse Delay Resolution                     |     | 169.54 |      | ps               | f <sub>CLKIN</sub> = 2949.12 MHz                                                                            |

| Maximum Frequency Coarse Delay              |     | 1500   |      | MHz              |                                                                                                             |

| CLOCK OUTPUT COARSE DELAY (SLIP BASED)      |     |        |      |                  |                                                                                                             |

| Coarse Delay                                |     |        |      |                  |                                                                                                             |

| Adjustment Range                            |     | 1 to ∞ |      | CLKIN period     |                                                                                                             |

| Resolution                                  |     | 339.08 |      | ps               | f <sub>CLKIN</sub> = 2949.12 MHz                                                                            |

| Maximum Frequency Coarse Delay              |     | 1600   |      | MHz              |                                                                                                             |

<sup>1</sup> Guaranteed by design and characterization.

# CLOCK OUTPUT DRIVER CHARACTERISTICS

### Table 7.

| Parameter                             | Min  | Тур                    | Max  | Unit        | Test Conditions/Comments                          |

|---------------------------------------|------|------------------------|------|-------------|---------------------------------------------------|

| CML MODE (LOW POWER)                  |      |                        |      |             | R <sub>L</sub> = 100 Ω, 9.6 mA                    |

| −3 dB Bandwidth                       |      | 1950                   |      | MHz         | Differential output voltage = 980 mV p-p diff     |

| Output Rise Time                      |      | 175                    |      | ps          | f <sub>CLKOUT</sub> = 245.76 MHz, 20% to 80%      |

|                                       |      | 145                    |      | ps          | f <sub>CLKOUT</sub> = 983.04 MHz, 20% to 80%      |

| Output Fall Time                      |      | 185                    |      | ps          | f <sub>CLKOUT</sub> = 245.76 MHz, 20% to 80%      |

|                                       |      | 145                    |      | ps          | f <sub>CLKOUT</sub> = 983.04 MHz, 20% to 80%      |

| Output Duty Cycle <sup>1</sup>        | 47.5 | 50                     | 52.5 | %           | f <sub>CLKOUT</sub> = 1075 MHz (2150 MHz/2)       |

| Differential Output Voltage Magnitude |      | 1390                   |      | mV p-p diff | f <sub>CLKOUT</sub> = 245.76 MHz (2949.12 MHz/12) |

|                                       |      | 1360                   |      | mV p-p diff | f <sub>CLKOUT</sub> = 983.04 MHz (2949.12 MHz/3)  |

| Common-Mode Output Voltage            |      | V <sub>CC</sub> - 1.05 |      | V           | f <sub>CLKOUT</sub> = 245.76 MHz (2949.12 MHz/12) |

| CML MODE (HIGH POWER)                 |      |                        |      |             | R <sub>L</sub> = 100 Ω, 14.5 mA                   |

| -3 dB Bandwidth                       |      | 1500                   |      | MHz         | Differential output voltage = 1470 mV p-p diff    |

| Output Rise Time                      |      | 250                    |      | ps          | f <sub>CLKOUT</sub> = 245.76 MHz, 20% to 80%      |

|                                       |      | 165                    |      | ps          | f <sub>CLKOUT</sub> = 983.04 MHz, 20% to 80%      |

| Output Fall Time                      |      | 255                    |      | ps          | f <sub>CLKOUT</sub> = 245.76 MHz, 20% to 80%      |

|                                       |      | 170                    |      | ps          | f <sub>CLKOUT</sub> = 983.04 MHz, 20% to 80%      |

| Output Duty Cycle <sup>1</sup>        | 47.5 | 50                     | 52.5 | %           | f <sub>CLKOUT</sub> = 1075 MHz (2150 MHz/2)       |

| Differential Output Voltage Magnitude |      | 2000                   |      | mV p-p diff | f <sub>CLKOUT</sub> = 245.76 MHz (2949.12 MHz/12) |

|                                       |      | 1800                   |      | mV p-p diff | f <sub>CLKOUT</sub> = 983.04 MHz (2949.12 MHz/3)  |

| Differential Output                   |      |                        |      |             |                                                   |

| Voltage Magnitude                     |      | 590                    |      | mV p-p diff | f <sub>CLKOUT</sub> = 3200 MHz                    |

| Power                                 |      | -3.6                   |      | dBm diff    | f <sub>CLKOUT</sub> = 3200 MHz                    |

| Common-Mode Output Voltage            |      | V <sub>CC</sub> - 1.6  |      | V           | f <sub>CLKOUT</sub> = 245.76 MHz (2949.12 MHz/12) |

| LVPECL MODE                           |      |                        |      |             | R <sub>L</sub> = 150 Ω, 4.8 mA                    |

| −3 dB Bandwidth                       |      | 2400                   |      | MHz         | Differential output voltage = 1240 mV p-p diff    |

### Table 7. (Continued)

| Parameter                             | Min  | Тур                   | Max  | Unit        | Test Conditions/Comments                                   |

|---------------------------------------|------|-----------------------|------|-------------|------------------------------------------------------------|

| Output Rise Time                      |      | 135                   |      | ps          | f <sub>CLKOUT</sub> = 245.76 MHz, 20% to 80%               |

|                                       |      | 130                   |      | ps          | f <sub>CLKOUT</sub> = 983.04 MHz, 20% to 80%               |

| Output Fall Time                      |      | 135                   |      | ps          | f <sub>CLKOUT</sub> = 245.76 MHz, 20% to 80%               |

|                                       |      | 130                   |      | ps          | f <sub>CLKOUT</sub> = 983.04 MHz, 20% to 80%               |

| Output Duty Cycle <sup>1</sup>        | 47.5 | 50                    | 52.5 | %           | f <sub>CLKOUT</sub> = 1075 MHz (2150 MHz/2)                |

| Differential Output Voltage Magnitude |      | 1760                  |      | mV p-p diff | f <sub>CLKOUT</sub> = 245.76 MHz (2949.12 MHz/12)          |

|                                       |      | 1850                  |      | mV p-p diff | f <sub>CLKOUT</sub> = 983.04 MHz (2949.12 MHz/3)           |

| Differential Output                   |      |                       |      |             |                                                            |

| Voltage Magnitude                     |      | 930                   |      | mV p-p diff | f <sub>CLKOUT</sub> = 3200 MHz                             |

| Power                                 |      | 0.3                   |      | dBm diff    | f <sub>CLKOUT</sub> = 3200 MHz                             |

| Common-Mode Output Voltage            |      | V <sub>CC</sub> – 1.3 |      | V           | f <sub>CLKOUT</sub> = 245.76 MHz (2949.12 MHz/12)          |

| LVDS MODE (LOW POWER) <sup>2</sup>    |      |                       |      |             | 1.75 mA                                                    |

| Maximum Operating Frequency           |      | 1700                  |      | MHz         | Differential output voltage = 320 mV p-p diff              |

| Output Rise Time                      |      | 135                   |      | ps          | f <sub>CLKOUT</sub> = 245.76 MHz, 20% to 80%               |

|                                       |      | 100                   |      | ps          | $f_{CLKOUT} = 983.04$ MHz, 20% to 80%                      |

| Output Fall Time                      |      | 135                   |      | ps          | f <sub>CLKOUT</sub> = 245.76 MHz, 20% to 80%               |

|                                       |      | 95                    |      | ps          | f <sub>CLKOUT</sub> = 983.04 MHz, 20% to 80%               |

| Output Duty Cycle <sup>1</sup>        | 47.5 | 50                    | 52.5 | %           | f <sub>CLKOUT</sub> = 1075 MHz (2150 MHz/2)                |

| Differential Output Voltage Magnitude |      | 390                   |      | mV p-p diff | f <sub>CLKOUT</sub> = 245.76 MHz (2949.12 MHz/12)          |

| Common-Mode Output Voltage            |      | 1.1                   |      | V           | f <sub>CLKOUT</sub> = 245.76 MHz (2949.12 MHz/12)          |

| LVDS MODE (HIGH POWER) <sup>2</sup>   |      |                       |      |             | 3.5 mA                                                     |

| Maximum Operating Frequency           |      | 1700                  |      | MHz         | Differential output voltage = 600 mV p-p diff              |

| Output Rise Time                      |      | 145                   |      | ps          | f <sub>CLKOUT</sub> = 245.76 MHz, 20% to 80%               |

|                                       |      | 105                   |      | ps          | $f_{CLKOUT} = 983.04 \text{ MHz}, 20\% \text{ to } 80\%$   |

| Output Fall Time                      |      | 145                   |      | ps          | f <sub>CLKOUT</sub> = 245.76 MHz, 20% to 80%               |

|                                       |      | 100                   |      | ps          | f <sub>CLKOUT</sub> = 983.04 MHz, 20% to 80%               |

| Output Duty Cycle <sup>1</sup>        | 47.5 | 50                    | 52.5 | %           | $f_{CLKOUT} = 1075 \text{ MHz} (2150 \text{ MHz}/2)$       |

| Differential Output Voltage Magnitude |      | 750                   |      | mV p-p diff | $f_{CLKOUT} = 245.76 \text{ MHz} (2949.12 \text{ MHz}/12)$ |

|                                       |      | 730                   |      | mV p-p diff | f <sub>CLKOUT</sub> = 983.04 MHz (2949.12 MHz/3)           |

| Common-Mode Output Voltage            |      | 1.1                   |      | V           | $f_{CLKOUT} = 245.76 \text{ MHz} (2949.12 \text{ MHz}/12)$ |

| CMOS MODE                             |      |                       |      |             |                                                            |

| Maximum Operating Frequency           |      | 600                   |      | MHz         | Single-ended output voltage = 940 mV p-p diff              |

| Output Rise Time                      |      | 425                   |      | ps          | $f_{CLKOUT} = 245.76 \text{ MHz}, 20\% \text{ to } 80\%$   |

| Output Fall Time                      |      | 420                   |      | ps          | $f_{CLKOUT} = 245.76 \text{ MHz}, 20% \text{ to 80\%}$     |

| Output Duty Cycle <sup>1</sup>        | 47.5 | 420<br>50             | 52.5 | %           | $f_{CLKOUT} = 1075 \text{ MHz} (2150 \text{ MHz}/2)$       |

| Output Voltage                        | 11.0 | ~~                    | 02.0 |             |                                                            |

| High                                  |      | V <sub>CC</sub>       |      | V           | Load current = 1 mA                                        |

|                                       |      | V <sub>CC</sub> - 0.5 |      | V           | Load current = 10 mA                                       |

| Low                                   |      | 0.07                  |      | V           | Load current = 1 mA                                        |

| LOW                                   |      | 0.07                  |      | V           | Load current = 10 mA                                       |

<sup>1</sup> Guaranteed by design and characterization.

<sup>2</sup> Refer to the Clock Output Network section for the N-Pulse SYSREF generation operation.

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 8.

| Parameter                                          | Rating           |

|----------------------------------------------------|------------------|

| VCC1, VCC2, VCC3, VCC4, VCC5, VCC6, VCC7 to Ground | -0.3 V to +3.6 V |

| Maximum Junction Temperature                       | 125°C            |

| Storage Temperature Range                          | -65°C to +125°C  |

| Operating Temperature Range                        | -40°C to +85°C   |

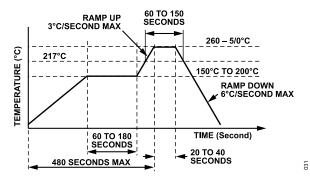

| Peak Reflow Temperature                            | 260°C            |

| ESD Sensitivity Level                              |                  |

| Human Body Model (HBM)                             | Class 1C         |

| Charged Device Model (CDM)                         | Class 2B         |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

# THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.  $\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.  $\theta_{JB}$  is the junction to bottom ground paddle thermal resistance.

### Table 9. Thermal Resistance

| РСВ Туре            | θ <sub>JA</sub>  | θ <sub>JC</sub> | θ <sub>JB</sub> | Unit |

|---------------------|------------------|-----------------|-----------------|------|

| JEDEC 2s2p<br>Board | N/A <sup>1</sup> | 13.40           | 6.92            | °C/W |

<sup>1</sup> N/A means not applicable.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2.

#### Table 10. Pin Function Descriptions

| Pin No. | Mnemonic     | Type <sup>1</sup> | Description                                                                                                                                  |

|---------|--------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CLKOUT0      | 0                 | True Clock Output Channel 0. Default DCLK profile.                                                                                           |

| 2       | CLKOUT0      | 0                 | Complementary Clock Output Channel 0. Default DCLK profile.                                                                                  |

| 3       | SCLKOUT1     | 0                 | True Clock Output Channel 1. Default SYSREF profile.                                                                                         |

| 4       | SCLKOUT1     | 0                 | Complementary Clock Output Channel 1. Default SYSREF profile.                                                                                |

| 5       | RESET        | I                 | Device Reset Input. Active high. For normal operation, set RESET to 0.                                                                       |

| 6       | BGAPBYP1     |                   | Band Gap Bypass Capacitor Connection. Connect a 4.7 µF capacitor to ground. This pin affects all internally regulated supplies.              |

| 7       | LDOBYP2      |                   | LDO Bypass 2. Connect a 4.7 µF capacitor to ground. The internal digital supply is 1.8 V. This pin is the LDO bypass for the SYSREF section. |

| 8       | VCC1_CLKDIST | Р                 | 3.3 V Supply for CLK Distribution.                                                                                                           |

| 9       | SCLKOUT3     | 0                 | True Clock Output Channel 3. Default SYSREF profile.                                                                                         |

| 10      | SCLKOUT3     | 0                 | Complementary Clock Output Channel 3. Default SYSREF profile.                                                                                |

| 11      | CLKOUT2      | 0                 | True Clock Output Channel 2. Default DCLK profile.                                                                                           |

| 12      | CLKOUT2      | 0                 | Complementary Clock Output Channel 2. Default DCLK profile.                                                                                  |

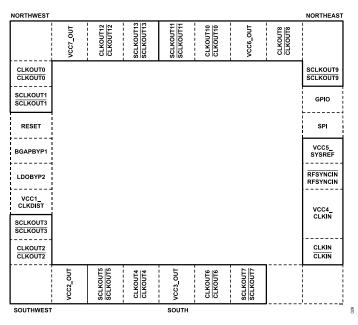

| 13      | VCC2_OUT     | Р                 | Power Supply for Clock Group 1 (Southwest)—Channel 2 and Channel 3. See the Clock Grouping, Skew, and Crosstalk section.                     |

| 14      | RSV          | R                 | Reserved Pin. This pin must be tied to ground.                                                                                               |

| 15      | SCLKOUT5     | 0                 | True Clock Output Channel 5. Default SYSREF profile.                                                                                         |

| 16      | SCLKOUT5     | 0                 | Complementary Clock Output Channel 5. Default SYSREF profile.                                                                                |

| 17      | CLKOUT4      | 0                 | True Clock Output Channel 4. Default DCLK profile.                                                                                           |

| 18      | CLKOUT4      | 0                 | Complementary Clock Output Channel 4. Default DCLK profile.                                                                                  |

| 19      | VCC3_OUT     | Р                 | Power Supply for Clock Group 2 (South)—Channel 4, Channel 5, Channel 6, and Channel 7. See the Clock Grouping, Skew, and Crosstalk section.  |

| 20      | CLKOUT6      | 0                 | True Clock Output Channel 6. Default DCLK profile.                                                                                           |

| 21      | CLKOUT6      | 0                 | Complementary Clock Output Channel 6. Default DCLK profile.                                                                                  |

| 22      | SCLKOUT7     | 0                 | True Clock Output Channel 7. Default SYSREF profile.                                                                                         |

| 23      | SCLKOUT7     | 0                 | Complementary Clock Output Channel 7. Default SYSREF profile.                                                                                |

| 24      | RSV          | R                 | Reserved Pin. This pin must be tied to ground.                                                                                               |

| 25      | CLKIN        | 1                 | Complementary Clock Input.                                                                                                                   |

| 26      | CLKIN        | 1                 | True Clock Input.                                                                                                                            |

| 27      | VCC4_CLKIN   | Р                 | Power Supply for the Clock Input Path.                                                                                                       |

| 28      | RFSYNCIN     | 1                 | True RF Synchronization Input with Deterministic Delay.                                                                                      |

| 29      | RFSYNCIN     | I                 | Complementary RF Synchronization Input with Deterministic Delay.                                                                             |

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

### Table 10. Pin Function Descriptions (Continued)

| Pin No. | Mnemonic    | Type <sup>1</sup> | Description                                                                                                                                       |

|---------|-------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 30      | VCC5_SYSREF | Р                 | Power Supply for Common SYSREF Divider.                                                                                                           |

| 31      | SLEN        | I/O               | SPI Latch Enable.                                                                                                                                 |

| 32      | SCLK        | I/O               | SPI Clock.                                                                                                                                        |

| 33      | SDATA       | I/O               | SPI Data.                                                                                                                                         |

| 34      | GPIO        | I/O               | Programmable General-Purpose Input/Output.                                                                                                        |

| 35      | SCLKOUT9    | 0                 | True Clock Output Channel 9. Default SYSREF profile.                                                                                              |

| 36      | SCLKOUT9    | 0                 | Complementary Clock Output Channel 9. Default SYSREF profile.                                                                                     |

| 37      | CLKOUT8     | 0                 | True Clock Output Channel 8. Default DCLK profile.                                                                                                |

| 38      | CLKOUT8     | 0                 | Complementary Clock Output Channel 8. Default DCLK profile.                                                                                       |

| 39      | VCC6_OUT    | P                 | Power Supply for Clock Group 3 (North)—Channel 8, Channel 9, Channel 10, and Channel 11. See the Clock Grouping, Skew, and Crosstalk section.     |

| 40      | CLKOUT10    | 0                 | True Clock Output Channel 10. Default DCLK profile.                                                                                               |

| 41      | CLKOUT10    | 0                 | Complementary Clock Output Channel 10. Default DCLK profile.                                                                                      |

| 42      | SCLKOUT11   | 0                 | True Clock Output Channel 11. Default SYSREF profile.                                                                                             |

| 43      | SCLKOUT11   | 0                 | Complementary Clock Output Channel 11. Default SYSREF profile.                                                                                    |

| 44      | SCLKOUT13   | 0                 | True Clock Output Channel 13. Default SYSREF profile.                                                                                             |

| 45      | SCLKOUT13   | 0                 | Complementary Clock Output Channel 13. Default SYSREF profile.                                                                                    |

| 46      | CLKOUT12    | 0                 | True Clock Output Channel 12. Default DCLK profile.                                                                                               |

| 47      | CLKOUT12    | 0                 | Complementary Clock Output Channel 12. Default DCLK profile.                                                                                      |

| 48      | VCC7_OUT    | P                 | Power Supply for Clock Group 0 (Northwest)—Channel 0, Channel 1, Channel 12, and Channel 13. See the Clock Grouping, Skew, and Crosstalk section. |

|         | EP          |                   | Exposed Pad. Connect the exposed pad to a high quality RF/dc ground.                                                                              |

$^{1}\;$  O is output, I is input, P is power, R is reserved, and I/O is input/output.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 3. Additive Jjitter at 983.04 MHz at Output

Figure 4. Absolute Phase Noise Measured at 983.04 MHz at Output

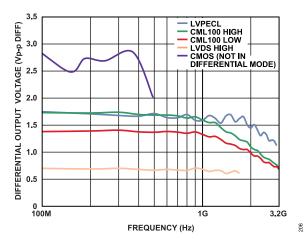

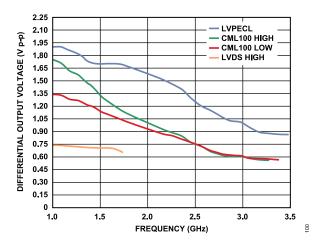

Figure 5. Differential Output Power vs. Frequency over Various Modes

Figure 6. Differential Output Voltage vs. Frequency over Various Modes

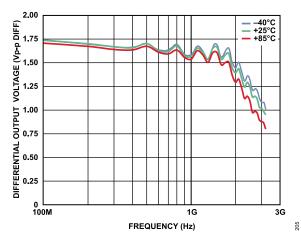

Figure 7. LVPECL Differential Output Power vs. Frequency over Various Temperatures

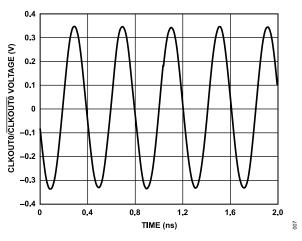

Figure 8. Differential CLKOUT0/CLKOUT0 at 2457 MHz, LVPECL

### **TYPICAL PERFORMANCE CHARACTERISTICS**

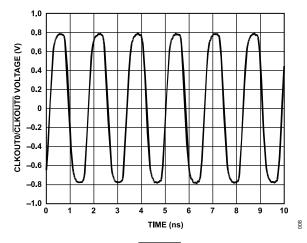

Figure 9. Differential CLKOUT0/CLKOUT0 Voltage at 614.4 MHz, LVPECL

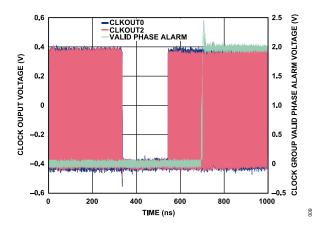

Figure 10. Output Channel Synchronization Before and After Rephase

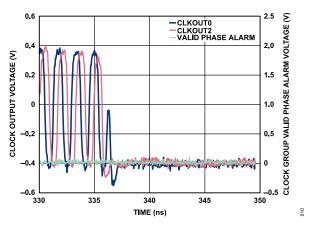

Figure 11. Output Channel Synchronization Before Rephase

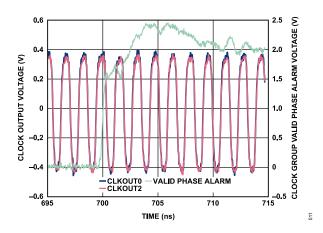

Figure 12. Output Channel Synchronization After Rephase

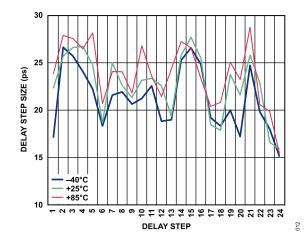

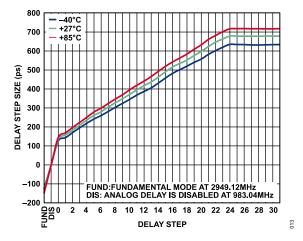

Figure 13. Analog Delay Step Size vs. Delay Step over Temperature, LVPECL at 983.04 MHz

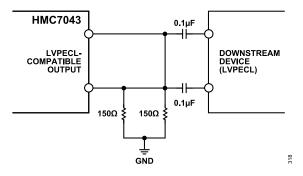

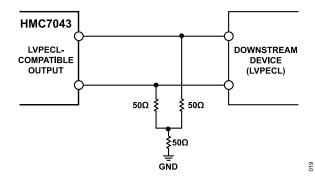

Figure 14. Analog Delay vs. Delay Setting over Temperature, LVPECL at 983.04 MHz

# **TYPICAL APPLICATION CIRCUITS**

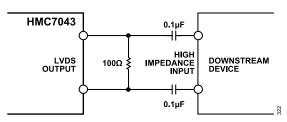

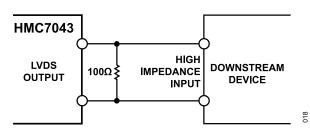

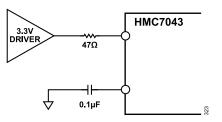

Figure 15. AC-Coupled LVDS Output Driver

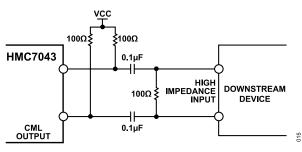

Figure 16. AC-Coupled CML (Configured High-Z) Output Driver

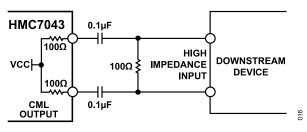

Figure 17. AC-Coupled CML (Internal) Output Driver

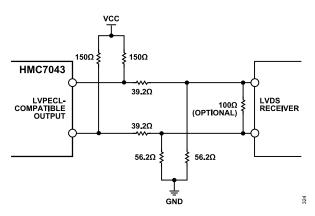

Figure 18. AC-Coupled LVPECL Output Driver

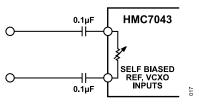

Figure 19. CLKIN/ CLKIN , RFSYNCIN Input Differential Mode

Figure 20. DC-Coupled LVDS Output Driver

Figure 21. DC-Coupled LVPECL Output Driver

Figure 22. DC-Coupled CML (Internal) Output Driver

Figure 23. CLKIN, RFSYNCIN Input Single-Ended Mode

Figure 24. Level Translation for LVDS N-Pulse Operation (Place 100  $\Omega$ Termination Resistor If Receiver Does Not Have It.)

# TERMINOLOGY

# **Phase Jitter and Phase Noise**

An ideal sine wave has a continuous and even progression of phase with time from 0° to 360° for each cycle. Actual signals, however, display a certain amount of variation from ideal phase progression over time. This phenomenon is phase jitter. Although many causes can contribute to phase jitter, one major cause is random noise, which is characterized statistically as being Gaussian (normal) in distribution.

This phase jitter leads to the energy of the sine wave in the frequency domain spreading out, producing a continuous power spectrum. This power spectrum is usually reported as a series of values whose units are dBc/Hz at a given offset in frequency from the sine wave (carrier). The value is a ratio (expressed in decibels) of the power contained within a 1 Hz bandwidth with respect to the power at the carrier frequency. For each measurement, the offset from the carrier frequency is also given.

It is meaningful to integrate the total power contained within some interval of offset frequencies (for example, 10 kHz to 10 MHz). This is the integrated phase noise over that frequency offset interval and can be readily related to the time jitter due to the phase noise within that offset frequency interval.

Phase noise has a detrimental effect on the performance of analogto-digital converters (ADCs), digital-to-analog converters (DACs), and RF mixers. It lowers the achievable dynamic range of the converters and mixers, although they are affected in somewhat different ways.

## **Time Jitter**

Phase noise is a frequency domain phenomenon. In the time domain, the same effect is exhibited as time jitter. When observing a sine wave, the time of successive zero crossings varies. In a square wave, the time jitter is a displacement of the edges from their ideal (regular) times of occurrence. In both cases, the variations in timing from the ideal are the time jitter. Because these variations are random in nature, the time jitter is specified in seconds root mean square (rms) or 1 sigma of the Gaussian distribution.

Time jitter that occurs on a sampling clock for a DAC or an ADC decreases the signal-to-noise ratio (SNR) and dynamic range of the converter. A sampling clock with the lowest possible jitter provides the highest performance from a given converter.

### **Additive Phase Noise**

Additive phase noise is the amount of phase noise that is attributable to the device or subsystem being measured. The phase noise of any external oscillators or clock sources is subtracted, which makes it possible to predict the degree to which the device impacts the total system phase noise when used in conjunction with the various oscillators and clock sources, each of which contributes a phase noise to the total. In many cases, the phase noise of one element dominates the system phase noise. When there are multiple contributors to phase noise, the total is the square root of the sum of squares of the individual contributors.

### Additive Time Jitter

Additive time jitter is the amount of time jitter that is attributable to the device or subsystem being measured. The time jitter of any external oscillators or clock sources is subtracted, which makes it possible to predict the degree to which the device impacts the total system time jitter when used in conjunction with the various oscillators and clock sources, each of which contributes a time jitter to the total. In many cases, the time jitter of the external oscillators and clock sources dominates the system time jitter.

The HMC7043 is a high performance, clock distribution IC designed for extending the number of clock signals across the system with minimal noise contribution. The device can be used for distributing the noise sensitive reference clocks for high speed data converters with either parallel or serial (JESD204B/C) interfaces, FPGAs, and local oscillators. The HMC7043 is designed to meet the requirements of demanding base station designs, and offers a wide range of clock management and distribution features to simplify baseband and radio card clock tree designs. The device provides 14 low noise and configurable outputs to offer flexibility in distributing clocks while applying frequency division, phase adjustment, cycle slip, and external signal synchronization options.

The HMC7043 generates up to seven DCLK and SYSREF clock pairs per the JESD204B/C interface requirements. The system designer can generate a lower number of DCLK and SYSREF pairs, and configure the remaining output signal paths as DCLKs, additional SYSREFs, or other reference clocks with independent phase and frequency adjustment. Frequency adjustment can be accomplished by selecting the appropriate output divider values.

One of the unique features of the HMC7043 is the independent flexible phase management of each of the 14 channels. Using a combination of divider slip based, digital (coarse) and analog (fine) delay adjustments, each channel can be programmed to have a different phase offset. The phase adjustment capability allows the designer to offset board flight time delay variations, match data converter sample windows, and meet JESD204B/C synchronization challenges. The output signal path design of the HMC7043 is implemented to ensure both linear phase adjustment steps and minimal noise perturbation when phase adjustment circuits are turned on.

The HMC7043 provides output clock signals of up to 3.2 GHz, while having the flexibility to support input reference frequencies of up to 6 GHz when the internal clock division blocks are turned on. The

higher frequency support enables higher bandwidth RF designs, and allows for distribution of low noise RF phase-locked loop (PLL) voltage controlled oscillator (VCO) outputs as well as other critical clocks across the system.

One of the key challenges in JESD204B/C system designs is ensuring the synchronization of data converter frame alignment across the system, from the FPGA or digital front end (DFE) to ADCs and DACs through a large clock tree that may comprise multiple clock generation and distribution ICs.

There are two input paths on the HMC7043; one is for the clock signal that is distributed, and the other may be used as an external synchronization signal. In typical JESD204B/C systems, serial data converter interfaces, there may be a need to ensure that all clock signals that are sent to the data converters have phases which are controlled by an FPGA. By virtue of the RF SYNC input, the device ensures that output signals have a deterministic phase alignment to this synchronization input. The RF SYNC input can also implement multiple device clock trees by nesting more than one HMC7043 to generate an even larger clock distribution network, while still maintaining phase alignment across the clock tree.

Offering excellent crosstalk, frequency isolation, and spurious performance, the device generates independent frequencies in both single-ended and differential formats including LVPECL, LVDS, CML, and CMOS, and different bias conditions to offset varying board insertion losses. The outputs can also be programmed for AC or DC coupling and 50  $\Omega$  or 100  $\Omega$  internal and external termination options.

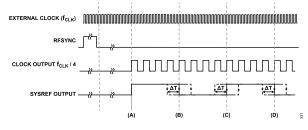

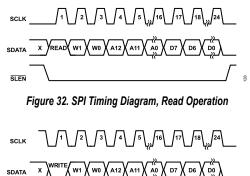

The HMC7043 is programmed via a 3-wire serial port interface (SPI). The HMC7043 is offered in a 48-lead, 7 mm × 7 mm, LFCSP package with the exposed pad to ground.

### DETAILED BLOCK DIAGRAM

Figure 25. Detailed Block Diagram

### **CLOCK INPUT NETWORK**

# Input Termination Network—Common for All Input Buffers

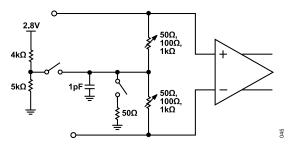

The two clock and RFSYNC input buffers share similar architecture and control features. The input termination network is configurable to 100  $\Omega$ , 200  $\Omega$ , and 2 k $\Omega$  differentially. It is typically AC-coupled on the board, and uses the on-chip resistive divider to set the internal common-mode voltage, V<sub>CM</sub>, to 2.1 V.

By closing the 50  $\Omega$  termination switch (see Figure 26), the network also can serve as the termination system for an LVPECL driver. Although the input termination network for the two clock and RFSYNC input buffers is identical, the buffer behind the network is different.

Figure 26. On-Chip Termination Network for Clock and RFSYNC Buffers

### **Recommendations for Normal Use**

For both buffer types, unless there are extenuating circumstances in the application, use 100  $\Omega$  differential termination resistors to control reflections, to use the on-chip dc bias network to set the common mode level, and to externally ac couple the input signals in. Do not use a receiver side dc termination of the LVPECL signal.

### Single-Ended Operation

The buffers can support a single-ended signal with slightly reduced input sensitivity and bandwidth. If driving any of the buffers singleended, ac couple the unused leg of the buffer to ground at the input of the die.

### **Maximum Signal Swing Considerations**

The internal supplies to these input buffers are supplied directly from 3.3 V. The ESD network and parasitic diodes can generally shunt away excess power and protect the internal circuits (with-standing reference powers above 13 dBm). Nevertheless, to protect from latch-up concerns, the signals on the reference inputs must not exceed the 3.3 V internal supply. For a 2.1 V common mode, 50  $\Omega$  single-ended source, this allows ~1200 mV of amplitude, or 11 dBm maximum reference power.

# **CLOCK OUTPUT NETWORK**

The HMC7043 is a high performance clock buffer, is appropriate for JESD204B/C data converters, and much of the uniqueness of a JESD204B/C clock generation chip relates to the array of output channels. In this device, the output network requirements include the following:

- A large number of device clock (DCLK) and synchronization (SYSREF) channels

- Very good phase noise floor of the DCLK channels that can be connected to critical data converter sample clock inputs

- Deterministic phase alignment between all output channels relative to one another

- Fine phase control of synchronization channels with respect to the DCLK channel

- ▶ Frequency coverage to satisfy typical clock rates in systems

- Skew between SYSREF and DCLK channels that is much less than a DCLK period

- Spur and crosstalk performance that does not impact system budgets

The HMC7043 output network supports the following recommended features, which are sometimes critical in user applications:

- Deterministic synchronization of the output channels with respect to an external signal (RFSYNC), which allows multichip synchronization and clean expansion to larger systems

- Pulse generator behavior to temporarily generate a synchronization pulse stream at a user request

- The flexibility to define unused JESD204B/C SYSREF and DCLK channels for other purposes

- Glitchless phase control of signals relative to each other

- ▶ 50% duty cycle clocks with odd division ratios

- Multimode output buffers with a variety of swings and termination options

- Skew between all channels is much less than a DCLK period

- Adjustable performance vs. power consumption for less sensitive clock channels

Figure 27. Clock Output Network Simplified Diagram

Each of the 14 output channels are logically identical. The only distinction between the SYSREF and DCLK channels is in the SPI configuration, and in how they are used. Each channel contains independent dividers, phase adjustment, and analog delay circuits. This combination provides the ultimate flexibility, cleanly accommodating nonJESD204B/C devices in the system.

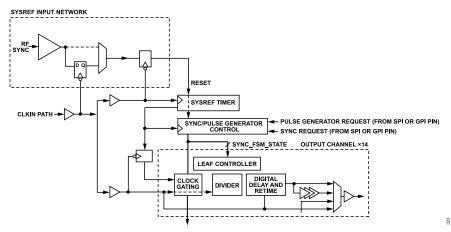

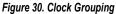

In addition to the 14 output channel dividers, an internal SYSREF timer continually operates, and the synchronization of the output channel dividers occurs deterministically with respect to this timer, which the user can rephased deterministically by the user through GPI or SPI or deterministically by using the RFSYNCIN/ RFSYN-CIN differential pins.

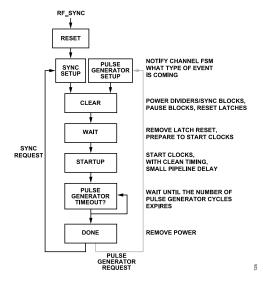

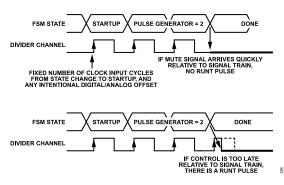

The pulse generator functionality of the JESD204B and JES204C standards involves temporarily generating SYSREF output pulses, with appropriate phasing, to downstream devices. The centralized SYSREF timer and the associated SYNC/pulse generator control manage the process of enabling the intended SYSREF channels, phasing them, and then disabling them for signal integrity and power saving advantages.

HMC7043 can provide continuous SYSREF clocks in LVPECL, CML, LVDS, and CMOS modes and N-pulse SYSREF clocks in LVPECL, CML, and CMOS modes. If N-pulse LVDS SYSREF clock is needed, output driver type must be set as LVPECL and level translation circuitry given in Figure 24 must be placed between clock channel and LVDS downstream device.

## **Basic Output Divider Channel**

Each of the 14 output channels are logically identical, and support divide ratios from 1 to 4094. The supported odd divide ratios (1, 3, or 5) have 50.0% duty cycle. The only distinction between a SYS-REF channel and a device clock channel is in the SPI configuration and the typical usage of a given channel.

For basic functionality and phase control, each output path consists of the following:

- Divider—generates the logic signal of the appropriate frequency and phase

- Digital phase adjust—adjusts the phase of each channel in increments of ½ clock input cycles

- Retimer—a low noise flip flop to retime the channel, removing any accumulated jitter

- ► Analog fine delay—provides a number of ~25 ps delay steps

- Selection mux—selects the fundamental, divider, analog delay, or an alternate path

- Multimode output buffer—low noise LVDS, CML, CMOS, or LVPECL

The digital phase adjuster and retimer launch on either clock phase of the clock input, depending on the digital phase adjust setpoint (Coarse Digital Delay[4:0]).

To support divider synchronization, arbitrary phase slips, and pulse generator modes, the following blocks are included:

- A clock gating stage pauses the clock for synchronization or slip operations

- An output channel leaf (×14) controller that manages slip, synchronization, and pulse generators with information from the SYSREF finite state machine (FSM)

Each channel has an array of control signals. Some of the controls are described in Table 11.

System wide broadcast signals can be triggered from the SPI or general-purpose input (GPI) port to issue a SYNC command (to align dividers to the system internal SYSREF timer), issue a pulse generator stream, (temporarily exporting SYSREF signals to receivers), or to cause the dividers to slip a number of clock input cycles to adjust their phases.

Individual dividers can be made sensitive to these events by adjusting their slip enable, SYNC enable, and Start-Up Mode[1:0] configuration, as described in Table 12.

When output buffers are configured in CMOS mode and phase alignment is required among the outputs, additional multislip delays must be issued for Channel 0, Channel 3, Channel 5, Channel 6, Channel 9, Channel 10, and Channel 13. The value of the delay must be as large as half of the selected divider ratio. Note that this requirement of having additional multislip delays is not needed when the channels are used in LVPECL, CML, or LVDS mode.

If a channel is configured to behave as a pulse generator, to temporarily power up and power down according to the GPI and SPI pulse generator commands; additional controls define the behavior outside of the pulse generator chain (see Table 13).

Each divider has an additional phase offset register that adjusts the start phase or influences the behavior of slip events sent via the SPI (see Table 14).

Table 15 outlines the typical configuration combinations for a DCLK channel relative to a SYSREF synchronization channel. Note that other combinations are possible. Synchronization of downstream devices can be managed manually, or by using the pulse generator functionality of the HMC7043. See the Typical Programming Sequence section for more information about the differences between the two methods.

### Table 11. Basic Divider Controls

| Bit Name                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|