# **Engineer-to-Engineer Note**

Technical notes on using Analog Devices products, processors and development tools Visit our Web resources http://www.analog.com/ee-notes and http://www.analog.com/processors or e-mail processor.support@analog.com or processor.tools.support@analog.com for technical support.

# ADSP-BF70x Blackfin+<sup>TM</sup> Processor Optimization Techniques

Contributed by Li Liu

Rev 1 – December 15, 2016

## Introduction

Analog Devices' Blackfin+<sup>TM</sup> processors were enhanced as compared with the previous generation Blackfin devices to provide single-cycle 32-bit multiplication or 16-bit complex math operations, dynamic branch prediction, support for misaligned data accesses, ECC/multi-parity-protected on-chip memory, and improved memory bandwidth. The Blackfin+ processors are comprised of the ADSP-BF70x products.

This EE-Note describes how to optimize C/C++ applications to fully utilize these advantageous features, though most of the coding tips presented in this note are also applicable to the previous Blackfin processors as well. All of the examples in this note were implemented using an ADSP-BF707 EZ-Board® and CrossCore® Embedded Studio (CCES) 2.1.0. Please refer to *Getting Started with CrossCore Embedded Studio 1.1.x (EE-372)*<sup>[1]</sup> to learn how to begin development with CCES.

# **Blackfin+** Core Overview

The first step in writing efficient C/C++ code is to understand the processor on which a developer is working. This section will introduce the features of the ADSP-BF70x processor and emphasize a few that impact programming of it. First of all, Blackfin+ is a 32-bit fixed-point processor, meaning that math operations on floating-point numbers are emulated by software. In other words, the processor needs multiple cycles to complete one floating-point math operation; however, the same fixed-point math operation may only need one cycle. Similarly, 64-bit integer math operations are emulated by software.

The ADSP-BF70x processor supports efficient fractional math operations (16- or 32-bit) by using the native fixed-point data types *fract* or *accum* (as defined in the stdfix.h header file) or by calling built-in functions for fractional math operations. In the latter case, fractional numbers are declared as *fract16* or *fract32*, which are type-defined in CCES as *short* and *int*, respectively. It is important to remember that fractional numbers are different from floating-point numbers. The fractional number has a range of [-1.0, 1.0). Please refer to the *Data Storage Formats* section of the *Compiler and Library Manual for Blackfin*<sup>[2]</sup>, the *Numeric Formats* section of the *Blackfin+ Programming Reference*<sup>[3]</sup>, and the <u>Manipulating Fractional Data</u> section of this note for more details.

Copyright 2016, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Engineer-to-Engineer Notes.

#### **Enhanced Computation Capability**

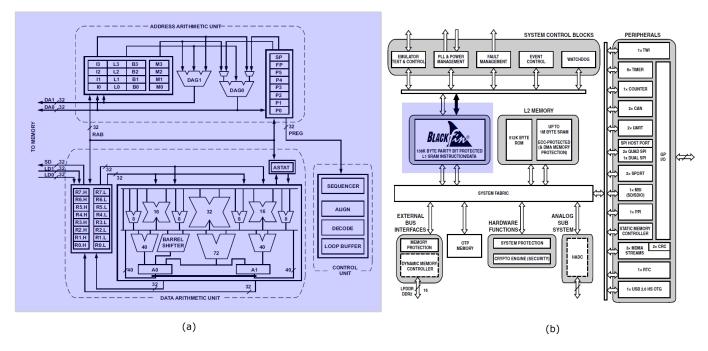

As shown in Figure 1(a), the processor core has two 16-bit multipliers, two 40-bit accumulators, two 40-bit Arithmetic Logic Units (ALU), four video ALUs, and a 40-bit shifter. The enhanced multipliers enable the processor to handle one 32-bit or two 16-bit integer multiplications in one cycle. Even though 32-bit multiplication is supported on Blackfin+ processors, the developer should utilize 16-bit multiplication whenever possible to double computation capability. The video ALUs are able to simultaneously complete quad 8-bit video computations, including add/subtract, average, pack/unpack and subtract-absolute-accumulate. Choosing an appropriate data type for an application is always critical for achieving the best performance. The width of a specific data type is compiler-dependent, so the developer should not assume it.

Figure 1. ADSP-BF70x Overview: (a) Processor Core; (b) Functional Block Diagram

Choosing proper data types usually requires a developer to know maximum and/or minimum variable values in a given function. Actually, it is tedious work to modify all data types of a program which have thousands of lines of code. Instead, choosing optimal data types only for functions (hotspot functions) that intensively utilize the processor may be a better balance of work load and performance gain. How to find these hotspot functions is covered in the Using the Profilers to Analyze Code Execution section of this note. It should be noted that the Blackfin+ architecture favors the use of 32-bit data types in control code for optimal performance and code size. Therefore, the developer should not change every int variable to a short or char type.

The processor supports a modified Harvard architecture, as shown in Figure 1(a). Data and instructions are fetched from the processor memory via dedicated data and instruction buses, respectively. It should be noted that there are three data buses in the processor. In other words, the processor is able to simultaneously compute and access data (two loads or one load and one store). This simultaneous execution can be achieved

from C/C++ code. Following the recommendations presented in this note will significantly increase the likelihood that the compiler generates the most efficient assembly code possible.

#### **Hierarchical Memory Structure**

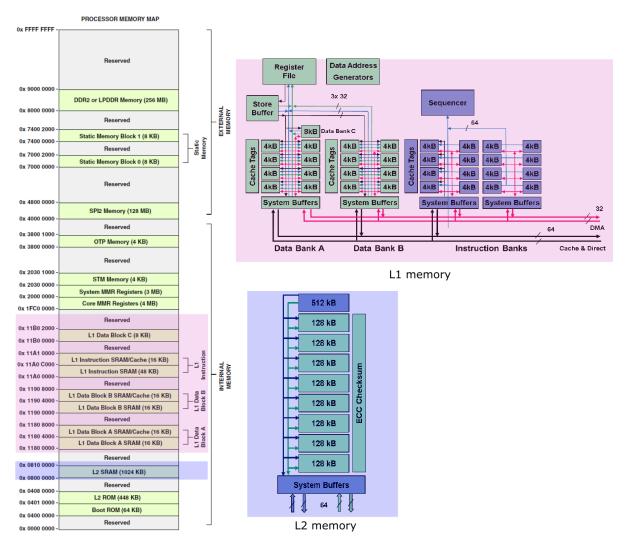

The processor has a hierarchical memory structure, a fast and small Level 1 (L1) on-chip memory running at the processor core clock, a large Level 2 (L2) on-chip memory running at the processor system clock, support for an even larger Level 3 (L3) off-chip memory, and other memory spaces, as shown in Figure 1(b) and Figure 2. This note is only focused on the L1, L2 and L3 memory spaces. The Blackfin+ memory is viewed as a unified 4G byte address space, using 32-bit addresses. A key difference between the L1, L2 and L3 memory spaces is their access speed. All instructions and data of an application should be deployed on the fastest possible memory. However, for most applications, this is not possible due to the limited L1/L2 memory size. Therefore, the developer must think about how to allocate memory for instructions and data to achieve the best performance.

Figure 2. ADSP-BF707 Memory Architecture

As manually managing L1 memory may be challenging for some developers, an alternative is to enable the processor's instruction and data caches. For ADSP-BF70x devices, 32 KB of L1 data memory and 16 KB of instruction memory can be used as cache. After the caches are enabled, even if the instructions and data of an application reside in L2/L3 memory, the processor can ultimately access a copy of them in L1 cache at the core clock rate. This approach is also effective when an application is too complex or difficult to distinguish hotspot functions.

The L1 and L2 memory spaces are split into several separate banks. This design is a key factor to avoid data access conflicts. For example, if a function computes the sum of two vectors of the same length, the application allocate the buffers to different data banks so that the processor can simultaneously access the elements of the two vectors using different data buses.

#### **Branch Prediction**

On Blackfin+ processors, a 10-stage pipeline is used to ensure that the processor is able to execute one instruction per cycle. However, the pipeline incurs a problem when conditional code exists (e.g., *if/else*, *while*, *for*, etc.). For example, in the execution stage of the conditional code, the processor knows that it will need the instructions of Condition A in the next cycle; however, the instructions of Condition B have been fetched and decoded for the next cycle because these instructions are the next contiguous instructions following the conditional code. In this case, the processor has to discard the instructions in the pipeline and instead fetch/decode the instructions associated with Condition A, thus wasting a few precious cycles. If the conditional code is in a loop, the performance will further degrade as the conditional code executes many times.

To resolve this problem, the Blackfin+ processor has a dynamic branch predictor (BP) that improves the performance of conditional code by remembering where the code vectored to the previous time it was executed. The BP has been proven to effectively reduce a program's execution time. For a developer, additional actions are not required to use the BP because it has been enabled by default after coming out of reset. Please refer to *Tuning Dynamic Branch Prediction on ADSP-BF70x Blackfin*+<sup>TM</sup> *Processors (EE-373)*<sup>[4]</sup> for details.

#### **Managing Processor Clocks**

The core, memory and peripherals of the ADSP-BF707 processor run at different frequencies. The Dynamic Power Management (DPM) block and the Clock Generation Unit (CGU) allow the developer to configure the core and system frequencies. Do not assume that the processor is set to run with the highest frequency after reset. The developer should configure the processor's core and system frequencies to achieve the best processor performance, especially for a custom board design. The processor core and system frequencies can be easily managed by calling dedicated System Service and Device Driver APIs. Please refer to the CCES On-Line Help and the *System Services & Device Drivers: CrossCore Embedded Studio* on-line training video for details.

Copyright 2016, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Engineer-to-Engineer Notes.

#### **Direct Memory Access (DMA)**

As mentioned, the processor has a hierarchical memory structure comprising multiple memory spaces with different access speeds. The core is able to access data in L1 memory in one core cycle and data in L2 memory in multiple core cycles, with longer access times for L3 memory. If data are in L2/L3 memory, the processor has to stall for multiple core cycles until the data is ready. Using cache is one way to make an application execute efficiently. But if too many cache misses occur, the application may not achieve the desired performance. To solve this, Direct Memory Access (DMA), can be used to allow data to be moved between L2/L3 memory and L1 memory without core intervention.

Additionally, as was the case with core buses simultaneously accessing different banks of memory, the same concept also holds true for the DMA channels. As the DMA engines use a dedicated bus for transfers, it will also compete with the core for access to a targeted bank of memory. Therefore, choosing different memory banks for receiving and sending data via DMA to remove conflicts with the core can improve the data throughput of an application.

#### **Trigger Routing Unit (TRU)**

The Trigger Routing Unit (TRU) provides system-level event control without core intervention. The TRU links a trigger master (the generator of an event) to a trigger slave (the receiver of the event). In this way, the receiver can automatically respond to the sender without using a traditional interrupt, where a core is required to pass the event to the receiver. The TRU is typically used in starting a DMA transfer when a specific event occurs (e.g., another DMA transfer completes) or to synchronize concurrent activities.

Using the TRU, especially when an application involves an operating system, avoids the need to perform a context switch when using traditional interrupts. The configuration of the TRU is a one-time event and is reusable until the developer modifies the trigger masters/slaves. Please refer to *Utilizing the Trigger Routing Unit for System Level Synchronization (EE-360)*<sup>[5]</sup> and the *ADSP-BF70x hardware reference manual*<sup>[6]</sup> for details.

# **Improving Performance Using the CCES Compiler and Debug Tools**

For many developers, C/C++ is the primary programming language. After coding, the compiler and its complementary code-generation toolchain convert the source code into an executable program. Efficient C/C++ code will make an application run faster and use less memory and power. Therefore, it is important to use an optimizing compiler such as that provided in CCES.

Most Blackfin-based applications are currently being developed using the CCES Integrated Development Environment (IDE), which contains tools for developing an application on an embedded platform, such as an editor, debugger, compiler, etc. The developer should always work with the latest version of CCES for a new project and read the *compiler manual* to understand the best use of the Blackfin+ compiler before starting development. The chapter, *Achieving Optimal Performance from C/C++ Source Code* describes many of the coding tips presented in this section.

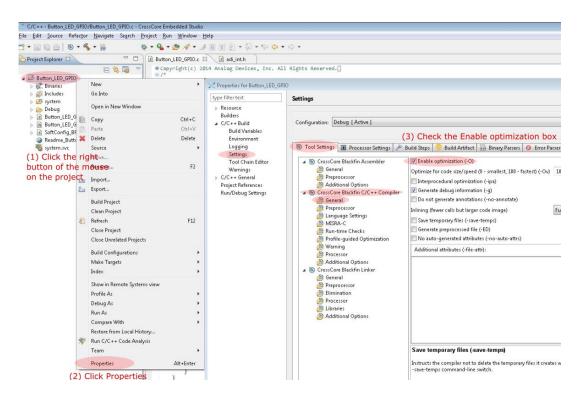

#### **Using Appropriate Compiler Configurations**

The first step for generating efficient assembly code is to enable optimization in the compiler. This achieves good performance with minimum effort. To enable optimization, as shown in Figure 3, right-click the project name in the **Project Explorer** window, then click **Properties** in the pop-up menu. Check the **Enable Optimization** box in C/C++ Build  $\rightarrow$  Settings  $\rightarrow$  Tool Settings  $\rightarrow$  CrossCore Blackfin C/C++ Compiler  $\rightarrow$  General. By default, the compiler optimizes the application for the fastest performance.

Figure 3. Enabling Compiler Optimization

For a complex application, smaller code size may be preferred versus optimal performance so that the processor can more efficiently use the processor cache (fewer cache misses). In this case, set **Optimize the code size/speed** to **0**, as shown in Figure 3.

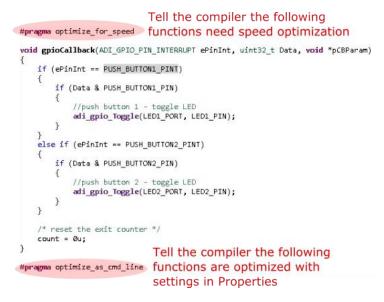

As a general principle, 80% of execution time is spent in 20% of an application's code. Therefore, in practice, the majority of the code should be optimized for size, whereas the hotspot functions should be optimized for speed. To achieve this, the developer should set the project to optimize for code size in the *Project* **Properties** but set specific source files to optimize for speed in the *File* **Properties** (right-click the source file name instead of the project name to bring up the file-specific options). If specific functions within a file require different optimization settings, **DO NOT** change the *File* **Properties**. Instead, add a pragma before the functions that need an optimization strategy that differs from the project settings, as shown in Listing 1. The **optimize\_for\_speed** pragma instructs the compiler to optimize the functions for maximum speed. **DO NOT** forget to add **#pragma optimize\_as\_cmd\_line** after the last line of the functions that need speed optimization, otherwise the subsequent functions that are supposed to be optimized for size will be

optimized for speed. For the example in <u>Listing 1</u>, **#pragma optimize\_for\_space** does the same as **#pragma optimize\_as\_cmd\_line**.

Listing 1. Specifying Optimization for a Function

CCES provides two build configurations, Debug and Release. The Debug version of a program contains additional debug information and is linked to the Debug version of the system service libraries and device drivers. Debug mode disables the compiler optimization (default setting) and results in a larger and less efficient executable program. Therefore, an application should be built with the Release configuration or with optimization enabled by the compiler in the Debug configuration before starting further optimization. By default, optimization by the compiler has been enabled in the Release configuration.

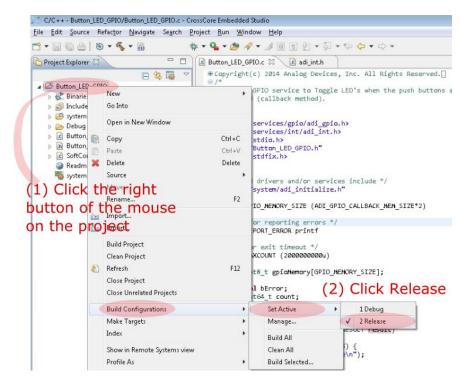

As shown in <u>Figure 4</u>, right-click the project name in the **Project Explorer** window, then click **Build Configurations**-Set Active-Release in the pop-up menu to change to the Release configuration.

Figure 4. Building in Release Configuration

#### Using the Profilers to Analyze Code Execution

Optimizing hotspot functions is a relatively quick and effective approach to improve an application's performance. CCES provides powerful profiling tools that can assist the developer to understand the core usage of each function in an application. Thus, the developer can concentrate on optimizing the hotspot functions instead of the whole application.

Generally, there are two approaches to obtaining the profiling results of an application, *statistical* profiling and *instrumented* profiling. The difference between them is that statistical profiling does not insert additional code, and recompilation is not required. The statistical profiling tool measures the performance of an application by sampling the processor's Program Counter (PC) register at random intervals while the application is running. Thus, the statistical profiling is not as accurate as the instrumented profiling. It is recommended that statistical profiling is used first, and instrumented profiling can be leveraged if the results fail to clearly identify the hotspot functions.

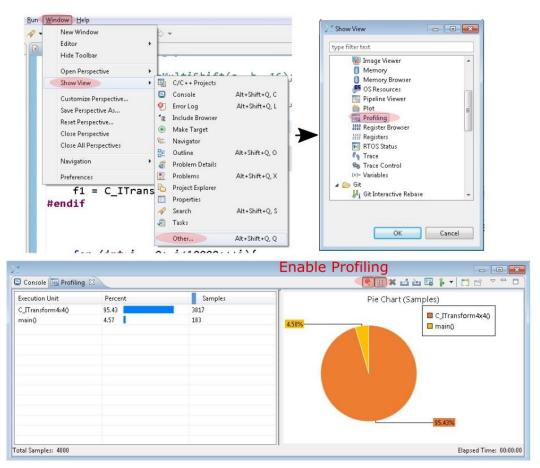

As shown in <u>Figure 5</u>, open *Profiling* in **Window→Show View→Other→Debug**.

Figure 5. Statistical Profiling

With this view opened with profiling enabled, statistical profiling will automatically run in the background after the program is loaded into the processor and run. The lower portion of Figure 5 depicts the profiling results for a fixed-point 4x4 Inverse Discrete Cosine Transform (IDCT) executed on the ADSP-BF707 EZ-Board evaluation system, indicating that the IDCT computation accounted for 95.43% of the total execution time. It should be noted that the program should run for more than 50 ms so that sufficient data can be collected for the statistical profiling tool. Please refer to the *Profiling View Help Contents* in CCES for details.

The statistical profiling tool only works in emulation mode. If profiling results are desired in simulation mode, linear profiling should be used. The major difference between the two profiling methods is that the simulator samples every PC executed and thus the linear profiling is much slower than the statistical profiling. In addition, the Blackfin+ simulator is not cycle-accurate and only provides an estimated profiling result.

To enable instrumented profiling, right-click the project name in the **Project Explorer** window, then click **Properties** in the pop-up menu. Check the box in C/C++ **Build** $\rightarrow$ **Settings** $\rightarrow$ **Tool Settings** $\rightarrow$ **CrossCore**

Copyright 2016, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Engineer-to-Engineer Notes.

**Blackfin C/C++ Compiler** $\rightarrow$ **Processor**, as shown in Figure 6. After that, build the project and run it. In this example, the IDCT was executed 400 times on the EZ-board evaluation system.

| type filter text                                                                                                                                                                                                                                | Settings                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| <ul> <li>&gt; Resource<br/>Builders</li> <li>■ C/C++ Build<br/>Build Variables<br/>Environment<br/>Logging<br/>Settings<br/>Tool Chain Editor<br/>Warnings</li> <li>&gt; C/C++ General<br/>Project References<br/>Run/Debug Settings</li> </ul> | Configuration: Debug [Active ]<br>Tool Settings Processor Settings<br>ConstCore Blackfin Assembler<br>General<br>CrossCore Blackfin Assembler<br>Additional Options<br>CrossCore Blackfin C/C++ Compiler<br>General<br>Preprocessor<br>Additional Options<br>MISRA-C<br>Run-time Checks<br>Profile-quided Optimization | Build Steps       Build Artifact       Binary Parset         Ø Enable compiler instrumented profiling (-p)         Processor speed (MHz) (-D_PROCESSOR_SPEE)         Double size         Allow mixing of sizes (-double-size-any)         Treat uninitialized global vars as         Ø CPLBs are enabled (-cplbs)         SDRAM Bank 0 is in use (-sdram)         Do not introduce saturation to integer arithm | Check the box<br>D_):<br>32-bit (IEEE single precision) (-doubl<br>zero-initialized (-decls-strong) |

Figure 6. Enabling Profiling in the Compiler Configuration Settings

To create a profiling result file, click **File** $\rightarrow$ **New** $\rightarrow$ **Code Analysis Report**, as shown in <u>Figure 7(a)</u>. Then, check **Instrumented Profiling**, as shown in <u>Figure 7(b)</u>. After that, select the path for the generated .prf file (<u>Figure 7(c)</u>).

| C/C++ - myOptimizationExample/src/myOptimizationExample.c - Cr                                                     | ossCore Embedded Studio                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Edit Source Refactor Navigate Search Target Project I                                                         | <u>R</u> un <u>W</u> indow <u>H</u> elp                                              | 🔿 Code coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                    | 🖬 CrossCore Project 🗸 🚽 🤿 א                                                          | A code coverage report contains the source definition of each profiled function in your application, the function definition's source lines, and the amount of times each source line has been executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Open File                                                                                                          | Project                                                                              | To collect Code coverage information: you must compile and run your application for Profile Guided Optimization for either simulators or hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Close Ctrl+W<br>Close All Ctrl+Shift+W                                                                             | Source Folder                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Save     Ctrl+S       Save As     Save All       Save All     Ctrl+Shift+S       Revert     Move       Move     F2 | Cource File  File File File File File File File                                      | Heap debugging     A heap debugging report contains heap size, peak usage, the amount of heap unused, and any heap operation problems, such as memory leaks.     To collect Heap debugging information: you must compile and run your application with Link against heap tracing libraries enabled.     Instrumented profiling     Check the box     An instrumented profiling report shows each profiled function name and the source file in which it is located, and the percentage of profiled time spent     executing each profiled motion in your application.     To collect Instrumented profiling information: you must compile and run your application with Compiler instrumented profiling enabled. |

| (a)                                                                                                                |                                                                                      | (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| The profiling file Output file                                                                                     | the data file: C:\Users\Iliu4\cces\2.0.0\m<br>Data file: C:\Users\Iliu4\cces\2.0.0\m | nyOptimizationExample\Release\myOptimizationExample.dxe<br>nyOptimizationExample\Release\myOptimizationExample.prf<br>nyOptimizationExample\profiling_report.html                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                    |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

(c)

Figure 7. Creating the Profiling Report

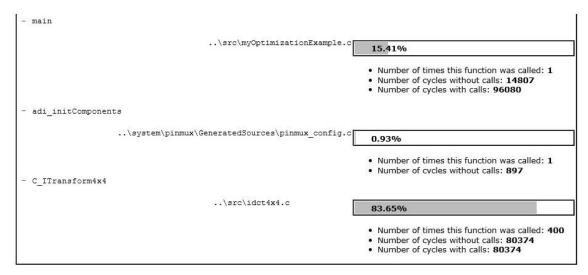

Figure 8 shows the instrumented profiling results.

Figure 8. Example Profiling Report

As can be seen, the IDCT accounted for 83.65% of the total execution time, and the hotspot function has been identified. Instrumented profiling results are based on processor cycles consumed while executing the functions. For a given function, multiple-cycle stalls incurred due to core accesses to L2/L3 memory are accounted for in the time used by the function, even though the core is stalled. As such, the cycle count may be bloated as a result of non-optimal memory placement as compared to the cycles required for the computation itself, which is something that can be improved upon with strategic management of the memory architecture when mapping code and data in the system.

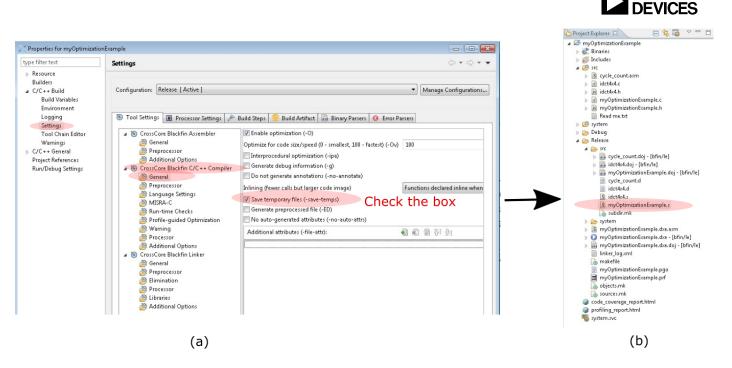

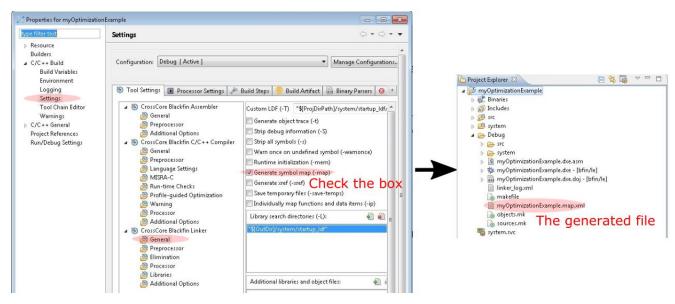

#### **Maintaining Temporary Files**

In addition to the profiling tools, CCES also allows for saving of the assembly code produced by the compiler during the project build process, which may be useful to verify if a specific function has been optimized well by the compiler or if further hand-optimization might be possible. By default, the toolchain discards these intermediary files, but overriding this behavior is possible via the project's settings. Right-click the project name in the **Project Explorer** window and click **Properties** in the pop-up menu. Check the "Save Temporary Files" box in C/C++ Build $\rightarrow$ Settings $\rightarrow$ Tool Settings $\rightarrow$ CrossCore Blackfin C/C++ Compiler $\rightarrow$ General, as shown in Figure 9(a).

Figure 9. Saving Compiler-Generated Assembly Code

When the project is rebuilt with this option enabled, the generated assembly source file having the same name as the C file but with a .s suffix, will appear in the /src folder in the debug configuration's output directory, as shown in Figure 9(b).

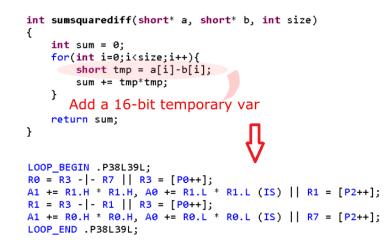

As an example where access to the intermediary assembly source file is valuable, consider a function that computes the sum of the squared difference between two vectors, as shown in <u>Figure 10</u> with the C source at the top and the equivalent compiler-produced assembly code at the bottom:

```

int sumsquarediff(short* a, short* b, int size)

{

int sum = 0:

for(int i=0;i<size;i++){</pre>

sum += (a[i]-b[i])*(a[i]-b[i]);

}

sum = \sum_{i=0}^{N-1} (x_i - y_i)^2

return sum:

}

.P38L17:

The compiler treats

the operands as 32-bit

LOOP_BEGIN .P38L17L;

R1 = W[P2++](X);

R0 = R1 - R2 (NS)

A1:0 += R3 * R3 (IS, NS) || R2 = W[P0++] (X);

R3 = R1 - R2 (NS) || R1 = W[P2++] (X);

A1:0 += R0 * R0 (IS, NS) || R2 = W[P0++] (X);

LOOP_END .P38L17L;

```

Figure 10. C and Assembly Code for the sumsquareddiff() Function

ANALOG

While it looks concise, the assembly code is actually not optimally efficient despite the fact that compiler optimization is enabled. The following sections will address optimizing this example to achieve better performance.

#### Helping the Compiler to Understand C/C++ Code

As mentioned previously, data types are compiler-dependent. For Blackfin+ processors, *char*, *short* and *int* data types are 8-, 16-, and 32-bit, respectively. The C code in Figure 10 utilizes *short* and *int*, which can be considered a typical implementation for this sum of squared differences routine. The corresponding assembly code consists of four math instructions – two subtractions and two multiply-accumulates. In practice, the result of a 16-bit multiplication is a 32-bit number. However, the assembly code uses A1:0, two accumulators (40-bit A1 and 40-bit A0) to store the result. This is because the code implicitly uses a 32-bit multiplication, and the compiler therefore uses A1:0 (80-bit) to store a 64-bit result. In other words, the assembly code wastes half of a valuable computing resource.

A common issue that prevents the compiler from optimizing things efficiently is that it cannot predict if an intermediate result (such as the one from the subtraction in Figure 10) can safely inherit the operand's data type. If it cannot prove that such computations do not overflow, it must use the type defined by the C standard. The subtraction result in Figure 10 will be a 32-bit number when the operands are large positive or negative numbers. For example, for two operands, 0x6666 (26214) and 0x8001 (-32767), the result cannot be represented by a signed 16-bit integer.

A quick way to make the compiler aware of the fact that the math operations are 16-bit is to add a temporary 16-bit variable to store the intermediate subtraction result to, as shown in <u>Figure 11</u>.

Figure 11. Optimized C/ASM Code for the Example

Consequently, as can be seen in the generated assembly source, the math operations are 16-bit, and the compiler can issue two 16-bit multiplications in parallel.

The purpose of this example is to remind the developer of the importance of carrying out three suggestions while writing/optimizing C code:

- 1. Know the maximum or minimum values of variables.

- 2. Choose appropriate data types for variables.

- 3. Examine the generated assembly code during optimization.

#### **Native Fixed-Point Types**

As mentioned in the <u>Introduction</u>, Blackfin+ processors support fractional numbers, which are not defined in standard C. Thus, in practice, fractional numbers are often stored as *short* (16-bit) or *int* (32-bit) data type. However, a better technique for functions that involve fractional numbers is to use the native fixedpoint types supported by the compiler so that the compiler can better understand C code and has a better chance of generating more efficient assembly code. Refer to the *Compiler Manual* for details about fractional numbers.

Again consider the function in Figure 10, except this time with knowledge of the input and output actually being fractional data, where the input pointers (*short* \*) actually point to two fractional arrays rather than to integer arrays. The *fract* data type is a 16-bit signed fractional type (one sign bit and 15 fractional data bits), and the *accum* data type is a 40-bit signed fractional type (nine sign bits and 31 fractional data bits). If the function is now modified to utilize these data types, the optimal fractional format math will be performed on the processor, as shown in Figure 12.

```

int sumsquarediff(short* a, short* b, int size)

{

Use native fixed point types:

fract and accum

fract * fr_a = (fract *) a;

fract * fr_b = (fract *) b;

accum sum = 0;

for(int i=0;i<size;++i){</pre>

sum += (fr_a[i]-fr_b[i])*(fr_a[i]-fr_b[i]);

return bitslr((long fract) sum);

}

LOOP_BEGIN .P38L19L;

R2.L = R1.L - R2.L (S) || R0 = W[P2++] (X);

A0 += R3.L * R3.L || R1 = W[P0++] (X);

R3.L = R0.L - R1.L (S) || R1 = W[P2++] (X);

A0 += R2.L * R2.L || R2 = W[P0++] (X);

LOOP END .P38L19L;

```

Figure 12. Optimizing C Code Using Native Fixed-Point Data Types

This example demonstrates that the native fixed-point data type can help the compiler to understand the computation. However, only one multiplier and accumulator is used in the assembly code, as shown in Figure 12. Further optimization can be done so that the assembly code is as efficient as that shown in Figure 11.

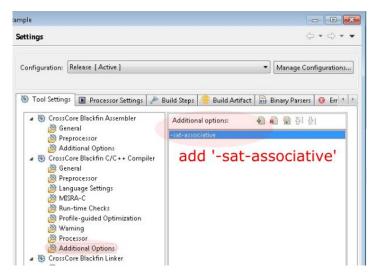

#### **Vectorizing the Accumulation**

The compiler usually does not vectorize fractional accumulations unless it is told that simultaneously using two accumulators is safe. In other words, only using the native fixed-point types may not generate the best assembly code. To vectorize the accumulators, saturating arithmetic (as used in fractional arithmetic) should specifically be allowed to be reordered. This is selectable in the compiler settings by selecting the Additional Options page of the C/C++ Build  $\rightarrow$  Settings  $\rightarrow$  Tool Settings  $\rightarrow$  CrossCore Blackfin C/C++ Compiler tree under the project properties page and keying in "-sat-associative", as shown in Figure 13.

Figure 13. Adding Compiler Option to Vectorize the Accumulators

When the project is subsequently rebuilt, the assembly code is updated, as shown in Listing 2.

```

LOOP_BEGIN .P38L41L;

R0 = R3 -|- R7 (S) || R3 = [P0++];

A1 += R1.H * R1.H, A0 += R1.L * R1.L || R1 = [P2++];

R1 = R3 -|- R1 (S) || R3 = [P0++];

A1 += R0.H * R0.H, A0 += R0.L * R0.L || R7 = [P2++];

LOOP_END .P38L41L;

```

Listing 2. Optimized Assembly Code with -sat-associative Option Enabled

Note that the code in Listing 2 is not exactly the same as that in Figure 11, as the assembly instruction utilize different instruction modifiers (suffixes), which have different meanings in the computation. Please refer to the *Instruction Set Reference* pages in the *Blackfin+ Programming Reference* for details.

#### **Impact of Assembly Instruction Suffixes**

For Blackfin+ processors, a fractional number and a *short* integer, which have the same number of bits, represent totally different values. For example, 0x1000 (16-bit) is 4096 (integer) or 0.125 (fractional). The compiler generates assembly code based on the data types of variables and utilizes instruction suffixes to differentiate operands' data types. Thus, the same instruction with different suffixes yields different results. As a comparison, the multiply-accumulate operation in Figure 11 is identical to that of the same compiler-generated code of Listing 2 except for the suffix, as highlighted in Figure 14.

short tmp = a[i]-b[i]; sum += tmp\*tmp; Different suffix A1 += R1.H \* R1.H, A0 += R1.L \* R1.L (IS) sum += mult\_fr1x32(a[i]-b[i],a[i]-b[i]); A1 += R1.H \* R1.H, A0 += R1.L \* R1.L

#### Figure 14. Comparing ASM Instructions Produced By Compiler

The (**IS**) suffix indicates that the operands are signed integers. The difference between these two assembly instructions is that the instruction without the suffix is multiplying two fractional numbers, which means that the unscaled result will be in the format 2.30 (with two sign bits and 30 fractional data bits). As such, the 1.31 fractional format output is left-shifted by one bit, thus doubling the result. This behavior lends itself to a trick for a specific integer math operation where a multiplication is followed by a 1-bit left shift, such as the code in Figure 15.

| <br>int sumMultiShift(short* a, short* b, int size)<br>{                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------|

| <pre>int sum = 0;<br/>for(int i=0;i<size;i++){<br>int tmp = a[i]*b[i];<br/>sum += tmp&lt;&lt;1;<br/>}</size;i++){<br></pre> |

| }                                                                                                                           |

| LOOP_BEGIN .P38L30L;<br>A1 += R0.H * R1.H, A0 += R0.L * R1.L    R0 = [P1++]    R1 = [P0++];<br>LOOP_END .P38L30L;           |

Figure 15. C and Assembly Code for Multiplication Followed by 1-bit Left Shift

As can be seen, the compiler automatically optimizes the C code to a single assembly instruction.

#### **Using Built-In Functions**

The compiler includes a set of built-in functions that facilitate the generation of efficient code. For example, there is a built-in function associated with the multiply-accumulate used in Figure 11 called **mult\_fr1x32(**), as shown in Figure 16:

int sumsquarediff(short\* a, short\* b, int size)

{

fract32 sum = 0;

for(int i=0;i<size;++i){

sum += mult\_fr1x32(a[i]-b[i],a[i]-b[i]);

}

Call builtin function

return sum;

}

LOOP\_BEGIN .P38L41L;

R0 = R3 -|- R7 || R3 = [P0++];

A1 += R1.H \* R1.H, A0 += R1.L \* R1.L || R1 = [P2++];

R1 = R3 -|- R1 || R3 = [P0++];

A1 += R0.H \* R0.H, A0 += R0.L \* R0.L || R7 = [P2++];

LOOP\_END .P38L41L;</pre>

Figure 16. Using Compiler Built-In Functions

As can be seen, the compiler-produced assembly code is fully optimized, as expected. Refer to the *compiler manual* for details regarding all the supported built-in functions.

Built-in functions are compiler-dependent and are not portable to other platforms.

#### Using the Optimized DSP Run-Time Library

A number of DSP functions have been implemented and optimized for Blackfin+ processors. Before developing an algorithm, it is good practice to first search the CCES tools installation to determine if the basic functions of the algorithm have been included in the DSP run-time library. Using the optimized DSP run-time functions will save lots of development time and avoid the need for time-consuming optimization. Functions contained in the DSP run-time library include **Fast Fourier Transforms**, **Finite/Infinite Impulse Filters**, **Matrix** computations, **Convolution**, **Statistics**, etc. Refer to the *compiler manual* for more details.

#### **Improve Iteration Efficiency**

A common feature of many hotspot functions is that they contain loops that are iterated numerous times. An insignificant improvement for a single loop iteration may accumulate to become a significant opportunity for performance improvement when the iteration is executed many times. For example, if conditional code exists in the iteration, the performance improvement resulting from such an optimization may be more significant when considering the number of times the code is executed. Thus, conditional code should be avoided in loop bodies, especially in inner loops.

Blackfin+ processors support two levels of zero-overhead hardware loops. This feature is utilized when the number of iterations for a loop – or "trip count" – can be computed before the loop starts. Otherwise, the compiler utilizes "*jump*" instructions to implement the loop.

The C code in <u>Figure 11</u> is applicable for any number of loop iterations. If the trip count is a known value or in a range, specifying it in the C code will enable the compiler to make more reliable decisions about the optimization strategy for the loop, such as allowing the loop to be partially unrolled or vectorized. A set of pragmas can be used to provide the compiler with more information about a loop (refer to the *compiler manual* for details). Some of the relevant pragmas are:

- **#pragma loop\_count(min, max, modulo)** informs the compiler of the minimum and maximum trip counts of the loop, as well as a number known to exactly divide the trip count

- **#pragma different\_banks** informs the compiler that parallel accesses can occur concurrently because data is in different memory banks

- **#pragma no\_alias** informs the compiler that no load or store operation within the body of the loop accesses the same memory

In most cases where a C function calls another function, a few lines of assembly code are required and are inserted to store values in scratch registers before entering a sub-function and to restore the registers' values after returning from the sub-function. This means that extra cycles are needed to complete the required context switch, which means that calling sub-functions inside a loop will somewhat degrade performance. As such, the compiler will try to avoid generating a hardware loop if the loop body contains a function call. Therefore, it will improve performance to expand small functions within loop bodies whenever possible or to use the "*inline*" qualifier to tell the compiler to try to inline those functions.

#### Using the volatile ANSI C Extension

During optimization, the compiler assumes that variables' values are not changed unless they are explicitly modified in the code. This means that values can be loaded from memory in advance and reused if they are known to be static between uses. However, for variables storing data from the peripherals, values in memory may be written in a way that is not detectable by the compiler. Writes to such variables may also occur in interrupt handlers, which again cannot be seen by the compiler's optimizer. To avoid the compiler using stale values, the *volatile* ANSI C extension must be used when declaring such implicitly-modified variables. The same is true for variables such as loop counters, which can be initialized in the loop's construct and not modified anywhere other than in the loop definition. As the counter is not used nor modified anywhere else, the optimizer can remove it unless instructed not to by the *volatile* extension. This concept, as well as several other common issues occurring when optimization is enabled, is discussed in the FAQ entitled "Why does my code stop working when I enable optimization?"<sup>[9]</sup> in Analog Devices' Engineer Zone.

#### **Avoid Division**

Division on Blackfin+ processors is emulated by software and takes multiple cycles to complete (>12). Thus, division operations should be avoided whenever possible. For binary divisors (2, 4, 8, ...,  $2^{31}$ ), the compiler replaces the division with a single-cycle shift operation. It may also replace a division by a sequence of multiplications when the divisor is a known value.

#### **Optimizing an Application Using Blackfin+ Assembly Code**

Writing assembly language should be considered to be the last resort when optimizing an application. This technique is not recommended unless the compiler does not generate efficient enough assembly code after the above optimization approaches have been applied. In most cases, only a small proportion of application functions might benefit by being written in assembly code. Although this note does not cover algorithm optimization, this should be performed prior to trying to write assembly code.

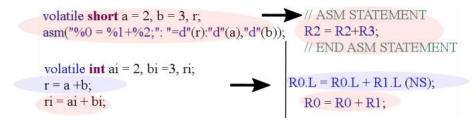

In general, there are two approaches to using assembly language in an application, either indirectly writing assembly-like code in a C/C++ source file or directly writing assembly code in a dedicated assembly source file. This note will only cover the former, as the latter requires a deeper understanding of Blackfin+ programming skills.

The asm() ANSI C extension allows assembly instructions to be dropped in situ into the compiler's output from within the structure of an otherwise fully C/C++ source file. Although this technique is easier than directly writing a full module in assembly code, it is important to take care to avoid creating bugs at the assembly level or within the C run-time environment, as the compiler is largely unaware of the text being inserted inside the asm() construct. If the text inside the construct contains a syntax error, it will be flagged as such when parsed by the assembler during the project build. However, concepts such as register utilization, data type matching, and the C/Assembly interface must be considered when creating this code, as the compiler is unaware of how this assembly code will behave when inserted into the compiler-generated assembly code output.

For example, the code in Figure 17 calculates the sum of two integers.

Figure 17. Example asm() Construct

Although the variables a, b and r are declared as *short int* (16-bit data), the asm() construct specifies the registers as 32-bit by using the d designator (directing the compiler to use a data register). Thus, variables a and b occupy the whole 32-bit data registers R2 and R3 (pink ellipses). In contrast, the compiler correctly understands the C code and utilizes only the lower 16-bit halves of the data registers (blue ellipses).

To correct this issue, the asm() construct should be written as asm("%0 = %1 + %2;":"=H''(r):"H''(a),"H''(b));. The "H" asks the compiler to only use the lower/higher 16-bit half of a data register rather than the whole 32-bit register. Please refer to the CCES On-Line Help *Inline Assembly Language Support Keyword (asm)* topic for details about the asm() ANSI C extension syntax.

# **Memory Optimization**

To obtain a highly efficient program, optimizing algorithms/code is only a portion of the effort. Utilizing placement of data/instructions in memory to take full advantage of the architecture also plays an important role in improving overall application performance. As covered previously, the profiling tool should be used to identify hotspot functions before starting memory optimization. If the compiler-generated assembly code for those functions has been optimized to the extent where additional efforts will only gain marginal improvement, it is time to consider optimizing the system memory map for the application. The primary principle of memory optimization is to allocate memory for instructions and data based on their importance. The most frequently executed instructions and accessed data should be loaded into L1 memory wherever possible. If there is not enough space in L1 memory, L2 memory should be used next, followed lastly by L3 memory.

#### **Cache Management**

ADSP-BF707 processors have a 64 KB region of memory for each of data and instructions, plus an 8 KB scratchpad memory for data, as shown in <u>Figure 2</u>. 32KB of data memory and 16 KB of instruction memory can be configured as cache. For a complex application, enabling both of these caches should significantly improve its performance.

The cache can be configured in CCES by double-clicking the *System Configuration* (**system.svc**) file in the **Project Explorer**. If the **Startup Code/LDF** tab at the bottom of the window is active, the cache settings are accessible via the **Cache Configuration** tab on the left, as shown in <u>Figure 18</u>.

| Project Explorer 🛛 📃 🗖                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | imyOptimizationExample.c                                 | 🍯 *myOptimizationExample/system.svc 🛛                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------|

| □ 🕏 🗟 🔻                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Startup Code/LDF                                         |                                                                                     |

| GenerationExample     GenerationExample     Generation     Ge | Code Generation Options<br>These options control the gen | eration of the Startup Code and LDF                                                 |

| Bebug     Best                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Startup Code                                             | Startup Code Configuration                                                          |

| <ul> <li>jo jo j</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Cache Configuration                                      | Cache and Memory Protection,<br>De Instruction and data cache<br>Instruction cache: |

| myOptimizationExample.d.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LDF                                                      | Enable instruction cache                                                            |

| linker_log.xml                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          | Data cache:                                                                         |

| objects.mk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          | Enable data cache on banks A and B                                                  |

| sources.mk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          | Cache mapping set size:                                                             |

| system.svc (2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ) Choose small                                           | Small: 16 KB 👻                                                                      |

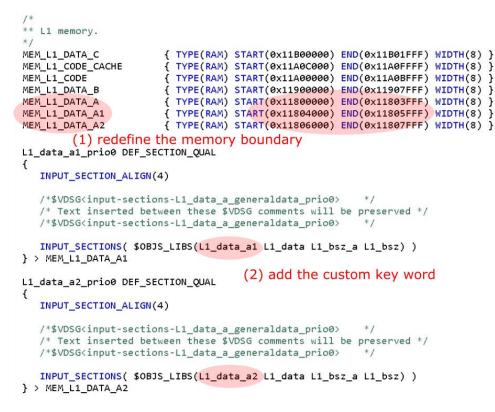

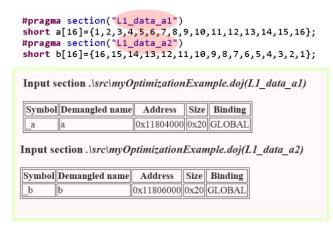

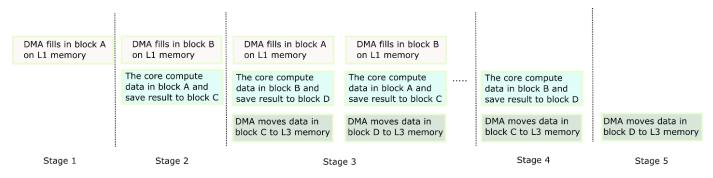

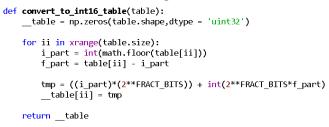

| No. and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          | Permit alteration of CPLB Table entries<br>Data cache mode:                         |