# AN-1507 **APPLICATION NOTE**

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### Stable, Closed-Loop, Automatic Power Control for RF Applications

#### **CIRCUIT FUNCTION AND BENEFITS**

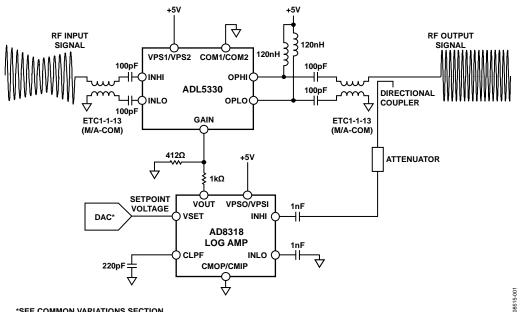

The circuit shown in Figure 1 provides closed-loop, automatic power control using a variable gain amplifier (VGA), ADL5330, and a log detector, AD8318. Due to the high temperature stability of the AD8318, this circuit provides stability over temperature because the AD8318 radio frequency (RF) detector ensures the

same level of temperature stability at the output of the ADL5330 VGA. The addition of the log amp detector converts the ADL5330 from an open-loop variable gain amplifier to a closed-loop output power control circuit. Because the AD8318, like the ADL5330, has a linear in dB transfer function, the output power (POUT) vs. the setpoint transfer function also follows a linear in dB characteristic.

\*SEE COMMON VARIATIONS SECTION

Figure 1. ADL5330 Operating in an Automatic Gain Control Loop in Combination with the AD8318 (Simplified Schematic: Decoupling and All Connections Not Shown)

### **TABLE OF CONTENTS**

| Circuit Function and Benefits | 1 |

|-------------------------------|---|

| Revision History              | 2 |

| Circuit Description           | 3 |

| Common Variations | .4 |

|-------------------|----|

| References        | .4 |

#### **REVISION HISTORY**

#### 11/2017—Rev. B to Rev. C

| Document Title Changed from CN0050 to AN-1507 Univers | sal |

|-------------------------------------------------------|-----|

| Changes to Figure 1                                   | . 1 |

| Changes to Circuit Description Section                | . 3 |

| Changes to Common Variations Section                  | .4  |

#### 9/2010-Rev. A to Rev. B

| Changes to Figure 1                    | 1 |

|----------------------------------------|---|

| Changes to Circuit Description Section | 3 |

| Changes to Common Variations Section   | 3 |

#### 11/2009-Rev. 0 to Rev. A

| Updated Format                | Universal |

|-------------------------------|-----------|

| Changes to Circuit Note Title | 1         |

#### 10/2008—Revision 0: Initial Version

#### **CIRCUIT DESCRIPTION**

Although the ADL5330 VGA provides accurate gain control, precise regulation of output power can be achieved with an automatic gain control (AGC) loop. Figure 1 shows the ADL5330 operating in an AGC loop. The addition of the AD8318 log amp allows the AGC to have improved temperature stability over a wide output power control range.

To operate the ADL5330 VGA in an AGC loop, a sample of the output RF must be fed back to the detector (typically using a directional coupler and additional attenuation). A setpoint voltage is applied by a digital-to-analog converter (DAC) to the VSET input of the detector, and the VOUT pin is connected to the GAIN pin of the ADL5330. Based on the defined linear in dB relationship of the detector between the VOUT pin and the RF input signal, the detector adjusts the voltage on the GAIN pin (the VOUT pin of the detector is an error amplifier output) until the level at the RF input corresponds to the applied setpoint voltage. The GAIN pin settles to a value that results in the correct balance between the input signal level at the detector and the setpoint voltage.

The basic connections for operating the ADL5330 in an AGC loop with the AD8318 are shown in Figure 1. The AD8318 is a 1 MHz to 8 GHz, precision, demodulating, logarithmic amplifier. It offers a large detection range of 60 dB with  $\pm$ 0.5 dB temperature stability. The gain control pin of the ADL5330 is controlled by the output pin of the AD8318. This voltage, V<sub>OUT</sub>, has a range of 0 V to approximately VPS1/VPS2. To avoid overdrive recovery issues, the AD8318 output voltage can be scaled down using a resistive divider to interface with the 0 V to 1.4 V gain control range of the ADL5330.

A coupler with an attenuation of 23 dB is used to match the desired maximum output power from the VGA to the top end of the linear operating range of the AD8318 (at approximately -5 dBm at 900 MHz).

The error amplifier of the detector uses CLPF, a ground referenced capacitor pin, to integrate the error signal (in the form of a current). A capacitor must be connected to CLPF to set the loop bandwidth and to ensure loop stability.

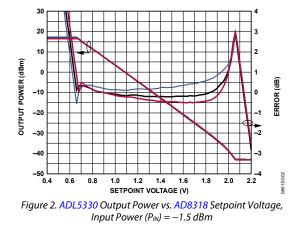

Figure 2 shows the transfer function of the output power vs. the VSET voltage over temperature for a 900 MHz sine wave with an input power of -1.5 dBm. Note that the power control of the AD8318 has a negative sense. Decreasing the V<sub>SET</sub> voltage, which corresponds to demanding a higher signal from the ADL5330, tends to increase the gain.

The AGC loop is capable of controlling signals just under the full 60 dB gain control range of the ADL5330. The performance over temperature is most accurate over the highest power range, where it is generally most critical. Across the top 40 dB range of output power, the linear conformance error is well within  $\pm 0.5$  dB over temperature.

The broadband noise added by the logarithmic amplifier is negligible.

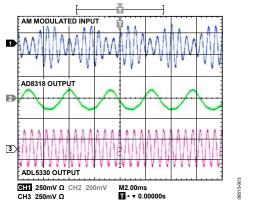

For the AGC loop to remain in equilibrium, the AD8318 must track the envelope of the ADL5330 output signal and provide the necessary voltage levels to the ADL5330 gain control input. Figure 3 shows an oscilloscope measurement of the AGC loop depicted in Figure 1. A 100 MHz sine wave with 50% amplitude modulation (AM) is applied to the ADL5330. The output signal from the ADL5330 is a constant envelope sine wave with amplitude corresponding to a setpoint voltage at the AD8318 of 1.5 V. Figure 3 also shows the gain control response of the AD8318 to the changing input envelope.

Figure 3. Oscilloscope Showing an AM Modulated Input Signal

## AN-1507

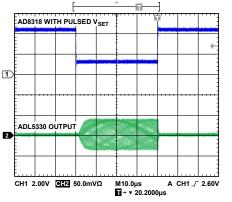

Figure 4 shows the response of the AGC RF output to a pulse on the VSET voltage. As VSET decreases to 1 V, the AGC loop responds with an RF burst. The response time and the amount of signal integration are controlled by the capacitance at the AD8318 CLPF pin. This function is analogous to the feedback capacitor around an integrating amplifier. An increase in the capacitance results in slower response time.

Figure 4. Oscilloscope Showing the ADL5330 Output

The circuit must be constructed on a multilayer printed circuit board (PCB) with a large area ground plane. Proper layout, grounding, and decoupling techniques must be used to achieve optimum performance (see the MT-031 Tutorial, the MT-101 Tutorial, and the EVAL-ADL5330 and EVAL-AD8318 evaluation board layouts).

On the bottom of the ADL5330 and AD8318 chip scale packages, there is an exposed compressed paddle. This paddle is internally connected to the ground of the chip. Solder the paddle to the low impedance ground plane on the printed circuit board to ensure specified electrical performance and to provide thermal relief. It is also recommended that the ground planes on all layers under the paddle be stitched together with vias to reduce thermal impedance.

#### **COMMON VARIATIONS**

This circuit can be used to implement a constant power out function (fixed setpoint with variable input power) or a variable power out function (variable setpoint with fixed or variable input power). If a lower output power control range is desired, the AD8318 log amp (60 dB power detection range) can be replaced with either the AD8317 (50 dB power detection range) or the AD8319 (45 dB power detection range). For a constant output power function, the lowest dynamic range detector (AD8319) is adequate because the loop always servos the detector input power to a constant level.

The ADL5330 VGA, which is optimized for transmit applications, can be replaced by the AD8368 VGA. The AD8368 is optimized for receive low application frequencies of up to 800 MHz and provides 34 dB of linear in dB voltage controlled variable gain.

There are a number of DACs suitable for this application. All of the following DACs have internal references: the AD5660/AD5640/AD5620 single 16-bit/14-bit/12-bit DACs, the AD5663R/AD5643R/AD5623R dual 16-bit/14-bit/12-bit DACs, and the AD5664R/AD5644R/AD5624R quad 16-bit/14-bit/12-bit DACs.

#### REFERENCES

- Dana Whitlow, Design and Operation of Automatic Gain Control Loops for Receivers in Modern Communications Systems, Analog Devices Wireless Seminar, Chapter 8, 2006.

- MT-031 Tutorial, *Grounding Data Converters and Solving the Mystery of "AGND" and "DGND,"* Analog Devices.

- MT-073 Tutorial, *High Speed Variable Gain Amplifiers*, Analog Devices.

- MT-077 Tutorial, Log Amp Basics, Analog Devices.

- MT-078 Tutorial, High Speed Log Amps, Analog Devices.

- MT-101 Tutorial, Decoupling Techniques, Analog Devices.

©2008–2017 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. AN08515-0-11/17(C)