## III: 非線形回路を理解する

### 3-1 対数回路

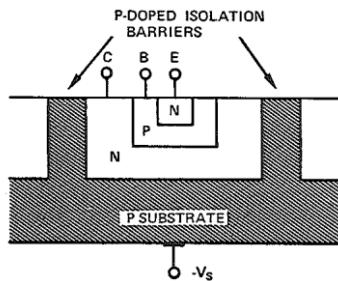

現代の対数回路は、ほぼ例外なくシリコン接合デバイス固有の対数特性を利用しています。IC 上で対として構成され簡単に入手できるこれらのデバイスは、温度変動に対して容易に補償でき、低コストで、通常  $10^{-2}$  A ~  $10^{-1}$  A の広いダイナミックレンジが得られることが特徴です。

この章では、これらのデバイスの基本的な特性、熱安定性と動的安定性の両方を得るための手法、よく使われるいくつかの回路、仕様と定義、および調整とテストの方法について説明します。

#### 基本的な検討事項

「理想対数ダイオード」の特性は、電流と電圧の関係によって評価されます。

$$I = I_o (e^{qV/kT} - 1) \quad (1)$$

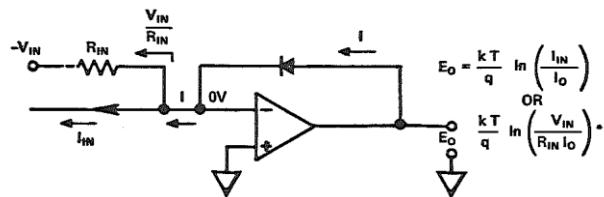

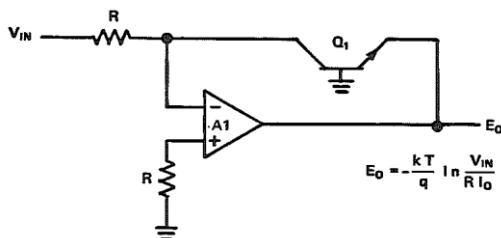

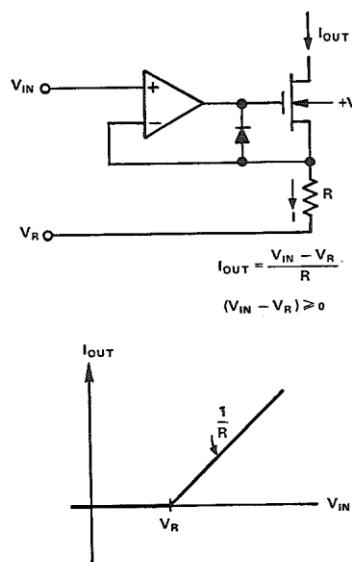

オペアンプの帰還パスに接続された理想対数ダイオードは（図 1）、出力電圧を次式の値に制限します。

$$E_o = \frac{kT}{q} \ln(I/I_o) = \frac{kT}{q} \ln(10) \cdot \log(I/I_o) \quad (2)$$

ただし、 $I/I_0 \gg 1$  とします。

$q$  は単位電荷  $1.60219 \times 10^{-19} C$  に等しい定数

$k$  はボルツマン定数、 $1.38062 \times 10^{-23} J/K$

$T$  は絶対温度、 $K = ^\circ C + 273.15$

$I_0$  は  $E_0 (= V) = 0$  の時の外挿電流

室温付近の代表的な丸めた数値は以下の通りです。

| $^\circ C$ | $T(K)$ | $\frac{kT}{q}$ | $\frac{kT}{q} \ln(10)$ |

|------------|--------|----------------|------------------------|

| 24.21      | 297.36 | 25.62mV        | →59. mV                |

| →25.       | 298.15 | 25.69mV        | 59.16mV                |

| 26.85      | →300.  | 25.85mV        | 59.52mV                |

| 28.58      | 301.73 | →26. mV        | 59.87mV                |

| 29.25      | 302.4  | 26.06mV        | →60. mV                |

したがって、 $25^\circ C$  での  $I$  の変化が  $10:1$  の時の  $E_0$  の変化は  $59.16mV$  で、 $I$  の変化が  $e:1$  ( $2.7183$ ) の時の  $E_0$  の変化は  $25.69mV$  です。

このようなダイオードは非常に役に立ちます。ダイオードは 2 端子デバイスなので、バイポーラ電流に使用できます。また、いくつか直列に積み重ね、より大きな電圧を得ることができ、グラウンドから離れた電圧で使用可能です。残念ながら、2 端子デバイスとして市販されているほとんどのダイオードは、対数動作の範囲が限られています。上端では、大きいオーム抵抗によって追加の電圧降下が生じます。

$$V = \frac{kT}{q} \ln(I/I_0) + IR_B \quad (3)$$

下端では、次式のように、傾きの乗数  $m^*$  ( $1 \leq m \leq 4$ ) が 1 回あるいは複数回変化します。

$$V = m \frac{kT}{q} \ln(I/I_0) \quad (4)$$

$m$  の大きさと、傾きが変化する電圧の値は、両方とも（同一ファミリー内の）個々のデバイスに依存するので、汎用ダイオードは、オーム抵抗を相殺するような回路を工夫できるとしても、1 または 2 ディケードにわたる正確な対数動作は実用的ではありません。

\* この係数は、表面反転層／チャンネルなどの拡張領域での拡散電流や、空間電荷領域内の発生と再結合のメカニズムによるものです。

また、専用ダイオードは、ダイオード接続したモノリシック・デュアル・トランジスタに価格で競合できません。

図 1: 理想対数ダイオード回路

### トランジスタダイオード構成

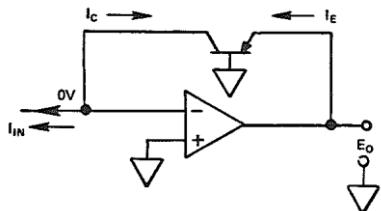

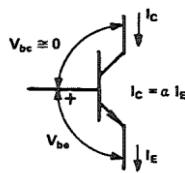

オペアンプの帰還パスに接続されたトランジスタを図 2a に示します。コレクタ電流は、入力電流または電圧によって決まります。理想オペアンプはコレクタ電流を入力電流と等しい値に維持し、コレクタ電圧をゼロに保ちます。ベース電流は独立して流れますが、ベースが接地されているので、コレクタとベースは同電位です。アンプの出力電圧はエミッタ・ベース間電圧でもあります。この電圧は、必要な量のエミッタ電流を供給する一方で、コレクタの制約を満たすのに必要な値でなければなりません。

それでは、この回路の動作を決定する関係を調べてみましょう。ベースを接地したバイポーラ・トランジスタのエミッタおよびコレクタ電流に合わせて修正した Ebers-Moll 方程式<sup>1</sup>は、次のようにになります。

$$I_E = I_{ES}(\epsilon^{qV_E/kT} - 1) - \alpha_I I_{CS}(\epsilon^{qV_C/kT} - 1) + \sum I_{ES_i}(\epsilon^{qV_E/m_i kT} - 1) \quad (5)$$

$$\begin{aligned} I_C &= -\alpha_N I_{ES}(\epsilon^{qV_E/kT} - 1) + I_{CS}(\epsilon^{qV_C/kT} - 1) \\ &\quad + \sum I_{CS_j}(\epsilon^{qV_C/m_j kT} - 1) \end{aligned} \quad (6)$$

<sup>1</sup> "Multiplication and Logarithmic Conversion by Operational-Amplifier-Transistor Circuits," by W.L.Paterson, *The Review of Scientific Instruments*, 34-12, December 1963.

ここで、

$V_E$  と  $V_C$  はエミッタ-ベース間電圧とコレクタ-ベース間電圧

$I_{ES}$  と  $I_{CS}$  は、エミッタとコレクタの飽和電流

$\alpha_N$  と  $\alpha_I$  は順方向と逆方向の電流伝達率

$m_i > 1$ 、 $m_j > 1$  は、ベース回路を流れる「収集されない」電流成分です。

a. トランジスタダイオード (PNP)

b. ダイオード接続トランジスタ\*\*。

2 端子デバイスとして、一方の極性の入力電流で動作するのは 1 種類のみ (NPN または PNP) 。

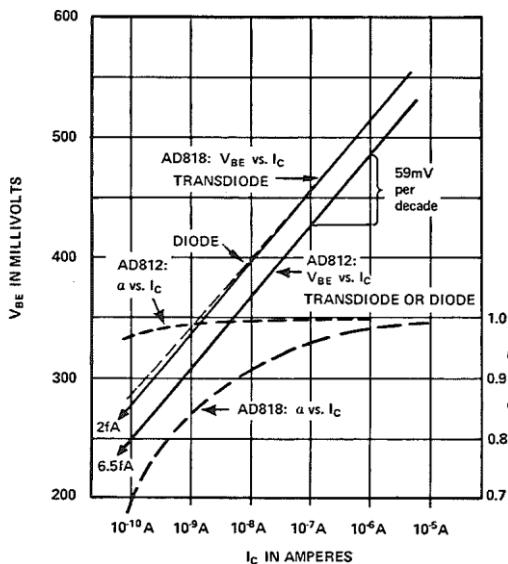

c. トランジスタダイオードとダイオードの  $V_{BE}$  および  $\alpha$  と  $I_c$  の関係

(2 種類のデュアル・トランジスタ・タイプ)

図 2: トランジスタダイオードとダイオード接続トランジスタ

図 2a の回路では、 $V_C$  がゼロに保持されるので、コレクタ電流とエミッタ電圧 (6) の関係は次のようになります。

$$I_C = -\alpha_N I_{ES} (\epsilon^{qV_E/kT} - 1) \quad (6a)$$

オペアンプがコレクタ電流を入力電流に等しくかつ反対方向に保つので、出力電圧  $V_E$  は次の値でなければなりません。

$$V_E = \frac{kT}{q} \ln(I_{IN}/I_{ES}) - \frac{kT}{q} \ln \alpha_N^* \quad (6b)$$

これは、 $I_{IN}/I_{ES} \gg 1$  の場合です。通常、対数動作に使われるほとんどのシリコン・プレーナ・トランジスタ・タイプでは、 $I_{ES}$  が  $10^{-3}$  A 以下のレベルです。したがって、(6b) の関係は非常に広い電流範囲にわたって成り立ちます。 $\alpha_N$  はほぼ 1 で、(6b) が成り立つ電流範囲では基本的に一定です。したがって、( $\ln \alpha_N$ ) 項は無視できます ( $\alpha_N = 0.99$  の場合、その寄与度は約  $1/4$ mV の一定オフセット)。この式の  $\alpha_N$  は、よく使われる接地されたベース電流のゲイン  $\alpha = I_C/I_E$  と混同しないようにする必要があります。エミッタ電流には、コレクタ電流と  $m_i > 1$  項の両方が含まれるので、 $\alpha = I_C/I_E$  (常に  $\alpha_N$  未満) はエミッタ電圧の関数です。エミッタ電圧は、低い電流値では大幅に減少します。対数回路に広く使われている 2 個のデュアル・トランジスタ・タイプの  $V_{BE}$  と  $\alpha$  のプロットを図 2c に示します。 $\alpha$  が 1 を大きく下回るような電流でも、対数応答の忠実度が優れていることに注意してください。

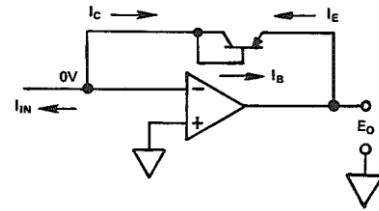

トランジスタのコレクタとベースを互いに接続すると、2 端子ダイオードが形成されます (図 2b)。それを流れる電流はエミッタ電流なので、このモデルに従えば、トランジスタの動作は (5) によって支配されます。第 1 項はコレクタ電流にほぼ等しく、第 2 項はゼロです。したがって、 $m_i > 1$  の項の和はベース電流に等しくなります。

\*PNP トランジスタの場合、入力電流  $I_{IN}$  は図示されている方向が正です。入力電流が逆方向で正の場合は、NPN トランジスタが使用されています。式 (5) と式 (6) の電流と電圧の極性は反転します。

次式により、

$$\begin{aligned} I_{IN} &= -I_C - I_B = -I_C \left[ 1 + \frac{1}{h_{FE}} \right] \\ &= \alpha_N I_{ES} (e^{qV_E/kT} - 1) \left[ 1 + \frac{1}{h_{FE}} \right] \end{aligned} \quad (7)$$

$1/h_{FE}$  を  $m_i > 1$  項の基準と見なすことは理に適っています。 (7) 式から次式が導けます。

$$V_E = \frac{kT}{q} \ln(I_{IN}/I_{ES}) - \frac{kT}{q} \ln \left[ \alpha_N \left( 1 + \frac{1}{h_{FE}} \right) \right] \quad (7a)$$

$1/h_{FE}$  は  $(1 - \alpha)/\alpha$  に等しいので、誤差項は  $+kT/q \ln(\alpha/\alpha_N)$  に等しくなります。このモデルに従えば、誤差の代表値は次のようにになります。

| $h_{FE}$             | $\alpha/\alpha_N$ | $-\frac{kT}{q} \ln(\alpha/\alpha_N)$<br>mV @ 25°C |

|----------------------|-------------------|---------------------------------------------------|

| $(\alpha_N \cong 1)$ |                   |                                                   |

| $\infty$             | 1                 | 0                                                 |

| 1000                 | 0.999             | 0.03                                              |

| 200                  | 0.995             | 0.13                                              |

| 100                  | 0.99              | 0.26                                              |

| 50                   | 0.98              | 0.51                                              |

| 19                   | 0.95              | 1.32                                              |

| 11.5                 | 0.92              | 2.14                                              |

| 9                    | 0.9               | 2.7                                               |

| 4                    | 0.8               | 5.7                                               |

| 3                    | 0.75              | 7.4                                               |

| 1                    | 0.5               | 17.8                                              |

対数ダイオードとして使用するトランジスタは  $h_{FE}$  の値が高くなればならず、広いエミッタ電流範囲にわたってその値を維持する必要があることは明らかです。トランスダイオードおよび 2 端子ダイオードとして接続した AD812 (高  $h_{FE}$  のデュアル・モノリシック・トランジスタ) と AD818 (低バルク抵抗の大型デュアル・モノリシック・トランジスタ) の比較を図 2c に示します。

AD818 は、低電流では対数ダイオードとして性能が劣るように見えますが、直列抵抗値が小さいので、1mA を超える電流では対数動作に適しており、高電流では AD812 より 1 枠以上優れています。

### その他の誤差源

$V_{CB} \neq 0$  の場合は、式 (6) のその他の項が誤差電流の原因となり、(入力電流が小さい場合特に)  $V_E$  に大きく影響することがあります。(6) から、順方向導通領域では次式が成り立ちます。

$$V_E = \frac{kT}{q} \ln \left[ \frac{I_{IN}}{\alpha_N I_{ES}} + \frac{I_{CS}}{\alpha_N I_{ES}} (\epsilon^{qV_C/kT} - 1) + \Sigma (\text{etc.}) \right] \quad (8)$$

ベースを接地したアプリケーションの場合は、アンプのオフセット電圧  $V_{OS}$  が、どの同相入力電圧とも同様にコレクタ電圧をバイアスします。ベース駆動のアプリケーションでは、 $V_{CB}$  の予想スイングと求められる低電流範囲が、そのアプリケーションに使用するデバイスに適合していることを、設計者が確認する必要があります。実効コレクタ電流誤差の大きさは、エミッタとベースを互いに接続し、電圧  $V_C$  をかけて、実験により決定できます\*。 $V_E = 0$  なので、コレクタ電流は  $V_C \neq 0$  の項からのみ構成されます。逆バイアス状態では誤差電流が非常に小さくなるので、コレクタ-ベース・ダイオードに順方向バイアスをかけた状態で行うこの測定は、ワーストケースです。過大な電流や電圧を与えないように注意する必要があります。

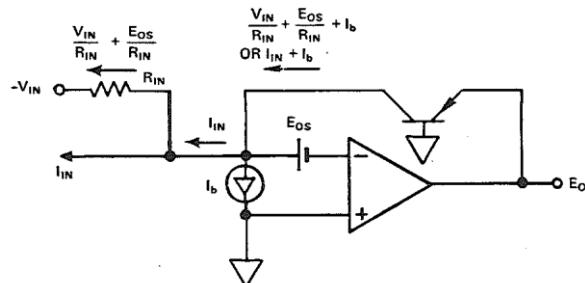

アンプのバイアス電流  $I_b$  は入力基準の線形性誤差を発生させ、出力に対数適合誤差を発生させます(図 3)。

\* PNP ワンジスタの場合  $V_{CB}$  は正で、NPN の場合は負です。

図 3: オフセット電圧誤差とバイアス電流誤差

| INPUT                         | ERROR                                                                                                           |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------|

| $\frac{I_{IN} + I_b}{I_{IN}}$ | $\frac{kT}{q} \left( \ln \left[ \frac{I_{IN} + I_b}{\alpha I_{ES}} \right] - \ln \frac{I_{IN}}{I_{ES}} \right)$ |

| 0.9                           | - 2.7 mV                                                                                                        |

| 0.99                          | - 0.26mV                                                                                                        |

| 0.999                         | -26. $\mu$ V                                                                                                    |

| 1.000                         | 0                                                                                                               |

| 1.001                         | 26. $\mu$ V                                                                                                     |

| 1.01                          | 0.26mV                                                                                                          |

| 1.1                           | 2.45mV                                                                                                          |

アンプのオフセット電圧  $E_{OS}$  は、入力抵抗の関数として帰還パスに誤差電流を発生させます ( $E_{OS}/R_{IN}$ )。この電流は、バイアス電流誤差と同じ影響を及ぼします。 $1/R_{IN} \rightarrow 0$  の時の電流源の計測では、 $E_{OS}$  の主な寄与は  $V_{CB}$  への影響を通じて現れます。

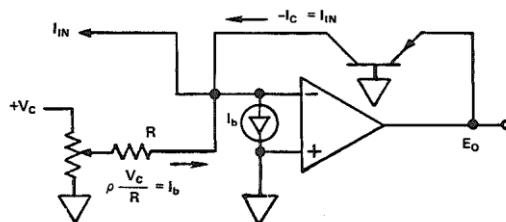

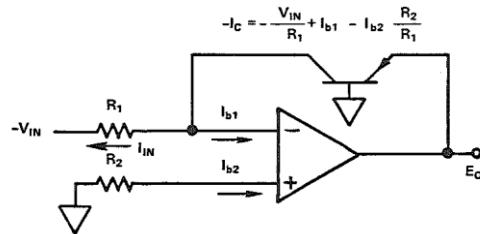

バイアス電流を減らす方法はいくつかあります。最も効果的で分かりやすいのは、適切な仕様のアンプを選ぶことです。ただし、より控えめな性能（と価格）のアンプを使うことができる可能性があります。図 4a の構成では、補償電流が合計されて、ある 1 つの温度でバイアス電流誤差をゼロにします。4b の構成では、（アンプ入力がトラッキングを行う場合）正入力と直列の補償抵抗がトラッキング・バイアス電流補償を与えます。

$$-I_C = I_{IN} + I_{b_1} - I_{b_2} \frac{R_2}{R_1} \quad (9)$$

例えば、 $I_{b1} = I_{b2}$ 、 $R_1 = R_2$ 、 $-I_C = I_{IN}$  の場合は、 $I_{b2}R_2$  が、 $V_C$  の影響が顕著になるほど大きくならないようにします。これにより、バイポーラ・トランジスタ入力のオペアンプの使用を可能にする電流レベルにとって、問題となることはほとんどありません。

a. 補償電流による  $I_b$  の影響の除去

b. 対称化による  $I_b$  の影響の除去

図 4: バイアス電流の影響の除去

オフセット電圧による電流誤差は、アンプをゼロ調整することによって 1 つの温度で（およびある程度は温度範囲で）減らすことができます。それ以外では、周囲温度を制御するか、適切な性能のアンプを指定する必要があります。 $I_{ES}$  は  $10^{-14}$  A 以下になることがあるので、オペアンプの選択については十分な検討を行うことが重要です。また、通常、対数性能範囲の下限は、アンプの入力特性と回路設計に関する設計者のスキルによって決定されるので、加算点のリーク電流の発生源に関しても十分検討する必要があります。

さらに、この他にも誤差の発生源が 2 つあります。

これらは 1 個のトランジスタや 1 個のダイオードの使用時には避け難いものですが、本章後半に述べる回路手法によって最小限に抑えることができます。これらは  $I_{ES}$  の温度変動（約  $10^{\circ}\text{C}$  の上昇ごとに 2 倍）と、温度に対する  $kT/q$  の比例特性（ $25^{\circ}\text{C}$  で  $0.33\%/\text{ }^{\circ}\text{C}$ ）で、その変化量は約  $2 \text{ mV}/\text{ }^{\circ}\text{C}$ 、つまり  $8\%/\text{ }^{\circ}\text{C}$  ( $\epsilon$  あたり) で、これは許容し難い値です。

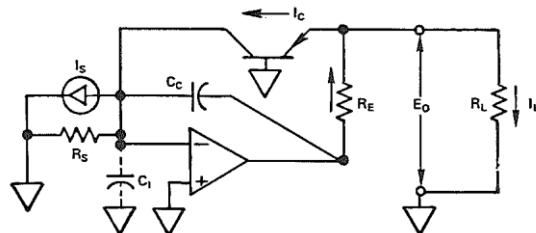

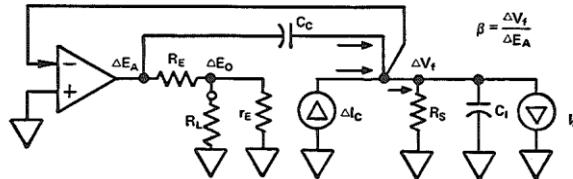

### クローズドループ安定性

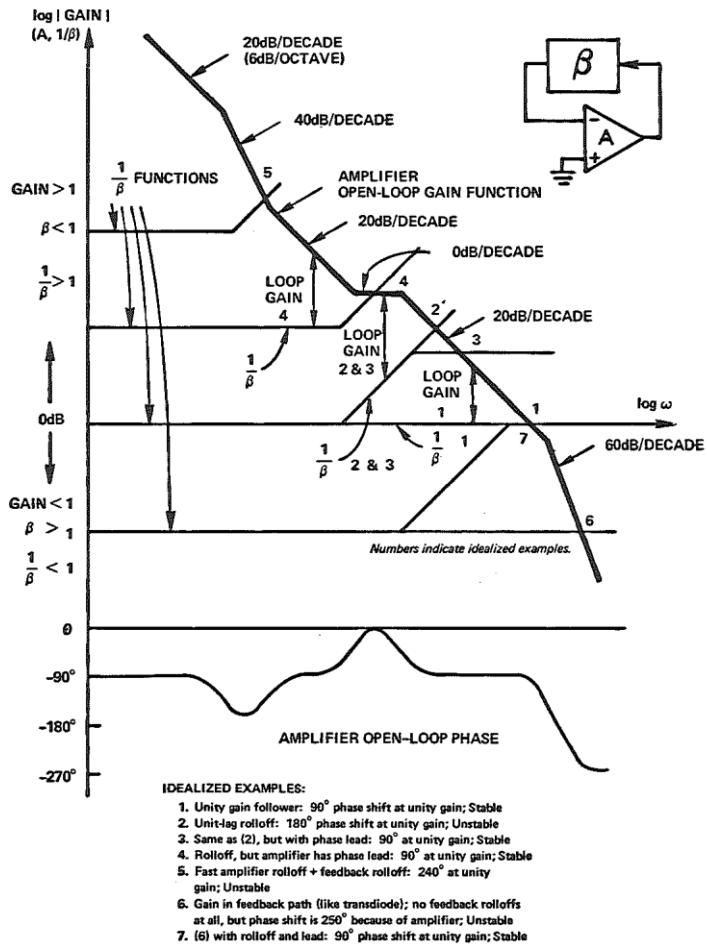

オペアンプ回路で安定性に必要な条件は、ループ・ゲイン  $A\beta$  が 1 より小さくなる周波数でループ全体の位相シフトが  $180^{\circ}$  未満であることです。最小位相の RC ネットワークを使う回路のボード線図上では、これは、 $A$  と  $\beta$  がループ・ゲイン 1 のレベルを通過する際の勾配の違いが、 $40 \text{ dB/decade}$  未満であることを示唆しています（図 5）。受動帰還部品で構成したオペアンプ回路では、 $1/\beta$  が 1 未満になることはありません。したがって、アンプのゲインが  $20 \text{ dB/decade}$  で 1 にロールオフする場合は、その回路を抵抗帰還で安定させる必要があります。

しかし、トランスタイオード接続では、帰還パス（能動パスと非線形パスの両方）が、より高い入力電流レベルで電圧ゲインを得ている場合があり、純粋な抵抗帰還（可能な場合）でも安定性を保証できないことがあります。これは、アンプのゲインが 1 を大幅に下回る周波数でユニティ・ゲイン・クロスオーバーが生じることがあり、それに伴う位相シフトも大きいためです。さらに、ゲインが信号レベルの関数であると言う事実によって、高レベルでの安定性を取るか、低レベルでの帯域幅を取るかの選択を余儀なくされることがあります。

エミッタ電圧の小さな変化に対する実効帰還アドミタンスは、次式で表されます。

$$\frac{dI_C}{dV_E} = \frac{q}{kT} I_C \cong \frac{I_C}{0.026} = \frac{1}{r_E} \quad (10)$$

上限付近のエミッタ電流とコレクタ電流はほぼ等しいので、エミッタ回路の電流は  $0.026/I_C$  です。

図 5: ループゲイン ( $A\beta$ ) が安定した状態と不安定な状態を示す

ボード線図の安定性解析。 $A\beta = A / (1/\beta)$ 。対数スケールでは

ループゲインをグラフから予測でき ( $\log A\beta = \log A - \log (1/\beta)$ ) 、

交差位置で  $0\text{ dB}$  です。数値は理想的な例を示します。

$r_E$  の範囲は極めて広く、例えば  $1\text{mA}$  で  $26\Omega$ 、 $1\text{nA}$  では  $26\text{M}\Omega$  です。したがって、この帰還素子の両端に容量を直接接続する従来の方法で回路を安定させようとするのは、非現実的です。例えば、上限で  $1.6\text{ MHz}$  のブレーク周波数を得るには、対数トランジスタに  $0.039\text{ }\mu\text{F}$  の容量を並列に接続する必要があります。

これは、下限でのブレーク周波数が 1.6 Hz であることを意味します。さらに、最大電圧がわずか 0.6 V ほどでも、アンプで  $26\Omega$  の負荷を駆動するのは簡単ではないでしょう（ほとんどのオペアンプは  $1\text{k}\Omega$  以上の負荷に対して定格が定められています）。

このジレンマに対する簡単な解決策は、アンプ出力およびエミッタと直列に抵抗  $R_E$  を接続することです（図 6）。この抵抗はアンプの負担を減らし、アンプ出力とエミッタ間の減衰器として機能します。これで、アンプ出力と加算点の間に接続された帰還コンデンサ  $C_c$  の容量をかなり小さくできますが、出力は依然としてエミッタから取られるので（かつ依然としてループによりサーボ制御されるので）、回路の応答がかなり速くなります。 $R_E$  は、アンプの出力仕様に合わせてできるだけ大きさします。この抵抗を流れる電流はエミッタ電流に負荷電流を加えた値に等しく、最大ダイオード電圧が約 0.7 V なので、10 V アンプの場合は次のようにになります。

$$R_E \cong \frac{9.3V}{I_C + I_L} \quad (11)$$

また、 $R_E$  は過大な順方向電圧から接合部を保護します。

図 6: 安定化素子  $R_E$  と  $C_c$  を使用したトランジスタダイオード回路

帰還容量の選択は、加算点容量と最大および最小電流レベルに依存します。その値は、ボード線図（図 7）から以下のようにして決定できます。

ループの帰還部分の小信号応答  $\beta = \Delta V_f / \Delta E_A$  は、次式から得ることができます。

$$\frac{\Delta V_f}{R_s} (1 + R_s C_I p) = (\Delta E_A - \Delta V_f) C_c p + \Delta I_c \quad (12)$$

ここで、

$$\Delta I_c = \frac{\Delta E_o}{r_E} = \frac{\Delta E_A}{R_E + r_E}^*$$

これを  $\beta$  について解くと、

$$\beta = \frac{\Delta V_f}{\Delta E_A} = \frac{R_s}{R_E + r_E} \frac{1 + (R_E + r_E) C_c p}{1 + R_s (C_I + C_c) p} \quad (13)$$

入力が電流源の場合は ( $R_s \rightarrow \infty$ )

$$\beta = \frac{1 + (R_E + r_E) C_c p}{(R_E + r_E) (C_I + C_c) p} \quad (14)$$

高い周波数では ( $\rho \rightarrow j\omega \gg 2\pi f_T$ )

$$\beta = \frac{C_c}{C_I + C_c} \quad (15)$$

低い周波数での電圧の場合 ( $R_s$  有限)

$$\beta = \frac{R_s}{R_E + r_E} \quad (16)$$

(式 (10) から)  $r_E$  が  $I_C$  に逆比例していることに留意すると、 $r_E$  を含む時定数は、 $I_C$  の値が小さい場合は  $r_E$  に比例し、 $I_C$  の値が大きい場合は一定 ( $\approx R_E$ ) になります。

\* 負荷抵抗がある場合は、常に、 $r_E R_E / R_L$  を  $(R_E + r_E)$  に加えることによって負荷抵抗の影響を含めることができます。

小信号を安定させるには、分子のブレーク周波数  $\omega_C = 1 / (R_E + r_E) C_C$  を、 $I_C$  の最大値で  $1/\beta = 1 + C_I/C_C$  が アンプのオープン・ループ・ゲインのプロットと交差する周波数より、少なくとも 1 オクターブ低くします（つまり  $1/2$ ）。

例えば、 $R_E = 2.2 \text{ k}\Omega$ 、 $\omega_t = 10^7 \text{ rad/s}$ 、 $C_I = 10 \text{ pF}$ 、 $r_E (@1 \text{ mA}) = 26 \Omega$  の場合は、次のようになります。

$$\frac{1}{2200C_C} = \frac{1}{2} \frac{\omega_t}{1 + C_I/C_C} \quad (17)$$

これを  $C_C$  について解くと、結果は  $88 \text{ pF}$  となります。したがって、 $100 \text{ pF}$  が妥当な値です。

a. 安定性解析用のモデル

b. ボード・ゲイン線図

図 7: トランジスタ回路のボード線図安定性解析

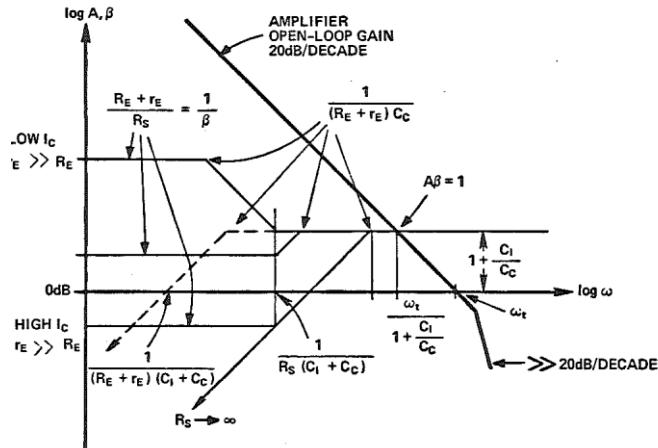

## 実用回路

これまで考えてきた基本回路は、温度の影響を受けやすいため、実用的価値はほとんどありません。また、デバイスごとに異なるリファレンス電流  $\alpha I_{ES}$  の値に出力レベルが依存している上、とにかく温度の影響を非常に受けやすく、温度が  $10^{\circ}\text{C}$  上昇するごとに出力レベルはほぼ倍になります。スケール・ファクタ  $kT/q$  は絶対温度に比例して変化し、室温 ( $27^{\circ}\text{C}$ ) 付近での変化率は  $0.33\%/\text{ }^{\circ}\text{C}$  です。

2 個のマッチングしたトランジスタ（一定のコレクタ電流と温度に対する  $V_{BE}$  のマッチング）の場合、 $\alpha I_{ES}$  項の比が温度に対して一定になる傾向があります。このため、温度に伴う  $\alpha I_{ES}$  の変動を補償するために、対数トランジスタはほぼ例外なくペアで使われます。補償は減算を行うことによって実現されます。

$$\frac{kT}{q} \ln \frac{I_1}{\alpha I_{ES_1}} - \frac{kT}{q} \ln \frac{I_2}{\alpha I_{ES_2}} = \frac{kT}{q} \left[ \ln \frac{I_1}{I_2} + \ln \frac{\alpha I_{ES_2}}{\alpha I_{ES_1}} \right] \quad (18)$$

誤差項は  $\ln(1) = 0$  に非常に近い定数です。誤差項を無視できない場合は、後続段で固定値の電圧または電流をバイアスすることによって相殺できます。

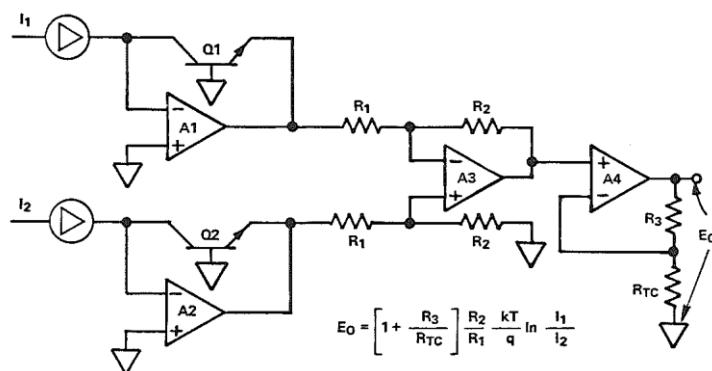

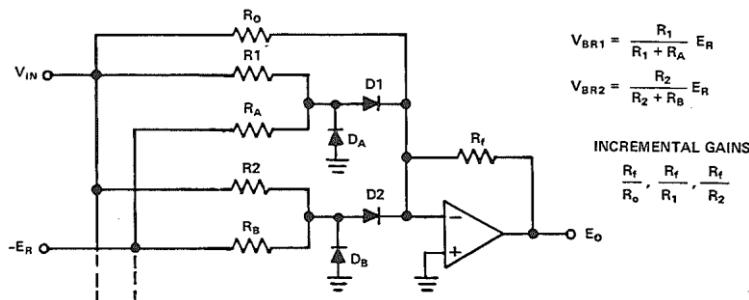

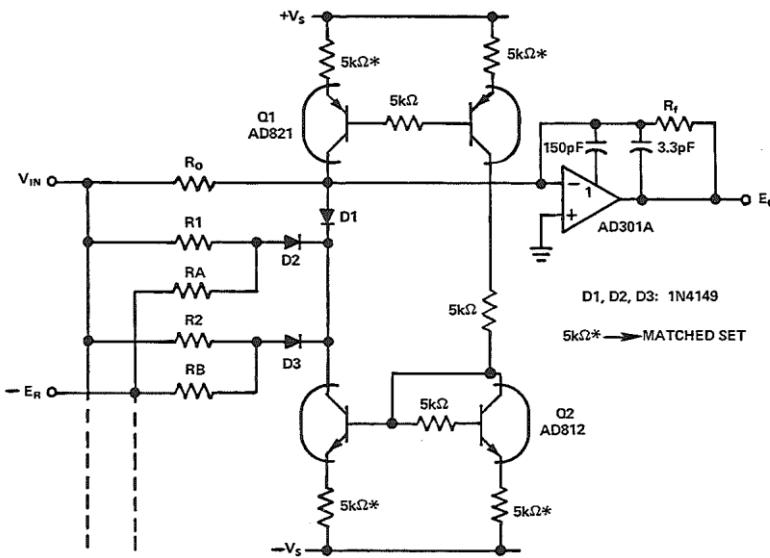

減算は、図 8 と 9 に示すように減算器を使用するか、図 10、11、12 に示すように対数素子を逆向きで直列に接続することによって実行できます。

図 8 では、NPN トランジスタとともに示されている A1 と A2 の出力は次式で表されます。

$$E_{o_1} = -\frac{kT}{q} \ln \frac{I_1}{\alpha I_{ES_1}}, \quad E_{o_2} = -\frac{kT}{q} \ln \frac{I_2}{\alpha I_{ES_2}} \quad (19)$$

これらが A3 の回路で差し引かれて、出力が得られます。

$$E_o = \frac{R_2 kT}{R_1 q} \left( \ln \left[ \frac{I_1}{I_2} \right] + \text{const.} \right) \quad \text{const.} \rightarrow 0 \quad (20)$$

図 8:  $I_{ES}$  を温度補償した対数比回路

これで、トランジスタが適切にマッチングされていれば、この対数比回路の性能が  $I_{ES}$  に影響されることはありません。 $I_1$  入力を見たとき、基準とする  $I_2$  入力を  $I_1$  が正規化出来る値に設定することにより、 $I_2$  に対する比率が決定できます。つまり  $I_2 = I_1$  の場合は、 $\ln(I_1/I_2) = 0$  です。 $I_2$  は、例えば  $I_1$  の範囲の上限値または下限値に設定するか、対称性を確保するためのトランジスタの形状をベースに設定することができます。

$kT/q$  は便利な電圧値であるとは通常考えられないので、 $R_2/R_1$  は、適切な値のゲインを得るためにスケーリングすることができます。例えば、回路の出力のスケール・ファクタを 1V/ディケードにしたい場合は、次のようにになります。

$$E_o = K \log_{10}(I_1/I_2) = 1.0 \log_{10}(I_1/I_2) \quad (21)$$

この場合は、 $25^\circ\text{C}$  で  $R_2/R_1 = q/(kT \ln 10) = 16.903$  です。

必要とされる安定性と温度変動範囲に対して、この回路が温度の影響を受けすぎる場合 ( $0.33\%/\text{ }^\circ\text{C}$ )、値が等しく方向が逆の温度係数を持つゲイン段を後に追加することができます。図 9 では、ユニティ・ゲイン減算器の後にゲイン付きフォロワ回路が接続されています。抵抗  $R_{TC}$  は、下に示すゲインの式の温度感度が  $-0.33\%/\text{ }^\circ\text{C}$  となるように選びます。

$$G = 1 + \frac{R_3}{R_{TC}} \quad (22)$$

例えば、 $G = 16.9$ 、 $25^\circ\text{C}$  で  $R_{TC} = 1 \text{ k}\Omega$  の場合は  $R_3 = 15.9 \text{ k}\Omega$  で、 $R_{TC}$  の温度係数  $\approx +0.35\%/\text{ }^\circ\text{C}$  です。

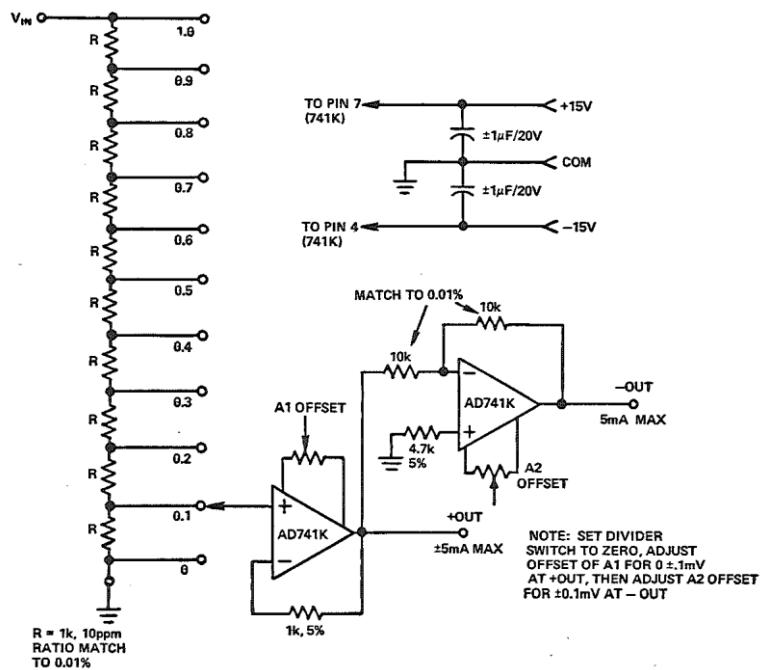

回路設計者に便利なように、モデル 751 対数回路素子には、マッチングしたトランジスタのペア（751P は PNP、751N は NPN）と、対数トランジスタ回路（4-1 項を参照）に温度補償されたゲインを与えるように設計された抵抗分圧器が含まれています。

図 9:  $I_{ES}$  と  $kT/q$  の両方を補償した対数回路

図 8 と図 9 の回路では、見やすいように、動的安定化素子の  $R_E$  と  $C_C$  が省略されています。しかしこれらの素子は、図 6 と同様に、A1 と A2 両方の回路内に使われるでしょう。

図 8 と 9 の回路は作動しますが、実装が高価になる傾向があり、一定リファレンスの対数コンバータの設計に使われることは稀です。図 10 と 11 の回路はもう少し一般的で、少し修正すれば逆対数動作に使用できます。これらの回路が図 8 および 9 の回路と異なるのは、逆向きに直列接続された対数ダイオードによって減算を行う点です。

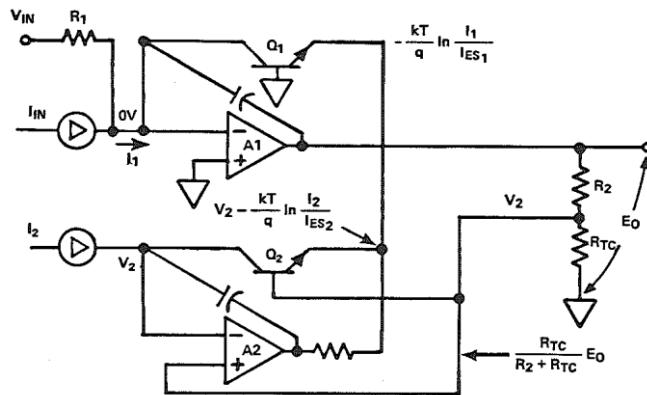

図 10 にその原理を示します。I<sub>1</sub> は入力電流で、これは電流源によって供給するか、入力抵抗  $R_{IN}$  を通して入力電圧  $V_{IN}$  により生成することができます。I<sub>2</sub> はリファレンスか、あるいは電流源によって供給される 2 つめの入力電流です。

Q1 のエミッタ-ベース間電圧は  $-kT/q \ln (I_1/\alpha I_{ES1})$  です。Q2 の  $h_{FE}$  が高い値だとすると（従ってベース電流が無視できるとすると）、Q2 のエミッタ-ベース間電圧は  $-kT/q \ln (I_2/\alpha I_{ES2})$  です。

図 10: 温度補償した対数回路

Q2 のベース電圧は  $E_{oR_{TC}} / (R_2 + R_{TC})$  なので Q1 のベース電圧は 0 であり、エミッタは両方とも同じ電圧になります。

$$V_2 - \frac{kT}{q} \ln \frac{I_2}{\alpha I_{ES_2}} = - \frac{kT}{q} \ln \frac{I_1}{\alpha I_{ES_1}} \quad (23)$$

$$E_o = \left[ 1 + \frac{R_2}{R_{TC}} \right] V_2 = - \left[ 1 + \frac{R}{R_{TC}} \right] \frac{kT}{q} \ln \left[ \frac{I_1}{I_2} \frac{\alpha I_{ES2}}{\alpha I_{ES1}} \right] \quad (24)$$

$V_2$  を  $A_2$  のリファレンス入力に「ブートストラップ」接続すると、 $A_2$  の負入力は  $V_2$  に追従するので、 $Q_2$  のコレクタ・ベース電圧がゼロに保たれます。ただし、 $I_2$  は、電流源、 $V_2$  のリファレンスとして使われる電圧源、または大きな抵抗値と直列に接続された高電圧源のいずれかから供給する必要があります。

抵抗分圧器は  $kT/q$  の温度変化に対して補償し、より大きいスケール・ファクタを提供します。25 °C で  $(I + R_2/R_{TC}) = 16.9$  の場合は、次式が成り立ちます。

$$E_o = - 1V \cdot \log_{10} \frac{I_1}{I_2} \quad (25)$$

図 11 は同様の回路を示していますが、単一の電流または電圧入力信号（もしくは合計値）を正確に対数変換するために、電流リファレンスは固定されています。リファレンス電流の値は  $V_{Z1}/R_3$  です。

$$E_o = K \log_{10} \frac{I_{IN}}{I_{REF}} = K \log_{10} \frac{V_{IN}}{E_{REF}} \quad (26)$$

ここで、

$$E_{REF} = V_{Z1} \left[ \frac{R_{IN}}{R_3} \right]$$

および

$$K = \left[ 1 + \frac{R_2}{R_{TC}} \right] \frac{kT}{q} \ln 10$$

図 11: 内部電流リファレンスを備えた温度補償された対数回路

抵抗  $R_6$  は、ダイナミック・レンジの上限 1 mA を拡張することを可能にし、その負性抵抗効果は  $Q_1$  のバルク抵抗の電圧降下を相殺する傾向があります。 $R_6$  の抵抗値は式 (27) で計算します。

$$R_6 = \frac{R_5}{R_B} \frac{R_{TC} R_2}{R_{TC} + R_2} \quad (27)$$

ここで、 $R_B$  はバルク抵抗です。

### 逆関数動作

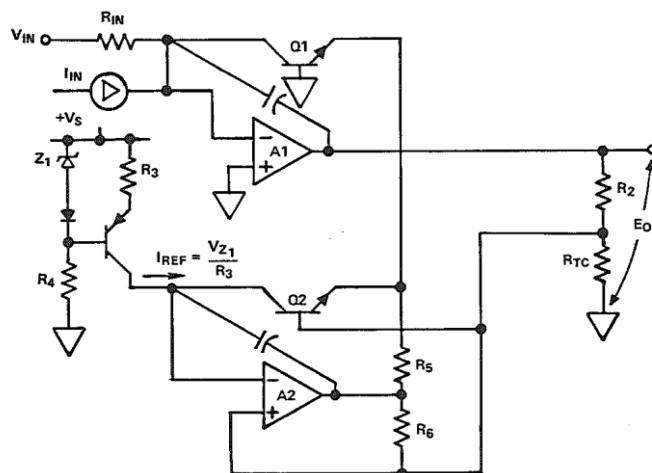

入力抵抗と対数素子の位置を入れ替えると、同じ基本回路構成を使って逆対数を求めることができます。

$$E_o = -E_{REF} e^{-V_{IN}/K} = -E_{REF} (10)^{-V_{IN}/K_{10}} \quad (28)*$$

図 12 で、 $Q_2$  が  $\pm 600$  mV のベース電圧変動に影響されることなく、対数動作に十分なリファレンス電流値で動作すると仮定すると、次式が成り立ちます。

$$-\frac{kT}{q} \ln \left[ \frac{E_o}{R_1 \alpha I_{ES1}} \right] = \left[ \frac{R_{TC}}{R_2 + R_{TC}} \right] V_{IN} - \frac{kT}{q} \ln \left[ \frac{I_{REF}}{\alpha I_{ES2}} \right] \quad (29)$$

$$\frac{q}{kT} \left[ \frac{R_{TC}}{R_2 + R_{TC}} \right] V_{IN} = -\ln \left[ \frac{E_o}{R_1 I_{REF}} \frac{\alpha I_{ES2}}{\alpha I_{ES1}} \right] \quad (30)$$

あるいは、底を 10 にすると次のようになります。

$$= -(1n 10) \log_{10} \left[ \frac{E_o}{R_1 I_{REF}} \frac{\alpha I_{ES2}}{\alpha I_{ES1}} \right] \quad (31)$$

\*  $E_{REF} = I_{REF} R_1$

$\alpha I_{ES2} = \alpha I_{ES1}$  で、なおかつ次式が成り立つとすると、

$$\frac{kT}{q} \left[ 1 + \frac{R_2}{R_{TC}} \right] \ln 10 = K_{10}$$

出力は次のようにになります。

$$E_o = R_1 I_{REF} (10)^{-V_{IN}/K_{10}} \quad (31)$$

図 12: 逆対数（指数）回路

### 対数モジュール

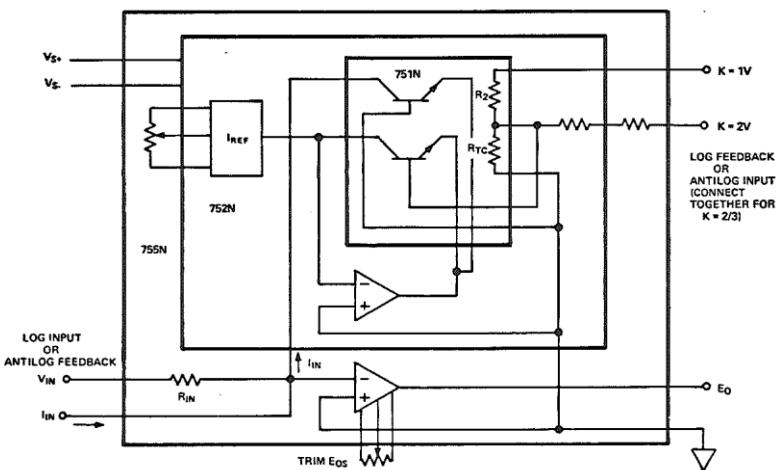

図 11 の回路は、モデル 755 (N と P) や 752 (N と P) に使われている回路と似ています。これら 2 つのファミリーには以下の主な違いがあります。755 は完全な自己完結型の対数回路で、出力アンプ A1 を内蔵しています。

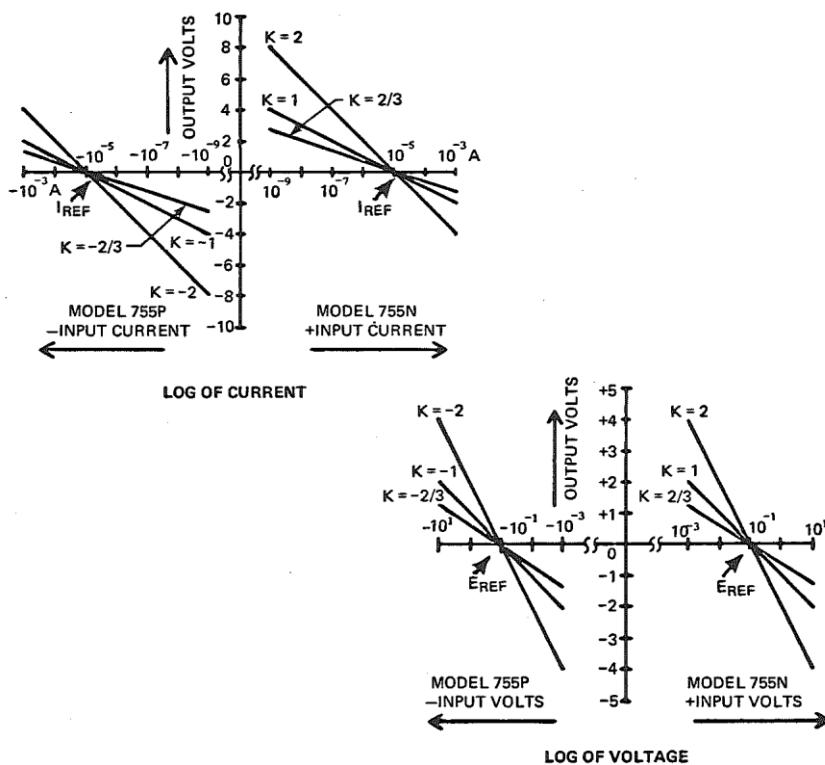

K は固定値選択式 (2/3, 1、および 2) で  $I_{REF}$  も固定されており (ただし変更可能)、4 ディケードの電圧範囲と 6 ディケードの電流範囲での動作に対して仕様が定められています。これに対し 752 の入力電流範囲は 7 ディケードで、外付けのアンプを必要とし、K も  $I_{REF}$  も約 10:1 の範囲で調整することができます (図 13)。755 の下限側での主な誤差源はアンプなので、より広い電流または電圧範囲が得られるようにオペアンプを選択すれば、752 を使用することができます。

この方法はパラメータ選択の柔軟性を高めることもでき、相補的なペアで使用して、 $\sinh$  または  $\sinh^{-1}$ （「バイポーラ対数」）関数を形成することができます。

図 13: 対数／逆対数モジュールの比較ブロック図（簡略図）

### 名称と特性（N と P）

「N」バージョンと「P」バージョンを選択できるすべての対数デバイスにおいて、N は基本的な対数素子として NPN トランジスタが使われていることを示し、P は PNP トランジスタが使われていることを示します。

N バージョン（図 14）の特性は以下の通りです。

- 対数接続の入力電圧または電流は常に正。

- 逆対数（指数）接続の出力電圧は常に正。

- 対数接続の出力電圧は、 $V_{IN} > E_{REF}$  または  $I_{IN} > I_{REF}$  の場合は負で、 $V_{IN} < E_{REF}$  または  $I_{IN} < I_{REF}$  の場合は正。

- 逆対数接続の出力電圧は、負入力では  $E_{REF}$  より大きい正の値で、正入力では  $E_{REF}$  より小さい正の値、ゼロ入力では  $E_{REF}$  と等しくなります。

- 対数接続では、 $V_{IN}$  または  $I_{IN}$  がゼロに近付くにつれて、出力が正の限界値に近付きます。

- 逆対数接続では、入力が大きい正の値を取ると、出力がゼロに近付きます。

図 14: 対数接続したモデル 755N と 755P の

出力対入力の関係（対数入力スケール）

— 電圧と極性の関係を示している

P バージョンの特性は以下の通りです。

- 対数接続の入力電圧または電流は常に負。

- 逆対数（指数）接続の出力電圧は常に負。

- 対数接続の出力電圧は、 $V_{IN} > E_{REF}^*$  または  $I_{IN} > I_{REF}$  の場合は負で、 $V_{IN} < E_{REF}$  または  $I_{IN} < I_{REF}$  の場合は正。

- 逆対数接続の出力電圧は、負入力では  $E_{REF}$  より大きい正の値（小さい負の値）で、正入力では  $E_{REF}$  より小さい正の値、ゼロ入力では  $E_{REF}$  と等しくなります。

- 対数接続では、 $V_{IN}$  または  $I_{IN}$  がゼロに近付くにつれて、出力が負の限界値に近付きます。

- 逆対数接続では、入力が大きい負の値を取ると、出力がゼロに近付きます。、

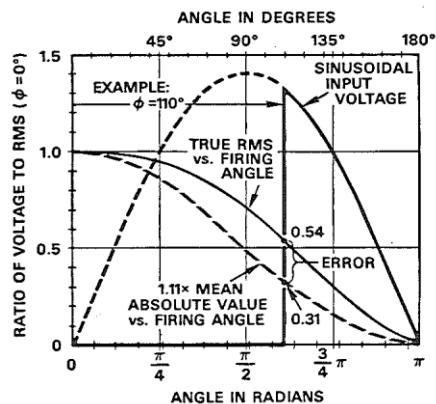

### 対数デバイスの仕様設定

対数デバイスの誤差は、入力または出力を基準とすることができます。入力の比が等しい場合は（所定のスケール・ファクタに対する）出力の増分も等しくなるのが対数の便利な特性なので、任意の入力レベルでのパーセント誤差は、出力でのミリボルト・レベルの変化に変換できます。あるいは、その逆の変換も可能です。対数デバイスの仕様を設定する際、誤差の方向が未知の場合は、引数の大きさを減らす方法を考えられていると想定するのが安全です（つまり、20 % 低い  $\log 0.8$  は -0.097 ですが、20 % 高い  $\log 1.2$  は 0.079 に過ぎません）。下の表は、よく使われる 3 種類の K について、パーセント入力誤差（低）とミリボルト出力の増分の関係を示したものです。K の単位は V/decade (10 倍の入力変化に対するボルト数) です。

等価誤差の表

| Error R.T.I.<br>% low | Output error (mV)                        |          |          |

|-----------------------|------------------------------------------|----------|----------|

|                       | Error RTO = $-K \log_{10} (1 - RTI/100)$ | $K = 1V$ | $K = 2V$ |

| 0.1                   | 0.43                                     | 0.87     | 0.29     |

| 0.5                   | 2.18                                     | 4.35     | 1.45     |

| 1.0                   | 4.36                                     | 8.73     | 2.91     |

| 3.0                   | 13.2                                     | 26.5     | 8.82     |

| 4.0                   | 17.7                                     | 35.5     | 11.8     |

| 5.0                   | 22.3                                     | 44.6     | 14.9     |

| 10.0                  | 45.8                                     | 91.5     | 30.5     |

\*つまり、 $E_{REF}$  より大きい正の  $V_{IN}$ 、または小さい負の  $V_{IN}$

†4-1 項の表 4 も合わせて参照のこと。

中間値を求めるには、線形補間が十分適しています。

誤差が K の公称値またはフルスケール ( $= nK$ ) のパーセント、もしくはその他同様の基準値のパーセントで表されていることが明確に示されている場合を除き、(対数の) 出力誤差をパーセントで表すのは良い方法とは見なされません。

モデル 755 (ここでの例に使用) などのデバイスを使用する場合は、ログアンプに関連する誤差源をしっかりと理解することが、最良の結果を実現する上で役立ちます。主な誤差源は 2 つあります。

1. オフセットを含む (理想対数式の定数の許容差や変化による) パラメータ誤差。

2. 対数適合度誤差。これは、ヌル化とキャリブレーションによってすべてのパラメータの影響を除去した後に残る誤差です。

パラメータ誤差は、以下の式で定義されるように、電圧および電流動作に対して個別に表されます。

$$E_o = -K \log_{10} \frac{V_{IN} - E_{os}}{E_{REF}}$$

および

$$E_o = -K \log_{10} \frac{I_{IN} - I_{os}}{I_{REF}} \quad (32)$$

スケール・ファクタ (K) は、対数モードで接続されている時に、1 ディケード (つまり 10:1) の入力変化に対する出力の電圧変化です。スケール・ファクタの誤差はゲインまたはスロープの変化に相当し、公称値のパーセントで規定されます。K は「N」型では正で、「P」型では負です。モデル 755 の仕様は、最大許容差が 1 %、温度 ( $0^\circ \sim 70^\circ\text{C}$ ) による変化が最大 0.04 %/ $^\circ\text{C}$  です。

オフセット電圧 ( $E_{os}$ ) は、対数動作に使用するオペアンプに依存します。その影響は、入力抵抗と直列の小さい電圧によるものです。高インピーダンス電流源による電流の対数演算では、誤差の影響を無視できます。

しかし、電圧の対数演算では、誤差によって  $V_{IN}$  が変化します。室温での誤差はゼロに調整できますが、使用温度範囲でのドリフトを検討する必要があります。755 では  $E_{OS}$  が  $0 \pm 400 \mu V$  で、最大ドリフトは  $\pm 15 \mu V / ^\circ C$  です。

リファレンス電圧 ( $E_{REF}$ ) は実効内部生成電圧で、すべての電圧はこの電圧と比較されます。この電圧は内部生成されたリファレンス電流  $I_{REF}$  に関係しており、その関係は  $E_{REF} = I_{REF}R_{IN}$  で表されます。ここで  $R_{IN}$  は入力抵抗の値です。通常、 $I_{REF}$  は  $R_{IN}$  よりかなり安定性に欠けるので、実質的に、すべての許容差は  $I_{REF}$  によるものです。755N では、 $E_{REF}$  の公称値は  $+0.1 V \pm 3\%$  (最大 3 mV) で、最大温度係数は  $0.1 \% / ^\circ C$  です。755P では、 $E_{REF} \approx -0.1 V$  で、許容差は同じです。

オフセット電流 ( $I_{OS}$ ) は、アンプのバイアス電流に浮遊リーク電流を加えたものです。このパラメータは、ナノアンペア領域の信号を処理する場合に大きな誤差源となることがあります。このため、755 のようなデバイスでは、この値が  $10 pA$  ( $10^\circ C$  上昇するごとに 2 倍) 以内に抑えられています。

リファレンス電流 ( $I_{REF}$ ) は内部生成された電流源出力で、すべての入力電流がこの電流と比較されます。 $I_{REF}$  の許容誤差は、出力の DC オフセットとして現れます。755N では、 $I_{REF}$  は最大  $+10 \mu A$   $+3\% \pm 0.1 \% / ^\circ C$  です (755P では  $I_{REF}$  の極性は負)。表から、この入力パラメータの  $\pm 3\%$  の許容差は出力の  $\pm 13.2 mV$  に相当し、これは入力信号とは無関係のオフセットで、リファレンス電流を調整することによって除去できます (調整が可能な場合)。また、スケール・ファクタ減衰器に電流を注入することによって出力に電圧を加えるか、あるいは単純に出力の接続先で一定のバイアスを加えることによっても除去できます。

パラメータ誤差に加えて、対数適合度誤差も考慮する必要があります。パラメータを調製して、オフセット、スケール・ファクタ、およびリファレンス誤差を補償した後も、出力は依然として (主にレンジの境界付近で) 理想的な対数動作から外れることが分かります。理想対数デバイスの動作は片対数プロット上で線形なので、対数適合度誤差は、対象範囲における片対数プロット上の直線からの偏差です。

モデル 755 の場合、対数関係の線形性が最も良好なのは、電流レンジの中央 4 ディケード部分 ( $10 \text{ nA} \sim 100 \mu\text{A}$ ) です。この範囲での対数適合度誤差は、 $\pm 0.57\% \text{ RTI}$ 、つまり  $2.18 \text{ mV RTO}$  です ( $K = 1$ )。

自由度が大きければ（パラメータとユーザー変数両方に關して）、対数デバイスの仕様を 1 つの全体的数値にまとめることができるのは言うまでもありません。1 つの代替策として、必要な範囲に収まる性能を計算するのに十分な情報が提供されています。モデル 755 の仕様を例として取り上げましたが、もちろん読者は、データシートやアナログ・デバイセズ製品ガイド、その他の媒体によって、設計開始時に入手可能なデバイスの特性を十分に把握するよう努める必要があります。デバイス動作についての読者の理解を助けるために、本章の最後に 755 の詳細な仕様が示されています。特定デバイスに関するアプリケーション情報については、データシートに詳細が示されています。

## 対数および逆対数デバイス

これまで検討してきたタイプの対数回路では、基本的に何が起きているかについて、以下のように因果関係を説明することができます。

1. 回路の入力に電流が与えられ、アンプの入力電圧が生じます。

2. アンプの出力電圧が反対方向に変化します。

3. 対数ダイオードの入力に加わるアンプ出力電圧 ( $V_{BE}$ ) によってコレクタ電流が流れ、アンプの入力電流をバランスさせ、入力電圧がゼロに保持されます。

4. アンプの出力は入力電流の対数に比例しますが、対数ダイオードの出力電流は、その入力電圧の逆対数に比例します。

したがって、すべての対数デバイスは、オペアンプと逆対数（指数）回路で構成されていると見なすことができます。したがって、すでに述べたように入力抵抗と帰還素子を入れ替えると、加算点に逆対数入力電流を生成し、それに対応する逆対数電圧を出力に発生させる回路が得られます\*。

逆対数接続では同じ誤差源が存在し、これは次の特性方程式で検討することができます。

$$E_o = E_{REF}(10)^{-V_{IN}/K} \pm E_{os} \quad (33)$$

入力の一定の増分として現れる誤差は、出力に一定のパーセント誤差を生じます。

755 は、対数動作用にも逆対数動作用にも接続することができます。752 を外付けのオペアンプとともに使用すれば、対数動作用にも逆対数動作用にも接続することができます。図 15 に示すチャートは、 $\pm 10^{\circ}\text{C}$  の範囲で  $\pm 2\%$  の誤差という制約のもとで、さまざまなタイプのオペアンプを使用した 752 と 755 の動作レンジを比較しています。チョッパ安定化アンプ (233J) は電圧レンジを、低バイアス電流 FET (42J) は電流レンジを最大限まで広げ、汎用 FET (40J) はコストを最小限に抑えます。

| LOG MODULE                                                     | 755                                                          | 752 OPERATING WITH OP AMP                                                                  |                                      |                                          |

|----------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------|

|                                                                |                                                              | 233J<br>Chopper<br>Stabilized                                                              | 42J<br>Electrometer<br>FET           | 40J<br>Economy<br>FET                    |

| Op Amp Type →                                                  | Internal-High Performance FET                                |                                                                                            |                                      |                                          |

| Input Range for $\pm 2\%$ Error, Over $\pm 10^{\circ}\text{C}$ |                                                              |                                                                                            |                                      |                                          |

| $V_{in}^1$                                                     | 3.5mV to 10V                                                 | 500μV to 10V                                                                               | 37.5mV to 10V                        | 25mV to 10V                              |

| $E_{os}$ Drift                                                 | 150μV                                                        | 10μV                                                                                       | 750μV                                | 500μV                                    |

| $I_{in}$                                                       | 1nA to 1mA                                                   | 3.5nA to 1mA                                                                               | 50pA <sup>2</sup> to 1mA             | 5nA to 1mA                               |

| $I_{os} + I_{os}$ Drift                                        | 20pA                                                         | 70pA                                                                                       | 1pA                                  | 100pA                                    |

| Selection Criteria                                             | Complete log amplifier, high performance, trimmed internally | Extends lower limit of voltage range. Minimum drift and offset errors, long term stability | Extends lower limit of current range | Lowest cost for a complete log amplifier |

| Relative Costs (1–9)                                           | 100%                                                         | 140%                                                                                       | 104%                                 | 80%                                      |

<sup>1</sup>Values selected are consistent with a 10kΩ input register.

<sup>2</sup>Log conformity error restricts the lowest input signal to 100pA.

図 15: 755 フル機能対数／逆対数モジュールと 752 対数／逆対数トランスクンダクタの能力の比較

\* 対数ダイオードは、 $R_E$  によってアンプの出力電圧から絶縁されて、 $r_E$  の両端に出力（副産物）として対数電圧を生成する電流フォロワと見なすこともできます。

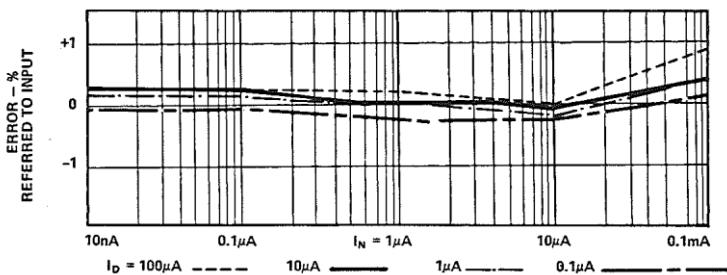

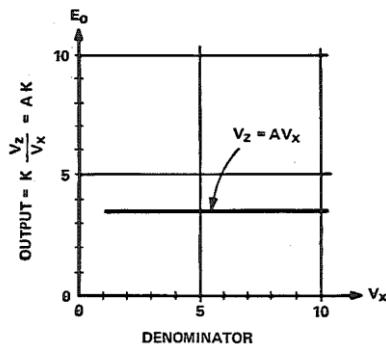

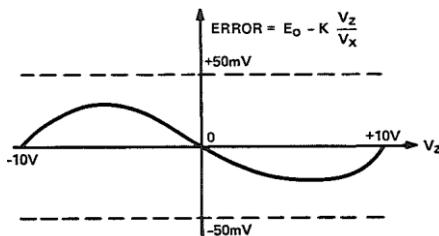

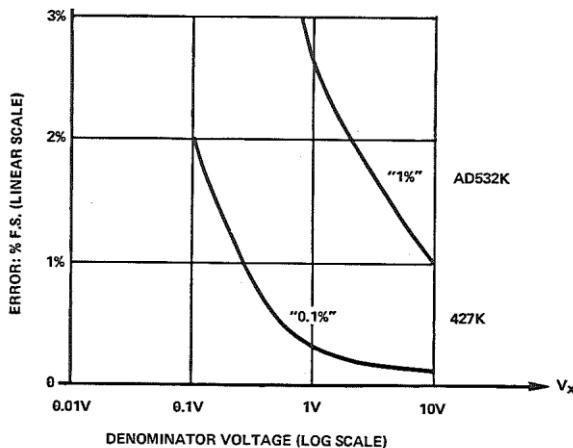

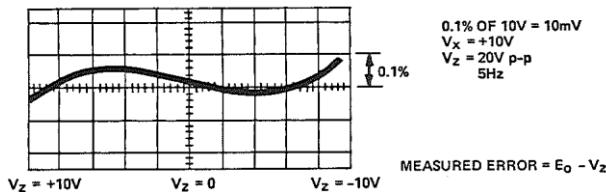

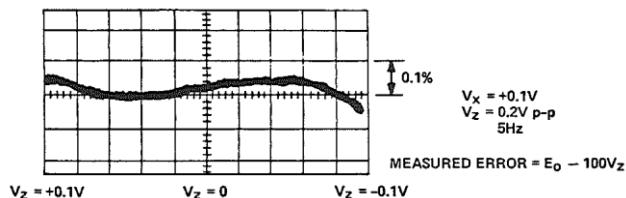

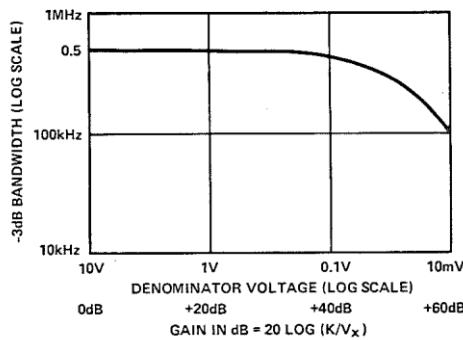

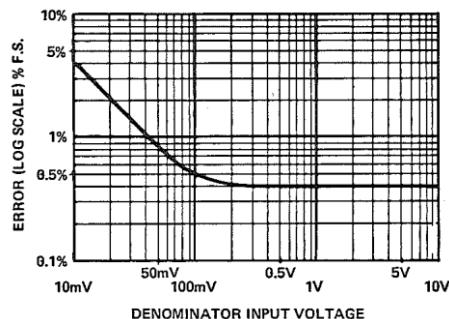

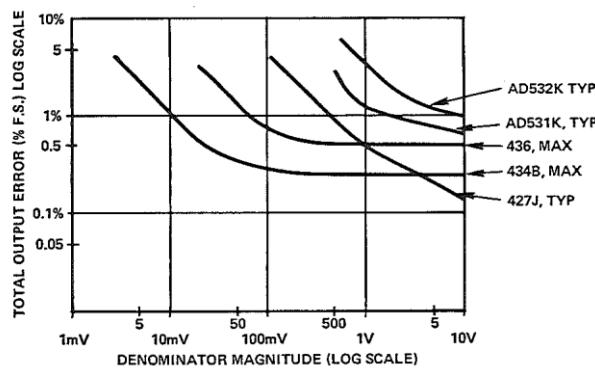

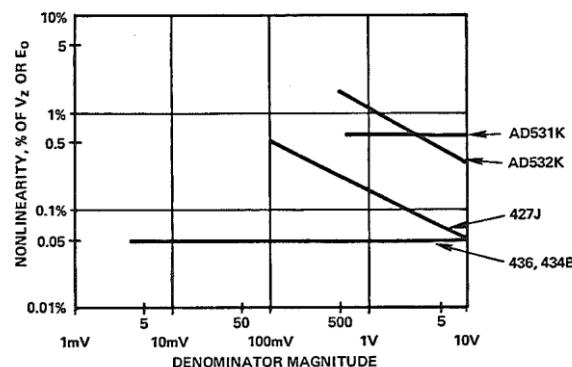

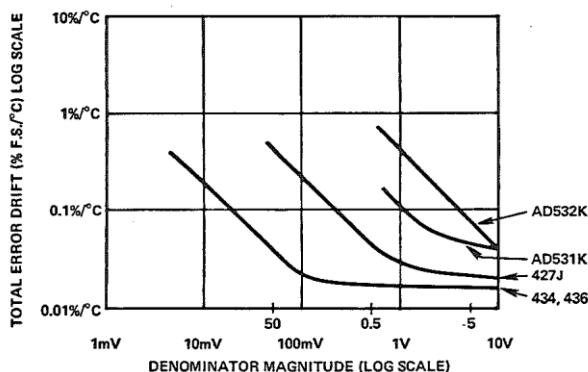

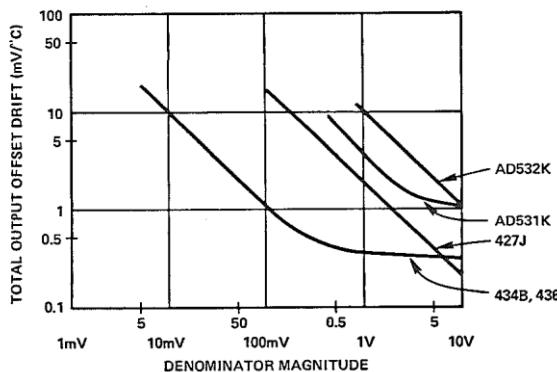

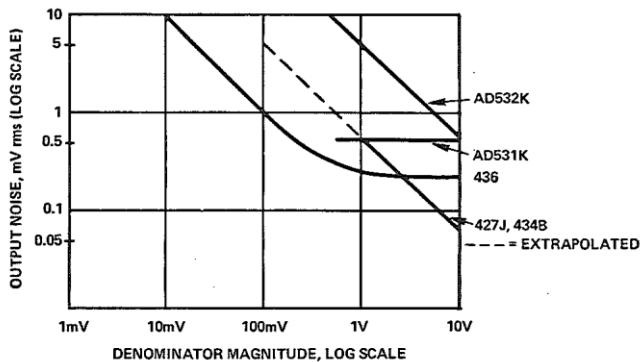

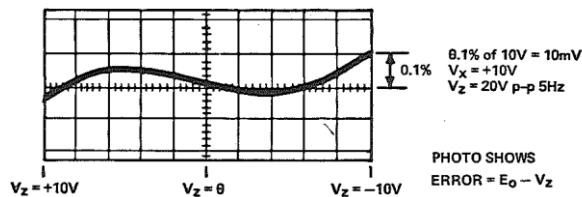

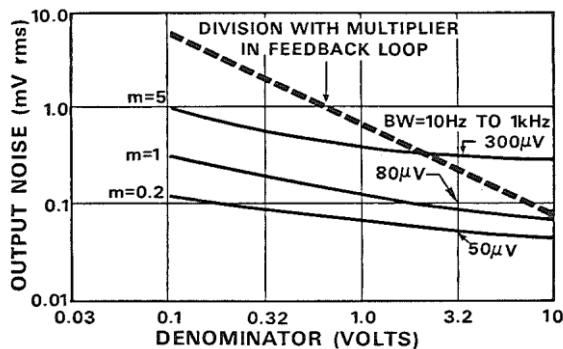

756 は、可変リファレンスや比の対数を必要とするアプリケーション用に設計されています。その対数比適合度は 1 % で、その範囲は通常 7 ディケードです（4 ディケードの分子変化、3 ディケードの分母変化）。図 16 は、比を基準とした % 誤差の代表的な値を 4 つの  $I_D$  値に対し  $I_N$  の関数として示しています。

図 16: モデル 756 対数比モジュールの対数適合度誤差

## 動的誤差

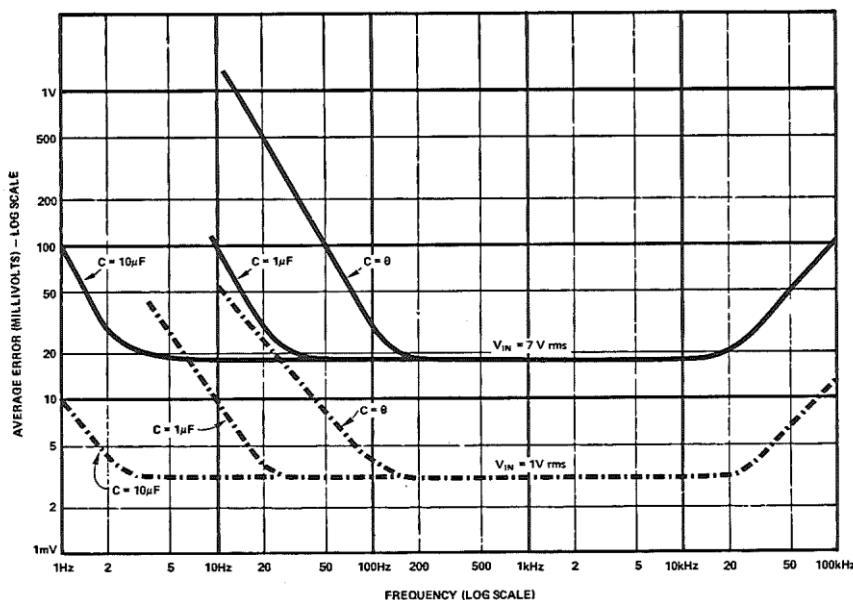

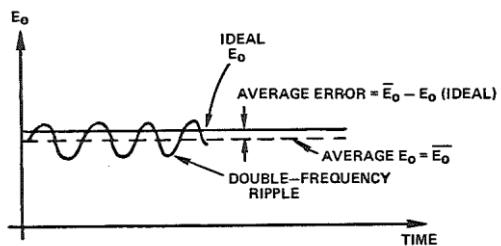

対数デバイスの速度と周波数応答は、スケーリング、信号レベル、および変化の方向に依存します。通常は、 $1 \mu\text{A}$  を超えると応答が積分器の時定数に支配され、信号レベルにともなってはほとんど変化しません。 $1 \mu\text{A}$  未満では  $r_{EC_C}$  が応答を支配し、入力電流に比例して速度が低下します。755 の応答時間の代表値の表を下に示します。信号の大きさが増える場合の方が、減る場合より応答時間が短くなるのは興味深い点です。これは、新しい電流値が速度を決定するからです。

| $I_{IN}$ (Increasing)            | Time             | $I_{IN}$ (Decreasing)            | Time             |

|----------------------------------|------------------|----------------------------------|------------------|

| $1\text{nA}$ to $10\text{nA}$    | $1\text{ms}$     | $10\text{nA}$ to $1\text{nA}$    | $4.5\text{ms}$   |

| $10\text{nA}$ to $100\text{nA}$  | $100\mu\text{s}$ | $100\text{nA}$ to $10\text{nA}$  | $400\mu\text{s}$ |

| $100\text{nA}$ to $1\mu\text{A}$ | $7\mu\text{s}$   | $1\mu\text{A}$ to $100\text{nA}$ | $30\mu\text{s}$  |

| $1\mu\text{A}$ to $1\text{mA}$   | $4\mu\text{s}$   | $1\text{mA}$ to $1\mu\text{A}$   | $7\mu\text{s}$   |

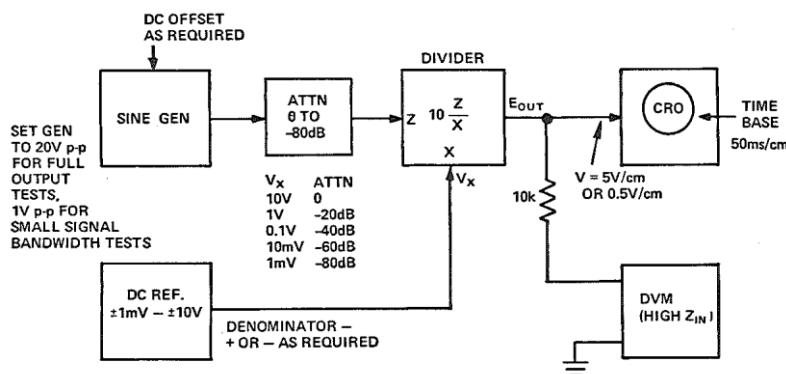

もちろん対数応答は、非対称非線形の遅延時間と同様に、広い範囲の正弦波に歪みを発生させます。したがって周波数応答は、異なる電流レベルでの小信号応答によって与えられます。

755 の代表的周波数応答 (-3dB) は以下の通りです。

| $I_{IN}$ | -3dB frequency |

|----------|----------------|

| 1nA      | 80Hz           |

| 1μA      | 10kHz          |

| 10μA     | 40kHz          |

| 1mA      | 100kHz         |

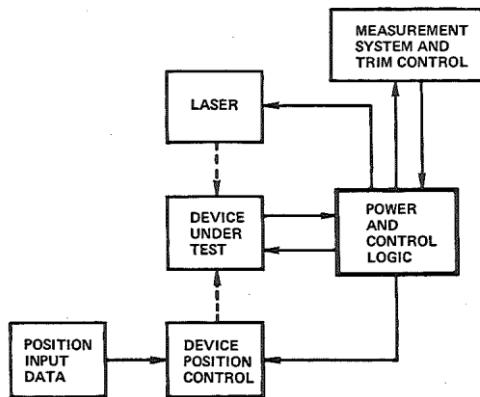

### 対数デバイスのテスト

後述の基本テストを行うには、以下の装置（または同等品）が有用です。

ピコアンペア電流源 Keithley 261

高精度 DC 電圧基準器 Electronic Development Corp. 100N

ファンクション・ジェネレータ Hewlett-Packard 3310A

デジタル電圧計 Hewlett-Packard 8300A

オシロスコープ Tektronix 543B (Type 1A5 プリアンプ搭載)

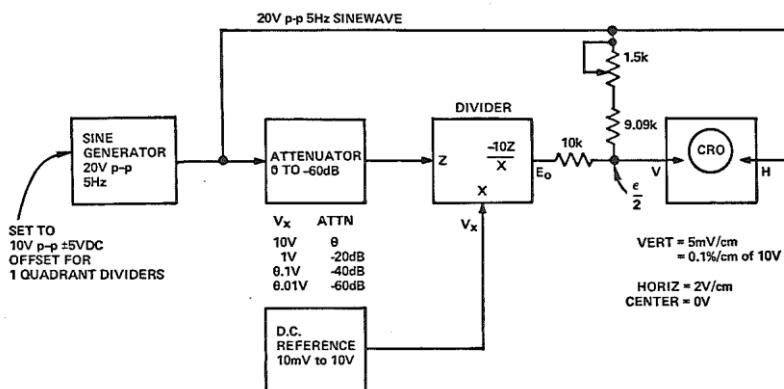

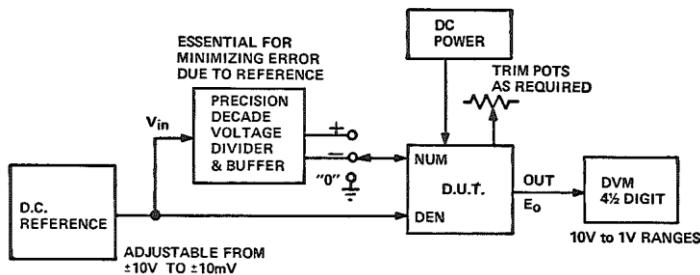

このセクションでは、スケール・ファクタ、対数適合度誤差、リファレンス電流精度、応答時間、帯域幅、入力オフセットなど、対数デバイスのいくつかの基本的パラメータを（与えられた対数デバイスに適用される範囲で）評価するための回路と手法について述べます。フル機能の自己完結型「ブラック・ボックス」である 755 には、これらのパラメータすべてが適用されます。これらについては、755 の測定に関連して説明します。

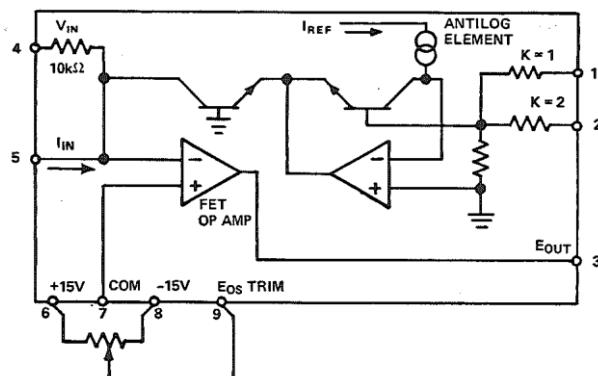

説明を簡潔にするために、ピン番号接続を使用します。ピン接続と回路機能間の関係を図 17 (755N の簡略機能図) に示しますが、その原理は同様のデバイスすべてに適用されます。結果は、計測時にどの程度注意を払うかに依存します。

スケール・ファクタ (K) は、対数構成に接続した状態で、入力の 1 ディケード (10:1) の変化に対する出力電圧の変化として定義されます。これは、出力の片対数プロットの勾配です。

図 17: モデル 755 の接続図

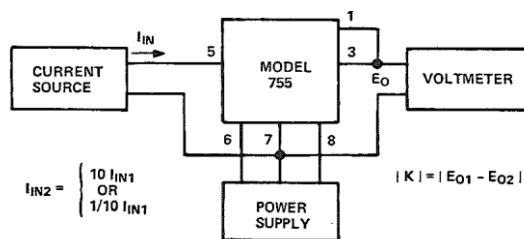

スケール・ファクタの計測は、電流源を使用する方法が最も簡単です。ピン 5（入力加算点）に電流  $I_1$  を与えて、出力を測定します。電流を正確に 10 倍 ( $10I_1$ ) まで増加させて、再び出力を測定します。スケール・ファクタは、これら 2 つの測定値の単純な差です。

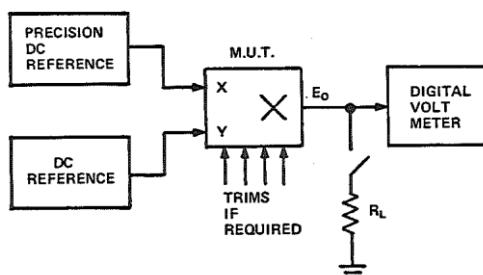

図 18: 電流入力によるスケール・ファクタ計測

(図は  $k=1$  の場合)

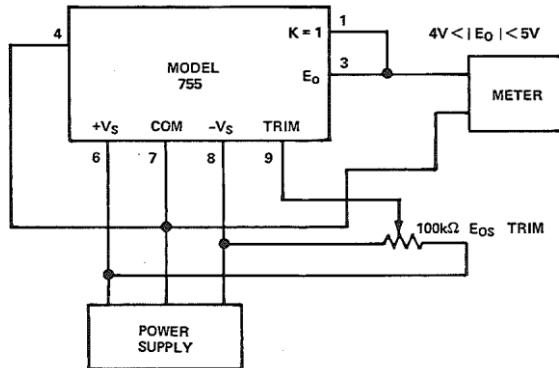

スケール・ファクタを電圧モードで計測したい場合、最初に、入力電圧オフセットを慎重に調整して、値をほぼゼロにする必要があります。図 19 に示す回路を使用し、電圧入力（ピン 4）を接地した状態で、微妙な調整を行うことができます。N 型デバイスの出力は、外付けの  $100\text{ k}\Omega$  10 回転トリマ・ポテンショメータを使用して、 $+4\text{ V} \sim +5\text{ V}$  の間に調整できます（755P の場合、調整範囲は  $-4\text{ V} \sim +5\text{ V}$  です）。

$E_{REF}$  は  $10^{-1}V$  なので、入力を接地した状態で出力電圧が  $4V \sim 5V$  ということは、 $E_{OS}$  が  $4 \sim 5$  ディケード低い（つまり  $1 \sim 10 \mu V$ ）であることを示しています。

オフセット電圧の調整後、入力  $V_{IN1}$  と  $10V_{IN1}$  を順にピン 4 に加え、それらに対する出力の差を取ることにより、電流入力の場合と同じ方法（図 18）でスケール・ファクタを計測することができます。

図 19: 対数モードでの  $E_{OS}$  のトリミング

リファレンス電圧は、入力とリファレンスの比が 1 になる入力電圧です。この値に対する対数出力はゼロです。したがって、あるユニットのリファレンス電圧の値は、 $E_{REF}$  (755N の場合  $0.1 V$ ) に近い正確に決定された電圧を入力 (4) に加え、出力がゼロとなるように調整して、実験的に計測されます。リファレンス電圧を変更するには、電流入力 (5) に適切な値の外付け抵抗を接続して、それを入力抵抗として使用するか、または電流リファレンスを変更するか、もしくは出力の外付け計算アンプに定数を追加することができます。これらいずれの方法でも、入力に必要な値を正確に与え、出力がゼロとなるよう調整することによって、リファレンス電圧の新しい値を校正することができます。

リファレンス電流は、入力とリファレンスの比が 1 になる時の入力電流値です。この値に対する対数出力はゼロです。これは、正確に測定した調整可能な入力電流を与えて、出力がゼロになるように調整することによって、リファレンス電圧と同様に測定されます。755N の  $I_{REF}$  は約  $10 \mu A$  です。

$I_{REF}$  は、出力の外付け加算アンプに定数を追加するか、リファレンス源に変更を加えることによって変更できます。これは 756 対数比ユニットの入力変数であり、752 対数／逆対数トランスコンダクタでは調整可能で、755 では固定されています。しかし 755 でも、未使用の K ピン（ピン 1 または 2）に電流源から電流を与えることによって、これを変更することができます。必要な電流の値は、1 ディケードのシフトにつき  $66 \mu\text{A}$  です。補正だけ必要な場合、感度は 1 % の変化あたり  $0.29 \mu\text{A}$  程度です。シフトが小さい場合は、値の大きい抵抗 ( $>> 2.2 \text{ M}\Omega$ ) と直列の電圧によって電流を生成することができます。

対数適合度誤差は、実際の出力電圧と対数変換式によって予測された出力電圧の差で、オフセット、リファレンス・シフト、およびスケール・ファクタの影響は、いずれも除去されるか、計算に入れられています。片対数グラフに出力と入力をプロットすると直線になるはずです。この直線との偏差が対数適合度誤差です（出力は線形スケール、入力は対数スケールで計測されます）。プロットされた出力値を結んでスムーズな曲線を描けるように、対象範囲に対して十分な入力電圧値または電流値を与えます。また、入力を正確に決定し、出力を正確に測定し、対象となる大きさの許容値がよく見えるように、十分大きな用紙を使用します。以上で「最良の直線」を描くことができます。この直線からの偏差が、対数適合度誤差を表します。

より繊細なプロット方法は、実際の出力値から予想出力値を引いて、その結果（全誤差）を、対数スケールの入力に対して線形スケールにプロットします。こうすると、「最良直線」が平均勾配とオフセット誤差を表わし、この直線からの偏差が対数適合度誤差を表します。出力誤差は、等価誤差の表（188 ページ）を使って入力基準で表すことができます。

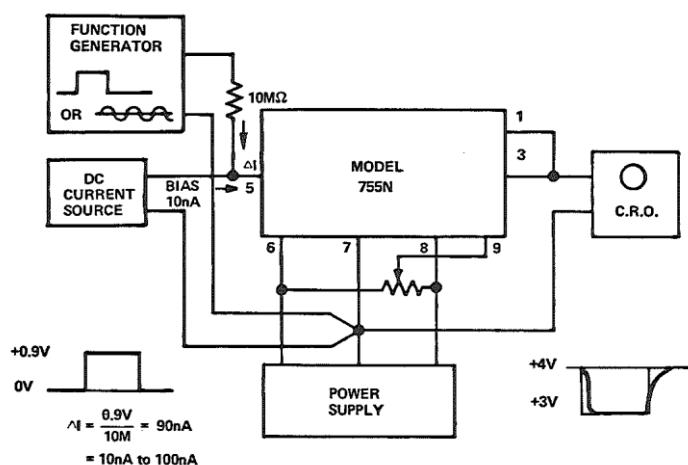

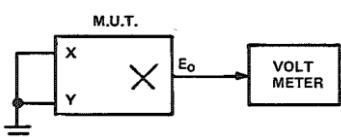

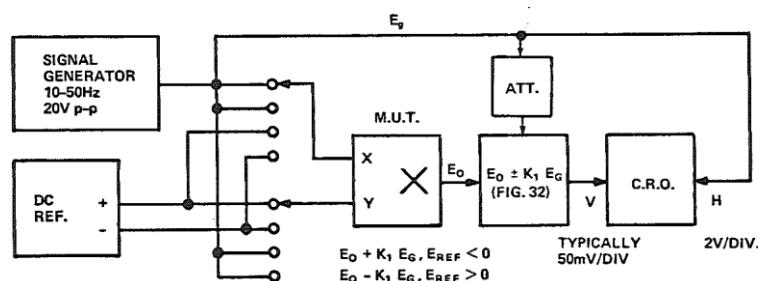

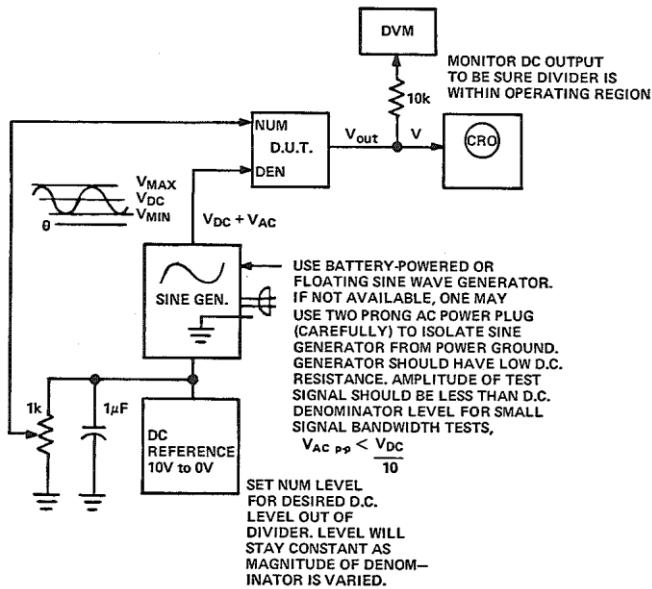

ダイナミック計測は、適切なバイアス・レベルからのわずかな変化、あるいはバイアス・レベル近辺でのわずかな変化を観察することによって行います。インクリメンタルに変化させるのに,DC バイアスと電圧入力（大きい外付け抵抗と直列）を足し合わせるには、電流入力を使用できます（図 20）。

例えば、 $I_{IN}$  が 10 nA から 100 nA に増加する際の応答時間、あるいは 100 nA から 10 nA に減少する際の応答時間を測定するには、(755N の) ピン 5 に 10 nA の電流を与えます。10 MΩ の抵抗を通して、0 V から立ち上がる 0.9 V の矩形波を与えます。この矩形波は、90 nA のインクリメンタルな電流ステップを生成します。全体の入力スイングは 10 ~ 100 nA です。パルスが十分な幅を備えていると仮定すると、増加ステップと減少ステップ両方に対する応答を同時に見ることができます。出力 ( $K = 1$ ) では、増加入力ステップ応答は +4 V から +3V ヘスイングし、減少入力応答は +3 V から +4 V ヘスイングします。

図 20: インクリメンタルな応答計測

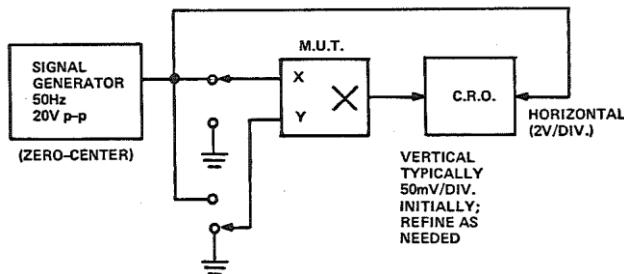

通常、周波数応答は、固定入力値に対し  $\pm 5\%$  の正弦波偏差を使うことによって計測します。例えば、1 μA レベルでは偏差は  $\pm 50$  nA になります。電流入力 (5) に 1 μA の DC を与え、1 MΩ の抵抗を通してそれを 100mV<sub>p-p</sub> と加算します。低周波数での出力スイングは、43.5 mV<sub>p-p</sub> にします。入力振幅を一定に保ちながら、出力振幅が 30.5 mV<sub>p-p</sub> になるまで周波数を上げます。これは、出力振幅がその低周波数での値から 3 dB 下がる周波数です。

## まとめ

第 1 部では対数デバイスの概要を示し、第 2 部ではアプリケーションについて説明しました。また、この章では、対数デバイスの基本的な特性、熱的および動的な安定性を得る手法、よく使われる回路、仕様と定義、および調整とテストの方法について述べてきました。4-1、4-2、4-3 項、「設計者のための手引き」には、対数、対数比、および逆対数アプリケーション用デバイスについての追加情報と、その選択および使用のためのガイドラインが与えられています。

## 3-1 項の付録

## 代表的対数／逆対数モジュールの詳細仕様（モデル 755N と 755P）

(別途注記の無い限り +25 °C および ±15 VDC での代表値)

| TRANSFER FUNCTIONS                                   | DYNAMIC RANGE OF INPUT                   |

|------------------------------------------------------|------------------------------------------|

| Log of Current                                       | 120dB                                    |

| $E_o = -K \log_{10} \frac{I_{in} - I_{OS}}{I_{REF}}$ | 1nA to 1mA (755N)<br>-1nA to -1mA (755P) |

| Log of Voltage                                       | 80dB                                     |

| $E_o = -K \log_{10} \frac{E_{in} - E_{OS}}{E_{REF}}$ | 1mV to 10V (755N)<br>-1mV to -10V (755P) |

| Antilog of Voltage                                   |                                          |

| $E_o = E_{REF} 10^{-E_{in}/K} \pm E_{OS}$            | -2 ≤ E <sub>in</sub> /K ≤ 2              |

## 伝達関数パラメータ

| Symbol           | Value      | Tolerance     | Drift         | Note |

|------------------|------------|---------------|---------------|------|

| K                | 2/3, 1, 2V | 1% max        | ±0.04%/°C max | 1, 2 |

| E <sub>REF</sub> | 0.1V       | 3% max        | ±0.1%/°C max  | 2    |

| I <sub>REF</sub> | 10μA       | 3% max        | ±0.1%/°C max  | 2    |

| E <sub>OS</sub>  | 0 ± tol.   | ±400μV        | ±15μV/°C max  | 3    |

| I <sub>OS</sub>  | 0 ± tol.   | +0, -10pA max | 2x/10°C       |      |

## 入力を基準とした対数適合度誤差

| Input Current Range      | Conformity Error | Input Voltage Range | Conformity Error |

|--------------------------|------------------|---------------------|------------------|

| 1nA to 10nA              | ±1% max          |                     |                  |

| 10nA to 100μA            | ±0.5% max        | 1mV to 1V           | ±0.5% max        |

| 100μA to 1mA             | ±1% max          | 1V to 10V           | ±1% max          |

| 1nA to 1mA (Total Range) | ±1% max          |                     |                  |

## 応答時間

| I <sub>in</sub> (increasing) | Time  | I <sub>in</sub> (decreasing) | Time  |

|------------------------------|-------|------------------------------|-------|

| 1nA to 10nA                  | 1ms   | 10nA to 1nA                  | 4.5ms |

| 10nA to 100nA                | 100μs | 100nA to 10nA                | 400μs |

| 100nA to 1μA                 | 7μs   | 1μA to 100nA                 | 30μs  |

| 1μA to 1mA                   | 4μs   | 1mA to 1μA                   | 7μs   |

## 小信号周波数応答

| $I_{IN}$ (Level) | 3dB Down At |

|------------------|-------------|

| 1nA              | 80Hz        |

| 1μA              | 10kHz       |

| 10μA             | 40kHz       |

| 1mA              | 100kHz      |

## 入力基準ノイズ、10 kHz 帯域幅

|               |              |

|---------------|--------------|

| Noise Voltage | $2\mu V$ rms |

| Noise Current | $2pA$ rms    |

## 定格出力（注記 4）

$\pm 10V, \pm 5mA$

## 電力要件（静止時）

$\pm 15V$ , regulated  $\pm 1\%$ , 7mA

## 温度

|           |                                   |

|-----------|-----------------------------------|

| Operating | $0^{\circ}C$ to $+70^{\circ}C$    |

| Derated   | $-25^{\circ}C$ to $+85^{\circ}C$  |

| Storage   | $-55^{\circ}C$ to $+125^{\circ}C$ |

## 機械的仕様

|           |                                   |

|-----------|-----------------------------------|

| Case Size | $1.5'' \times 1.5'' \times 0.4''$ |

| Weight    | $38.1 \times 38.1 \times 10.2$ mm |

|           | 1 oz. (28.3g)                     |

## 価格

|         |         |

|---------|---------|

| (1-9)   | \$55.00 |

| (10-24) | \$49.00 |

## 注記:

1.  $K = 1V$  の場合は端子 1 を、 $K = 2V$  の場合は端子 2 を、 $K = 2/3V$  の場合は端子 1 と 2 を使用（互いに短絡）。

2. パラメータは 755N の場合は +、755P の場合は -。

3. 外部からゼロに調整可能。

4. どのピンのグラウンドへの短絡によってもデバイスが損傷することはありません。

5. 仕様は予告なく変更されることがあります。

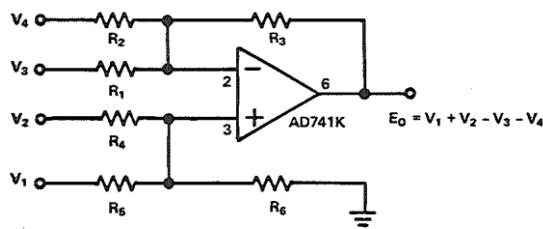

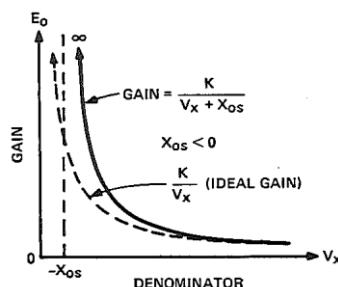

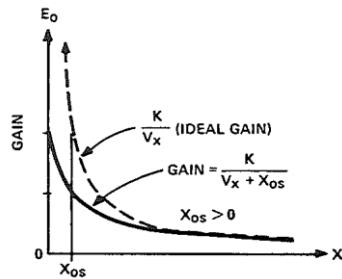

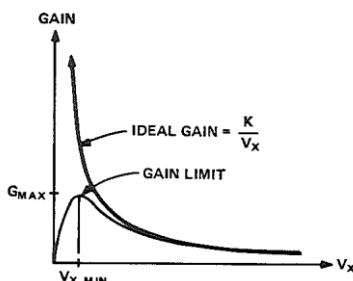

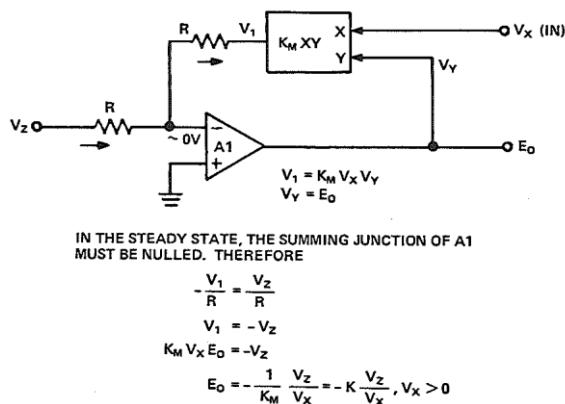

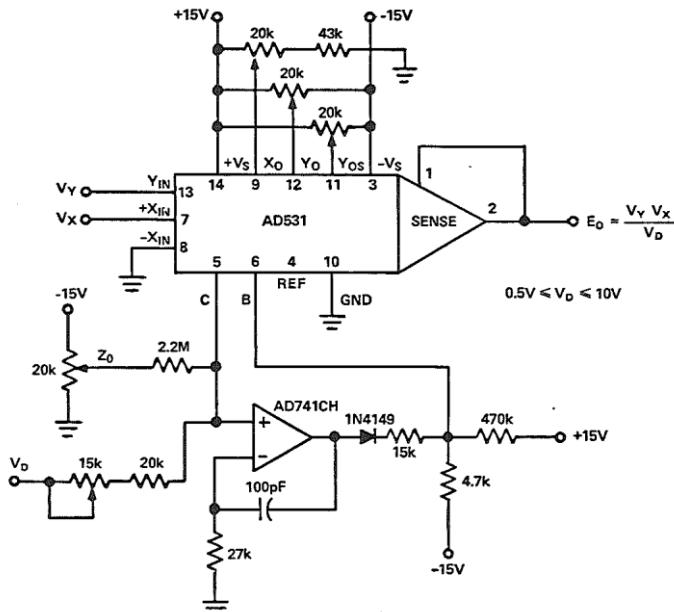

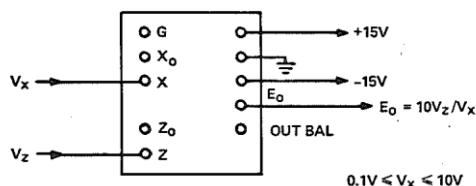

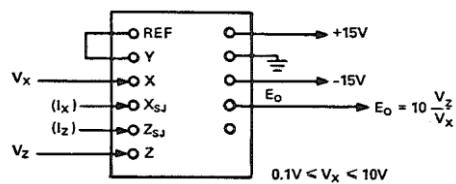

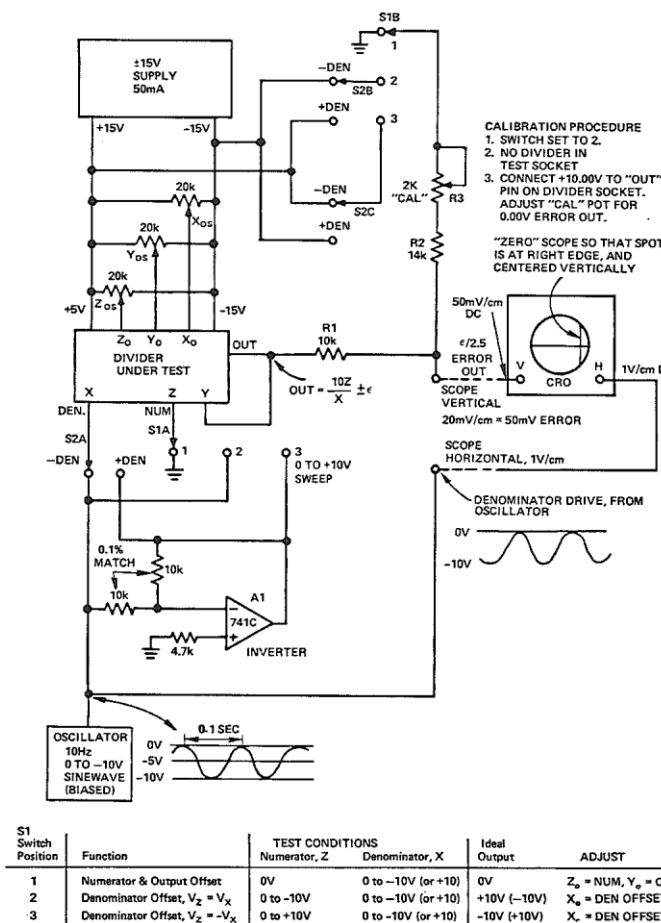

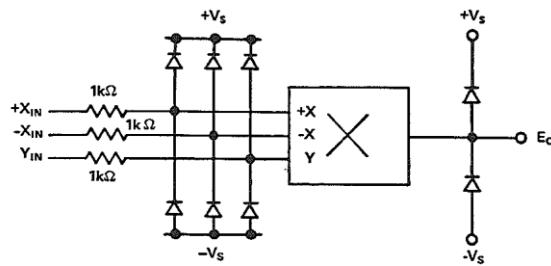

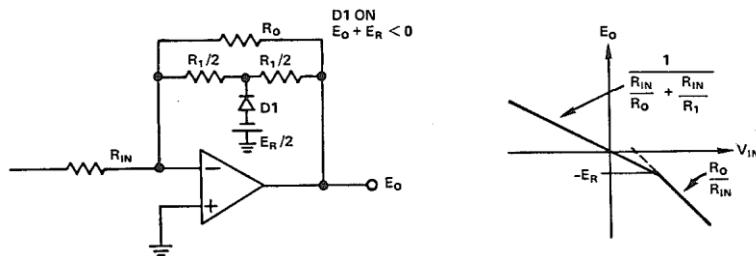

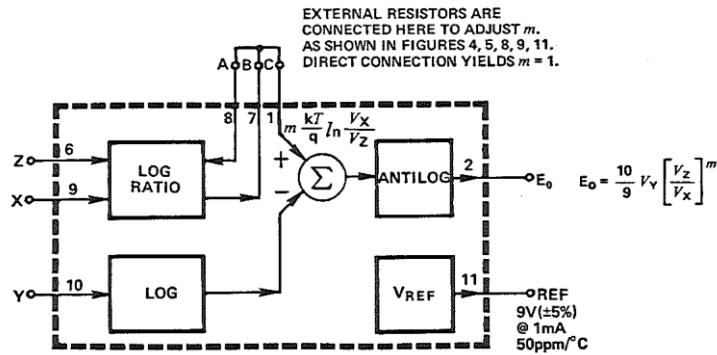

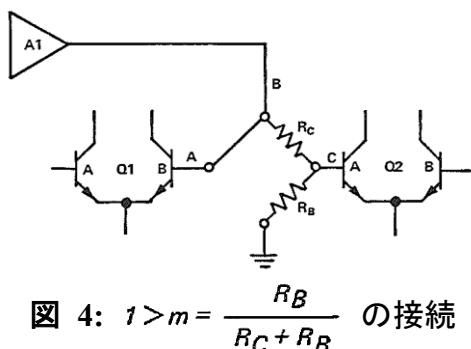

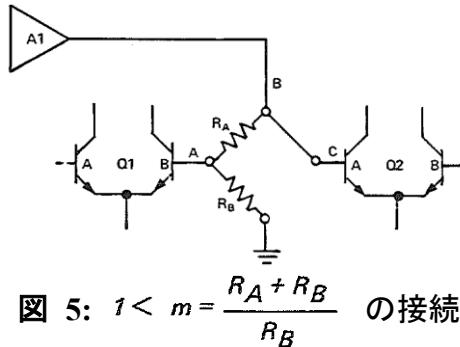

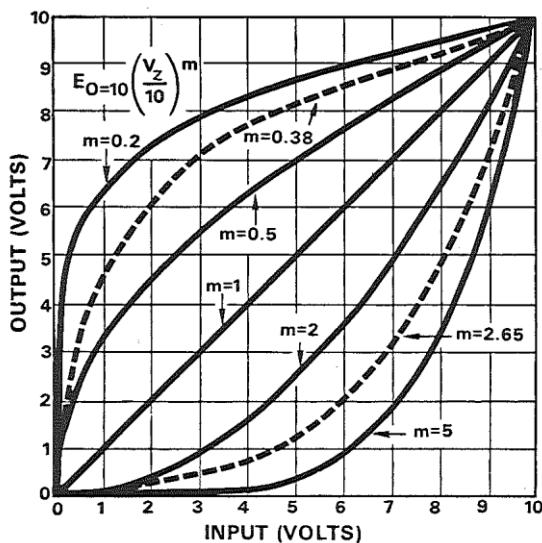

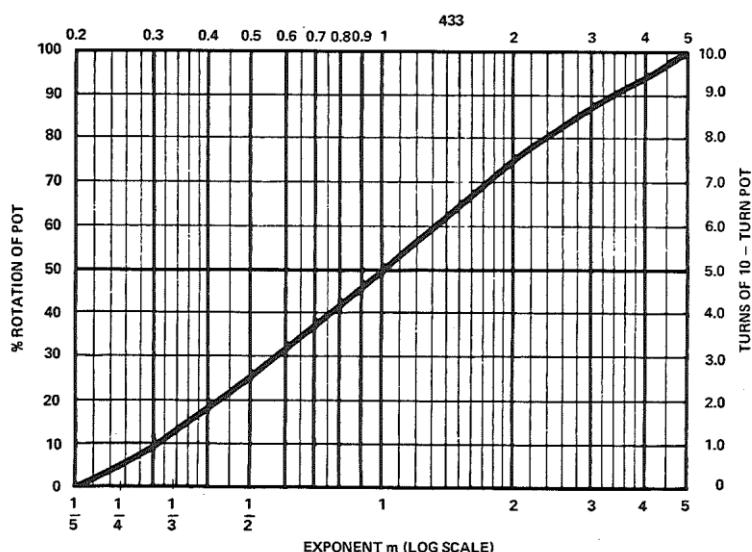

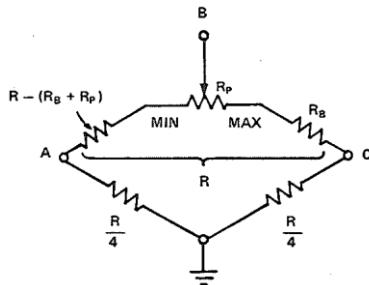

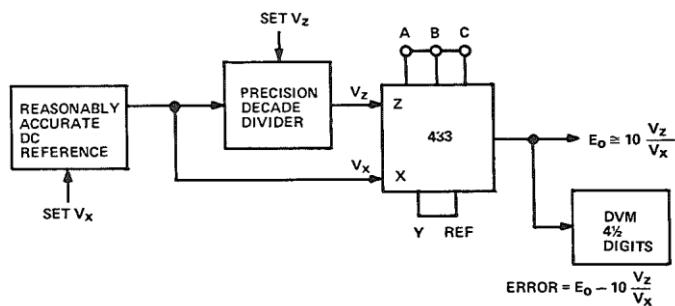

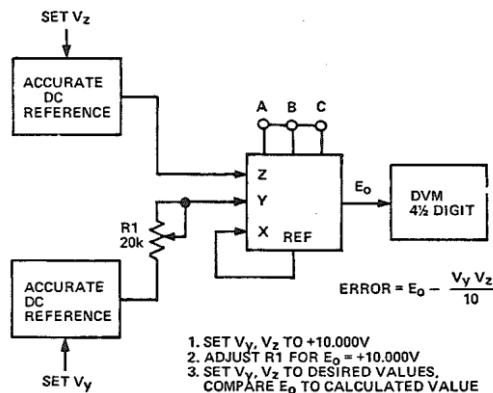

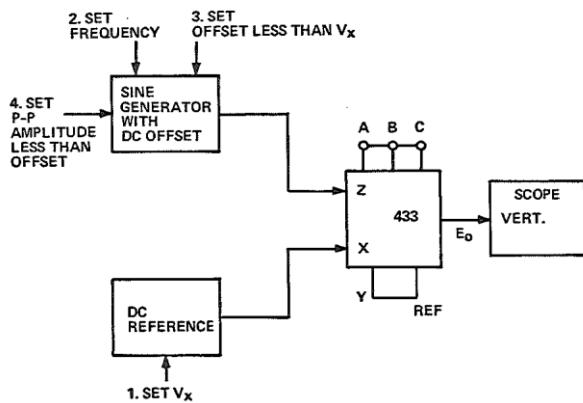

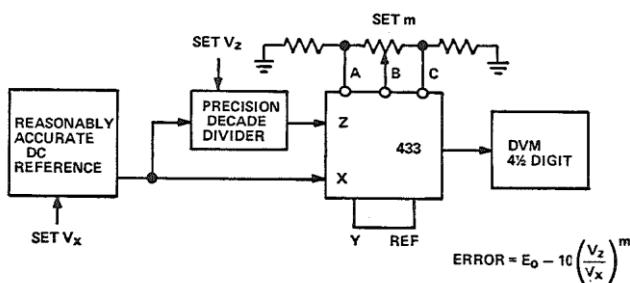

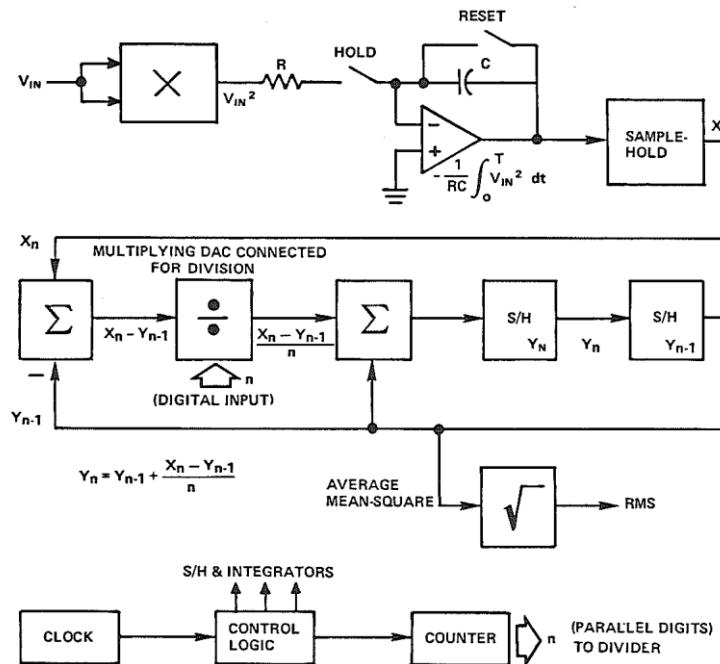

### 3-2 乗算器

アナログ乗算器は、2つまたはそれ以上の独立した入力電圧または電流の積に比例する出力電圧または電流を生成するデバイスです。

$$E_o = V_x V_y / V_r = K V_x V_y \quad (1)$$

比例定数  $1/V_r$  の次元は  $V^{-1}$  です。 $V_r$  は、回路内の特定の電圧または電流を使って確認するか、単独で決定することができます。通常は 10 V に固定されます。

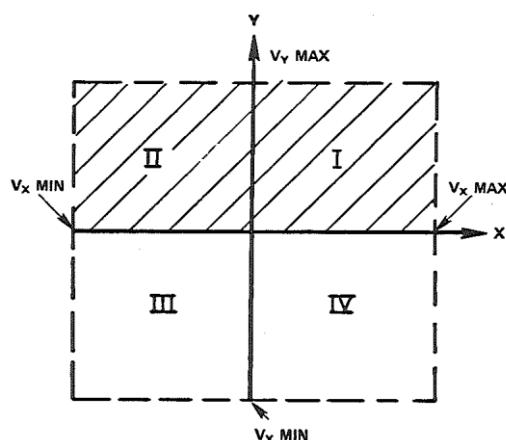

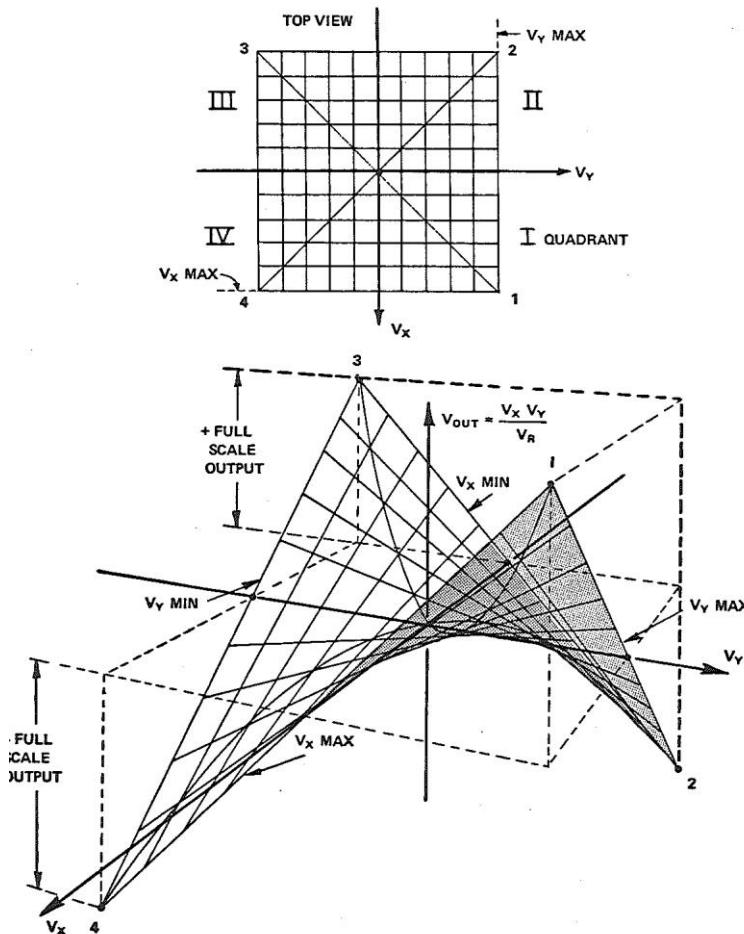

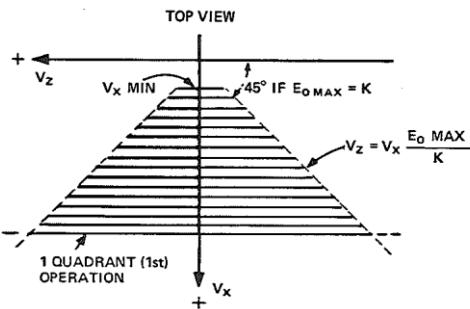

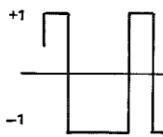

乗算器の動作範囲は入力によって定めることができます。2入力で各入力が2つの極性を取り得る場合、極性の組み合わせは4種類です。これは、X-Y 平面の4つの象限として図示できます（図1）。

図 1: 乗算器の動作座標

動作領域内の入力ペアは、乗算器の出力電圧を一意に決定します。4 象限の組み合わせすべてを受け入れて適切な極性の出力を生成することのできる乗算器は、「4 象限乗算器」と呼ばれます。「2 象限」乗算器は一方の入力の  $\pm$  信号と、もう一方の入力の単極信号に応答します。例えば、 $\pm V_x$  と  $+V_y$  に応答する乗算器は、斜線で示された I 象限と II 象限からなる半平面で動作します。

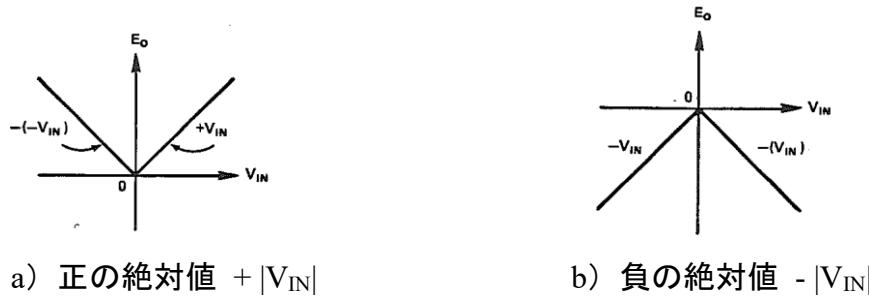

1 象限乗算器は、1 つの象限のユニポーラ入力にだけ応答します。 $V_x$  と  $V_y$  の両方が正の値に制限されている場合、その乗算器は第 1 象限で動作します。乗算器の中には、適切な数の象限に応答しても出力の極性が反転しているものがあります。その式は  $E_O = -KV_xV_y$  です。单一象限内の 1 つまたは複数の入力に応答する乗算器は、前段に絶対値回路を置き、後段に符号絶対値出力回路を置くことによって、複数象限の演算に使用できます。この場合、出力の極性は入力の極性によって決まります（文面から受ける印象の通り手順は面倒ですが、一部の乗算型 D/A コンバータなどのデバイスでは一般的です）。入力と出力をオフセットすることによって、多象限動作を実現することもできます（図 21 参照）。

### 乗算の手法

現時点では、電子式アナログ乗算を行うための最も一般的な方法は、可変トランスクンタクタンスとパルス幅、パルス高変調の 2 つです。第 3 の方法である対数／逆対数法も普及しつつあり、特に低速高精度の計算によく使われています。

この章では、これら 3 種類の乗算器の回路設計と、全体的性能に影響を与える要素について詳しく説明します。

これまで、アナログ・コンピューティング、通信、および計測用の回路には他にも多くのタイプの乗算器と変調器が使われており、また、現在でも使われています。これらの例には、二乗差掛け算器、ダイオードリング、FET、磁気デバイス（例えばホール効果）などが含まれます。

ここではこれらのタイプの設計については触れませんが、仕様とテストに関する説明の大半は、これらにも当てはまります。

### 乗算の特性

乗算の代数的特性はアナログ乗算器の設計と仕様の決定的要素なので、これらの特性のいくつかと、それらの物理的乗算器性能との対応を改めて見直しておくと、理解を助けます。

設計や特性評価に直接影響する顕著な乗算特性の 1 つは、3 種類の入力の組み合わせで積がゼロになる事実です。

| Input State | Theoretical Output | Error Parameter          |

|-------------|--------------------|--------------------------|

| 1           | $0 \cdot 0 = 0$    | Offset                   |

| 2           | $0 \cdot Y = 0$    | Y-Null, or Y Feedthrough |

| 3           | $X \cdot 0 = 0$    | X-Null, or X Feedthrough |

もう 1 つの重要な特性は、積の大きさと入力の関係です。ほとんどの一般的乗算器がそうであるように、両方の積が常に  $V_r$  より小さいと仮定すると（つまり、 $V_r$  がフル・スケール）、積は常に  $V_r$  以下となります。

$$4 \quad 0 \leq |V_x, V_y| \leq V_r \quad \text{Input Constraint} \quad (2)$$

$$5 \quad |V_x \cdot V_y / V_r| \leq V_r \quad \text{Output Constraint} \quad (3)$$

2 つの入力が等しくないと、(2) の条件が満たされる場合、その積は小さい方の入力より小さくなります。つまり、次の関係が成り立つとします。

$$|V_x| < |V_y| \quad (4)$$

および

$$|V_x V_y / V_r| < V_r \quad (5)$$

この場合は次式が成り立ちます。

$$|V_x V_y / V_r| < V_x \quad (6)$$

式 2 ~ 6 は、理想乗算器の出力は小さい入力で穏やかに動作することを示しています。どちらかの入力または両方の入力がゼロになると、出力もゼロになります。1 次（線形）誤差がゼロに調整されると仮定すると、本章で取り上げるアナログ乗算器回路は、この理想動作に驚くほど近い動作をします。その理由は、誤差の非線形形成分 ( $f(V_x, V_y)$ ) が  $V_x$  と  $V_y$  の連続関数で、 $V_x$  と  $V_y$  がゼロに減少するとこの成分もゼロになるからです。乗算器の誤差源、および回路設計と誤差の関係について説明している以下のセクションでは、その理由を示します。

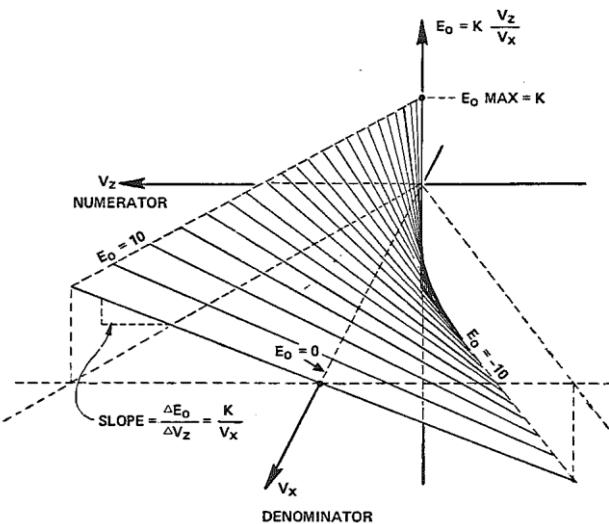

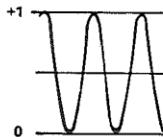

乗算関数は、次の式を表す 3 次元の面で表わすことができます。

$$Z = X Y \quad (7)$$

この面の形状は、以下の特性によって概要を示すことができます。

1. X 軸および Y 軸に沿った出力 (Z) はゼロです (フィードスルーがゼロ)。

2. 一方の入力が一定の場合、出力はもう一方の入力に直線的に比例し、勾配 (ゲイン) は一定入力によって決まります。

3. 両方の入力が等しい場合 ( $X = Y$  または  $X = -Y$ )、出力は入力の二乗に比例します。これは、極性が逆で互いに接する 2 つの放物線を、I-III の対角線と II-IV の対角線に対応する位置に直角に生成します。

これらの要件に適合する曲面は、図 2 に描かれている双曲放物面（鞍型曲面）です。放物線部分は、曲面と、対角線を通る垂直面および対角線に平行な垂直面との交線に相当します。（条件 3）。

直線要素は X 軸および Y 軸に平行な垂直面と曲面との交線で（条件 2）、曲面は X 軸と Y 軸および両軸の交点 0 に沿って X-Y 平面を通過します（条件 1）。

図 2:4 象限乗算器 – 入力／出力曲面

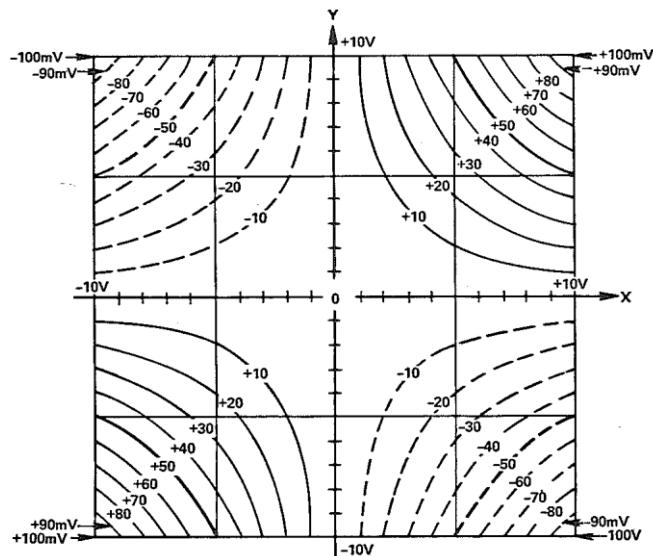

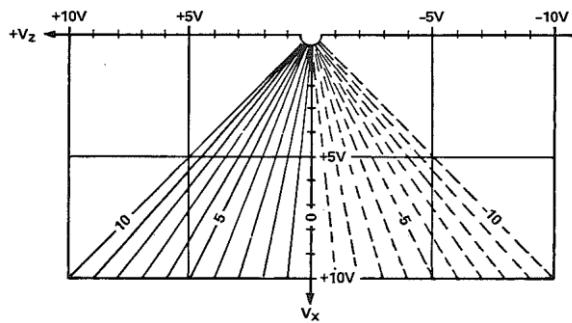

水平面と関数の交線は双曲線になります。つまり、コンター・マップは、対角線 I-III に沿って丘を登っていき、対角線 II-IV に沿って谷を下っていく一連の直角双曲線を示します（図 5）。

図で 1、2、3、4 と表示された曲面のコーナーは、各象限での乗算器の最大出力を表しています。これらの最大値は、 $\pm X$  と  $\pm Y$  の 4 つの組み合わせに生じます。

乗算器は実際明らかに非線形ですが、乗算器を非線形デバイスとする考え方には矛盾しているように見えるかもしれません。結局、X または Y を一定値として動作させた乗算器のゲイン特性を実際に計測すれば、線形の出力／入力関係が得られるはずです。つまり、乗算器はゲイン  $KX$  の線形アンプとして動作します。実際のところ、通常、「線形」乗算器は（1）の理想的な関係に従うものと考えられています。

一方の入力を固定すれば乗算器は確かに線形デバイスであり、概念的には、固定ゲインのアンプで置き換える可能なのは明らかです。信号入力はゲインを変化させることはできないので、出力には信号が線形に再生されます。

両方の入力を変化させると、応答は確かに非線形です。例えば、X と Y の両方に同じ入力が与えられた場合、出力は入力の二乗に比例します。これは明らかに非線形の動作で、比例の基準にも重ね合わせの基準にも当てはまりません（1 ページ参照）。

$$\text{If } V_{IN} = V_1 \quad E_{out} = KV_1^2 \quad (8)$$

$$\text{If } V_{IN} = V_2 \quad E_{out} = KV_2^2 \quad (9)$$

$$\text{If } V_{IN} = V_1 + V_2 \quad E_{out} \neq K(V_1^2 + V_2^2) \quad (10)$$

これを幾何学的に解釈すると、双曲放物面は展開面、つまり、円筒や円錐のように直線要素から構成できる曲面です。

一方の出力を一定に保てば理想的なアナログ乗算器は線形デバイスになる、というのは役に立つ事実です。この事実により、デバイスの特性が本質的には非線形であるにも関わらず、実際の乗算器の動作の特性評価、調整、校正、および測定を、線形の観点で容易に行えます。

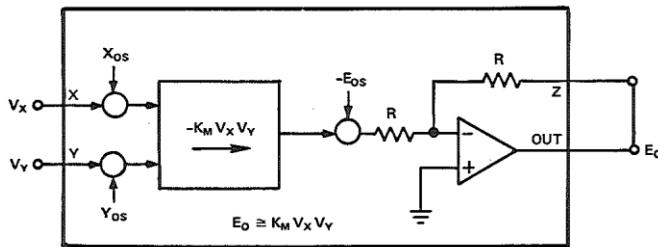

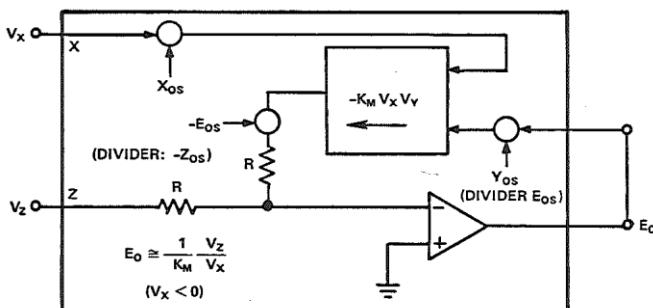

## 実際のアナログ乗算器の誤差

実際のアナログ乗算器の出力は、その入力の理論的積と異なります。一般にその差  $\epsilon$  の大きさは予測困難ですが、次式で定義されます。

$$E_o = K V_x V_y \pm \epsilon(V_x, V_y) \quad (11)$$

(11) に記号で示された誤差を、回路内の誤差源に直接関係する項に展開することは、乗算器回路の特性を検討する上で非常に有効です。アナログ乗算器には、4 つの主要な静的（つまり DC）誤差があります（動的誤差については後で、乗算器の仕様のセクションで説明します）。

| Error            | Symbol           |

|------------------|------------------|

| 1. Input Offsets | $X_{os}, Y_{os}$ |

| 2. Output Offset | $Z_{os}$         |

| 3. Scale Factor  | $\Delta K$       |

| 4. Nonlinearity  | $f(X, Y)$        |

これらの誤差の影響は、次式のように適用できます。

$$E_o = (K + \Delta K) \left\{ (V_x + X_{os}) (V_y + Y_{os}) + Z_{os} + f(X, Y) \right\} \quad (12)$$

式を展開して項をまとめると次のようになります。

$$E_o = KV_x V_y + \underbrace{\Delta K V_x V_y}_{\epsilon(X, Y)} + (K + \Delta K) \left\{ V_x Y_{os} + V_y X_{os} + Y_{os} X_{os} + Z_{os} + f(X, Y) \right\} \quad (13)$$

この長い一連の誤差項は、それを個別に考えることによって整理できます。

| 項                  | 説明          | 入力への依存性                      |

|--------------------|-------------|------------------------------|

| $KV_x V_y$         | 真の積         | 一方の入力または両方の入力がゼロになると、積もゼロになる |

| $\Delta K V_x V_y$ | スケール・ファクタ誤差 | $V_x, V_y = 0$ でゼロになる        |

厳密に言うと以下の項には  $K + \Delta K$  を掛けますが、 $\Delta K$  と他の誤差の積は 2 次誤差であってほとんど問題にならないため、 $\Delta K$  の影響は無視することができます。

|                 |                                   |                                                       |

|-----------------|-----------------------------------|-------------------------------------------------------|

| $V_x Y_{os}$    | Y 入力の DC オフセットによる線形<br>「X」フィードスルー | $V_x$ に比例                                             |

| $V_y X_{os}$    | X 入力の DC オフセットによる線形<br>「Y」フィードスルー | $V_y$ に比例                                             |

| $X_{os} Y_{os}$ | X、Y の入力オフセットによる出力オフセット            | $V_x, V_y$ には依存しない                                    |

| $Z_{os}$        | 出力オフセット                           | $V_x, V_y$ には依存しない                                    |

| $F(X, Y)$       | 非線形性                              | $V_x$ と $V_y$ の両方に依存。 $V_x, V_y$ 、その累乗および外積に依存する項を含む。 |

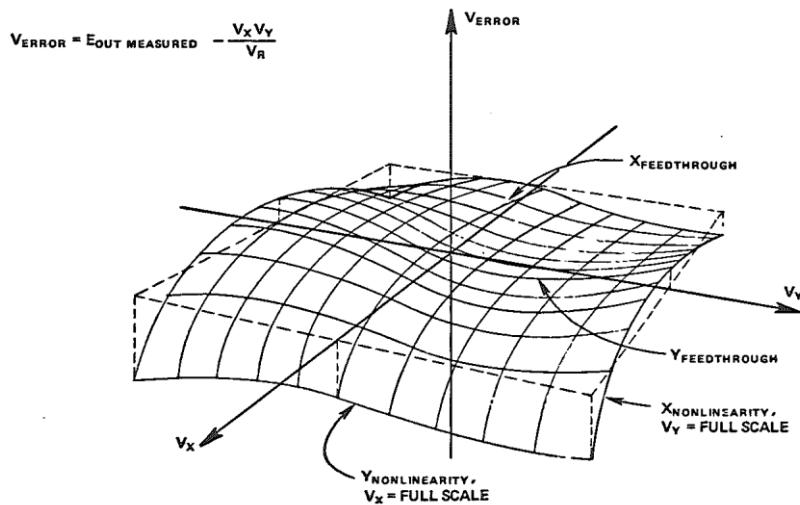

実際のアナログ乗算器の誤差  $\epsilon(X, Y)$  は、実際の乗算器出力と理論値の差を表す曲面として可視化することができます。一般に、この誤差曲面は歪みや振れがあって平坦ではなく、丘の多い田舎の地形に良く似ています。4 象限乗算器の仮想誤差曲面を図 3 に示します。グラフの高さ、つまり Z 座標が、次式で表される誤差  $\epsilon(X, Y)$  を示しています。

$$\epsilon(X, Y) = E_o(\text{actual}) - KV_x V_y = E_o - V_x V_y / V_r \quad (14)$$

ここで、

$E_o$  = 乗算器出力電圧の測定値

$V_x$  = X 入力電圧

$V_y$  = Y 入力電圧

$KV_x V_y$  = 理想出力電圧

$\epsilon(X, Y)$  は、(13) の誤差項の和に相当する測定電圧です。

図 3: 乗算器誤差曲面

誤差曲面を使用してアナログ乗算器の静的誤差を記述するのは面倒に見えるかもしれません、これは（13）の個々の誤差成分の全体的な3次元的影響を可視化する最も簡単な方法です\*。

例えば、「線形」X フィードスルー  $V_x Y_{\text{OS}}$  の影響を考えます。 $Y_{\text{OS}}$  が小さい正の量だとすると、 $V_x$  が増加するにつれて乗算器の出力も比例して増加します。 $V_x$  が負になると、出力も負になります。この影響が Y 入力に依存しないのは明らかですが、これは、式 10 には  $V_x Y_{\text{OS}}$  が追加誤差として示されているためです。線形 X フィードスルーがあると、XY 平面を真横から見た図（図 4）に示すように、誤差面が Y 軸の周りに傾きます。

同様に、X オフセット（「線形」Y フィードスルー）があると、誤差面全体が X 軸周りに傾きます。DC オフセット  $X_{\text{OX}} Y_{\text{OS}} + Z_{\text{OS}}$  の影響があると、面全体が Z（出力）軸に沿って上下に移動します。

\*誤差曲面は主に可視化のための手段として使われます。これと、2 次元コンター表現 ("iso-vers": iso は「等しい」、ver (ity) は「正確さ」の意) は、この目的のために使われています。しかし、誤差関数の形はユニットごとに、また、さまざまな調整段や熱環境ごとに大きく異なるので、誤差曲面は個々のデバイスのデータのコンパクト表現としてほとんど役に立ちません。

図 4: 線形 X フィードスルーは、Y=0 における誤差曲面の断面として表示できます。

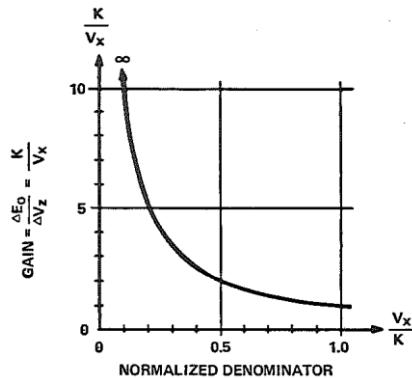

スケール・ファクタ  $\Delta K$  の影響はそれだけで考えられますが、これは次式で定義される誤差曲面を生成します。

$$\epsilon(XY)_K = \Delta KV_x V_y \quad (15)$$

図 5: 1 % の正のスケール・ファクタ誤差曲面（他の誤差はすべてゼロ）の ISO-VER 表現。コンター間隔: 10 mV

これは、乗算器出力  $V_z = KV_x V_y$  を単純にスケールダウンしたものです。したがって、スケール・ファクタ誤差は図 2 に描かれているように双曲放物面になるはずですが、大きさはずっと小さくなります。図 5 は 2 次元コンター (Iso-ver) で表したものです。非線形性  $f(X,Y)$  の影響は、公称値としては直線となる X 軸または Y 軸に平行な要素に曲率を生じさせます。つまり、XZ 平面または YZ 平面に平行な乗算器出力曲面を通る断面が、直線ではなくなります（図 6）。

図 6: X の非線形性は、任意の Y 値における誤差曲面の断面として見ることが可能。

以上をまとめると、2 入力アナログ乗算器には、「トリミング可能」な静的誤差源が 4 つあります。（13）を参照すると、これらは以下の通りです。

1. X の入力オフセット（線形 Y フィードスルー）

2. Y の入力オフセット（線形 X フィードスルー）

3. 出力オフセット

4. スケール・ファクタ誤差

これら 4 つの誤差の影響は、誤差 1、2、3 に対して大きさが同じで極性が逆のオフセットを導入することによって、さらに 4 に対してスケール・ファクタ（イン）を精密に調整することによって、ゼロにすることができます。4 つの誤差をゼロに調整した後に残る誤差は、乗算器 の本質的な非線形性  $f(X,Y)$  によるものです。一般に非線形性を軽減することはできませんが、特定のケースでは、次の「トランスクンダクタンス乗算器」のセクションで説明されているように、かなりの部分を相殺することができます。

## トランスコンダクタンス乗算器

可変トランスコンダクタンス乗算器は、少なくとも概念的には最も単純なタイプのアナログ乗算器です。一方の入力変数は能動デバイスのゲイン（トランスコンダクタンス）を制御し、これにより、制御入力に比例して他方の入力を増幅します。

アナログ・コンピューティング用および通信用信号処理のための「トランスコンダクタンス」（あるいは「トランスレジスタンス」）乗算器と変調器を作成するために、トランジスタ、FET、真空管などのさまざまな能動デバイスが使われてきましたが、それらの成功の度合はそれぞれ異なります。しかし、現在提供されている「トランスコンダクタンス」乗算器のほとんどすべてが、能動素子としてシリコン接合トランジスタを使用しています。これは、トランジスタのコレクタ電流とトランスコンダクタンスの間に、式（16）に示す線形の一貫した関係が成り立つためです。

$$\frac{dI_c}{dV_{be}} = \frac{q}{kT} I_c \quad (16)$$

ここで、

$I_c$  = コレクタ電流 (A)

$V_{be}$  = ベース・エミッタ電圧 (V)

$q$  = 電荷の単位 =  $1.60219 \times 10^{-19}$  クーロン

$k$  = ボルツマン定数 =  $1.38062 \times 10^{-23}$  joules/ $^{\circ}\text{K}$

$T$  = 絶対温度 ( $^{\circ}\text{K}$ ) =  $^{\circ}\text{C} + 273.15$

$q/kT = 25^{\circ}\text{C}$  で  $1/(25.69 \text{ mV})$

乗算器としての特性は、増分  $\Delta I_c$ 、 $\Delta V_{be}$  (図 7) が十分に小さい場合に見ることができます。

$$\Delta I_c = \frac{q}{kT} I_c \cdot \Delta V_{be} \quad (17)$$

図 7: NPN ツランジスタに使われる記号

式 (16) は、下に示す簡略化した接合部の式を微分することによって得られます\*。

$$I_c = \alpha_N I_{ES} (e^{qV_{be}/kT} - 1) \quad (18)$$

$\alpha_N$  = 電荷移動係数  $\approx 0.99$

$I_{ES}$  = エミッタ飽和電流、 $10^{-12} \sim 10^{-14}$  A @25 °C

この時、ツランジスタのコレクタ・ベース電圧はゼロと仮定します。

$$\frac{I_c}{I_{ES}} \gg 1 ,$$

それでも電流レベルは十分に低いので、オーム抵抗（たとえば、ベース拡散抵抗、エミッタ・コンタクト抵抗、およびバルク抵抗）は無視できます。代表的なモノリシック・デュアル・ツランジスタでは、これはコレクタ電流が 100 μA 以下であることを意味します。100 μA の場合、トランスコンダクタンスは 26 °C で約 1/260 mho です。モノリシック・ツランジスタの代表的な寄生抵抗値は約 3 Ω ですが、これは、トランスコンダクタンスを約 1 % 減少させます。

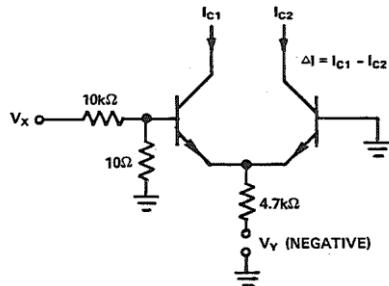

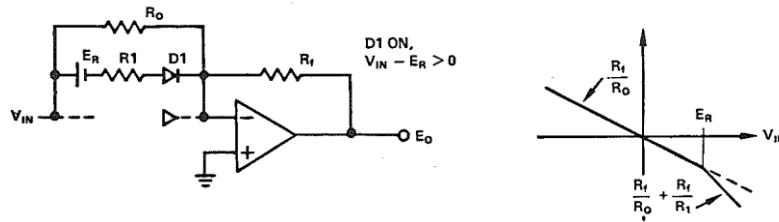

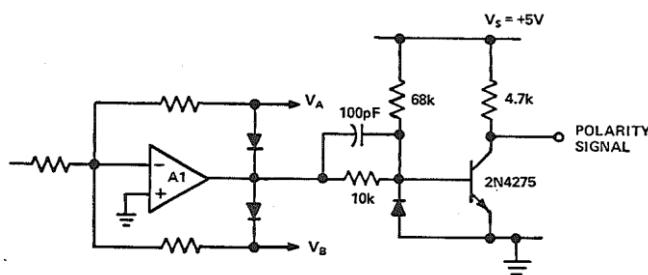

簡単な 2 象限可変トランスコンダクタンス乗算器は、図 8 に示すように、1 対のツランジスタといくつかの抵抗を使って構成できます。この乗算器の出力を Q1 と Q2 のコレクタ電流の差と見なすと、この回路の出力と入力の関係は式 19 と 20 で表されます。

$$I_{c_1} - I_{c_2} = \Delta I_c = \frac{q}{kT} \frac{V_y + 0.6}{4.7 \times 10^3} \cdot 10^{-3} V_x \quad (19)$$

$$\Delta I_c = 8.3 \times 10^{-6} (V_y + 0.6) V_x \quad \text{at } 25^\circ\text{C} \quad (20)$$

\* 3-1 項の式 (6) を参照。

図 8: 簡単な 2 象限可変コンダクタンス乗算器

式 (20) が示すように、出力のコレクタ電流の差は、入力電圧  $V_x$  と  $V_y$  の積に比例しますが、以下の制約があります。

1. Y 入力には、Q1 と Q2 の仮定された（一定の） $V_{BE}$  による 0.6 V のオフセットがあります。したがって、受け入れ得る  $V_y$  の最も正側に近い値は -0.6 V です。また、 $V_{be}$  は一定ではありません。Q1 と Q2 の  $V_{be}$  は  $|V_y|$  の増加に伴って増加し、Y 入力に非線形性を生じさせます。これらの問題は、Y 入力の抵抗に代えて、より精巧な電圧電流コンバータを使用することによって解決できます。

2. スケール・ファクタは温度の関数で、25 °C 付近では  $-0.33\%/\text{°C}$  の率で減少します。これは、X 入力に温度補償抵抗を使用することで解決できますが、精密な補償を行うことは困難です。

3. 式 (18) に示すようにコレクタ電流とベース・エミッタ電圧は指数関係にあるので、X 入力は非線形です。X 入力に 1000:1 の減衰器を使用すれば  $\pm 10 \text{ V}$  のレンジが 2 つのベース間で  $\pm 10 \text{ mV}$  になるので、実際の X 信号は熱電圧  $kT/q$  ( $25.69 \text{ mV} @ 25 \text{ °C}$ ) 未満になります。ただし、この小さい信号でも X 入力信号には 7 % の非線形性が生じます。この非線形性は X 入力の減衰を大きくすることによって小さくできますが、代償として S/N 比が減少してしまいます。

以上のような理由から、差動ペアは、高レベルのアナログ乗算器として特に有用、あるいは魅力的というわけではありません。しかし、受信信号がすでに十分に小さい（数ミリボルト以下）RF アプリケーションのミキサーとしては、極めて有効です。

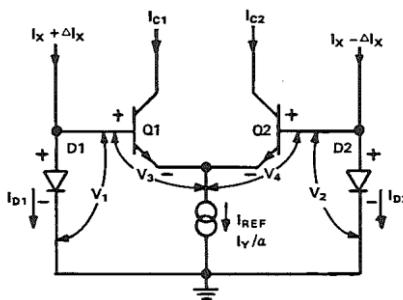

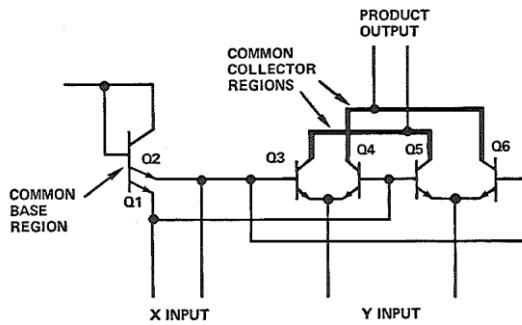

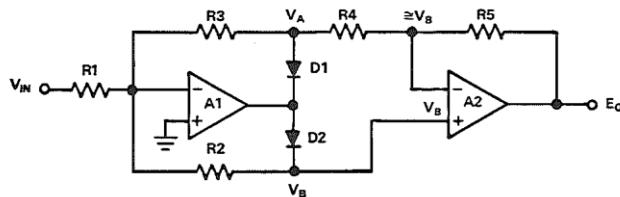

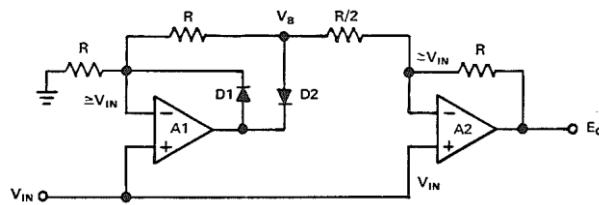

非線形性、ダイナミック・レンジの制約、温度係数など、簡単な差動ペアの問題点に対しては、適切かつ本質的に単純な解決策があります<sup>1</sup>。ギルバート回路は、誤差が少ない（約 1%）上に帯域幅が広く (>100MHz が可能)、しかも比較的単純なので、短期間に広く使われるようになりました。実際、今では「トランスコンダクタンス」乗算と同義語になっています。図 9 に示す基本回路は、ダイオード（またはダイオード接続したトランジスタ\*\*) の指数特性を使って、差動ペアのベース入力（以後、便宜上「X」入力と記します）の指數非線形性を補償します。

バランスが取られた X 入力電流  $I_{D1}$  と  $I_{D2}$  がダイオード D1 と D2 を通過して、電圧  $V_1$  と  $V_2$  を発生させますが、これらの電圧は電流の対数に比例します ( $\alpha_N \approx 1$ )。

$$V_1 = \frac{kT}{q} \ln \frac{I_{D1}}{I_{ES1}} \quad (21)$$

$$V_2 = \frac{kT}{q} \ln \frac{I_{D2}}{I_{ES2}} \quad (22)$$

図 9: 線形化した 2 象限乗算器（原理）

<sup>1</sup> "A new Wide-Band Amplifier Technique," by Barrie Gilbert, *IEEE Journal of Solid-State Circuits*. December, 1968, Volume SC-3, No. 4, pp. 353-365.

$Q_1$  と  $Q_2$  のコレクタ電流はそれらのベース・エミッタ電圧（式 18）または差動入力電圧 ( $V_{BE1}$  -  $V_{BE2}$ ) の指数関数なので、 $D_1$  と  $D_2$  によって与えられる対数入力電圧が、 $Q_1$  と  $Q_2$  の指数非線形性をすべてではないにしてもある程度相殺し、結果として  $I_{D1}$ 、 $I_{D2}$  と  $I_{C1}$ 、 $I_{C2}$  の関係は線形になると仮定することは合理的です。実際、線形化は理論的には完璧であり、実際の回路でもほぼ完璧で、驚くほど有用な結果が得られます。これは、以下のように証明できます。

仮定:

1.  $I_{C1} = I_{C2}$  および  $I_{D1} = I_{D2}$  の場合、 $Q_1$ 、 $Q_2$  および  $D_1$ 、 $D_2$  のペアの差動オフセット電圧はゼロ。

2.  $Q_1$ 、 $Q_2$ 、 $D_1$ 、 $D_2$  は理想接合部の式 (18) に従う。

$D_1$  の陰極から  $Q_1$ 、 $Q_2$ 、さらに  $D_2$  の陰極へと続くループの周りの電圧  $V_1$  ~  $V_4$  の合計は、ゼロでなければなりません。

$$V_1 - V_3 + V_4 - V_2 = 0 \quad (23)$$

$$V_1 - V_2 = V_3 - V_4 \quad (24)$$

$Q_1$ 、 $Q_2$  のベース・エミッタ電圧は、そのコレクタ電流の対数に比例します。

$$V_{BE1} = V_3 = \frac{kT}{q} \ln \frac{I_{C1}}{I_{ESQ1}} \quad (25)$$

$$V_{BE2} = V_4 = \frac{kT}{q} \ln \frac{I_{C2}}{I_{ESQ2}} \quad (26)$$

これらを (24) の  $V_1$  ~  $V_4$  に代入します。

$$\frac{kT}{q} \ln \frac{I_{D1}}{I_{ES1}} - \frac{kT}{q} \ln \frac{I_{D2}}{I_{ES2}} = \frac{kT}{q} \ln \frac{I_{C1}}{I_{ESQ1}} - \frac{kT}{q} \ln \frac{I_{C2}}{I_{ESQ2}} \quad (27)$$

$kT/q$  項を削除して対数の差を比の対数として書き直すと、次式が得られます。

$$\ln \frac{I_{D_1} I_{ES_2}}{I_{D_2} I_{ES_1}} = \ln \frac{I_{C_1} I_{ESQ_2}}{I_{C_2} I_{ESQ_1}} \quad (28)$$

すでに仮定したように、トランジスタとダイオードのマッチングが取られていれば定数はすべて同じで、次式が得られます。

$$\ln \frac{I_{D_1}}{I_{D_2}} = \ln \frac{I_{C_1}}{I_{C_2}} \quad (29)$$

比の対数が等しいなら、比も等しくなければなりません。

$$\frac{I_{D_1}}{I_{D_2}} = \frac{I_{C_1}}{I_{C_2}} \quad (30)$$

この結果は重要で、「出力」電流  $I_{C_1}$  と  $I_{C_2}$  の比は、温度や電流の大きさに関わらず、入力電流  $I_{D_1}$  と  $I_{D_2}$  の比に比例することを示しています。つまり、概念的には線形化は完璧であり、X の入力から出力への伝達特性は温度によらず一定です。

乗算器の関係は (30) から直接導くことができます。X 入力は、2 つのダイオード電流  $I_{D_1}$  と  $I_{D_2}$  の差  $2\Delta I_x$  であると仮定します。Y 入力がエミッタ電流  $I_{REF}$  を制御します。乗算器の出力は、Q1 と Q2 のコレクタ電流の差  $2\Delta I_C$  です。

$$I_{D_1} = I_x + \Delta I_x \quad (31)$$

$$I_{D_2} = I_x - \Delta I_x \quad (32)$$

$$-I_x < \Delta I_x < I_x \quad (33)$$

$$I_{C_1} + I_{C_2} = \alpha I_{REF} \cong I_y \quad (\alpha \cong 1) \quad (34)$$

$Q_1$ 、 $Q_2$  および  $D_1$ 、 $D_2$  は整合していると仮定し、 $Q_1$  と  $Q_2$  は高い  $\beta$  値 ( $> 100$ 、 $\alpha \approx 1$ ) を有しています。

$$I_{C1} = I_y/2 + \Delta I_c/2 \quad (35)$$

$$I_{C2} = I_y/2 - \Delta I_c/2 \quad (36)$$

$$-I_y/2 < \Delta I_c < I_y/2, \quad I_y > 0 \quad (37)$$

これを (29) の  $I_C$  と  $I_D$  に代入します。

$$\frac{I_x + \Delta I_x}{I_x - \Delta I_x} = \frac{I_y/2 + \Delta I_c/2}{I_y/2 - \Delta I_c/2} \quad (38)$$

さらに代数的に整理すると、次式が得られます。

$$\Delta I_c = \frac{\Delta I_x \cdot I_y}{I_x} \quad (39)$$

出力電流は、X 入力の差分電流  $\Delta I_x$  と Y 入力の電流の積に比例し、X の静電流  $I_x$  に逆比例します。 $I_x$  は、2 象限乗算器（バイポーラ  $\Delta X$  入力とユニポーラ Y 入力）としてのスケール・ファクタを決定していると見ることができます。この回路は 2 象限除算器としても機能し、この場合は  $I_y$  が一定、分母 ( $I_x$ ) がユニポーラ、分子 ( $\Delta I_x$ ) がバイポーラです。この線形化乗算器（図 9）は非常に優れた性能を備えており、以下の点で、単純な差動乗算器よりも大幅に改善されています。

1. 広い帯域幅: 回路は基本的に「電流モード」です。数 mA の電流レベルでは、100 MHz を超える帯域幅が得られます。乗算器で通常使われる低い電流レベル (< 1 mA) では、1 ~ 10 MHz の帯域幅が容易に得られます。

2. 優れた線形性: 式 (39) は、入力と出力の関係が正確に乗算であることを示しています。実際には多少の誤差 (< 1 %) がありますが、これについては後述します。

それでも、線形化されていない乗算器より大きく改善されています。

3. 優れた温度安定性: 式 (39) は、入力と出力の関係が温度に依存しないことを示しています。実際の回路にはわずかな温度依存性があり、その一部は温度によるトランジスタの  $\beta$  の変化によります ( $\beta$  の影響は無視できると仮定して (39) を導き出しました)。温度に伴うゲイン変化は  $0.02\%/\text{^\circ C}$  以下に抑えることができますが、これは、単純な差動乗算器 ( $0.3\%/\text{^\circ C}$ ) より 1 枠以上改善されています。

4. 広いダイナミック・レンジ: X (ベース) 入力が線形化されているので、ほぼ  $-I_x < \Delta I_x < I_x$  と等しい範囲にわたって X 入力電流の比を変化させることができます、差動ペアよりもはるかに大きい入力信号を使うことができます。

これらの利点の結果として、線形化された「ゲイン・セル」が、乗算器の汎用ビルディング・ブロックとしてほぼ例外なく受け入れられるようになりました。これは、わずかに変更を加えると、2 象限乗算回路として直接使用できます。

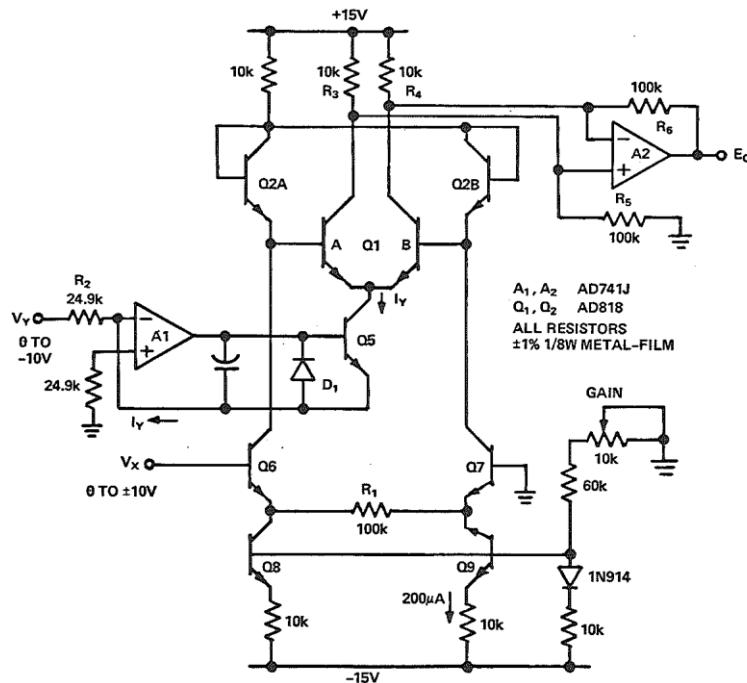

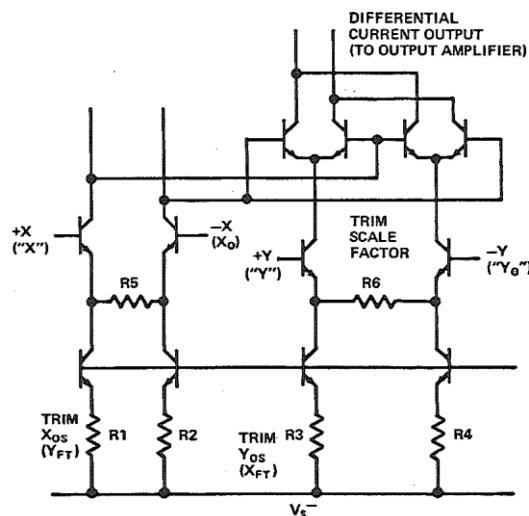

## 2 象限乗算器

図 10 の回路は、実際に機能する 2 象限乗算器の例です。差動 X 入力電流は、抵抗 R1 によってエミッタを結合した差動ペア Q6、Q7 から得られます。定電流源 Q8、Q9 は、Q6、Q7 のエミッタに  $I_x$  バイアスを提供します。 $100\text{ k}\Omega$  のエミッタ抵抗 R1 は、入力電圧  $V_x$  1 ボルトあたりの差動 X 電流  $\Delta I_x$  を決定します。

X 入力電流は、図 9 の回路のようにコレクタ（つまり陽極）を駆動するのではなく、ダイオード接続トランジスタ\*\* Q2A と Q2B のエミッタを駆動します。この「反転」接続はエミッタが低インピーダンスで、X 入力段 Q6、Q7 からの電流をいつでも受け入れることができるので、駆動がずっと容易です。「反転」回路と基本電流セルの実用上の唯一の違いは、出力も反転することです（つまり入力と  $180^\circ$  位相が違います）。

これは、出力アンプの位相を正しく設定することによって、簡単に修正できます。

Y 入力電流は、クローズド・ループ制御された電流源 A1-Q5 から得られます。Q5 の  $\beta$  が非常に高い ( $> 400$ ) 場合は Q5 のコレクタ電流が  $V_y/R_2$  となります。誤差は無視できる程度です。ダイオード D1 は、Y の入力電圧が正になった時に、Q5 のベース・エミッタ接合がブレークダウンを起こさないように保護します。差動出力電流 (Q1A-Q1B のコレクタ間) は、ダイナミック・ブリッジ R3、R4、R5、R6、および A2 によってシングルエンド電圧に変換されます。これらの抵抗は、Y 入力信号に伴う同相入力電圧の変化による出力電圧誤差を最小限に抑えるために、極めて正確に (0.1 %) 整合していかなければなりません。

図 10: 実際の 2 象限可変トランジスタコンダクタンス乗算器

2 象限乗算器は、1 つの入力のフィードスルーを非常に低くする必要がある場合、特に有用です。Y 入力がゼロの状態では、出力は入力から実効的に切断されて、X 入力信号を少なくとも 80 dB 減衰します。

この利点には欠点が伴います。Y 入力が小さくなると、Q1A と Q1B の電流が減少して回路の帯域幅が狭くなります。

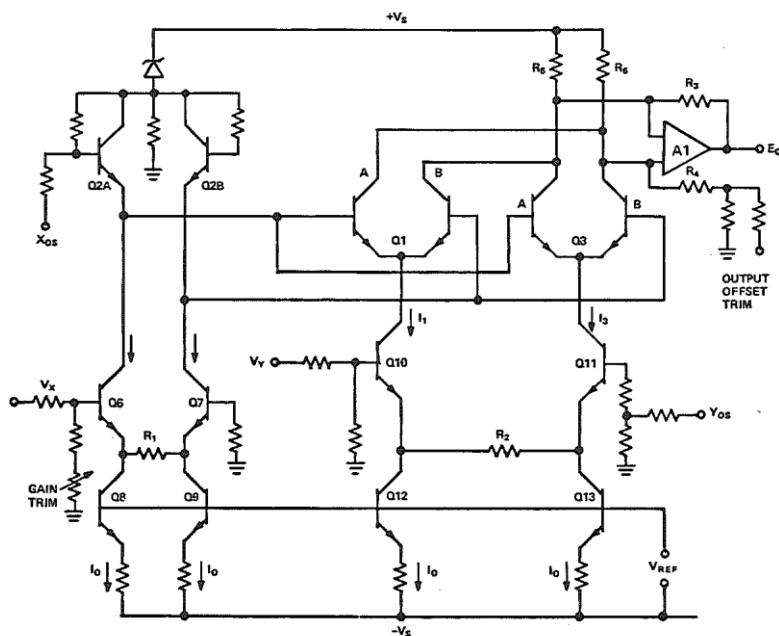

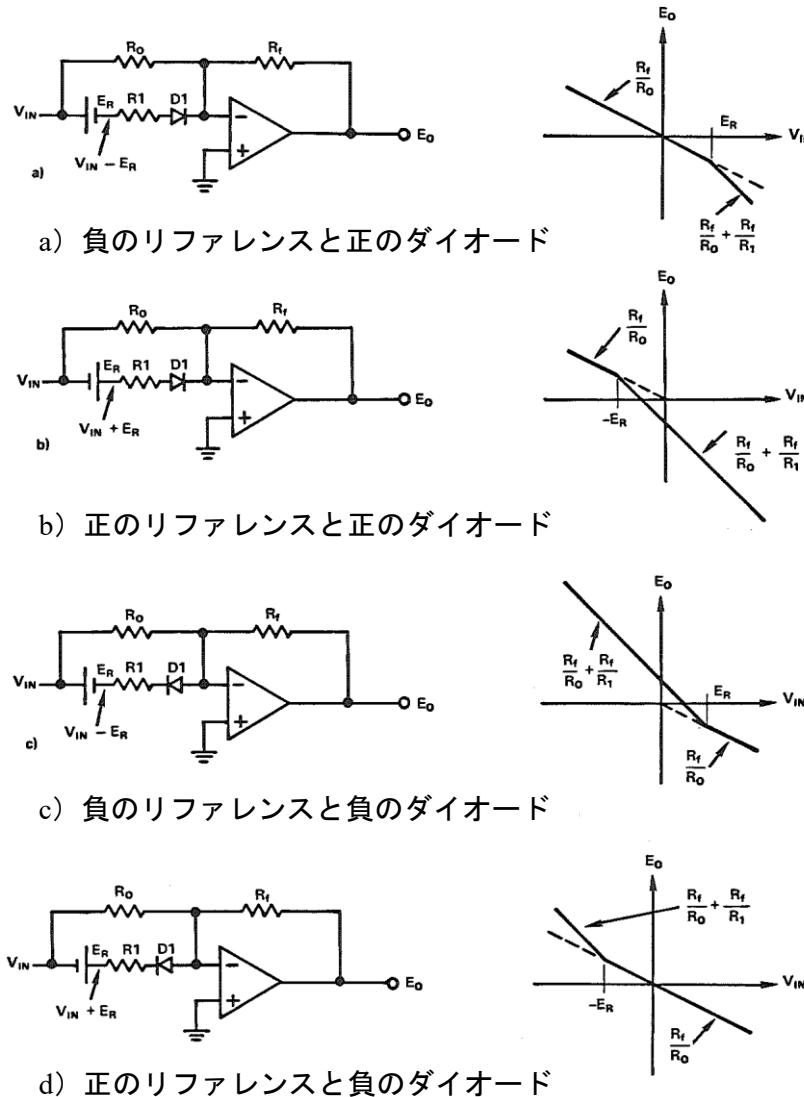

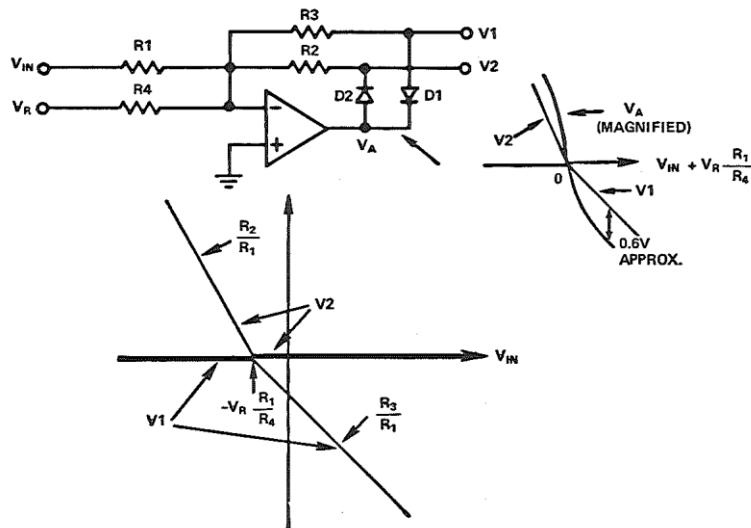

#### 4 象限乗算器

基本的な 2 象限線形化乗算器回路は、X 入力または Y 入力のどちらにもバイポーラ信号を受け入れて、4 象限で動作するように拡張できます。これは、2 番目の差動ペア Q3A-B を追加することによって実現されます。追加差動ペアのベースは、図 11 に示すように Q1 のベースと並列に接続します。追加ペアのコレクタは Q1A-B のコレクタにクロス接続します。2 象限乗算器のシングルエンド Y 電流源は、X 電流源と同じ差動電流源 Q10、R2、Q11 に置き換えられます。

図 11: 4 象限可変トランスクンダクタンス乗算器

2つある Y 電流源の一方の出力は Q1A-B のエミッタに、もう一方は Q3A-B のエミッタに接続されています。したがって、 $V_y$  は差動ペア Q1A-B を流れる電流と Q3A-B を流れる電流の比を変化させ、それらの相対ゲインを制御します。例えば、 $Y=0$  の場合は  $I_1=I_3$  となり、2つのペアのゲインが等しくなります。これらのペアのコレクタはクロス結合されていて（ベースは並列）出力が相殺されるので、X 入力の信号の正味ゲインはゼロです。この「バランス」状態では、 $V_y=0$  の場合、X 入力はヌル化されます。

$$E_o = V_x \cdot 0 = 0 \quad (40)$$

Y 入力にゼロ以外の電圧が加わると、電流  $I_1$  と  $I_3$  はアンバランス状態になります。

$$I_1 = I_{10} + V_y/R_2 \quad (41)$$

$$I_3 = I_{30} - V_y/R_2 \quad (42)$$

このアンバランス状態により、2つのペア Q1A-B と Q3A-B のゲインはもはや相殺されないので、X 入力信号が乗算器の出力に現われます。Y 入力が正の場合は  $I_1$  が  $I_3$  より大きくなって Q1A-B のゲインが優勢となるので、正の出力電圧が生じます（正の X に対して）。これに対し、Y 入力が負の場合は Q3A-B のゲインが優勢となり、正の X 入力に対しては負の出力電圧が、負の X 入力に対しては正の出力電圧が生じます。

Y 入力から出力への信号伝達動作は、2象限乗算器での動作に似ています。X 入力がゼロで、Q1、Q2、Q3 の各トランジスタ・ペアが整合していれば、Q1A-B の側と Q3A-B の側の間で電流  $I_1$  と  $I_3$  の変化が均等に分割されるので、Y の値に関わらず出力はゼロになります。

$$E_o = 0 \cdot V_y = 0 \quad (43)$$

乗算器の全体的な出力と入力の関係は、以下のように (39) から導くことができます ( $I_0 = I_x$ )。Q1A-B の出力は次式で表されます。

$$\Delta I_{C_1} = \frac{\Delta I_x I_1}{I_0} \quad (44)$$

同様に、Q3A-B については次式が成り立ちます。

$$\Delta I_{C_3} = \frac{\Delta I_x I_3}{I_0} \quad (45)$$

Q1A-B と Q3A-B のコレクタはクロス結合されているので、出力電流が差し引かれます。差は  $\Delta I_c$  です。

$$\Delta I_c = \Delta I_{C_1} - \Delta I_{C_3} \quad (46)$$

$$\Delta I_c = \frac{\Delta I_x}{I_0} (I_1 - I_3) \quad (47)$$

(41) と (42) から  $I_1$  と  $I_3$  を代入すると、次のようになります。

$$\Delta I_c = \frac{\Delta I_x}{I_0} (I_{10} + V_y/R_2 - I_{30} + V_y/R_2) \quad (48)$$

さらに、 $I_{10} = I_{30}$  なので、次式が得られます。

$$\Delta I_c = 2 \frac{\Delta I_x}{I_0} \cdot \frac{V_y}{R_2} \quad (49)$$

正味差動出力電流は、2 象限乗算器の場合と同様に、A1 と R3、R4、R5、R6 によってシングルエンド出力電圧に変換されます。

$$E_o = \Delta I_c R_3 \quad (50)$$

(50) は次のように整理することができます。

$$E_0 = \frac{2R_3}{R_1 R_2 I_0} V_x \cdot V_y \quad (51)$$

$$-I_o R_2 < V_y < I_o R_2 \quad (52)$$

$$-I_o R_1 < V_x < I_o R_1 \quad (53)$$

乗算器のスケール・ファクタは  $R_3/R_1R_2I_0$  によって設定され、求められる次元  $V^{-1}$  になります。

#### 4 象限トランスコンダクタンス乗算器の性能

可変トランスコンダクタンス乗算器の全体性能は優れたものであり、電子アナログ乗算器の最も一般的なタイプとなっています。ギルバート型線形化乗算器の成功の理由は 3 つあります。

1. 良好的な精度: フルスケールの  $\pm 1\%$  未満の全体誤差 (10 V で 100 mV) を簡単に実現できます。誤差は入力レベルに比例し、入力がゼロに向かうと誤差もゼロに近付きます (ゼロに調整可能な DC オフセットを除く)。実際に、「非線形」誤差の最大値は簡単な線形方程式で示すことができます。

$$\epsilon(X, Y) = \frac{\epsilon_x}{100} V_x + \frac{\epsilon_y}{100} V_y \quad (54)$$

ここで、

$\epsilon_x = X$  入力の規定された非線形性 (%)

$\epsilon_y = Y$  入力の規定された非線形性 (%)

2. 広い帯域幅: 電圧出力乗算器で最大 10 MHz、電流出力で 100 MHz 以上。帯域幅が 10 MHz 未満の場合、帯域幅は信号レベルや入力パス (X または Y) には依存しません

3. 比較的単純で低価格: 可変コンダクタンス乗算器は、「ディスクリート」部品を使って構成するか、「モノリシック」で作成することができます。いずれの場合も、本質的に回路が単純で一定した性能が得られるので、他のいかなる 4 象限乗算器より低価格です。以降ではこれらの要素についてより詳しく解説し、実際の回路や部品の要件に関連付けていきます。

### トランスコンダクタンス乗算器の精度に影響を与える要素

これまでの可変トランスコンダクタンス乗算器の説明では、トランジスタが理想接合方程式に従い、トランジスタが完璧に整合しており、電流ゲインが無限大であると仮定しました。また、対称パス内の電流は、信号の注入によって生じる違いを除き、すべて等しいと仮定しました。実際の回路では、トランジスタや抵抗は「理想的」ではなく、完璧に整合することは（まず）決してありません。これらの不整合や「理想」動作からのずれは、線形誤差（入力および出力オフセット、スケール・ファクタ誤差）や非線形誤差（2 次および 3 次高調波歪み）を発生します。

この章の冒頭で示したように、線形誤差は理論的にはゼロに調整可能で、実際の回路でも無視できるレベルにまで調整することができます。図 11 には 4 つのトリム・ポイントが示されています。

1. X オフセット: 線形 Y フィードスルーをゼロに調整するために使用します。

2. Y オフセット: 線形 X フィードスルーをゼロに調整します。

3. 出力オフセット

4. スケール・ファクタ、つまりゲイン。

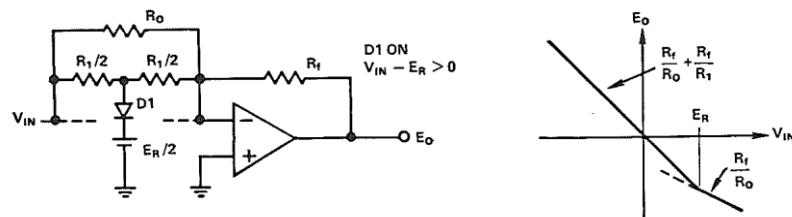

## 非線形誤差

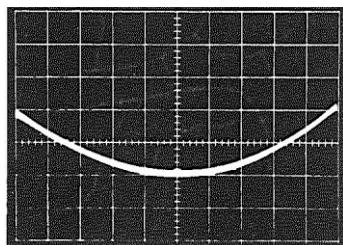

可変トランジスタコンダクタンス乗算器における非線形の主な発生源は、2つの差動ペア Q1A-B と Q3A-B の間の電流のアンバランスか、オフセット電圧の不整合です。これらのペアのオフセット間に  $500 \mu\text{V}$  の不整合があると、X 入力に（フルスケールの）1% の非線形性とフィードスルーが生じます。図 12 に示すように、この非線形性は  $V_x^2$  に比例します。幸い、ディスクリート回路では特性の近いものをペアに組むことができ、集積回路内では「同じ」トランジスタをレイアウトすることができるので、平均オフセットの不整合が  $500 \mu\text{V}$  未満の場合、X の非線形性は通常 1% 未満です。

図 12: 放物線状の X の非線形性

X の 2 次非線形性は Y の入力信号振幅にはあまり依存しないので、以下に説明するように、 $X^2$  で表される非線形性は、X 入力信号の一部を Y 入力にクロス結合することによって大幅に減らすことができます。

$X^2$  で表される非線形性のもう 1 つの発生源として考えられるのは、 $V_x = 0$  の時に、ダイオード接続トランジスタ\*\* Q2A と Q2B を流れる電流のアンバランスです。これらの電流は、正確に整合した抵抗を X の電流源に使用することによって等しくすることができます。

図 13 に示すように、X 入力は、ある条件下では著しい 3 次 (S 字形) の非線形性を示すことがあります。3 次歪みは、差動ペア Q1A-B と Q3A-B のエミッタ抵抗のオーミック成分によって生じます。

オーム（定）抵抗は、 $qI_c/kT$  の理論値からトランスクタンスを減少させて、非線形性を生じさせます。高速乗算器は高電流で動作するので、オーム抵抗によるこれらの非線形性のために速度と精度のトレードオフが避けられなくなると見なされます。

トランスクタンス乗算器の Y 入力の非線形性は比較的小さく、通常  $\pm 0.1\% \sim \pm 0.2\%$  です。差動ペア Q1A-B と Q3A-B のオフセット電圧の不整合と、初期 Y 入力電流のアンバランスが Y の非線形性とフィードスルーに与える影響は無視できる程度であり、常に低い値を示します。

図 13: 3 次 X 非線形性

エミッタ抵抗が  $kT/qI_c$  ( $I_c = 1 \text{ mA}$  で  $26 \Omega$ 、 $T = 300^\circ\text{K}$ ) と比べて大きくな場合、差動電流コンバータへの X と Y の入力電圧は、非線形性を生じる可能性があります。

### トランスクタンス乗算器の動特性

トランスクタンス乗算器は基本的に電流モード回路なので、帯域幅が広く、過渡応答が高速です。100 MHz 以上の電流出力帯域幅は、乗算器のトランジスタを 10 mA 以上のエミッタ電流で動作させることによって実現できます。しかし、最良の DC 精度を得るために設計された回路は、これよりずっと低い  $10 \mu\text{A} \sim 1 \text{ mA}$  の電流で動作し、帯域幅は 1 ~ 10 MHz です。帯域幅の制限は主に出力アンプによるもので、このアンプはコレクタ電流の差を出力電圧に変換します。

4 象限可変トランスクタンス乗算器の帯域幅は X または Y 入力に関して同じであり、出力アンプのスルーレートの制限を除き、信号レベルには依存しません。

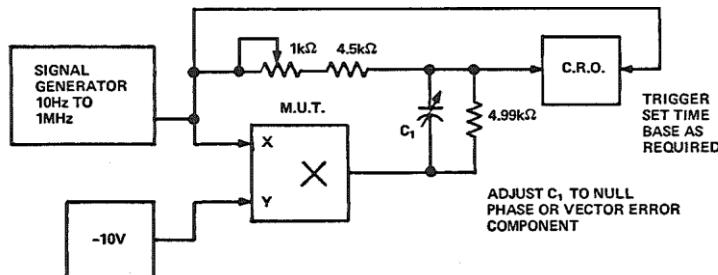

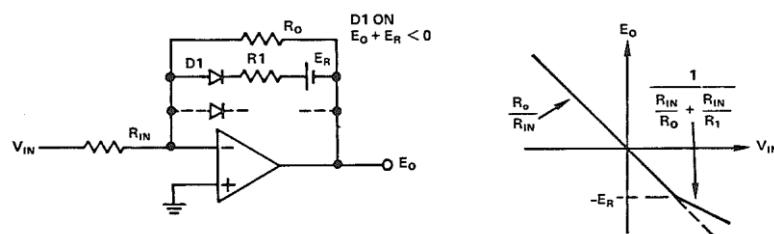

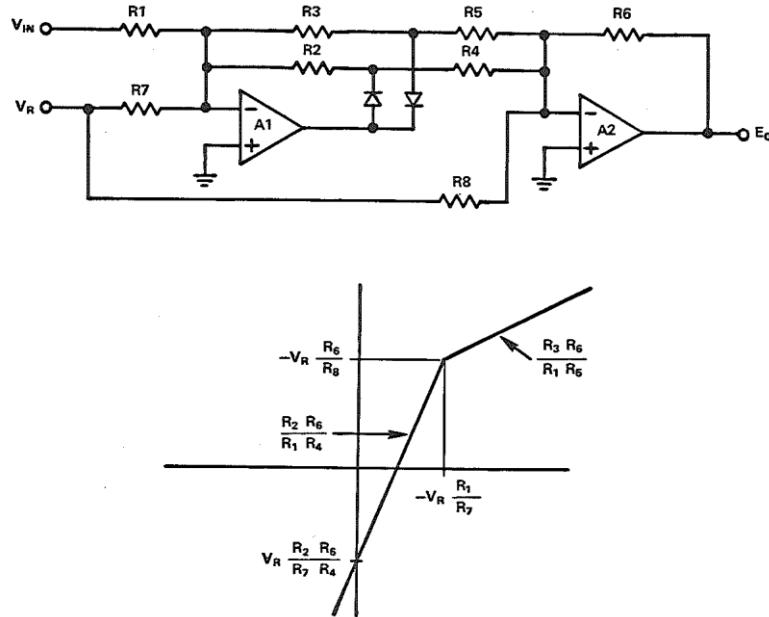

## トランスコンダクタンス乗算器の線形化

図 11 の 4 象限可変トランスコンダクタンス乗算器回路で顕著なのは、上に述べた理由から、X 入力の 2 次非線形性とフィードスルーです。Y 入力の非線形性は、通常、「X」の歪みに比べると無視できる程度です。すべての 1 次誤差（線形フィードスルー、出力オフセット、スケール・ファクタ誤差）をゼロに調整した場合、乗算器の入力と出力の関係は、次式により高い精度で近似できます。

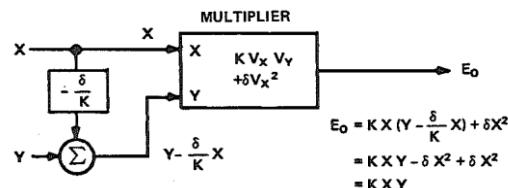

$$E_o = KV_x V_y \pm \delta V_x^2 f(V_y) \quad (55)$$

非線形項  $\delta V_x^2 f(V_y)$  が  $V_y$  に依存しない場合（あるいは大きく影響されない場合）は、図 14 に示すように X 入力信号の一部を Y 入力に加えるか Y 入力から引くことによって、 $\delta V_x^2$  の非線形性を相殺することができます。

幸い、 $\delta X^2$  の非線形性が Y 入力に大きく影響されることはないので（つまり  $f(Y)$  はほぼ一定）、この相殺方法は実際の回路でも比較的良好に機能します。通常、フィードスルーの  $X^2$  成分 ( $Y=0$ ) はフルスケールの 0.1 % 未満まで減らすことができ（60 dB でゼロに抑制）、X の非線形性 ( $V_y = 10 V$ ) は半分に減らすことができます。それに応じて、全体の誤差が減少します。

図 14: 2 次高調波歪みを無くすことによる線形性の改善

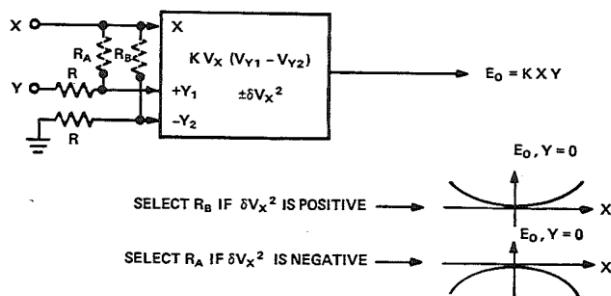

乗算器に X の線形化を適用する方法を図 15 に示します。この方法は、ソース抵抗がかなり低い（ $100 \Omega$  以下）ことと、正負両方（差動）の Y 入力が与えられていることに依存しています。多くの乗算器では（例えばアナログ・デバイセズのこのタイプの乗算器）、 $Y_0$  トリム端子を線形化回路の -Y 入力として使用できます（ただし必ずしも同じ感度ではありません）。

図 15: 乗算器への線形化の適用

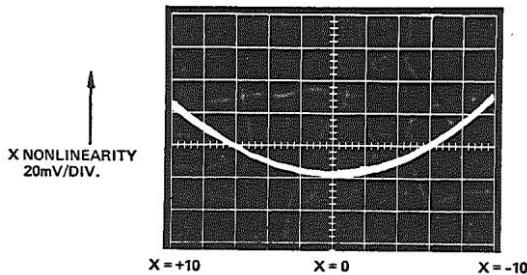

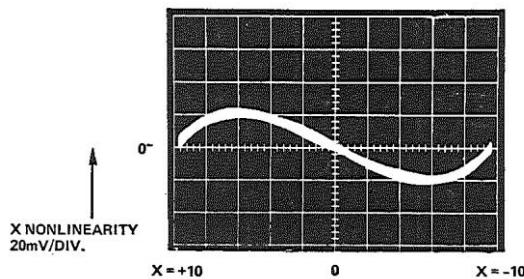

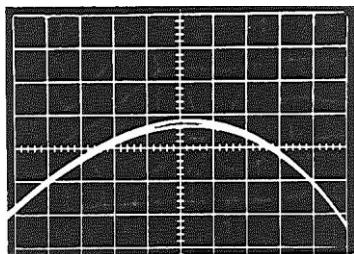

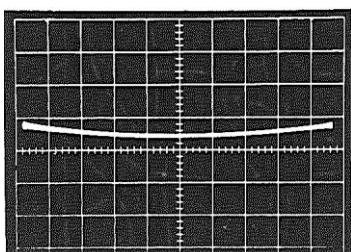

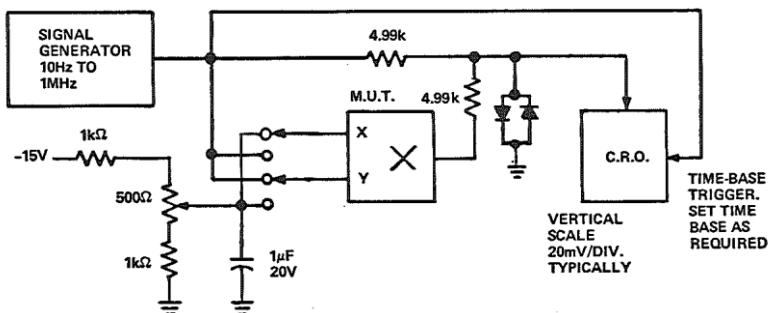

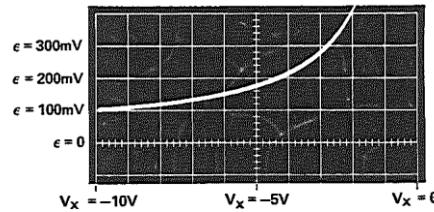

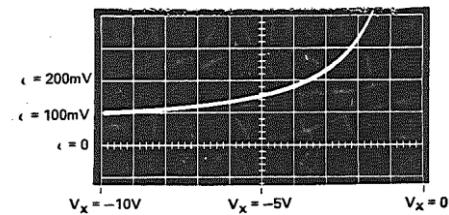

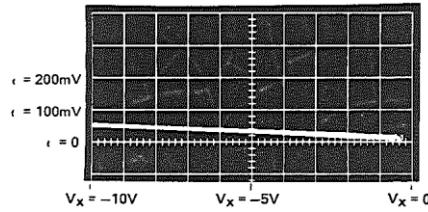

乗算器に対して線形化を行った結果を図 16 ~ 18 に示します。低周波数と高周波数両方のフィードスルーが減少している点に特に注意してください。

Y 入力にはクロス結合による線形化手法を適用できますが、Y の非線形性は何もしなくても一般に非常に小さいので、「収穫遞減の法則」（効果の低減）が当てはまります。

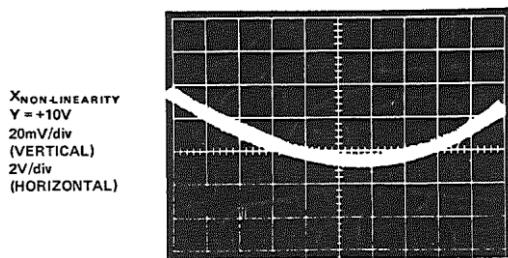

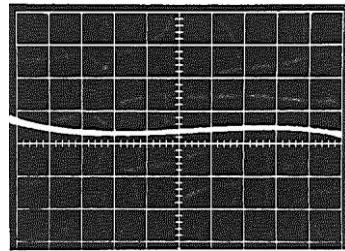

a. 線形化前

b. 線形化後

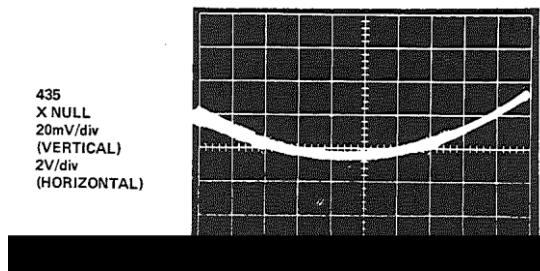

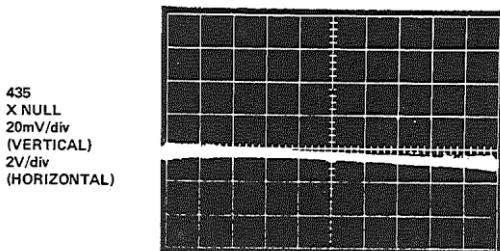

図 16: トランジコンダクタンス乗算器の X の線形化の効果

(X = ±10 V、Y = 0、垂直スケール 20 mV/div.)

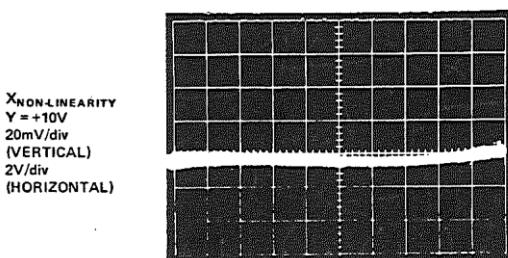

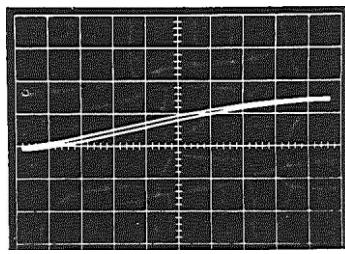

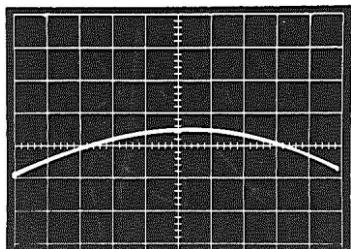

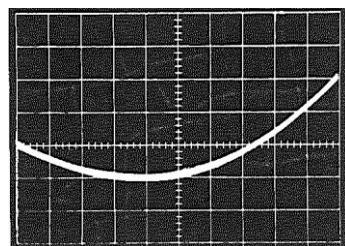

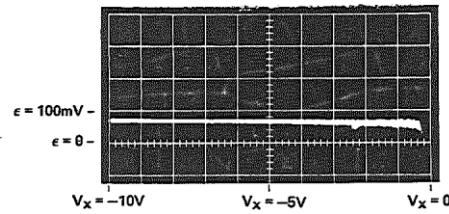

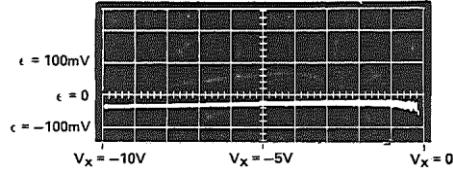

a. 線形化前

b. 線形化後

図 17: 図 16 と同じ乗算器の X の線形化の効果

(X =  $\pm 10$  V、Y = +10 V、垂直スケール 20 mV/div.)

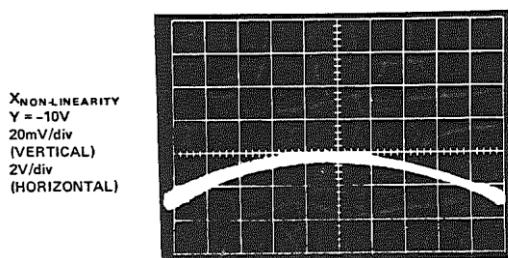

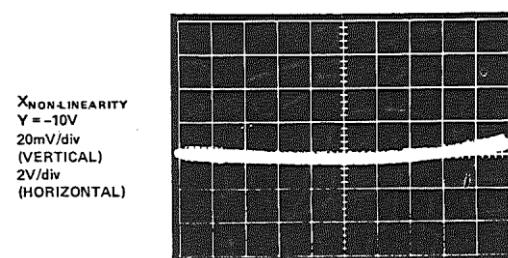

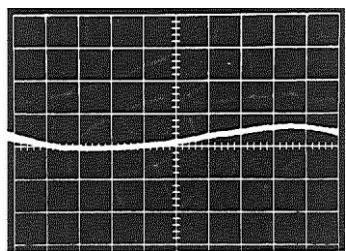

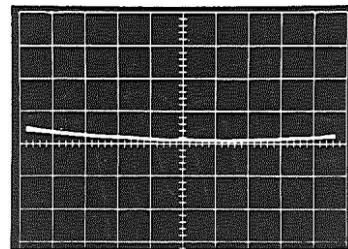

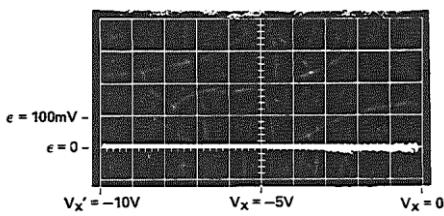

a. 線形化前

b. 線形化後

図 18: 図 16 と同じ乗算器の X の線形化の効果

(X =  $\pm 10$  V、Y = -10 V、垂直スケール 20 mV/div.)

クロス結合線形化手法は、一方または両方の入力に 2 次非線形性があるあらゆる乗算器に適用できます。全体の誤差の減少量は、一方の入力の非線形性が他方の入力の信号レベルからどの程度独立しているのかによって異なります。

一般に、一方の入力の 2 次非線形性を完全に相殺できるのは、他方の入力がある特定の値になった場合だけで、その値は 1 つしかありません。例えば、X のフィードスルーの 2 次成分 ( $X = \pm F.S.$ ,  $Y = 0$ ) は完全に相殺することができますが、X の 2 次非線形性はその一部しか相殺することができます、場合によっては増加してしまうことさえあります。

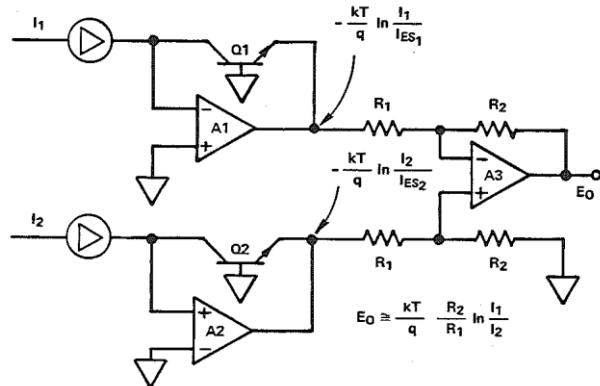

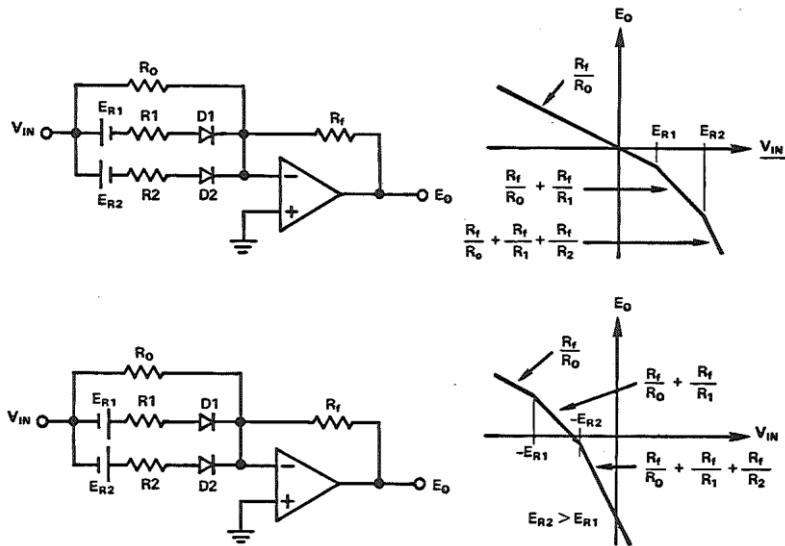

### 対数／逆対数乗算器

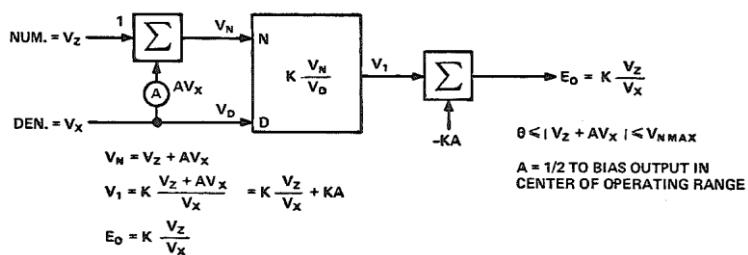

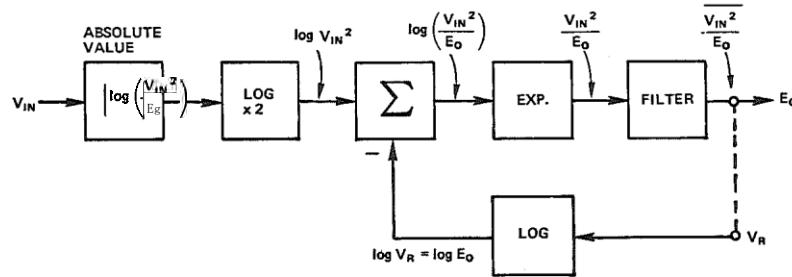

対数／逆対数乗算器は 2 つ以上の変数の対数を加算することによってそれらの積を表すものであり、計算尺の C 尺と D 尺の電気的等価回路です。

$$X \cdot Y = e^{(\ln X + \ln Y)} \quad (56)$$

対数／逆対数乗算器は精度と温度安定性に優れしており、より複雑なパルス変調乗算器に近い性能を示します。誤差がフルスケールの 0.25 % 未満で、ドリフトが 0.01 %/ °C の性能を容易に実現できます。基本的な対数／逆対数乗算器の動作は 1 象限に制限されますが（通常は第 1 象限）、で説明するように、4 つの象限で動作するようにオフセットすることが可能です（オフセット手法、あるいは前出の絶対値／符号絶対値手法は、あらゆる 1 象限乗算器に適用できます）。

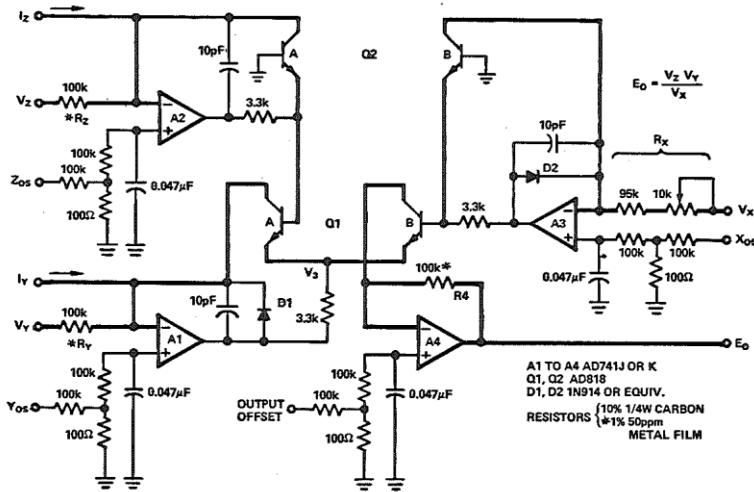

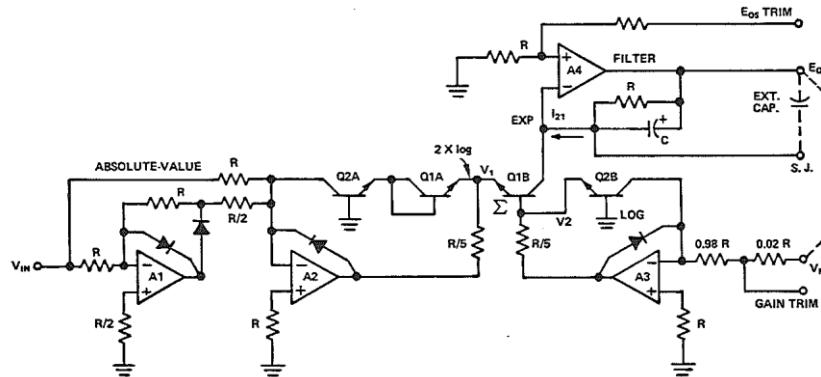

### 回路説明

対数／逆対数乗算器回路は、シリコン接合トランジスタの対数特性に依存しているという点で、トランジスタコンダクタンス乗算器回路と密接に関係しています。

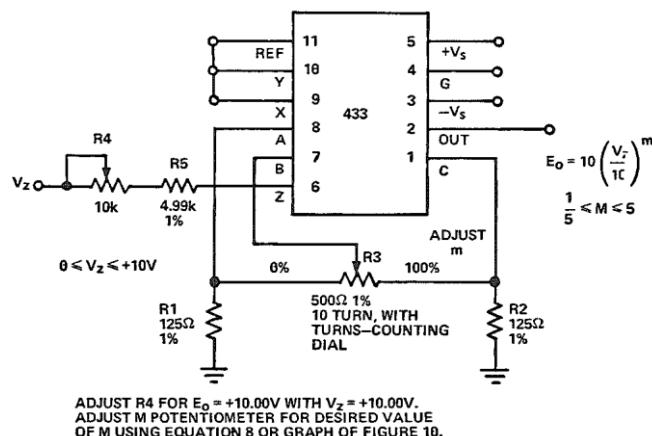

対数／逆対数乗算器の基本構成要素は、3-1 項に詳細を示すパターソン・ダイオード（「トランスタスダイオード」ログアンプ）です。この回路はトランジスタの対数特性を巧みに活用しており（特に低電流時）、アナログ乗算器などのより複雑な回路に簡単に組み込めます。

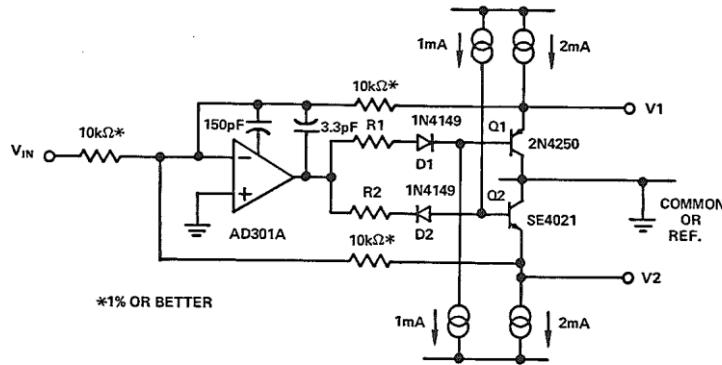

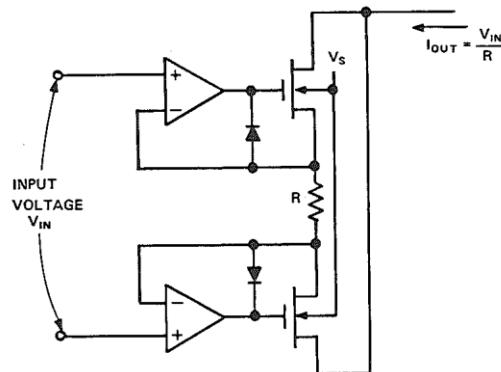

便宜上、図 19 に示す基本的なトランスタスダイオード・ログアンプの動作をここで再度見ておきます。

図 19: 基本的なトランスタスダイオード・ログアンプ

オペアンプ A1 のオフセット電流とオフセット電圧がゼロだと仮定すると、Q1 のコレクタ電流は  $V_{IN}/R$  となります。A1 の出力は Q1 のエミッタを駆動するので、Q1 のエミッタ・ベース電圧は次式で表されます。

$$E_o = V_{EB} = -\frac{kT}{q} \ln \frac{V_{IN}/R}{\alpha_N I_{ES}} \quad (57)$$

$$\alpha \approx 1$$

$$I_{ES} = \text{エミッタ飽和電流、} \sim 10^{-14} \text{ A}$$

$$\alpha_N I_{ES} = I_0 \text{ とします。}$$

したがって、A1 の出力は入力電圧の対数に比例し、(kT/q と  $I_0$  の両方を通して) 温度によっても変化します。乗算器回路にログアンプを使用すると、温度依存性を無くすことができます。

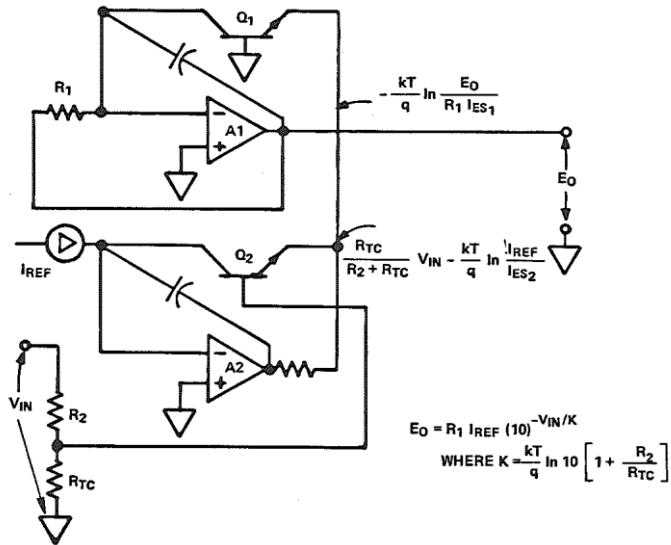

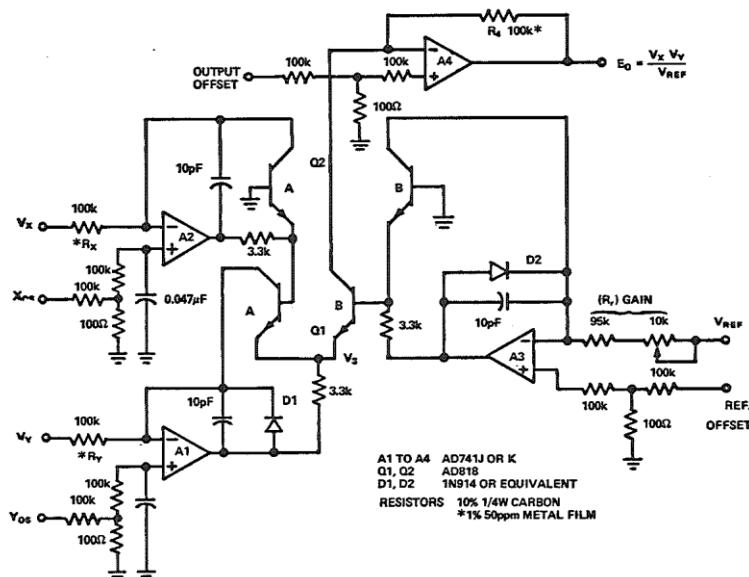

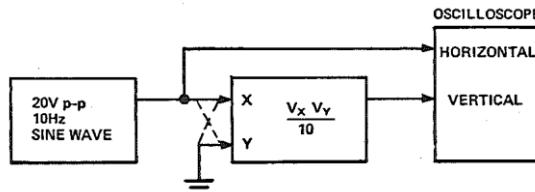

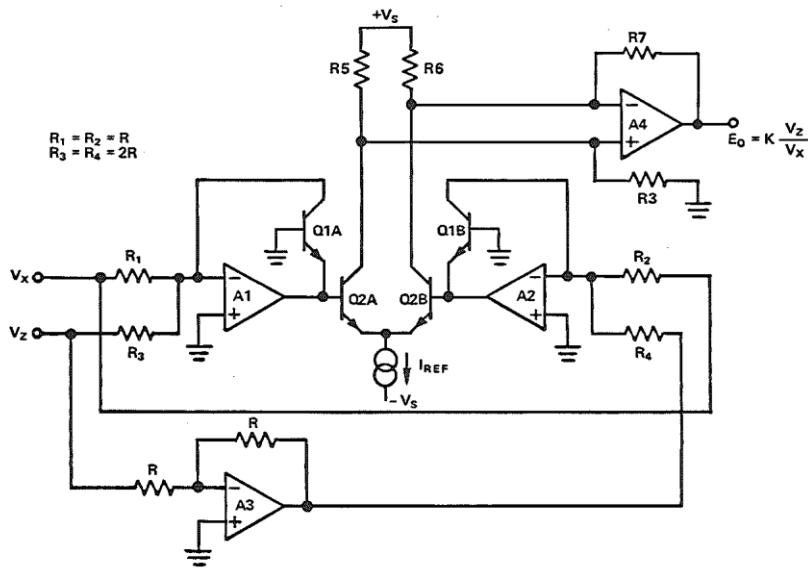

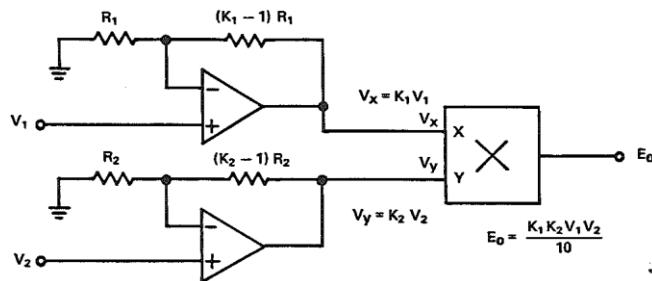

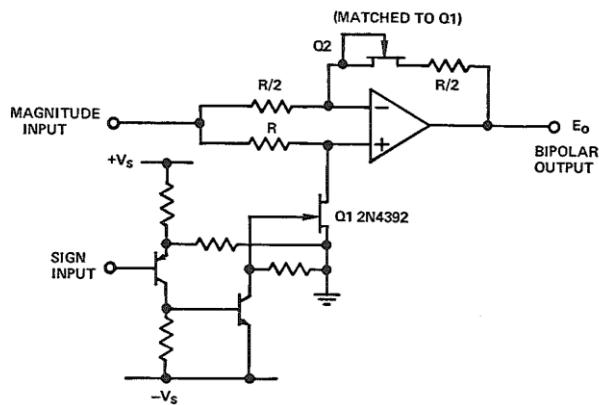

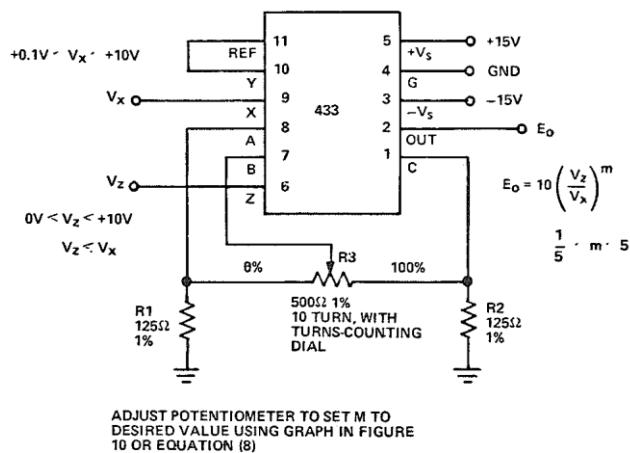

2 入力対数／逆対数乗算器の回路図を図 20 に示します。2 つの入力  $V_x$  と  $V_y$  が、2 つの独立したトランスタスダイオード・ログアンプ A1-Q1A と A2-Q2A を駆動します。

Q2A のベースはグラウンド電位で、Q1A のベースは Q2A のエミッタに接続されています。したがって、Q1A のエミッタの電圧は、以下のように  $V_x$  と  $V_y$  の対数の合計に比例します。

$$V_{EB2A} = - \frac{kT}{q} \ln \frac{V_x}{R_x I_{o2A}} \quad (58)$$

$$V_{EB1A} = - \frac{kT}{q} \ln \frac{V_y}{R_y I_{o1A}} \quad (59)$$

$$V_3 = V_{1_A} + V_{2_A} \quad (60)$$

$$-V_3 = \frac{kT}{q} \left( \ln \frac{V_x}{R_x I_{o2A}} + \ln \frac{V_y}{R_y I_{o1A}} \right) \quad (61)$$

$$V_3 = - \frac{kT}{q} \ln \frac{V_x \cdot V_y}{R_x R_y I_{o_{2A}} I_{o_{1A}}} \quad (62)$$

図 20: 対数／逆対数乗算器

次のステップは、温度依存性を無くすような具合に  $V_3$  の逆対数を取ることです。 $V_3$  は、直列に接続されている Q1 と Q2 の「B」側にあるベース・エミッタ回路の両端に現われることに注意してください。

$$V_3 = V_{EB1A} + V_{EB2A} = V_{EB1B} + V_{EB2B} \quad (63)$$

一定リファレンス入力  $V_{REF}$  を次のように仮定します。

$$V_{EB2B} = -\frac{kT}{q} \ln \frac{V_{REF}}{R_r I_{o2B}} \quad (64)$$

(63) を  $V_{EB1B}$  について解くと次のようにになります。

$$V_{EB1B} = V_{EB1A} + V_{EB2A} - V_{EB2B} \quad (65)$$

$$V_{EB1B} = \frac{kT}{q} \ln \frac{V_x V_y R_r I_{o2B}}{V_{REF} R_x R_y I_{o2A} I_{o1A}} \quad (66)$$

$V_{EB1B} > 100$  mV の範囲では、コレクタ電流はベース・エミッタ電圧に対して指數関係になります。

$$I_{C1B} = I_{o1B} e^{qV_{EB1B}/kT} \quad (67)$$

(66) と (67) を結合すると以下の式が得られます。

$$I_{C1B} = I_{o1B} \exp \left\{ \frac{q}{kT} \frac{kT}{q} \ln \frac{V_x V_y R_r I_{o2B}}{V_{REF} R_x R_y I_{o2A} I_{o1A}} \right\} \quad (68)$$

$$I_{C1B} = \frac{I_{o1B} I_{o2B} V_x V_y R_r}{I_{o1A} I_{o2A} V_{REF} R_x R_y} \quad (69)$$

トランジスタ Q1 と Q2 が單一チップ上に形成されている場合、 $I_0$  項は相殺されます。

$$\frac{I_{o_{1B}}}{I_{o_{1A}}} = \frac{I_{o_{2B}}}{I_{o_{2A}}} = 1 \quad (70)$$

出力アンプ A4 と帰還抵抗 R4 が  $I_{C1B}$  を電圧に変換します。

$$E_o = R_4 \cdot I_{C1B} \quad (71)$$

$$E_o = \left\{ \frac{R_4 R_i}{R_x R_y} \right\} \frac{V_x V_y}{V_{REF}} \quad (72)$$

$$V_x, V_y \geq 0, V_{REF} > 0$$

したがって、図 20 の回路は、温度に影響されない（抵抗が追従できる程度に優れた値となり得る）スケール・ファクタで乗算と除算を行います。出力入力間の伝達関数も、トランジスタの電流ゲイン ( $\beta$ ) には依存しません。

### 対数／逆対数乗算器の性能

実際の対数／逆対数乗算器の真の性能は、示されているように理想乗算器の性能にごく近いものになります。静的な精度誤差と温度ドリフトは非常に小さい値です。対数／逆対数乗算器の主な静的誤差源は以下の通りです。

- トランジスタの対数適合度誤差: フルスケール付近の X 入力または Y 入力に対する対数トランジスタ Q1A と Q2A の電流は、約  $100 \mu\text{A}$  です。この電流レベルでは、エミッタのオーム抵抗の影響が見られるようになり、約 0.1 % の非線形性が生じます。フルスケール電流を  $100 \mu\text{A}$  に制限すれば、非線形性が大きくなるのを防ぐことができます。

2. オペアンプ A1 ~ A4 の入力電流とオフセット電圧は、X、Y、およびリファレンス入力と信号出力に「オフセット」誤差を発生させます。これらのオフセットは約 5 mV 程度で、アンプ A1 ~ A4 のリファレンス（つまり「+」）入力をオフセットすることによって、簡単に 0.1 mV 未満にトリミングできます。

3. 抵抗許容誤差: これはスケール・ファクタに誤差を発生させますが、「ゲイン」ポテンショメータによって調整できます。

4. トランジスタ・ペア Q1A-B と Q2A-B は、1 ミリボルトのオフセットあたり 4 % のスケール・ファクタ誤差を発生させます。この誤差はゲイン・トリミングで除去されます。

対数／逆対数乗算器の温度に対する安定性は良好です。 $R_x$ 、 $R_y$ 、 $R_r$ 、および  $R_4$  に 50 ppm の抵抗を使用した場合、スケール・ファクタのドリフトは、約 0.01 %/ °C です。入力および出力のオフセット・ドリフトはオペアンプによって決まり、 $V_{REF} = 10V$  の場合、約 20  $\mu V/ ^\circ C$  になります。 $V_{REF}$  の値がこれより低い場合、入力オフセット・ドリフトは出力に  $10/V_{REF}$  を掛けた値になります。

他の対数回路同様、対数／逆対数乗算器の帯域幅は入力の大きさに比例します。この効果は、減少した電流ではループ・ゲインが減少し、それに応じてループの時定数が大きくなるためです。通常、乗算器の帯域幅は 10 V 入力に対し 100 KHz で、入力が 0.1 V になると帯域幅は 1 kHz に減少します。

入力と出力のオフセットとスケール・ファクタが調整されている場合、対数／逆対数乗算器の合計誤差は (10 V に対し)  $\pm 10 \text{ mV}$  未満です。誤差は入力の減少とともに小さくなり、0 ~ +10 V の出力レンジで、代表値が出力の 0.1 % 未満で、これに固定の出力オフセットが加わります。

## 1 象限乗算器を 4 象限動作用にオフセット

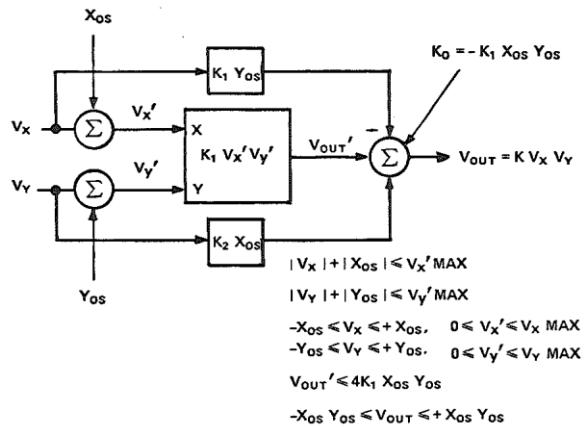

すべての 1 象限乗算器は、入力と出力を適切にオフセットすることによって、4 象限で動作させることができます。乗算器自体は 1 象限デバイスのままで、通常のユニポーラ範囲内に中心を定めたバイアス点の周りで動作します。

オフセット方法は、オフセットが X および Y 入力に及ぼす影響を考えることによって求められます。

$$E_o = K_1(V_x + X_{os})(V_y + Y_{os}) \quad (73)$$

$$E_o = K_1(V_x V_y + X_{os} V_y + V_x Y_{os} + X_{os} Y_{os}) \quad (74)$$

入力オフセットの効果は、出力オフセット  $X_{os}Y_{os}$  と、2 つの線形フィードスルー項  $X_{os}V_y$  と  $V_xY_{os}$  を発生させることです。 $X_{os} > |V_x|_{max}$ かつ  $Y_{os} > |V_y|_{max}$  だとすると  $V_x$  と  $V_y$  は正負いずれにもなることができますが、(74) の  $E_o$  は正のままでです。望ましくない項 ( $K_1V_xV_y$  以外の項) を (74) から差し引くと、 $E_o$  は正負いずれにもなることができ、望みの結果が得られます。

$$E_o = K_1 V_x V_y + K_1(X_{os} V_y + V_x Y_{os} + X_{os} Y_{os}) - K_0 - K_2 V_x - K_3 V_y \quad (75)$$

$K_0 = K_1 X_{os} Y_{os}$  とすると、 $K_2 = K_1 Y_{os}$ 、かつ  $K_3 = K_1 X_{os}$  です。従って次式が得られます。

$$E_o = K_1 V_x V_y \quad (76)$$

ここで、 $V_x$  と  $V_y$  の極性は任意です。

オフセットの設定と入力結合の方法を図 21 のブロック図に示します。このオフセット方法は、図 20 に示す対数／逆対数乗算器に使用できます。これは、乗算器の初期調整をかなり複雑なものとします。また、リファレンス電圧 ( $V_{REF}$ ) を一定にする必要があります。そうしないと、「フィードスルー」とオフセットが相殺された状態が維持されません。さらに、4 象限対数/逆対数乗算器では、X および Y 入力が負の場合は（対数トランジスタ内の電流量が減少する）、正入力の場合より速度が遅くなり、ゼロを中心とする対称波形ではこの方法の効果が薄れます。

このような短所はありますが、オフセット乗算器は誤差をフルスケールの 0.1 % に調整でき、非線形性は 0.05 % 程度です。

図 21:1 象限乗算器を 4 象限動作用にオフセット。

乗算器のスケール・ファクタの変更により、加算出力に出力オフセットと

フィードスルー・シフトを生成。

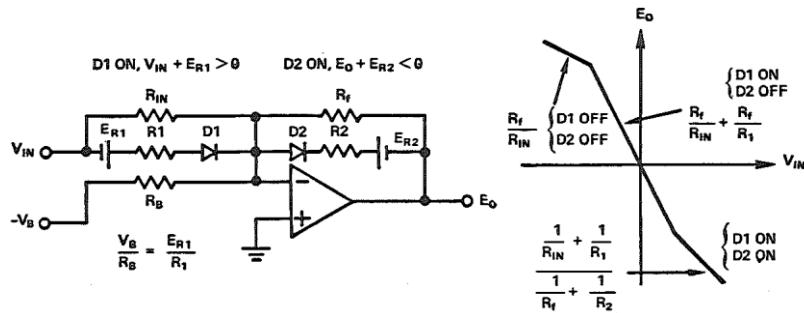

### パルス変調乗算器

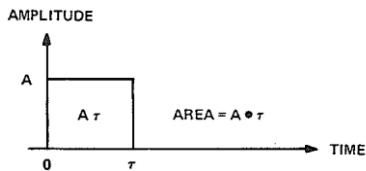

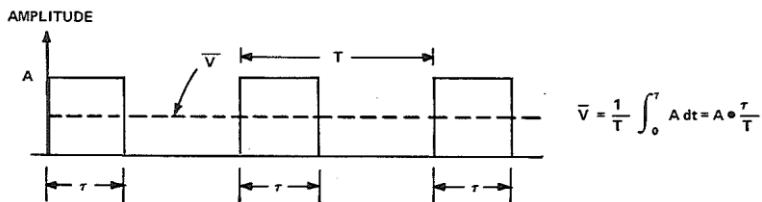

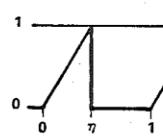

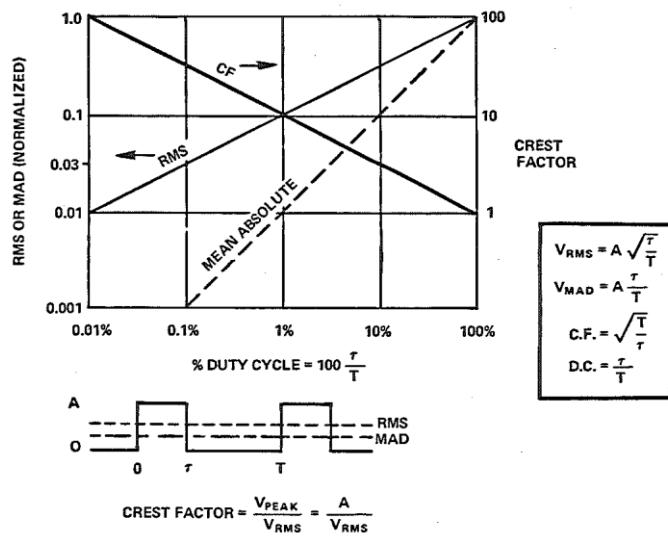

パルス変調乗算器は、矩形パルス下の面積はパルス振幅とパルス幅の積に比例する、という原理に基づいて動作します（図 22）。

図 22: パルス変調の基本原理

さらに、矩形パルス列の平均値は、周期に対するオン時間の比（デューティ・サイクル）とパルス振幅の積に比例します（図 23）。

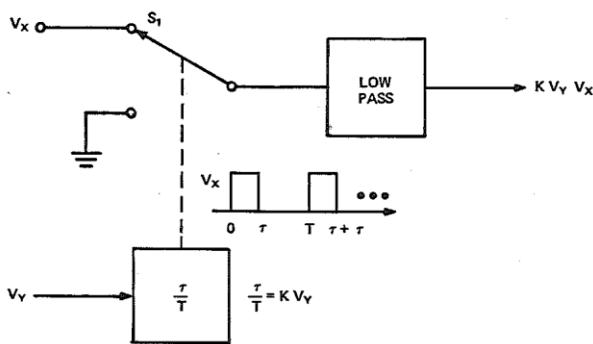

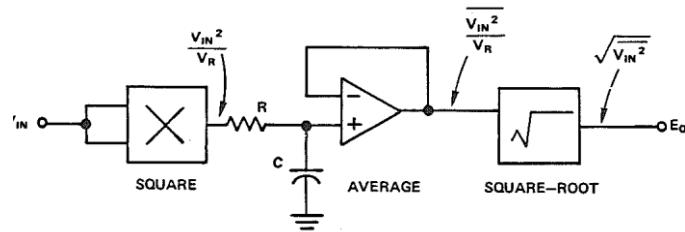

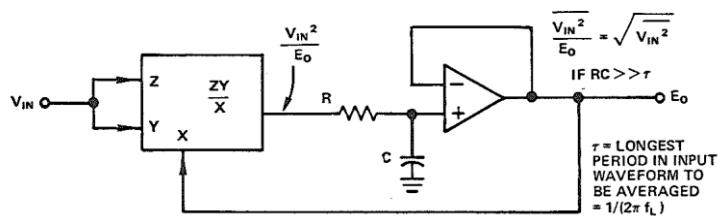

乗算器は、この手法を使って構成できます。一方の入力はパルスの振幅を制御するために使用し、もう一方の入力はデューティ・サイクルを制御するために使用します。結果として得られるパルス列にはローパス・フィルタがかけられ、2 つの入力の積に比例する平均値を出力します。簡単な 2 象限パルス変調乗算器のブロック図を図 24 に示します。

図 23: 矩形波パルス列の平均値は、振幅とデューティ・サイクルの積に比例

図 24: 2 象限パルス変調乗算器のブロック図。

Y 入力はパルス列のデューティ・サイクルを制御し、さらにパルス列がスイッチ S1 を駆動します。スイッチは入力とグラウンド間を交互に切り替え、デューティ・サイクルに比例する時間だけ入力を接続します。平均化フィルタの出力は、積  $V_x V_y$  に比例した値になります。X 入力は正または負のどちらにもなれます but、デューティ・サイクル  $\tau/T$  は負にならないので、Y 入力は正の値に制限されます。

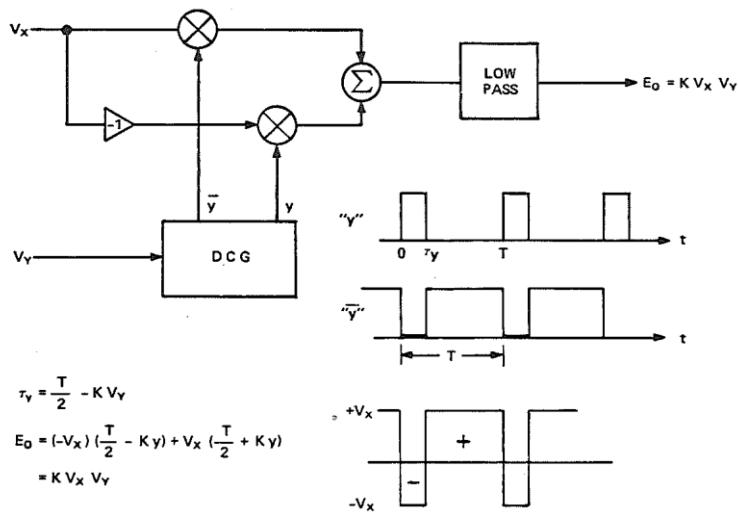

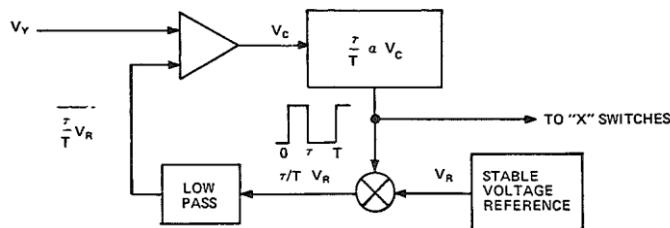

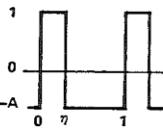

図 25 のブロック図に示されているように、パルス変調技術は、Y 入力がゼロのときデューティ・サイクルが 50 % となるように「バランス」スイッチングとデューティ・サイクル・ジェネレータを使用することによって、4 象限動作に拡大できます。

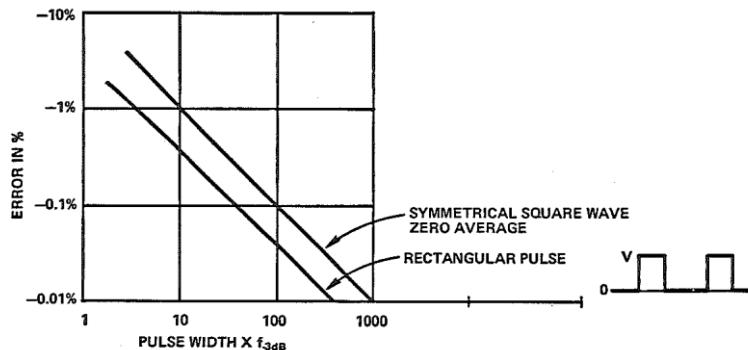

### パルス変調乗算器の性能

パルス幅／パルス高変調は、本質的に最も正確なアナログ乗算方法です。誤差がフルスケールの 0.1 % 未満で、非線形性が 0.02 % の精度を容易に実現できます。

図 25:4 象限パルス変調乗算器

この高い精度は、非線形素子（FET またはトランジスタ）のゲインと入力電圧の関係そのものを利用するのではなく、それらの素子をスイッチとして使用することによるものです。

パルス変調乗算器は概念的には 100 % 正確ですが、実際の乗算器の精度を制限する誤差源がいくつあります。最も大きな制限は、実際のスイッチとデューティ・サイクル・ジェネレータの非理想動作によるものです。しかし、変調技術自体に内在する制限も 1 つあります。信号周波数は、十分な平均化時間を得るために、平均化周波数より十分に低くなければなりません。アナログの平均化では、常に有限の（ただし通常は無視できる）リップル成分が出力に残ります。通常、キャリア周波数は、信号周波数の少なくとも 10 ~ 100 倍とする必要があります。

さらに、キャリア周波数は、部品で決まる誤差によって制限されます。

1. スイッチ制御端子と信号バス間の容量、例えば FET のゲート・チャンネル間容量。この容量は、スイッチのオン／オフごとに電荷を信号バスに結合させるので、オフセット電圧が生じます。オフセットは信号レベルによって異なり、非線形性が生じます。

「ダンプ電荷」効果は、低容量スイッチや低キャリア周波数を使用して信号パスに結合される平均電荷（電流）を小さくすることにより、最小限に抑えることができます。

2. スイッチのオン／オフ抵抗: FET スイッチや CMOS スイッチ（リード・リレーでも可）には、測定可能なオン抵抗と有限のオフ抵抗があります。オンに対するオフの比が高ければ ( $> 10,000$ ) 、スイッチによる誤差は小さくて済みます。この比が低いと、スイッチ・オフの時に入力信号の一部が出力にリークして、フィードスルーが大きくなります。

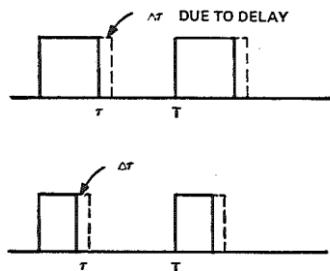

3. デューティ・サイクル・ジェネレータの線形性: 可変デューティ・サイクルのパルス・ジェネレータは、潜在的に非線形性の最も大きな発生源です。制御入力  $V_y$  は、かなり広い範囲にわたってオフ時間に対するオン時間の比を正確に決定する必要があります。これは 4 象限乗算器では特に重要です。図 26 に示すように、デューティ・サイクルが減少するにつれて、固定されたタイミング誤差、例えば遅延が、オン時間のより大きな部分を占めるようになります。この結果、非線形性が生じます。

図 26: デューティ・サイクル・ジェネレータとスイッチを合わせた

非対称固定遅延によって生じる非線形誤差。

$\Delta\tau$  は 比例からのずれで、 $\tau$  が大きくても小さくても同じです。

デューティ・サイクル・ジェネレータの非線形性は、図 27 のブロック図に示すクローズドループ回路を使うことによって、任意の低いレベルまで減らすことができます。

入力電圧  $V_y$  は、チョップされたリファレンス電圧の平均値と比較されます。

コンパレータの出力は、チョッパのオフ時間に対するオン時間を制御して、その平均出力電圧値が定常状態の  $V_y$  と等しくなるようにします。

図 27: クローズドループ・デューティ・サイクル・ジェネレータ

デューティ・サイクル  $\tau/T$  とコンパレータの出力電圧の関係は、それが 1 つの値である限り、重要ではありません。システム全体の線形性は、コンパレータの閾値の精度と平均化の時間によって決まります。この方法によって 0.01 % 未満の非線形性を実現することができます。

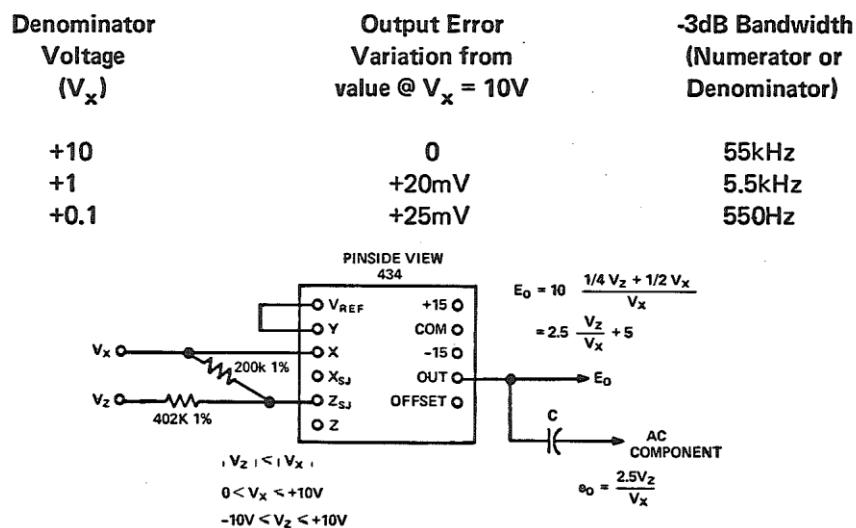

### 乗算器の仕様

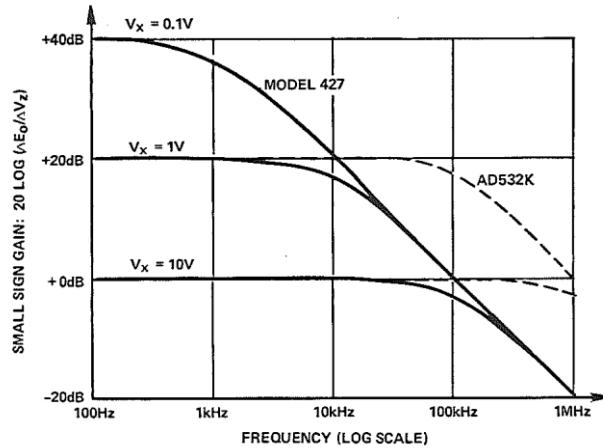

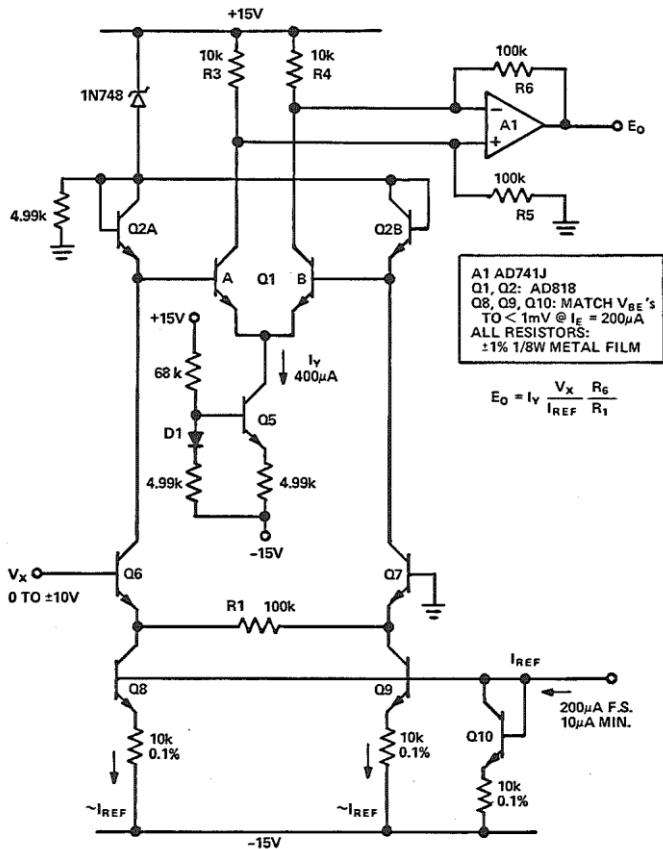

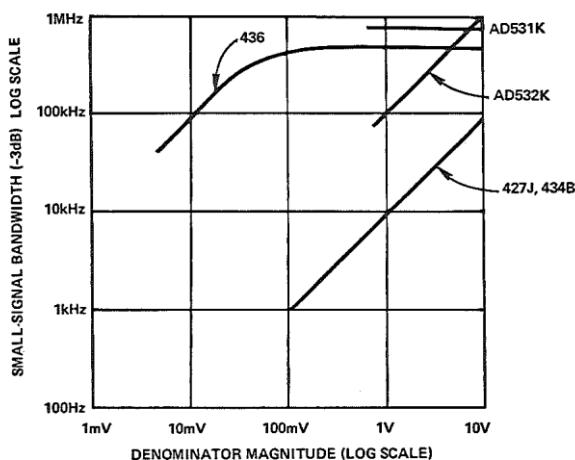

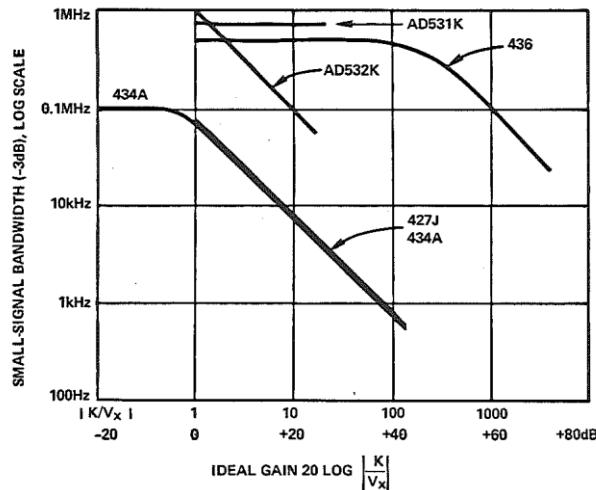

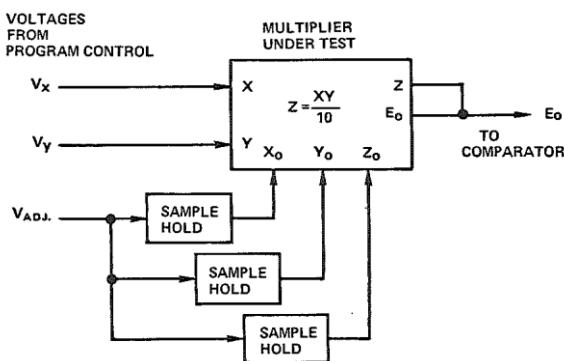

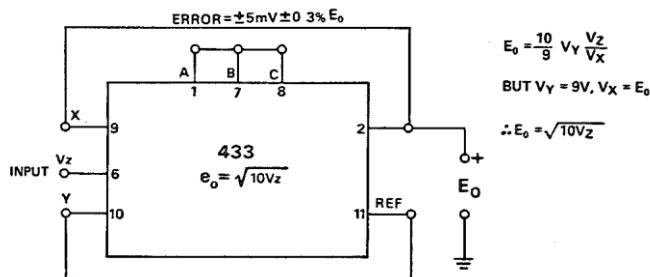

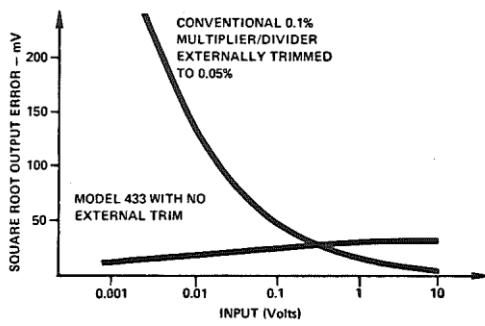

乗算器の仕様と、それら仕様の乗算器回路設計への依存度を理解する最良の方法は、恐らく、乗算器のデータシートに示されている仕様を充分読み直すことです。以下に示す比較表には、この章に述べた 3 つの方式、つまり、トランスコンダクタンス方式 (432, 429)、パルス変調方式 (427)、および対数/逆対数方式 (434) を使ったモジュラー型乗算器の仕様が示されています。

432 は低価格の 4 象限トランスコンダクタンス乗算器です。誤差は 1 % ~ 2 % で十分な帯域幅を有し、サイズは小型です。これは、外部トリムを使用する集積回路の AD533 に相当し、トリム回路を内蔵した AD532 より少し多めに電力を消費します。

429 は高速 (10 MHz) の 4 象限トランスコンダクタンス乗算器で、誤差が小さく (0.5 %) 非線形性も低く抑えられています。妥協を排したディスクリート設計で、乗算器セクションにモノリシック・デュアル・トランジスタと高速ディスクリート部品の出力アンプを使用しています。

427 は高精度 (0.25 % 誤差) のパルス変調 4 象限乗算器です。

高周波キャリア (3 MHz) を使用すると 100 kHz の信号帯域幅が可能ですが、これは、通常のパルス変調乗算器の帯域幅より 100 ~ 1000 倍上回ります。

434 は高精度（誤差 0.25 %）と多機能性を兼ね備えた 1 象限対数/逆対数乗算器で、乗算と除算を同時にを行うことができます。

### 仕様 (246 ~ 247 ページ)

比較仕様表\*の最初の 4 行には、読者が各自の用途に最適な乗算器を即座に見つけられるように、乗算器ごとに顕著な特長がまとめられています。乗算器の選択については、4-4 項の「設計者のための補助資料」に詳しい解説が示されているので、ここでは省略します。

### 乗算器の特性 (MULTIPLICATION CHARACTERISTICS)

仕様のこのブロックには、以下に続く仕様部分に詳細に示されているすべての誤差源（オフセット、スケール・ファクタ、非線形性、フィードスルー）から生じる全体の静的誤差が示されています。

**出力関数 (Output Function)** : 2 つの入力電圧  $V_x$ 、 $V_y$ 、出力電圧  $E_o$ 、およびスケール定数  $V_r$  の間の理想的な関数関係を定義します。すべての誤差は、この伝達関数からの偏差として定義され、フルスケール (10 V) のパーセンテージとして規定されています。代表的な伝達関数を下に示します。

$$E_o = \frac{V_x V_y}{10V} \quad (77)$$

$V_x = V_y = 10 \text{ V}$  の場合は次のようにになります。

$$E_o = \frac{10 \times 10}{10} = 10 \text{ V} \quad (78)$$

\* この表は一部を省略した一例で、対照的なモジュラー型乗算器が含まれています。記載されている情報は 1973 年夏時点の情報です。これらのタイプや各クラス内のその他多数のタイプ、およびその他多数の IC タイプの詳細情報については、アナログ・デバイセズ製品ガイドの最新版、またはその補遺を参照することをお勧めします。

## 乗算器/除算器（ディスクリート）

仕様の概要（別途指定のない限り 25 °C、±15 VDC での代表値）

| MULTIPLICATION TECHNIQUE                      |                                        | TRANSCONDUCTANCE                           |                   |

|-----------------------------------------------|----------------------------------------|--------------------------------------------|-------------------|

| Model <sup>1</sup>                            |                                        | Economy                                    | Accurate Wideband |

| Price *1-9                                    | \$29 (\$45)                            | \$109 (\$139)                              |                   |

| Price 10-24                                   | \$27 (\$43)                            | \$104 (\$129)                              |                   |

| Full Scale Accuracy <sup>2</sup>              | 2% (1%)                                | 1% (0.5%)                                  |                   |

| Divides and Square Roots                      | YES                                    | YES                                        |                   |

| Multiplication Characteristics                |                                        |                                            |                   |

| Output Function                               | XY/10                                  | XY/10                                      |                   |

| Error, Internal Trim (±)                      | 2%(1%) max                             | 1%(0.5%) max                               |                   |

| Error, External Trim (±)                      | 1.0% (0.6%)                            | 0.7% (0.3%)                                |                   |

| Accuracy vs. Temperature (±)                  | 0.06%/°C (0.04%/°C)                    | 0.05%/°C (0.04%/°C max)                    |                   |

| Accuracy vs. Supply (±)                       | 0.1%                                   | 0.03%                                      |                   |

| Warm up Time to Specifications                | 1 min                                  | 1 sec                                      |                   |

| Output Offset (±)                             |                                        |                                            |                   |

| Initial                                       | 20mV (25mV max)                        | 20mV (10mV) max                            |                   |

| Average vs. Temperature 0°C to +70°C          | 2mV/°C (1mV/°C)                        | 2mV/°C (1mV/°C max)                        |                   |

| Average vs. Supply                            | 10mV/%                                 | 1mV/%                                      |                   |

| Scale Factor (±)                              |                                        |                                            |                   |

| Initial Error                                 | 1% (0.5%)                              | 0.5% (0.25%)                               |                   |

| Non Linearity (±)                             |                                        |                                            |                   |

| X Input (X = 20V p-p, Y = ±10VDC)             | 0.8% (0.6% max)                        | 0.5% (0.2%) max                            |                   |

| Y Input (Y = 20V p-p, X = ±10VDC)             | 0.4% (0.3% max)                        | 0.3% (0.2%) max                            |                   |

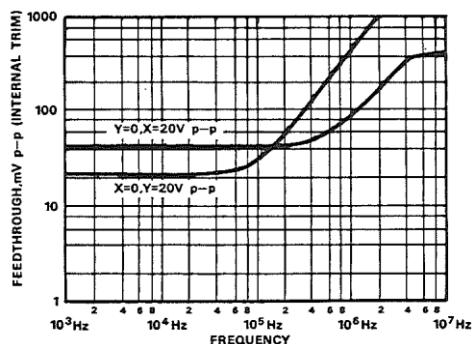

| Feedthrough                                   |                                        |                                            |                   |

| X = 0, Y = 20V p-p 50Hz<br>with external trim | 80mV (50mV) p-p max<br>30mV p-p        | 25mV (10mV) p-p max<br>8mV (5mV) p-p       |                   |

| Y = 0, X = 20V p-p 50Hz<br>with external trim | 120mV (100mV) p-p max<br>N/A           | 50mV (15mV) p-p max<br>35mV (10mV) p-p     |                   |

| Feedthrough vs. Temperature, each input       | 1mV p-p/°C                             | 2mV p-p/°C                                 |                   |

| Bandwidth                                     |                                        |                                            |                   |

| -3dB Small Signal                             | 1MHz                                   | 10MHz                                      |                   |

| Full Power Response                           | 700kHz                                 | 2MHz min                                   |                   |

| Slew Rate                                     | 45V/usec                               | 120V/usec min.                             |                   |

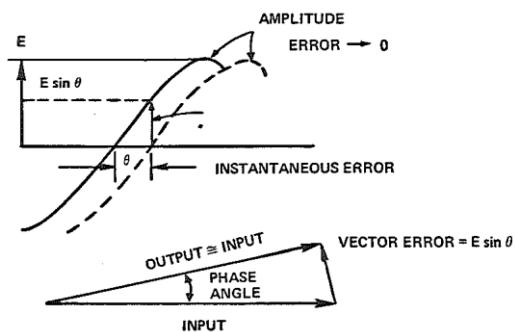

| Small Signal Amplitude Error (±)              | 1% @ 40kHz                             | 1% at 300kHz min                           |                   |

| Small Signal Vector Error (±)                 | 1% @ 10kHz                             | 1% at 50kHz min                            |                   |

| Settling Time for ±10V Step                   | 1μsec to 2%                            | 0.5μsec to 1%                              |                   |

| Overload Recovery                             | 3μsec                                  | 0.15μsec                                   |                   |

| Output Noise                                  |                                        |                                            |                   |

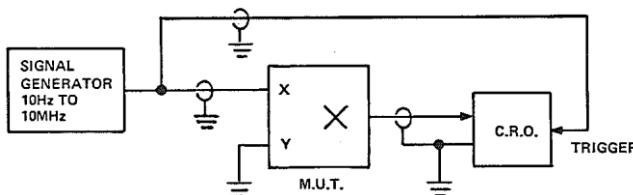

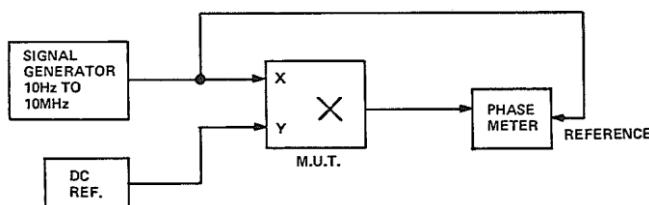

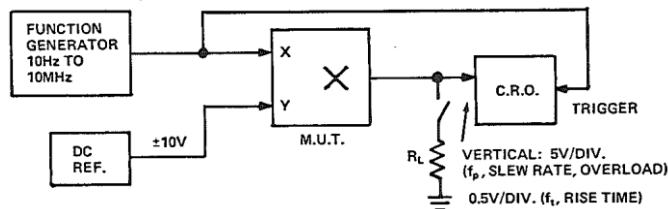

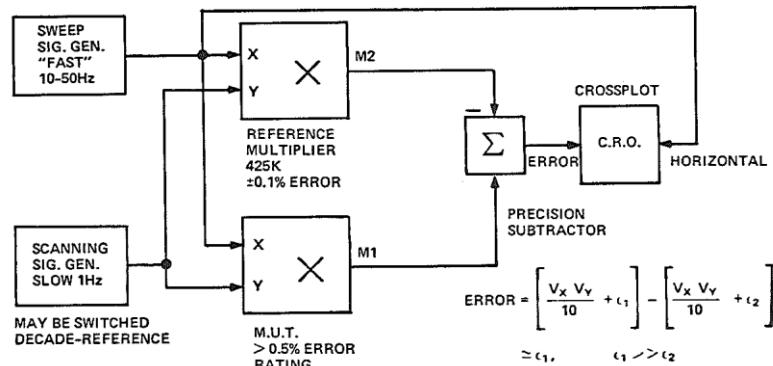

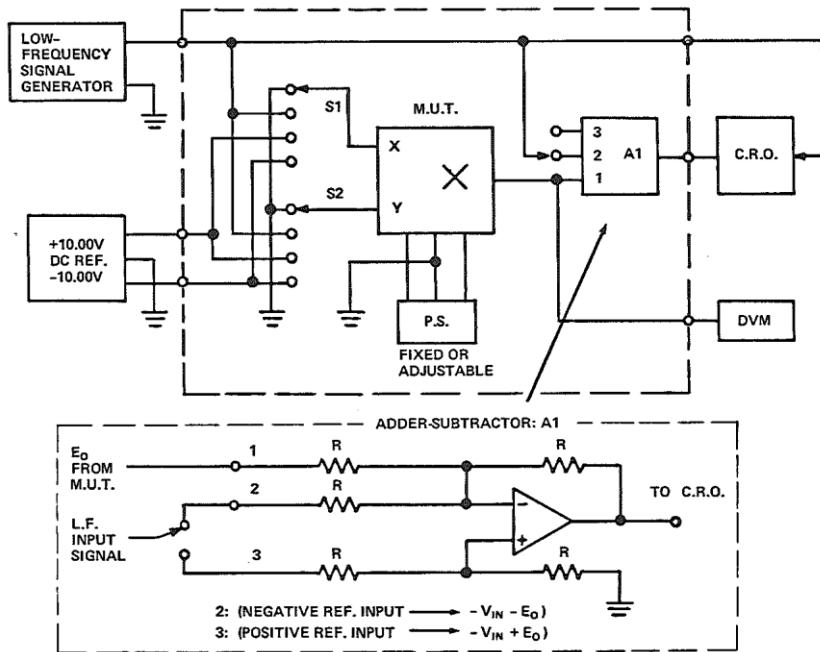

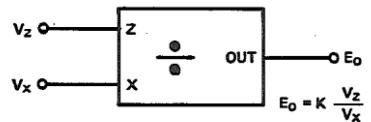

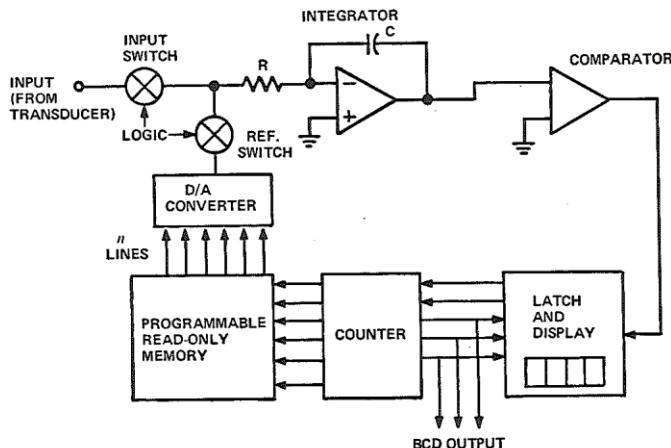

| 5Hz to 10kHz                                  | 600μV rms                              | 500μV rms                                  |                   |