# Precision Timing™ジェネレータ付き 12ビットCCD信号処理プロセッサ

# AD9995

## 特長

- 6相の垂直転送クロックをサポート

- 相関ダブル・サンプリング (CDS)

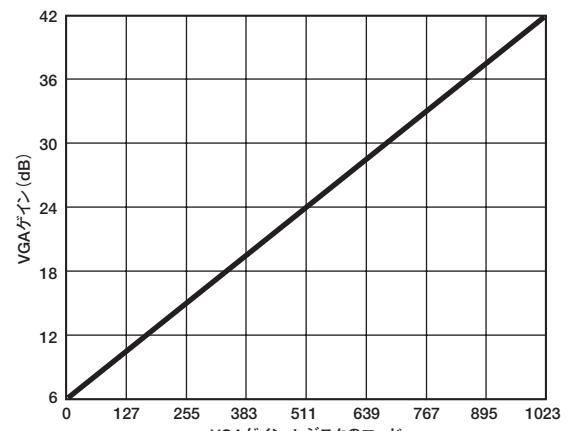

- 6~42dBの10ビット可変ゲイン・アンプ (VGA)

- 12ビット36MHzのA/Dコンバータ

- 可変レベル制御付きの黒レベル・クランプ

- 完全なオンチップ・タイミング・ジェネレータ

- 600ps分解能のPrecision Timingコア

- オンチップ3V水平/RGドライバ

- 2相と4相のHクロック・モード

- 電子/メカシャッター・モード

- 外部水晶発振器用のオンチップ・ドライバ

- 外部同期入力のあるオンチップ同期ジェネレータ

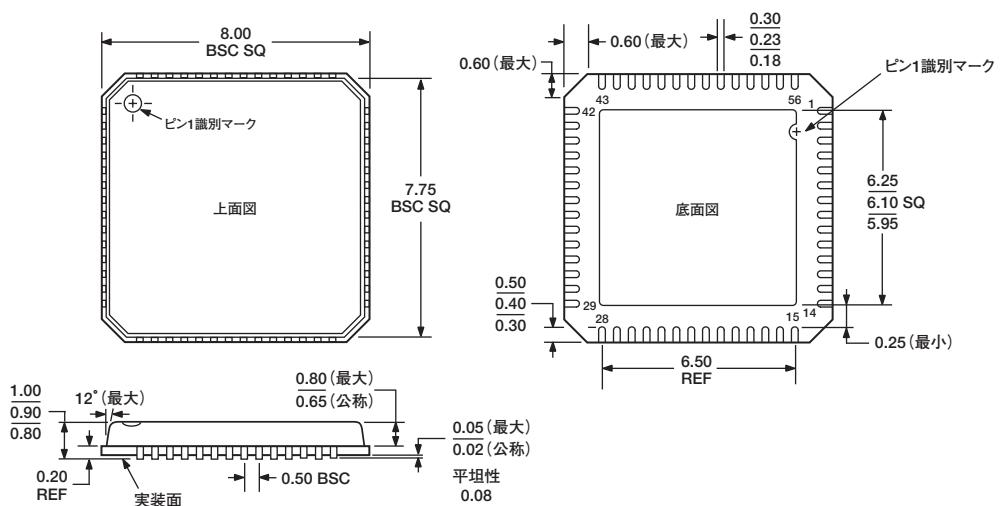

- 56ピンLFCSPパッケージ

## アプリケーション

デジタル・スチル・カメラ

デジタル・ビデオ・カムコーダ

工業用画像処理

## 概要

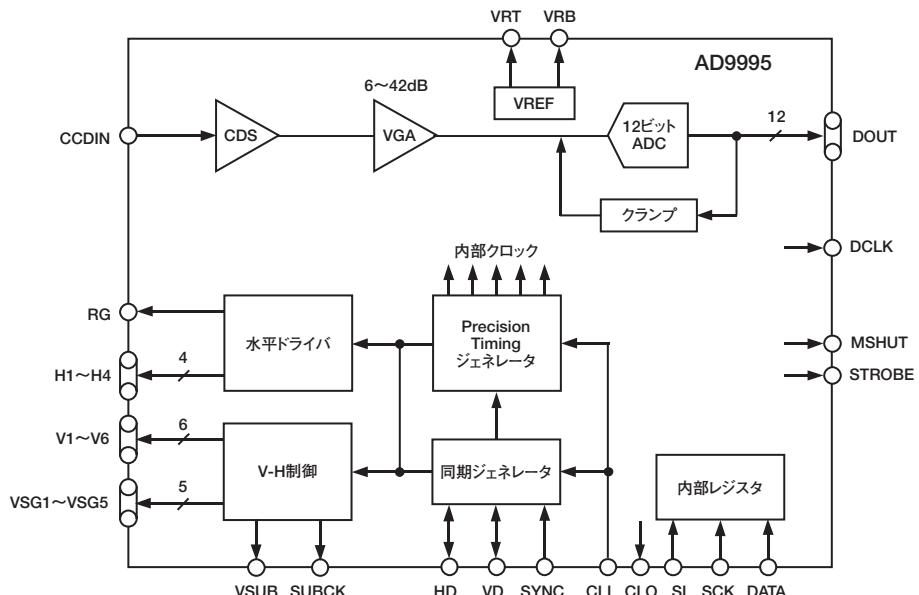

AD9995は、デジタル・スチル・カメラやカムコーダなどのアプリケーション用に高集積化されたCCD信号処理プロセッサです。これには、AD変換するアナログ・フロントエンド、全ての機能をプログラミングできるタイミング・ジェネレータが集積されています。このタイミング・ジェネレータは4相または6相の垂直転送パルスのタイミングをサポートします。Precision Timingコアは36MHzの動作のとき、600psで高速系のタイミングを調整することができます。

AD9995は、36MHzのピクセル・クロック・レートで規定されています。アナログ・フロントエンドは、黒レベル・クランプ、CDS、VGAと12ビットA/Dコンバータ（ADC）が集積されています。タイミング・ジェネレータは、CCDを駆動させるのに必要な全てのクロック信号であるRG、Hクロック、Vクロック、センサー・ゲート・パルス、基板クロック、そして基板バイアス・コントロール・パルスなどを発生することができます。動作は、3線シリアル・インターフェースにより設定します。

パッケージは56ピンLFCSPで、AD9995は-20°Cから85°Cで動作が規定されています。

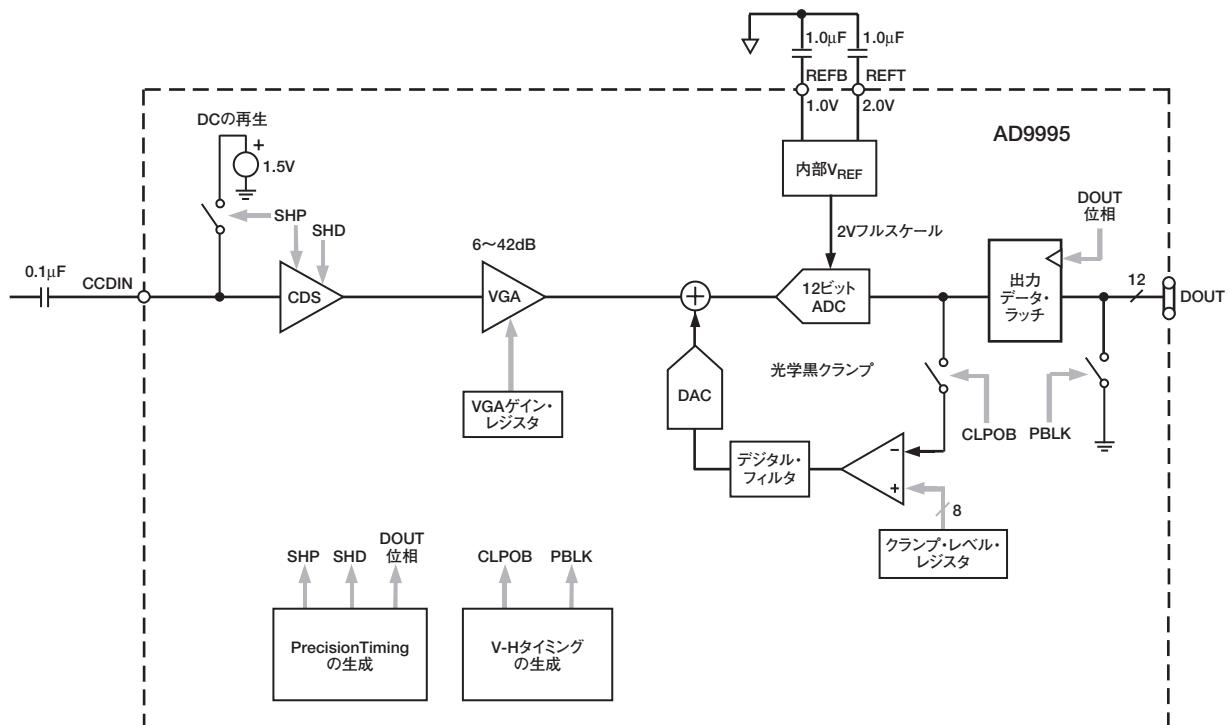

## 機能ブロック図

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。本紙記載の商標および登録商標は、各社の所有に属します。

© 2003 Analog Devices, Inc. All rights reserved.

REV. 0

アナログ・デバイセズ株式会社

本 社／〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワー

大阪営業所／ 〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪MTビル2号

電話03(5402)8200

電話06(6350)6868(代)

## 目次

---

|                               |    |                          |    |

|-------------------------------|----|--------------------------|----|

| 仕様                            | 3  | 垂直タイミングの例                | 24 |

| デジタル仕様                        | 3  | 信号極性についての重要な注意事項         | 24 |

| アナログ仕様                        | 4  | シャッター・タイミングの制御           | 26 |

| タイミング仕様                       | 5  | ノーマル・シャッター動作             | 26 |

| 絶対最大定格                        | 5  | 高精度シャッター動作               | 26 |

| パッケージの熱特性                     | 5  | 低速シャッター動作                | 26 |

| オーダー・ガイド                      | 5  | SUBCKの停止                 | 27 |

| ピン配置                          | 6  | 露光後の読み出し                 | 27 |

| ピン機能の説明                       | 6  | TRIGGERレジスタの使い方          | 27 |

| 用語集                           | 7  | VSUBの制御                  | 28 |

| 等価回路                          | 7  | MSHUTとSTROBEの制御          | 28 |

| 代表的な性能特性                      | 8  | TRIGGERレジスタの制限           | 29 |

| システム概要                        | 9  | 露光と読み出しの例                | 30 |

| Precision Timingによる高速タイミングの生成 | 10 | アナログ・フロントエンドの説明と動作       | 31 |

| タイミング分解能                      | 10 | DCの再生                    | 31 |

| 高速クロックのプログラマビリティ              | 10 | 相関ダブル・サンプラー              | 31 |

| HドライバとRG出力                    | 11 | 可変ゲイン・アンプ                | 31 |

| デジタル・データ出力                    | 11 | A/Dコンバータ                 | 31 |

| 水平クランプとブランкиング                | 13 | 光学黒クランプ                  | 32 |

| CLPOBとPBLKの個々のパターン            | 13 | デジタル・データ出力               | 32 |

| 個々のHBLKパターン                   | 13 | パワーアップと同期                | 33 |

| 特殊なHBLKパターンの生成                | 14 | マスター・モードに推奨するパワーアップ      |    |

| HBLKライン・オルタネーションの生成           | 14 | シーケンス                    | 33 |

| 水平タイミング・シーケンスの例               | 15 | 外部SYNC信号なしでソフトウェアSYNCを生成 | 33 |

| 垂直タイミングの生成                    | 16 | マスター・モード動作時のSYNC         | 34 |

| 垂直パターン・グループ (VPAT)            | 17 | スレーブ・モードでのパワーアップと同期      | 34 |

| 垂直シーケンス (VSEQ)                | 18 | スタンバイ・モード動作              | 34 |

| 完全なフィールド:Vシーケンスの結合            | 19 | 回路レイアウト情報                | 36 |

| VシーケンスとHBLKに対するライン・オルタネーション   |    | シリアル・インターフェースのタイミング      | 37 |

| の生成                           | 20 | レジスタ・アドレスのBank 1と2       | 38 |

| VSGアクティブ・ライン区間での2番目の          |    | 新しいレジスタ値の更新              | 39 |

| Vパターン・グループ                    | 20 | レジスタBank 1の詳細リスト         | 40 |

| スイープ・モード動作                    | 21 | レジスタBank 2の詳細リスト         | 43 |

| マルチプライヤ・モード                   | 21 | 外形寸法                     | 59 |

| 垂直センサー・ゲート (シフト・ゲート) のパターン    | 22 |                          |    |

| モード・レジスタ                      | 23 |                          |    |

# AD9995 — 仕様

| パラメータ                       | Min | Typ | Max  | 単位  |

|-----------------------------|-----|-----|------|-----|

| 温度範囲                        |     |     |      |     |

| 動作                          | −20 |     | +85  | ℃   |

| 保存                          | −65 |     | +150 | ℃   |

| 電源電圧                        |     |     |      |     |

| AVDD (AFEアナログ電源)            | 2.7 | 3.0 | 3.6  | V   |

| TCVDD (タイミング・コア・アナログ電源)     | 2.7 | 3.0 | 3.6  | V   |

| RGVDD (RG ドライバ)             | 2.7 | 3.0 | 3.6  | V   |

| HVDD (H1~H4 ドライバ)           | 2.7 | 3.0 | 3.6  | V   |

| DRVDD (データ出力ドライバ)           | 2.7 | 3.0 | 3.6  | V   |

| DVDD (デジタル)                 | 2.7 | 3.0 | 3.6  | V   |

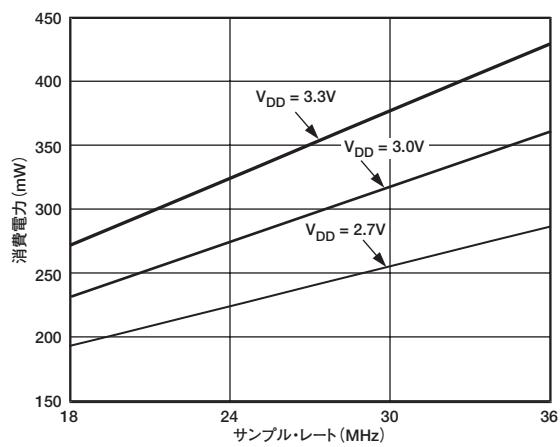

| 消費電力 (出力曲線については特性1を参照)      |     |     |      |     |

| 36MHz、標準電源レベル、100pF H1~H4負荷 | 360 |     |      | mW  |

| HVDDのみからの電源*                | 130 |     |      | mW  |

| スタンバイ1モード                   | 130 |     |      | mW  |

| スタンバイ2モード                   | 12  |     |      | mW  |

| スタンバイ3モード                   | 0.5 |     |      | mW  |

| 最大クロック・レート (CLI)            | 36  |     |      | MHz |

\* HVDDの電源電圧の違いによる消費電力は以下のような等価式でおおよそ求めることができます。

HVDDの消費電力 =  $(C_{LOAD} \times HVDD \times ピクセル周波数) \times HVDD \times$  使用するH出力の数

消費電力を低減させるためには、H出力を2つのみ使用して負荷を低減させるか、さらに/もしくはHVDDの電源電圧を下げるこです。

仕様は予告なしに変更することがあります。

## デジタル仕様 (特に指定のない限り、RGVDD=HVDD=DVDD=DRVDD=2.7~3.6V、C<sub>L</sub>=20pF、T<sub>MIN</sub>~T<sub>MAX</sub>)

| パラメータ                           | 記号              | Min     | Typ | Max | 単位 |

|---------------------------------|-----------------|---------|-----|-----|----|

| ロジック入力                          |                 |         |     |     |    |

| ハイレベル入力電圧                       | V <sub>IH</sub> | 2.1     |     | 0.6 | V  |

| ローレベル入力電圧                       | V <sub>IL</sub> |         |     |     | V  |

| ハイレベル入力電流                       | I <sub>IH</sub> | 10      |     |     | μA |

| ローレベル入力電流                       | I <sub>IL</sub> | 10      |     |     | μA |

| 入力容量                            | C <sub>IN</sub> | 10      |     |     | pF |

| ロジック出力 (HとRG以外)                 |                 |         |     |     |    |

| ハイレベル出力電圧 @I <sub>OH</sub> =2mA | V <sub>OH</sub> | 2.2     |     |     | V  |

| ローレベル出力電圧 @I <sub>OL</sub> =2mA | V <sub>OL</sub> |         |     | 0.5 | V  |

| RGおよびHドライバの出力 (H1~H4)           |                 |         |     |     |    |

| ハイレベル出力電圧 (最大電流の時)              | V <sub>OH</sub> | VDD−0.5 |     |     | V  |

| ローレベル出力電圧 (最大電流の時)              | V <sub>OL</sub> |         |     | 0.5 | V  |

| 最大出力電流 (プログラマブル)                |                 | 30      |     |     | mA |

| 最大負荷容量 (出力ごと)                   |                 | 100     |     |     | pF |

仕様は予告なしに変更することがあります。

# AD9995

## アナログ仕様 (特に指定のない限り、AVDD=3.0V、f<sub>CLi</sub>=36MHz、標準タイミング仕様、T<sub>MIN</sub>~T<sub>MAX</sub>)

| パラメータ                                                                           | Min         | Typ                       | Max         | 単位                       | 注                                                                                     |

|---------------------------------------------------------------------------------|-------------|---------------------------|-------------|--------------------------|---------------------------------------------------------------------------------------|

| CDS*                                                                            |             |                           |             |                          |                                                                                       |

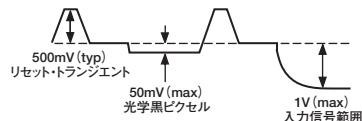

| 許容CCDリセット・トランジエント<br>飽和前の最大入力レンジ<br>最大CCD黒ピクセル振幅                                | 1.0         | 500<br>±50                |             | mV<br>Vp-p<br>mV         |                                                                                       |

| 可変ゲイン・アンプ (VGA)                                                                 |             | 1024                      |             | ステップ                     |                                                                                       |

| ゲイン制御分解能<br>ゲイン単調性<br>ゲイン・レンジ<br>最小ゲイン (VGAコード0)<br>最大ゲイン (VGAコード1023)          |             | 保証済み                      | 6<br>42     | dB<br>dB                 |                                                                                       |

| 黒レベル・クランプ                                                                       |             | 256                       |             | ステップ                     |                                                                                       |

| クランプ・レベル分解能<br>クランプ・レベル<br>最小クランプ・レベル (コード0)<br>最大クランプ・レベル (コード255)             |             | 0<br>255                  |             | LSB<br>LSB               | ADCの出力で測定                                                                             |

| A/Dコンバータ                                                                        | 12          |                           |             | ビット                      |                                                                                       |

| 分解能<br>微分非直線性 (DNL)<br>ノードミスコード<br>フルスケール入力電圧                                   | -1.0        | ±0.5<br>保証済み<br>2.0       | +1.0        | LSB<br>V                 |                                                                                       |

| リファレンス                                                                          |             | 2.0                       |             | V                        |                                                                                       |

| 上側リファレンス電圧 (REFT)<br>下側リファレンス電圧 (REFB)                                          |             | 1.0                       |             | V                        |                                                                                       |

| システム性能                                                                          |             |                           |             |                          | シグナル・チェーンの全体を含む                                                                       |

| ゲイン精度<br>低ゲイン (VGAコード0)<br>最大ゲイン (VGAコード1023)<br>ピーケ非直線性、入力信号: 500mV<br>総合出力ノイズ | 5.0<br>40.5 | 5.5<br>41.5<br>0.2<br>0.8 | 6.0<br>42.5 | dB<br>dB<br>%<br>LSB rms | ゲイン=(0.0351×コード)+6dB<br>12dBのゲインを適用<br>ACをグラウンドとする入力、6dB<br>のゲインを適用<br>電源をステップ変化させて測定 |

| 電源除去比 (PSR)                                                                     |             | 50                        |             | dB                       |                                                                                       |

\* 入力信号特性は次のように定義されます。

仕様は予告なしに変更することがあります。

## タイミング仕様 (特に指定のない限り、 $C_L=20\text{pF}$ 、 $\text{AVDD}=\text{DVDD}=\text{DRVDD}=3.0\text{V}$ 、 $f_{\text{CLI}}=36\text{MHz}$ )

| パラメータ                                                                                                                                                                         | 記号                  | Min  | Typ  | Max  | 単位   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|------|------|

| マスター・クロック、CLI (図4)<br>CLIクロック周期<br>CLIハイ／ロー・パルス幅<br>CLI立ち上がりエッジから内部ピクセル位置0までの遅延                                                                                               | $t_{\text{CONV}}$   | 27.8 |      |      | ns   |

|                                                                                                                                                                               | $t_{\text{CLIDLY}}$ | 11.2 | 13.9 | 16.6 | ns   |

| AFE CLPOB パルス幅 <sup>1, 2</sup> (図9と図14)                                                                                                                                       |                     | 6    |      |      | ns   |

| AFEサンプル位置 <sup>1</sup> (図7)<br>SHPサンプル・エッジからSHDサンプル・エッジまで                                                                                                                     | $t_{\text{SI}}$     | 2    | 20   |      | ピクセル |

| データ出力 (図8aと図8b)<br>DCLK立ち上がりエッジからの出力遅延 <sup>1</sup><br>SHP/SHDのサンプリングからDOUTまでのパイプライン遅延                                                                                        | $t_{\text{OD}}$     | 12.5 | 13.9 |      | ns   |

| シリアル・インターフェース (図40aと図40b)<br>最大SCK周波数<br>SLからSCKへのセットアップ・タイム<br>SCKからSLへのホールド・タイム<br>SDATA有効からSCK立ち上がりエッジへのセットアップ<br>SCK立ち下がりエッジからSDATA有効へのホールド<br>SCK立ち下がりエッジからSDATA有効への読み出し | $f_{\text{SCLK}}$   | 8    | 10   | 11   | MHz  |

| $t_{\text{LS}}$                                                                                                                                                               | 10                  |      |      | ns   |      |

| $t_{\text{LH}}$                                                                                                                                                               | 10                  |      |      | ns   |      |

| $t_{\text{DS}}$                                                                                                                                                               | 10                  |      |      | ns   |      |

| $t_{\text{DH}}$                                                                                                                                                               | 10                  |      |      | ns   |      |

| $t_{\text{DV}}$                                                                                                                                                               | 10                  |      |      | ns   |      |

注

<sup>1</sup> パラメータはプログラマブルです。<sup>2</sup> 最小CLPOBのパルス幅は機能的な動作でのみ規定しています。幅の広いパルスはクランプ・ノイズの低減に寄与しますので推奨しています。

仕様は予告なしに変更することがあります。

## 絶対最大定格\*

| パラメータ        | 基準    | Min  | Max       | 単位 |

|--------------|-------|------|-----------|----|

| AVDD         | AVSS  | -0.3 | +3.9      | V  |

| TCVDD        | TCVSS | -0.3 | +3.9      | V  |

| HVDD         | HVSS  | -0.3 | +3.9      | V  |

| RGVDD        | RGVSS | -0.3 | +3.9      | V  |

| DVDD         | DVSS  | -0.3 | +3.9      | V  |

| DRVDD        | DRVSS | -0.3 | +3.9      | V  |

| RG出力         | RGVSS | -0.3 | RGVDD+0.3 | V  |

| H1～H4出力      | HVSS  | -0.3 | HVDD+0.3  | V  |

| デジタル出力       | DVSS  | -0.3 | DVDD+0.3  | V  |

| デジタル入力       | DVSS  | -0.3 | DVDD+0.3  | V  |

| SCK、SL、SDATA | DVSS  | -0.3 | DVDD+0.3  | V  |

| REFT、REFB、   | AVSS  | -0.3 | AVDD+0.3  | V  |

| CCDIN        |       |      |           |    |

| ジャンクション温度    |       | 150  |           | °C |

| ピン温度、10秒     |       | 350  |           | °C |

\*上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、これらの規定値またはこの仕様の動作に関するセクションに記載されている規定値を超える条件でのデバイス動作を定めたものではありません。長時間デバイスを絶対最大定格状態にすると、デバイスの信頼性に影響を与えることがあります。絶対最大定格は個別にのみ適用し、定格値を組み合わせて適用することはできません。特に指定のない限り、他のすべての電圧はGNDを基準とします。

## 注意

ESD (静電放電) の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されます。AD9995は当社独自のESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

# AD9995

## ピン配置

## ピン機能の説明<sup>1</sup>

| ピン | 記号    | タイプ <sup>2</sup> | 説明                  | ピン | 記号     | タイプ <sup>2</sup> | 説明                                                 |

|----|-------|------------------|---------------------|----|--------|------------------|----------------------------------------------------|

| 1  | D5    | DO               | データ出力               | 35 | CLI    | DI               | リファレンス・クロック入力                                      |

| 2  | D6    | DO               | データ出力               | 36 | AVDD   | P                | AFE用アナログ電源                                         |

| 3  | D7    | DO               | データ出力               | 37 | CCDIN  | AI               | CCD信号入力                                            |

| 4  | D8    | DO               | データ出力               | 38 | AVSS   | P                | AFE用アナログ・グラウンド                                     |

| 5  | D9    | DO               | データ出力               | 39 | REFT   | AO               | リファレンス上側バイパス                                       |

| 6  | D10   | DO               | データ出力               | 40 | REFB   | AO               | リファレンス下側バイパス                                       |

| 7  | D11   | DO               | データ出力 (MSB)         | 41 | SL     | DI               | 3線式シリアル負荷パルス                                       |

| 8  | DRVDD | P                | データ出力ドライバ電源         | 42 | SDI    | DI               | 3線式シリアル・データ入力                                      |

| 9  | DRVSS | P                | データ出力ドライバ・グラウンド     | 43 | SCK    | DI               | 3線式シリアル・クロック                                       |

| 10 | VSUB  | DO               | CCD基板バイアス           | 44 | MSHUT  | DO               | メカシャッター・パルス                                        |

| 11 | SUBCK | DO               | CCD基板クロック (Eシャッター)  | 45 | STROBE | DO               | ストロボ・パルス                                           |

| 12 | V1    | DO               | CCD垂直転送クロック1        | 46 | SYNC   | DI               | 外付けシステム同期入力                                        |

| 13 | V2    | DO               | CCD垂直転送クロック2        | 47 | VD     | DIO              | 垂直同期パルス                                            |

| 14 | V3    | DO               | CCD垂直転送クロック3        |    |        |                  | (スレーブ・モードでは入力、マスター・モードでは出力)                        |

| 15 | V4    | DO               | CCD垂直転送クロック4        |    |        |                  |                                                    |

| 16 | V5    | DO               | CCD垂直転送クロック5        | 48 | DVSS   | P                | デジタル・グラウンド                                         |

| 17 | V6    | DO               | CCD垂直転送クロック6        | 49 | DVDD   | P                | VSG、V1~V6、HD/VD、MSHUT、STROBE、SYNC、シリアル・インターフェース用電源 |

| 18 | VSG1  | DO               | CCDセンサー・ゲート・パルス1    | 50 | HD     | DIO              | 水平同期パルス                                            |

| 19 | VSG2  | DO               | CCDセンサー・ゲート・パルス2    |    |        |                  | (スレーブ・モードでは入力、マスター・モードでは出力)                        |

| 20 | VSG3  | DO               | CCDセンサー・ゲート・パルス3    |    |        |                  |                                                    |

| 21 | VSG4  | DO               | CCDセンサー・ゲート・パルス4    | 51 | DCLK   | DO               | データ・クロック出力                                         |

| 22 | VSG5  | DO               | CCDセンサー・ゲート・パルス5    | 52 | D0     | DO               | データ出力 (LSB)                                        |

| 23 | H1    | DO               | CCD水平クロック1          | 53 | D1     | DO               | データ出力                                              |

| 24 | H2    | DO               | CCD水平クロック2          | 54 | D2     | DO               | データ出力                                              |

| 25 | HVSS  | P                | H1~H4ドライバ・グラウンド     | 55 | D3     | DO               | データ出力                                              |

| 26 | HVDD  | P                | H1~H4ドライバ電源         | 56 | D4     | DO               | データ出力                                              |

| 27 | H3    | DO               | CCD水平クロック3          |    |        |                  |                                                    |

| 28 | H4    | DO               | CCD水平クロック4          |    |        |                  |                                                    |

| 29 | RGVSS | P                | RGドライバ・グラウンド        |    |        |                  |                                                    |

| 30 | RG    | DO               | CCDリセット・ゲート・クロック    |    |        |                  |                                                    |

| 31 | RGVDD | P                | RGドライバ電源            |    |        |                  |                                                    |

| 32 | TCVSS | P                | タイミング・コア用アナログ・グラウンド |    |        |                  |                                                    |

| 33 | TCVDD | P                | タイミング・コア用アナログ電源     |    |        |                  |                                                    |

| 34 | CLO   | DO               | 水晶発振器用クロック出力        |    |        |                  |                                                    |

注

<sup>1</sup> 回路構成については図38を参照。

<sup>2</sup> AI=アナログ入力、AO=アナログ出力、DI=デジタル入力、DO=デジタル出力、DIO=デジタル入/出力、P=電源

## 用語集

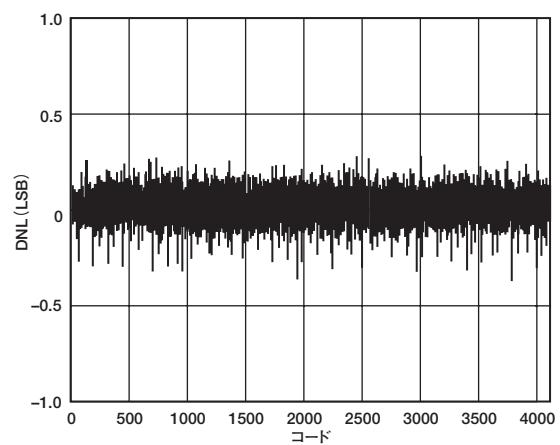

### 微分非直線性 (DNL)

理想的なADCは正確に1LSBごとにコードの遷移箇所があります。DNLはこの理想的な値からの偏差です。したがって、全てのコードは有限の値をとります。ノーミスコードとは、12ビットの分解能のとき、4096の全てのコードが存在することを意味します。

### ピーク非直線性

ピーク非直線性 (Peak Nonlinearity) は、信号処理ブロックにおいて、AD9995の出力に対する理想的な直線からの最大偏差になります。ゼロスケールは、最初のコード遷移の0.5LSB前に発生します。フルスケールは、最後のコード遷移を1.5LSB分越えた値として定義されます。偏差とは、それぞれのコードの中点から真の直線までの差を計測した値です。このエラーは、フルスケールを2Vとしたときのパーセンテージ (%) で表現さ

れます。入力信号はADCのフルスケールに合うように常に増幅されます。

### 総合出力ノイズ

rms出力ノイズはヒストグラムの手法を使用して測定されます。ADC出力コードの標準偏差はLSBで算出され、ある指定された増幅率で全ての信号処理ブロックを経由した出力ノイズをrmsで表します。出力ノイズはADCの分解能がnビットのときに、 $1\text{LSB} = (\text{ADCのフルスケール})/2^n$ の関係を使用して等価的な電圧に変換することができます。AD9995の場合、1LSBは0.488mVです。

### 電源除去比 (PSR)

PSRは電源ピンにステップ状の変化を与えて測定します。PSRは電源電圧に規定のステップ状の変化を与え、そのときの出力データの変化から計算されます。

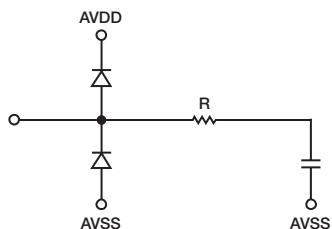

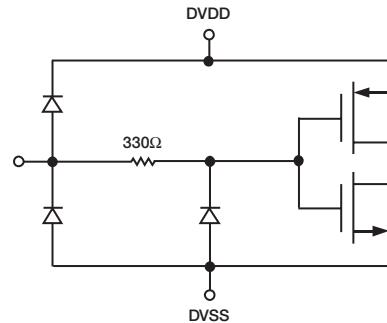

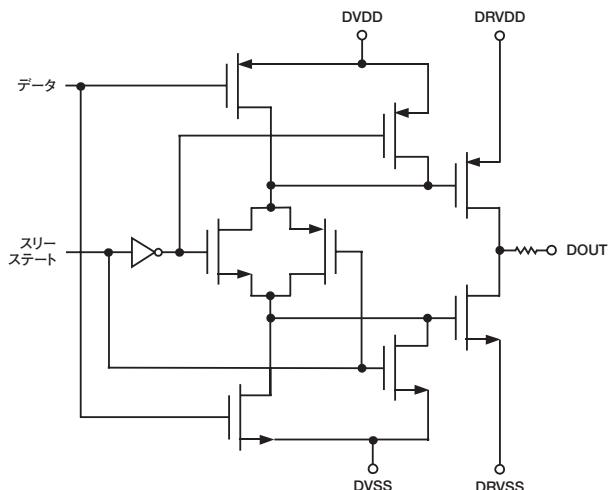

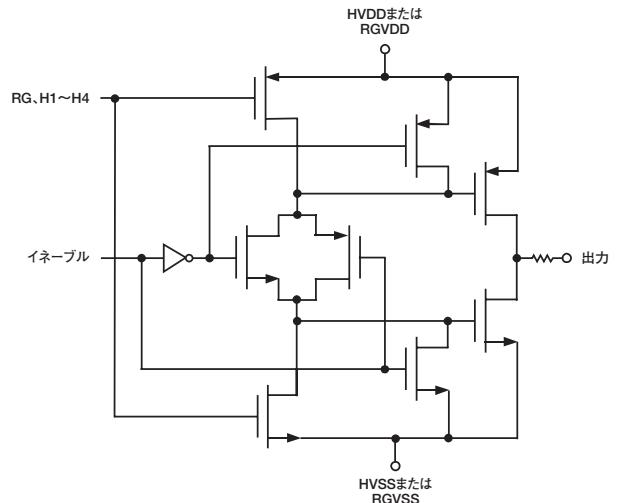

## 等価回路

回路1. CCDIN

回路3. デジタル入力

回路2. デジタル・データ出力

回路4. H1~H4、RG ドライバ

# AD9995 — 代表的な性能特性

## システム概要

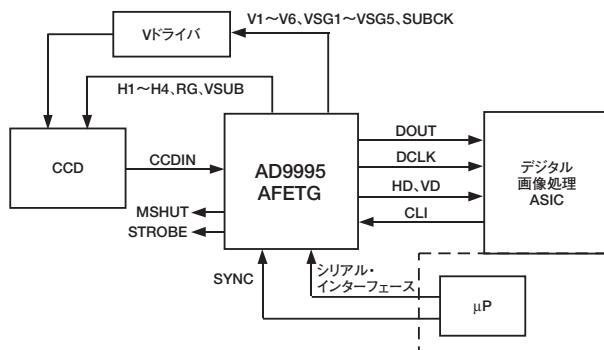

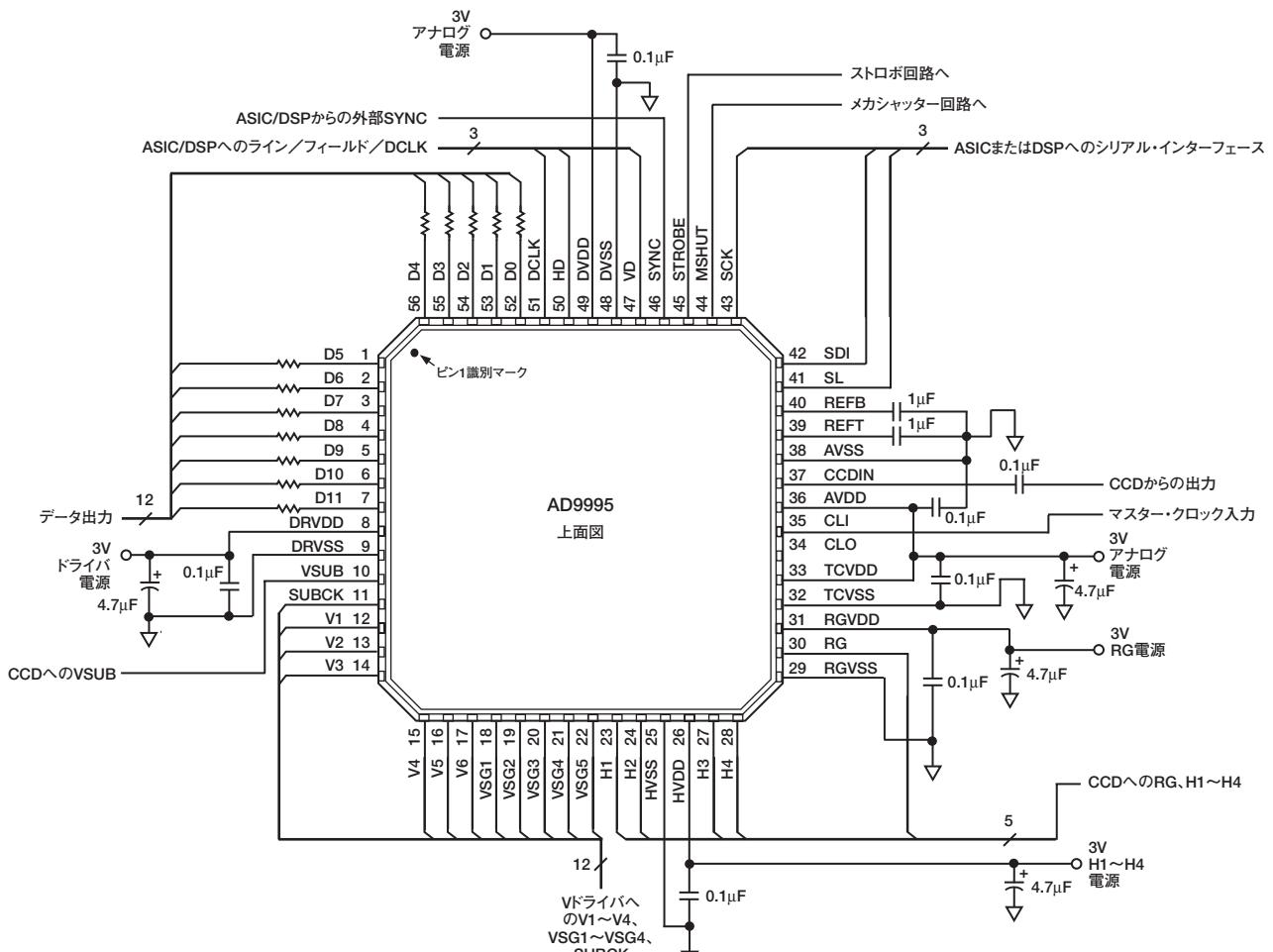

図1は、AD9995をマスター・モード (Master Mode) で使用したときの一般的なブロック図です。CCD出力は、CDS (Correlated Double Sampler: 相関ダブル・サンプラー)、VGA (Variable Gain Amplifier)、黒レベル・クランプ、ADC (Analog to Digital Converter) で構成されているAFE (Analog Front End) 回路へ供給されます。デジタル化されたピクセル情報は、デジタル信号処理や圧縮処理で構成されているデジタル・イメージ・プロセッサに送られます。CCDを動作させるために全てのCCDタイミングのパラメータは3線シリアル・インターフェースを介して、マイクロ・プロセッサからAD9995へ書き込まれます。システム・マスター・クロックであるCLI (Clock Input) はイメージ・プロセッサもしくは水晶発振器から供給され、AD9995が全ての水平転送クロック信号や垂直転送クロック信号、AFEで必要なクロックを生成します。外部から同期をかけるためにマイクロ・プロセッサからのSYNCパルスを使用することができ、内部のカウンタをリセットし、VDとHDの出力に再同期をかけます。

同様にAD9995はスレーブ・モード (Slave Mode) としての使用も可能で、VDとHDを外部のイメージ・プロセッサより供給することができます。このモードでは、AD9995のタイミングはVDとHDにより同期がかかります。

図1. 代表的なシステム・ブロック図、マスター・モード

H1～H4やRGのためのHドライバもまたAD9995に搭載されており、CCDに直接接続することが可能です。Hドライバの電圧は3.3Vまでサポートされています。外部にVドライバが必要で、垂直転送クロック (Vertical Transfer Clock)、センサー・ゲート・パルス (Sensor Gate Pulse)、基板クロック (Substrate Clock) を出力します。

AD9995では、またMSHUT (Mechanical Shutter) やSTROBE (Stroboscopic) 出力も設定でき、メカシャッターやストロボ (フラッシュ) 用の回路のトリガ信号として使用できます。

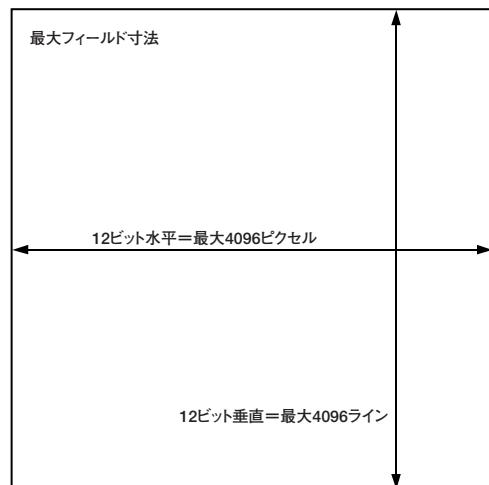

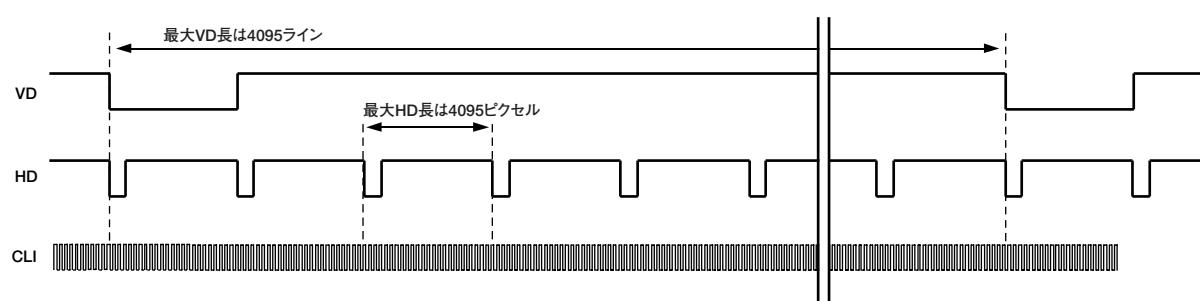

図2と3は、AD9995でサポートできる最大の水平方向と垂直方向のカウンタ数を表しています。全ての水平方向や垂直方向のクロックはこれらのカウンタより制御され、それぞれライン位置とピクセル位置を指定します。最大のHDの長さは1ラインあたり4095ピクセルで、最大のVDの長さは1フィールドあたり4095ラインです。

図2. 垂直カウンタと水平カウンタ

図3. VD/HDの最大寸法

# AD9995

## Precision Timingによる高速タイミングの生成

AD9995は、柔軟なPrecision Timingコアを使用して高速系タイミング信号を生成しています。このコアはCCDセンサーに必要なタイミング（リセット・ゲート：RG、水平転送クロック：H1～H4）とAFEで必要なタイミング（SHP/SHD）などを生成できるように構成されています。このシステムにより、回路設計者は水平クロックによるCCDセンサーからの読み出し信号とAFEの相関ダブル・サンプリングのタイミングを精度良く調整することで、画像品質を最適化することができます。

AD9995の高速系タイミングはマスター・モードやスレーブ・モードでも同じ動作をします。同期やパイプライン遅延の詳細については、「パワーアップと同期」の項を参照してください。

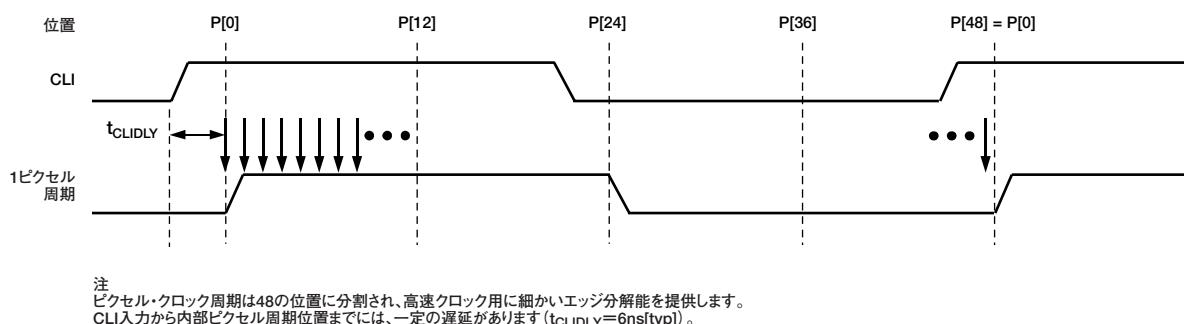

### タイミング分解能

Precision Timingコアは等倍のマスター・クロック入力（CLI）をリファレンスとして使用します。このクロックはCCDセンサーのピクセル・クロックの周波数と同じになります。図4に、内部のタイミング・コアがどのようにマスター・クロックの周期を48ステップ（48のエッジ）に分割するかを示します。20MHzのCLIの周波数を使用したとき、このタイミング・コアのエッジ分解能は1nsです。等倍のシステム・クロックを利用できない場合、CLIDIVIDEレジスタ（アドレス0x30）を使用

し、2倍のリファレンス・クロックを使用することもできます。AD9995は内部に1/2の分周回路を持っています。

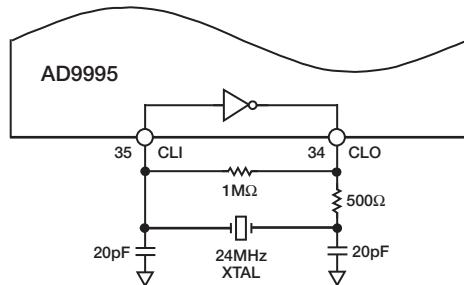

AD9995は同様にマスター・クロック出力としてCLO（CLIの反転出力）を持っています。この出力は水晶発振器用のドライバとして使用するものです。水晶発振器はCLIとCLOの間に接続し、AD9995のマスター・クロックを発生させるために使用します。水晶発振器を使用したときの詳細については、図39を参照してください。

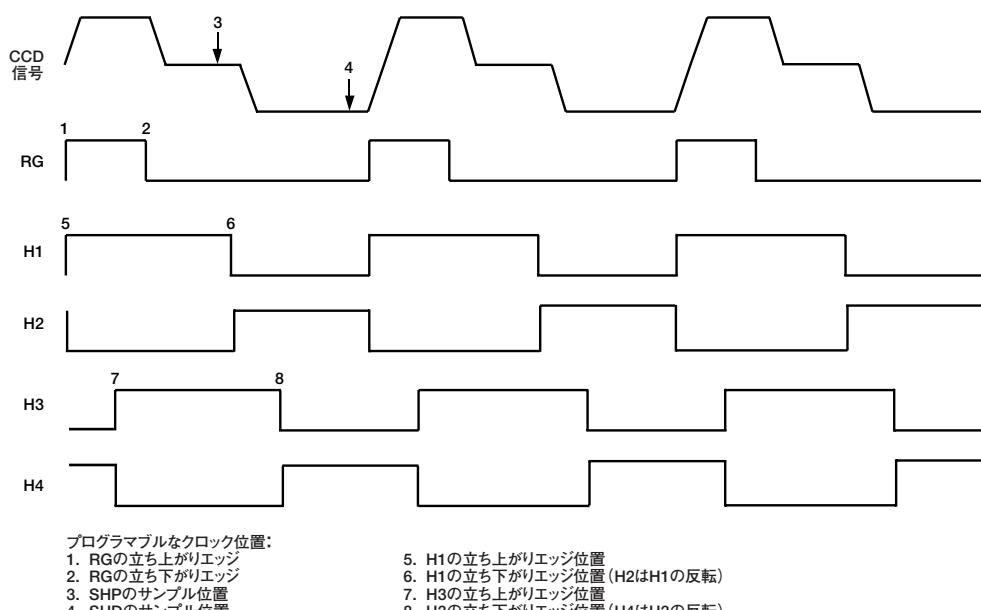

### 高速クロックのプログラマビリティ

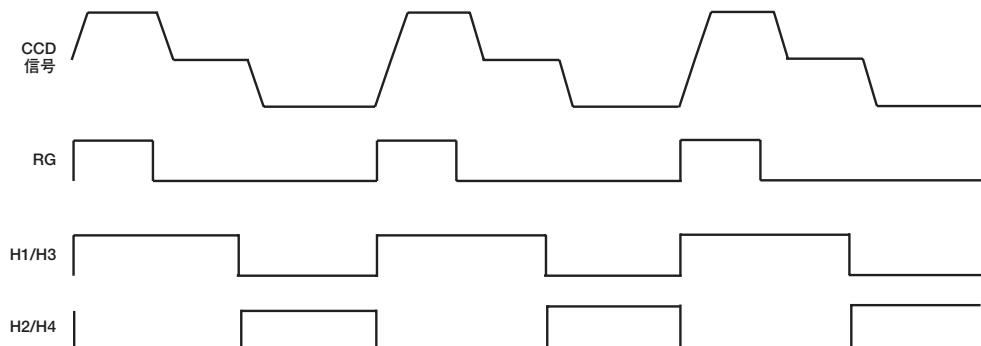

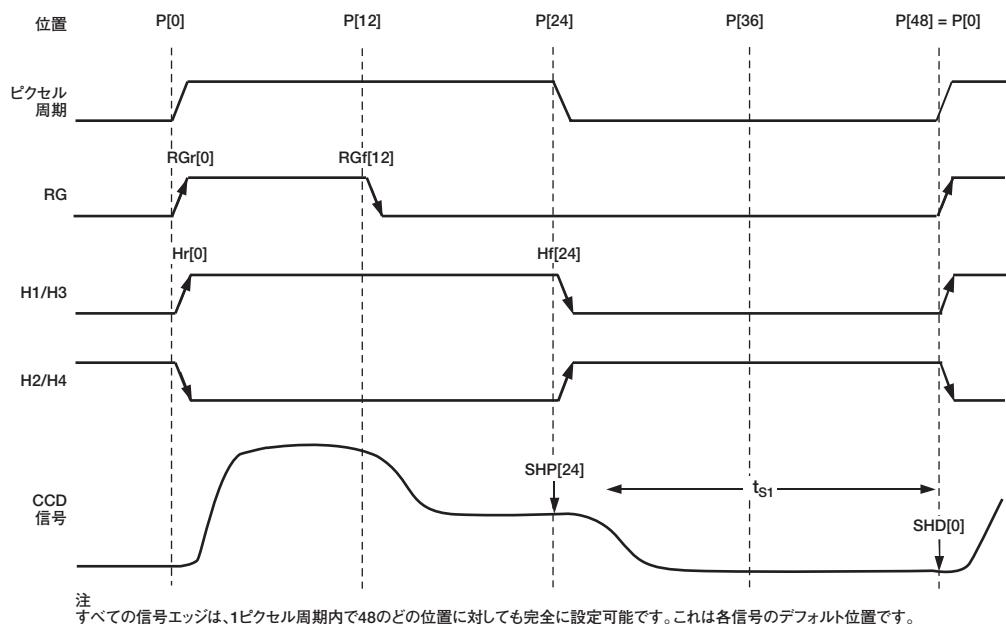

図5は、高速系クロックであるRG、H1～H4、SHP、SHDがどのようにして発生されるかを示しています。RGパルスは立ち上がりエッジと立ち下がりエッジの位置の設定が可能で、極性の設定もできます。水平転送クロックであるH1とH3は立ち上がりエッジと立ち下がりエッジ、極性を設定できます。H2とH4は常時それぞれH1とH3の反転になります。表Iに、高速系タイミングのレジスタとパラメータを示します。図6は一般的な2相水平転送クロックのタイミングを示しており、H3とH4はH1とH2のエッジ位置と同じになります。

エッジ位置は6ビットのデータ幅で設定しますが、有効な設定は48のエッジです。したがって、レジスタの値は4つのセグメントに分かれ、それぞれのセグメントが12のエッジ位置を表しています。表IIは、エッジ位置に設定するためのレジスタの値を示しています。

図4. CLIマスター・クロック入力からの高速クロック分解能

図5. 高速クロックのプログラマブルな位置設定

図7は、全ての高速系クロックのデフォルト位置を表しています。

### HドライバとRG出力

高速系クロックのエッジ位置がいろいろ設定可能であるのに加えて、AD9995の特長としてRGとH1～H4には出力ドライバ回路が備わっています。これらのドライバ回路はCCDに直接接続するのに十分な能力を持っています。HドライバとRGドライバの出力電流はDRVCONTROLレジスタ（アドレス0x35）を使用することによって、CCDの負荷に適するように立ち上がり時間と立ち下がり時間を調整することができます。3ビットのデータ幅でドライブ電流を設定することができ、4.1mAごとに可変できます。最小の設定値は0でOFFもしくはハイ・インピーダンス出力となります。最大の設定値は7で、ドライブ電流値は30.1mAとなります。

図5、6、7に示すように、H2とH4はそれぞれH1とH3の反転となります。H1とH2の交差する位置は出力振幅の50%ほどになりますが、このクロスポイントの位置はプログラマブルではありません。

### デジタル・データ出力

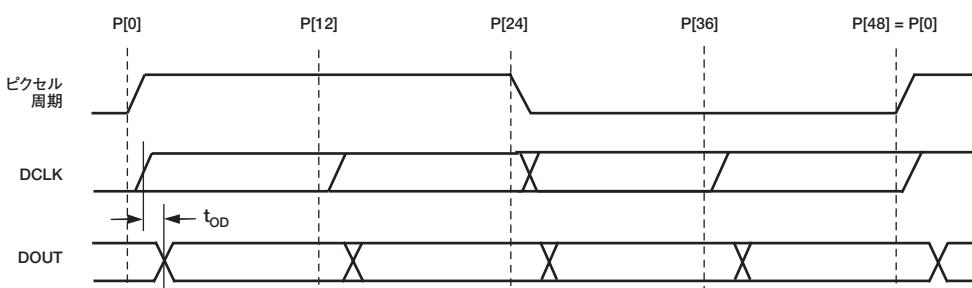

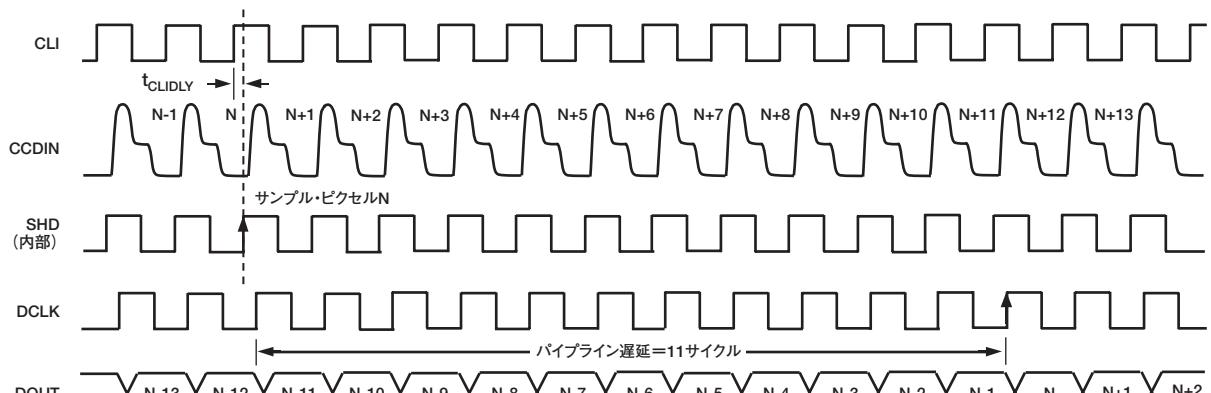

AD9995のデータ出力とDCLKの位相は、DOUTPHASEレジスタ（アドレス0x37、ビット[5:0]）を使用することにより設定可能です。図8aに示すように0から47のどのエッジでも設定できます。通常、DOUTとDCLK信号は、DOUTPHASEレジスタの内容に基づいて位相が変化します。DCLK出力の位相は、DCLKMODEレジスタ（アドレス0x37、ビット6）に「1」を書き込むことにより、固定の位置にすることができます。このモードではDCLK出力はCLO（CLIの反転）の位相と同じに固定されますが、データ出力の位相は設定可能です。

DCLKの立ち上がりエッジからDOUTの遷移位置には、 $t_{OD}$ と呼ばれる一定の遅延量があります。この遅延量はDOUTDELAYレジスタ（アドレス0x37、ビット[8:7]）を使うことで、0nsから12nsの4つの値で設定することができます。デフォルトの値は8nsです。

AD9995のパイプライン遅延を図8bに示します。CCDからの入力信号はSHDでサンプリングされ、11サイクルの遅延の後にそのデータが出力されます。

表I. H1、H3、RG、SHP/SHDに対するコア・レジスタのタイミング・パラメータ

| パラメータ    | 長さ | 範囲          | 説明                            |

|----------|----|-------------|-------------------------------|

| 極性       | 1b | ハイレベル／ローレベル | H1、H3、RGの極性制御（0=非反転、1=反転）     |

| 立ち上がりエッジ | 6b | 0～47エッジ位置   | H1、H3、RGの立ち上がりエッジ位置           |

| 立ち下がりエッジ | 6b | 0～47エッジ位置   | H1、H3、RGの立ち下がりエッジ位置           |

| サンプリング位置 | 6b | 0～47エッジ位置   | 内部SHP信号とSHD信号のサンプリング位置        |

| ドライブ強度   | 3b | 0～47電流ステップ  | H1～H4出力とRG出力の駆動電流（4.1mA／ステップ） |

H1とH3に対して同じトグル位置を使用すると、標準の2相Hクロックが発生します。

図6. 2相Hクロックの動作

表II. Precision Timingのエッジ位置

| セグメント | エッジ位置（10進） | レジスタ値（10進） | レジスタ値（2進）     |

|-------|------------|------------|---------------|

| I     | 0～11       | 0～11       | 000000～001011 |

| II    | 12～23      | 16～27      | 010000～011011 |

| III   | 24～35      | 32～43      | 100000～101011 |

| IV    | 36～47      | 48～59      | 110000～111011 |

# AD9995

図7. 高速タイミングのデフォルト位置

図8a. デジタル出力の位相調整

図8b. パイプライン遅延

## 水平クランプとブランкиング

AD9995の水平クランプとブランキング・パルスは、さまざまなアプリケーションに対応できるように設定することができます。CLPOB、PBLK、HBLKは、それぞれのフィールドの異なるリージョン（領域）に別々に設定することができます。これにより、黒画素のクランプとブランキングのパターンをそれぞれの読み出しの箇所で変化させることができ、異なる読み出し転送のタイミングや高速転送ラインなどに対応させることができます。

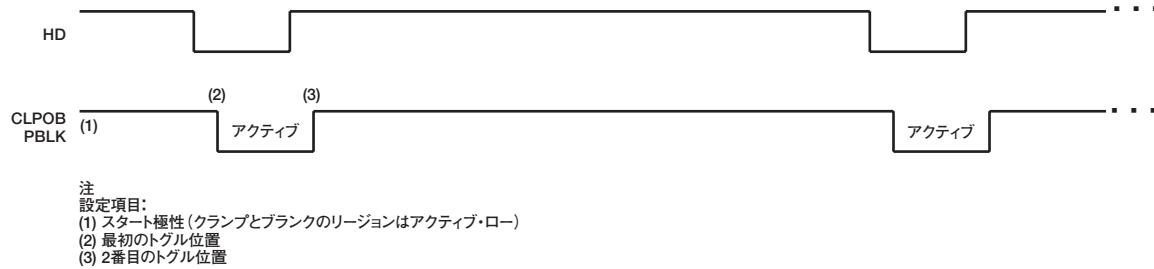

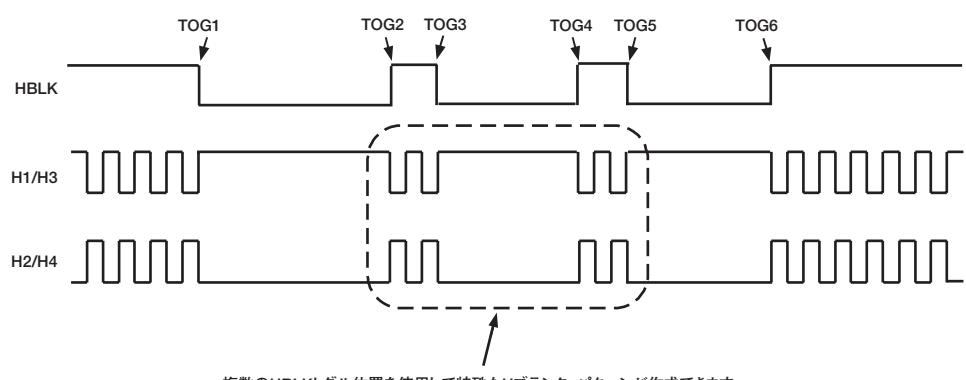

### CLPOBとPBLKの個々のパターン

図9に表しているように、CLPOBとPBLKはAFEの水平タイミングを構成しています。これら2つの信号は、表IIIのレジスタを使用して別々に設定することができます。SPOL（Start Polarity）は信号のスタート極性、TOG1とTOG2はそれぞれパルスの1番目のトグル位置と2番目のトグル位置を示します。両方の信号ともアクティブ・ローであり、それぞれ適宜に使用してください。

CLPOBとPBLKは、10のVシーケンス（V-Sequence）ごとに設定します。「垂直タイミングの生成」の項に説明するように、

10の個別のVシーケンスを作成することができ、それぞれのVシーケンスにCLPOBとPBLKの個別のパルス・パターンを割り当てます。図9に示すように、シーケンス・チェンジ・ポジション（SCP）は読み出しのフィールドをそれぞれのリージョンに分割します。1つ1つのVシーケンスはそれぞれのリージョンに割り当てられ、それぞれの垂直転送のVシーケンス・タイミングに合わせてCLPOBとPBLKのパルスを適宜対応させます。

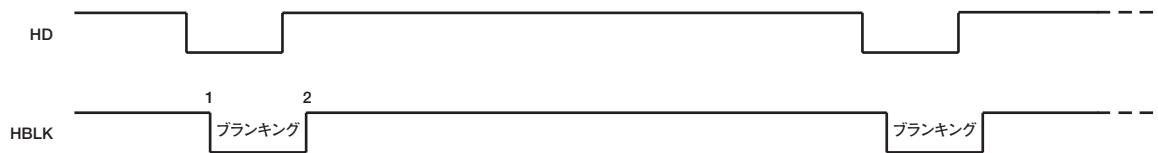

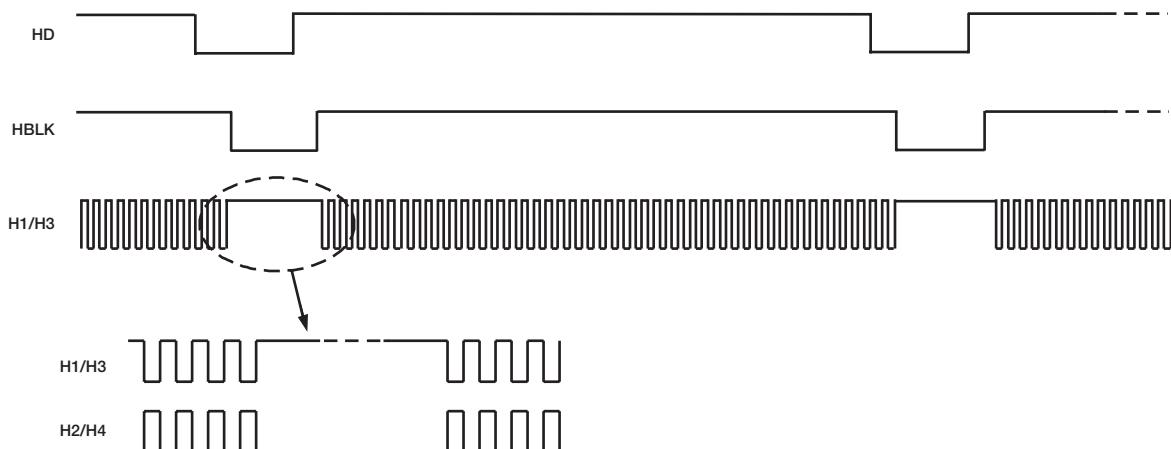

### 個々のHBLKパターン

図10に示すように、HBLKの設定方法はCLPOBやPBLKの設定方法に似ています。しかしながら、HBLKについてはスタート極性制御はできません。ブランキング期間を開始し停止するためのトグル位置の設定のみが可能です。加えて、ブランキング期間におけるH1～H4の信号の極性を決めるためのHBLKMASKというレジスタがあります。HBLKMASKをハイに設定すると、図11にあるようにブランキング期間の極性はH1=H3=ロー、H2=H4=ハイとなります。CLPOBやPBLKと同じように、HBLKレジスタはそれぞれのVシーケンスに割り当てられ、異なるブランキング信号が異なる垂直転送タイミングのシーケンスと一緒に使用できるようになります。

図9. クランプ・パルスとプリブランク・パルスの配置

表III. CLPOBとPBLKのパターン・レジスタ

| レジスタ | 長さ  | 範囲           | 説明                             |

|------|-----|--------------|--------------------------------|

| SPOL | 1b  | ハイレベル／ローレベル  | Vシーケンス0～9に対するCLPOB/PBLKのスタート極性 |

| TOG1 | 12b | 0～4095ピクセル位置 | Vシーケンス0～9に対するライン内の最初のトグル位置     |

| TOG2 | 12b | 0～4095ピクセル位置 | Vシーケンス0～9に対するライン内の2番目のトグル位置    |

表IV. HBLKパターン・レジスタ

| レジスタ     | 長さ  | 範囲               | 説明                                                                                                     |

|----------|-----|------------------|--------------------------------------------------------------------------------------------------------|

| HBLKMASK | 1b  | ハイレベル／ローレベル      | H1/H3に対するマスク極性（0=H1/H3ロー、1=H1/H3ハイレベル）                                                                 |

| HBLKALT  | 2b  | 0～3のオルタネーション・モード | HBLKの奇数／偶数オルタネーションをイネーブル。トグル位置0=オルタネーションをディスエーブル。1=TOG1-TOG2奇数、TOG3-TOG6偶数。2=3=TOG1-TOG2偶数、TOG3-TOG6奇数 |

| HBLKTOG1 | 12b | 0～4095のピクセル位置    | 各Vシーケンス0～9に対するライン内の最初のトグル位置                                                                            |

| HBLKTOG2 | 12b | 0～4095のピクセル位置    | 各Vシーケンス0～9に対するライン内の2番目のトグル位置                                                                           |

| HBLKTOG3 | 12b | 0～4095のピクセル位置    | 各Vシーケンス0～9に対するライン内の3番目のトグル位置                                                                           |

| HBLKTOG4 | 12b | 0～4095のピクセル位置    | 各Vシーケンス0～9に対するライン内の4番目のトグル位置                                                                           |

| HBLKTOG5 | 12b | 0～4095のピクセル位置    | 各Vシーケンス0～9に対するライン内の5番目のトグル位置                                                                           |

| HBLKTOG6 | 12b | 0～4095のピクセル位置    | 各Vシーケンス0～9に対するライン内の6番目のトグル位置                                                                           |

# AD9995

## 特殊なHBLKパターンの生成

HBLKには6つのトグル位置設定があります。通常は、2つのトグル位置を設定すれば一般的なHBLKのパターンを作成することができます。しかしながら、図12に示すように、さらにトグル位置設定を加えることによってSpecial HBLK（特殊なHBLK）パターンを生成することができます。このパターンの例は、6つのトグル位置を設定することにより、HBLKのブランкиング内に2つのグループのパターンを生成することができます。そして、トグル位置を変更することにより、異なるパターンを作成することができます。

## HBLKライン・オルタネーションの生成

AD9995の機能の1つとして、奇数ラインと偶数ラインでHBLKのトグル位置を可変させることができます。この機能はVパターンのオルタネーションと同時にもしくは単独で使うことができます。HBLKALTに「1」を書き込むと、TOG1とTOG2は奇数ラインでのみ有効となり、TOG3からTOG6は偶数ラインで有効になります。HBLKALTレジスタに「2」を書き込むと、1のときは反対になり、TOG1とTOG2は偶数ラインで有効となり、TOG3からTOG6は奇数ラインで有効になります。「垂直タイミングの生成」の「ライン・オルタネーション」の項に詳細な動作が記載されています。

- 設定項目:

1. 最初のトグル位置=ブランкиングのスタート

2. 2番目のトグル位置=ブランкиングの終わり

図10. 水平ブランкиング (HBLK) パルスの配置

ブランкиング時のH1の極性はプログラマブルです (H2はH1の反対の極性)

図11. HBLKマスクの制御

複数のHBLKトグル位置を使用して特殊なHブランク・パターンが作成できます

図12. 特殊なHBLKパターンの生成

## 水平タイミング・シーケンスの例

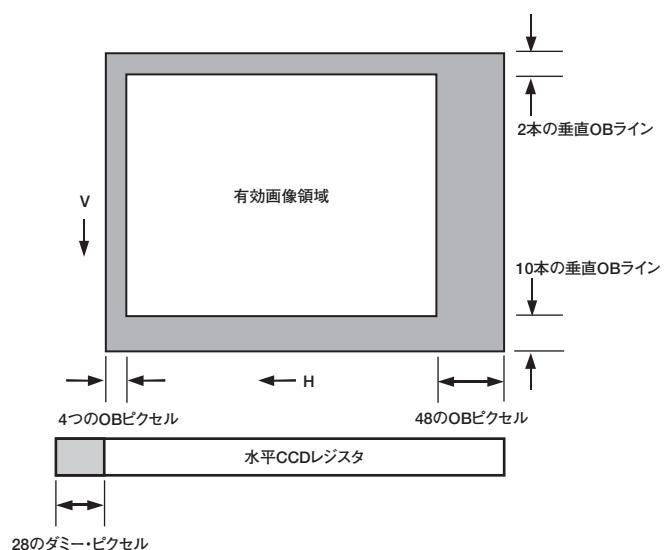

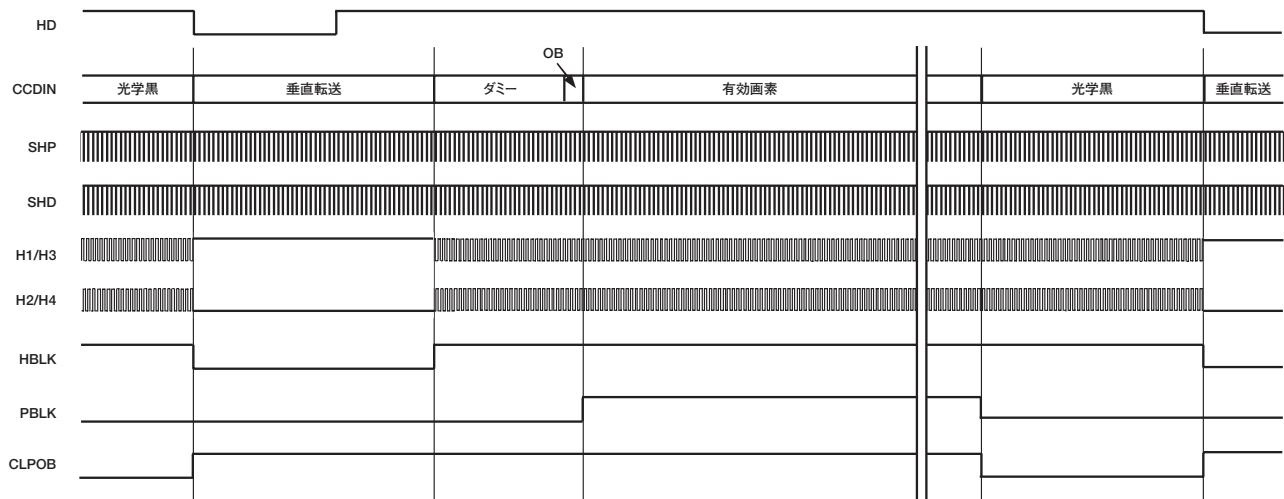

図13にCCDのレイアウトの例を示します。水平レジスタには28のダミー・ピクセルがあり、CCDセンサーからのそれぞれのラインで読み出されます。垂直方向では読み出しの前に光学的黒（Optical Black : OB）のラインが10本、読み出しの後に2本あります。水平方向では前に4つのOBピクセルがあり、後ろに48のOBピクセルがあります。

図14に有効画素の読み出し時に使用される基本的なシーケンスを表します。それぞれのラインの後ろに48のOBピクセルがあり、CLPOB信号用に利用されます。PBLKはオプションです。

CCDセンサーの無効画素期間のデジタル出力をブランクにするために利用されます。HBLKは垂直転送の期間に使用されます。

HBLK、CLPOB、PBLKのパラメータはVシーケンス・レジスタで設定できます。

OBラインの全てに対してクランプする別のシーケンスのように、精巧なクランプ仕様にすることもできます。これは、OBラインの読み出しに異なるVシーケンスを設定することが必要です。

図13. CCDの構成例

図14. 水平シーケンスの例

# AD9995

## 垂直タイミングの生成

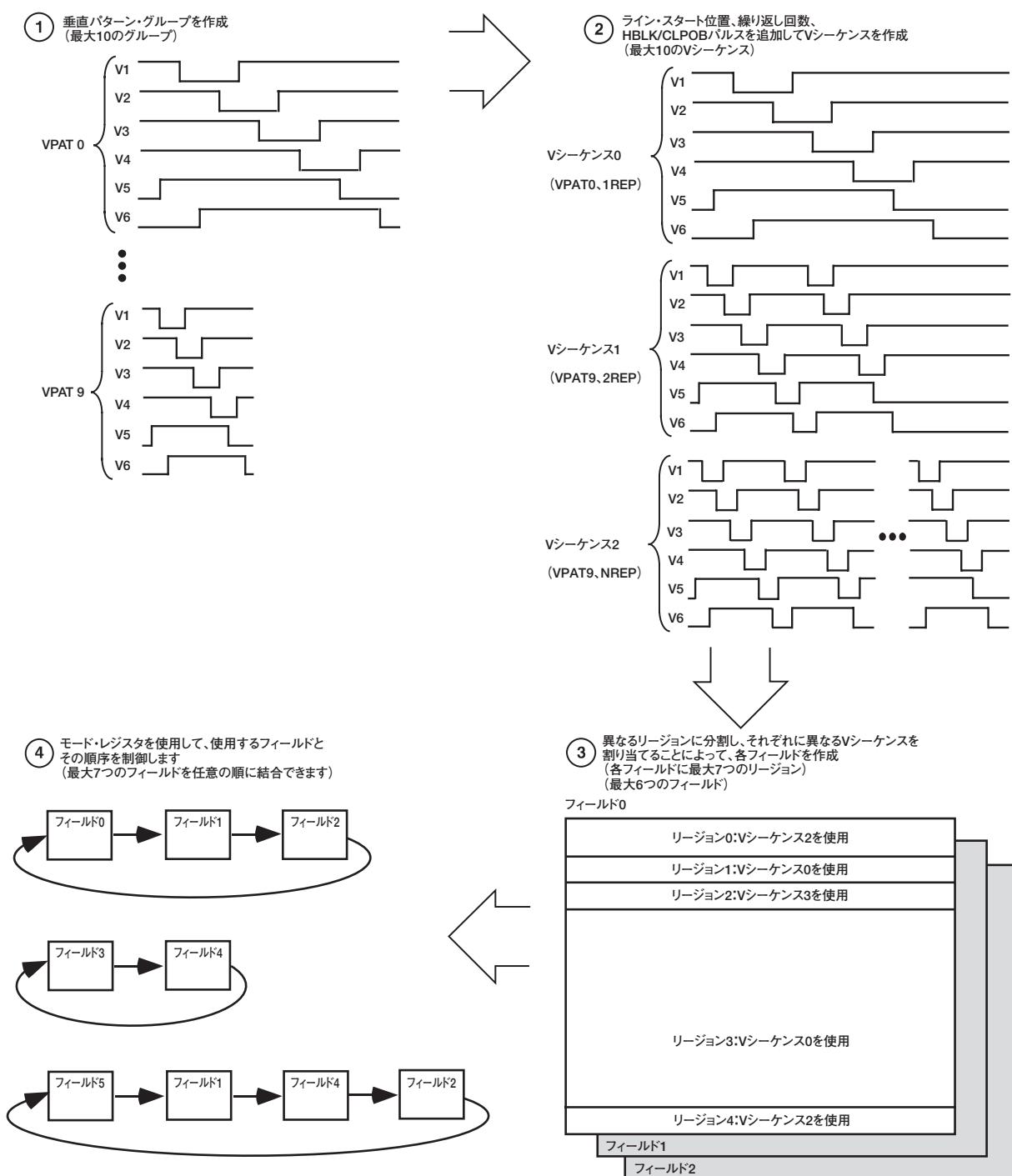

AD9995はCCDの垂直転送のタイミングを作成するのに非常に柔軟に対応でき、さまざまなCCDセンサーや異なるシステムをサポートすることができます。6相の垂直転送パルスであるV1からV6は、それぞれのラインのピクセルデータをCCDセンサーの水平転送レジスタへ移動させるのに使用します。AD9995は4つのステップを踏むことによって、さまざまな読み出し仕様に対応できるように、それぞれ別々に出力を設定することができます。

図15は、垂直タイミングの生成方法を4つのステップで示しています。初めに垂直パターン・グループ (Vertical Pattern

Group) レジスタを使用して、それぞれ個別のパルス・パターンを作ります。次にそのVパターン・グループ (V-Pattern Group) にさらに設定項目を加えて、シーケンス (Sequence) として設定します。3番目に1つのフィールド内を別々のリージョンに分割し、そしてシーケンスをそれぞれのリージョンに割り当てます。それぞれのフィールドは7つの異なるリージョンまで分割することができ、高速転送の領域や固有の垂直転送ライン・シフトなどにも使用できるようになっています。最大6つのフィールドを作成しておくことができます。最後に、モード・レジスタでさまざまな仕様に対応したフィールドの読み出し順番を設定します。

図15. 垂直タイミング生成のまとめ

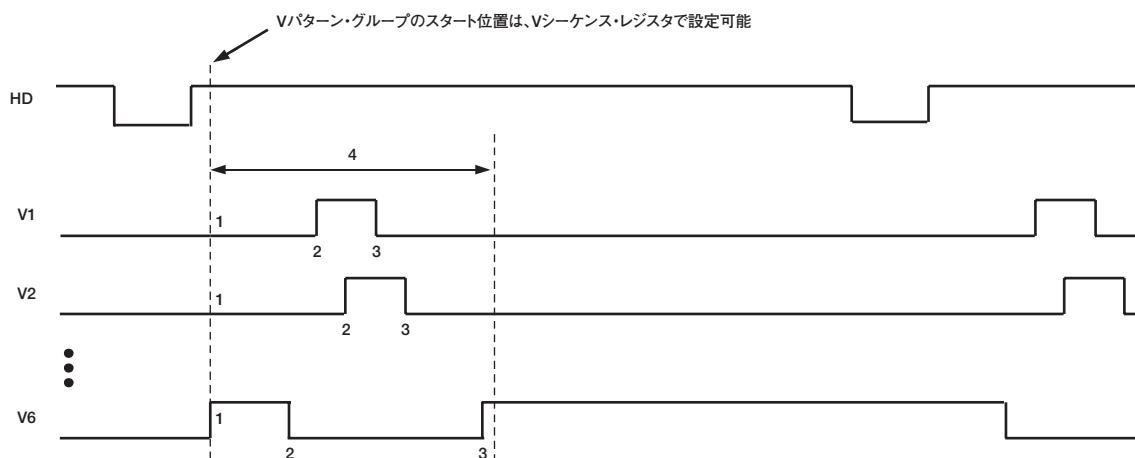

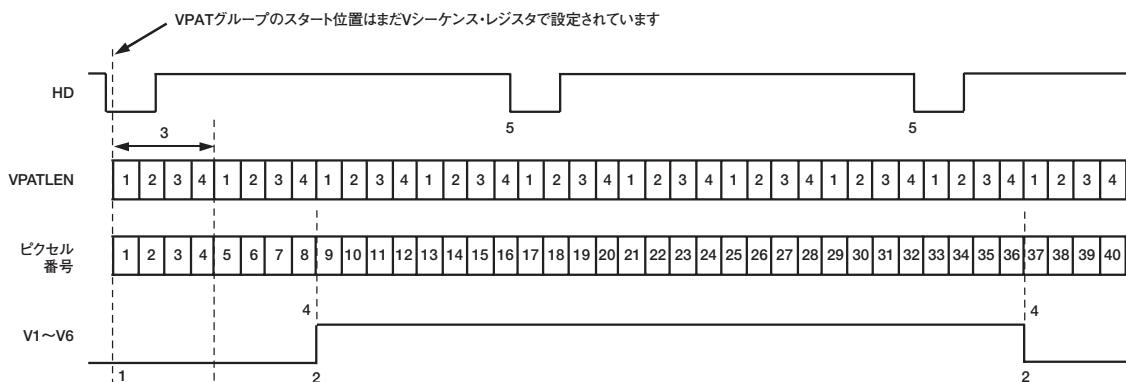

### 垂直パターン・グループ (VPAT)

垂直パターン・グループは、それぞれのV1からV6の出力信号のパターンを定義します。表Vに10のVパターン・グループを作成するのに使用するレジスタをまとめています。スタート極性 (VPOL) は垂直転送シーケンスを開始するときの極性を決め、V1からV6の出力それぞれに対しハイカローを設定します。1番目、2番目、3番目のトグル位置 (VTOG1、VTOG2、VTOG3) は水平ラインでパルス極性が変化する箇所をピクセルの位置として設定します。4番目のトグル位置設定 (VTOG4) はVパターン・グループ8と9で利用できます。全てのトグル位置設定は12ビットの値で設定することができ、水平ラインのどの場所にでも指定することができます。別のレジスタであるVPATSTARTは1水平ライン内でどの場所からVパターン・グループを開始させるかを決めるレジスタです（「垂直シーケンス」を参照）。VPATLENレジスタはVパターン・グループの合計の長さを指定するもので、同じパターンが繰り返されている

ときの繰り返し回数をピクセル数で設定します（「垂直シーケンス」を参照）。

FREEZEレジスタとRESUMEレジスタはV1～V6の出力を一時的に停止させたり開始させたりするレジスタです。FREEZEレジスタで設定されるピクセル位置で、V1からV6の出力はそのときの状態であるハイカローかのDC値に固定になります。V1からV6の出力は、RESUMEレジスタで設定されているピクセル位置までそのDC値を保持します。FREEZE/RESUMEレジスタは2セットありますので、垂直転送の出力を同じ水平ライン内の2箇所に挿入することができます。FREEZEレジスタとRESUMEレジスタの設定位置はVパターン・グループ・レジスタの中にありますが、VMASKレジスタを使用して別に有効にする必要があります。詳細は「垂直シーケンス」の項に記載しています。

表V. 垂直パターン・グループ・レジスタ

| レジスタ    | 長さ  | 範囲            | 説明                              |

|---------|-----|---------------|---------------------------------|

| VPOL    | 1b  | ハイレベル／ローレベル   | 各V1～V6出力のスタート極性                 |

| VTOG1   | 12b | 0～4096のピクセル位置 | 各V1～V6出力に対するライン内の最初のトグル位置       |

| VTOG2   | 12b | 0～4096のピクセル位置 | 各V1～V6出力に対するライン内の2番目のトグル位置      |

| VTOG3   | 12b | 0～4096のピクセル位置 | 各V1～V6出力に対するライン内の3番目のトグル位置      |

| VTOG4   | 12b | 0～4096のピクセル位置 | Vパターン・グループ8と9でのみ使用可能な、4番目のトグル位置 |

| VPATLEN | 12b | 0～4096のピクセル   | 各Vパターン・グループの合計長                 |

| FREEZE1 | 12b | 0～4096のピクセル位置 | V1～V6出力を現在レベル（スタティックDC）に保持      |

| RESUME1 | 12b | 0～4096のピクセル位置 | V1～V6出力の動作を再開してパターンを終了          |

| FREEZE2 | 12b | 0～4096のピクセル位置 | V1～V6出力を現在レベル（スタティックDC）に保持      |

| RESUME2 | 12b | 0～4096のピクセル位置 | V1～V6出力の動作を再開してパターンを終了          |

各Vパターンに対する設定項目:

1. スタート極性

2. 最初のトグル位置

3. 2番目のトグル位置 (3番目のトグル位置も使用可能、4番目のトグル位置はVパターン・グループ8と9に対して使用可能)

4. V1～V6の全出力に対する合計パターン長

図16. 垂直パターン・グループのプログラマビリティ

# AD9995

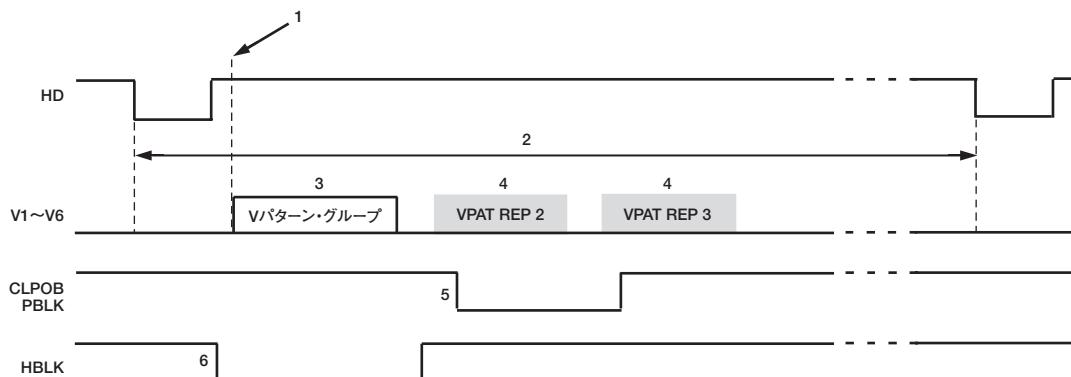

## 垂直シーケンス (VSEQ)

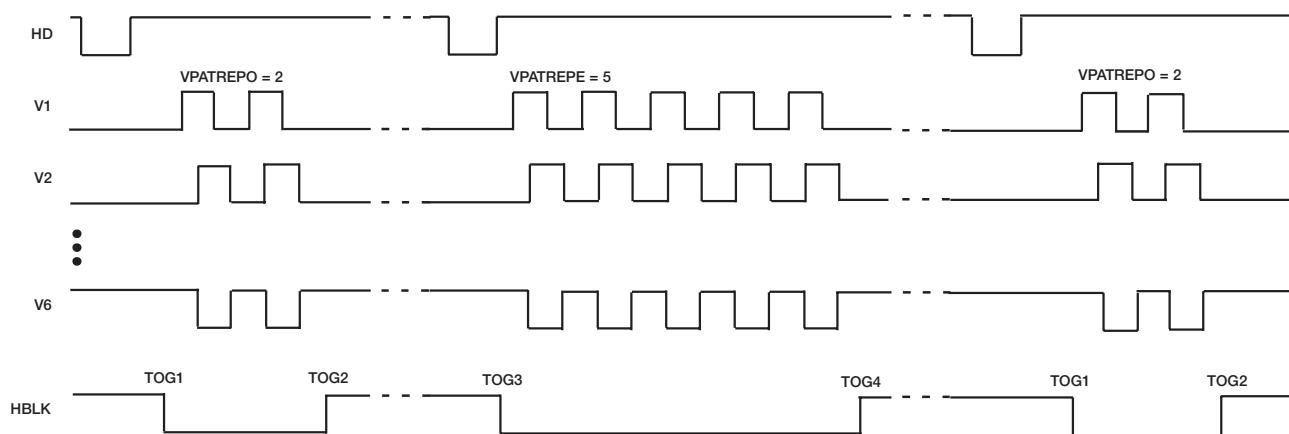

垂直シーケンスは10のVパターン・グループから選択した1つに対し、繰り返し回数、スタート位置、水平クランプ、水平ブランкиングなどを設定したものです。最大10のVシーケンスを設定できますが、それらのレジスタを表VIに表します。図17は、どのようにしてこれらのレジスタがそれぞれのVシーケンスを作成するために使うことができるかを示しています。

VPATSEL (V-Pattern Select) レジスタは、どのVパターン・グループをそのVシーケンスのために使用するかを決めるレジスタです。基本的なVパターン・グループには高速転送シフトやラインごとの混合のために、VPATREPO (V-Pattern Repetition Odd) レジスタやVPATREPE (V-Pattern Repetition Even) レジスタを使用して、繰り返し回数の設定が追加されます。一般的にこれら2つのレジスタには同じ値を書き込みます。しかしながら、奇数ラインと偶数ラインの垂直転送クロックの繰り返し回数が異なる場合には、それぞれのレジスタに違う値を書き込

みます（「垂直シーケンス」の「ライン・オルタネーション」の項を参照）。VPATSTART (V-Pattern Start) レジスタはVパターンがその水平ラインのどのピクセル位置から開始するかを設定します。VMASK (V Mask) レジスタはFREEZE/RESUMEレジスタと共に使用し、垂直転送パルスの出力をマスクする（出力させない）動作をさせることができます。FREEZE1/RESUME1とFREEZE2/RESUME2のどちらかもしくは両方とも使用することができます。

HDLEN (HD Length) レジスタは水平ラインの長さ（ピクセル数）を指定します。それぞれのVシーケンスはさまざまな読み出し方法を駆使するために、それぞれ異なる水平ラインの長さを持つこともあります。水平ラインの長さは最大4096ピクセル数まで設定することができます。フィールド内の最後の水平ライン長は、HDLAST (HD Last Line Length) レジスタを使用して異なる値を指定することもできます。HDLASTレジスタはFieldレジスタの中にあります。

表VI. Vシーケンス・レジスタ (HBLK、CLPOB、PBLKレジスタについては表IIIとIVを参照)

| レジスタ      | 長さ  | 範囲               | 説明                                                                                                                  |

|-----------|-----|------------------|---------------------------------------------------------------------------------------------------------------------|

| VPATSEL   | 4b  | 0~9のVパターン・グループ番号 | 各Vシーケンスに対して選択されたVパターン・グループ                                                                                          |

| VMASK     | 2b  | 0~3のマスク・モード      | FREEZE/RESUMEレジスタで指定した位置でV1~V6出力のマスキングをイネーブル。0=マスクなし、1=FREEZE1/RESUME1をイネーブル、2=FREEZE2/RESUME2をイネーブル、3=1と2の両方をイネーブル |

| VPATREPO  | 12b | 0~4095の繰り返し回数    | 奇数ラインに対するVパターン・グループの繰り返し回数                                                                                          |

| VPATREPE  | 12b | 0~4095の繰り返し回数    | 奇数／偶数オルタネーションが必要でない場合は、VPATREPEに等しく設定<br>偶数ラインに対するVパターン・グループの繰り返し回数                                                 |

| VPATSTART | 12b | 0~4095のピクセル位置    | 奇数／偶数オルタネーションが必要でない場合は、VPATREPOに等しく設定<br>選択されたVパターン・グループのスタート位置                                                     |

| HDLEN     | 12b | 0~4095のピクセル数     | 各Vシーケンス内のラインのHDライン長                                                                                                 |

- 各Vシーケンスに対する設定項目:

1. 選択されたVパターン・グループのライン内のスタート位置

2. HDライン長

3. 任意のVパターン・グループを選択するためのVパターン選択 (VPATSEL)

4. Vパターン・グループの繰り返し回数 (必要な場合)

5. CLPOB信号とPBLK信号に対するスタート極性とトグル位置

6. HBLK信号に対するマスキング極性とトグル位置

図17. Vシーケンスのプログラマビリティ

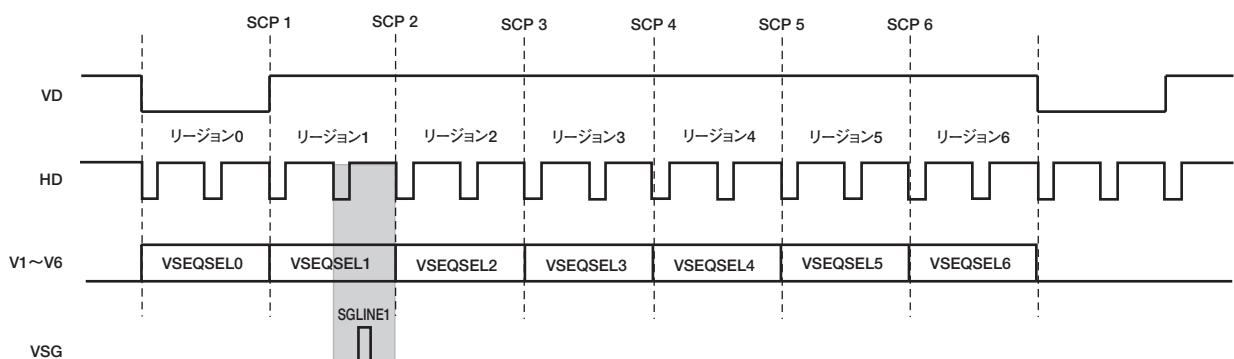

### 完全なフィールド：Vシーケンスの結合

Vシーケンスを作成した後は、それらを組み合わせることにより異なる読み出しフィールドを作成します。1つのフィールドには最大7つの異なるリージョンを構成することができ、それぞれのリージョンに対し異なるVシーケンスを選択します。図18はシーケンス・チェンジ・ポジション (SCP) がどのようにしてリージョンを水平ラインごとに分割するかを表しており、VSEQSELレジスタはそれぞれのリージョンにどのVシーケンスを割り当てるかを選択しています。VSG (Vertical Sensor Gate) パルス出力の設定は、このフィールド・レジスタの中にはあります。

表VIIは、複数のフィールドを構成するためのレジスタをまとめています。最大6の異なるフィールド情報を前もって設定しておくことができます。

VSEQSELレジスタはそれぞれのリージョンに対し10あるVシーケンスのうち、どのVシーケンスをどのリージョンに割り当てるかを選択します。SWEEPレジスタはどのリージョンに対してもスイープ (Sweep) モードを適用するのかを決めます。MULTI (Multiplier: 乗算) レジスタはどのリージョンに対してマルチプライヤ (乗算) モードを実行させるのかを指定しま

す。SCPレジスタはそれぞれのリージョン同士を分割するためには水平ラインの値で設定します。VDLEN (VD Length) レジスタは1フィールドが全部で何ラインあるかを設定します。水平ラインの長さの設定にはHDLEN (HD Length) レジスタを使用します。これはピクセル数で設定するレジスタで、Vシーケンス・レジスタの中にはあります。しかし、HDLASTレジスタはフィールドの最後の水平ライン長のピクセル数を指定することができます。VPATSECONDレジスタは、センサー・ゲート (VSG) ラインでV1~V6の出力に2番目のVパターン・グループを追加するときに使用します。

SGMASK (Sensor Gate Mask) レジスタはそれぞれのVSG出力を有効にするか無効にするかを指定します。それぞれのVSG出力には1ビット分が与えられており、ハイのときはそのVSG出力が無効になり、ローのときはそのVSG出力が有効になります。SGPATSEL (Sensor Gate Pattern Select) レジスタはそれぞれのVSG出力に対し、4つあるSGパターンからどれを選択するのかに使われます。SG Patternレジスタを使用し固有のSGパターンを作成できます。SGLINE1レジスタは、VSG出力をフィールドのどのラインで発生させるかを決めています。SGLINE2レジスタもあり、同じVSGパルスを異なるラインに再度発生させることもできます。

表VII. フィールド・レジスタ

| レジスタ       | 長さ  | 範囲               | 説明                                                                             |

|------------|-----|------------------|--------------------------------------------------------------------------------|

| VSEQSEL    | 4b  | 0~9のVシーケンス番号     | フィールド内の各リージョンに対して選択されたVシーケンス                                                   |

| SWEEP      | 1b  | ハイレベル/ローレベル      | ハイレベルに設定すると、各リージョンのスイープ・モードをイネーブル                                              |

| MULTI      | 1b  | ハイレベル/ローレベル      | ハイレベルに設定すると、各リージョンのマルチプライヤ・モードをイネーブル                                           |

| SCP        | 12b | 0~4095のライン番号     | 各リージョンのシーケンス・チェンジ・ポジション                                                        |

| VDLEN      | 12b | 0~4095のライン番号     | 各フィールド内の合計ライン数                                                                 |

| HDLAST     | 12b | 0~4095のピクセル番号    | 各フィールド内の最後のHDラインの長さ (ピクセル)                                                     |

| VPATSECOND | 4b  | 0~9のVパターン・グループ番号 | VSGライン区間で適用される2番目のパターンに対して選択されるVパターン・グループ                                      |

| SGMASK     | 6b  | ハイレベル/ローレベル、各VSG | 個々のVSG出力をマスクするにはハイレベルに設定。VSG1 [0], VSG2 [1], VSG3 [2], VSG4 [3], VSG5 [4]      |

| SGPATSEL   | 12b | 0~3のパターン番号、各VSG  | 各VSG出力のVSGパターン番号を選択。VSG1 [1:0], VSG2 [3:2], VSG3 [5:4], VSG4 [7:6], VSG5 [9:8] |

| SGLINE1    | 12b | 0~4095のライン番号     | VSGがアクティブになっているフィールド内のラインを選択                                                   |

| SGLINE2    | 12b | 0~4095のライン番号     | VSG信号を繰り返すためにフィールド内の2番目のラインを選択                                                 |

フィールド設定：

1. シーケンス・チェンジ・ポジション (SCP1~6) では、フィールド内の7つのリージョンをそれぞれ定義。

2. VSEQSEL0~6で、リージョンごとに希望するVシーケンス (0~9) を選択。

3. SGLINE1レジスタで、センサー・ゲート・パルスが入るフィールド内のHDラインを選択。

図18. フィールド全体のリージョンへの分割

# AD9995

## VシーケンスとHBLKに対する ライン・オルタネーションの生成

低解像度の読み出しにおいて、CCDによってはラインごとの垂直転送クロックの数が異なります。AD9995はこのような駆動に対応するために、VPATREPO (V Pattern Repetition Odd: 奇数ラインのVパターン繰り返し) レジスタとVPATREPE (V Pattern Repetition Even: 偶数ラインのVパターン繰り返し) レジスタを持っています。これにより、Vパターンの繰り返し回数を奇数ラインと偶数ラインとで異なる値に設定することができます。注意する点としては、繰り返し回数を偶数ラインと奇数ラインで異なる値にすることはできますが、Vパターン・グループとしては同じものを使用しなければならないことです。

さらにHBLK (Horizontal Blanking) もまた偶数ラインと奇数ラインで違う信号にすることができます。HBLKALT (HBLK Alternation) レジスタをハイに設定すると、HBLKのTOG1 (Toggle Position 1) とTOG2 (Toggle Position 2) の値は奇数ラインで使用され、TOG3~6 (Toggle Position 3, 4, 5, 6) は偶数ラインで使用されます。この設定により、HBLKによるブランкиング期間を奇数ラインと偶数ラインで違う幅に調整することができます。

図19に、VPATの繰り返し回数設定のオルタネーションとHBLKのオルタネーションと一緒に使用した場合の例を示しま

- 注

1. Vパターン・グループの繰り返し回数は、奇数ラインと偶数ラインで異なる値に設定することができます。

2. 奇数／偶数ラインに対して異なるHBLKパターンを生成するために、HBLKトグル位置を奇数ラインと偶数ラインの間で異なる値に設定することができます。

図19. VPAT繰り返しとHBLKトグル位置の奇数／偶数ライン・オルタネーション

図20. センサー・ゲート・ライン区間での2番目のVPATグループの例

す。VPATとHBLKのオルタネーション・モードは別々に使用することも可能です。

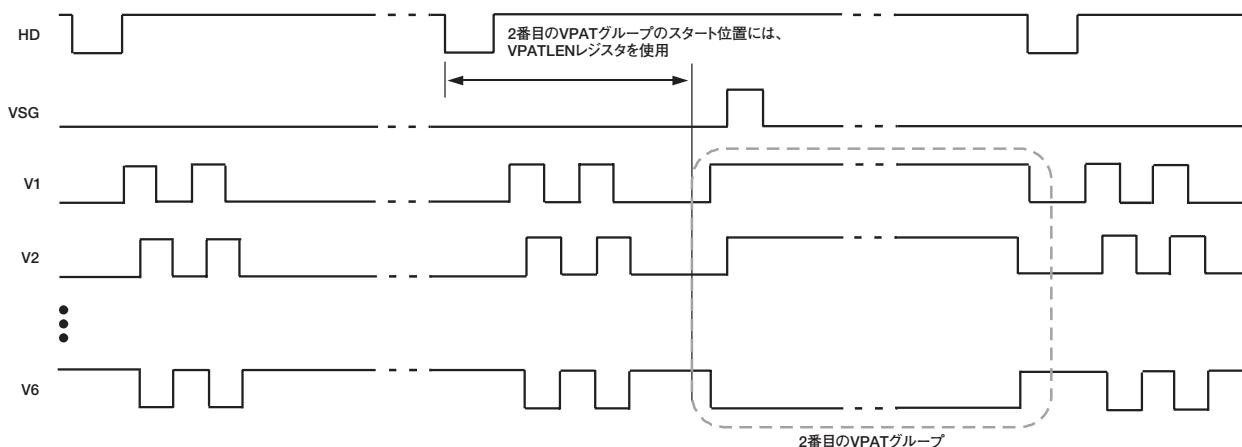

## VSGアクティブ・ライン区間での2番目のVパターン・グループ

ほとんどのCCDセンサーはセンサー・ゲートのライン内では、異なる垂直転送のタイミングを必要とします。AD9995はセンサー・ゲート・パルスであるVSG1~VSG5がアクティブな期間に、2番目のVパターン・グループをV1~V6に出力させることができます。図20は、通常のVSGのラインにV1~V6までのVパターン・グループが2つ発生している様子を示しています。VSGラインの最初のVパターン・グループは他のリージョンと同じ方法で適宜VSEQSEL (V Sequence Select) レジスタで選択します。2番目のVパターン・グループはVSGラインだけで有効になりますが、これはフィールド・レジスタの中にあるVPATSECOND (V Pattern Second) レジスタで選択します。2番目のVPATグループのスタート位置に対しては、選択されたVPATレジスタの中のVPATLENレジスタを使用します。なぜならば、VPATLENレジスタはスタート位置として使用され、VPATの長さ設定としては使用できないからです。したがって2番目のVPATグループには繰り返し回数を設定することはできません。

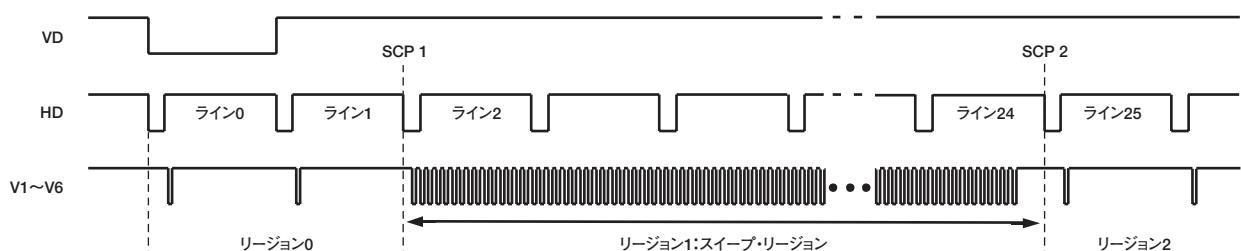

## スイープ・モード動作

AD9995にはスイープ・モード (Sweep Mode) と呼ばれる垂直転送のタイミングに関するモードがあります。このモードは、多数のHDラインにまたがってたくさんのパルスを繰り返し発生させる場合などに使用します。一つの例としてはCCD読み出し動作の開始時に使用します。それは露光期間の終わりであり、センサー・ゲート・パルスにより画像が読み出される動作の前までになります。この駆動を行うとインターラインCCDの垂直転送レジスタにある電荷は空になります。これは、V1～V6出力から多量のパルス列をCCDに与えることにより、高速で電荷を転送させているからです。CCDセンサーの垂直分解能によりますが、2,000クロックから3,000クロックが、CCDの垂直転送レジスタ内の全ての電荷を転送するのに必要となります。この駆動は多数のHDラインにまたがって連続して発生しています。AD9995の垂直転送のタイミングは1HD内に収まっているのが普通ですが、スイープ・モードを有効にするとそのリージョンが終了するまでに発生しているHD境界は無視されます。どのリージョンでもスイープ・モードを有効にすることができる、必要に応じてSWEEPレジスタをハイにすることでスイープ・モードを有効にします。

図21にスイープ・モードの例を示します。CCDの垂直分解能に応じて垂直転送のパルス数が必要です。V1～V6の出力はVパターン・レジスタ（表VII参照）を使用して作成します。一つのパルスを極性（Polarity）レジスタとトグル位置（Toggle Position）レジスタを使用して作成します。CCDに必要とされる垂直転送のパルスの繰り返し回数を設定します。繰り返し回数はVシーケンス・レジスタの中のVPATREPを使用して設定します。これにより必要な期間だけパルスが繰り返されることになります。通常、垂直転送のパルス列はHDラインの終わりまで有効ですが、スイープ・モードをこのリージョンで有効にするとHD境界は無視されます。図21はスイープ・リージョンを23HDに設定した場合を示しています。スイープ・モード・リージョンが終了し、次のリージョンになると通常の動作に戻

ります。スイープ・モードを使用するときには、リージョンの境界がどこになるのかをシーケンス・チェンジ・ポジションを使用して確認しておき、必要なライン数を設定しなければなりません。これは、スイープの動作が次のVシーケンスにオーバラップしないようにするためです。

## マルチプライヤ・モード

とても広い垂直転送のタイミングのパルスを生成するためには、そのリージョンをマルチプライヤ・リージョン（Multiplier Region）に指定しなければなりません。このモードではVパターン・レジスタをこれまでとは少し違う使い方をします。マルチプライヤ・モード（Multiplier Mode）は通常のCCDの駆動とは異なる動作をさせるために使用します。それは、垂直転送のパルスが1HDラインより長いパルスになる場合です。

スタート極性とトグル位置は通常のVPATの設定と同じ使い方を踏襲しますが、VPATLENは違う使い方をします。VPATグループのトグル位置（VTOG1, 2, 3）の設定のためのピクセル・カウンタ（HDカウンタ）を使用する代わりに、VPATLENはVTOGの位置を「乗算」することにより、非常に長いパルスを生成することができます。実際のトグル位置の値を算出するには、スタート位置の後ろのピクセル数でカウントし、次の式を使用します。

$$\text{マルチプライヤ・モードのトグル位置} = \text{VTOG} \times \text{VPATLEN}$$

VTOGレジスタの値はVPATLENの値で乗算されるので、トグル位置を置くことのできる設定分解能は減少します。たとえば、VPATLEN=4とした場合、トグル位置はピクセル・ステップで設定できるのではなく、4ピクセルごとに設定されます。表VIIIは、マルチプライヤ・モードの動作時、どのようにしてVPATグループ・レジスタが使われるかを表しています。マルチプライヤ・モードでは、VPATREPOとVPATREPEは同じ値に設定し、大きい値に合わせて設定します。

図21. 高速垂直シフトに対するスイープ・リージョンの例

表VIII. マルチプライヤ・モード・レジスタのパラメータ

| レジスタ    | 長さ  | 範囲            | 説明                                 |

|---------|-----|---------------|------------------------------------|

| MULTI   | 1b  | ハイレベル/ローレベル   | ハイレベルではマルチプライヤ・モードをイネーブル           |

| VPOL    | 1b  | ハイレベル/ローレベル   | 各VPATグループ内のV1～V6信号のスタート極性          |

| VTOG1   | 12b | 0～4095のピクセル位置 | 各VPATグループ内のV1～V6信号の最初のトグル位置        |

| VTOG2   | 12b | 0～4095のピクセル位置 | 各VPATグループ内のV1～V6信号の2番目のトグル位置       |

| VTOG3   | 12b | 0～4095のピクセル位置 | 各VPATグループ内のV1～V6信号の3番目のトグル位置       |

| VPATLEN | 10b | 0～1023のピクセル   | トグル位置カウンタの倍率として使用                  |

| VPATREP | 12b | 0～4096        | VPATREPE/VPATREPOにはTOG2または3と同じ値を設定 |

# AD9995

図22に動作の例を示しています。まず、最初のトグル位置を2に、次のトグル位置を9に設定しています。マルチプライヤ・モードを設定していない場合、Vシーケンスのトグル位置は1HD内になり、そのままピクセル番号で、2と9の位置になります。マルチプライヤ・モードに設定している場合、それらはVTPLEN=4の値で乗算されるので、最初のトグル位置はピクセル番号でいうと8、次にくるトグル位置は36となります。スイープ・モードを有効にすると、HDを越えてトグル位置を設定することができます。

## 垂直センサー・ゲート（シフト・ゲート）のパターン

インターラインCCDでは、垂直センサー・ゲート（VSG）は、受光領域から遮光領域へ電荷を転送するのに使用されます。遮光されている垂直転送レジスタから画像はV1～V6の垂直転送パルスと高速水平転送クロックを適宜使用し、ラインごとに読み出しが行われます。

表IXはVSGパターン（VSG Pattern）レジスタのまとめです。AD9995には5つのVSG出力（VSG1～VSG5）があります。そ

れぞれの出力はSGPATSEL（Sensor Gate Pattern Select）レジスタを使用して、4つのセンサー・ゲート信号のパターンから1つをそれぞれに対し割り当てます。それぞれのパターンはVパターン・グループと同じような方法で設定することができ、スタート極性（SGPOL）、1番目のトグル位置（SGTOG1）と2番目のトグル位置（SGTOG2）を使用します。VSG1～VSG5のパルスが発生する水平ラインは、SGLINE1（Sensor gate line 1）レジスタやSGLINE2（Sensor gate line 2）レジスタを使用します。さらにSGMASKレジスタを使用することにより、VSG1～VSG5の出力は個別に無効の設定することができます。個別に設定できることもあり、全てのSGパターンをあらかじめ設定しておくことが可能です。違うフィールドであっても、適宜必要なパルスを出力させることもできます。柔軟性を持たせるため、SGPATSEL、SGMASK、SGLINEレジスタはそれぞれのフィールドで別々に設定できるようになっています。詳細は「フィールド」の項を参照してください。

- マルチプライヤ・モードVパターン・グループのプロパティ:

1. スタート極性 (上:STARTPOL=0)

2. 1番目、2番目、3番目のトグル位置 (上:VTOG1=2, VTOG2=9)

3. VPATカウントの長さ (上:VPATLEN=4)。これはトグル位置変化のための最小分解能。

4. トグル位置は (VTOG×VPATLEN) の位置で発生。

5. スイープ・リージョンがイネーブルの場合、上に示すように、VパルスがHD境界を越えることもあります。

図22. 長い垂直パルス・タイミングに対するマルチプライヤ・リージョンの例

表IX. VSGパターン・レジスタ（表VIIのフィールド・レジスタも参照）

| レジスタ   | 長さ  | 範囲            | 説明                           |

|--------|-----|---------------|------------------------------|

| SGPOL  | 1b  | ハイレベル／ローレベル   | SGパターン0～3に対するセンサー・ゲートのスタート極性 |

| SGTOG1 | 12b | 0～4095のピクセル位置 | SGパターン0～3に対する最初のトグル位置        |

| SGTOG2 | 12b | 0～4095のピクセル位置 | SGパターン0～3に対する2番目のトグル位置       |

- 各パターンに対する設定項目:

1. パルスのスタート極性

2. 最初のトグル位置

3. 2番目のトグル位置

4. フィールド内のVSGパルスに対するアクティブ・ライン (パターンごとではなく、フィールド・レジスタでプログラマブル)

図23. 垂直センサー・ゲート・パルスの配置

## モード・レジスタ

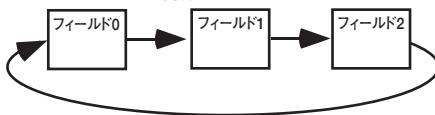

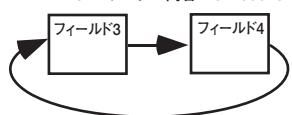

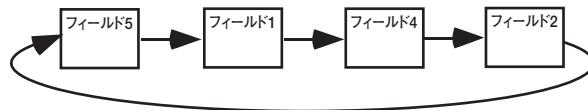

モード (Mode) レジスタは、AD9995のフィールドを選択するための1つのレジスタです。全てのフィールド、Vシーケンス、Vパターン・グループなどの情報は、通常、電源起動後に書き込んでおきます。動作中は、モード・レジスタにより、現在のシステム条件に合わせてどのようなフィールド・タイミングの組み合わせでも選択できるようになっています。前もって書き込んでおくこととモード・レジスタを組み合わせることのメリットとしては、カメラ動作中の書き込み動作を大幅に減らすことができます。カメラ動作中にモード切り替えを行うときは、全ての垂直転送のタイミングを書き込みにいくのではなく、ほんの少しのレジスタに書き込みを行うことで対応できます。

デジタル・スチル・カメラの基本的なアプリケーションでは5つの異なる垂直転送のタイミングを持つフィールドが必要です。ドラフト・モード、オートフォーカス・モード、そして、スチル画像の読み出しモード（3フィールド）です。5つのフィールドの全てのレジスタの情報は、電源起動後に書き込んでおくことができます。そして、カメラ動作中にはモード・レ

ジスタを選択することによりどのフィールドを実際の動作とさせるか、どのようにカメラの動作を行うかなどを設定します。

表Xはモード (Mode) レジスタのビットをどのように使うかを示したものです。MSBの3つのビットであるD23～D21は全部で何フィールドをモード・レジスタで制御するかに使います。これら3ビットで1から7のどの値でも選択することができます。残りのビットも3ビットずつに分かれ、どのような順番で6つのフィールドを切り替えていくかを選択します。1回のモード・レジスタへの書き込みで、最大7フィールドの切り替えができます。AD9995はまず最初のフィールド・ビットから開始し、続いて2番目のフィールド・ビット、次に……というように、VDごとにフィールドが切り替わっていきます。

D23～D21のビットに必要なフィールド数全てを設定した後、AD9995は1番目フィールドから始まりそれを繰り返していきます。モード・レジスタに新たに書き込みを行うまでこの動作を繰り返します。図24に、異なるフィールドの組み合わせを行うためのモード・レジスタの使用例を示します。

表X. モード・レジスタのデータ・ビット分析 (D23=MSB)

| D23           | 22 | 21 | 20        | 19        | 18        | 17        | 16        | 15        | 14        | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | D0 |

|---------------|----|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|----|----|----|----|---|---|---|---|---|---|---|---|---|----|

| 使用するフィールドの合計数 |    |    | 7番目のフィールド | 6番目のフィールド | 5番目のフィールド | 4番目のフィールド | 3番目のフィールド | 2番目のフィールド | 1番目のフィールド |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

| 1=1番目のフィールドのみ |    |    | 0=フィールド0  |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

| 7=7つの全フィールド   |    |    | 5=フィールド5  |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

| 0=無効          |    |    | 6、7=無効    |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

例1:

合計フィールド=3、1番目のフィールド=フィールド0、2番目のフィールド=フィールド1、

3番目のフィールド=フィールド2

モード・レジスタの内容=0x600088

例2:

合計フィールド=2、1番目のフィールド=フィールド3、2番目のフィールド=フィールド4

モード・レジスタの内容=0x400023

例3:

合計フィールド=4、1番目のフィールド=フィールド5、2番目のフィールド=フィールド1、

3番目のフィールド=フィールド4、4番目のフィールド=フィールド2

モード・レジスタの内容=0x80050D

図24. モード・レジスタによるフィールド・タイミングの選択

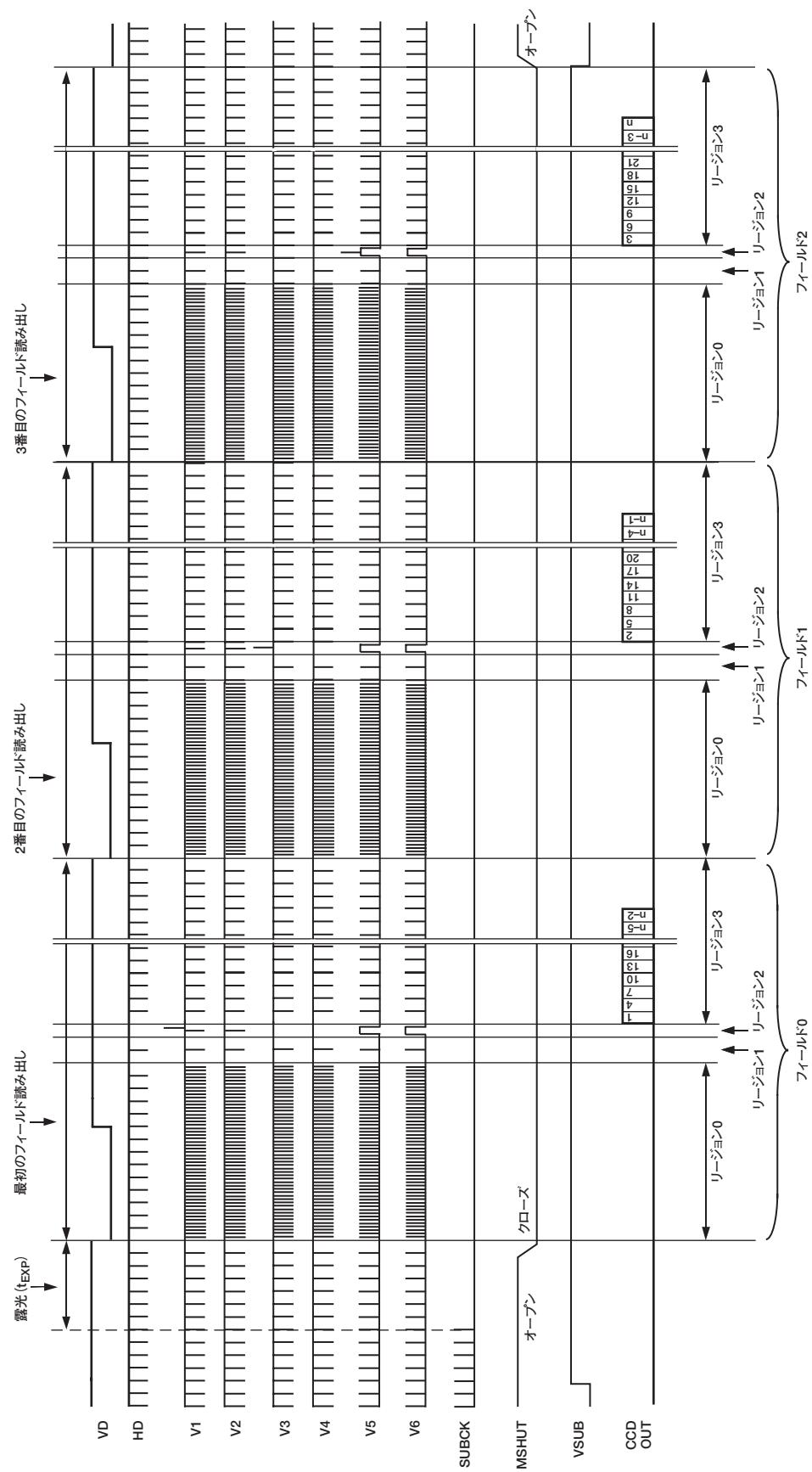

## 垂直タイミングの例

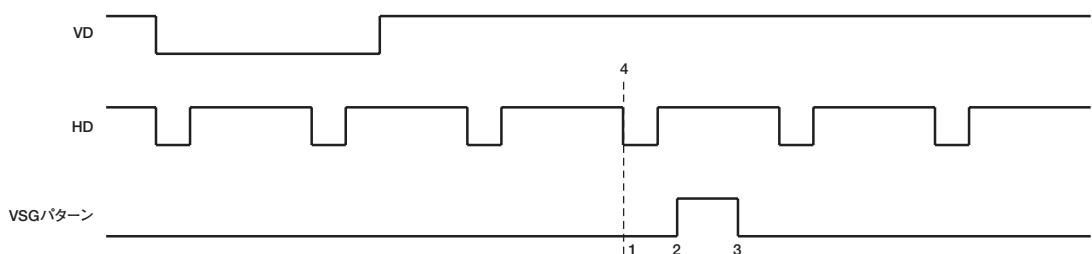

AD9995の垂直転送タイミングの作成をどのように行うかを理解するために、図25のようなCCDタイミング・チャートを例に考えます。この例は一般的な3フィールド読み出しのCCDのタイミング・チャートを表しています。前述のフィールドの項で解説したように、それぞれの読み出しのフィールドは読み出しのそれぞれのステップを行うためにリージョンとして分割されています。シーケンス・チェンジ・ポジション（SCP）はそれぞれのリージョンのライン境界を決定し、そしてVSEQSELレジスタはそれぞれのリージョンにそれに適したVシーケンスを割り当てています。Vシーケンスにはそれぞれのリージョンに必要なタイミング情報が含まれており、それらはV1～V6パルス（VPATグループを使用して作成）、HBLK/CLPOBタイミング、そしてSGのアクティブなラインで発生するVSGパターンです。

このタイミングの例では、それぞれの3つの読み出しフィールドを4つのリージョンに分割することができます。リージョン0、リージョン1、リージョン2、リージョン3です。AD9995は最大6つまでの個別のフィールドを設定しておくことができるので、フィールド0、フィールド1、フィールド2のフィールド・レジスタの3つでこの例にあるCCDのタイミングのように駆動させることができます。この例では各読み出しフィールドの4つあるリージョン同士は非常に酷似していますが、フィールド・レジスタは他のいろいろなタイミング・チャートにも柔軟に対応できます。

リージョン0は高速垂直転送リージョンで、スイープ・モードをこのタイミングとして使用することができ、CCDの垂直転送

レジスタにある電荷を空にするために、必要な高速垂直転送のパルス数を設定します。

リージョン1は2ライン分だけですが、通常の垂直転送のタイミングに使用します。このリージョン内のタイミングはリージョン3のタイミングと同じです。

リージョン2はセンサー・ゲート・ラインで、VSGパルスが画像を垂直転送レジスタに転送する箇所です。このリージョンはSGアクティブライン用に2番目のVパターンを使用します。

リージョン3は、通常の垂直転送のタイミングで1ラインを転送し、リージョン1と同じタイミングになります。

つまり、3つのフィールドにはそれぞれ4つのリージョンが必要になっています。リージョン1とリージョン3は本質的に同じであることから、レジスタ設定の煩雑さが減少します。

実際の読み出し動作では他のレジスタも必要となります。モード・レジスタ、シャッター制御レジスタ（TRIGGER、SUBCK、VSUB、MSHUT、STROBE）と、AFEのゲイン・レジスタなどです。これらのレジスタについては、他の例で説明します。

### 信号極性についての重要な注意事項

AD9995で、V1～V6、VSG1～VSG5、SUBCKなどを生成するとき、Vドライバはこれらの信号を反転させることに注意しなければなりません。Vドライバの入力と出力のタイミングをチェックし、適宜、AD9995の出力極性を調整してください。

# AD9995

## シャッター・タイミングの制御

CCD画像の露光時間はCCDの基板クロック（SUBCK）信号で制御することができ、このパルスは蓄積された電荷を消失させるためにCCDの基板を叩きます。AD9995はノーマル・シャッター、高精度シャッター、低速シャッターの3つの電子シャッター・モードをサポートしています。SUBCKパルスを使うことによって、AD9995は数フィールド読み出しの間にSUBCKを停止するように、さまざまな読み出しに適応させることができます。AD9995はまた外部のメカシャッター（MSHUT）やストロボ／フラッシュ（STROBE）やCCDのバイアス・レベル選択信号（VSUB）の出力を制御することができます。

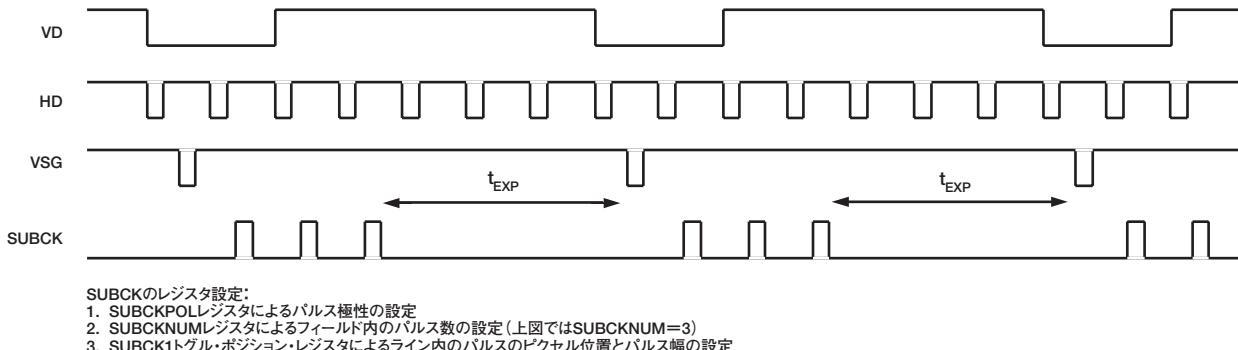

### ノーマル・シャッター動作

デフォルトでは、AD9995はVDフィールドごとにSUBCKを出力させているようなノーマル・シャッター・モードになっています（図26参照）。SUBCKパルスは1ラインに1回発生し、露光時間の長さは、1フィールド内でパルスが何ライン発生しているかで決まります。SUBCKパルスの極性とトグル位置はSUBCKPOL（Substrate Clock Polarity）レジスタとSUBCK1TOG（Substrate 1 Toggle）レジスタを使用して1ライン内で設定します（表XI参照）。1フィールド内のSUBCKの数はSUBCKNUM（Substrate Clock Number）レジスタ（アドレス0x63）で設定できます。

図26に示すように、通常、SUBCKパルスはSGACTLINEレジスタでそれぞれのフィールドに対して設定されたSGラインの次のラインから発生し始めます。SUBCKPOL、SUBCK1TOG、SUBCK2TOG、SUBCKNUM、SUBCKSUPPRESS（Substrate Suppress）レジスタ値は、センサー・ゲート・ラインの後の最初のラインで更新されます。「新しいレジスタ値の更新」の項を参照してください。

図26. ノーマル・シャッター・モード

図27. 高精度シャッター・モード

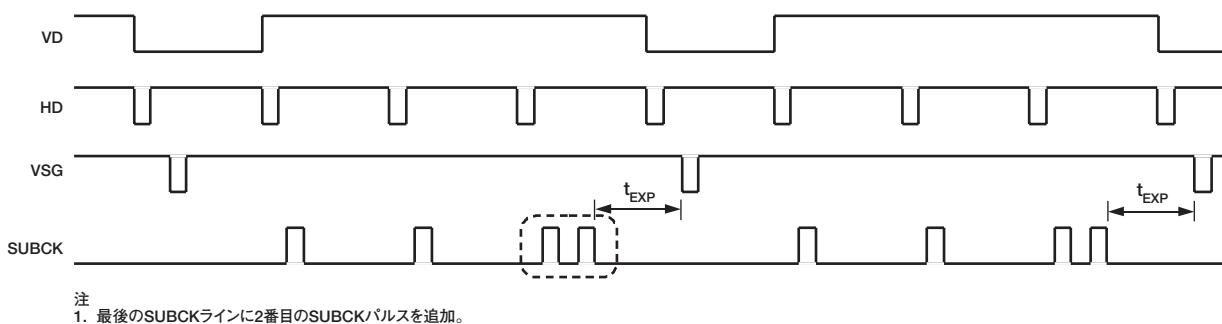

### 高精度シャッター動作

高精度シャッターは、ノーマル・シャッターと同じように使用することができますが、最後のSUBCKパルスの設定を制御するためのレジスタがあります。このモードでは、SUBCKパルスは1ラインあたりに1回発生しますが、図27に示すように、SUBCK2TOGレジスタで設定される位置に追加のSUBCKが発生します。このモードを使用することにより、高精度な露光時間を制御することができます。SUBCK2TOGレジスタを最大値（0xFFFFFFF）にすることで、最後のSUBCKを発生させないモードにすることができます（デフォルト）。

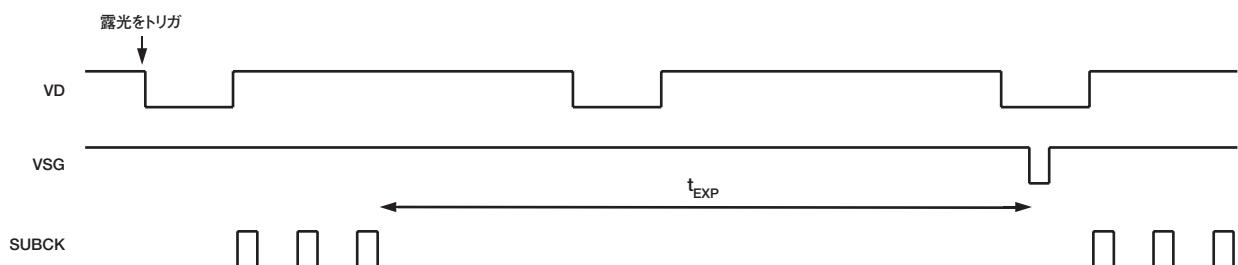

### 低速シャッター動作

ノーマル・シャッター・モードと高精度シャッター・モードは露光時間が1フィールドより短い場合に使用します。1フィールドより長い露光時間にしたい場合は、低速シャッター・モードを使用することができます。AD9995は長い露光時間を設定するために異なるカウンタを使用しています。低速シャッター・モードのフィールド数はEXPOSUREレジスタ（アドレス0x62）で設定できます。図28に示すように、このシャッター・モードは、最大4095フィールドまでSUBCKとVSGの出力を停止させることができます。VDとHDの出力はVDHDOFFレジスタを1に設定することにより、この露光時間中に停止させることができます。

低速シャッター動作を発生させるには、TRIGGERレジスタのD3ビットに書き込むことにより、長時間露光を開始させなければなりません。このビットにハイを書き込むと、AD9995は次のVDエッジから露光動作を開始します。EXPOSUREレジスタを0より大きな値に設定すると、AD9995は後に続くフィールドのSUBCK出力を停止します。

TRIGGERレジスタを使用して露光を発生させ、EXPOSUREレジスタに0を書き込むと、SUBCKの振る舞いはノーマル・シャッター・モードや高精度シャッター・モードと同じ結果になります。このときはTRIGGERレジスタは使用しません。

### SUBCKの停止

通常、SUBCKはセンサー・ゲート・ライン（VSG）の後のラインから開始します。いくつかのCCDセンサーにおいて、SUBCKパルスはVSGの次のライン、もしくはそれに続く複数のラインで出力しないことが必要になります。SUBCKSUPPRESSレジスタは、VSGラインの後に何ライン分SUBCKを出力しないかを設定できるレジスタです。

### 露光後の読み出し

露光後、センサー・ゲート（VSG）動作が始まるにより、CCDのデータの読み出しが発生します。デフォルトでは、AD9995はVSGパルスを毎フィールド発生させます。この場合、CCDのプレビュー・モードのように1回の露光と1回の読み出しだけが必要とされ、VSGとSUBCKパルスは毎フィールド発生します。

しかしながら、多くの場合、読み出しが完全に終了するまでの読み出しの期間、SUBCKの停止が必要です。READOUTレジスタは、露光の後に何フィールド分SUBCKを停止しておくかを設定するレジスタです。READOUTは0から7までのフィールド数を設定することができます。通常、電源起動時に設定し、

露光の書き込み時には設定しないようにします。一般的なインターレースCCDの読み出しモードは、2フィールド分のSUBCKの停止期間が必要です（READOUT=2）。3フィールド、6相CCDは3フィールド分のSUBCKの停止期間が読み出し開始の後に必要です（READOUT=3）。

SUBCK出力が、最後の読み出しフィールドから必要な場合、単純にREADOUTレジスタに実際の読み出しフィールド数から1を減算した値を設定します。

露光の動作と同様に、TRIGGERレジスタを使用することにより、読み出し動作は開始します。

### TRIGGERレジスタの使い方

前述のとおり、AD9995はデフォルトでSUBCKとVSGを毎フィールド発生させています。この動作はCCDのプレビューのように、連続露光と読み出し動作には有効です。しかしながら、CCDが長時間の露光を必要とする場合や複数フィールドの読み出しが必要な場合、TRIGGERレジスタが指定された露光と読み出しのシーケンスを開始するのに必要となります。

通常、露光と読み出しのビットはTRIGGERレジスタの中で一緒に使用されます。これは露光と読み出し動作を前もって決めてから開始させるためです。一度、露光を完了したら、読み出しは自動的に開始します。EXPOSUREとREADOUTレジスタの値はそれぞれの期間で決められます。

注

1. EXPOSUREレジスタにゼロより大きい値を設定して、SUBCKを複数フィールド分停止させることができます。

2. 上の例ではEXPOSURE=1を使用。

3. 低速露光を開始するには、TRIGGERレジスタも使用する必要があります。

4. VDHDOFFレジスタ=1によって、VD/HD出力も停止できます。

図28. EXPOSUREレジスタによる低速シャッター・モード

表XI. シャッター・モード・レジスタのパラメータ

| レジスタ           | 長さ  | 範囲             | 説明                                                                      |

|----------------|-----|----------------|-------------------------------------------------------------------------|

| TRIGGER        | 5b  | 5つの信号に対するオン/オフ | VSUB [0], MSHUT [1], STROBE [2], Exposure [3], Readout Start [4]に対するトリガ |

| READOUT        | 3b  | 0~7のフィールド数     | 露光後にSUBCKを停止させるフィールド数                                                   |

| EXPOSURE       | 12b | 0~4095のフィールド数  | 露光時にSUBCKとVSGを停止させるフィールド数（低速シャッター）                                      |

| VDHDOFF        | 1b  | オン/オフ          | 露光時にVD/HD出力をディスエーブル（1=オン、0=オフ）                                          |

| SUBCKPOL*      | 1b  | ハイレベル/ローレベル    | SUBCK1とSUBCK2に対するSUBCKのスタート極性                                           |

| SUBCK1TOG*     | 24b | 0~4095のピクセル位置  | 最初のSUBCKパルスに対するトグル位置（ノーマル・シャッター）                                        |

| SUBCK2TOG*     | 24b | 0~4095のピクセル位置  | 最後のラインでの2番目のSUBCKパルスに対するトグル位置（高精度）                                      |

| SUBCKNUM*      | 12b | 1~4095のパルス数    | フィールド当たりの合計SUBCK数（ラインごとに1パルス）                                           |

| SUBCKSUPPRESS* | 12b | 0~4095のパルス数    | VSGライン後にさらにSUBCKを停止させるためのライン数                                           |

\*レジスタはVD更新されず、センサー・ゲート・ラインの後のラインの開始で更新されます。

# AD9995

露光動作のトリガなしで、読み出し動作のトリガを行うこともできます。この場合、次のVDで読み出しが発生し、SUBCKはREADOUTレジスタの値に従って、停止します。

TRIGGERレジスタは同様にSTROBE、MSHUT、VSUBなどを作動するためにも使用されます。それぞれの信号は別々に制御することができますが、露光と読み出し動作のトリガに依存します。

図23に露光と読み出し動作のトリガの例を示しています。

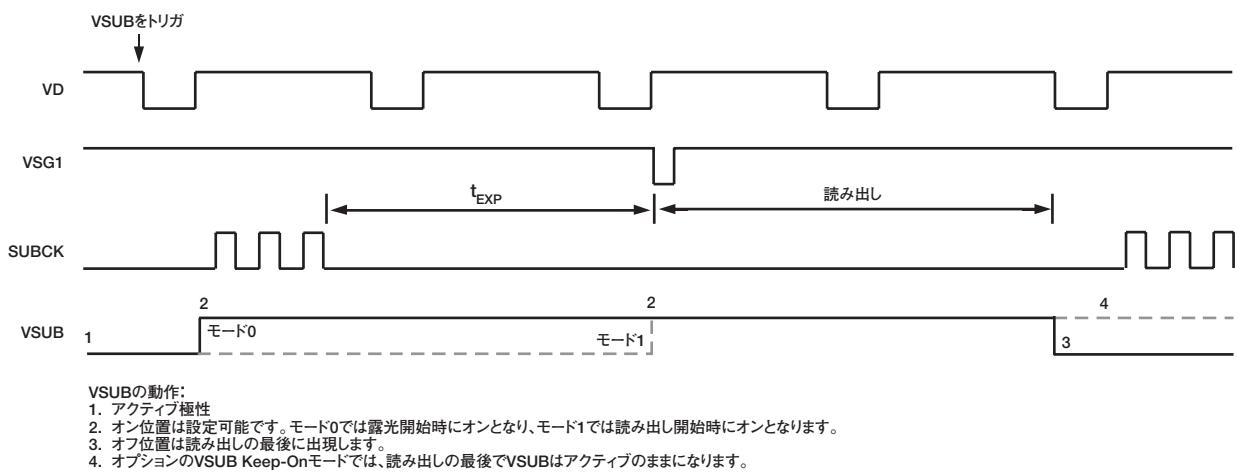

## VSUBの制御

CCDの読み出し時のバイアス（VSUB）はいろいろなCCDに適した設定が可能です。図29に示す2つのモードが利用できます。モード0（Mode 0）では、VSUBは露光が始まる最後のSUBCKのフィールドでアクティブになります。オン位置（図29の立ち上がりエッジ）はこのフィールド内のどのラインでも設定可能です。VSUBは読み出しの終わりまで、ハイのままでです。モード1（Mode 1）では、VSUBは読み出しが開始するところまではハイにはなりません。

VSUB Keep Onと呼ばれる機能も使用できます。このビットをハイにすると、VSUBは読み出しが終わった後も引き続きハイを保持します。VSUBをローにしたい場合、このビットをローに書き込んでください。

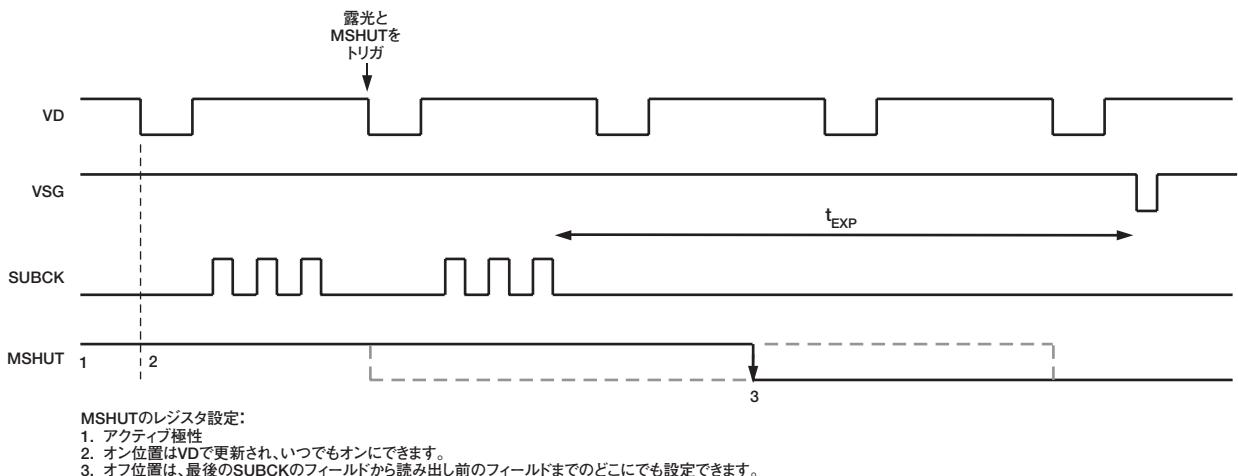

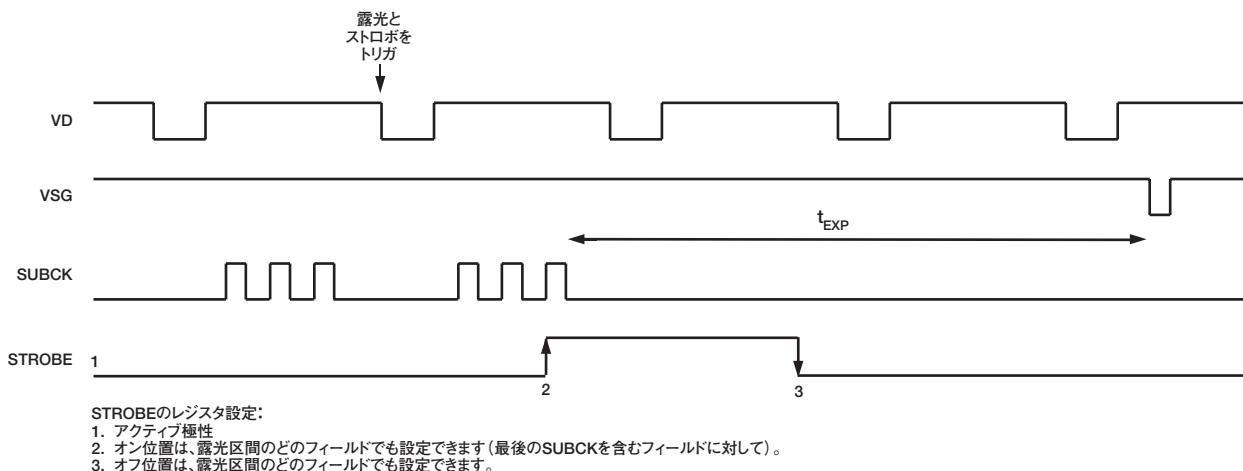

## MSHUTとSTROBEの制御

MSHUTとSTROBE動作を図30、31、32に示します。表XIIは、MSHUTとSTROBE出力を設定するためのパラメータを表します。MSHUT出力はMSHUTONレジスタで切り替えられ、MSHUTOFFレジスタで設定された値までそのレベルを保持します。MSHUTOFFはFD（フィールド）、LN（ライン）、PX（ピクセル）レジスタにより、露光時間内であればどの位置でも指定できるレジスタです。STROBEパルスはONとOFFの位置で定義されます。STROBON\_FDはSTROBEがオンになるフィールドを指定し、露光が始まる前の最後のSUBCKを含むフィールドを指定します。STROBON\_LNPXレジスタは、STROBON\_FDで指定されたフィールドの中のラインとピクセルの位置を指定します。STROBEのオフ位置は、最後のSUBCKを含むフィールド内に対してどのフィールド、どのライン、どのピクセルの位置でも指定することができます。

図29. VSUBのプログラマビリティ

図30. MSHUT出力のプログラマビリティ

### TRIGGERレジスタの制限

TRIGGERレジスタは露光と読み出しを規定できますが、使用には制限があります。

一度、露光+読み出しの動作が開始したら、次の露光/読み出しのトリガはできません。少なくとも、1フィールド(VD)の期間が次に露光+読み出しが始まるまで必要です。

MSHUTのトリガ動作にも同じような制限があります。MSHUTOFFの動作が終了してから少なくとも1フィールド分確保しないと、次のMSHUTOFFの設定はできません。

VSUBのトリガ動作は露光+読み出し動作の間に2フィールド分を必要としますが、これはVSUBのオン/オフを正常に機能させるためです。もし、VSUBがそれぞれ連続する露光と読み出しでこの動作を必要としない場合、この制限は無視できます。VSUB Keep-On モードは、連続して露光と読み出しを続けるときなどに有効です。

図31. STROBE出力のプログラマビリティ

表XII. VSUBレジスタ、MSHUTレジスタ、STROBEレジスタのパラメータ

| レジスタ          | 長さ  | 範囲                | 説明                                               |

|---------------|-----|-------------------|--------------------------------------------------|

| VSUBMODE[0]   | 1b  | ハイレベル/ローレベル       | VSUBモード (0=モード0, 1=モード1) (図29を参照)                |

| VSUBMODE[1]   | 1b  | ハイレベル/ローレベル       | VSUB Keep-Onモード。ハイレベルに設定すると、VSUBは読み出し後にアクティブを維持。 |

| VSUBON[11:0]  | 12b | 0~4095のライン位置      | VSUBのオン位置。フィールドの任意のラインでアクティブを開始。                 |

| VSUBON[12]    | 1b  | ハイレベル/ローレベル       | VSUBのアクティブ極性                                     |

| MSHUTPOL[0]   | 1b  | ハイレベル/ローレベル       | MSHUTのアクティブ極性                                    |

| MSHUTPOL[1]   | 1b  | オン/オフ             | MSHUTの手動イネーブル (1=アクティブ、つまりオープン)                  |

| MSHUTON       | 24b | 0~4095のライン/ピクセル位置 | MSHUTのオン位置ライン[11:0]とピクセル[23:12]位置                |

| MSHUTOFF_FD   | 12b | 0~4095のフィールド位置    | MSHUTをオフにするフィールド位置 (非アクティブ、つまりクローズ)              |

| MSHUTOFF_LNPX | 24b | 0~4095のライン/ピクセル位置 | MSHUTをオフにするライン/ピクセル位置 (非アクティブ、つまりクローズ)           |

| STROBEPOL     | 1b  | ハイレベル/ローレベル       | STROBEのアクティブ極性                                   |

| STROBON_FD    | 12b | 0~4095のフィールド位置    | 最後のSUBCKフィールドに対するSTROBEのオン・フィールド位置               |

| STROBON_LNPX  | 24b | 0~4095のライン/ピクセル位置 | STROBEのオン・ライン/ピクセル位置                             |

| STROBOFF_FD   | 12b | 0~4095のフィールド位置    | 最後のSUBCKフィールドに対するSTROBEのオフ・フィールド位置               |

| STROBOFF_LNPX | 24b | 0~4095のライン/ピクセル位置 | STROBEのオフ・ライン/ピクセル位置                             |

# AD9995

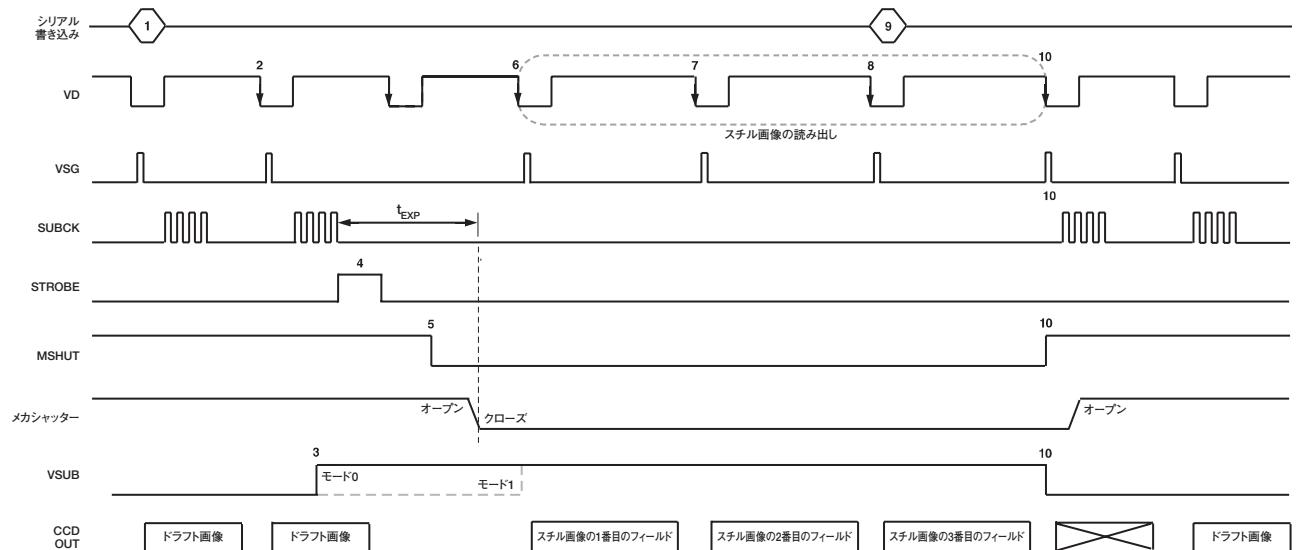

### 露光と読み出しの例

図32. シャッター信号とモード・レジスタによる露光とスチル画像読み出しの例

1. READOUTレジスタ（アドレス0x61）に、CCDデータの読み出し期間として何フィールド分SUBCKを停止しておくかを書き込みます。この例では、READOUT=3。

**EXPOSURE**レジスタ（アドレス0x62）には露光期間中に何フィールド分、SUBCKとVSG出力を停止しておくかを書き込みます。この例ではEXPOSURE=1です。

TRIGGERレジスタ（アドレス0x60）でSTROBE、MSHUT、VSUBの信号を有効にし、露光と読み出しを開始します。全ての動作（図32のように）をさせるためには、TRIGGERレジスタにデータとしてTRIGGER=31を書き込みます。読み出しへは露光期間が終了したあと自動的に開始します。

MODEレジスタ（アドレス0x1B）は次の5フィールドの動作を決めるために書き込みます。最初の2フィールドは露光期間で、それまでの動作であるドラフト・モードのフィールドと同じです。その後、スチル画像取り込みのための読み出しフィールドになります。このドラフト・モードのためのレジスタと3つの読み出しフィールドは前もって設定しておきます。

2. VD/HDの立ち下がりエッジで、項目1のレジスタの内容が更新されます。

3. VSUBモード=0（アドレス0x67）のときは、VSUB出力はVSUBONレジスタ（アドレス0x68）で指定されたラインでオンになります。

4. STROBE出力の切り替えは、STROBEONとSTROBEOFFレジスタ（アドレス0x6E～0x71）で指定します。

5. MSHUT出力のオフは、MSHUTOFFレジスタ（アドレス0x6Bと0x6C）で指定します。

6. 次のVDの立ち下がりエッジで自動的に1番目のフィールドの読み出しが開始します。

7. 次のVDの立ち下がりエッジで自動的に2番目のフィールドの読み出しが開始します。

8. 次のVDの立ち下がりエッジで自動的に3番目のフィールドの読み出しが開始します。

9. ドラフト・モードにするために、MODEレジスタに書き込みます。

メカシャッターをオープンするために、MSHUTON（アドレス0x6A）を書き込みます。

10. VD/HDの立ち下がりエッジで項目9のレジスタ内容が更新されます。

VSG出力がドラフト・モードのタイミングに戻ります。

SUBCK出力が駆動モードに戻ります。

MSHUT出力がオンの位置（アクティブ、つまり「メカシャッター・オープン」）に戻ります。

VSUB出力がオフの位置（非アクティブ）に戻ります。

図33. アナログ・フロントエンドの機能ブロック図

### アナログ・フロントエンドの説明と動作

AD9995の信号処理プロセスを図33に示します。それぞれのプロセスは、CCDのピクセル・データから高品質な画像にするために使用されています。

#### DCの再生

CCD信号出力の大きなDCオフセットを下げるためにDC再生回路を使用し、外部に0.1μFコンデンサを直列に接続します。この再生回路により、CCDのDCレベルをAD9995の電源電圧である3Vに合うように約1.5Vまで下げます。

#### 相関ダブル・サンプラー (CDS)

CDS回路は、画像情報を抽出し、低周波数成分のノイズを除去するために、CCDのピクセル・データを2回サンプリングします。図7は、内部で発生するCDSクロックであるSHPとSHDがサンプリングする様子を示しており、それぞれCCD信号のリファレンス・レベルとCCD信号のレベルをサンプリングします。SHPとSHDのサンプリングする位置は、アドレス0x63にあるSAMPCONTROLレジスタで設定します。これら2つのクロックの位置は、CCDから最大の性能を引き出すために重要です。

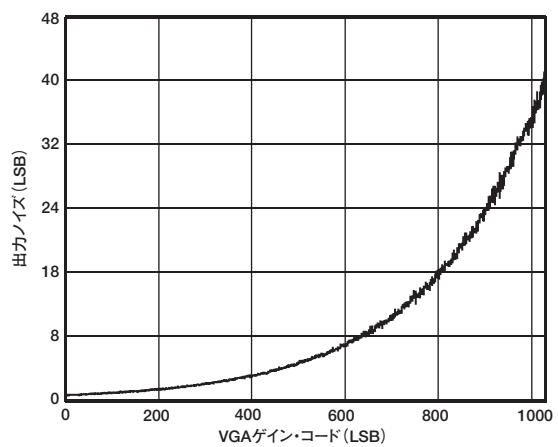

#### 可変ゲイン・アンプ (VGA)

VGAには6dBから42dBのゲイン・レンジがあり、シリアル・インターフェースを介して10ビットの分解能で設定できます。最小ゲインは6dBで、これは1Vの入力をADCの入力レンジである2Vに合わせるために必要なゲインです。CCDの出力が1Vのフルスケールのシステムを使用している場合、等価的なゲイン・レンジは0dBから36dBになります。

VGAのゲイン・カーブは「dBリニア」になります。実際のVGAゲインはゲイン・レジスタで設定し、次の等価式を使用します。

$$\text{ゲイン}(dB) = (0.0351 \times \text{コード}) + 6 \text{ dB}$$

コードの範囲は0~1023になります。

図34. VGAゲインのカーブ

#### A/Dコンバータ

AD9995は高性能A/Dコンバータ(ADC)を採用しており、高速性、消費電力も最適化しています。微分非直線性(DNL)の性能はTyp値で0.5LSBより良くなっています。ADCは2Vの入力レンジを持っています。AD9995の直線性とノイズ性能のグラフが特性2と特性3にあります。

# AD9995

## 光学黒クランプ

光学黒クランプ・ループ (Optical Black Clamp Loop) は、信号処理過程における残留オフセットを取り除くために使用され、CCDの黒レベルに重畳している低周波数変動に追従します。光学黒画素（遮光されている画素）は水平ラインごとにあり、ADCの出力で比較され所定の黒レベルにされます。これはクランプ・レベル (Clamp Level) レジスタで設定します。この値は0~255LSBの範囲内を256ステップで設定することができます。比較の結果として残っているエラー成分はノイズを減らすためにフィルタ処理され、正しい値にするためにADCの入力段にD/Aコンバータ (DAC) を介して加えられます。通常、光学黒クランプ・ループは水平ラインごとに1回オンになります。ただし、このループは特定のアプリケーションに合わせてゆるやかに更新できます。デジタル・クランプを後段のプロセッサで使用する場合、OPRMODE (Operation Mode) レジスタのビットD2を使用してAD9995の黒クランプ・ループを無効にすることができます。クランプ・ループを無効にしても、クランプ・レベル・レジスタをオフセット調整として使用することができます。

CLPOB (Clamp Optical Black) パルスはCCDの光学黒画素の位置に配置しなければなりません。クランプ・ノイズを最小にするために、CLPOBの幅は少なくとも20ピクセルは確保しておくことを推奨します。短いパルス幅でも使用できますが、クランプ・ノイズが増加したり、黒レベルの低周波数変動の追従性能が落ちたりする可能性があります。タイミングについては「水平クランプとブランкиング」「水平タイミング・シーケンスの例」の項を参照してください。

## デジタル・データ出力

AD9995のデジタル出力データは、DOPUTPHASE (Digital Output Phase) レジスタの値のタイミングでラッチされます (図33)。出力データ・タイミングは図8aにあります。出力をラッチせずにそのままデータを出力するモードもあり、その時にはADCの出力がそのまま直ちに出力データとして現れます。AFE CONTROLレジスタのビットD4を1に設定すると、出力ラッチを行いません。出力データは、AFE CONTROLレジスタのビットD3を「1」に設定することで無効 (three state: ハイ・インピーダンス) にすることもできます。

このデータ出力のコード配列は通常バイナリ・データですが、AFE CONTROLレジスタのビットD5を「1」にすることにより、グレイ・コード出力に変更することができます。

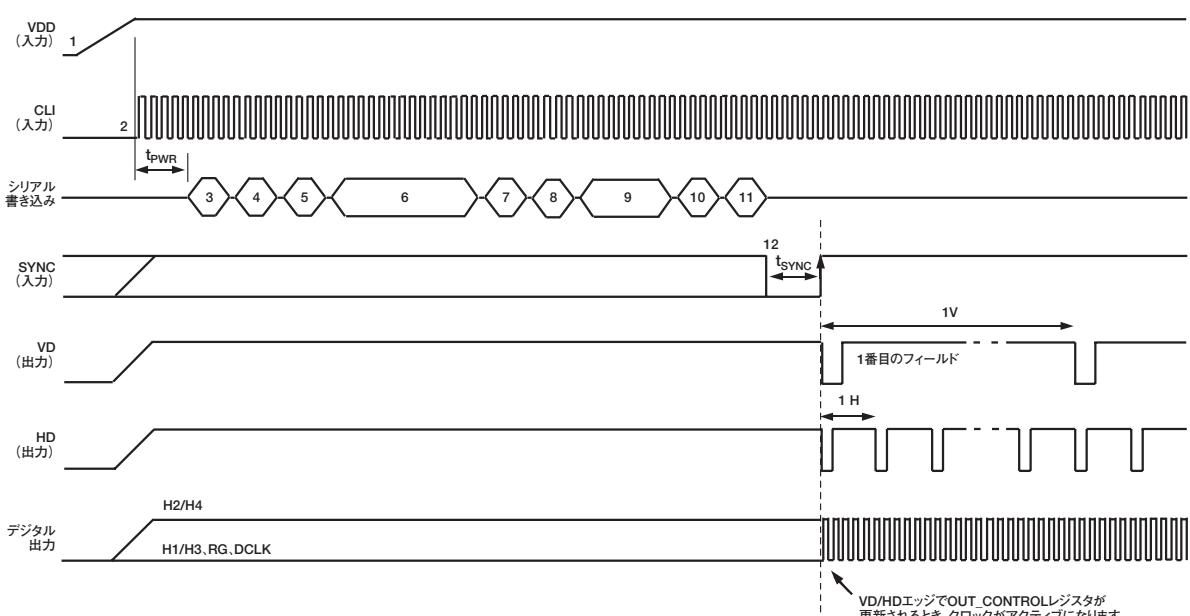

## パワーアップと同期

マスター・モードに推奨するパワーアップ・シーケンス

AD9995の電源起動時は、以下のパワーアップ・シーケンスを推奨します（図35にそれぞれのステップを示します）。マスター・モードではSYNC信号を必要とすることに注意してください。外部のSYNC信号を使用できない場合は、次のセクションに述べるようにSYNCPOLEレジスタに書き込むことにより、内部SYNCパルスを使用することで同様の動作が可能となります。

1. AD9995に電源を投入します。

2. マスター・クロック入力としてCLIを供給します。

3. SW\_RESETレジスタ（アドレス0x10：Bank 1）に「1」を書き込むことにより、AD9995のレジスタをリセットします。

4. デフォルトではAD9995はStandby3モードになっています。ノーマル動作にするために、AFE OPRMODEレジスタ（アドレス0x00：Bank 1）に、0x004を書き込みます。

5. BANKSELECTレジスタ（アドレス0x7F）に「1」を書き込みます。これはBank 2レジスタを選択するものです。

6. Bank 2レジスタ内の、VPAT Group、V-Sequence、フィールド・タイミング情報に関するレジスタなどへ必要な値を書き込みます。

7. BANKSELECTレジスタに「0」を書き込むことにより、Bank 1レジスタを選択します。

8. デフォルトではTGCORE\_RSTBレジスタ=0になっているので、内部のタイミング・コアはリセット状態になっています。TGCORE\_RSTBレジスタ（アドレス0x15：Bank 1）に「1」を書き込み、内部のタイミング・コアを動作させます。

9. 高速系タイミング、水平系タイミング、シャッター系タイミングなど必要なレジスタに書き込みます。

10. MASTERレジスタ（アドレス0x20：Bank 1）に「1」を書き込むことにより、AD9995をマスター・モードで動作させます。

11. OUT\_CONTROLレジスタ（アドレス0x11：Bank 1）に「1」を書き込みます。これにより、次のSYNCの立ち上がりエッジで、AD9995は駆動し始めます。

12. SYNCの生成：SYNCが電源起動時にハイであれば、少なくとも100nsの期間はSYNC入力をローにします。そしてSYNCをハイにします。これで内部のカウンタはリセットされ、VD/HDの動作を開始します。最初のVD/HDのエッジで、ほとんどのBank 1レジスタのアップデートを行い、OUT\_CONTROLは全ての出力を有効にします。

表XIII. パワーアップ・レジスタの書き込みシーケンス

| アドレス      | データ  | 説明                          |

|-----------|------|-----------------------------|

| 0x10      | 0x01 | 全レジスタをデフォルト値にリセット           |

| 0x00      | 0x04 | AFEとCLO発振器をパワーアップ           |

| 0x7F      | 0x01 | Bank 2レジスタを選択               |

| 0x00～0xFF |      | VPAT、V-Sequence、フィールド・タイミング |

| 0x7F      | 0x00 | Bank 1レジスタを選択               |

| 0x15      | 0x01 | 内部タイミング・コアをリセット             |

| 0x30～71   |      | 水平タイミングとシャッター・タイミング         |

| 0x20      | 0x01 | マスター・モードに設定                 |

| 0x11      | 0x01 | SYNC後にすべての出力をイネーブル          |

| 0x13      | 0x01 | SYNCPOLE（ソフトウェアSYNC専用）      |

## 外部SYNC信号なしでソフトウェアSYNCを生成

外部SYNC信号を使用できない場合は、SYNCPOLEレジスタ（アドレス0x13）を使用し、AD9995内で内部SYNC信号を生成することができます。ソフトウェアSYNCを使用する場合には、SYNC入力（ピン46）はグラウンド（VSS）に接続してください。

電源起動後、前述のステップ1からステップ11の操作を行います。ステップ12は、外部SYNCパルスを使用する代わりに、SYNCPOLEレジスタに「1」を書き込みます。これで、SYNC信号は内部で生成され、タイミング動作を開始します。

図35. 推奨するパワーアップ・シーケンスと同期、マスター・モード

# AD9995

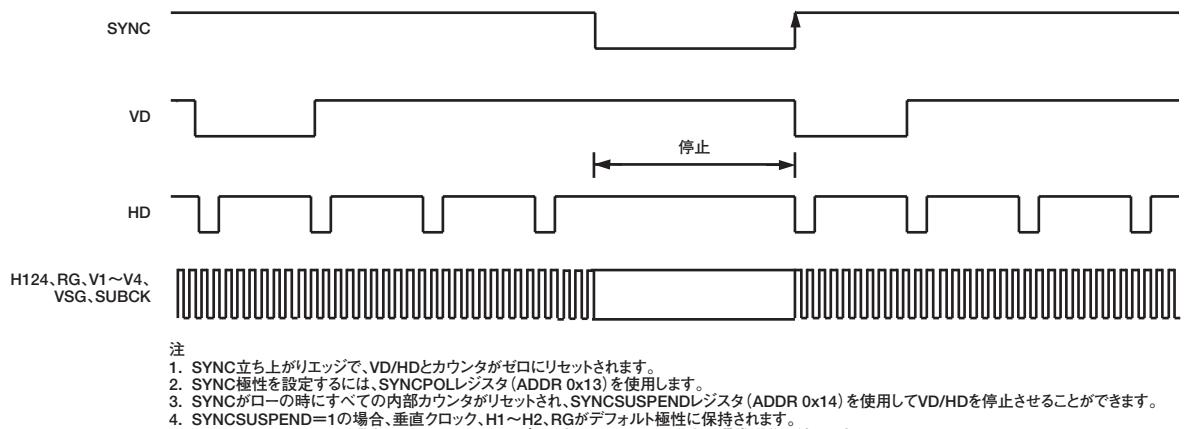

## マスター・モード動作時のSYNC

マスター・モード時であればいつでもSYNC入力を使用し、AD9995カウンタに外部タイミングとの再同期がかけられます(図36)。SYNCSUSPENDレジスタ(アドレス0x14)に「1」を書き込むことにより、SYNCの動作中に全てのデジタル出力を停止させておくことができます。

## スレーブ・モードでのパワーアップと同期

スレーブ・モードの電源起動動作は、マスター・モードの電源起動動作と次の2つの動作を除いて同じです。

- ・ステップ9の操作は行いません。マスター・モードの書き込みを行わないでください。

- ・スレーブ・モードではSYNCパルスは必要としません。ステップ12の代わりに外部からVDとHDを印加します。この動作によりAD9995は外部から同期がかけられ、Bank 1レジスタの内容がアップデートされ、タイミングが開始されます。

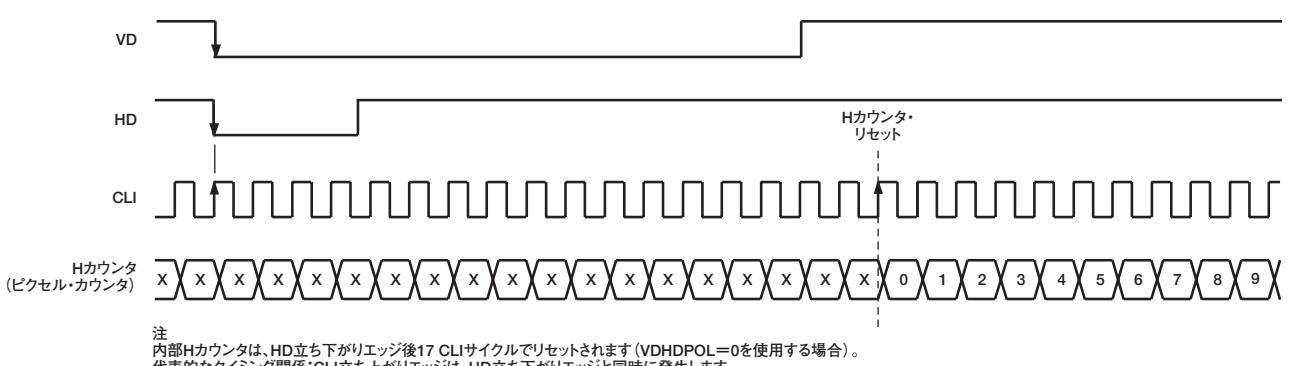

AD9995をスレーブ・モードで使用すると、VDとHDの入力により内部カウンタは同期がかけられます。VDの立ち上がりエッジに続いて、内部Hカウンタがリセットされるまで、HDの立ち上がりエッジからマスター・クロックであるCLIが17クロック分だけ必要です。図37に、このリセット動作を示します。

## スタンバイ・モード動作

AD9995には、実際の製品に使いやすいように、消費電力を最適化するための3つのスタンバイ・モード(Standby Mode)があります。OPRMODEレジスタのビット[1:0]はAD9995のパワーダウン時の状態を制御します。

OPRMODE[1:0]=00 = 通常動作

OPRMODE[1:0]=01 = スタンバイ1モード(Standby 1)

OPRMODE[1:0]=10 = スタンバイ2モード(Standby 2)

OPRMODE[1:0]=11 = スタンバイ3モード

(Standby 3: 最低消費電力)

表XIVに、それぞれのパワーダウン・モードの動作を示します。OUT\_CONTROLレジスタを使用したときのAD9995の状態は、スタンバイ1やスタンバイ2よりも優先されますが、スタンバイ3は、OUT\_CONTROLレジスタの動作よりも優先されます。スタンバイ3は、最小の消費電力を実現できますが、CLIとCLOの間の水晶発振器ドライバ回路もOFFにします。したがって、CLIとCLOをマスター・クロックを生成するために水晶発振器と併用している場合、回路はシャットダウンされて、クロック信号は出力されません。スタンバイ3モードから通常動作モードにするととき、OPRMODEレジスタに書き込みを行ってから少なくとも500μs経過後にタイミング・コアをリセットしなければなりません。これは、水晶発振器用の発振回路を駆動させるために必要な時間です。

図36. AD9995を外部タイミングに同期するSYNCのタイミング

図37. 外部VD/HDと内部Hカウンタとの同期、スレーブ・モード

表XIV. スタンバイ・モード動作

| I/O ブロック | スタンバイ3 (デフォルト) <sup>1, 2</sup> | OUT_CONT=LO <sup>2, 3</sup> | スタンバイ2 <sup>3, 4</sup> | スタンバイ1 <sup>3, 4</sup> |

|----------|--------------------------------|-----------------------------|------------------------|------------------------|

| AFE      | オフ                             | 変更なし                        | オフ                     | REFT、REFBのみオン          |

| タイミング・コア | オフ                             | 変更なし                        | オフ                     | オン                     |

| CLO発振器   | オフ                             | 変更なし                        | オン                     | オン                     |

| CLO      | HI                             | 動作中                         | 動作中                    | 動作中                    |

| V1       | LO                             | LO                          | LO                     | LO                     |

| V2       | LO                             | LO                          | LO                     | LO                     |

| V3       | LO                             | LO                          | LO                     | LO                     |

| V4       | LO                             | LO                          | LO                     | LO                     |

| V5       | LO                             | HI                          | HI                     | HI                     |

| V6       | LO                             | HI                          | HI                     | HI                     |

| VSG1     | LO                             | HI                          | HI                     | HI                     |

| VSG2     | LO                             | HI                          | HI                     | HI                     |

| VSG3     | LO                             | HI                          | HI                     | HI                     |

| VSG4     | LO                             | HI                          | HI                     | HI                     |

| VSG5     | LO                             | HI                          | HI                     | HI                     |

| SUBCK    | LO                             | HI                          | HI                     | HI                     |

| VSUB     | LO                             | LO                          | LO                     | LO                     |

| MSHUT    | LO                             | LO                          | LO                     | LO                     |

| STROBE   | LO                             | LO                          | LO                     | LO                     |

| H1       | Hi-Z                           | LO                          | LO (4.3mA)             | LO (4.3mA)             |

| H2       | Hi-Z                           | HI                          | HI (4.3mA)             | HI (4.3mA)             |

| H3       | Hi-Z                           | LO                          | LO (4.3mA)             | LO (4.3mA)             |

| H4       | Hi-Z                           | HI                          | HI (4.3mA)             | HI (4.3mA)             |

| RG       | Hi-Z                           | LO                          | LO (4.3mA)             | LO (4.3mA)             |

| VD       | LO                             | VDHDPOL値                    | VDHDPOL値               | 動作中                    |

| HD       | LO                             | VDHDPOL値                    | VDHDPOL値               | 動作中                    |

| DCLK     | LO                             | LO                          | LO                     | 動作中                    |

| DOUT     | LO                             | LO                          | LO                     | LO                     |

注

<sup>1</sup> スタンバイ3を終了するには、まずOPRMODE[1:0]に00を書き込んでから、発振器の適切なセトリングを保証するために約500μs後にタイミング・コアをリセットします。<sup>2</sup> 出力極性を決定するために、スタンバイ3モードはOUT\_CONTROLよりも優先されます。<sup>3</sup> OUT\_CONTROL=LOはスタンバイ1と2よりも優先されるので、これらの極性ではOUT\_CONT=HIを想定します。<sup>4</sup> スタンバイ1と2では、HとRGのドライブ強度が最小値 (4.3mA) に設定されます。

## AD9995

図38. AD9995の代表的な回路構成

## 回路レイアウト情報

AD9995の通常の結線図を図38に示します。PCボードのレイアウトはAD9995から優れた画像品質を得るために特に重要です。全ての電源ピン、特にAVDD1、TCVDD、RGVDD、HVDDなどはGNDに対し高周波数特性のよいチップ・コンデンサでデカップリングしなければなりません。デカップリング・コンデンサはできるだけ電源ピンの近くに配置されていなければならず、GNDとのインピーダンスをできるだけ最小にしなければなりません。ここでは、4.7 $\mu$ Fか、それ以上の大きな値のデカップリング・コンデンサをそれぞれの電源であるAVDD、RGVDD、HVDD、DRVDDに接続する必要がありますが、全てを個別のピンに接続する必要はありません。ほとんどのアプリケーションではHVDDとRGVDDを共有することができますが、その場合別々の電源はそれぞれ別々にバイパスされます。DRVDDには異なる3Vの電源を使用することができますが、この電源のデカップリングはAD9995の他の電源と同じGNDに対して行ってください。DRVSSに異なるGNDを接続するレイアウトは推奨しません。パッケージ底面にある露出パドルは、大きなパッドにハンダ付けすることを推奨します。このパッドはグラウンド・プレーンにバイアス接続されます。

アナログ系のバイパス・ピンであるREFT (Reference Top) とREFB (Reference Bottom) も、同様にそれらに対応するGNDピンにできるだけ近くなるようにデカップリングしてください。アナログ入力 (CCDIN) のコンデンサはこの入力ピンに近くなるように配置してください。

H1～H4とRGのラインは、信号の余分な歪みを避けるために低インダクタンスになるように設計してください。CCDによってH1～H4には大きな電流変動が発生するので、太い配線が望まれます。可能であれば、AD9995を物理的にCCDの近くに置くと、これらの信号ラインのインダクタンス成分を減少させることができます。通常、AD9995からCCDへの信号ループは可能な限り直線にしてください。

AD9995は水晶発振器を駆動させるために、発振回路を内蔵しています。図39は24MHzの水晶発振器を使用したときの回路の例です。外付けの抵抗とコンデンサの実際の値は使用する水晶発振器のデータシートを参照してください。

図39. 水晶発振器ドライバのアプリケーション

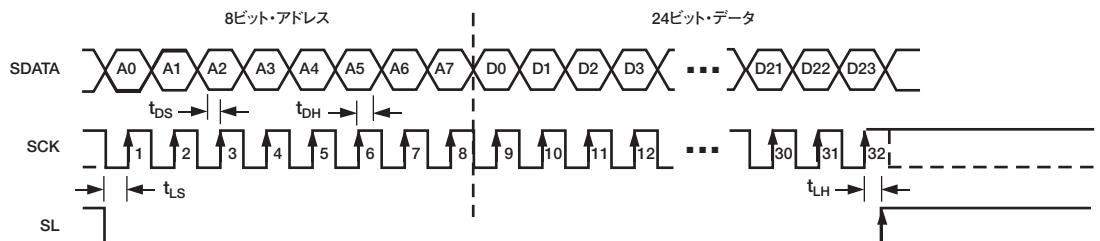

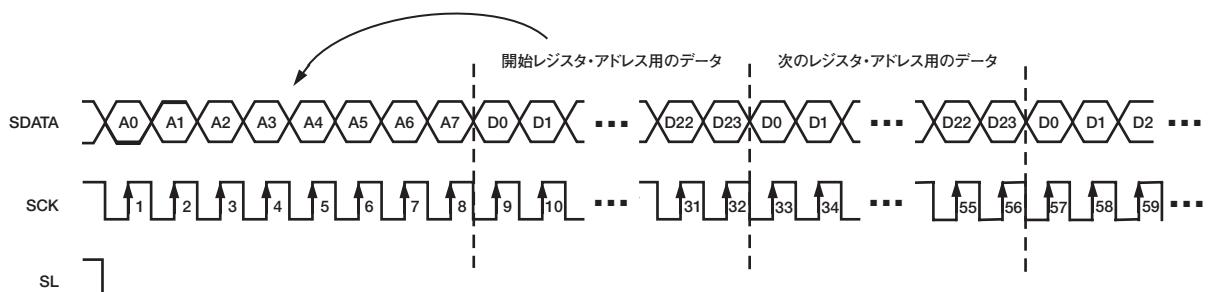

## シリアル・インターフェースのタイミング

AD9995の全ての内部レジスタは3線シリアル・インターフェースでアクセスします。それぞれのレジスタは8ビットのアドレスと24ビットのデータで表記され、アドレスもデータもLSBから開始します。それぞれのレジスタに書き込むためには32ビットの動作を必要とします（図40a参照）。多くのレジスタ・データは24ビットより少ないので、全て24ビット分のデータを書き込まなければなりません。もしデータ幅が10ビット分しかない場合、上の14ビットは「ドント・ケア」となり、シリアルでの書き込みは0で埋められます。もし、24ビットより少なければそのレジスタは新しいデータに更新されません。

図40bに、より効率的なレジスタへの書き込み方法を示します。これはAD9995のアドレス自動更新（Address Auto-Increment）と呼ばれます。この方法を使用すれば、小さい方のアドレスを最初に書き込んだ後は、連続して24ビットのデータだけを書き込むことが可能になります。それぞれの新しい24ビット・ワードは自動的に次の大きいアドレスのレジスタ・データとなります。レジスタにそれぞれの8ビットのアドレスを書き込まないことによって、より早くレジスタをロードできます。アドレス自動更新はどのアドレスから開始することも可能です。2つのレジスタしか書き込まない場合も、全部のレジスタに書き込む場合も、この方法を使用できます。

図40a. シリアル書き込み動作

図40b. 連続シリアル書き込み動作

# AD9995

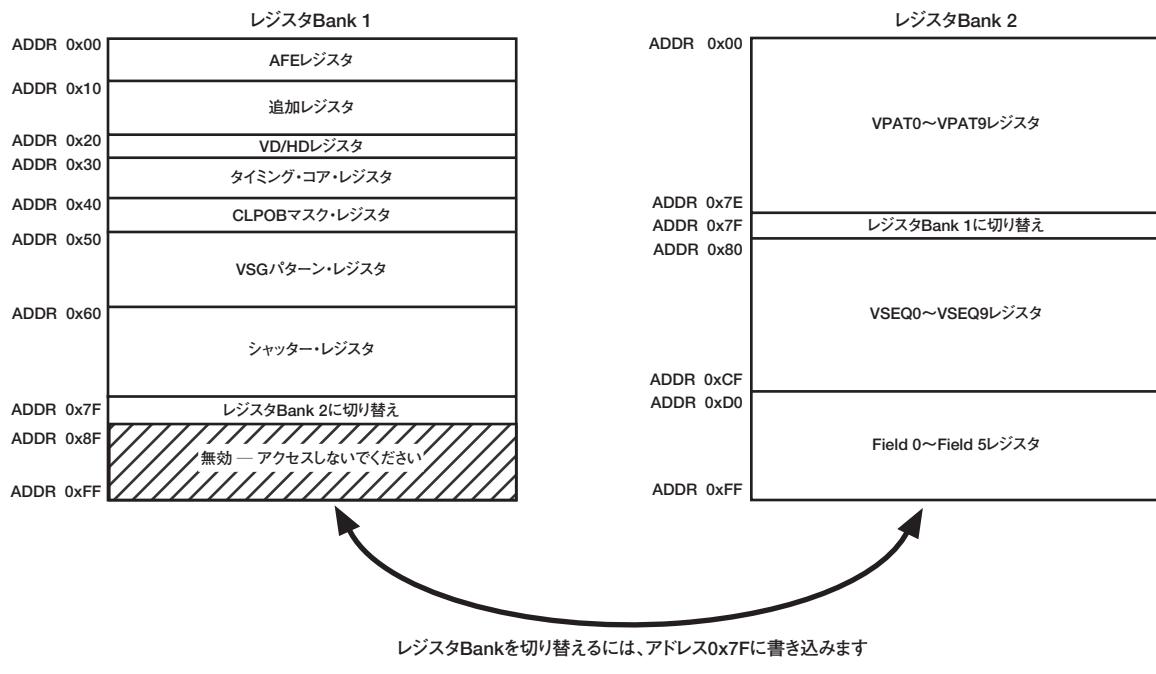

## レジスタ・アドレスのBank 1と2

AD9995のアドレスは2つの領域に分けられています。レジスタBank 1とレジスタBank 2です。図41にアドレスがどのように2つに分けられているかを示します。レジスタBank 1には、AFE、追加、VD/HD、タイミング・コア、CLPOBマスク、VSGパターンとシャッターなどが割り当てられています。レジスタBank 2には、Vパターン、Vシーケンス、フィールドなどが割り当てられています。

AD9995に書き込むとき、アドレス0x7Fにどちらのバンクに書き込むかを指定します。Bank 1に書き込むときは、アドレス0x7Fに0を書き込み、Bank 2に書き込むときはアドレス0x7Fに1を書き込んでください。

レジスタBank 1には、多くの使用しないアドレスがあることに注意してください。アドレス0x00から0x7Fの未定義アドレスは、アドレス自動更新の機能を使用して、0を書き込むこともできます。ただし、0x7Fアドレスより上の未定義のアドレスに対しては、何も書き込まないでください。AD9995が正常動作しなくなる恐れがあります。

図41. 内部レジスタBank 1と2のレイアウト

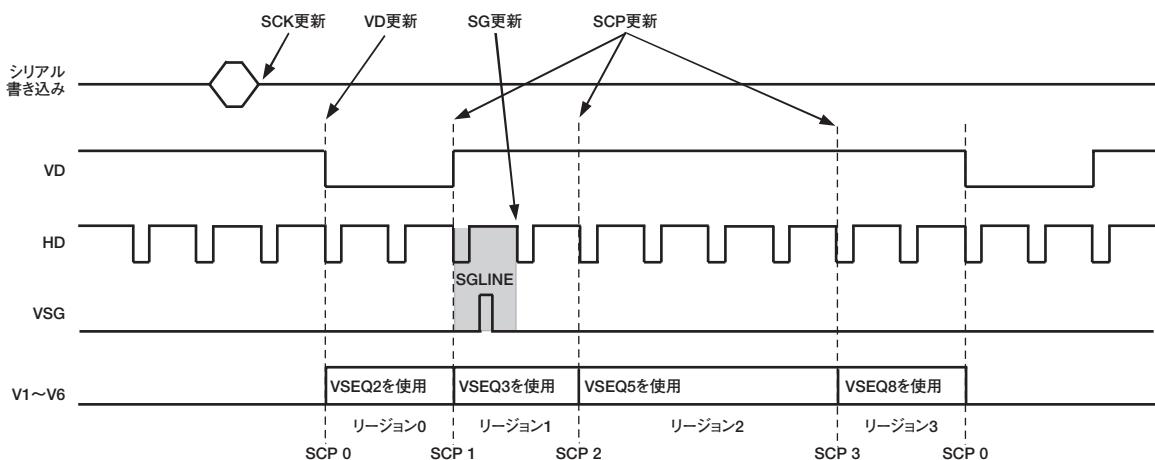

### 新しいレジスタ値の更新

AD9995の内部レジスタはレジスタにより異なる時間に更新されます。表XVに、4つの異なるレジスタの更新をまとめています。

1. **SCK更新**：いくつかのBank 1のレジスタは、24ビット (D23) のデータを書き込むと直ちに更新されます。これらのレジスタは、電源起動時やリセットなどのようにVDに依存しない機能について使用されます。これらのレジスタはBank 1レジスタ・マップの薄いグレイになっている箇所です。

Bank Selectレジスタ (Bank 1とBank 2のアドレス0x7F) も、SCK更新です。

2. **VD更新**：Bank 2のフィールド・レジスタと同様にBank 1のほとんどのレジスタは、次のVDの立ち下がりエッジで更新されます。これらのレジスタ値が次のVDの立ち下がりで更新されるまで、現在のフィールドには影響を与えず、新しいレジスタ値は次のフィールドで有効になります。Bank 1レジスタの更新はUPDATEレジスタ (アドレス0x19) を使用することにより、VDの立ち下がりエッジより遅らすことができます。これは、VD更新レジスタは、フィールド内のどのHDラインでも更新させることができるということです。

Bank 2レジスタはUPDATEレジスタの影響は受けません。

- SGライン更新**：Bank 1の中のいくつかのレジスタは、SGアクティブ・ラインの後のHDの立ち下がりエッジで更新されます。これらはSUBCK信号を制御するレジスタで、SUBCK出力はSGラインが終わるまで更新されません。これらのレジスタは、Bank 1レジスタ・マップの濃いグレイの箇所です。

- SCP更新**：Bank 2では、Vパターン・グループとVシーケンス・レジスタの全てのレジスタがそれらが使われる次のSCPで更新されます (アドレス: 0x00~0xCF、0x7F以外)。たとえば、図42では、垂直転送クロック出力としてリージョン1にVシーケンス3を使用しています。これは、Vシーケンス3のレジスタがVシーケンス3に使われているVパターンは、SCP1で更新されることを意味します。いくつもの書き込みが同じレジスタに対して行われると、最後の1つはSCP1までに書き込みを終了させなければなりません。同様に、Vシーケンス5レジスタの更新はSCP2で行われ、Vシーケンス8レジスタはSCP3で更新されます。

表XV. レジスタの更新位置

| 更新タイプ            | レジスタBank                  | 説明                                                                                                                                                                         |

|------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK更新<br>VD更新    | Bank 1のみ<br>Bank 1とBank 2 | 24番目のデータ・ビット (D23) がクロック入力されると、レジスタはすぐに更新されます。レジスタはVDの立ち下がりエッジで更新されます。Bank 1のアドレス0x19にあるUPDATEレジスタを使用すると、Bank 1のVD更新レジスタをさらに遅延させることができます。Bank 2の更新は、UPDATEレジスタによる影響を受けません。 |

| SGライン更新<br>SCP更新 | Bank 1のみ<br>Bank 2のみ      | レジスタは、SGアクティブ・ラインの最後のHD立ち下がりエッジで更新されます。<br>レジスタは、レジスタが使用される次のSCPで更新されます。                                                                                                   |

図42. レジスタの更新位置 (定義については表XVを参照)

# AD9995

## レジスタBank 1の詳細リスト

特に記載のない限り、すべてのレジスタはVD更新されます。

すべてのアドレスとデフォルト値は16進です。

=SCK更新

=SGライン更新

表XVI. AFEレジスタ・マップ

| アドレス | データ・ビットの内容 | デフォルト値 | レジスタ名      | レジスタ説明                     |

|------|------------|--------|------------|----------------------------|

| 00   | [11:0]     | 7      | OPRMODE    | AFE動作モード (詳細については表XXIVを参照) |

| 01   | [9:0]      | 0      | VGAGAIN    | VGAゲイン                     |

| 02   | [7:0]      | 80     | CLAMPLEVEL | 光学黒クランプ・レベル                |

| 03   | [11:0]     | 4      | CTLMODE    | AFE制御モード (詳細については表XXVを参照)  |

表XVII. 追加レジスタ・マップ

| アドレス | データ・ビットの内容 | デフォルト値 | レジスタ名         | レジスタ説明                                      |

|------|------------|--------|---------------|---------------------------------------------|

| 10   | [0]        | 0      | SW_RST        | ソフトウェア・リセット。1=全レジスタをデフォルトにリセットしてから、0に自己クリア。 |

| 11   | [0]        | 0      | OUTCONTROL    | 出力制御。0=全出力をDC非アクティブに設定。                     |

| 12   | [0]        | 1      | TEST USE      | 内部使用専用。1に設定すること。                            |

| 13   | [0]        | 0      | SYNCPOL       | SYNCのアクティブ極性 (0=アクティブ・ロー)                   |

| 14   | [0]        | 0      | SYNCSUSPEND   | SYNCアクティブ区間でクロックを停止 (1=停止)。                 |

| 15   | [0]        | 0      | TGCORE_RSTB   | タイミング・コア・リセット・バー。0=TGコアをリセット、1=動作を再開        |

| 16   | [0]        | 1      | OSC_PWRDOWN   | CLO発振器パワーダウン (0=発振器がパワーダウン)                 |

| 17   |            |        |               | 未使用                                         |

| 18   | [0]        | 0      | TEST USE      | 内部使用専用。0に設定すること。                            |

| 19   | [11:0]     | 0      | UPDATE        | シリアル更新。VD更新レジスタを更新するには、フィールド内でライン (HD) を設定。 |

| 1A   | [0]        | 0      | PREVENTUPDATE | VD更新レジスタの更新を禁止。1=更新を禁止。                     |

| 1B   | [23:0]     | 0      | MODE          | モード・レジスタ                                    |

| 1C   | [1:0]      | 0      | FIELDVAL      | フィールド値同期。0=次のフィールド0、1=次のフィールド1、2/3=次のフィールド2 |

表XVIII. VD/HDレジスタ・マップ

| アドレス | データ・ビットの内容 | デフォルト値 | レジスタ名    | レジスタ説明                              |

|------|------------|--------|----------|-------------------------------------|

| 20   | [0]        | 0      | MASTER   | VD/HDマスターまたはスレーブのタイミング (0=スレーブ・モード) |

| 21   | [0]        | 0      | VDHDPOL  | VD/HDアクティブ極性。0=ローレベル、1=ハイレベル        |

| 22   | [17:0]     | 0      | VDHDRISE | VD [17:12]とHD [11:0]の立ち上がりエッジ位置     |

表XIX. タイミング・コア・レジスタ・マップ

| アドレス | データ・ビットの内容 | デフォルト値 | レジスタ名       | レジスタ説明                                                                                                                              |

|------|------------|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 30   | [0]        | 0      | CLIDIVIDE   | CLI入力クロックを2分周。1=2分周                                                                                                                 |

| 31   | [12:0]     | 01001  | H1CONTROL   | H1信号制御：極性[0] (0=反転、1=反転なし)<br>H1立ち上がりエッジ位置[6:1]。H1立ち下がりエッジ位置[12:7]                                                                  |

| 32   | [12:0]     | 01001  | H3CONTROL   | H3信号制御：極性[0] (0=反転、1=反転なし)<br>H3立ち上がりエッジ位置[6:1]。H3立ち下がりエッジ位置[12:7]                                                                  |

| 33   | [12:0]     | 00801  | RGCONTROL   | RG信号制御：極性[0] (0=反転、1=反転なし)<br>RG立ち上がりエッジ位置[6:1]。RG立ち下がりエッジ位置[12:7]                                                                  |

| 34   | [1:0]      | 0      | HBLKRETIME  | HBLKから内部H1/H3へのクロックのタイミング再生。H1タイミング再生[0]。H3タイミング再生[1]<br>望ましい設定は各ビットとも1です。各ビットを1に設定すると、HBLKトグル位置に1サイクルの遅延が追加されます。                   |

| 35   | [14:0]     | 1249   | DRVCONTROL  | H1 [2:0]、H2 [5:3]、H3 [8:6]、H4 [11:9]、RG [14:12]のドライブ強度制御。ドライブの現在値：0=オフ、1=4.3mA、2=8.6mA、3=12.9mA、4=17.2mA、5=21.5mA、6=25.8mA、7=30.1mA |

| 36   | [11:0]     | 00024  | SAMPCONTROL | SHP/SHDのサンプル制御：SHPサンプリング位置[5:0]<br>SHDサンプリング位置[11:6]                                                                                |

| 37   | [8:0]      | 100    | DOUTCONTROL | DOUT位相制御[5:0]。DCLKモード[6]。DOUTDELAY [8:7]                                                                                            |

表XX. CLPOBマスク・レジスタ・マップ

| アドレス | データ・ビットの内容 | デフォルト値 | レジスタ名     | レジスタ説明                                   |

|------|------------|--------|-----------|------------------------------------------|

| 40   | [23:0]     | FFFFFF | CLPMASK01 | CLPOBライン・マスキング。ライン#0 [11:0]。ライン#1 [23:0] |

| 41   | [23:0]     | FFFFFF | CLPMASK23 | CLPOBライン・マスキング。ライン#2 [11:0]。ライン#3 [23:0] |

| 42   | [11:0]     | FFFFFF | CLPMASK4  | CLPOBライン・マスキング。ライン#4 [11:0]              |

表XXI. SGパターン・レジスタ・マップ

| アドレス | データ・ビットの内容 | デフォルト値 | レジスタ名     | レジスタ説明                                                    |

|------|------------|--------|-----------|-----------------------------------------------------------|

| 50   | [3:0]      | F      | SGPOL     | SGパターンのスタート極性。パターン#0 [0]。パターン#1 [1]。パターン#2 [2]。パターン#3 [3] |

| 51   | [23:0]     | FFFFFF | SGTOG12_0 | パターン#0。トグル位置1 [11:0]。トグル位置2 [23:12]                       |

| 52   | [23:0]     | FFFFFF | SGTOG12_1 | パターン#1。トグル位置1 [11:0]。トグル位置2 [23:12]                       |

| 53   | [23:0]     | FFFFFF | SGTOG12_2 | パターン#2。トグル位置1 [11:0]。トグル位置2 [23:12]                       |

| 54   | [23:0]     | FFFFFF | SGTOG12_3 | パターン#3。トグル位置1 [11:0]。トグル位置2 [23:12]                       |

表XXII. シャッター制御レジスタ・マップ

| アドレス | データ・ビットの内容        | デフォルト値 | レジスタ名                     | レジスタ説明                                                                                                          |

|------|-------------------|--------|---------------------------|-----------------------------------------------------------------------------------------------------------------|