## MAX77542

## 16VIN/16A の 4 相高効率降圧コンバータ

### 概要

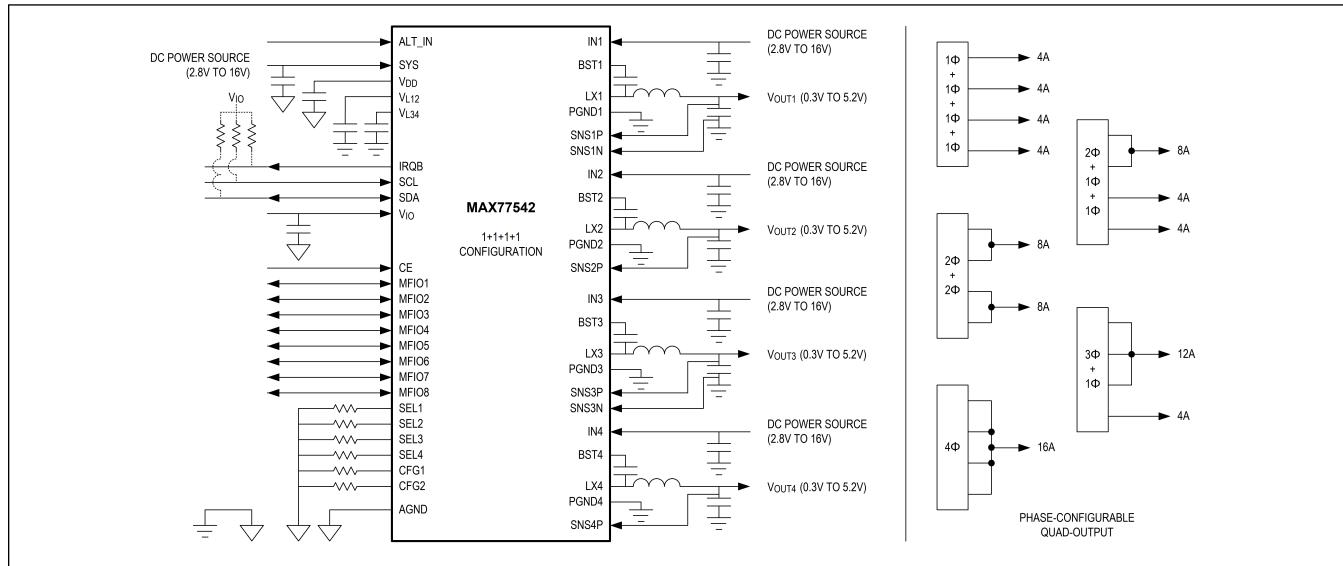

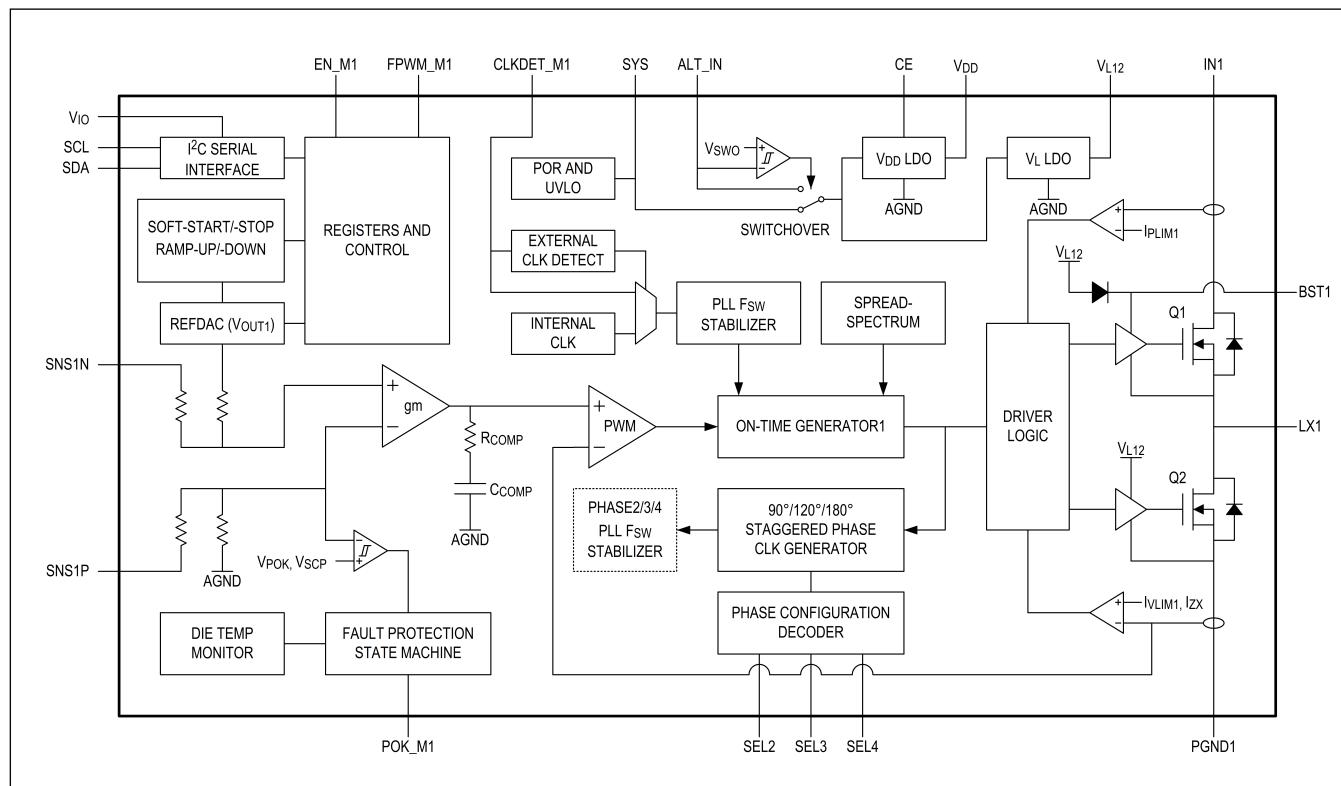

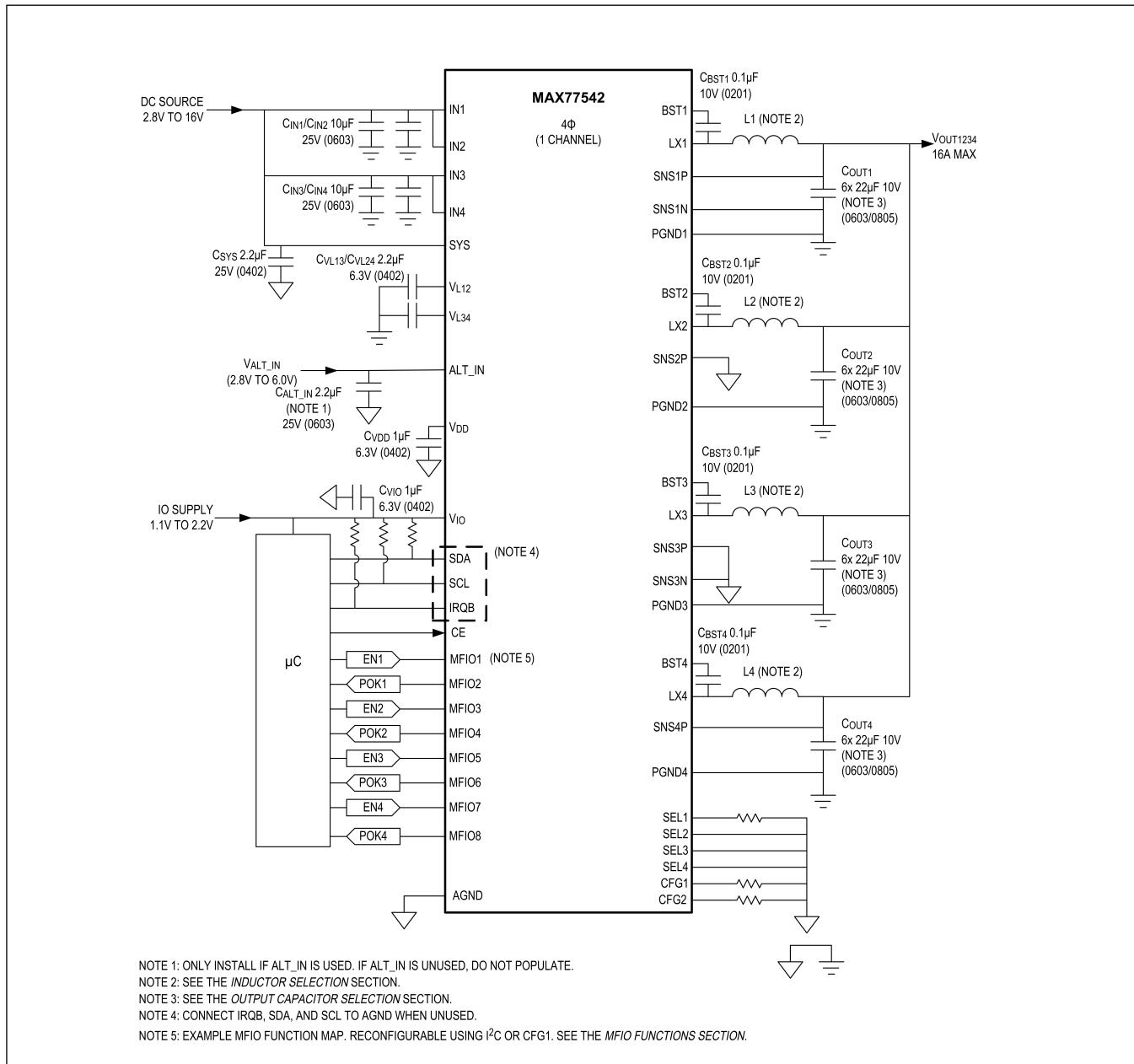

MAX77542 は、4 つの 4A スイッチング位相を備えた高効率降圧コンバータです。適応型 COT (オン時間一定) 電流モード制御方式を使用し、柔軟なアーキテクチャにより 5 つの位相構成に対応できます。幅広い入力電圧範囲を備えているため、1~3 セルのリチウムイオン・バッテリ、および USB 給電 (PD) 電源レールから 1V 未満の出力へ直接変換することが可能です。出力電圧は、抵抗を使用してプリセットでき、I<sup>2</sup>C 対応のインターフェースを通じて更に調整が可能です。

フレキシブル・シーケンサとプログラマブルなソフトスタート／ソフトストップ・スルーレートにより、動作状態間の遷移を制御することができます。プログラマブルなスイッチング周波数、周波数トラッキング、およびスペクトラム拡散機能を搭載しており、ノイズに敏感なアプリケーションに対してシステムを容易に最適化できます。多機能 I/O により、EN、LPM、FPWM、POK、RSTINB、および RSTOB ステータスに対する各出力を柔軟に制御することができます。一連の保護機能を内蔵しているため、異常な動作条件下でも安全な動作を確保します。

### アプリケーション

- 1~3 セルのリチウムイオン、および USB-C Power Delivery システム

- オーディオ／ビデオ機器および PCIe/RAID カード

- アプリケーション・プロセッサ、FPGA、DSP、ASIC

### 特長と利点

- 入力電圧範囲 : 2.8V~16V

- 出力電圧範囲 : 0.3V~5.2V

- 最大 16A (4A/Φ)、5 つの位相構成

- V<sub>OUT</sub> 精度 : ±0.5% (+25°C のデフォルト V<sub>OUT</sub> に対して)

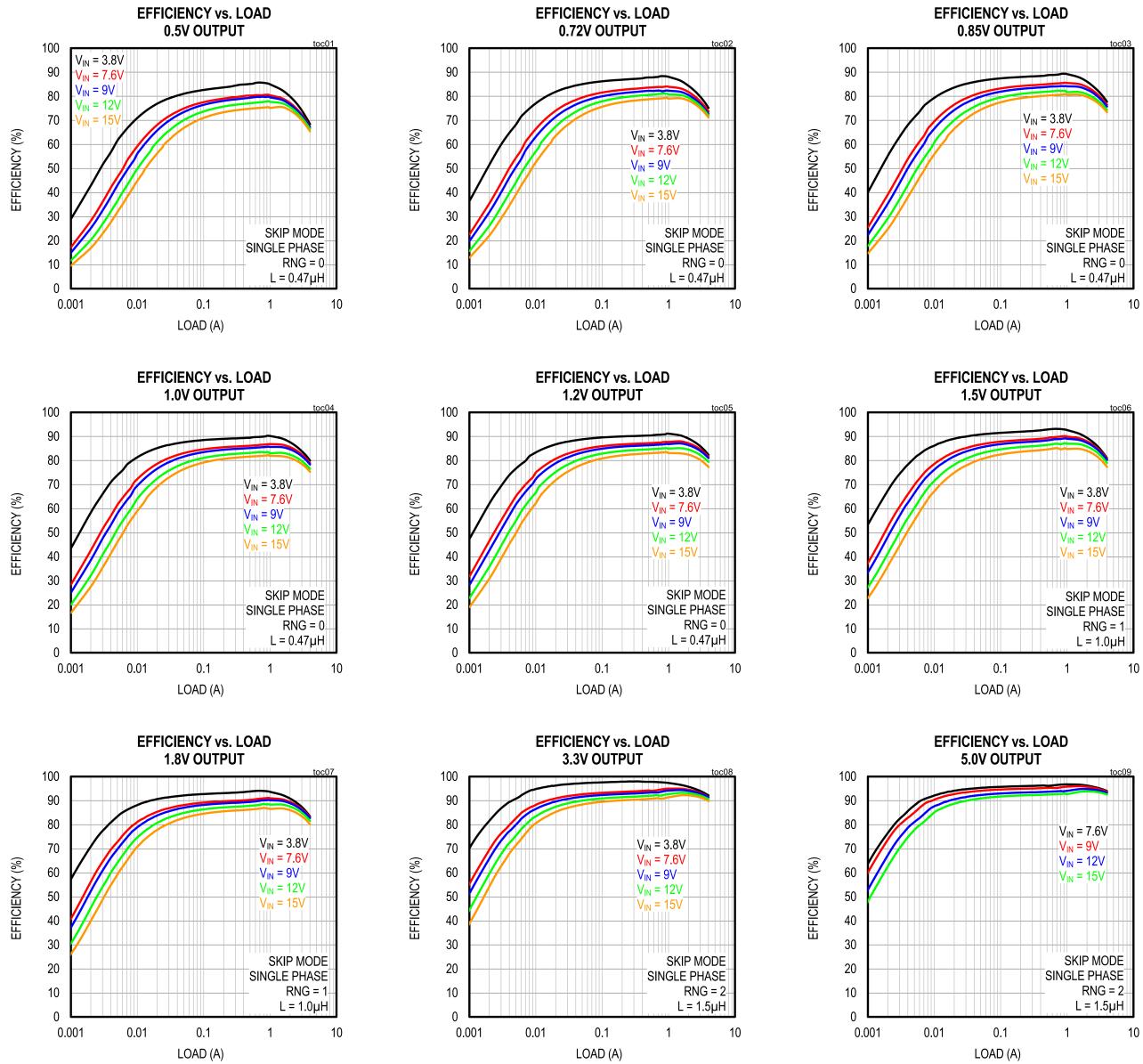

- ピーク効率 : 94% (7.6V<sub>IN</sub>、3.3V<sub>OUT</sub>、1MHz)

- 自動スキップ／PWM 遷移および低消費電力モード

- 最大デューティ・サイクル 98% のドロップアウト動作

- 差動出力電圧の検出

- ソフトスタート／ソフトストップ・スルーレートを備えたフレキシブル・シーケンサ

- プリバイアスされた起動およびアクティブ出力放電

- 公称スイッチング周波数 : 0.5MHz/1.0MHz/1.5MHz

- スペクトラム拡散変調により EMI を低減

- 内部／外部周波数トラッキング

- デフォルト V<sub>OUT</sub> と位相構成は R<sub>SELx</sub> で設定

- 多機能 I/O による EN、LPM、FPWM、POK

- UVLO、サーマル・シャットダウン、および短絡保護

- 高速 I<sup>2</sup>C シリアル・インターフェース

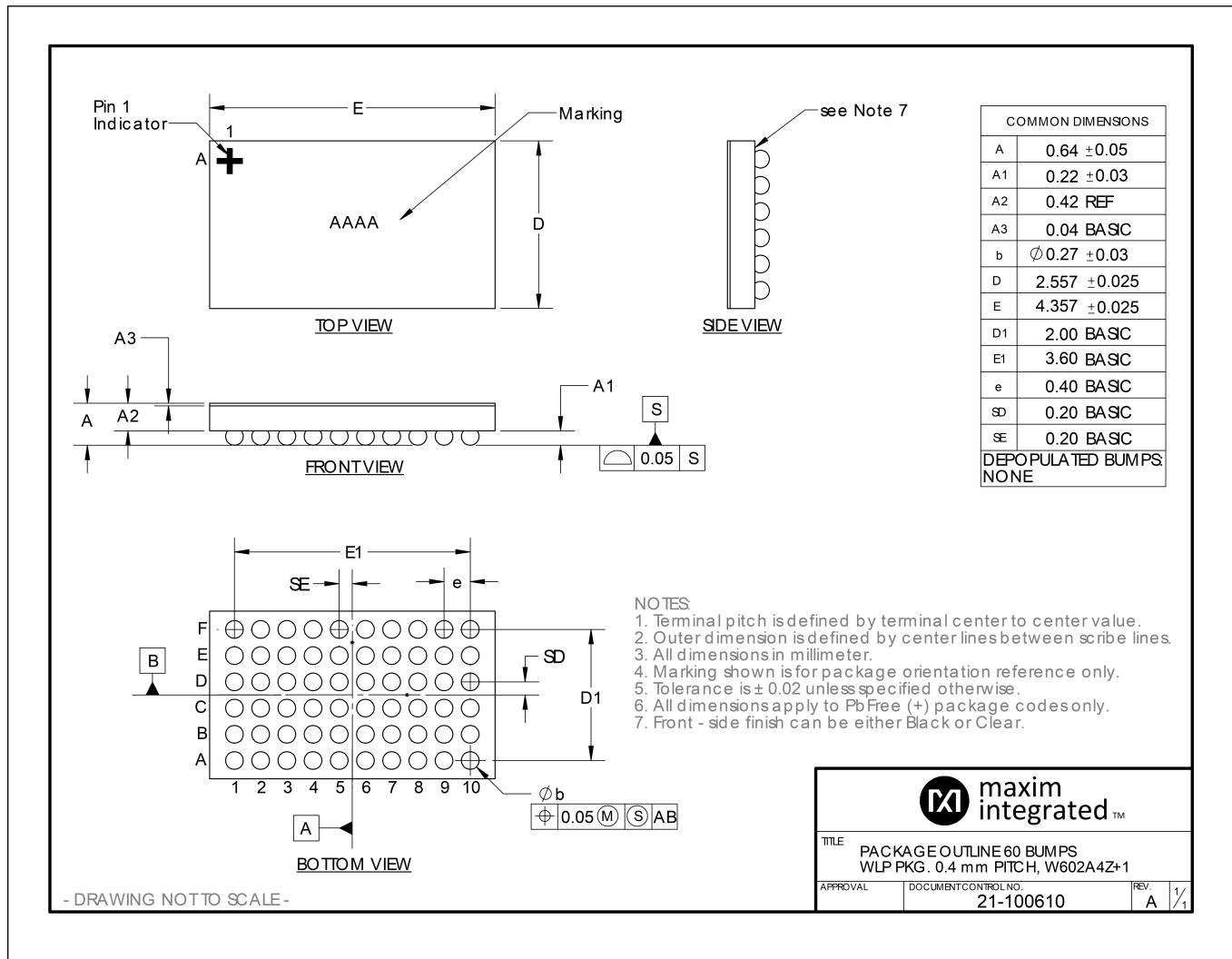

- 60 バンプ WLP (4.36mm × 2.56mm × 0.65mm)

- 総ソリューション・サイズ : 115mm<sup>2</sup> 未満 (2520 インダクタ使用時)

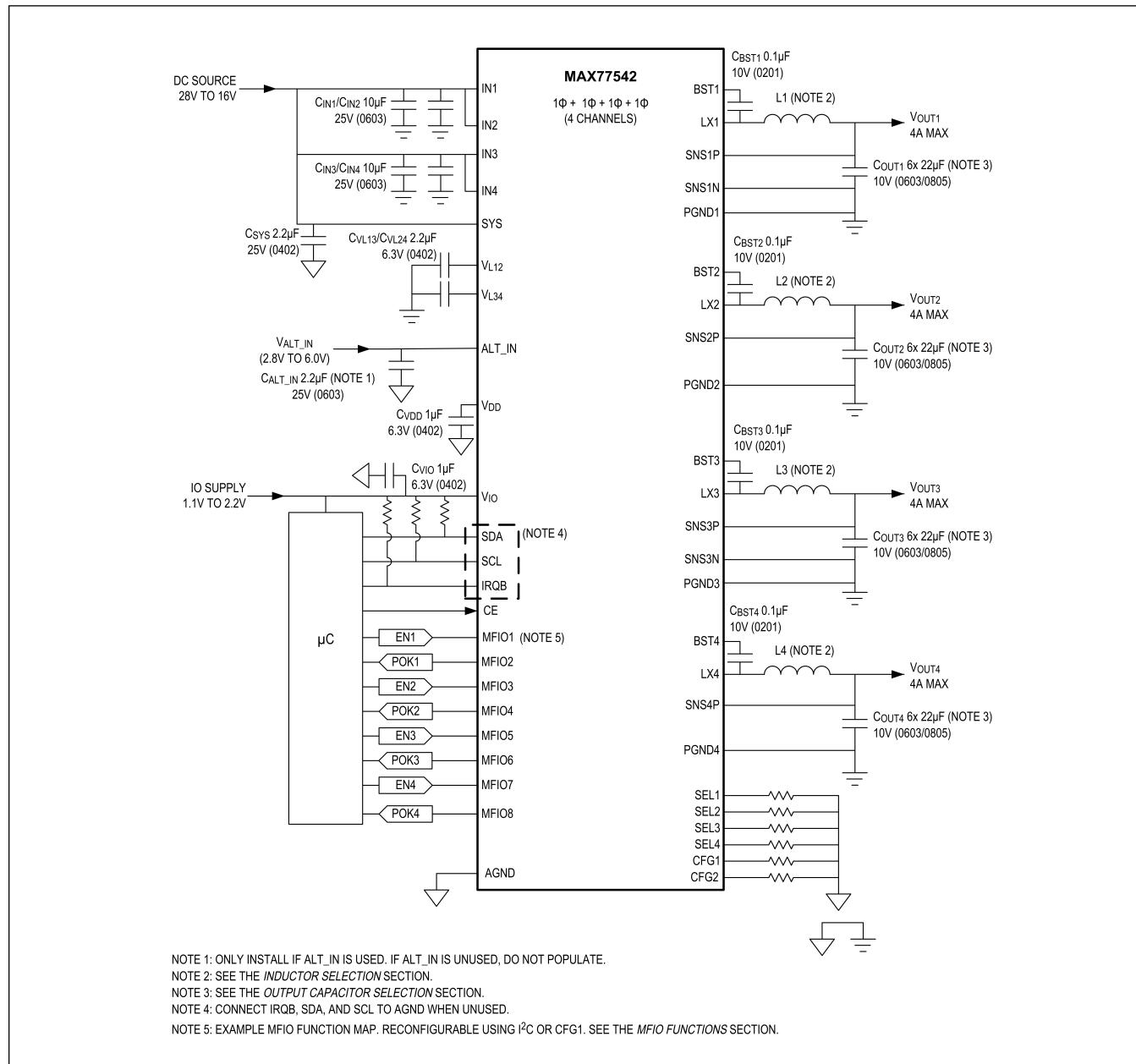

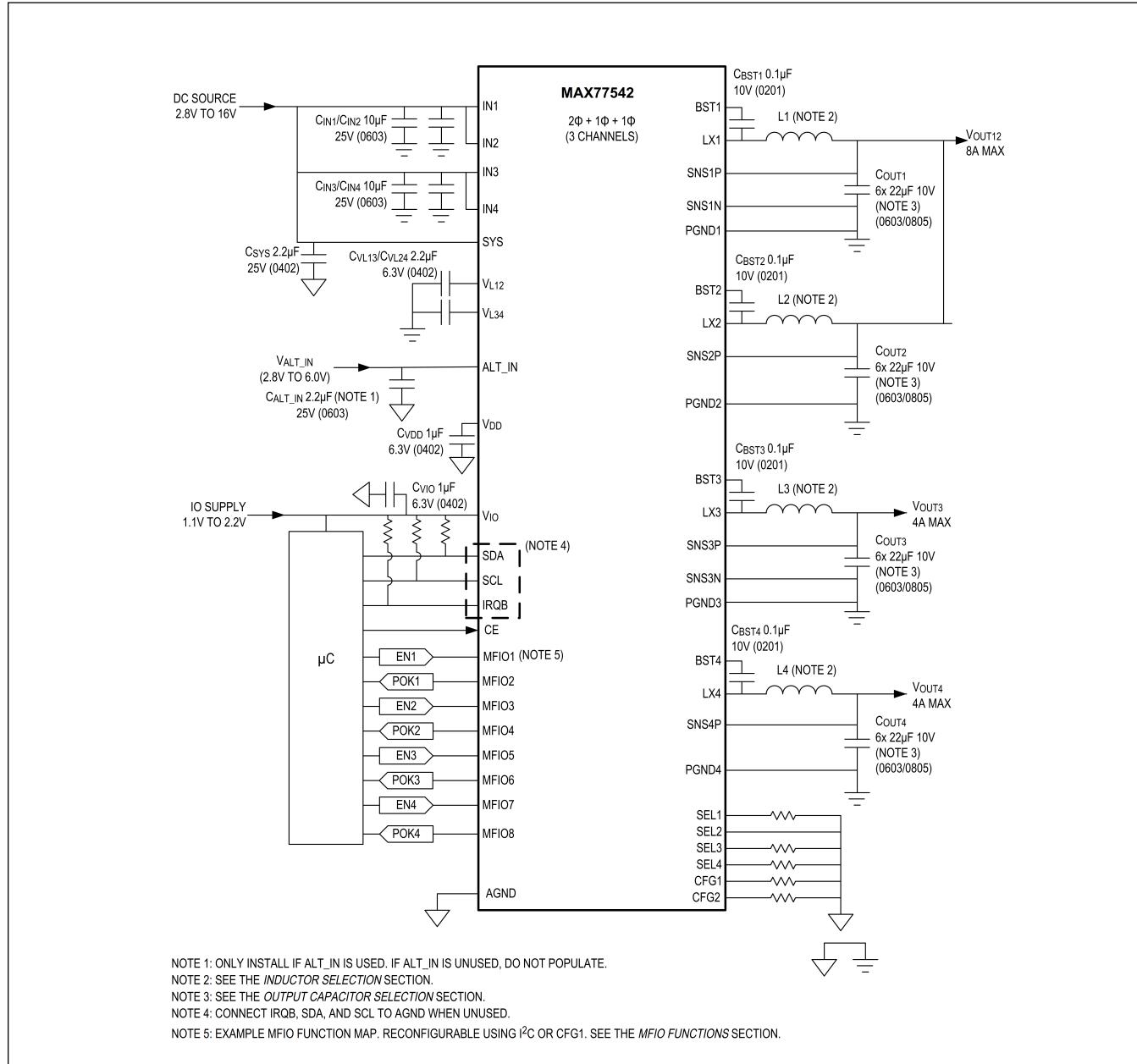

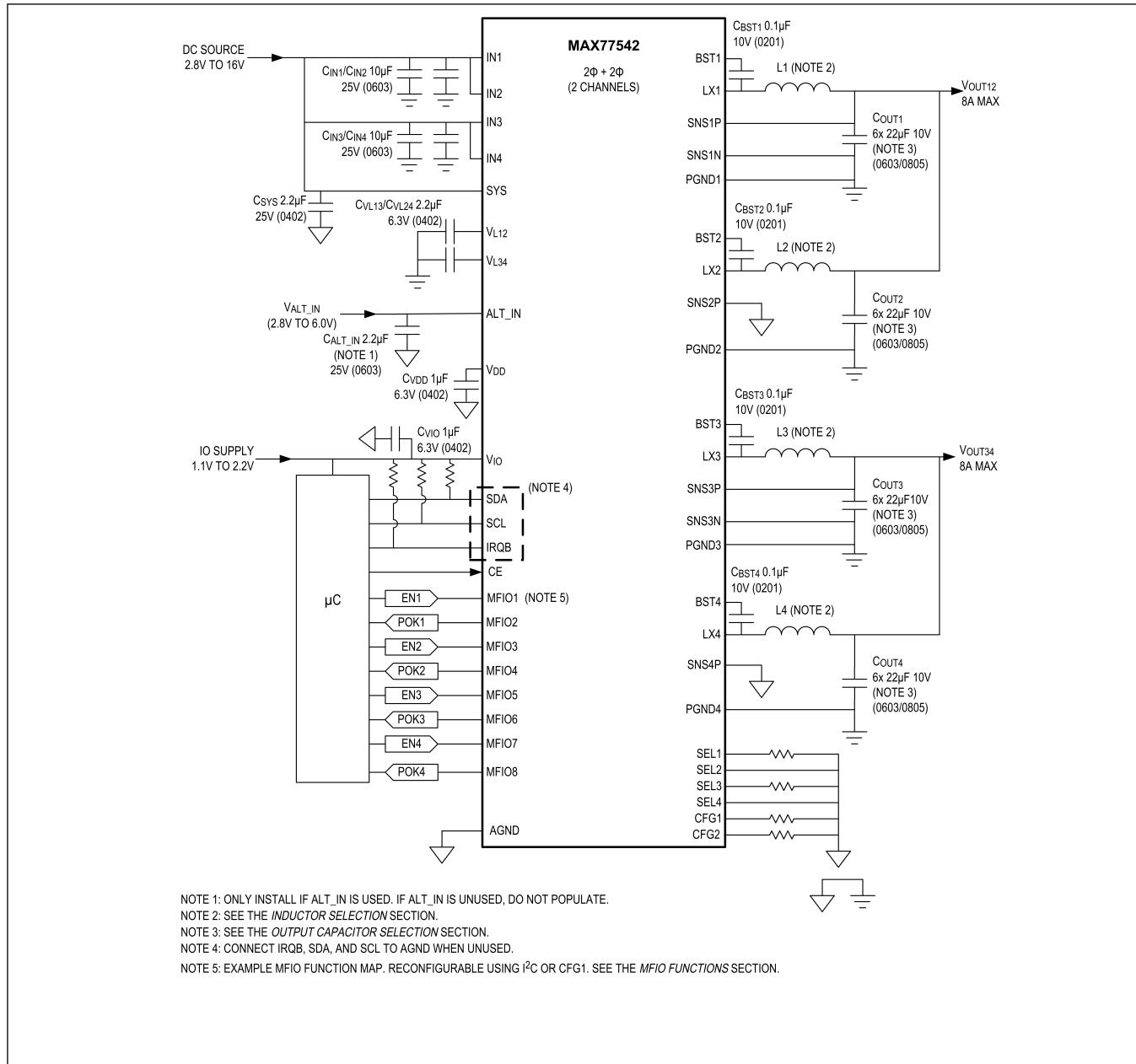

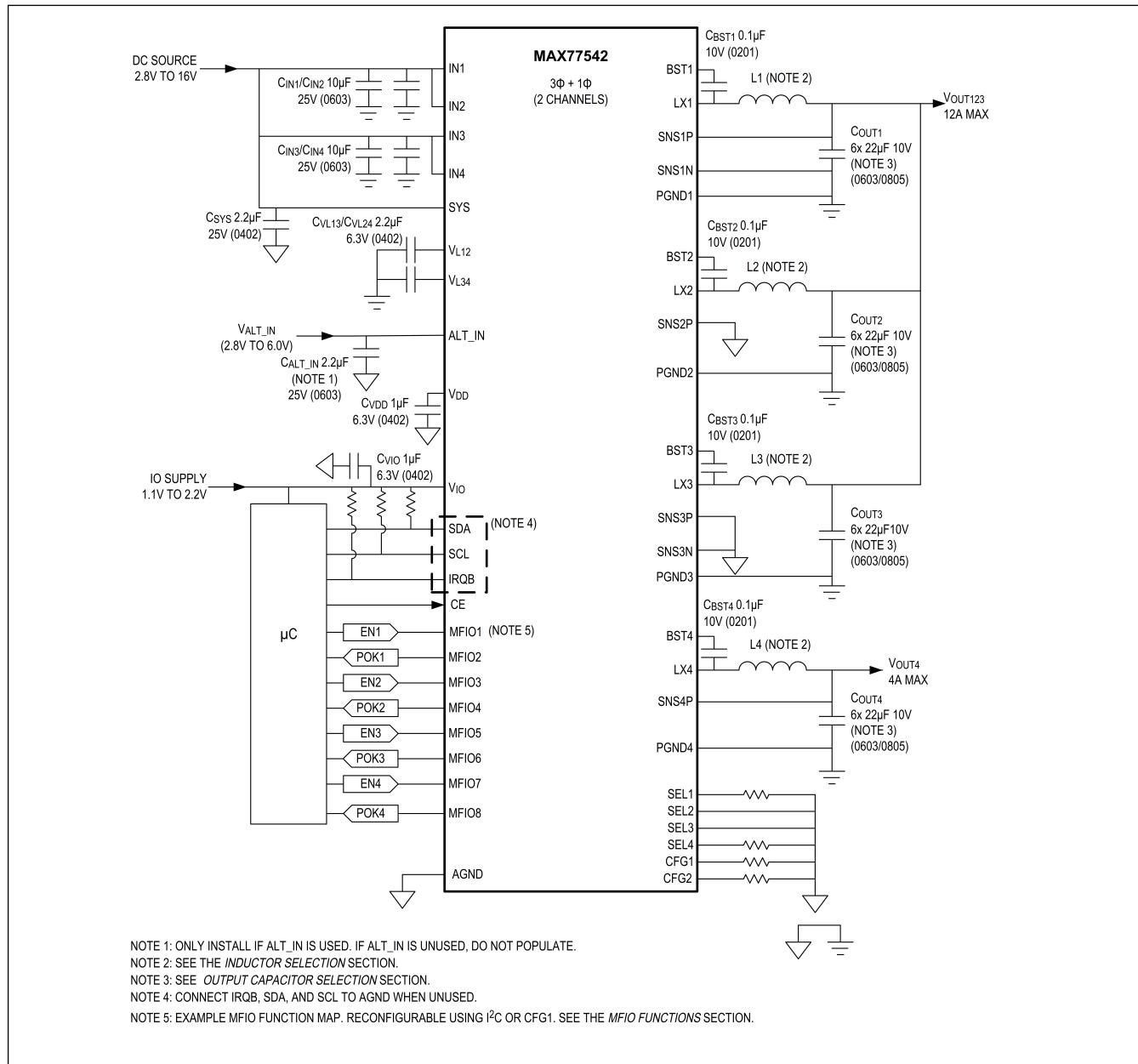

### 標準アプリケーション回路

標準アプリケーション回路の続きはデータシート末尾に記載されています。

オーダー情報はデータシート末尾に記載されています。

## 目次

|                                      |    |

|--------------------------------------|----|

| 概要                                   | 1  |

| アプリケーション                             | 1  |

| 特長と利点                                | 1  |

| 標準アプリケーション回路                         | 1  |

| 絶対最大定格                               | 7  |

| 推奨動作条件                               | 7  |

| パッケージ情報                              | 7  |

| 60 WLP (厚い UBM)                      | 7  |

| 電気的特性—トップ・レベル                        | 9  |

| 電気的特性—4 相構成の設定が可能な降圧コンバータ            | 11 |

| 電気的特性—多機能 I/O                        | 15 |

| 電気的特性—ADC                            | 16 |

| 電気的特性—I <sup>2</sup> C シリアル・インターフェース | 16 |

| 標準動作特性                               | 19 |

| ピン配置                                 | 28 |

| MAX77542                             | 28 |

| 端子説明                                 | 28 |

| 詳細—トップ・レベル                           | 31 |

| チップ・イネーブル (CE) および内部バイアス電源           | 31 |

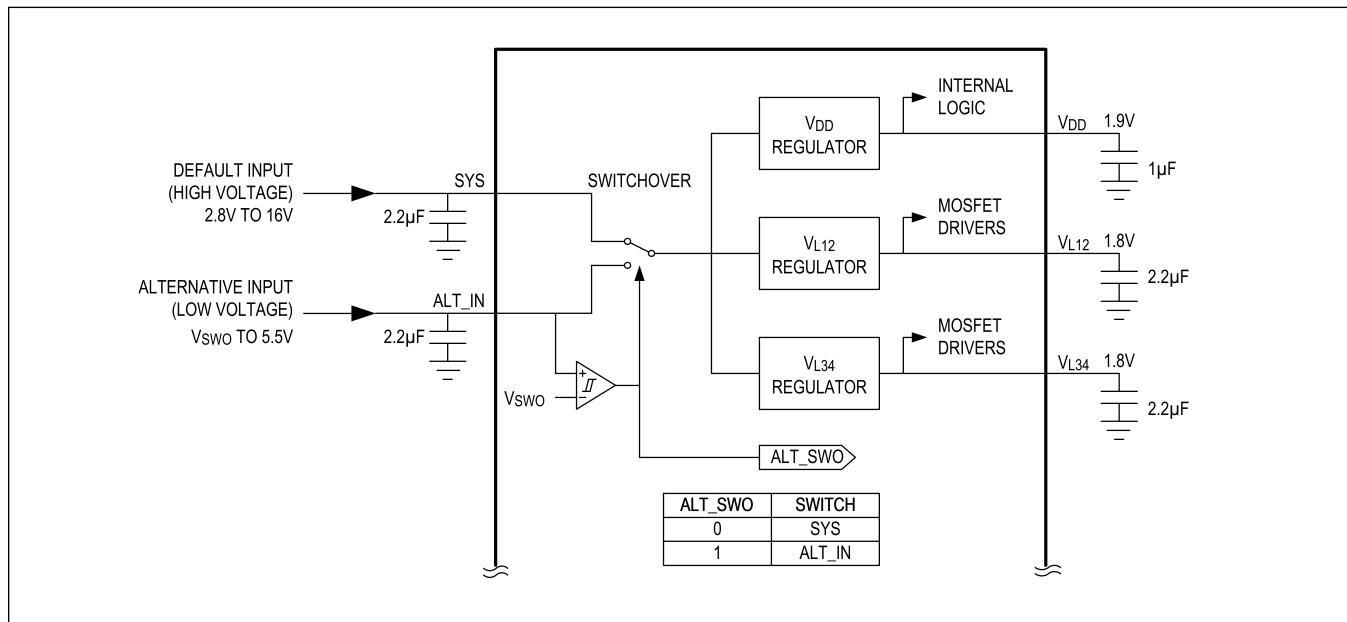

| 低電圧の代替入力 (ALT_IN)                    | 31 |

| デバイスの設定 (CFGx)                       | 32 |

| 出力イネーブル制御                            | 35 |

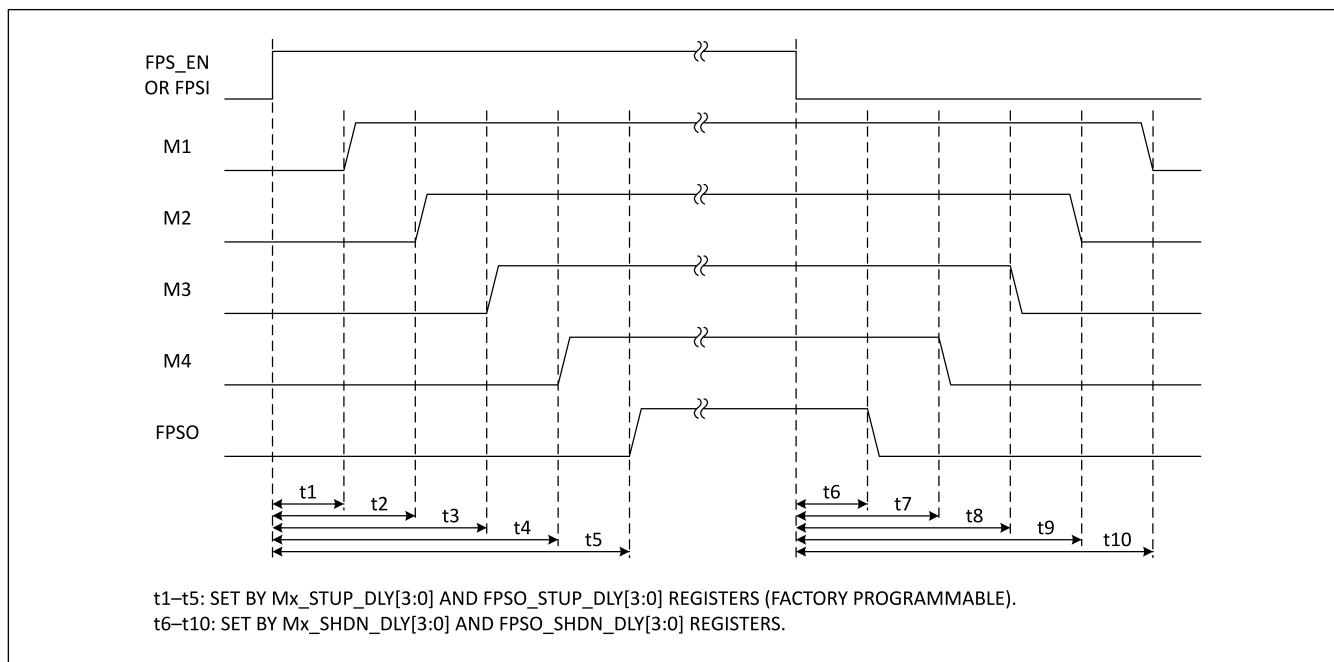

| フレキシブル・パワー・シーケンサ (FPS)               | 35 |

| 低電圧ロックアウト (UVLO)                     | 36 |

| V <sub>IO</sub> のフォルト                | 36 |

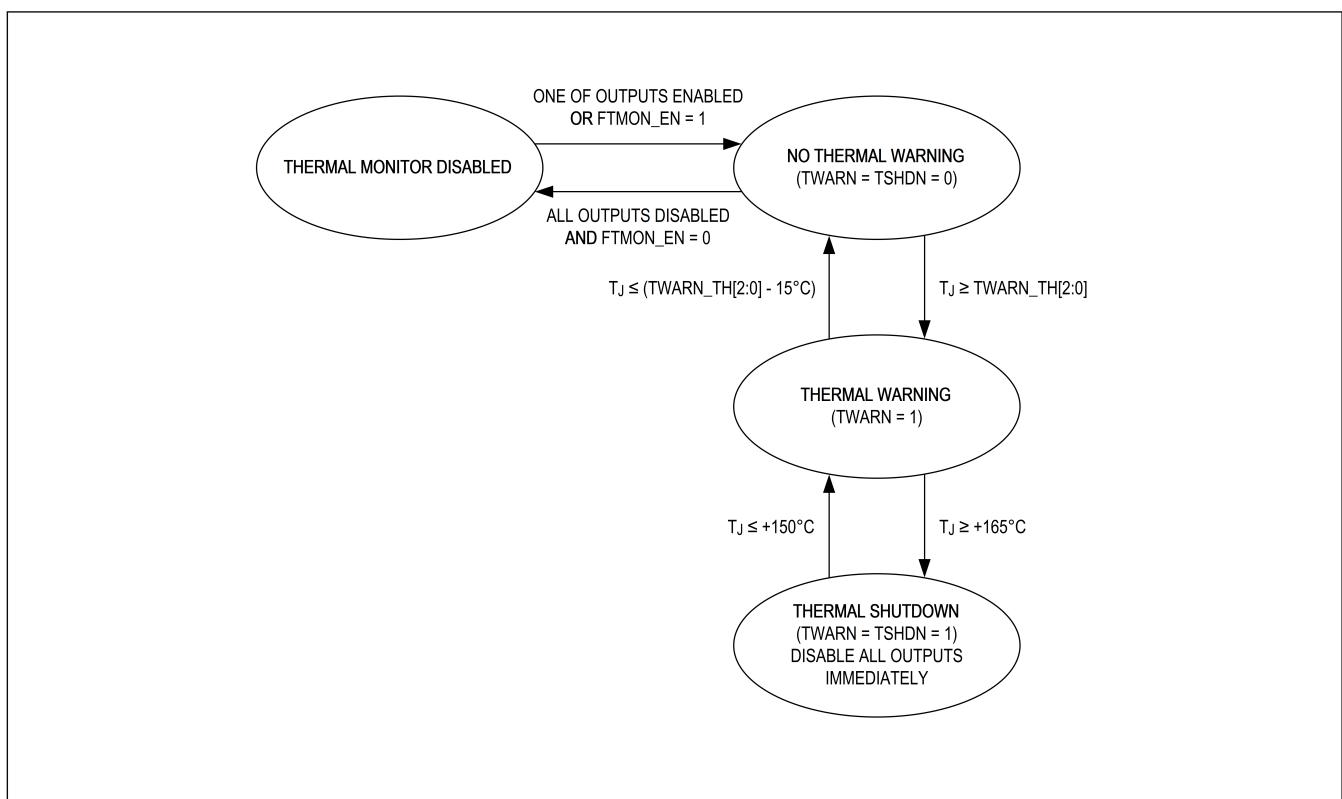

| 過熱警告およびサーマル・シャットダウン (TSHDN)          | 36 |

| リセット入出力                              | 37 |

| 割込み (IRQB)、マスクおよびステータス               | 37 |

| レジスタのリセット条件                          | 38 |

| 出荷時のオプション                            | 38 |

| 詳細—4 相構成の設定が可能な降圧コンバータ               | 39 |

| 降圧コンバータの制御方式                         | 39 |

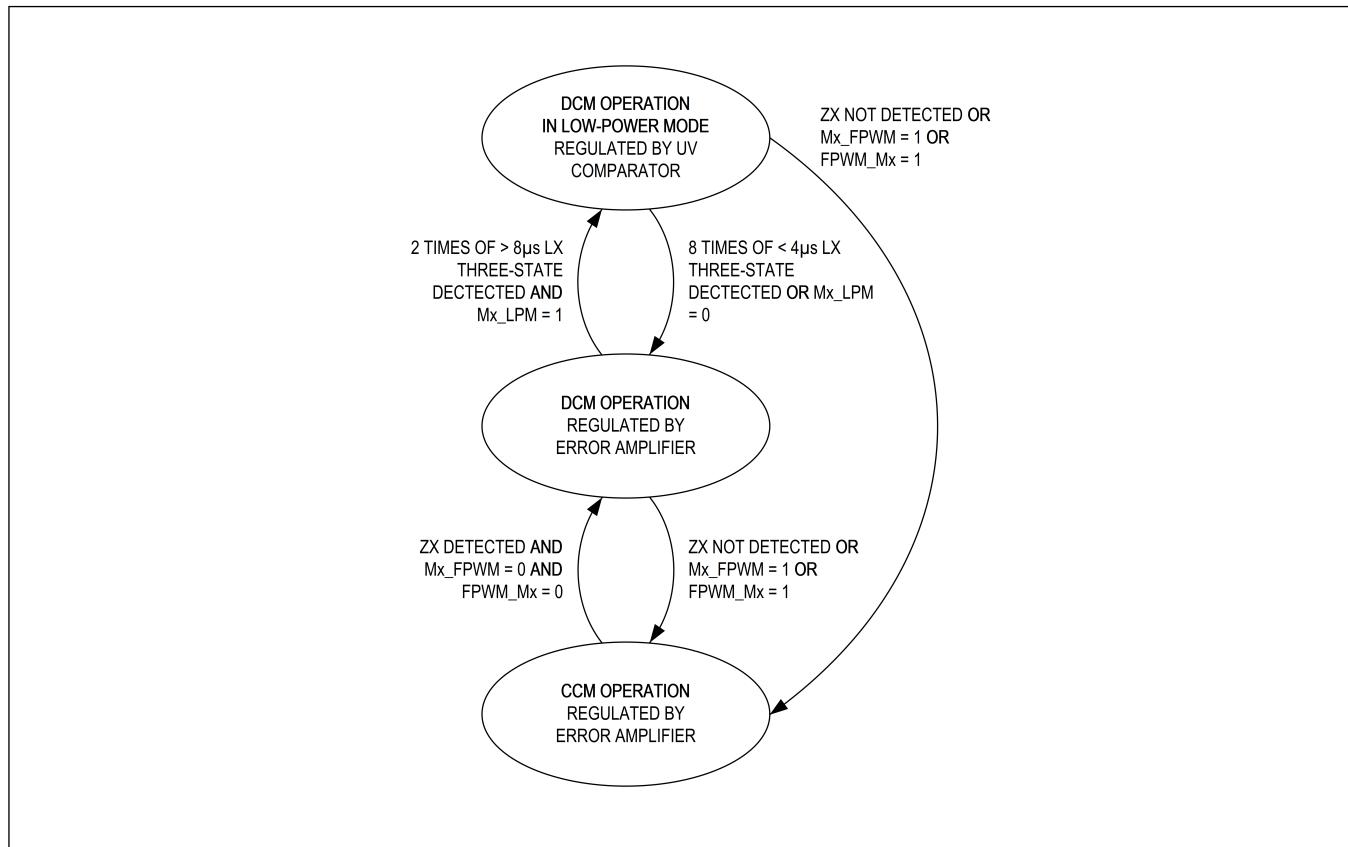

| 降圧動作モード                              | 40 |

| スキップ・モード                             | 40 |

| 低消費電力スキップ (LP-Skip) モード              | 41 |

| 強制 PWM (FPWM) モード                    | 41 |

| ドロップアウト・モード                          | 41 |

| スイッチング周波数                            | 41 |

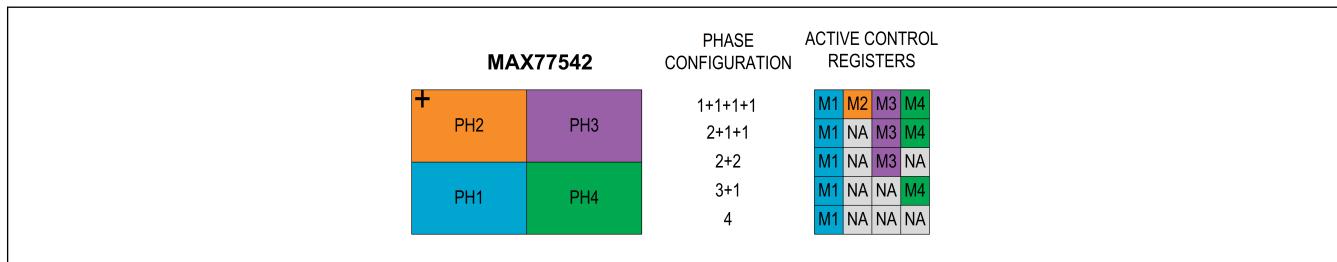

| 位相と出力の構成                             | 42 |

## 目次 (続き)

|                                |    |

|--------------------------------|----|

| デフォルト出力電圧の選択 (SELx) .....      | 43 |

| 出力電圧の設定 .....                  | 45 |

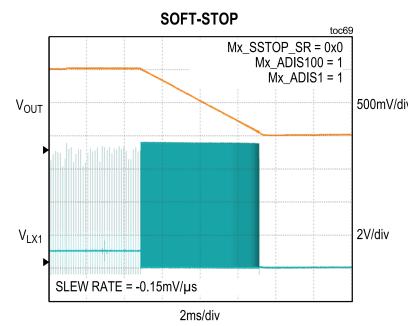

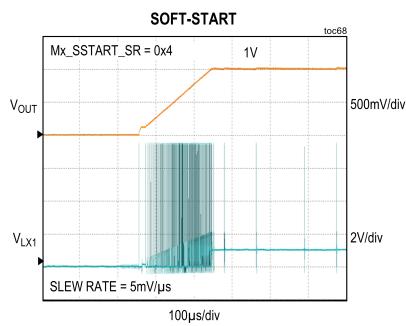

| ソフトスタートとソフトストップ .....          | 45 |

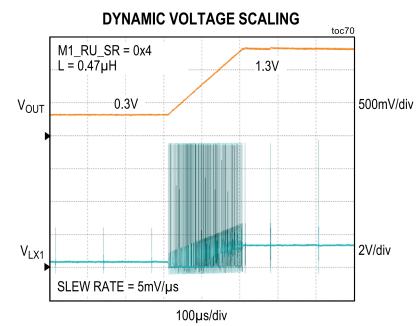

| ダイナミック出力電圧スケーリング .....         | 46 |

| 出力電圧のアクティブ放電 .....             | 46 |

| ブートストラップ・リフレッシュ .....          | 46 |

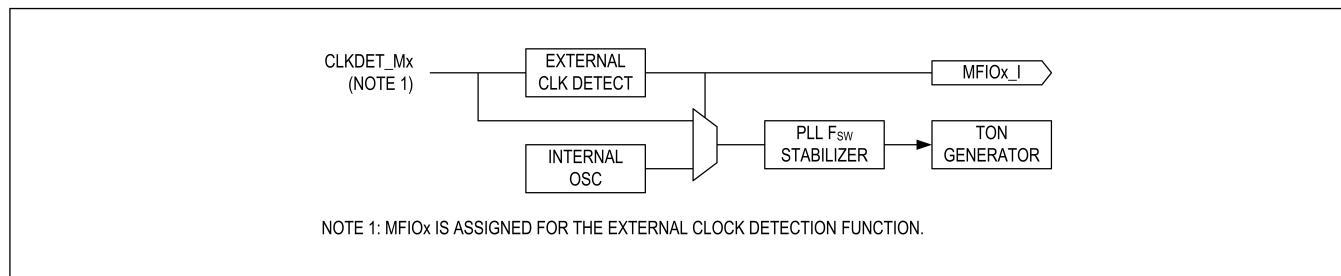

| 周波数トラッキング (FTRAK) .....        | 47 |

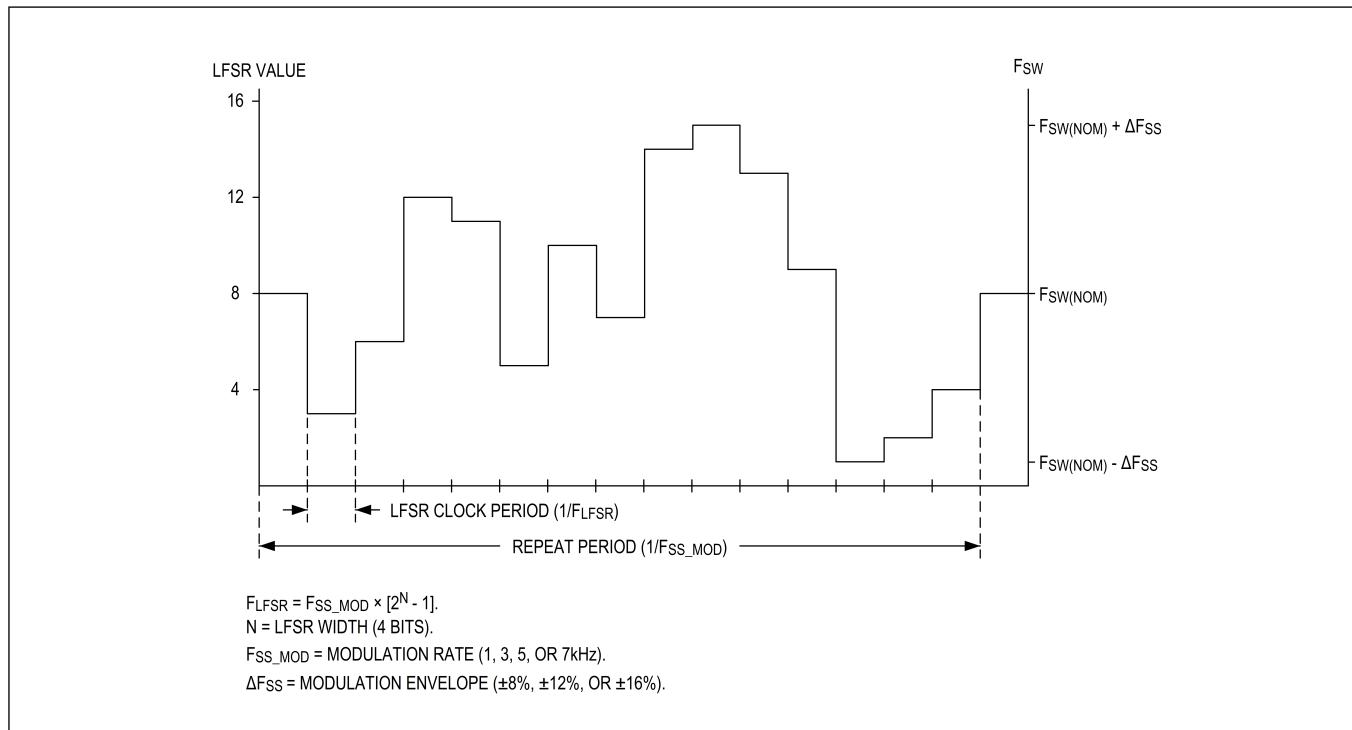

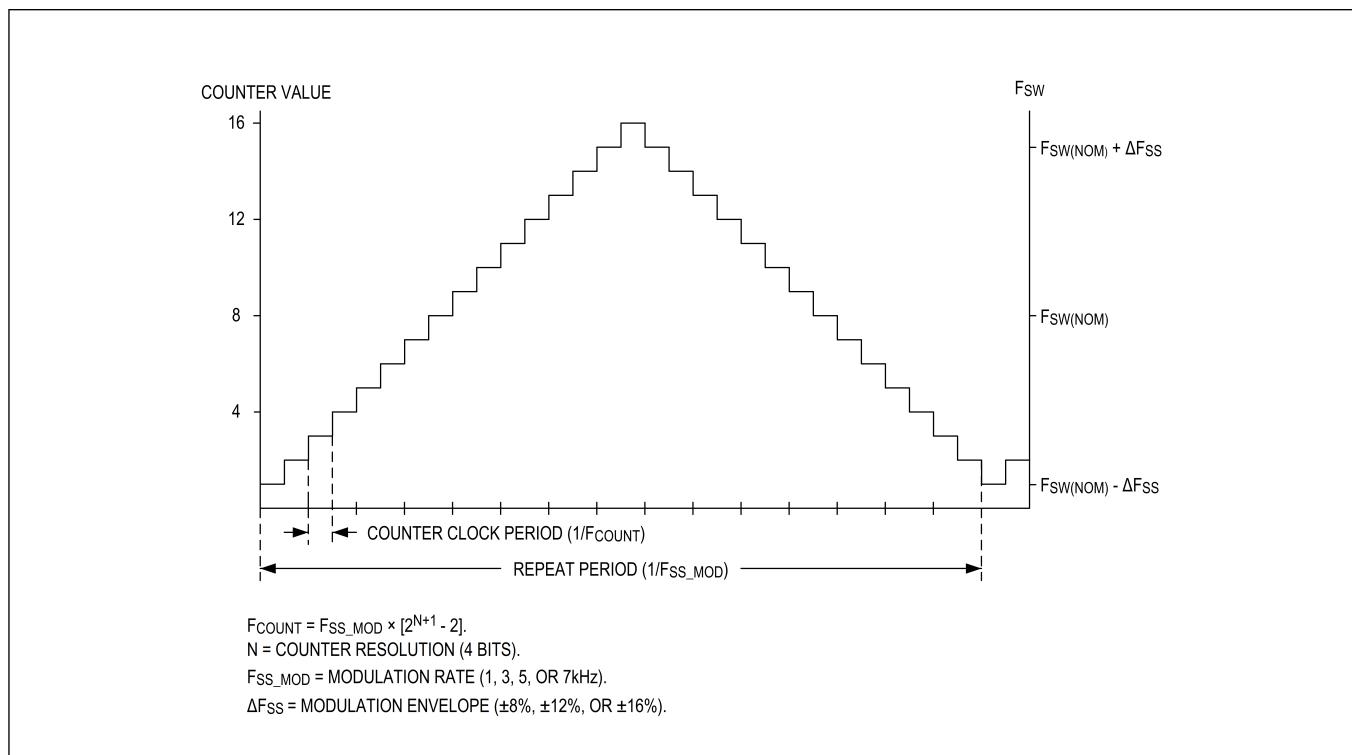

| スペクトラム拡散変調 .....               | 48 |

| 擬似乱数パターン .....                 | 48 |

| 三角波パターン .....                  | 49 |

| インダクタ電流制限値 .....               | 50 |

| パワーOK (POK) .....              | 50 |

| フォルト保護 .....                   | 50 |

| 詳細—多機能 I/O .....               | 52 |

| MFIO の機能 .....                 | 53 |

| 出力イネーブル (EN) .....             | 54 |

| 低消費電力モード (LPM) .....           | 54 |

| FPWM モード (FPWM) .....          | 54 |

| 外部クロック検出 (CLKDET) .....        | 54 |

| クロック出力 (CLKOUT) .....          | 54 |

| 出力電圧の選択 (VSEL) .....           | 54 |

| ブート (デフォルト) 出力電圧の選択 (VB) ..... | 54 |

| パワーOK (POK) 出力 .....           | 55 |

| FPS 入力 (FPSI) .....            | 55 |

| FPS 出力 (FPSO) .....            | 55 |

| システム・リセット入力 (RSTINB) .....     | 55 |

| システム・リセット出力 (RSTOB) .....      | 55 |

| 過熱警告出力 (TWARNB) .....          | 55 |

| 汎用入力 (GPI) .....               | 55 |

| 汎用出力 (GPO) .....               | 55 |

| ADC マルチプレクサ入力 (ADCMUX) .....   | 56 |

| バランス防止タイマー .....               | 56 |

| 内部プルダウン抵抗およびプルアップ抵抗 .....      | 56 |

| 出力ドライバ・モード .....               | 56 |

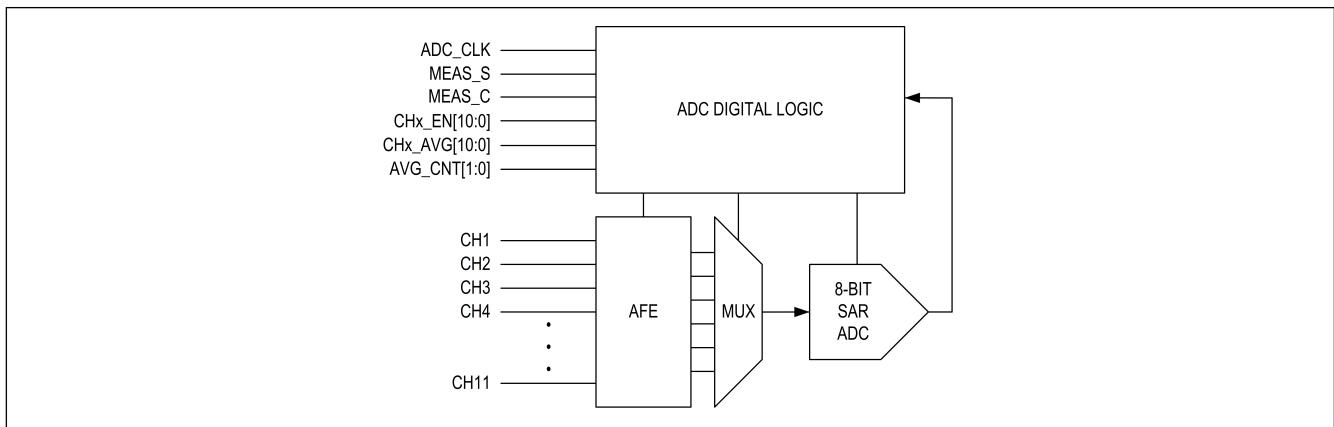

| 詳細—ADC .....                   | 56 |

| ADC のイネーブルおよび測定オプション .....     | 57 |

| 出力電流の測定 .....                  | 58 |

| 出力電圧の測定 .....                  | 58 |

| SYS 電圧の測定 .....                | 58 |

## 目次 (続き)

|                                  |     |

|----------------------------------|-----|

| ジャンクション温度の測定                     | 58  |

| 外部電圧の測定                          | 58  |

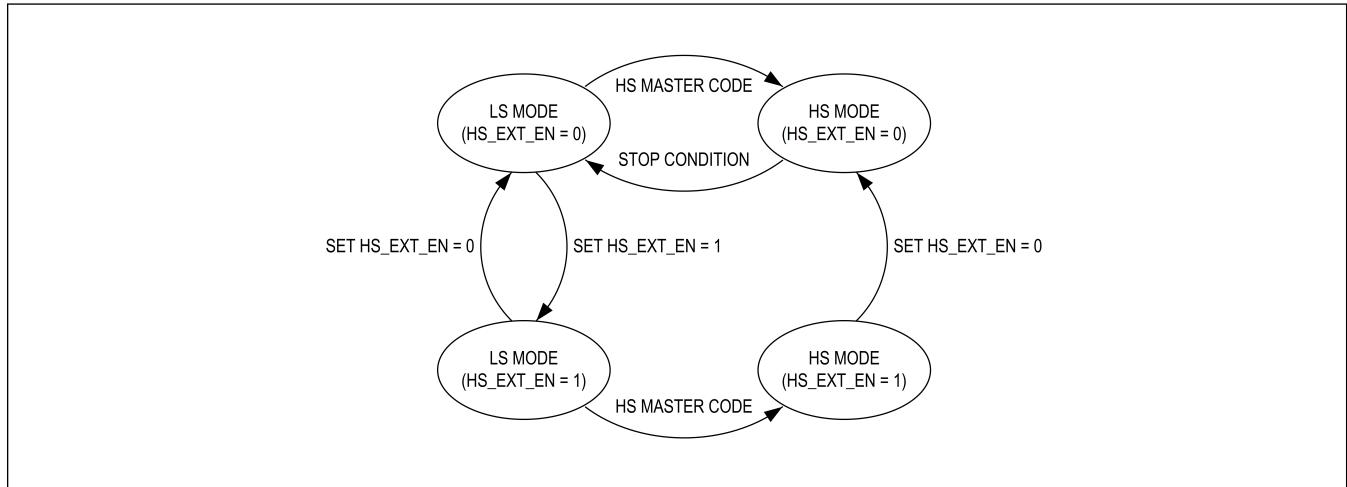

| 詳細—I <sup>2</sup> Cシリアル・インターフェース | 58  |

| スレーブ・アドレス                        | 58  |

| HS拡張モード                          | 59  |

| I <sup>2</sup> Cウォッチドッグ・タイマー     | 59  |

| レジスタ・マップ                         | 60  |

| MAX77542                         | 60  |

| レジスタの詳細                          | 63  |

| アプリケーション情報—4相構成の設定が可能な降圧コンバータ    | 113 |

| インダクタの選択                         | 113 |

| 入力コンデンサの選択                       | 113 |

| 出力コンデンサの選択                       | 113 |

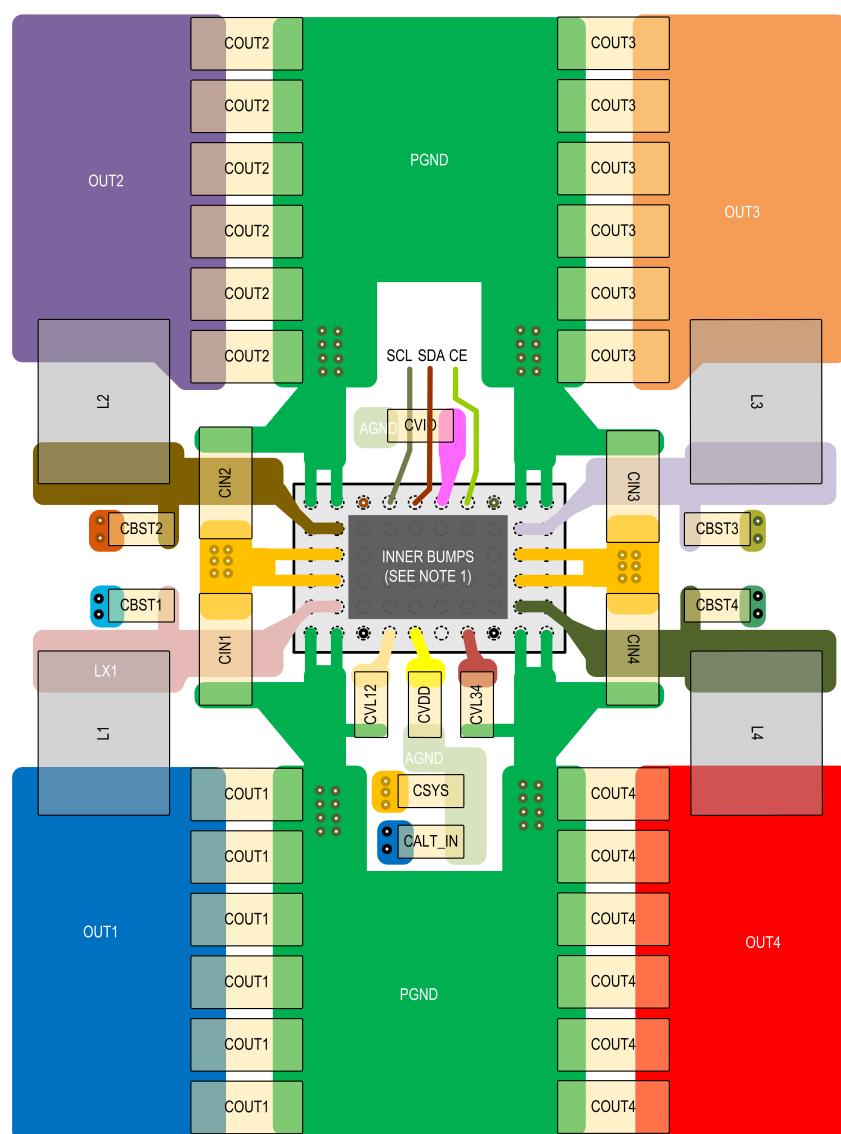

| PCBレイアウト時の一般的なガイドライン             | 114 |

| 不使用の出力                           | 115 |

| 標準アプリケーション回路                     | 116 |

| 1+1+1+1相構成                       | 116 |

| 2+1+1相構成                         | 117 |

| 2+2相構成                           | 118 |

| 3+1相構成                           | 119 |

| 4相構成                             | 120 |

| オーダー情報                           | 121 |

| 改訂履歴                             | 122 |

## 図一覧

|                                    |     |

|------------------------------------|-----|

| 図 1. 代替入力によるスイッチオーバー回路             | 32  |

| 図 2. 代表的なスタートアップおよびシャットダウン・シーケンス   | 36  |

| 図 3. 過熱警告およびサーマル・シャットダウン           | 37  |

| 図 4. 機能ブロック図                       | 39  |

| 図 5. 降圧動作モード                       | 40  |

| 図 6. アクティブ・コントロール・レジスタ             | 43  |

| 図 7. 周波数トラッキング                     | 47  |

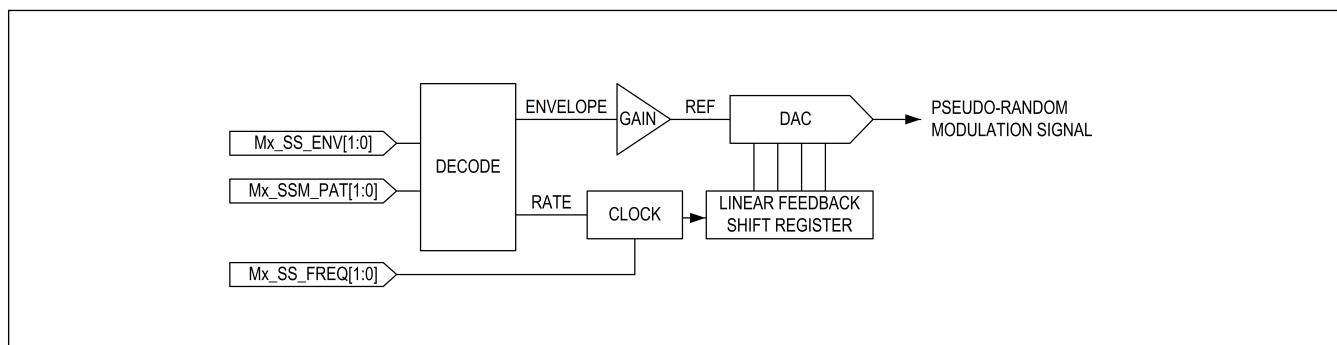

| 図 8. 擬似乱数変調エンジン                    | 48  |

| 図 9. 4 ビットの擬似乱数変調信号の例              | 49  |

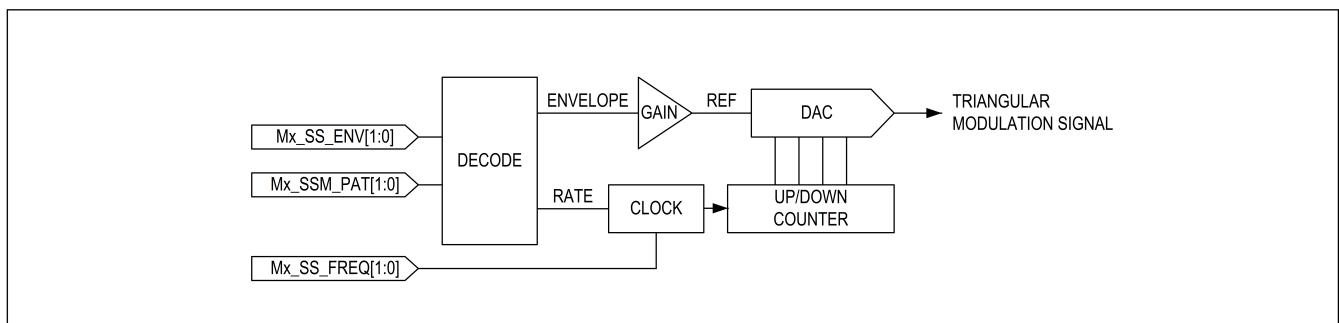

| 図 10. 三角波変調エンジン                    | 49  |

| 図 11. 4 ビットの三角波変調信号の例              | 50  |

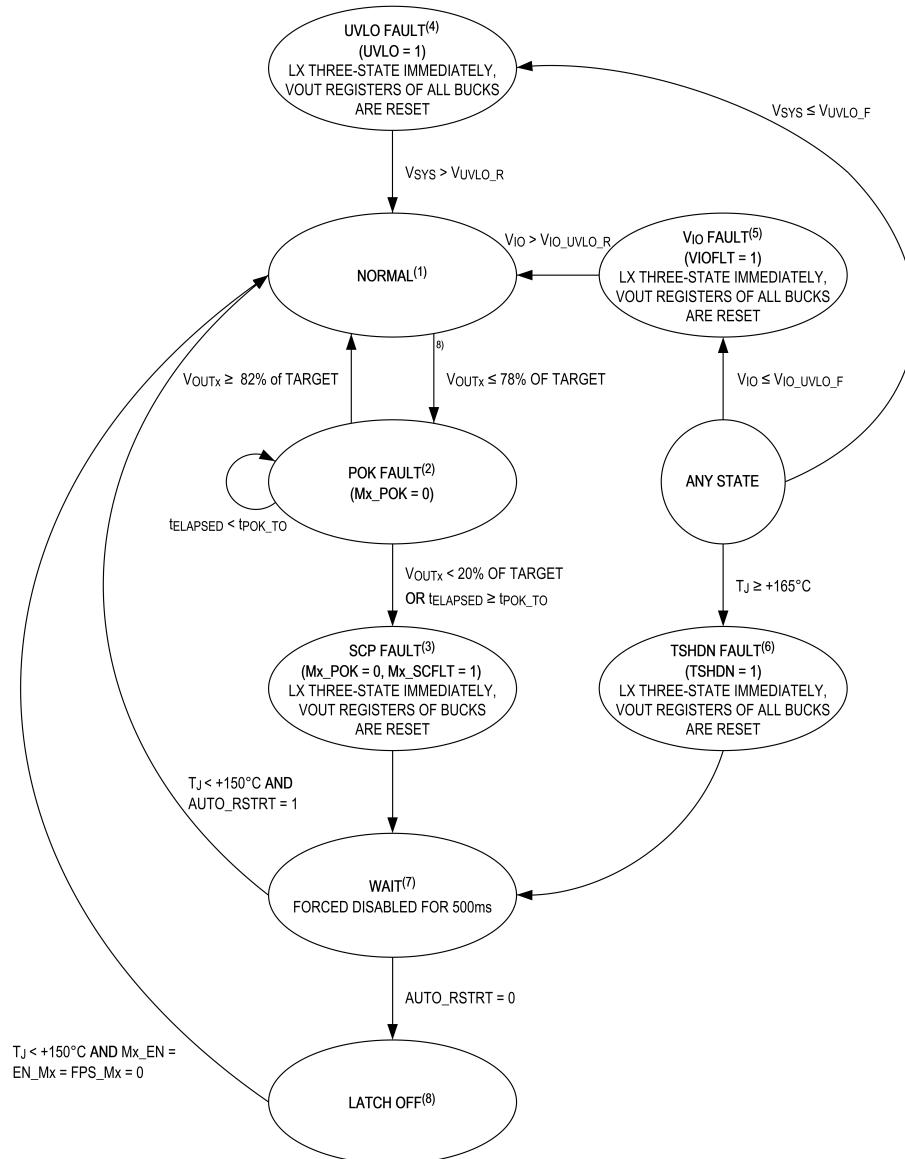

| 図 12. フォルト保護のステート図                 | 52  |

| 図 13. ADC ブロック図                    | 57  |

| 図 14. I <sup>2</sup> C 動作モードのステート図 | 59  |

| 図 15. PCB レイアウトの例                  | 115 |

## 表一覧

|                                                            |     |

|------------------------------------------------------------|-----|

| 表 1. V <sub>DD</sub> および I <sup>2</sup> C イネーブルの真理値表 ..... | 31  |

| 表 2. R <sub>CFG1</sub> によるデバイスの設定 .....                    | 32  |

| 表 3. R <sub>CFG2</sub> によるデバイスの設定 .....                    | 34  |

| 表 4. 工場出荷時に設定される MAX77542 のデフォルト値 (OTP オプション) .....        | 38  |

| 表 5. 位相構成の選択 .....                                         | 42  |

| 表 6. 降圧出力電圧検出の割り当て .....                                   | 42  |

| 表 7. デフォルト V <sub>OUT1</sub> の選択 .....                     | 43  |

| 表 8. デフォルト V <sub>OUT2/3/4</sub> の選択 .....                 | 44  |

| 表 9. 降圧出力電圧範囲 .....                                        | 45  |

| 表 10. M <sub>x</sub> _FSREN による降圧動作の設定 .....               | 46  |

| 表 11. ブートストラップ・リフレッシュ間隔の選択 .....                           | 46  |

| 表 12. M <sub>x</sub> _FTRAK イネーブルの真理値表 .....               | 47  |

| 表 13. 位相シーケンス .....                                        | 47  |

| 表 14. MFIO の機能 .....                                       | 53  |

| 表 15. MFIO I/O の選択 .....                                   | 53  |

| 表 16. バウンス防止タイマーの設定 .....                                  | 56  |

| 表 17. 内部抵抗の設定 .....                                        | 56  |

| 表 18. ADC 機能および測定範囲 .....                                  | 57  |

| 表 19. 推奨インダクタ .....                                        | 113 |

| 表 20. 推奨される実効出力容量の最小値 .....                                | 113 |

### 絶対最大定格

|                                                 |                                            |

|-------------------------------------------------|--------------------------------------------|

| SYS~AGND                                        | -0.3V~+17.6V                               |

| ALT_IN~AGND                                     | -0.3V~+6.0V                                |

| V <sub>DD</sub> ~AGND                           | -0.3V~+2.2V                                |

| V <sub>L12</sub> , V <sub>L34</sub> ~AGND, PGND | -0.3V~+2.2V                                |

| CE~AGND                                         | -0.3V~min (V <sub>SYS</sub> + 0.3, +17.6)V |

| CFGx~AGND                                       | -0.3V~min (V <sub>DD</sub> + 0.3, +2.2)V   |

| SELx~AGND                                       | -0.3V~min (V <sub>DD</sub> + 0.3, +2.2)V   |

| INx~PGNDx, AGND                                 | -0.3V~+17.6V                               |

| LXx~PGNDx                                       | -0.3V~+17.6V                               |

| LXx~PGNDx (10ns 未満)                             | (V <sub>IN</sub> - 22)V to +22V            |

| BSTx~LXx                                        | -0.3V~+2.2V                                |

| SNSxP~AGND                                      | -0.3V~+12.0V                               |

|                                           |                                          |

|-------------------------------------------|------------------------------------------|

| SNSxN~AGND                                | -0.3V~+0.3V                              |

| PGNDx~AGND                                | -0.3V~+0.3V                              |

| V <sub>IO</sub> ~AGND                     | -0.3V~+2.2V                              |

| SCL~AGND                                  | -0.3V~+2.2V                              |

| SDA~AGND                                  | -0.3V~+2.2V                              |

| IRQB~AGND                                 | -0.3V~+2.2V                              |

| MFIOx~AGND                                | -0.3V~min (V <sub>IO</sub> + 0.3, +2.2)V |

| 連続消費電力 (JESD51-7, T <sub>A</sub> = +70°C) |                                          |

| 60 WLP (+70°C を超えると 25.4mW/°C で劣化)        | 2037mW                                   |

| ジャンクション温度                                 | +150°C                                   |

| 保存温度範囲                                    | -65°C~+150°C                             |

| ハンダ処理温度 (リフロー)                            | +260°C                                   |

Note 1 : 各 LXx には、PGNDx および INx との間に内部クランプダイオードが接続されています。これらのダイオードに順方向バイアスをかけるアプリケーションでは、IC パッケージの消費電力制限値を超えないように注意してください。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### 推奨動作条件

| PARAMETER                  | SYMBOL           | CONDITION                                                                                                                                                                                                       | TYPICAL RANGE | UNIT |

|----------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|

| Input Voltage Range        | V <sub>IN</sub>  |                                                                                                                                                                                                                 | 2.8 to 16     | V    |

| Output Current Range       | I <sub>OUT</sub> | For continuous operation at 4A, the junction temperature (T <sub>J</sub> ) is limited to +120°C; if the junction temperature is higher than +120°C, the expected lifetime at 4A continuous operation is derated | 0 to 4        | A    |

| Junction Temperature Range | T <sub>J</sub>   |                                                                                                                                                                                                                 | -40 to +125   | °C   |

Note : これらの条件範囲は保証値ではありません。

### パッケージ情報

#### 60 WLP (厚い UBM)

|                                       |                                       |

|---------------------------------------|---------------------------------------|

| Packkage Code                         | W602A4Z+1                             |

| Outline Number                        | <a href="#">21-100610</a>             |

| Land Pattern Number                   | <a href="#">Application Note 1891</a> |

| Thermal Resistance, Four-Layer Board: |                                       |

| Junction-to-Ambient ( $\theta_{JA}$ ) | 39.27°C/W                             |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、[www.maximintegrated.com/packages](http://www.maximintegrated.com/packages) で確認してください。パッケージ・コードの「+」、「#」、「-」はRoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面はRoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、[www.maxim-ic.com/thermal-tutorial](http://www.maxim-ic.com/thermal-tutorial) を参照してください。

## 電気的特性-トップ・レベル

(特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 0.8V (M1\_RNG = 0x0)、V<sub>OUT2</sub> = 1.1V (M2\_RNG = 0x1)、V<sub>OUT3</sub> = 1.8V (M3\_RNG = 0x1)、V<sub>OUT4</sub> = 3.3V (M4\_RNG = 0x2)、単相の構成、V<sub>CE</sub> = 1.8V、V<sub>IO</sub> = 1.8V、T<sub>A</sub> = T<sub>J</sub> = -40°C ~ +125°C、代表値はT<sub>A</sub> = T<sub>J</sub> = +25°Cでの値です。Note 2。)

| PARAMETER                                                        | SYMBOL                              | CONDITIONS                                                                                                                              | MIN                            | TYP  | MAX | UNITS |

|------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|-----|-------|

| <b>INPUT VOLTAGE AND SUPPLY CURRENT</b>                          |                                     |                                                                                                                                         |                                |      |     |       |

| SYS and INx Voltage Range                                        | V <sub>SYS</sub> , V <sub>INx</sub> |                                                                                                                                         | 2.8                            | 16   |     | V     |

| SYS Undervoltage Lock-Out (UVLO)                                 | V <sub>UVLO_R</sub>                 | V <sub>SYS</sub> rising                                                                                                                 | 2.8                            | 2.9  | 3.0 | V     |

|                                                                  | V <sub>UVLO_F</sub>                 | V <sub>SYS</sub> falling with 200mV of hysteresis                                                                                       | 2.6                            | 2.7  | 2.8 |       |

| Power-On Reset (POR) Threshold (Note 7)                          | V <sub>POR</sub>                    | V <sub>SYS</sub> falling                                                                                                                |                                | 1.7  |     | V     |

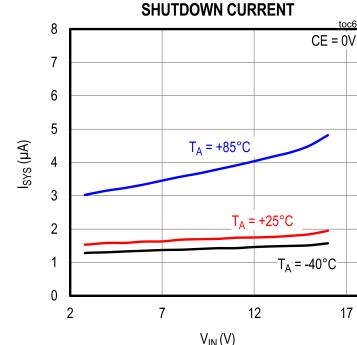

| Shutdown Supply Current (Note 3)                                 | I <sub>SHDN</sub>                   | V <sub>CE</sub> = 0V, T <sub>J</sub> = -40°C to +85°C                                                                                   |                                | 1.5  | 15  | μA    |

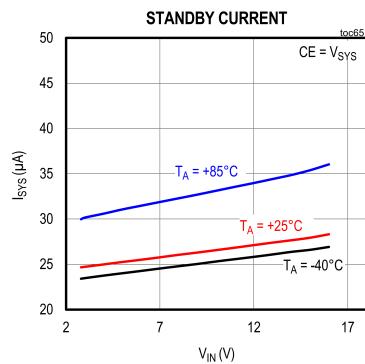

| Standby Supply Current (Note 3)                                  | I <sub>STBY</sub>                   | FTMON_EN = 0, all bucks are disabled, T <sub>J</sub> = -40°C to +85°C                                                                   |                                | 25   | 60  | μA    |

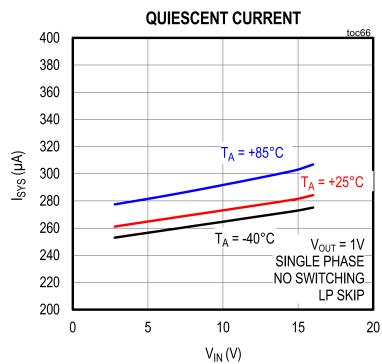

| Quiescent Supply Current in LP-Skip Mode (Note 3)                | I <sub>Q_LP-SKIP</sub>              | V <sub>ALT_IN</sub> = 0V, V <sub>OUT</sub> > V <sub>OUT(TARGET)</sub> , no load                                                         | Only one buck phase is enabled | 270  | 370 | μA    |

|                                                                  |                                     |                                                                                                                                         | Two buck phases are enabled    | 380  | 480 |       |

|                                                                  |                                     |                                                                                                                                         | Three buck phases are enabled  | 505  | 635 |       |

|                                                                  |                                     |                                                                                                                                         | All buck phases are enabled    | 625  | 755 |       |

| Quiescent Supply Current in Skip Mode (Note 3)                   | I <sub>Q_SKIP</sub>                 | V <sub>ALT_IN</sub> = 0V, V <sub>OUT</sub> > V <sub>OUT(TARGET)</sub> , no load                                                         | Only one buck phase is enabled | 300  | 405 | μA    |

|                                                                  |                                     |                                                                                                                                         | Two buck phases are enabled    | 450  | 555 |       |

|                                                                  |                                     |                                                                                                                                         | Three buck phases are enabled  | 620  | 750 |       |

|                                                                  |                                     |                                                                                                                                         | All buck phases are enabled    | 780  | 910 |       |

| <b>INTERNAL BIAS SUPPLY</b>                                      |                                     |                                                                                                                                         |                                |      |     |       |

| V <sub>DD</sub> Regulator Voltage                                | V <sub>DD</sub>                     |                                                                                                                                         |                                | 1.9  |     | V     |

| V <sub>DD</sub> Undervoltage Lock-Out (UVLO)                     | V <sub>DD_UVLO_F</sub>              |                                                                                                                                         |                                | 1.55 |     | V     |

| V <sub>L12</sub> , V <sub>L34</sub> Regulator Voltage            | V <sub>Lx</sub>                     |                                                                                                                                         |                                | 1.8  |     | V     |

| V <sub>L12</sub> , V <sub>L34</sub> Undervoltage Lock-Out (UVLO) | V <sub>L_UVLO_F</sub>               |                                                                                                                                         |                                | 1.55 |     | V     |

| ALT_IN Switchover Threshold                                      | V <sub>SWO</sub>                    | V <sub>ALT_IN</sub> rising, 100mV hysteresis, V <sub>L</sub> and V <sub>DD</sub> input switches from SYS to ALT_IN above this threshold | 2.7                            | 2.8  | 2.9 | V     |

| ALT_IN Valid Voltage Range                                       | V <sub>ALT_IN</sub>                 |                                                                                                                                         | V <sub>SWO</sub>               | 5.5  |     | V     |

| ALT_IN Shutdown Supply Current                                   | I <sub>ALT_IN_SHDN</sub>            | V <sub>CE</sub> = 0V, V <sub>ALT_IN</sub> = 3.3V                                                                                        |                                | 0.2  |     | μA    |

## 電気的特性-トップ・レベル (続き)

(特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 0.8V (M1\_RNG = 0x0)、V<sub>OUT2</sub> = 1.1V (M2\_RNG = 0x1)、V<sub>OUT3</sub> = 1.8V (M3\_RNG = 0x1)、V<sub>OUT4</sub> = 3.3V (M4\_RNG = 0x2)、単相の構成、V<sub>CE</sub> = 1.8V、V<sub>IO</sub> = 1.8V、T<sub>A</sub> = T<sub>J</sub> = -40°C ~ +125°C、代表値は T<sub>A</sub> = T<sub>J</sub> = +25°C での値です。Note 2。)

| PARAMETER                             | SYMBOL                | CONDITIONS                                                                                          | MIN                             | TYP  | MAX  | UNITS |

|---------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|---------------------------------|------|------|-------|

| <b>THERMAL PROTECTION</b>             |                       |                                                                                                     |                                 |      |      |       |

| Thermal Warning                       | T <sub>WARN</sub>     | T <sub>J</sub> rising, 15°C hysteresis                                                              | TWARN_TH[2:0] = 0x0             | +95  |      | °C    |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x1             | +100 |      |       |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x2             | +105 |      |       |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x3             | +110 |      |       |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x4             | +115 |      |       |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x5 (default)   | +120 |      |       |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x6             | +125 |      |       |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x7             | +130 |      |       |

| Thermal Shutdown (TSHDN)              | T <sub>SHDN</sub>     | T <sub>J</sub> rising, 15°C hysteresis                                                              |                                 | +165 |      | °C    |

| <b>FLEXIBLE POWER SEQUENCER (FPS)</b> |                       |                                                                                                     |                                 |      |      |       |

| Sequence Start Delay                  | t <sub>DLY_SEQ</sub>  | Delay from rising edge of FPS_EN signal to V <sub>OUTx</sub> ramping start-off in the 1st time slot | V <sub>Lx</sub> is enabled      | 100  |      | μs    |

| Time Slot Delay Step                  | t <sub>DLY_STEP</sub> | DLY_STEP[1:0] = 0x0                                                                                 |                                 | 0.5  |      | ms    |

|                                       |                       | DLY_STEP[1:0] = 0x1                                                                                 |                                 | 1.0  |      |       |

|                                       |                       | DLY_STEP[1:0] = 0x2                                                                                 |                                 | 2.0  |      |       |

|                                       |                       | DLY_STEP[1:0] = 0x3                                                                                 |                                 | 4.0  |      |       |

| Time Slot Accuracy                    | f <sub>OSC_ACC</sub>  | Root oscillator accuracy                                                                            |                                 | -5   | +5   | %     |

| <b>LOGIC INPUT AND OUTPUT</b>         |                       |                                                                                                     |                                 |      |      |       |

| CE Input Logic High Threshold         | V <sub>IH_CE</sub>    | CE_PD_EN = 0                                                                                        |                                 | 1.1  |      | V     |

|                                       |                       | CE_PD_EN = 1                                                                                        |                                 | 1.5  |      |       |

| CE Input Logic Low Threshold          | V <sub>IL_CE</sub>    |                                                                                                     |                                 |      | 0.4  | V     |

| IRQB Output Logic Low Threshold       | V <sub>OL_IRQB</sub>  | Sinking 2mA                                                                                         |                                 |      | 0.2  | V     |

| CE Pull-Down Current                  | I <sub>PD_CE</sub>    | CE_PD_EN = 1                                                                                        | 1.1V ≤ V <sub>CE</sub> ≤ 16V    | 0.5  | 1.7  | 4.0   |

|                                       |                       |                                                                                                     | V <sub>CE</sub> ≤ 0.4V          |      | 100  | 200   |

| CE Leakage Current                    | I <sub>LKG_CE</sub>   | V <sub>SYS</sub> = 16V, V <sub>CE</sub> = 0V and 16V, CE_PD_EN = 0                                  | T <sub>J</sub> = +25°C          |      | ±0.1 | μA    |

|                                       |                       |                                                                                                     | T <sub>J</sub> = +85°C (Note 5) |      | ±0.5 |       |

### 電気的特性-トップ・レベル (続き)

(特に指定のない限り、 $V_{SYS} = V_{INx} = 12V$ 、 $V_{OUT1} = 0.8V$  ( $M1\_RNG = 0x0$ )、 $V_{OUT2} = 1.1V$  ( $M2\_RNG = 0x1$ )、 $V_{OUT3} = 1.8V$  ( $M3\_RNG = 0x1$ )、 $V_{OUT4} = 3.3V$  ( $M4\_RNG = 0x2$ )、単相の構成、 $V_{CE} = 1.8V$ 、 $V_{IO} = 1.8V$ 、 $T_A = T_J = -40^{\circ}C \sim +125^{\circ}C$ 、代表値は  $T_A = T_J = +25^{\circ}C$  での値です。Note 2。)

| PARAMETER            | SYMBOL          | CONDITIONS                                                                          | MIN | TYP | MAX | UNITS   |

|----------------------|-----------------|-------------------------------------------------------------------------------------|-----|-----|-----|---------|

| IRQB Leakage Current | $I_{LKG\_IRQB}$ | IRQB set to high impedance (i.e., no interrupt pending), $V_{IRQB} = 0V$ and $2.0V$ | -1  |     | +1  | $\mu A$ |

### 電気的特性-4 相構成の設定が可能な降圧コンバータ

(特に指定のない限り、 $V_{SYS} = V_{INx} = 12V$ 、 $V_{OUT1} = 0.8V$  ( $M1\_RNG = 0x0$ )、 $V_{OUT2} = 1.1V$  ( $M2\_RNG = 0x1$ )、 $V_{OUT3} = 1.8V$  ( $M3\_RNG = 0x1$ )、 $V_{OUT4} = 3.3V$  ( $M4\_RNG = 0x2$ )、単相の構成、 $V_{CE} = 1.8V$ 、 $V_{IO} = 1.8V$ 、 $T_A = T_J = -40^{\circ}C \sim +125^{\circ}C$ 、代表値は  $T_A = T_J = +25^{\circ}C$  での値です。Note 2。)

| PARAMETER                             | SYMBOL         | CONDITIONS                                                                             | MIN  | TYP | MAX  | UNITS |

|---------------------------------------|----------------|----------------------------------------------------------------------------------------|------|-----|------|-------|

| <b>INPUT SUPPLY</b>                   |                |                                                                                        |      |     |      |       |

| Input-Voltage Range                   | $V_{INx}$      |                                                                                        | 2.8  |     | 16   | V     |

| <b>DC OUTPUT VOLTAGE AND ACCURACY</b> |                |                                                                                        |      |     |      |       |

| Output-Voltage Range                  | $V_{OUT\_RNG}$ | Low range ( $Mx\_RNG[1:0] = 0x0$ )                                                     | 0.3  | 1.3 |      | V     |

|                                       |                | Mid range ( $Mx\_RNG[1:0] = 0x1$ )                                                     | 0.6  | 2.6 |      |       |

|                                       |                | High range ( $Mx\_RNG[1:0] = 0x2$ )                                                    | 1.2  | 5.2 |      |       |

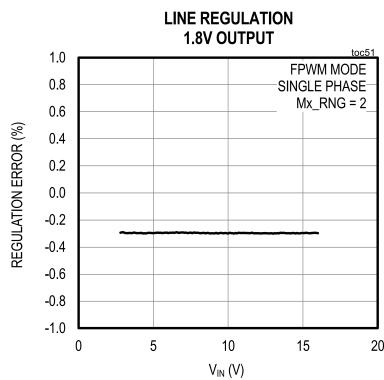

| Line Regulation                       |                | 1Φ, FPWM mode, $V_{INx} = 2.8V$ to $16V$ , $V_{OUT} = \text{default}$ , $I_{OUT} = 0A$ | -0.1 |     | +0.1 | %/V   |

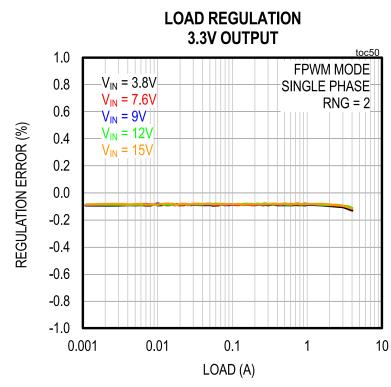

| Load Regulation                       |                | 1Φ, FPWM mode, $I_{OUT} = 0A$ to $4A$ (Note 2)                                         |      | 0.1 |      | %/A   |

## 電気的特性—4 相構成の設定が可能な降圧コンバータ（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 0.8V（M1\_RNG = 0x0）、V<sub>OUT2</sub> = 1.1V（M2\_RNG = 0x1）、V<sub>OUT3</sub> = 1.8V（M3\_RNG = 0x1）、V<sub>OUT4</sub> = 3.3V（M4\_RNG = 0x2）、単相の構成、V<sub>CE</sub> = 1.8V、V<sub>IO</sub> = 1.8V、T<sub>A</sub> = T<sub>J</sub> = -40°C ~ +125°C、代表値はT<sub>A</sub> = T<sub>J</sub> = +25°Cでの値です。Note 2。）

| PARAMETER                                       | SYMBOL               | CONDITIONS                                                                                                           | MIN                                                        | TYP                   | MAX  | UNITS |

|-------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------|------|-------|

| DC Output-Voltage Accuracy                      | V <sub>OUT_ACC</sub> | 0.3V ≤ V <sub>OUT</sub> < 0.5V (Mx_RNG = 0x0)                                                                        | -3.0                                                       |                       | +3.0 | %     |

|                                                 |                      | 0.5V ≤ V <sub>OUT</sub> < 0.8V (Mx_RNG = 0x0)                                                                        | -2.0                                                       |                       | +2.0 |       |

|                                                 |                      | 0.8V ≤ V <sub>OUT</sub> ≤ 1.3V (Mx_RNG = 0x0)                                                                        | -1.0                                                       |                       | +1.0 |       |

|                                                 |                      | 0.6V ≤ V <sub>OUT</sub> < 1.2V (Mx_RNG = 0x1)                                                                        | -3.0                                                       |                       | +3.0 |       |

|                                                 |                      | 1.2V ≤ V <sub>OUT</sub> < 1.9V (Mx_RNG = 0x1)                                                                        | -1.5                                                       |                       | +1.5 |       |

|                                                 |                      | 1.9V ≤ V <sub>OUT</sub> ≤ 2.6V (Mx_RNG = 0x1)                                                                        | -1.0                                                       |                       | +1.0 |       |

|                                                 |                      | 1.2V ≤ V <sub>OUT</sub> < 2.2V (Mx_RNG = 0x2)                                                                        | -3.0                                                       |                       | +3.0 |       |

|                                                 |                      | 2.2V ≤ V <sub>OUT</sub> < 3.6V (Mx_RNG = 0x2)                                                                        | -1.5                                                       |                       | +1.5 |       |

|                                                 |                      | 3.6V ≤ V <sub>OUT</sub> ≤ 5.2V (Mx_RNG = 0x2)                                                                        | -1.0                                                       |                       | +1.0 |       |

|                                                 |                      | 1Φ, FPWM mode, V <sub>INx</sub> = 2.8V to 16V, I <sub>OUT</sub> = 0A, T <sub>A</sub> = T <sub>J</sub> = 0°C to +85°C | V <sub>OUT</sub> = factory default, T <sub>J</sub> = +25°C | -0.5                  |      | +0.5  |

| POWER STAGE                                     |                      |                                                                                                                      |                                                            |                       |      |       |

| High-Side MOSFET Peak Current Limit             | I <sub>PLIM</sub>    | Mx_ILIM[1:0] = 0x0                                                                                                   | 3.1                                                        | 3.5                   | 3.9  | A     |

|                                                 |                      | Mx_ILIM[1:0] = 0x1                                                                                                   | 4.0                                                        | 4.5                   | 5.0  |       |

|                                                 |                      | Mx_ILIM[1:0] = 0x2                                                                                                   | 4.9                                                        | 5.5                   | 6.1  |       |

|                                                 |                      | Mx_ILIM[1:0] = 0x3                                                                                                   | 5.4                                                        | 6.0                   | 6.6  |       |

| Low-Side MOSFET Valley Current Limit            | I <sub>VLIM</sub>    | Tracks I <sub>PLIM</sub>                                                                                             |                                                            | I <sub>PLIM</sub> - 1 |      | A     |

| Low-Side MOSFET Negative Current Limit          | I <sub>NLIM</sub>    | FPWM mode                                                                                                            | -3.6                                                       | -3.0                  | -2.4 | A     |

| Low-Side MOSFET Zero-Crossing Current Threshold | I <sub>ZX</sub>      | Skip or LP-skip mode                                                                                                 |                                                            | 150                   |      | mA    |

| High-Side MOSFET On-Resistance                  | R <sub>ON_HS</sub>   | 1Φ, I <sub>LXx</sub> = 190mA                                                                                         | 35                                                         | 70                    |      | mΩ    |

## 電気的特性-4 相構成の設定が可能な降圧コンバータ（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 0.8V（M1\_RNG = 0x0）、V<sub>OUT2</sub> = 1.1V（M2\_RNG = 0x1）、V<sub>OUT3</sub> = 1.8V（M3\_RNG = 0x1）、V<sub>OUT4</sub> = 3.3V（M4\_RNG = 0x2）、単相の構成、V<sub>CE</sub> = 1.8V、V<sub>IO</sub> = 1.8V、T<sub>A</sub> = T<sub>J</sub> = -40°C ~ +125°C、代表値はT<sub>A</sub> = T<sub>J</sub> = +25°Cでの値です。Note 2。）

| PARAMETER                      | SYMBOL              | CONDITIONS                                                                                                                                           |                                          | MIN | TYP | MAX | UNITS |

|--------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| Low-Side MOSFET On-Resistance  | R <sub>ON_LS</sub>  | 1Φ, I <sub>LXX</sub> = -190mA                                                                                                                        |                                          |     | 18  | 40  | mΩ    |

| Nominal Switching Frequency    | F <sub>SW</sub>     | FPWM mode, no load, no external clock, T <sub>J</sub> = +25°C<br>(Note 4)                                                                            | M <sub>x</sub> _FREQ[1:0] = 0x0          | 0.5 |     |     | MHz   |

|                                |                     |                                                                                                                                                      | M <sub>x</sub> _FREQ[1:0] = 0x1          | 1   |     |     |       |

|                                |                     |                                                                                                                                                      | M <sub>x</sub> _FREQ[1:0] = 0x2          | 1.5 |     |     |       |

| Maximum Duty Cycle             | D <sub>MAX</sub>    | Drop-out region (V <sub>OUT</sub> falls below its regulation target)                                                                                 |                                          | 97  | 98  |     | %     |

| LX Active Discharge Resistance | R <sub>AD1</sub>    | 1Φ, buck output disabled, active discharge enabled (M <sub>x</sub> _ADIS1 = 1), resistance from corresponding LX <sub>X</sub> to PGND <sub>x</sub>   |                                          |     | 1   |     | Ω     |

|                                | R <sub>AD100</sub>  | 1Φ, buck output disabled, active discharge enabled (M <sub>x</sub> _ADIS100 = 1), resistance from corresponding LX <sub>X</sub> to PGND <sub>x</sub> |                                          |     | 100 |     |       |

| LX Leakage Current             | I <sub>LX_LKG</sub> | 1Φ, V <sub>LXX</sub> = 0V or 16V, M <sub>x</sub> _ADIS100 = 0                                                                                        | T <sub>J</sub> = +25°C                   | 1   | 15  |     | μA    |

|                                |                     |                                                                                                                                                      | T <sub>J</sub> = -40°C to +85°C (Note 5) | 1   |     |     |       |

## SLEW RATE AND TIMING

|                                  |                       |                                      |        |       |

|----------------------------------|-----------------------|--------------------------------------|--------|-------|

| Soft-Start Slew Rate<br>(Note 6) | ΔV <sub>OUT</sub> /Δt | M <sub>x</sub> _SSTART_SR[2:0] = 0x0 | 0.15   | mV/μs |

|                                  |                       | M <sub>x</sub> _SSTART_SR[2:0] = 0x1 | 0.625  |       |

|                                  |                       | M <sub>x</sub> _SSTART_SR[2:0] = 0x2 | 1.25   |       |

|                                  |                       | M <sub>x</sub> _SSTART_SR[2:0] = 0x3 | 2.5    |       |

|                                  |                       | M <sub>x</sub> _SSTART_SR[2:0] = 0x4 | 5      |       |

|                                  |                       | M <sub>x</sub> _SSTART_SR[2:0] = 0x5 | 10     |       |

|                                  |                       | M <sub>x</sub> _SSTART_SR[2:0] = 0x6 | 20     |       |

|                                  |                       | M <sub>x</sub> _SSTART_SR[2:0] = 0x7 | 40     |       |

| Soft-Stop Slew Rate<br>(Note 6)  | ΔV <sub>OUT</sub> /Δt | M <sub>x</sub> _SSTOP_SR[2:0] = 0x0  | -0.15  | mV/μs |

|                                  |                       | M <sub>x</sub> _SSTOP_SR[2:0] = 0x1  | -0.625 |       |

|                                  |                       | M <sub>x</sub> _SSTOP_SR[2:0] = 0x2  | -1.25  |       |

|                                  |                       | M <sub>x</sub> _SSTOP_SR[2:0] = 0x3  | -2.5   |       |

|                                  |                       | M <sub>x</sub> _SSTOP_SR[2:0] = 0x4  | -5     |       |

|                                  |                       | M <sub>x</sub> _SSTOP_SR[2:0] = 0x5  | -10    |       |

|                                  |                       | M <sub>x</sub> _SSTOP_SR[2:0] = 0x6  | -20    |       |

|                                  |                       | M <sub>x</sub> _SSTOP_SR[2:0] = 0x7  | -40    |       |

## 電気的特性-4 相構成の設定が可能な降圧コンバータ（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 0.8V（M1\_RNG = 0x0）、V<sub>OUT2</sub> = 1.1V（M2\_RNG = 0x1）、V<sub>OUT3</sub> = 1.8V（M3\_RNG = 0x1）、V<sub>OUT4</sub> = 3.3V（M4\_RNG = 0x2）、単相の構成、V<sub>CE</sub> = 1.8V、V<sub>IO</sub> = 1.8V、T<sub>A</sub> = T<sub>J</sub> = -40°C ~ +125°C、代表値はT<sub>A</sub> = T<sub>J</sub> = +25°Cでの値です。Note 2。）

| PARAMETER                                           | SYMBOL                    | CONDITIONS                                                                            |                                    | MIN    | TYP | MAX | UNITS |

|-----------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------|------------------------------------|--------|-----|-----|-------|

| Ramp-Up Slew Rate<br>(Note 6)                       | $\Delta V_{OUT}/\Delta t$ | Mx_RU_SR[2:0] = 0x0                                                                   |                                    | 0.15   |     |     | mV/μs |

|                                                     |                           | Mx_RU_SR[2:0] = 0x1                                                                   |                                    | 0.625  |     |     |       |

|                                                     |                           | Mx_RU_SR[2:0] = 0x2                                                                   |                                    | 1.25   |     |     |       |

|                                                     |                           | Mx_RU_SR[2:0] = 0x3                                                                   |                                    | 2.5    |     |     |       |

|                                                     |                           | Mx_RU_SR[2:0] = 0x4                                                                   |                                    | 5      |     |     |       |

|                                                     |                           | Mx_RU_SR[2:0] = 0x5                                                                   |                                    | 10     |     |     |       |

|                                                     |                           | Mx_RU_SR[2:0] = 0x6                                                                   |                                    | 20     |     |     |       |

|                                                     |                           | Mx_RU_SR[2:0] = 0x7                                                                   |                                    | 40     |     |     |       |

| Ramp-Down Slew Rate<br>(Note 6)                     | $\Delta V_{OUT}/\Delta t$ | Mx_RD_SR[2:0] = 0x0                                                                   |                                    | -0.15  |     |     | mV/μs |

|                                                     |                           | Mx_RD_SR[2:0] = 0x1                                                                   |                                    | -0.625 |     |     |       |

|                                                     |                           | Mx_RD_SR[2:0] = 0x2                                                                   |                                    | -1.25  |     |     |       |

|                                                     |                           | Mx_RD_SR[2:0] = 0x3                                                                   |                                    | -2.5   |     |     |       |

|                                                     |                           | Mx_RD_SR[2:0] = 0x4                                                                   |                                    | -5     |     |     |       |

|                                                     |                           | Mx_RD_SR[2:0] = 0x5                                                                   |                                    | -10    |     |     |       |

|                                                     |                           | Mx_RD_SR[2:0] = 0x6                                                                   |                                    | -20    |     |     |       |

|                                                     |                           | Mx_RD_SR[2:0] = 0x7                                                                   |                                    | -40    |     |     |       |

| Slew-Rate Accuracy                                  |                           | REFDAC slew-rate accuracy                                                             |                                    | -5     |     | +5  | %     |

| Turn-On Delay                                       | t <sub>DLY</sub>          | Delay from rising edge of EN_Mx (MFIOx) signal to V <sub>OUTx</sub> ramping start-off | V <sub>LX</sub> is pre-enabled     | 90     | 110 |     | μs    |

|                                                     |                           |                                                                                       | V <sub>LX</sub> is not pre-enabled | 110    | 150 |     |       |

| <b>FREQUENCY TRACKING</b>                           |                           |                                                                                       |                                    |        |     |     |       |

| External Frequency Tracking Lockable Range (Note 6) | F <sub>FFTRAK</sub>       | Expressed as a percentage of the nominal frequency set by Mx_FREQ[1:0]                |                                    | 95     | 105 |     | %     |

| <b>SPREAD-SPECTRUM</b>                              |                           |                                                                                       |                                    |        |     |     |       |

| Modulation Frequency (Note 6)                       | F <sub>SS_MOD</sub>       | Mx_SS_FREQ[1:0] = 0x0                                                                 |                                    | 1      |     |     | kHz   |

|                                                     |                           | Mx_SS_FREQ[1:0] = 0x1                                                                 |                                    | 3      |     |     |       |

|                                                     |                           | Mx_SS_FREQ[1:0] = 0x2                                                                 |                                    | 5      |     |     |       |

|                                                     |                           | Mx_SS_FREQ[1:0] = 0x3                                                                 |                                    | 7      |     |     |       |

| Modulation Envelope                                 | ΔF <sub>SS</sub>          | Mx_SS_ENV[1:0] = 0x1                                                                  |                                    | ±8     |     |     | %     |

|                                                     |                           | Mx_SS_ENV[1:0] = 0x2                                                                  |                                    | ±12    |     |     |       |

|                                                     |                           | Mx_SS_ENV[1:0] = 0x3                                                                  |                                    | ±16    |     |     |       |

| <b>POWER-OK AND SHORT-CIRCUIT PROTECTION</b>        |                           |                                                                                       |                                    |        |     |     |       |

| Power-OK Rising Threshold                           | V <sub>POK_R</sub>        | Expressed as a percentage of V <sub>OUT</sub>                                         |                                    | 77     | 82  | 87  | %     |

| Power-OK Falling Threshold                          | V <sub>POK_F</sub>        | Expressed as a percentage of V <sub>OUT</sub>                                         |                                    | 73     | 78  | 83  | %     |

## 電気的特性-4 相構成の設定が可能な降圧コンバータ（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 0.8V（M1\_RNG = 0x0）、V<sub>OUT2</sub> = 1.1V（M2\_RNG = 0x1）、V<sub>OUT3</sub> = 1.8V（M3\_RNG = 0x1）、V<sub>OUT4</sub> = 3.3V（M4\_RNG = 0x2）、単相の構成、V<sub>CE</sub> = 1.8V、V<sub>IO</sub> = 1.8V、T<sub>A</sub> = T<sub>J</sub> = -40°C～+125°C、代表値はT<sub>A</sub> = T<sub>J</sub> = +25°Cでの値です。Note 2。）

| PARAMETER                         | SYMBOL           | CONDITIONS                                                                     | MIN | TYP | MAX | UNITS |

|-----------------------------------|------------------|--------------------------------------------------------------------------------|-----|-----|-----|-------|

| Power-OK Fault Time-Out (Note 6)  | tPOK_TO          | POK_TO[1:0] = 0x1                                                              |     | 1   |     | ms    |

|                                   |                  | POK_TO[1:0] = 0x2                                                              |     | 5   |     |       |

|                                   |                  | POK_TO[1:0] = 0x3                                                              |     | 10  |     |       |

| Short-Circuit Detection Threshold | V <sub>SCP</sub> | V <sub>OUT</sub> falling, expressed as a percentage of target V <sub>OUT</sub> |     | 20  |     | %     |

## 電気的特性-多機能 I/O

（特に指定のない限り、V<sub>SYS</sub> = 12V、V<sub>CE</sub> = 1.8V、V<sub>IO</sub> = 1.8V、T<sub>A</sub> = T<sub>J</sub> = -40°C～+125°C、代表値はT<sub>A</sub> = T<sub>J</sub> = +25°Cでの値です。Note 2。）

| PARAMETER                       | SYMBOL               | CONDITIONS                                         | MIN                             | TYP                    | MAX  | UNITS |    |

|---------------------------------|----------------------|----------------------------------------------------|---------------------------------|------------------------|------|-------|----|

| <b>MULTIFUNCTION I/O (MFIO)</b> |                      |                                                    |                                 |                        |      |       |    |

| MFIO Input Logic High Threshold | V <sub>IH</sub>      |                                                    | 0.75 x V <sub>IO</sub>          |                        |      | V     |    |

| MFIO Input Logic Low Threshold  | V <sub>IL</sub>      |                                                    |                                 | 0.25 x V <sub>IO</sub> |      | V     |    |

| MFIO Output High Voltage        | V <sub>OH_MFIO</sub> | Push-pull output mode, sourcing 2mA                | 0.8 x V <sub>IO</sub>           |                        |      | V     |    |

| MFIO Output Low Voltage         | V <sub>OL_MFIO</sub> | Sinking 2mA                                        |                                 | 0.2                    |      | V     |    |

| MFIO Input Debounce Time        | t <sub>DB_MFIO</sub> | MFIOx_DEB[2:0] = 0x0                               |                                 | 0                      |      | μs    |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x1                               |                                 | 0.5                    |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x2                               |                                 | 1                      |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x3                               |                                 | 2                      |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x4                               |                                 | 4                      |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x5                               |                                 | 8                      |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x6                               |                                 | 16                     |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x7                               |                                 | 32                     |      |       |    |

| MFIO Pull-Down Resistance       | R <sub>PD_MFIO</sub> | Input mode, MFIOx_PDPD = 0x0                       | 400                             | 800                    | 1600 | kΩ    |    |

|                                 |                      | Input mode, MFIOx_PDPD = 0x1                       | 50                              | 100                    | 200  |       |    |

| MFIO Pull-Up Resistance         | R <sub>PU_MFIO</sub> | Input mode, MFIOx_PDPD = 0x2                       | 50                              | 100                    | 200  | kΩ    |    |

| MFIO Leakage Current            | I <sub>LK_MFIO</sub> | V <sub>MFIOx</sub> = 0V and 2.0V, MFIOx_PDPD = 0x3 | T <sub>J</sub> = +25°C          | -1.5                   | 0.01 | 1.5   | μA |

|                                 |                      |                                                    | T <sub>J</sub> = +85°C (Note 5) |                        | 0.1  |       |    |

## 電気的特性-ADC

(特に指定のない限り、V<sub>SYS</sub> = 12V、V<sub>CE</sub> = 1.8V、V<sub>IO</sub> = 1.8V、T<sub>A</sub> = T<sub>J</sub> = -40°C～+125°C、代表値はT<sub>A</sub> = T<sub>J</sub> = +25°Cでの値です。Note 2。)

| PARAMETER                                    | SYMBOL                | CONDITIONS                                                                     |                                                           | MIN | TYP | MAX | UNITS |  |

|----------------------------------------------|-----------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|-------|--|

| <b>READBACK ACCURACY (Note 7)</b>            |                       |                                                                                |                                                           |     |     |     |       |  |

| Output-Current Readback Accuracy             | I <sub>OUT_ADC</sub>  | 1Φ, I <sub>OUT</sub> = I <sub>OUT(MAX)</sub>                                   | T <sub>J</sub> = -40°C to +85°C                           | 5   |     | %   |       |  |

|                                              |                       |                                                                                | T <sub>J</sub> = +125°C                                   | 7.5 |     |     |       |  |

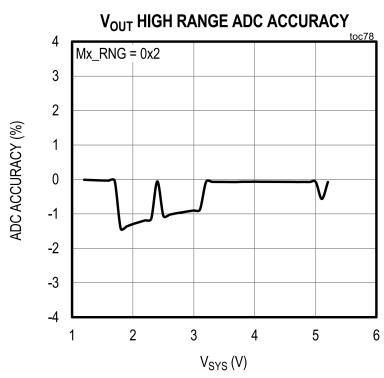

| Output-Voltage Readback Accuracy             | V <sub>OUT_ADC</sub>  | T <sub>J</sub> = -40°C to +85°C                                                |                                                           | 3   |     | %   |       |  |

|                                              |                       | T <sub>J</sub> = +125°C                                                        |                                                           | 5   |     |     |       |  |

| SYS Input-Voltage Readback Accuracy          | V <sub>SYS_ADC</sub>  | 3.0V ≤ V <sub>SYS</sub> ≤ 16V                                                  | T <sub>J</sub> = -40°C to +85°C                           | 3   |     | %   |       |  |

|                                              |                       |                                                                                | T <sub>J</sub> = +125°C                                   | 5   |     |     |       |  |

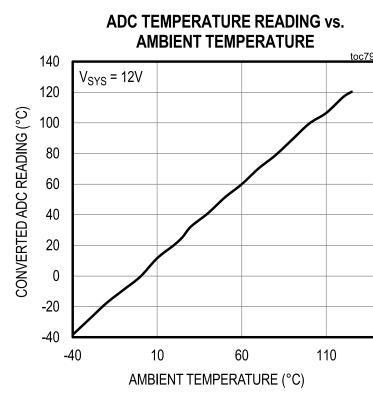

| Junction Temperature Readback Accuracy       | T <sub>J_ADC</sub>    | T <sub>J</sub> = +85°C to +125°C                                               |                                                           | 5   |     | %   |       |  |

| MFIO Voltage Readback Accuracy               | V <sub>MFIO_ADC</sub> | T <sub>J</sub> = -40°C to +85°C                                                |                                                           | 3   |     | %   |       |  |

|                                              |                       | T <sub>J</sub> = +125°C                                                        |                                                           | 5   |     |     |       |  |

| <b>TIMING (Note 6)</b>                       |                       |                                                                                |                                                           |     |     |     |       |  |

| Clock Frequency                              | f <sub>ADC</sub>      |                                                                                |                                                           |     | 1   | MHz |       |  |

| ADC Startup Time                             | t <sub>ADC_SU</sub>   | One of buck outputs is enabled                                                 |                                                           |     | 22  | μs  |       |  |

|                                              |                       | All buck outputs are disabled                                                  |                                                           |     | 26  |     |       |  |

| ADC Sampling Time                            | t <sub>SAMPLE</sub>   | Per channel                                                                    | I <sub>OUTX</sub> , T <sub>J</sub>                        | 1   |     | ms  |       |  |

|                                              |                       |                                                                                | V <sub>OUTX</sub> , V <sub>SYS</sub> , V <sub>MFIOX</sub> | 18  |     | μs  |       |  |

| Conversion Time                              | t <sub>CONV</sub>     | Per channel                                                                    |                                                           |     | 18  | μs  |       |  |

| Sampling Interval for Averaging Mode         | t <sub>INT_AVG</sub>  | Sampling interval for the same channel in averaging mode                       |                                                           |     | 5   | ms  |       |  |

| Sampling Interval for Continuous Measurement | t <sub>INT_CONT</sub> | Sampling interval for the same channel during continuous measurement operation |                                                           |     | 1   | s   |       |  |

電気的特性-I<sup>2</sup>C シリアル・インターフェース(特に指定のない限り、V<sub>SYS</sub> = 12V、V<sub>CE</sub> = 1.8V、V<sub>IO</sub> = 1.8V、T<sub>A</sub> = T<sub>J</sub> = -40°C～+125°C、代表値はT<sub>A</sub> = T<sub>J</sub> = +25°Cでの値です。Note 2。)

| PARAMETER                                    | SYMBOL                 | CONDITIONS                                                                                   |      | MIN                    | TYP  | MAX  | UNITS |

|----------------------------------------------|------------------------|----------------------------------------------------------------------------------------------|------|------------------------|------|------|-------|

| <b>I/O STAGE</b>                             |                        |                                                                                              |      |                        |      |      |       |

| V <sub>IO</sub> Supply Voltage               | V <sub>IO</sub>        |                                                                                              |      | 1.1                    | 1.8  | 2.0  | V     |

| V <sub>IO</sub> Dynamic Supply Current       | I <sub>IO</sub>        | f <sub>SCL</sub> = f <sub>SDA</sub> = 3.4MHz, V <sub>CE</sub> = 1.8V, all bucks are disabled | 5    |                        | μA   |      |       |

| SYS Dynamic Supply Current                   | I <sub>SYS</sub>       | f <sub>SCL</sub> = f <sub>SDA</sub> = 3.4MHz, V <sub>CE</sub> = 1.8V, all bucks are disabled | 40   |                        | μA   |      |       |

| V <sub>IO</sub> Undervoltage Lock-Out (UVLO) | V <sub>IO_UVLO_R</sub> | V <sub>IO</sub> rising                                                                       | 1.06 |                        | 1.09 | 1.12 | V     |

|                                              | V <sub>IO_UVLO_F</sub> | V <sub>IO</sub> falling                                                                      | 0.96 |                        | 0.99 | 1.02 |       |

| SCL, SDA Input Logic Low Threshold           | V <sub>IL</sub>        |                                                                                              |      | 0.25 × V <sub>IO</sub> |      | V    |       |

電気的特性—I<sup>2</sup>C シリアル・インターフェース（続き）

（特に指定のない限り、V<sub>SYS</sub> = 12V、V<sub>CE</sub> = 1.8V、V<sub>IO</sub> = 1.8V、T<sub>A</sub> = T<sub>J</sub> = -40°C～+125°C、代表値は T<sub>A</sub> = T<sub>J</sub> = +25°C での値です。Note 2。）

| PARAMETER                           | SYMBOL              | CONDITIONS                                       | MIN                    | TYP | MAX | UNITS |

|-------------------------------------|---------------------|--------------------------------------------------|------------------------|-----|-----|-------|

| SCL, SDA Input Logic High Threshold | V <sub>IH</sub>     |                                                  | 0.75 x V <sub>IO</sub> |     |     | V     |

| SCL, SDA Input Hysteresis           | V <sub>HYS</sub>    |                                                  |                        | 0.3 |     | V     |

| SDA Output Logic Low Threshold      | V <sub>OL_SDA</sub> | Sinking 20mA                                     |                        |     | 0.2 | V     |

| SCL, SDA Input Leakage Current      | I <sub>LKG</sub>    | V <sub>SCL</sub> = V <sub>SDA</sub> = 0V or 2.0V | -10                    |     | +10 | μA    |

| SCL, SDA Pin Capacitance            |                     | (Note 7)                                         |                        | 10  |     | pF    |

## STANDARD, FAST, AND FAST MODE PLUS TIMING

|                                                |                     |          |     |     |

|------------------------------------------------|---------------------|----------|-----|-----|

| Clock Frequency                                | f <sub>SCL</sub>    |          | 1   | MHz |

| Hold Time (Repeated) Start Condition           | t <sub>HD;STA</sub> |          | 260 | ns  |

| SCL Low Period                                 | t <sub>LOW</sub>    |          | 500 | ns  |

| SCL High Period                                | t <sub>HIGH</sub>   |          | 260 | ns  |

| Setup Time Repeated Start Condition            | t <sub>SU;STA</sub> |          | 260 | ns  |

| Data Hold Time                                 | t <sub>HD;DAT</sub> |          | 0   | μs  |

| Data Setup Time                                | t <sub>SU;DAT</sub> |          | 50  | ns  |

| Setup Time for Stop Condition                  | t <sub>SU;STO</sub> |          | 260 | ns  |

| Bus Free Time Between Stop and Start Condition | t <sub>BUF</sub>    |          | 0.5 | μs  |

| Input Filter Suppressed Spike Pulse Width      | t <sub>SP</sub>     | (Note 7) | 50  | ns  |

## HIGH-SPEED MODE TIMING

|                                           |                     |                 |     |     |

|-------------------------------------------|---------------------|-----------------|-----|-----|

| Clock Frequency                           | f <sub>SCL</sub>    | High-speed mode | 3.4 | MHz |

| Setup Time Repeated Start Condition       | t <sub>SU;STA</sub> |                 | 160 | ns  |

| Hold Time (Repeated) Start Condition      | t <sub>HD;STA</sub> |                 | 160 | ns  |

| SCL Low Period                            | t <sub>LOW</sub>    |                 | 160 | ns  |

| SCL High Period                           | t <sub>HIGH</sub>   |                 | 60  | ns  |

| Data Setup Time                           | t <sub>SU;DAT</sub> |                 | 10  | ns  |

| Data Hold Time                            | t <sub>HD;DAT</sub> |                 | 0   | μs  |

| Setup Time for Stop Condition             | t <sub>SU;STO</sub> |                 | 160 | ns  |

| Input Filter Suppressed Spike Pulse Width | t <sub>SP</sub>     | (Note 7)        | 10  | ns  |

Note 2 : MAX77542 は T<sub>J</sub> ≈ T<sub>A</sub> となるようなパルス負荷条件下でテストされています。制限値は T<sub>A</sub> = +25°C で 100% テストされています。動作温度範囲 (T<sub>j</sub> = -40°C～+125°C) における制限値は、統計的プロセス制御の方法を使用した設計および特性評価により確保されています。ここに示す仕様に見合った最大周囲温度は、具体的な動作条件、基板レイアウト、パッケージの熱抵抗定格値、およびその他の環境条件によって決まります。

Note 3 : 電源電流=  $I_{SYS} + I_{IN1} + I_{IN2} + I_{IN3} + I_{IN4}$ 。

Note 4 : スイッチング周波数はクロック発振器によって設定されるわけではありません。 $F_{SW}$ は、入力電圧、出力電圧、負荷、およびスペクトラム拡散の設置値によって変化します。

Note 5 : ATE の特性評価によって確保されています。製造時に直接テストされているわけではありません。

Note 6 : 設計により確保されています。スキャンによる出荷テストを行っています。

Note 7 : 出荷テストの対象外です。設計ガイドラインとしてのみ使用してください。

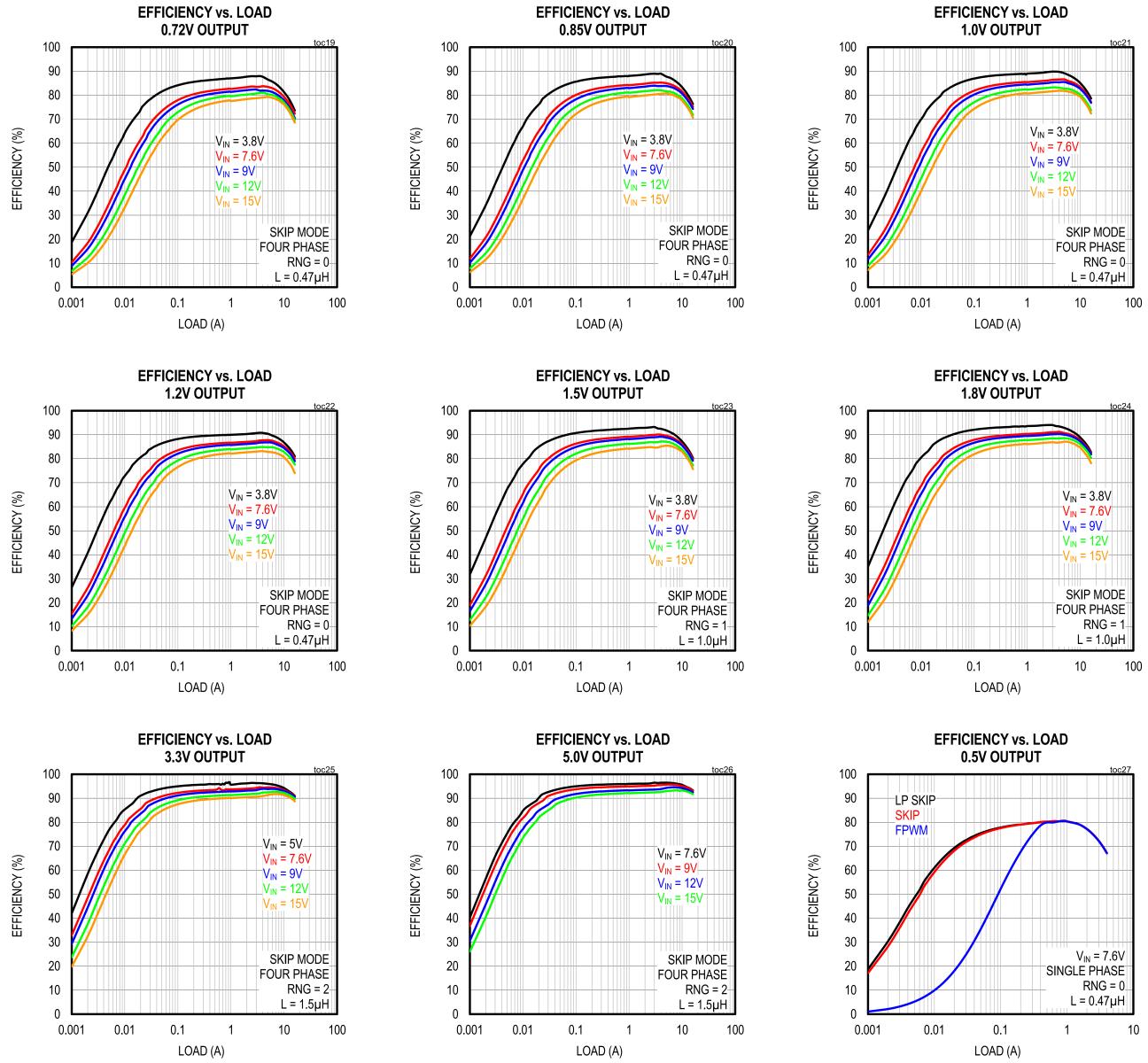

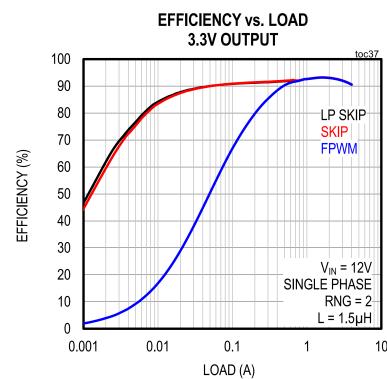

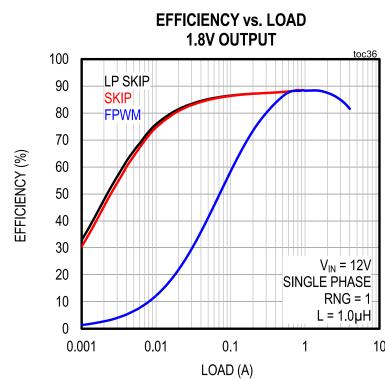

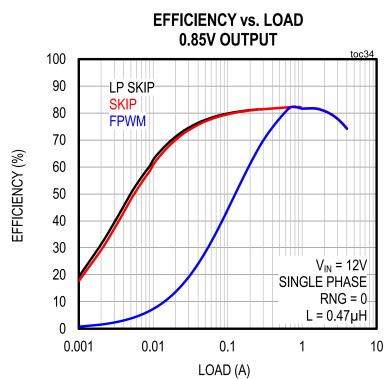

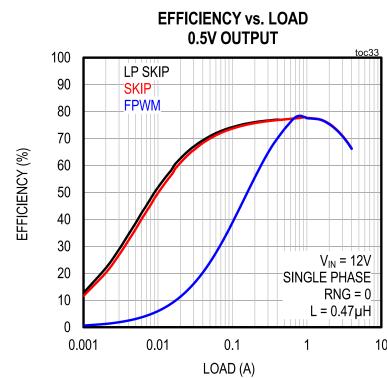

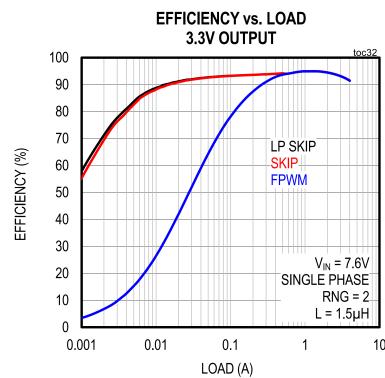

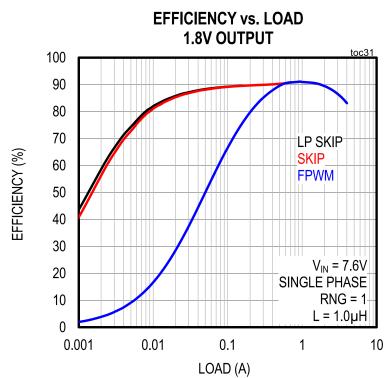

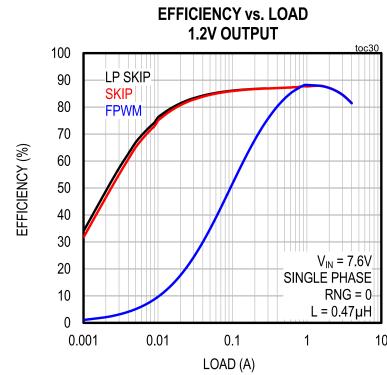

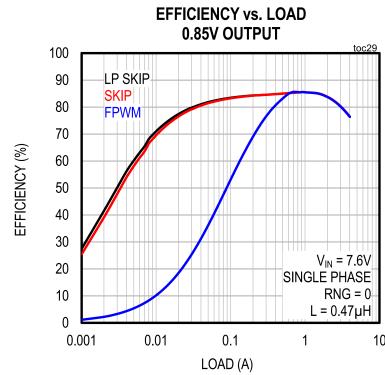

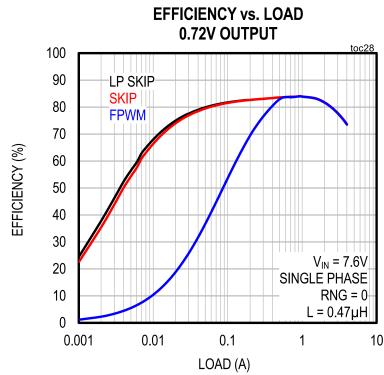

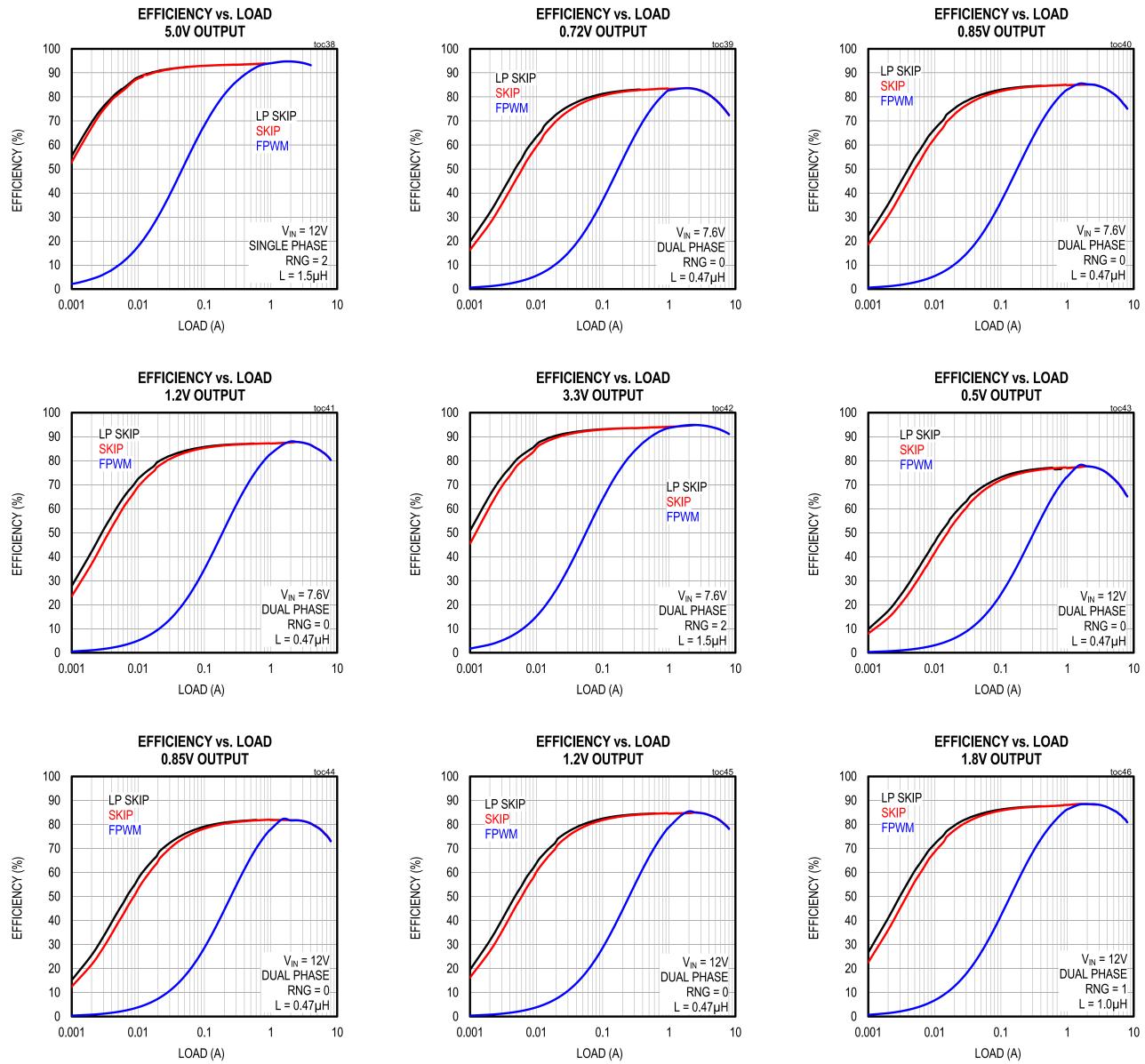

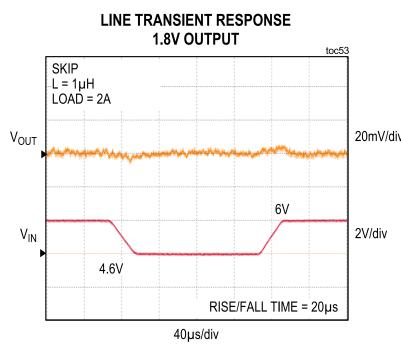

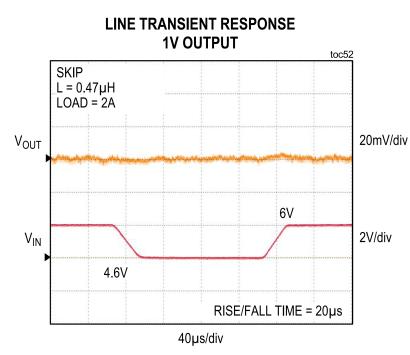

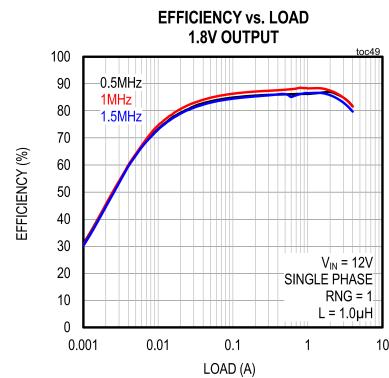

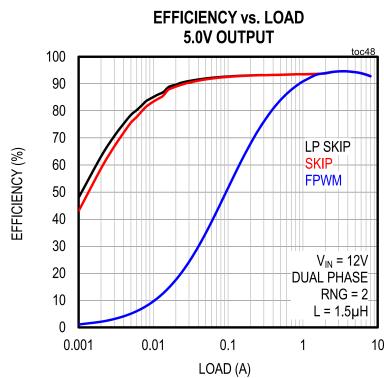

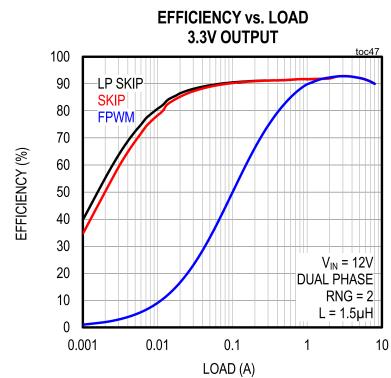

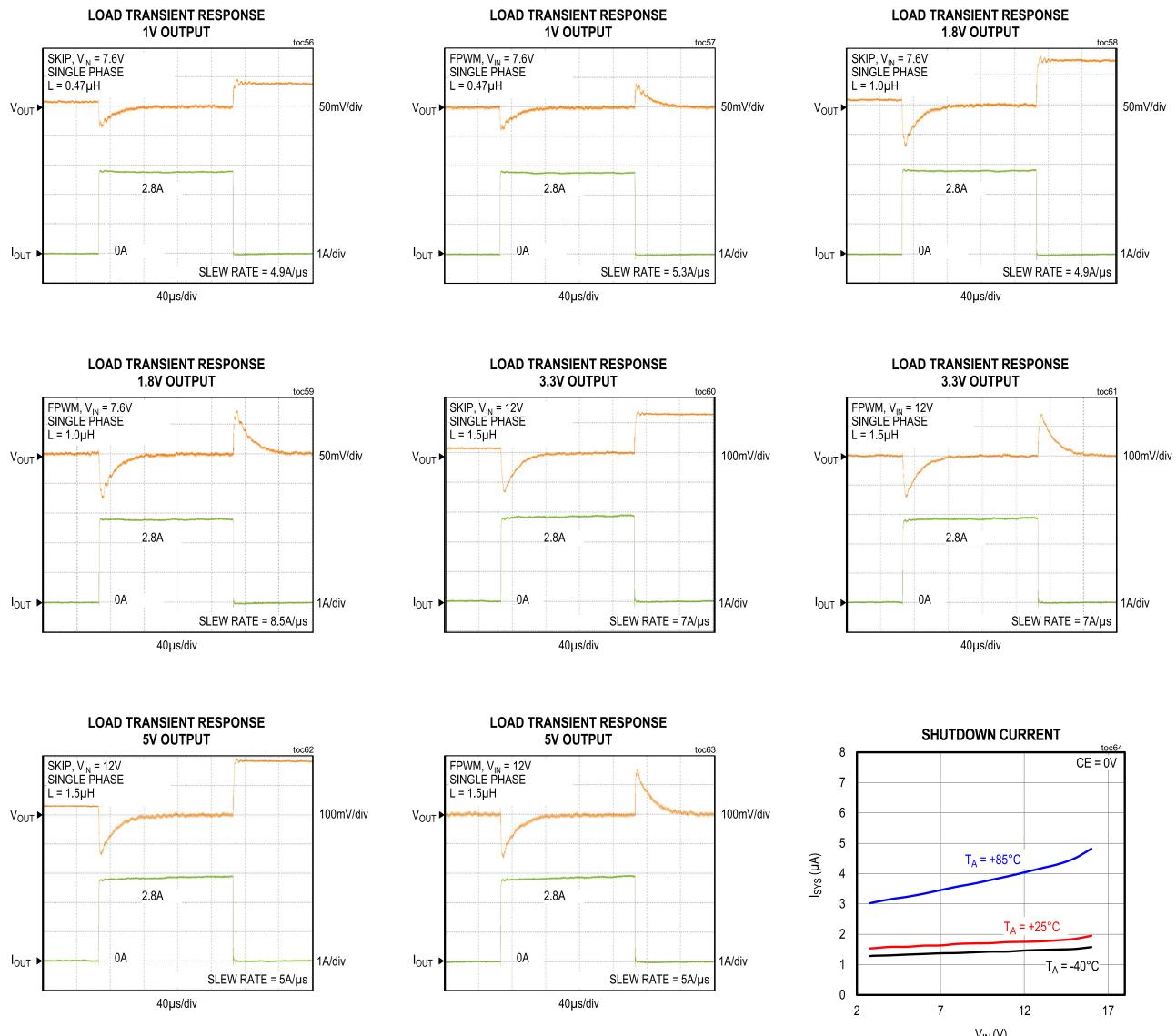

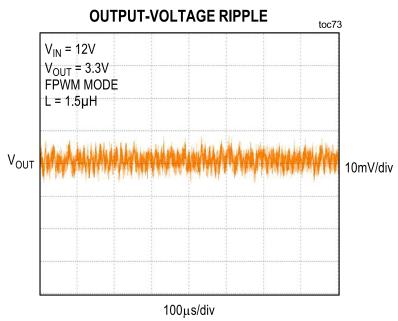

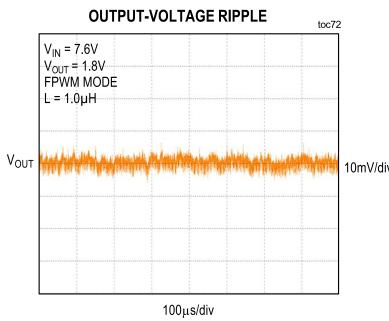

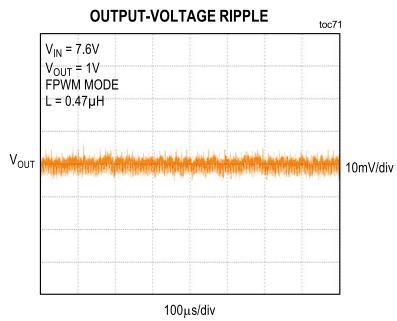

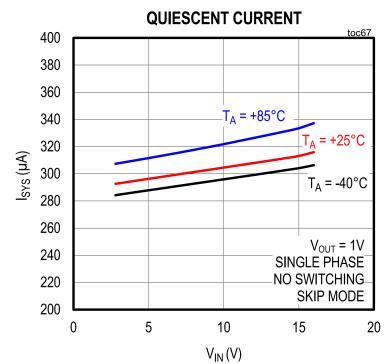

## 標準動作特性

(特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 1.0V、単相の構成、V<sub>VIO</sub> = 1.8V、スキップ・モード、T<sub>A</sub> = +25°C。)

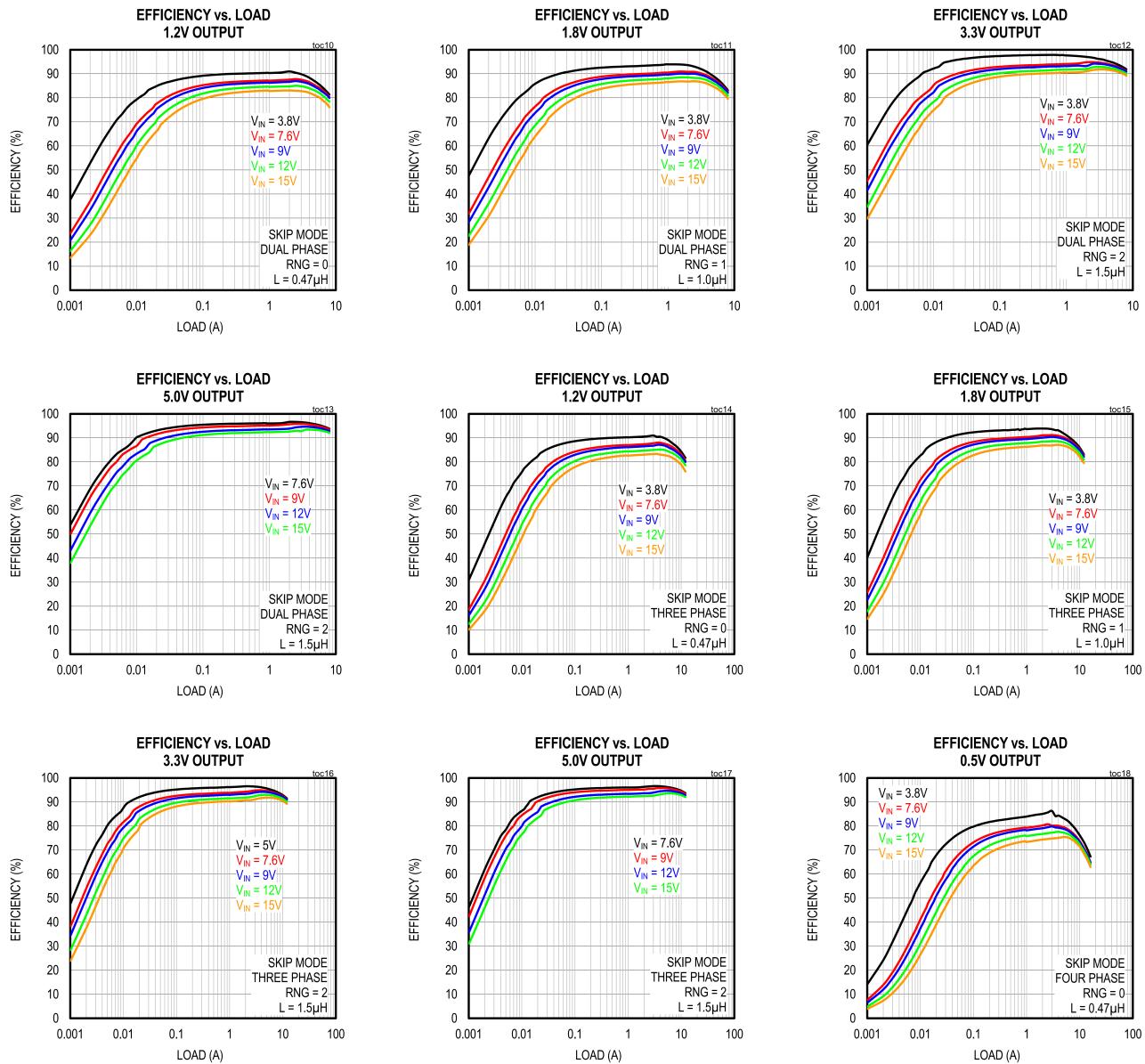

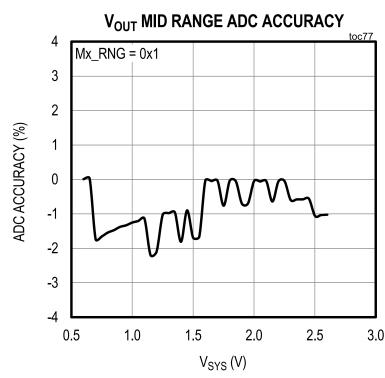

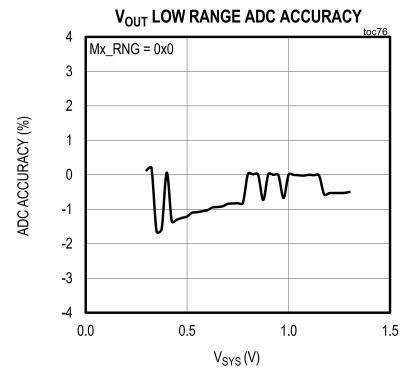

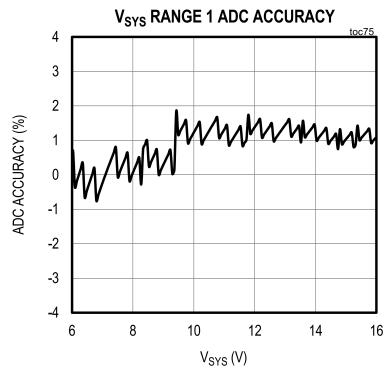

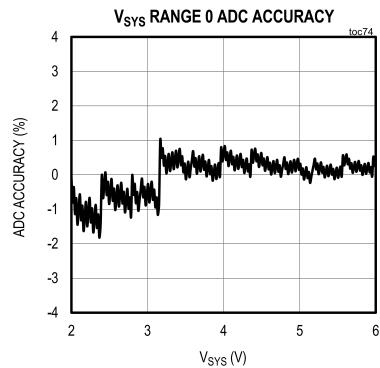

## 標準動作特性（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 1.0V、単相の構成、V<sub>VIO</sub> = 1.8V、スキップ・モード、T<sub>A</sub> = +25°C。）

## 標準動作特性（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 1.0V、単相の構成、V<sub>VIO</sub> = 1.8V、スキップ・モード、T<sub>A</sub> = +25°C。）

## 標準動作特性（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 1.0V、単相の構成、V<sub>VIO</sub> = 1.8V、スキップ・モード、T<sub>A</sub> = +25°C。）

## 標準動作特性（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 1.0V、単相の構成、V<sub>VIO</sub> = 1.8V、スキップ・モード、T<sub>A</sub> = +25°C。）

## 標準動作特性（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 1.0V、単相の構成、V<sub>VIO</sub> = 1.8V、スキップ・モード、T<sub>A</sub> = +25°C。）

## 標準動作特性（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 1.0V、単相の構成、V<sub>VIO</sub> = 1.8V、スキップ・モード、T<sub>A</sub> = +25°C。）

## 標準動作特性（続き）

（特に指定のない限り、V<sub>SYS</sub> = V<sub>INx</sub> = 12V、V<sub>OUT1</sub> = 1.0V、単相の構成、V<sub>VIO</sub> = 1.8V、スキップ・モード、T<sub>A</sub> = +25°C。）

## 標準動作特性（続き）

（特に指定のない限り、 $V_{SYS} = V_{INx} = 12V$ 、 $V_{OUT1} = 1.0V$ 、単相の構成、 $V_{VIO} = 1.8V$ 、スキップ・モード、 $T_A = +25^\circ C$ 。）

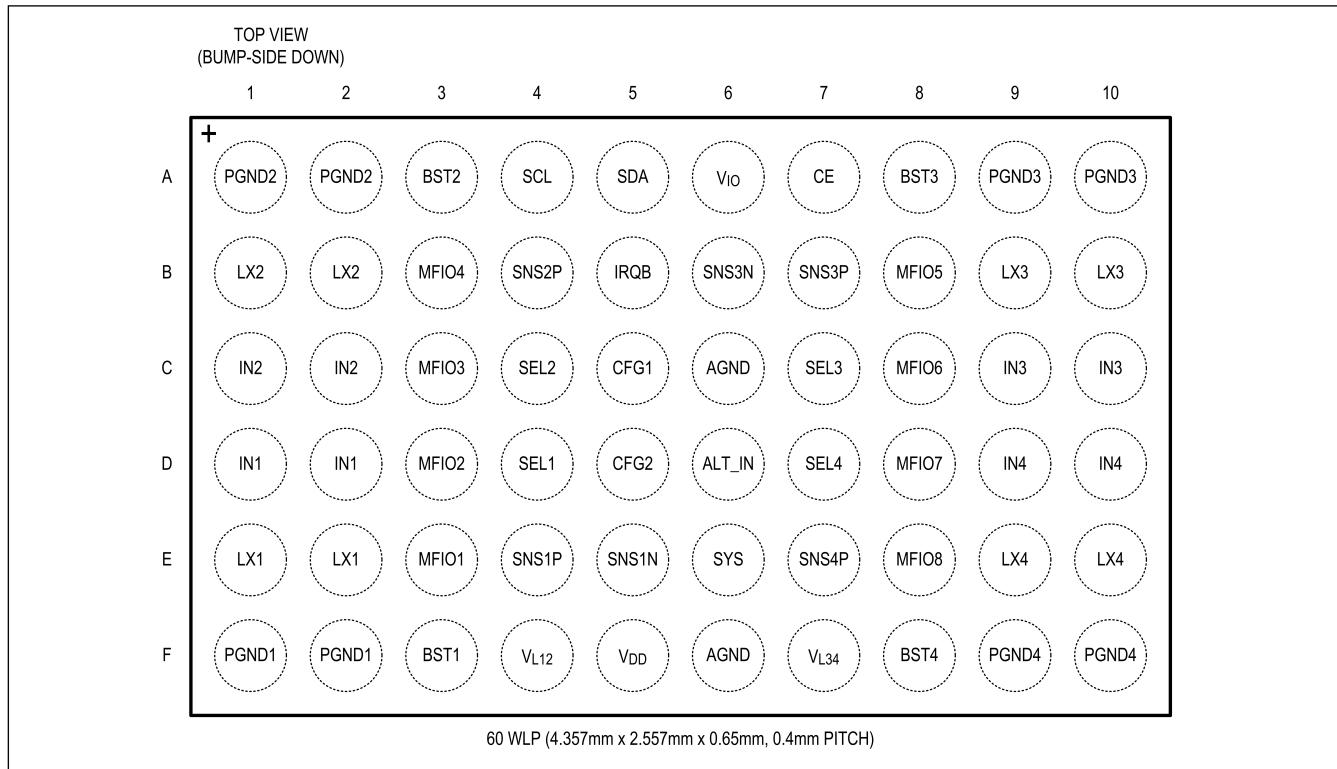

## ピン配置

## MAX77542

## 端子説明

| ピン                | 名称   | 説明                                                                  | タイプ  |

|-------------------|------|---------------------------------------------------------------------|------|

| <b>降圧スイッチング位相</b> |      |                                                                     |      |

| F3                | BST1 | 位相 1 のハイサイド MOSFET ドライバの電源。BST1 と LX1 の間に 0.1μF のセラミック・コンデンサを接続します。 | 電源入力 |

| A3                | BST2 | 位相 2 のハイサイド MOSFET ドライバの電源。BST2 と LX2 の間に 0.1μF のセラミック・コンデンサを接続します。 | 電源入力 |

| A8                | BST3 | 位相 3 のハイサイド MOSFET ドライバの電源。BST3 と LX3 の間に 0.1μF のセラミック・コンデンサを接続します。 | 電源入力 |

| F8                | BST4 | 位相 4 のハイサイド MOSFET ドライバの電源。BST4 と LX4 の間に 0.1μF のセラミック・コンデンサを接続します。 | 電源入力 |

| D1, D2            | IN1  | 位相 1 の入力。10μF のセラミック・コンデンサで PGND1 にバイパスします。                         | 電源入力 |

| C1, C2            | IN2  | 位相 2 の入力。10μF のセラミック・コンデンサで PGND2 にバイパスします。                         | 電源入力 |

| C9, C10           | IN3  | 位相 3 の入力。10μF のセラミック・コンデンサで PGND3 にバイパスします。                         | 電源入力 |

| D9, D10           | IN4  | 位相 4 の入力。10μF のセラミック・コンデンサで PGND4 にバイパスします。                         | 電源入力 |

| E1, E2            | LX1  | 位相 1 のスイッチング・ノード                                                    | 電源出力 |

| B1, B2            | LX2  | 位相 2 のスイッチング・ノード                                                    | 電源出力 |

| B9, B10           | LX3  | 位相 3 のスイッチング・ノード                                                    | 電源出力 |

| E9, E10           | LX4  | 位相 4 のスイッチング・ノード                                                    | 電源出力 |

## 端子説明（続き）

| ピン      | 名称    | 説明                                                                                 | タイプ    |

|---------|-------|------------------------------------------------------------------------------------|--------|

| F1, F2  | PGND1 | 位相 1 の電源グランド                                                                       | 電源グランド |

| A1, A2  | PGND2 | 位相 2 の電源グランド                                                                       | 電源グランド |

| A9, A10 | PGND3 | 位相 3 の電源グランド                                                                       | 電源グランド |

| F9, F10 | PGND4 | 位相 4 の電源グランド                                                                       | 電源グランド |

| E5      | SNS1N | 位相 1 の負側差動出力電圧の検出入力                                                                | アナログ入力 |

| E4      | SNS1P | 位相 1 の正側差動出力電圧の検出入力                                                                | アナログ入力 |

| B4      | SNS2P | 位相 2 の正側差動出力の検出入力。位相 2 が多相のコンバータのスレーブ位相になっている場合は、AGND に接続するか未接続のまま（フローティング）にします。   | アナログ入力 |

| B6      | SNS3N | 位相 3 の負側差動出力電圧の検出入力。位相 3 が多相のコンバータのスレーブ位相になっている場合は、AGND に接続するか未接続のまま（フローティング）にします。 | アナログ入力 |

| B7      | SNS3P | 位相 3 の正側差動出力電圧の検出入力。位相 3 が多相のコンバータのスレーブ位相になっている場合は、AGND に接続するか未接続のまま（フローティング）にします。 | アナログ入力 |

| E7      | SNS4P | 位相 4 の正側差動出力電圧の検出入力。位相 4 が多相のコンバータのスレーブ位相になっている場合は、AGND に接続するか未接続のまま（フローティング）にします。 | アナログ入力 |

## 内部バイアス電源

|        |           |                                                                                                                                                     |      |

|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| C6, F6 | AGND      | アナログ（静）グランド                                                                                                                                         | グランド |

| D6     | ALT_IN    | $V_{DD}$ 、 $V_{L12}$ 、 $V_{L34}$ の代替電源入力。使用する場合は、2.2 $\mu$ F のセラミック・コンデンサで AGND にバイパスします。詳細については、 <a href="#">低電圧の代替入力（ALT_IN）</a> のセクションを参照してください。 | 電源入力 |

| E6     | SYS       | システム電源入力（内部の $V_{DD}$ 、 $V_{L12}$ 、および $V_{L34}$ リニア電圧レギュレータに電源を供給します）。2.2 $\mu$ F のセラミック・コンデンサで AGND にバイパスします。                                     | 電源入力 |

| F5     | $V_{DD}$  | 内部バイアス電源出力。電源は SYS から供給されます。1 $\mu$ F のセラミック・コンデンサで AGND にバイパスします。このピンには外部から負荷を接続しないでください。                                                          | 電源出力 |

| F4     | $V_{L12}$ | 位相 1 と位相 2 の内部ゲート・ドライバの電源出力。電源は SYS から供給されます。 $V_{L12}$ は、2.2 $\mu$ F のセラミック・コンデンサで PGND にバイパスします。このピンには外部から負荷を接続しないでください。                          | 電源出力 |

| F7     | $V_{L34}$ | 位相 3 と位相 4 の内部ゲート・ドライバの電源出力。電源は SYS から供給されます。 $V_{L34}$ は、2.2 $\mu$ F のセラミック・コンデンサで PGND にバイパスします。このピンには外部から負荷を接続しないでください。                          | 電源出力 |

| A6     | $V_{IO}$  | I/O の電源入力。1 $\mu$ F のセラミック・コンデンサで AGND にバイパスします。                                                                                                    | 電源入力 |

## 制御およびシリアル・インターフェース

|    |      |                                                                                                                                                                                                                 |        |

|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| A7 | CE   | チップ・イネーブル入力（アクティブ・ハイ）。 $V_{DD}$ 、 $V_{L12}$ 、および $V_{L34}$ レギュレータと、I <sup>2</sup> C シリアル・インターフェースのイネーブル。詳細については、 <a href="#">チップ・イネーブル（CE）および内部バイアス電源</a> のセクションを参照してください。                                      | デジタル入力 |

| C5 | CFG1 | デバイス設定 1 の選択入力。選択用の抵抗 ( $R_{CFG1}$ ) を CFG1 と AGND の間に接続し、I <sup>2</sup> C のスレーブ・アドレスとデフォルトの MFIO 機能を設定します。デフォルトの設定値は、I <sup>2</sup> C を通じて上書きすることができます。詳細については、 <a href="#">デバイスの設定（CFGx）</a> のセクションを参照してください。 | アナログ入力 |

## 端子説明（続き）

| ピン | 名称   | 説明                                                                                                                                                                                                                                                                                                                | タイプ      |

|----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|