## 36V、5A/6A、全機能内蔵同期式降圧コンバータ

MAX42405/MAX42406

### 概要

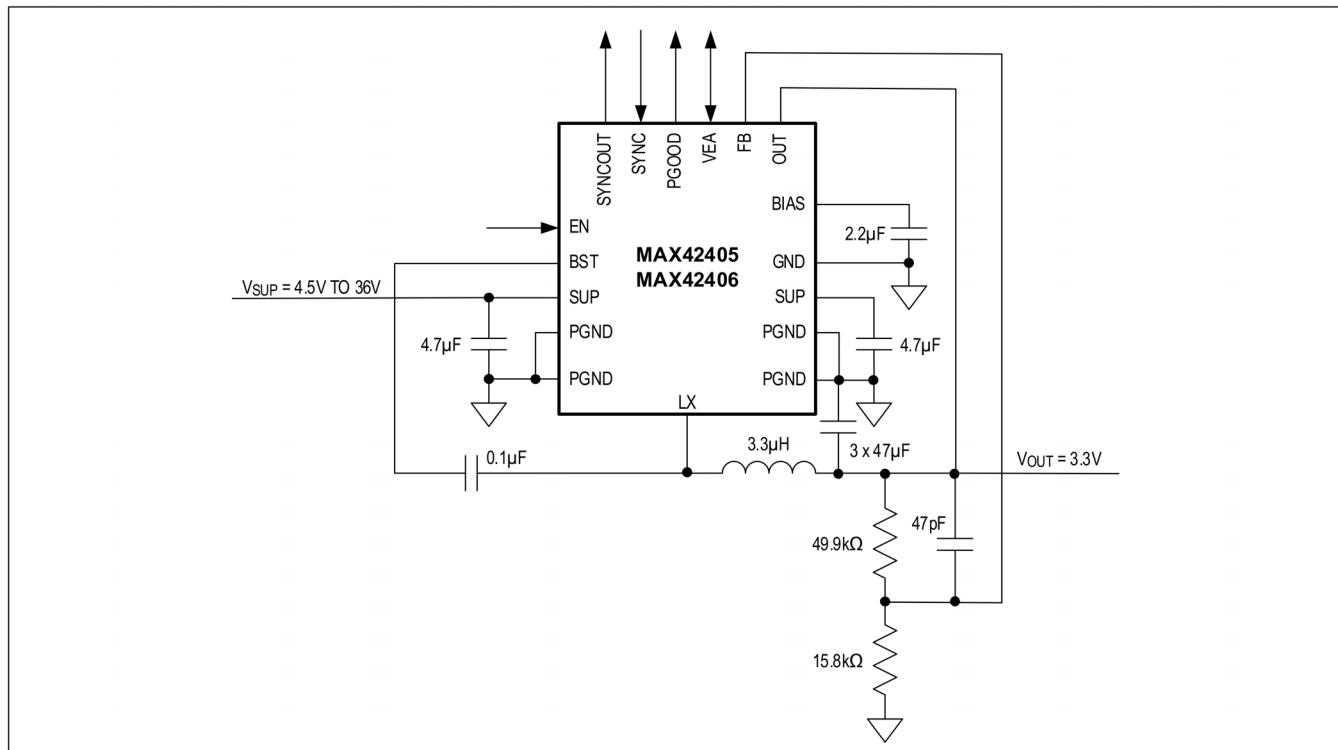

MAX42405/MAX42406 は、小型の同期式降圧コンバータで、ハイサイド・スイッチとローサイド・スイッチを内蔵した IC です。この IC は、4.5V～36V という広い入力電圧範囲を備え、最大 6A を供給するように設計されています。電圧品質は、PGOOD 信号を観察することで監視可能です。この IC は、非常に高いデューティ・サイクルで稼働することによりドロップアウト時でも動作が可能であるため、産業用アプリケーションに理想的です。

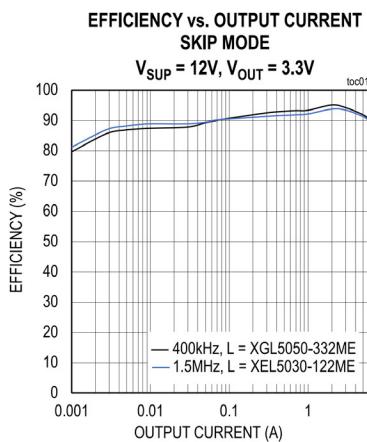

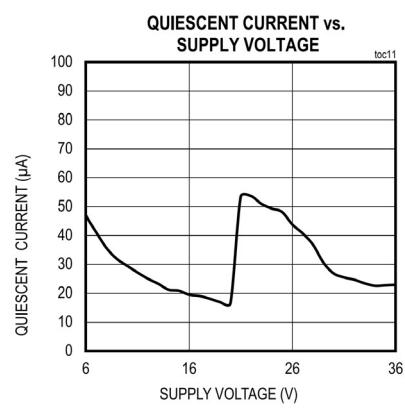

MAX42405/MAX42406 は、0.8V～10V のプログラマブルな電圧範囲を備えています。周波数は内部で 400kHz と 1.5MHz に固定されているので、外付け部品を少なくし、出力リップルを抑制することができます。この IC は、軽負荷時には自動的にスキップ・モードに入り、無負荷時には 10µA という超低自己消費電流になります。この製品ファミリ (MAX42408/MAX42410 を含む) からは、シングルフェーズ構成で 5A～10A、デュアルフェーズ構成で最大 20A を供給するピンツーピン互換品が提供されます。これらのデバイスはデュアルフェーズ動作にも最適化されており、非常に高い電流分担精度を備えています。

MAX42405/MAX42406 は小型 (3.5mm × 3.75mm) の 17 ピン FC2QFN パッケージで提供され、使用する外付け部品はごくわずかです。

### アプリケーション

- 産業オートメーション

- ポイントオブロード

- 分散型 DC 電源システム

### 特長と利点

- 小型サイズでありながら多機能

- 動作可能な  $V_{IN}$  範囲 : 4.5V～36V

- スキップ・モードでの自己消費電流 : 20µA

- 電界効果トランジスタ (FET) を内蔵した同期式 DC/DC コンバータ

- 400kHz と 1.5MHz の固定周波数オプション

- 内部ソフトスタート

- 2.5ms (400kHz 時)

- 3.5ms (1.5MHz 時)

- プログラマブルな出力 : 0.8V～10V

- 3.5mm × 3.75mm、17 ピン FC2QFN

- 対称パッケージにより優れた電磁干渉 (EMI) 性能を実現

- デュアルフェーズ機能

- 高出力設計にはデュアルフェーズ構成で使用可能

- VEA ピンの共有による動的電流分担

- 低  $I_Q$  動作能力 (デュアルフェーズ)

- PGOOD による正確な出力電圧モニタリング

- 強制パルス幅変調 (PWM) とスキップモード動作

- 低ドロップアウト動作

- 過熱および短絡の保護機能

- 動作温度範囲 : -40°C～+125°C

型番はデータシート末尾に記載されています。

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

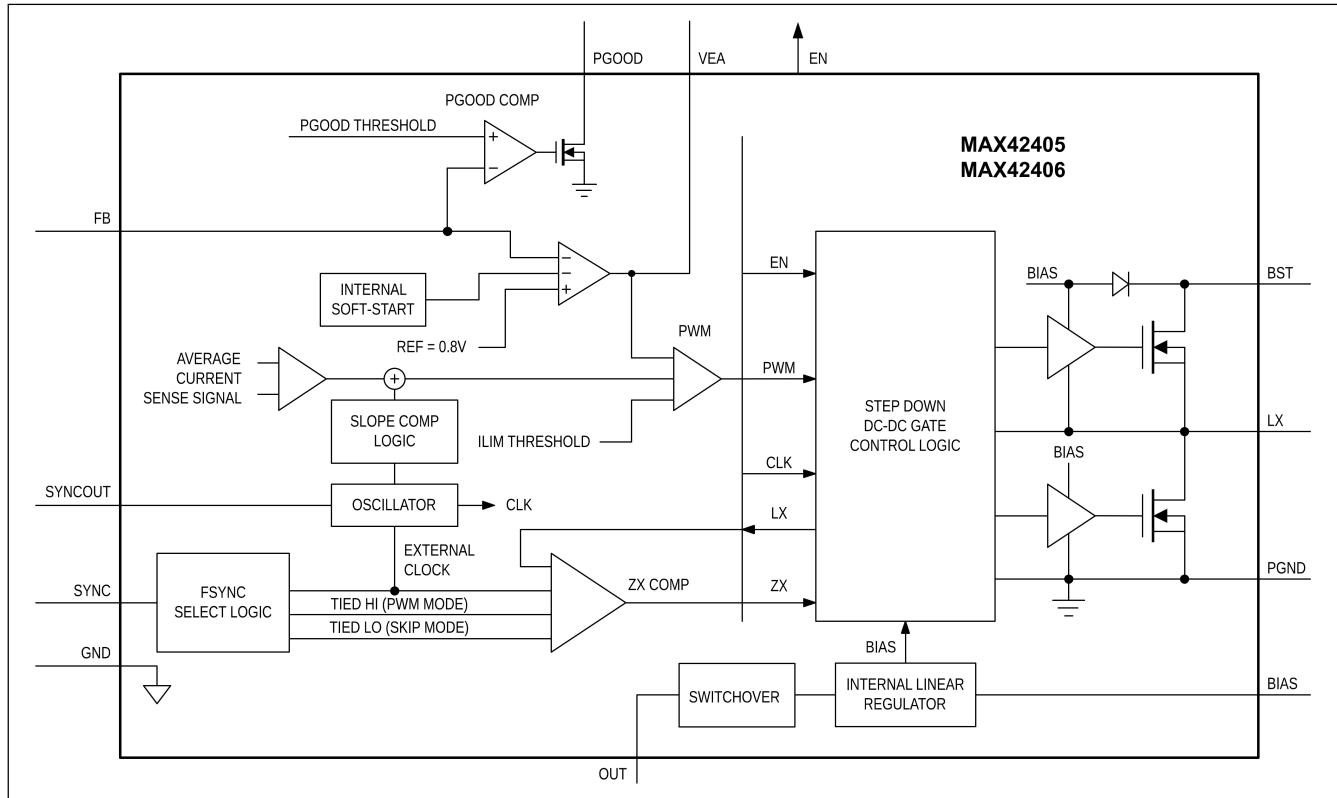

## 簡略化したブロック図

## 絶対最大定格

|         |                  |                                                         |              |

|---------|------------------|---------------------------------------------------------|--------------|

| SUP     | -0.3V～+42V       | BIAS                                                    | -0.3V～+2.2V  |

| EN      | -0.3V～+42V       | PGND～AGND                                               | -0.3V～+0.3V  |

| BST～LX  | -0.3V～+2.2V      | LX 連続 RMS 電流                                            | 6A           |

| BST     | -0.3V～+44V       | ESD 保護                                                  |              |

| LX      | -0.3V～SUP + 0.3V | 人体モデル                                                   | ±2kV         |

| SYNCOUT | -0.3V～+6V        | チャージ・デバイス・モデル                                           | ±750V        |

| SYNC    | -0.3V～+6V        | 連続消費電力 (TA = 70°C、+70°C を超えると 34.48mW/°C で<br>ディレーティング) | 2758mW       |

| VEA     | -0.3V～BIAS+0.3V  | 動作ジャンクション温度                                             | -40°C～+150°C |

| FB      | -0.3V～BIAS+0.3V  | 保存温度範囲                                                  | -65°C～+150°C |

| OUT     | -0.3V～+16V       | ハンド処理温度 (ハンド処理 : 10 秒)                                  | +300°C       |

| PGOOD   | -0.3V～+6V        |                                                         |              |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作あに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## パッケージ情報

|                                                    |            |

|----------------------------------------------------|------------|

| Package Code                                       | F173A3F+2F |

| Outline Number                                     | 21-100700  |

| Land Pattern Number                                | 90-100240  |

| <b>THERMAL RESISTANCE, JEDEC BOARD</b>             |            |

| Junction to Ambient ( $\theta_{JA}$ )              | 38.41°C/W  |

| Junction to Case ( $\theta_{JC}$ )                 | 10.35°C/W  |

| <b>THERMAL RESISTANCE, FOUR-LAYER EV KIT BOARD</b> |            |

| Junction to Ambient ( $\theta_{JA}$ )              | 29°C/W     |

| Junction to Case ( $\theta_{JC}$ )                 | 10.51°C/W  |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、<https://www.analog.com/en/design-center/packaging-quality-symbols-footprints/package-index.html> で確認してください。パッケージ・コードの「+」、「#」、「-」はRoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面は RoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、<https://www.analog.com/en/technical-articles/thermal-characterization-of-ic-packages.html> を参照してください。

## 電気的特性

(特に指定のない限り、 $V_{SUP} = V_{EN} = 14V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$ 。特に指定のない限り、代表値は  $T_A = +25^{\circ}C$  の通常条件下の値。

(Note 1、Note 2) )

| PARAMETER                                                                              | SYMBOL                  | CONDITIONS                                                                | MIN   | TYP   | MAX   | UNITS     |

|----------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------|-------|-------|-------|-----------|

| Supply Voltage Range                                                                   | $V_{SUP}$               |                                                                           | 4.5   | 36    |       | V         |

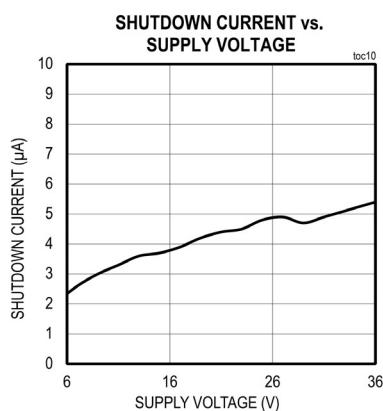

| Supply Current                                                                         | $I_{SUP\_SHDN}$         | $V_{EN} = 0V, T_A = +25^{\circ}C$                                         |       | 4     | 6     | $\mu A$   |

|                                                                                        | $I_{SUP}$               | $V_{EN} = \text{high}, V_{OUT} = 3.3V, \text{no load, switching}$         |       | 20    |       |           |

| SUP Undervoltage Lockout                                                               | $V_{SUP\_UVLO\_R\_ISE}$ | SUP voltage rising                                                        | 2.945 | 3.025 | 3.175 | V         |

|                                                                                        | $V_{SUP\_UVLO\_F\_ALL}$ | SUP voltage falling                                                       | 2.655 | 2.725 | 2.870 |           |

| BIAS Undervoltage Lockout                                                              | $V_{BIAS\_UVLO}$        | BIAS voltage falling                                                      | 1.53  | 1.58  | 1.63  | V         |

| BIAS Undervoltage Lock                                                                 | $V_{BIAS\_UVLO\_HYS}$   | BIAS UVLO hysteresis                                                      |       | 50    |       | mV        |

| BIAS Voltage                                                                           | $V_{BIAS}$              |                                                                           |       | 1.8   |       | V         |

| <b>BUCK CONVERTER</b>                                                                  |                         |                                                                           |       |       |       |           |

| Output Voltage Adjustable Range                                                        | $V_{OUT}$               |                                                                           | 0.8   | 10    |       | V         |

| Feedback Voltage Accuracy                                                              | $V_{FB\_PWM}$           | PWM mode, no load                                                         | 0.787 | 0.800 | 0.813 | V         |

| Feedback Leakage Current                                                               | $I_{FB}$                | $V_{FB} = 0.8V, T_A = +25^{\circ}C$                                       |       | 100   |       | nA        |

| High-Side Double diffusion metal oxide semiconductor field-effect (DMOS) On-Resistance | $R_{DSON\_HS}$          | $V_{BIAS} = 1.8V, I_{LX} = 2A$                                            |       | 46    | 95    | $m\Omega$ |

| Low-Side DMOS On-Resistance                                                            | $R_{DSON\_LS}$          | $V_{BIAS} = 1.8V, I_{LX} = 2A$                                            |       | 23    | 47    | $m\Omega$ |

| High-Side DMOS Current-Limit Threshold                                                 | $I_{LIM}$               | MAX42405                                                                  | 6.5   | 7.5   | 8.5   | A         |

|                                                                                        |                         | MAX42406                                                                  | 7.5   | 8.75  | 10    |           |

| Low-Side DMOS Negative Current-Limit Threshold                                         | $I_{NEG}$               | MAX42405                                                                  |       | -3    |       | A         |

|                                                                                        |                         | MAX42406                                                                  |       | -3.5  |       |           |

| LX Leakage                                                                             | $I_{LX\_LKG}$           | $V_{SUP} = 36V, V_{LX} = 0V, \text{or } V_{LX} = 36V, T_A = +25^{\circ}C$ |       | 1     |       | $\mu A$   |

| Soft-Start Ramp Time                                                                   | $t_{SS}$                | $f_{SW} = 400kHz$                                                         |       | 2.5   |       | ms        |

|                                                                                        |                         | $f_{SW} = 1.5MHz$                                                         |       | 3.5   |       |           |

| Minimum On-Time                                                                        | $t_{ON}$                | (Note 3)                                                                  |       | 36    | 65    | ns        |

| Maximum Duty Cycle                                                                     | $D_{MAX}$               | Dropout Mode                                                              |       | 96    |       | %         |

| <b>SWITCHING FREQUENCY</b>                                                             |                         |                                                                           |       |       |       |           |

| PWM Switching Frequency                                                                | $f_{SW}$                | 400kHz                                                                    | 360   | 400   | 440   | kHz       |

|                                                                                        |                         | 1.5MHz                                                                    | 1.375 | 1.500 | 1.625 | MHz       |

| SYNC External Clock Frequency                                                          | $f_{SYNC}$              | $f_{SW} = 400kHz$                                                         | 360   | 600   |       | kHz       |

|                                                                                        |                         | $f_{SW} = 1.5MHz$                                                         | 1.215 | 1.845 |       | MHz       |

| <b>PGOOD OUTPUT</b>                                                                    |                         |                                                                           |       |       |       |           |

| PGOOD Threshold                                                                        | $V_{PGOOD\_THR}$        | $V_{OUT}$ rising                                                          | 92    | 94    | 96    | %         |

(特に指定のない限り、 $V_{SUP} = V_{EN} = 14V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$ 。特に指定のない限り、代表値は  $T_A = +25^{\circ}C$  の通常条件下の値。

(Note 1、Note 2) )

| PARAMETER                    | SYMBOL           | CONDITIONS                                   |                   | MIN | TYP | MAX | UNITS       |

|------------------------------|------------------|----------------------------------------------|-------------------|-----|-----|-----|-------------|

|                              | $V_{PGOOD\_THF}$ | $V_{OUT}$ falling                            |                   | 91  | 93  | 95  |             |

| PGOOD Debounce Time          | $t_{DEB}$        | Rising                                       | $f_{SW} = 400kHz$ | 100 |     |     | $\mu s$     |

|                              |                  |                                              | $f_{SW} = 1.5MHz$ | 140 |     |     |             |

|                              |                  | Falling                                      | $f_{SW} = 400kHz$ | 50  |     |     |             |

|                              |                  |                                              | $f_{SW} = 1.5MHz$ | 70  |     |     |             |

| PGOOD Leakage Current        | $I_{PGOOD\_LKG}$ | $T_A = +25^{\circ}C$                         |                   |     | 1   |     | $\mu A$     |

| PGOOD Low Voltage Level      | $V_{PGOOD\_LOW}$ | Sinking 1mA                                  |                   |     | 0.4 |     | V           |

| <b>LOGIC LEVELS</b>          |                  |                                              |                   |     |     |     |             |

| EN High Voltage Level        | $V_{EN\_HIGH}$   |                                              |                   | 1.2 |     |     | V           |

| EN Low Voltage Level         | $V_{EN\_LOW}$    |                                              |                   |     | 0.5 |     | V           |

| EN Input Current             | $I_{EN}$         | $V_{EN} = V_{SUP} = 36V, T_A = +25^{\circ}C$ |                   |     | 1   |     | $\mu A$     |

| SYNC High Voltage Level      | $V_{SYNC\_HIGH}$ |                                              |                   | 1.4 |     |     | V           |

| SYNC Low Voltage Level       | $V_{SYNC\_LOW}$  |                                              |                   |     | 0.4 |     | V           |

| SYNCOUT Output Voltage Level | $V_{SYNCOUT}$    | No load                                      |                   | 2.6 | 3.3 | 3.9 | V           |

| <b>THERMAL PROTECTION</b>    |                  |                                              |                   |     |     |     |             |

| Thermal Shutdown             | $T_{SHDN}$       |                                              |                   | 175 |     |     | $^{\circ}C$ |

| Thermal Shutdown Hysteresis  | $T_{SHDN\_HYS}$  |                                              |                   | 20  |     |     | $^{\circ}C$ |

Note 1 : すべてのユニットは  $T_A = +25^{\circ}C$  で 100% 製品テストしています。動作温度範囲および関連する電源電圧に関する限界値は、設計および特性評価で保証しています。

Note 2 : デバイスは、 $T_J = +125^{\circ}C$  で 95,000 時間、および  $T_J = +150^{\circ}C$  で 5,000 時間まで連続動作するように設計しています。

Note 3 : 製品テストは行っていませんが、設計で保証しています。

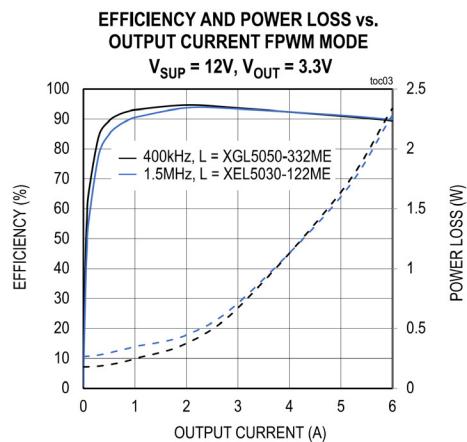

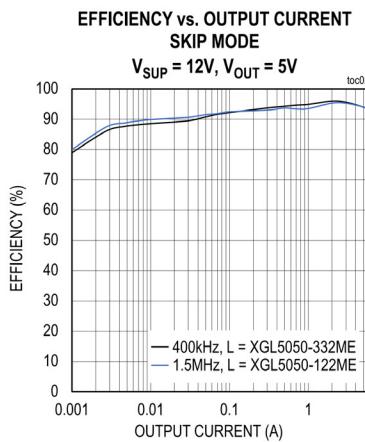

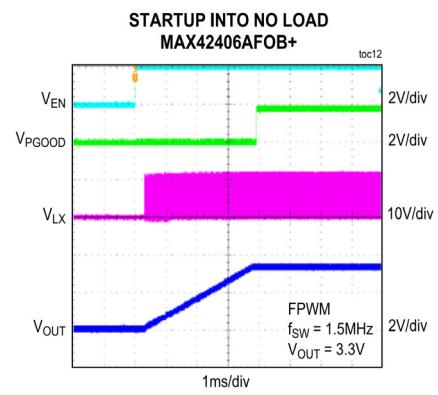

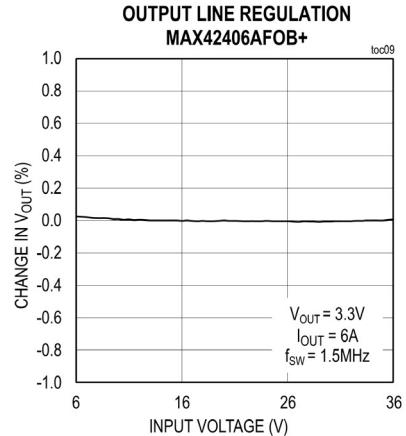

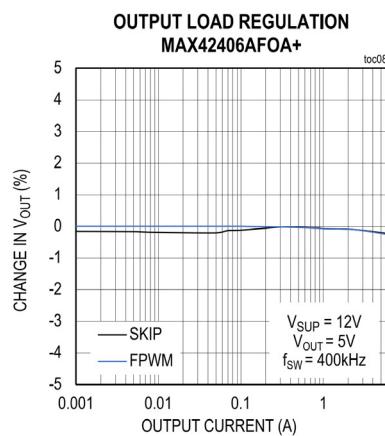

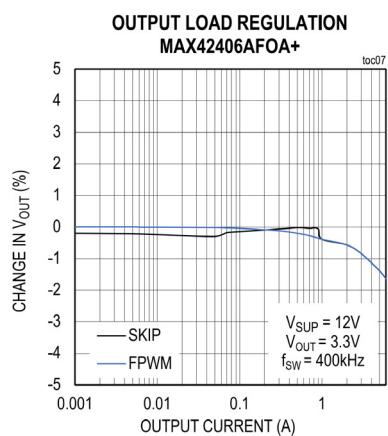

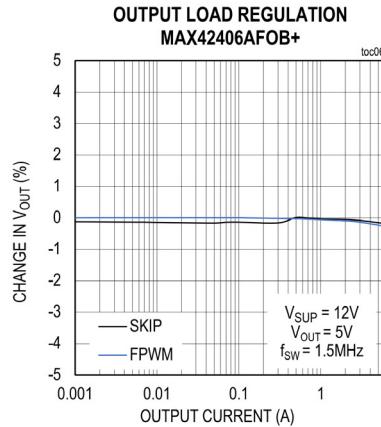

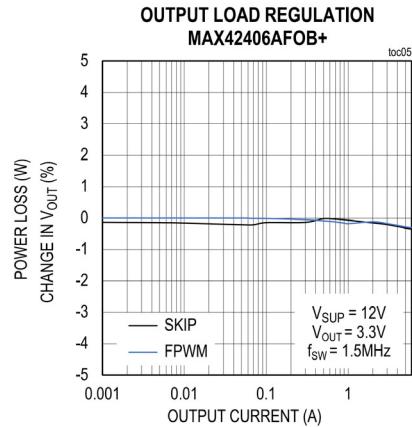

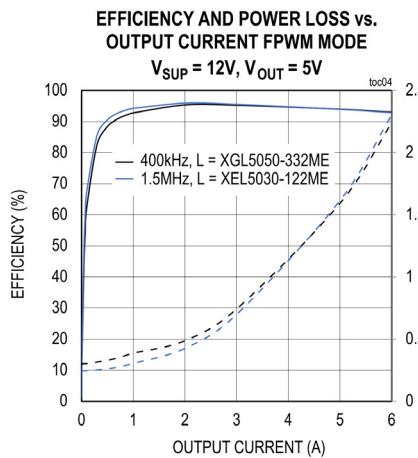

## 標準動作特性

(特に指定のない限り、 $V_{SUP} = V_{EN} = +14V$ 、 $T_A = +25^{\circ}C$ 。)

(特に指定のない限り、 $V_{SUP} = V_{EN} = +14V$ 、 $T_A = +25^{\circ}C$ 。)

(特に指定のない限り、 $V_{SUP} = V_{EN} = +14V$ 、 $T_A = +25^{\circ}\text{C}$ 。)

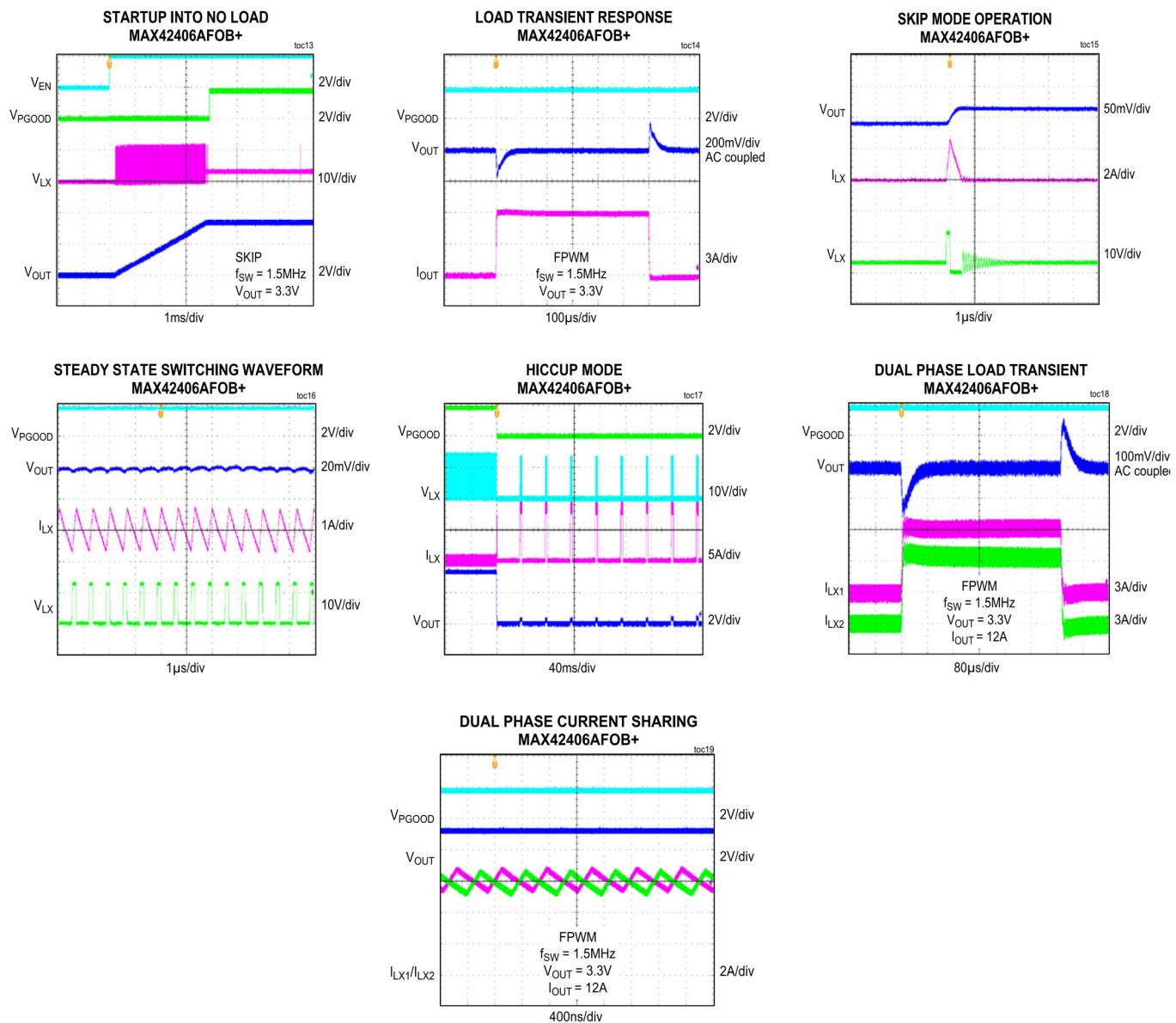

## ピン配置

## 端子説明

| ピン         | 名称      | 説明                                                                              |

|------------|---------|---------------------------------------------------------------------------------|

| 1          | EN      | 高電圧に適合した回路活性化用の入力。このピンがローの場合、この部品はオフです。                                         |

| 2          | BST     | ハイサイド・ドライバ電源。適正な動作のために、LX と BST の間に $0.1\mu F$ のコンデンサを接続します。                    |

| 3, 9       | SUP     | IC 電源入力。 $1\mu F$ 以上のセラミック・コンデンサを SUP から PGND の間にある $4.7\mu F$ のコンデンサと並列に接続します。 |

| 4, 5, 7, 8 | PGND    | パワー・グランド。すべての PGND ピンをまとめて接続します。                                                |

| 6          | LX      | 降圧スイッチング・ノード。この部品がオフの場合は高インピーダンスになります。LX を適切なインダクタのスイッチ側に接続します。                 |

| 10         | GND     | アナログ・グランド。                                                                      |

| 11         | BIAS    | 1.8V の内蔵 BIAS 電源。 $2\mu F$ 以上のセラミック・コンデンサを PGND に接続します。                         |

| 12         | FB      | フィードバック・ピン。OUT から FB の間にある抵抗分圧器を GND に接続して、出力電圧を設定します。                          |

| 13         | OUT     | 降圧レギュレータの出力電圧検出入力。                                                              |

| 14         | VEA     | 内部電圧ループのエラーアンプ出力。デュアルフェーズ動作の場合はターゲットの VEA に接続します。シングルフェーズ動作の場合は未接続のままにします。      |

| 15         | PGOOD   | オープンドレインのリセット出力。外部プルアップが必要です。                                                   |

| 16         | SYNC    | SYNC。GND に接続した場合、軽負荷ではスキップモード動作がイネーブルになります。BIAS に接続した場合、強制 PWM モードがイネーブルになります。  |

| 17         | SYNCOUT | マルチフェーズ動作用の $180^\circ$ 位相差クロック出力シングルフェーズ動作では SYNCOUT をオープンのままにします。             |

## 詳細

MAX42405/MAX42406 は、小型の同期式降圧コンバータで、ハイサイド・スイッチとローサイド・スイッチを内蔵しています。このデバイスは+4.5V～+36V の入力電圧を受けて最大 6A を供給するように設計されており、無負荷時に使われる自己消費電流はわずか 10 $\mu$ A です ( $V_{SUP} = 12V$ 、 $V_{OUT} = 3.3V$ )。電圧品質は、PGOOD 信号を観察することで監視可能です。この IC は、非常に高いデューティ・サイクルで動作することによりドロップアウト時でも動作が可能であるため、産業用アプリケーションに理想的です。

MAX42405/MAX42406 では、外付けの抵抗分圧器を使用して調整可能な出力電圧を実現します。周波数は内部で 400kHz と 1.5MHz に固定されているので、外付け部品を少なくし、出力リップルを抑制することが可能です。デバイスは、軽負荷時には自動的にスキップ・モードに入り (SYNC ピンがローに引き下げられ)、無負荷時には 10 $\mu$ A という超低自己消費電流になります。アーキテクチャは平均電流モード制御で、これにより電流ループのノイズ除去を大きく改善できるようになります。この IC の最小オンタイムは 33ns と小さく、周期をスキップせずに 1 段で大きな降圧比が可能になります。デバイスは、SYNCOUT と VEA を用いると、デュアルフェーズ構成でも使用できます。革新的な平均電流モード制御のアーキテクチャにより、トランジエント時のノイズ耐性と正確な動的電流分担が実現されます。最大 12A の出力電流を備えた高出力設計が、IC のデュアルフェーズ機能を使用した内蔵スイッチを用いることで可能になります。FC2QFN により、熱性能と EMI 性能の向上が実現されます。VIN から PGND までの対称的なピン配列により、EMI 性能が更に向上するので、低ノイズ設計が可能になります。

## リニア・レギュレータ出力 (BIAS)

このデバイスには、内部回路ブロックに給電する 1.8V のリニア・レギュレータ ( $V_{BIAS}$ ) が内蔵されています。 $V_{BIAS}$  から GND の間に 2.2 $\mu$ F のセラミック・コンデンサを接続します。バイアス・レギュレータは起動時に入力から電力を取り、起動が完了すると ( $V_{OUT} > 2.5V$  を満たすと) 出力に切り替えます。出力電圧が 1.8V 未満の場合、バイアス・レギュレータは常に入力に接続されています。

## システム・イネーブル (EN)

イネーブル制御入力 (EN) でデバイスを低電力シャットダウン・モードから起動します。EN は 4.5V までの入力レベルに適合しています。EN で内蔵のリニア (BIAS) レギュレータがオンになります。 $V_{BIAS}$  が内部ロックアウト・スレッショルド ( $V_{UVBIAS} = 1.63V$  (標準)) を超えると、コンバータが起動し、出力電圧はプログラムされたソフトスタート時間とともにランプ・アップします。

EN がロジックローの場合、デバイスはシャットダウンします。シャットダウンの間、BIAS レギュレータとゲート・ドライバはオフになります。シャットダウン時の電力状態は最も低く、自己消費電流は 4 $\mu$ A (標準) に低下します。EN をハイに駆動すると、デバイスがシャットダウンから復帰します。

## 同期入力 (SYNC)

MAX42405/MAX42406 は SYNC ピンを備えており、これは動作モードの選択および周波数の制御に使用されるロジックレベル入力です。SYNC を BIAS または外部クロックに接続すると、強制固定周波数 (FPWM) 動作がイネーブルになります。SYNC を GND に接続すると、自動スキップモード動作がイネーブルになり、軽負荷時の効率が改善されます。この IC は、SYNC ピンに印加される立上がりエッジで外部クロックに同期します。このデバイスは、2 周期内で外部クロックに同期します。2 クロック周期を過ぎても SYNC に外部クロック信号が現れない場合、デバイスは内部クロックを使用します。

## ソフトスタート

このデバイスは、2.5ms (400kHz 時) と 3.5ms (1.5MHz 時) のソフトスタートを内蔵しています。ソフトスタートは、出力電圧をレギュレーション・ポイントに向けて強制的にランプ・アップすることによって、起動時の突入電流を制限するものです。

## 短絡保護

このデバイスは、出力での短絡および過負荷状態からデバイスを保護する電流制限機能を備えています。短絡または過負荷状態が発生した場合、ハイサイド MOSFET は、インダクタ電流が仕様規定された LX 電流制限スレッショルドに達するまでオンのままになります。次に、コンバータはハイサイド MOSFET をオフ、ローサイド MOSFET をオンにして、インダクタ電流がランプ・ダウンできるようになります。インダクタ電流が電流制限スレッショルドを下回ると、コンバータはハイサイド MOSFET を再びオンにします。この繰り返しが、短絡または過負荷状態が解消されるまで続きます。

電流が制限されている状態で出力電圧が目標値の 25% を下回った場合、ハード・ショートが検出されます。これが発生すると、hiccup モードが起動して、1.5MHz では 35ms の間、400kHz では 25ms の間、出力がオフになります。その後、出力はソフトスタートに入って再び起動します。回路が短絡している間は、この繰り返しがいつまでも続きます。ソフトスタートの間、Hiccup モードはディスエーブルになります。

## サーマル・シャットダウン

サーマル・シャットダウンは、デバイスを過度な動作温度から保護するものです。ジャンクション温度が+175°Cを超えると、内蔵センサーが降圧コンバータをシャットダウンして、ICの温度を下げられるようにします。ジャンクション温度が15°C下がると、センサーによってICが再びオンになります。

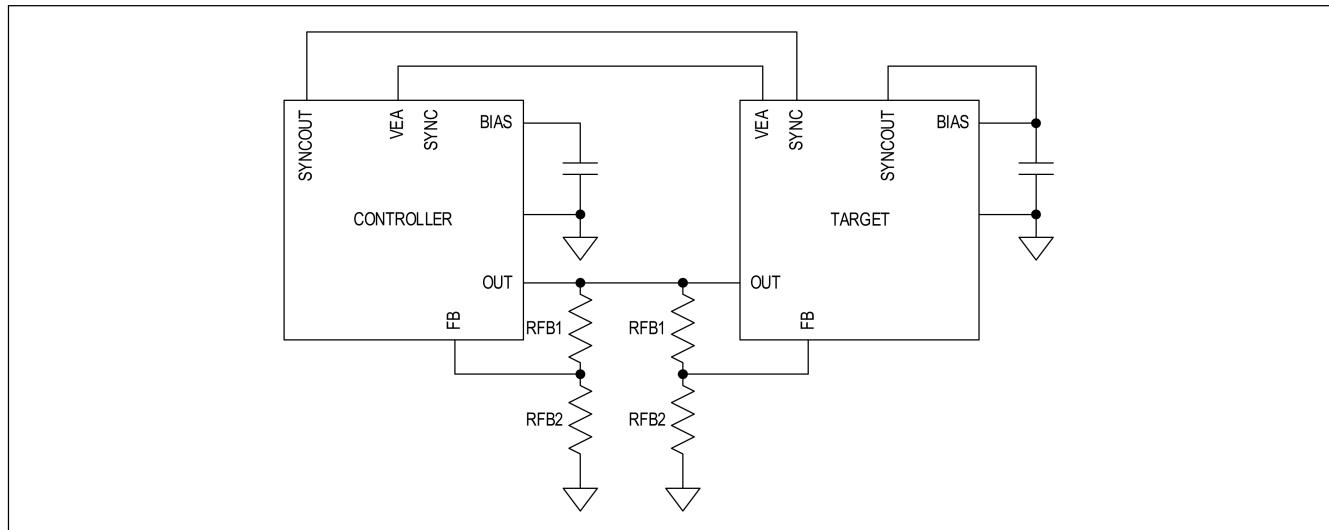

## マルチフェーズ動作

MAX42405/MAX42406は高電流アプリケーションの場合にデュアルフェーズ動作が可能であり、各ICの構成はコントローラまたはターゲットとすることができます。マルチフェーズ動作は、強制PWMモードだけを対象としています。SYNCOUTは、コントローラのクロックと180°の位相差を持つことになります。デバイスがスキップ・モードにある場合、SYNCOUTにはクロックが現れません。デュアルフェーズ構成で低IQ動作を可能にするには、ターゲットのENをディスエーブルにして、そのICをオフにし、自己消費電流を減らします。

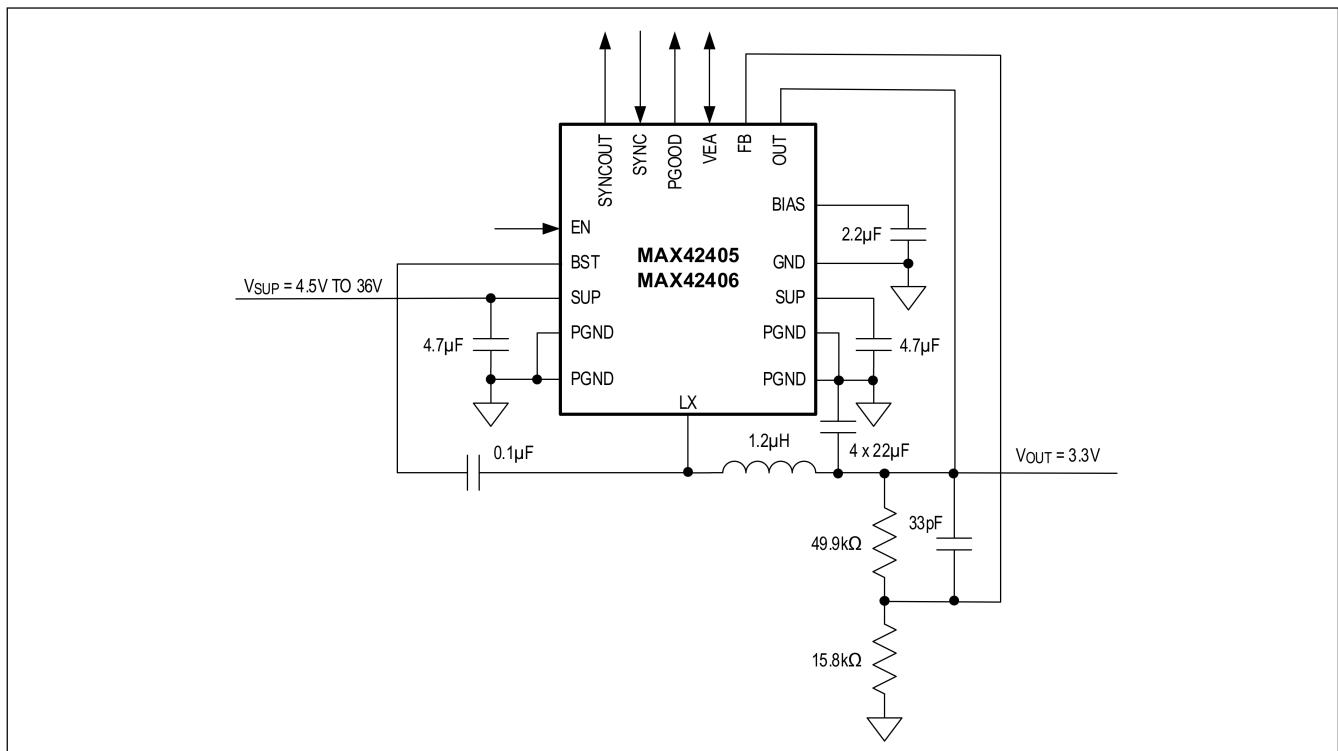

ターゲットの場合、SYNCOUTをBIASに接続します。ENがハイの場合、ICがコントローラなのか(SYNCOUTがBIASに接続されていない)またはターゲットなのかを検出する手順があることになります。VEAピンは、コントローラにとって電圧エラー・アンプの出力になり、ターゲットにとって電流エラー・アンプの入力になります。コントローラのVEAピンをターゲットのVEAピンに接続して、2つのフェーズ間でバランスの取れた電流分担を実現します。2つの別々の抵抗分圧器をICごとに使用して、コントローラとターゲットのFBピン同士が同じポイントに接続されないようにします。ターゲットICは(VEAピンを通して)コントローラの外側電圧ループを使用するので、出力電圧のミスマッチがいずれも避けられます。MAX42405/MAX42406を使用したデュアルフェーズ構成のセットアップについては図1を参照してください。

図1. 標準的なデュアルフェーズ構成のセットアップ

## アプリケーション情報

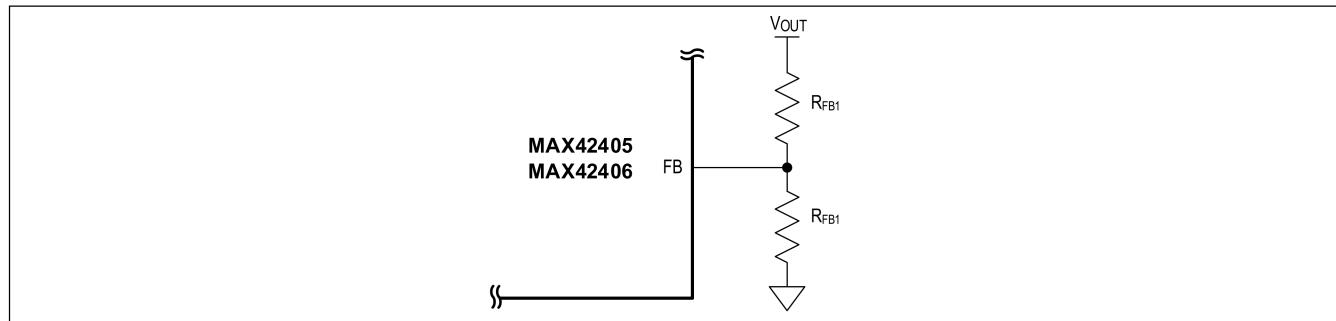

### 出力電圧の設定

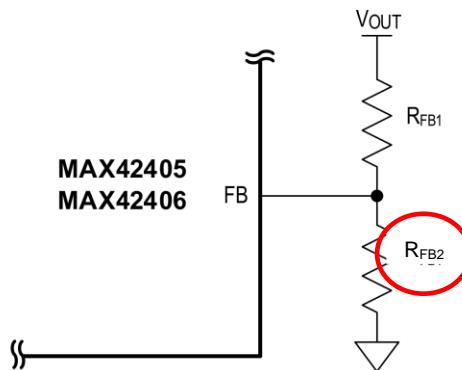

出力を0.8V～10Vに設定するには、出力(OUT)からGNDの間に抵抗分圧器を接続します(図2)。 $R_{FB2}$ (FBからGNDの間の抵抗)を50kΩ以下になるように選択します。次の式を用いて、 $R_{FB1}$ (OUTからFBの間の抵抗)を計算します。

式1:

$$R_{FB1} = R_{FB2} \times \left( \frac{V_{OUT}}{V_{FB}} - 1 \right)$$

ここで、 $V_{FB}$ はフィードバック・レギュレーション電圧です。[電気的特性](#)の表を参照してください。

図2. 外付け抵抗分圧器を使用した出力電圧の設定

表1には、調整可能な出力構成の出力範囲ごとに、選択する推奨部品が示されています。推奨部品は特定のアプリケーションに対して更に最適化できます。 $C_{FF}$ の値が表1に掲載されていますが、これは $R_{FB1} = 50\text{k}\Omega$ に基づいて推奨されたものです。推奨される $C_{FF}$ は $R_{FB1}$ の選択によって変わります。

表1. 推奨部品

| SWITCHING FREQUENCY (kHz) | VOUT (V)   | INDUCTOR (μH) | EFFECTIVE COUT (μF) | CFF (pF) |

|---------------------------|------------|---------------|---------------------|----------|

| 400                       | 0.8 to 1.8 | 1.5           | 440                 | 100      |

|                           | 1.8 to 3   | 3.3           | 440                 | 100      |

|                           | 3 to 5     | 3.3           | 150                 | 47       |

|                           | 5 to 10    | 4.7           | 90                  | 100      |

| 1500                      | 0.8 to 1.8 | 0.47          | 240                 | 10       |

|                           | 1.8 to 3   | 0.56          | 100                 | 33       |

|                           | 3 to 5     | 1.2           | 66                  | 33       |

|                           | 5 to 10    | 2.2           | 44                  | 82       |

### インダクタの選択

インダクタの設計は、サイズ、効率、制御ループの帯域幅、コンバータの安定性などの兼ね合いで決まります。インダクタンス値が足りないと、インダクタ電流のリップルが大きくなり、伝導損失の増加と出力電圧リップルの増大を招くことになります。MAX42405/MAX42406では勾配補償が内部で固定されているので、それが原因となって電流モード制御の不安定性が現れる可能性もあります。インダクタの値が大きいとリップルが抑制されますが、このソリューションのサイズとコストが増加し、応答が遅くなります。選択する公称標準値は、仕様規定されたインダクタンスの±30%以内とします。推奨されるインダクタの値については表1を参照してください。

## 入力コンデンサ

入力フィルタ・コンデンサは、電源から引き出されるピーク電流を抑制し、回路のスイッチングによって入力に生じるノイズおよび電圧リップルを低減します。MAX42405/MAX42406 は、EMI 性能の改善に活用できる対称的なピン配列を取り入れています。2 つの高周波 0603 またはより小型のコンデンサをパッケージの両側にある 2 つの SUP ピンに接続するのは、良好な EMI 性能を得るためにです。4.7 $\mu$ F (またはそれ以上) の高品質、低 ESR のセラミック・コンデンサを SUP ピンに接続するのは、入力電圧リップルを小さくするためです。

通常は、等価直列抵抗 (ESR) が高い、電解コンデンサなどのバルク・コンデンサも、フロントエンド回路の Q を下げるために、また入力電圧リップルを最小限に抑えるのに必要な残りの容量を提供するために必要となります。入力コンデンサの RMS 電流の必要条件 ( $I_{RMS}$ ) は次式で定義されます。

式 6 :

$$I_{RMS} = I_{LOAD(MAX)} \times \left( \frac{\sqrt{V_{OUT} \times (V_{SUP} - V_{OUT})}}{V_{SUP}} \right)$$

$I_{RMS}$  は入力電圧が出力電圧の 2 倍であるときに最大値を取ります。

$$V_{SUP} = 2 \times V_{OUT}$$

従って、

$$I_{RMS} = \frac{I_{LOAD(MAX)}}{2}$$

理想的な長期的信頼性を得るために、この RMS 入力電流における自己発熱による温度上昇が +10°C 未満になる入力コンデンサを選択してください。入力電圧リップルは、 $\Delta V_Q$  (コンデンサの放電によるもの) と  $\Delta V_{ESR}$  (コンデンサの ESR によるもの) で構成されています。入力には、高いリップル電流能力を備えた低 ESR のセラミック・コンデンサを使用します。ESR とコンデンサ放電の寄与分が等しく共に 50% であると仮定します。仕様規定された入力電圧リップルに必要な入力コンデンサと ESR は、次式を使用して計算します。

式 7 :

$$ESR_{IN} = \frac{\Delta V_{ESR}}{I_{OUT} + \Delta I_L / 2}$$

ここで、

$$\Delta I_L = \frac{(V_{SUP} - V_{OUT}) \times V_{OUT}}{V_{SUP} \times f_{SW} \times L}$$

また、

$$C_{IN} = \frac{I_{OUT} \times D(1 - D)}{\Delta V_Q \times f_{SW}}$$

$$D = \frac{V_{OUT}}{V_{SUP}}$$

ここで、

$I_{OUT}$  = 最大出力電流

$D$  = デューティ・サイクル

## 出力コンデンサ

出力容量を選択する際は、出力負荷トランジエント、出力電圧リップル、閉ループ安定性の各必要条件を満たすようにします。負荷ステップ時に、出力電流はほぼ瞬時に変わるのでに対して、インダクタは遅い反応を示します。このトランジエント時間の間に、負荷充電の必要条件が出力コンデンサから与えられるので、出力電圧にアンダーシュート／オーバーシュートが生じます。インダクタ電流で制御する降圧コンバータでは、MAX42405/MAX42406で利用されているように、出力容量も制御ループの安定性に影響を与えます。

出力リップルは、 $\Delta V_Q$ （コンデンサの放電によるもの）と  $\Delta V_{ESR}$ （出力コンデンサの ESR によるもの）で構成されています。出力には、ESR が低いセラミックまたはアルミニウムの電解コンデンサを使用します。アルミニウムの電解コンデンサの場合、出力リップル全体が  $\Delta V_{ESR}$  によるものです。式 8 を使用して、ESR の必要条件を計算し、それに応じてコンデンサを選択します。セラミック・コンデンサを使用する場合、ESR とコンデンサの放電による出力リップル電圧への寄与分は等しいと仮定します。次式は、仕様規定された出力電圧リップルに適した出力容量と ESR の必要条件を示しています。

式 8 :

$$ESR = \frac{\Delta V_{ESR}}{\Delta I_{P-P}}$$

$$C_{OUT} = \frac{\Delta I_{P-P}}{8 \times \Delta V_Q \times f_{SW}}$$

ここで、

$$\Delta I_{P-P} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN} \times f_{SW} \times L}$$

$$V_{OUT\_RIPPLE} = \Delta V_{ESR} + \Delta V_Q$$

$\Delta I_{P-P}$  は上式で計算されたピーク to ピークのインダクタ電流、 $f_{SW}$  はコンバータのスイッチング周波数です。

出力コンデンサは、コンバータがより大きいデューティ・サイクルに応答するまでステップ負荷電流を供給します。出力コンデンサの ESR における抵抗性ドロップとコンデンサ放電によって、ステップ負荷では電圧ドループが生じます。トランジエント負荷とリップルノイズ性能を改善するためには、ESR が低いタンタル・コンデンサとセラミック・コンデンサを組み合わせて使用します。出力電圧の最大偏差は、給電されている電子機器の許容限度未満に保ちます。セラミック・コンデンサを使用する場合、出力容量の放電と ESR ドロップの寄与分がそれぞれ 80% と 20% であると仮定します。次式を使用して、必要な ESR と容量の値を計算します。

式 9 :

$$C_{OUT} = \frac{\Delta I}{\Delta V \times 2\pi \times f_C}$$

ここで、 $\Delta I$  は負荷の変化、 $\Delta V$  は許容電圧ドリーブ、 $f_C$  はループのクロスオーバー周波数であり、この周波数は  $f_{SW}/10$  または 100kHz のいずれか小さい方とします。 $C_{OUT}$  に関する計算はいずれも、容量公差、温度、電圧の減定格を考慮する必要があります。表 1 は、スイッチング周波数および出力電圧に基づいて推奨された出力コンデンサの値を示しています。

## デュアルフェーズ動作

### デュアルフェーズでの低 $I_Q$ 動作

MAX42405/MAX42406 はデュアルフェーズ機能を備えており、各 IC をコントローラまたはターゲットとして構成することができます。コントローラの SYNCOUT ピンは、SYNC がハイに接続されている場合 (FPWM モード)、180° 位相差クロックを出力します。低  $I_Q$  モードでは、コントローラの SYNC ピンをローに引き下げる必要があります (スキップ・モード)。このモードでは、コントローラの SYNCOUT ピンにはクロックが現れず、コントローラ IC はスキップ・モードに入ります。この間、ターゲット IC の内部回路がオンのままになり、コントローラからの SYNCOUT 信号を能動的に探します。ターゲット IC がオンなので、両 IC がパルスをスキップしたとしても、自己消費電流はわずかに高くなります。

軽負荷時の効率を高め、 $I_Q$  を更に低減させるためには、ターゲットの EN をローに引き下げる必要があります。これにより、ターゲットとその内部回路がディスエーブルになり、更に  $I_Q$  が低減します。表 2 に低  $I_Q$  動作の真理値表をまとめています。

表 2. 低  $I_Q$  動作用の構成

| CONTROLLER             | TARGET    | MODE                            |

|------------------------|-----------|---------------------------------|

| EN = High, SYNC = BIAS | EN = High | FPWM (high $I_Q$ )              |

| EN = High, SYNC = Low  | EN = High | Skip mode (low $I_Q$ )          |

| EN = High, SYNC = Low  | EN = Low  | Standby mode (ultra-low $I_Q$ ) |

| EN = Low               | EN = High | Not allowed                     |

## 出力電圧の設定

出力電圧をある値に設定するためには、図 1 に示すように OUT、FB、GND の間に抵抗分圧器を接続します。コントローラとターゲットには、同一であっても別々の抵抗分圧器を推奨します。

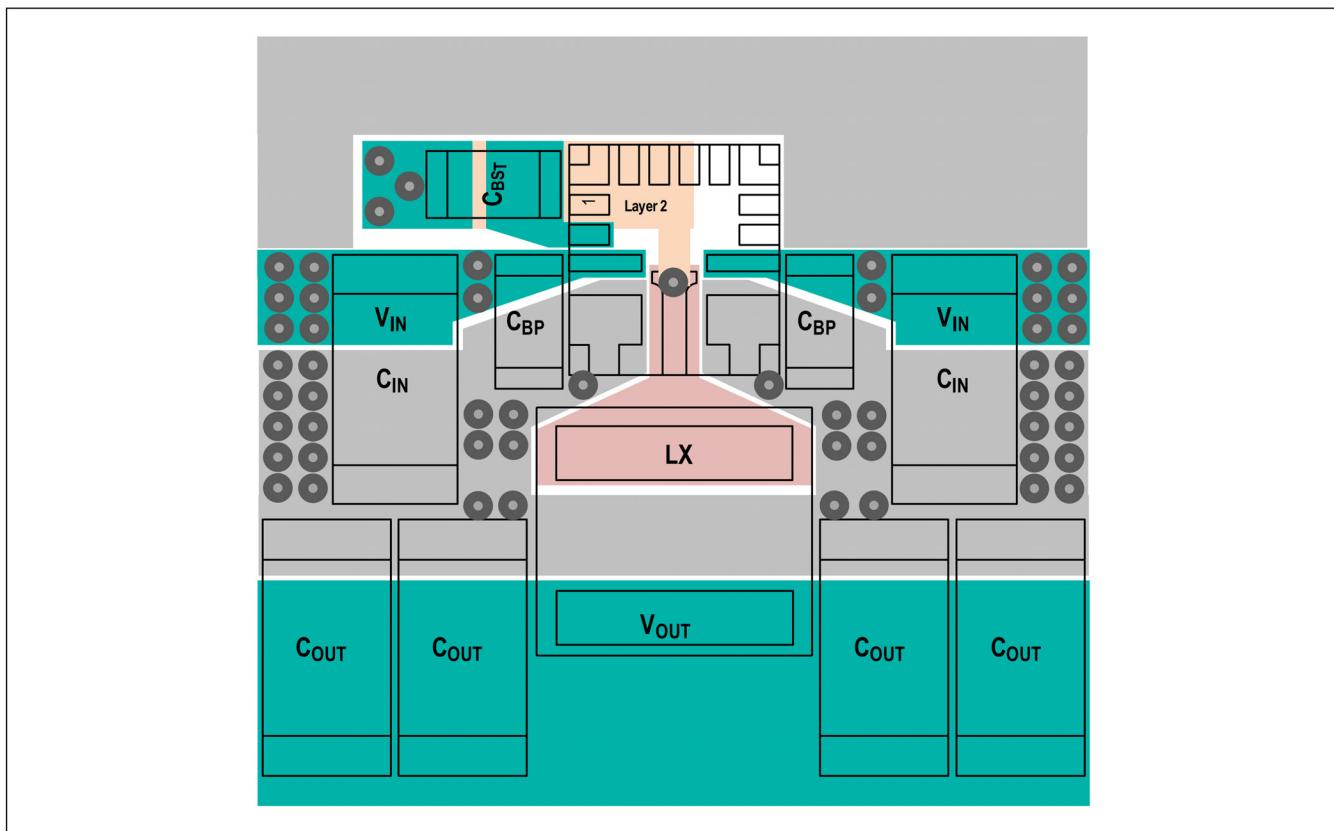

## PCB レイアウトのガイドライン

低スイッチング損失とノイズのない安定した動作を実現するには、慎重な PCB レイアウトが欠かせません。ノイズ耐性と消費電力の改善には可能な限り多層基板を使用します。優れた PCB レイアウトにするためには、図 3 および次のガイドラインを参照してください。

- 1) IC には正確なフットプリントを使用し、IC フットプリントの下にはできるだけ多くの銅プレーンを配置して、効率的な熱伝達を実現します。

- 2) セラミックの入力バイパス・コンデンサ  $C_{BP}$  と  $C_{IN}$  を、IC の両側にある SUP ピンと PGND ピンにできるだけ近づけて配置します。コンデンサと IC ピンの間には、(ビアなどの不連続点がない) 低インピーダンスの接続を使用します。 $C_{BP}$  は、IC の最も近くに配置する必要があり、また非常に優れた高周波性能 (小型パッケージ・サイズおよび高容量) を持つ必要があります。これにより、最適な EMI 除去が実現し、デバイスの内部ノイズは性能を低下させるおそれがあるものですが、これを最小限に抑えられることになります。

- 3) インダクタ (L)、出力コンデンサ ( $C_{OUT}$ )、ブートストラップ・コンデンサ ( $C_{BST}$ )、BIAS コンデンサ ( $C_{BIAS}$ ) を、電流ループで囲まれた面積を最小限にするように配置します。インダクタ (L) を IC の LX ピンにできるだけ近づけて配置し、LX ノードの面積を最小限にします。出力コンデンサ ( $C_{OUT}$ ) をインダクタの近くに配置して、 $C_{OUT}$  のグランド側が  $C_{IN}$  グランド接続の近くになるようにし、電流ループの面積を最小限にします。BIAS コンデンサ ( $C_{BIAS}$ ) を BIAS ピンの隣に配置します。

- 4) ブートストラップ・コンデンサ  $C_{BST}$  を IC に近づけて配置し、短くて幅広の配線パターンを使用してループの面積を最小限にし、寄生インダクタンスを最小限にします。リターン配線パターン ( $C_{BST}$  から LX の間) には最も近い層を使用して、インダクタンスを更に最小限にします。最適設計には、EV キットのレイアウトを参照してください。寄生インダクタンスが高いと、スイッチング速度に影響を与え (スイッチング損失が増加)、大量の  $dv/dt$  ノイズが発生する可能性があります。

- 5) IC に隣接している層には連続的な銅の GND プレーンを使用して、回路全体をシールドします。GND は、回路全体を囲むように上側にも敷き詰める必要があります。すべての放熱部品は冷却のために銅と十分に接続するようにしてください。インピーダンスを低くし、放熱を最大限にするために、複数のビアを使用して GND プレーン／領域を相互に接続します。IC の GND 端子および入力／出力／バイパス・コンデンサにビアを配置します。PGND と GND の接続を別々のプレーンまたは領域で分離したり絶縁したりしないでください。

- 6) フィードバック・ループ抵抗分圧器を (使用する場合には) IC の近くに配置して、フィードバックと OUT の接続をインダクタ、LX ノード、他のノイズの多い信号を避けて配線します。

図 3. PCB レイアウトの例

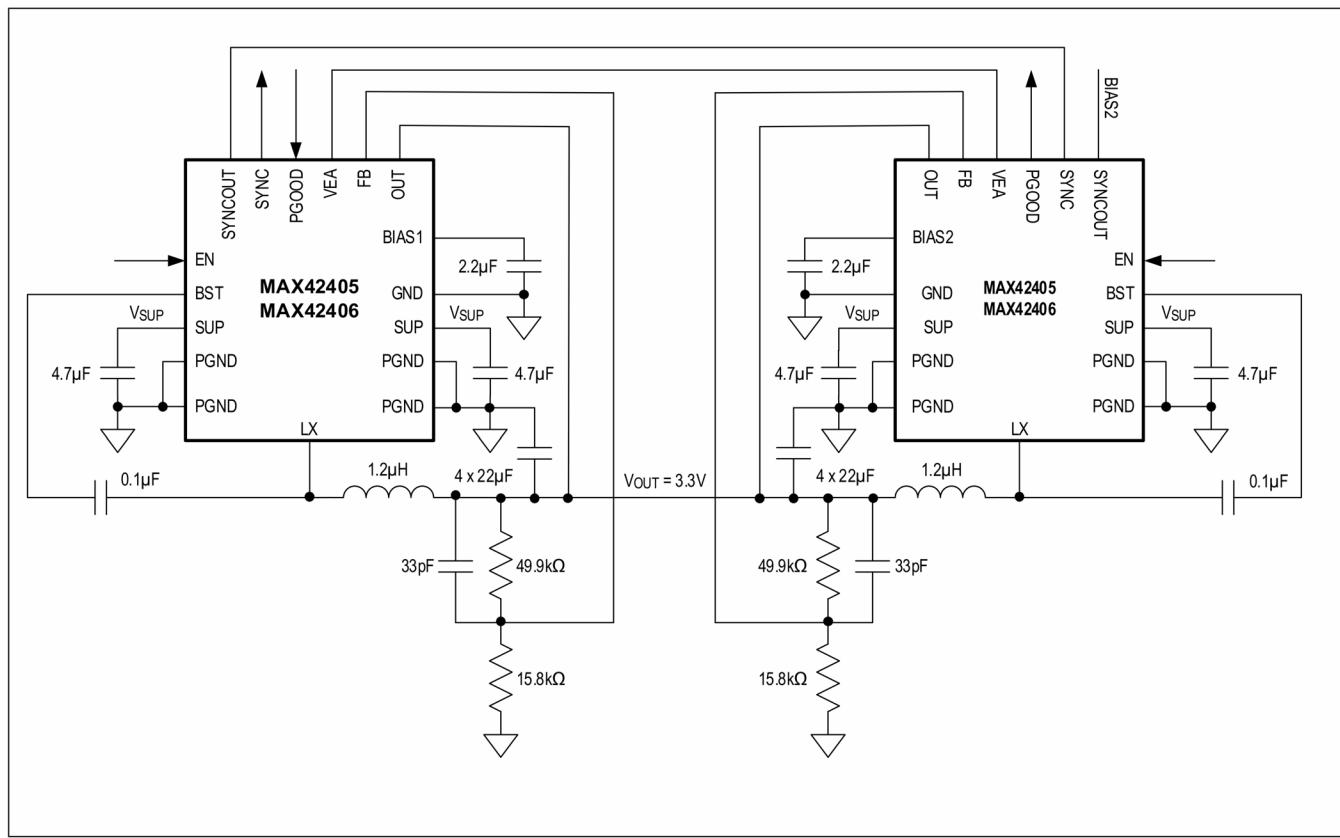

## 代表的なアプリケーション回路

## シングルフェーズ動作（400kHz 時）

## シングルフェーズ動作（1.5MHz 時）

## デュアルフェーズ動作、コントローラ/ターゲット（1.5MHz 時）

## 型番

| PART NUMBER    | V <sub>OUT</sub> (V)   | MAXIMUM LOAD CURRENT (A) | SWITCHING FREQUENCY |

|----------------|------------------------|--------------------------|---------------------|

| MAX42405AFOA+T | Adjustable 0.8V to 10V | 5                        | 400 kHz             |

| MAX42405AFOB+T | Adjustable 0.8V to 10V | 5                        | 1.5 MHz             |

| MAX42406AFOA+T | Adjustable 0.8V to 10V | 6                        | 400 kHz             |

| MAX42406AFOB+T | Adjustable 0.8V to 10V | 6                        | 1.5 MHz             |

+は鉛（Pb）フリー/RoHS準拠のパッケージであることを示します。

T = テープ&リール。

## 改訂履歴

| 版数 | 改訂日   | 説明                                                    | 改訂ページ                       |

|----|-------|-------------------------------------------------------|-----------------------------|

| 0  | 11/23 | 初版発行                                                  | -                           |

| 1  | 12/23 | 概要、特長と利点、絶対最大定格、電気的特性、標準動作特性、詳細、<br>アプリケーション情報の各項目を改訂 | 1, 3, 4, 5, 6, 9,<br>10, 11 |

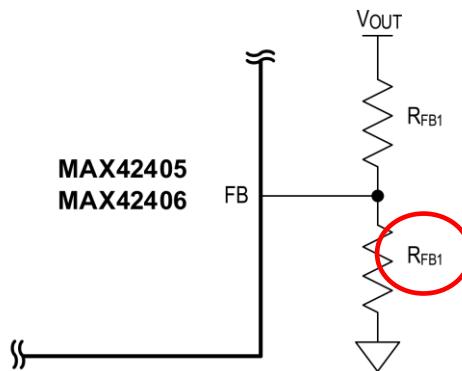

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2024年8月8日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものでです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2024年8月8日

製品名：MAX42405、MAX42406

対象となるデータシートのリビジョン(Rev)：Rev.1

訂正箇所：11頁、図2内の記号（下記の図を参照）

【誤】

【正】