MAX40080

## 高精度で高速サンプリング・レートのデジタル電流センス・アンプ

### 概要

MAX40080 は、高精度で高速応答の双方向電流センス・アンプで、デジタル出力と-0.1V（グランド・センシング）～36V の非常に広い入力コモンモード電圧範囲を備えています。

5 $\mu$ V の超低入力オフセットと、0.2%の非常に低いゲイン・エラーを特長としています。低入力オフセット電圧が特に重要なのは、これによって小さいセンス抵抗が使用でき、消費電力の節約になるにも関わらず、計測精度を損なわないためです。更に、±10mV から±50mV の間でプログラマブルな入力センシング範囲（または 125V/V から 25V/V の間でプログラマブルな入力ゲイン）という特徴もあり、これは低電流時の精度を向上させるのに非常に役立ちます。

内蔵の A/D コンバータはプログラマブルなサンプリング・レートと 12 ビットの分解能（電流計測用の符号ビットを含めて 13 ビット）を備えており、I<sup>2</sup>C に適合した SMBus 対応のインターフェースも特徴となっています。

ウェイクアップ電流スレッショルドと自動シャットダウン・モード（I<sup>2</sup>C が非アクティブの場合）も特徴として挙げられます。この両機能は、消費電力を最小限に抑えるよう設計されています。

デバイスは小型の 12 ピン WLP で（また、12 ピン TDFN でも）提供され、-40°C～+125°C の拡張動作温度範囲での動作がサポートされています。

### アプリケーション

- サーバのバックプレーン

- 基地局の PA 制御

- テレコム機器

- バッテリ駆動デバイス

- 産業用の制御およびオートメーション

### 利点と特長

- プログラマブルなサンプリング・レート：最大1Msps

- 広い入力コモンモード電圧範囲：

-0.1V（グランド・センシング）～36V

- プログラマブルな入力センシング範囲

(±10mV および±50mV)

- 非常に低い5 $\mu$ Vの入力オフセット電圧によって小さいセンス抵抗が使用可能

- I<sup>2</sup>Cに適合したSMBus対応のインターフェース（スマート・モードで電力を節約）：

- ウェイクアップ電流スレッショルド

- 低計測レート：4回／秒

- 自動シャットダウン（I<sup>2</sup>Cが非アクティブの場合）

- 双方向の電流センシング

- コモンモード電圧を36Vまでモニタリング

- スペースを節約する12バンプWLP (0.4mmピッチ) および12ピンTDFN

- ピーク電流の記録

- プログラマブルな過電流／過電圧スレッショルドおよび低電圧スレッショルド

- プログラマブルな応答時間を備えたアラート出力

- 深さが64セルのFIFO

型番はデータシート末尾に記載されています。

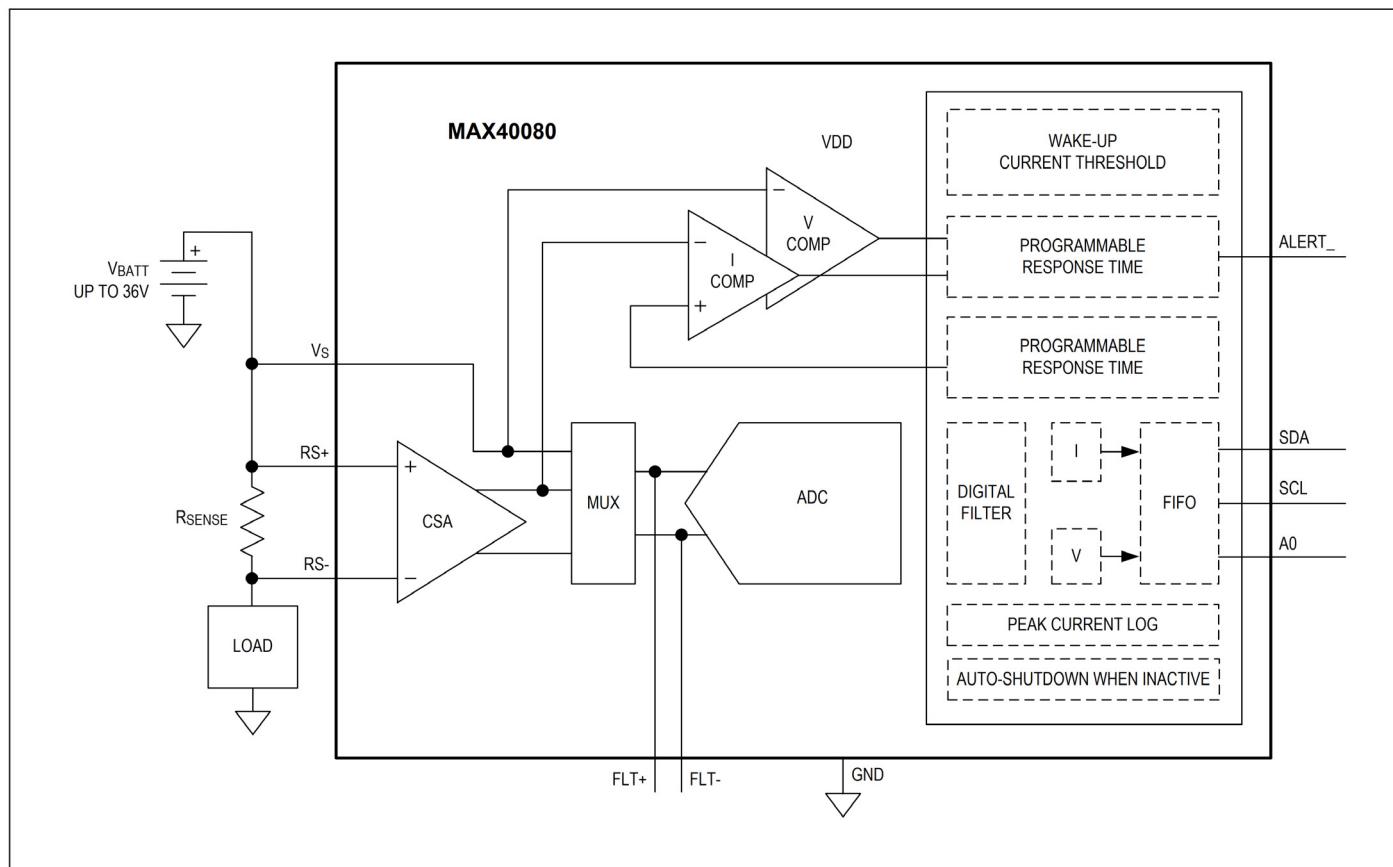

## ブロック図

## 目次

|                                             |    |

|---------------------------------------------|----|

| 概要                                          | 1  |

| アプリケーション                                    | 1  |

| 特長と利点                                       | 1  |

| ブロック図                                       | 2  |

| 絶対最大定格                                      | 7  |

| パッケージ情報                                     | 8  |

| WLP                                         | 8  |

| TDFN*                                       | 9  |

| 電気的特性                                       | 11 |

| 標準動作特性                                      | 15 |

| ピン配置                                        | 19 |

| WLP-12                                      | 19 |

| TDFN                                        | 19 |

| 端子説明                                        | 20 |

| 詳細                                          | 21 |

| I <sup>2</sup> C に適合した SMBus 対応のバス・インターフェース | 21 |

| I <sup>2</sup> C スレーブ・アドレス                  | 24 |

| I <sup>2</sup> C 通信速度                       | 25 |

| 最大 3.4MHz の動作に向けた HS モードの稼働                 | 25 |

| 動作モード                                       | 26 |

| クイック・コマンド                                   | 26 |

| アラート管理                                      | 26 |

| 内部レジスタ                                      | 27 |

| 設定レジスタ                                      | 28 |

| 動作モード                                       | 28 |

| I <sup>2</sup> C タイムアウト                     | 28 |

| アラート応答時間                                    | 28 |

| PEC                                         | 28 |

| 入力範囲                                        | 29 |

| HS モードの維持                                   | 29 |

| ADC のサンプリング・レート                             | 29 |

| デジタル・フィルタ                                   | 29 |

| ステータス・レジスタ                                  | 30 |

| ウェイクアップ電流                                   | 30 |

| 変換完了                                        | 31 |

| オーバーフロー電流                                   | 31 |

| オーバーフロー電圧またはアンダーフロー電圧                       | 31 |

| I <sup>2</sup> C タイムアウト                     | 31 |

| FIFO アラーム                                   | 31 |

| FIFO オーバーフロー                                | 31 |

## 目次（続き）

|                                    |    |

|------------------------------------|----|

| FIFO データ・カウント .....                | 31 |

| スレッショルド・レジスタおよびウェイクアップ電流レジスタ ..... | 31 |

| MAX_Peak_Current .....             | 32 |

| FIFO の設定 .....                     | 32 |

| Store IV .....                     | 32 |

| Overflow_Threshold .....           | 32 |

| RO .....                           | 32 |

| フラッシュ .....                        | 33 |

| FIFO からの電流および電圧の読出し .....          | 33 |

| INT_EN .....                       | 33 |

| アプリケーション情報 .....                   | 34 |

| フィルタの選択 .....                      | 34 |

| FIFO のデータ読出しレート .....              | 34 |

| 型番 .....                           | 36 |

| 改訂履歴 .....                         | 37 |

---

**図一覧**

|                                           |    |

|-------------------------------------------|----|

| 図 1. I <sup>2</sup> C/SMBus のタイミング図 ..... | 21 |

| 図 2. 2 バイトの書込み（ワード書込み） .....              | 21 |

| 図 3. 2 バイトの書込み（PEC バイト有り） .....           | 22 |

| 図 4. 2 バイトの読み出し（ワード読み出し） .....            | 22 |

| 図 5. 2 バイトの読み出し（PEC バイト有り） .....          | 22 |

| 図 6. 1 バイトの読み出し .....                     | 23 |

| 図 7. 1 バイトの読み出し（PEC 有り） .....             | 23 |

| 図 8. Read 32 .....                        | 23 |

| 図 9. Read 32 (PEC 有り) .....               | 24 |

| 図 10. HS モードの稼働 .....                     | 26 |

| 図 11. クイック・コマンド .....                     | 26 |

**表一覧**

|                                                            |    |

|------------------------------------------------------------|----|

| 表 1. I <sup>2</sup> C スレーブ・アドレス .....                      | 24 |

| 表 2. レジスタ機能と POR 状態 .....                                  | 27 |

| 表 3. 動作モード .....                                           | 28 |

| 表 4. サンプリング・レートの選択 .....                                   | 29 |

| 表 5. デジタル・フィルタの選択 .....                                    | 30 |

| 表 6. 出力データ・レートとサンプリング・レートの関係 .....                         | 30 |

| 表 7. スレッシュホールド・レジスタおよびウェイクアップ電流レジスタ .....                  | 31 |

| 表 8. フィルタ・コンデンサの選択 .....                                   | 34 |

| 表 9. FIFO のデータ読み出しレートと I <sup>2</sup> C インタフェース速度の関係 ..... | 34 |

| 表 10. 2 バイトの読み出し .....                                     | 35 |

| 表 11. 4 バイトの読み出し .....                                     | 35 |

**絶対最大定格**

|                                   |                              |

|-----------------------------------|------------------------------|

| V <sub>DD</sub> ～GND .....        | -0.3V～+2V                    |

| RS+～RS- .....                     | ±2V                          |

| V <sub>S</sub> 、RS+、RS-～GND ..... | -0.3V～+40V                   |

| 他のすべてのピン～GND .....                | -0.3V～V <sub>DD</sub> + 0.3V |

| 入力ピンへの連続電流 .....                  | 10mA                         |

|                                                                             |              |

|-----------------------------------------------------------------------------|--------------|

| 連続消費電力（多層基板）(T <sub>A</sub> = +70°C、+70°Cを超えると<br>13.73mW/Cでディレイティング) ..... | 1098.60mW    |

| 動作温度範囲 .....                                                                | -40°C～125°C  |

| ジャンクション温度 .....                                                             | +150°C       |

| 保存温度範囲 .....                                                                | -40°C～+150°C |

| はんだ処理温度（リフロー） .....                                                         | +260°C       |

上記の**絶対最大定格**を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## パッケージ情報

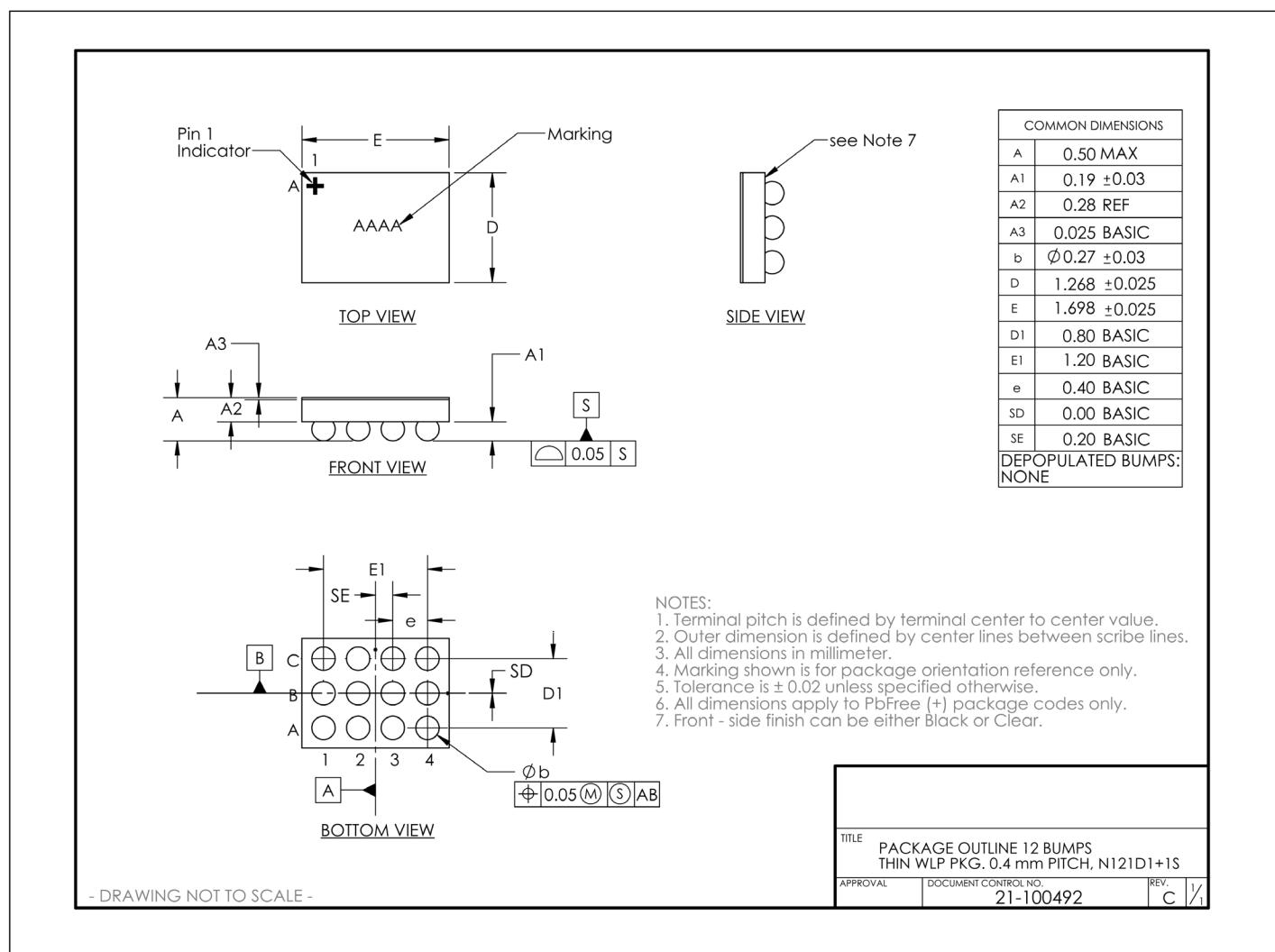

## WLP

|                                                       |                                |

|-------------------------------------------------------|--------------------------------|

| Package Code                                          | N121D1+1S                      |

| Outline Number                                        | 21-100492                      |

| Land Pattern Number                                   | Refer to Application Note 1891 |

| <b>Thermal Resistance, Four-Layer Board:</b>          |                                |

| Junction-to-Ambient ( $\theta_{JA}$ )                 | 72.82°C/W                      |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 17.90°C/W                      |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、[www.maximintegrated.com/packages](http://www.maximintegrated.com/packages) で確認してください。パッケージ・コードの「+」、「#」、「-」はRoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面はRoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、[www.maxim-ic.com/thermal-tutorial](http://www.maxim-ic.com/thermal-tutorial) を参照してください。

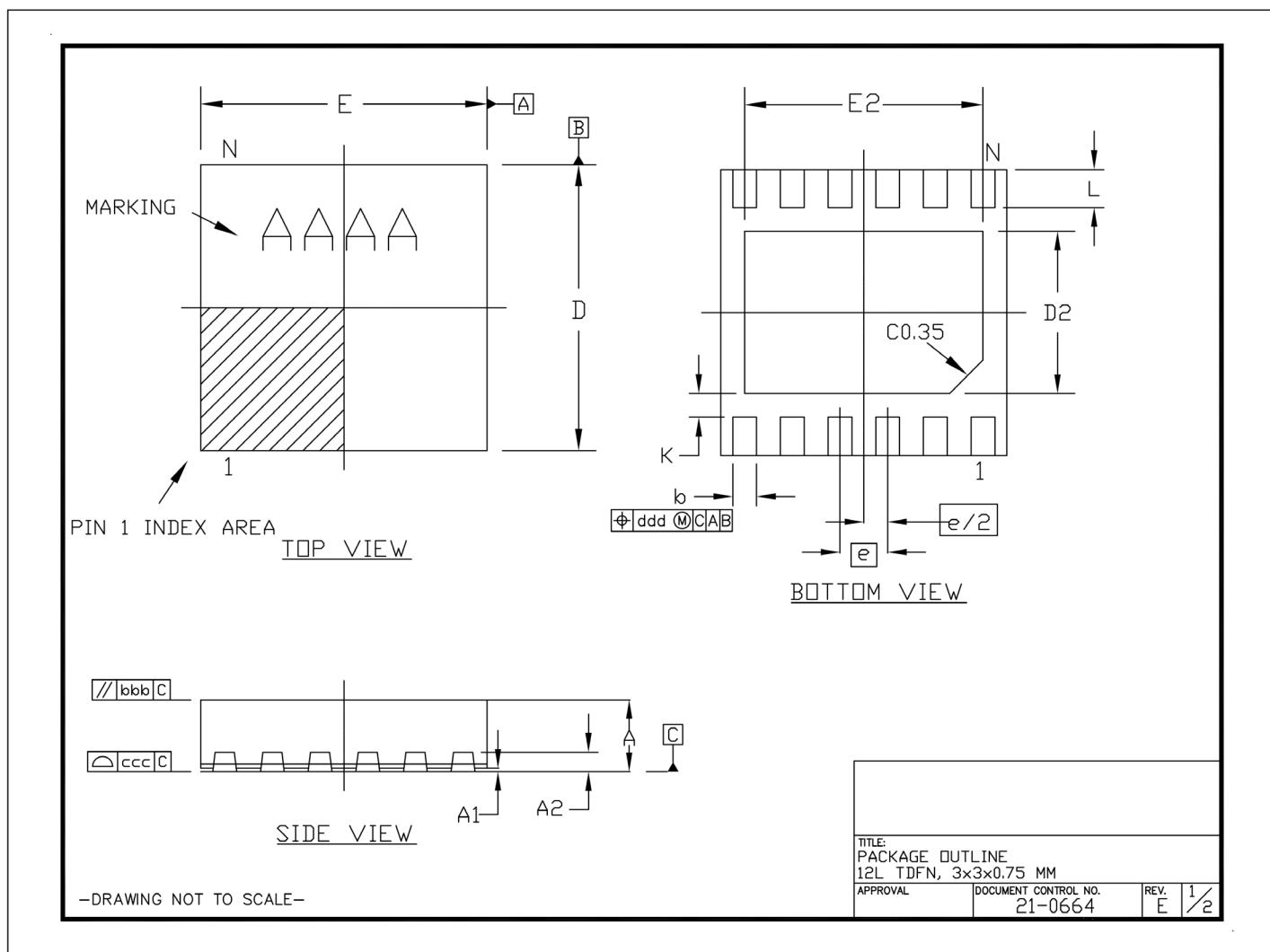

## TDFN\*

|                                                       |           |

|-------------------------------------------------------|-----------|

| Package Code                                          | TD1233+1C |

| Outline Number                                        | 21-0664   |

| Land Pattern Number                                   | 90-0397   |

| <b>Thermal Resistance, Single-Layer Board:</b>        |           |

| Junction-to-Ambient ( $\theta_{JA}$ )                 | 63 °C/W   |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 8.5 °C/W  |

| <b>Thermal Resistance, Four-Layer Board:</b>          |           |

| Junction-to-Ambient ( $\theta_{JA}$ )                 | 41 °C/W   |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 8.5 °C/W  |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、[www.maximintegrated.com/packages](http://www.maximintegrated.com/packages) で確認してください。パッケージ・コードの「+」、「#」、「-」はRoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面はRoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、[www.maxim-ic.com/thermal-tutorial](http://www.maxim-ic.com/thermal-tutorial) を参照してください。

| DIMENSIONAL REFERENCES |        |                     |       |      |                      |       |      |

|------------------------|--------|---------------------|-------|------|----------------------|-------|------|

|                        | SYMBOL | MIN                 | NOM   | MAX  | MIN                  | NOM   | MAX  |

| TOTAL THICKNESS        | A      | 0.7                 | 0.75  | 0.8  | 0.7                  | 0.75  | 0.8  |

| STAND OFF              | A1     | 0                   | 0.035 | 0.05 | 0                    | 0.035 | 0.05 |

| L/F THICKNESS          | A2     | 0.203 REF           |       |      | 0.203 REF            |       |      |

| LEAD WIDTH             | b      | 0.2                 | 0.25  | 0.3  | 0.2                  | 0.25  | 0.3  |

| BODY SIZE              | D      | 2.9                 | 3.0   | 3.1  | 2.95                 | 3.00  | 3.05 |

|                        | E      | 2.9                 | 3.0   | 3.1  | 2.95                 | 3.00  | 3.05 |

| LEAD PITCH             | e      | 0.5 BSC             |       |      | 0.5 BSC              |       |      |

| EP SIZE                | D2     | 1.6                 | 1.7   | 1.8  | 1.45                 | 1.55  | 1.65 |

|                        | E2     | 2.4                 | 2.5   | 2.6  | 2.4                  | 2.50  | 2.6  |

| LEAD LENGTH            | L      | 0.35                | 0.4   | 0.45 | 0.30                 | 0.4   | 0.50 |

| PACKAGE EDGE TOLERANCE | aaa    | 0.1                 |       |      | 0.1                  |       |      |

| MOLD FLATNESS          | bbb    | 0.1                 |       |      | 0.1                  |       |      |

| COPLANARITY            | ccc    | 0.08                |       |      | 0.08                 |       |      |

| LEAD OFFSET            | ddd    | 0.1                 |       |      | 0.1                  |       |      |

| EXP PAD TO LEAD EDGE   | K      | 0.25 min            |       |      | 0.25 min             |       |      |

| LEAD COUNT             | N      | 12                  |       |      | 12                   |       |      |

| PKG CODE:              |        | TD1233+1, TD1233+1C |       |      | TD1233+2, TD1233+2C, |       |      |

## NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. WARPAGE SHALL NOT EXCEED 0.10 mm.

3. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

4. COPLANARITY SHALL NOT EXCEED 0.08 mm.

5. MARKING SHOWN IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

6. ALL DIMENSIONS APPLY TO PbFREE (+) PKG. CODES ONLY.

-DRAWING NOT TO SCALE-

|                                                 |                                 |               |

|-------------------------------------------------|---------------------------------|---------------|

|                                                 |                                 |               |

| TITLE: PACKAGE OUTLINE<br>12L TDFN, 3x3x0.75 MM |                                 |               |

| APPROVAL                                        | DOCUMENT CONTROL NO.<br>21-0664 | REV.<br>E 2/2 |

**電気的特性**

(特に指定のない限り、 $V_{DD} = 1.8V$ 、 $V_{RS+} = V_{RS-} = +12V$ 、 $V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V$ 、 $V_S = +12V$ 、 $T_A = +25^\circ C$  での値であり、最小限界値および最大限界値は  $T_A = -40^\circ C \sim +125^\circ C$  の範囲内の値です。 (Note 1) )

| PARAMETER                                      | SYMBOL      | CONDITIONS                                                                                                                                                          | MIN      | TYP                   | MAX | UNITS           |

|------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------|-----|-----------------|

| <b>CURRENT MEASUREMENT</b>                     |             |                                                                                                                                                                     |          |                       |     |                 |

| Input Common Mode Range                        | $V_{CM}$    |                                                                                                                                                                     | -0.1     | 36                    | 36  | V               |

| Input Voltage Sense                            | $V_{SENSE}$ | ( $RS_+ - RS_-$ ), Option #1 programmable with I <sup>2</sup> C                                                                                                     |          | $\pm 50$              |     | mV              |

|                                                |             | ( $RS_+ - RS_-$ ), Option #2 programmable with I <sup>2</sup> C                                                                                                     |          | $\pm 10$              |     |                 |

| CSA Gain                                       | G           | $V_{SENSE} = \pm 10mV$ , Option #1 programmable with I <sup>2</sup> C                                                                                               |          | 125                   |     | VV              |

|                                                |             | $V_{SENSE} = \pm 10mV$ , Option #1 programmable with I <sup>2</sup> C                                                                                               |          | 25                    |     |                 |

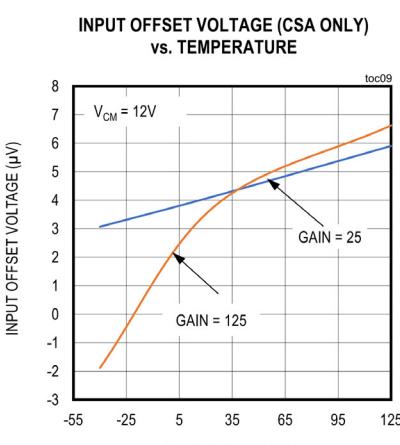

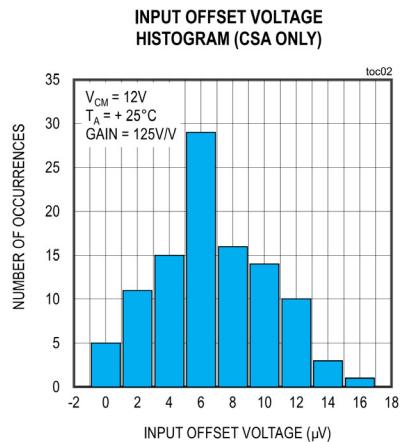

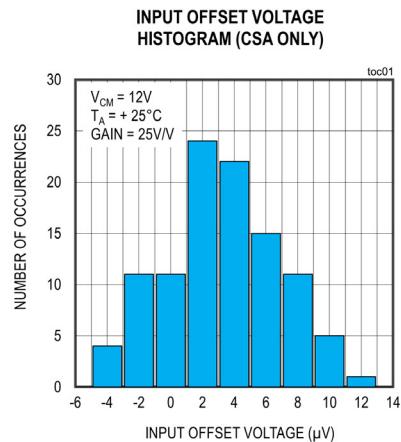

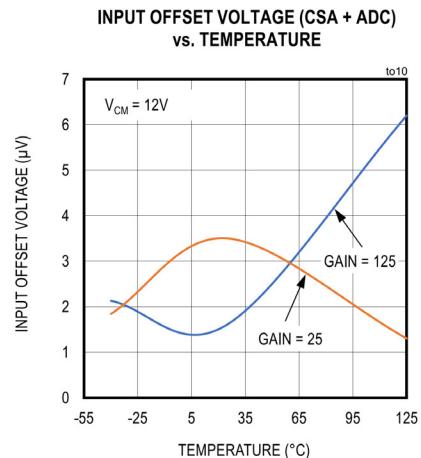

| Input Offset Voltage (CSA only)                | $V_{OS}$    | $T_A = +25^\circ C$                                                                                                                                                 | 5        | 20                    |     | $\mu V$         |

|                                                |             | $-40^\circ C \leq T_A \leq +125^\circ C$                                                                                                                            | 5        | 45                    |     |                 |

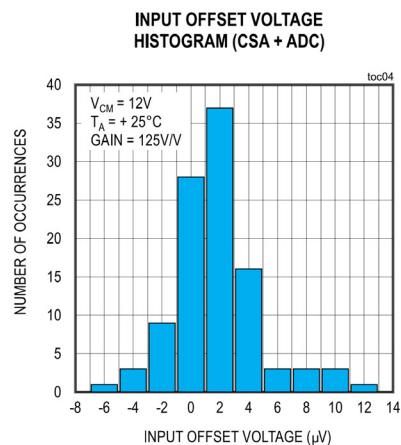

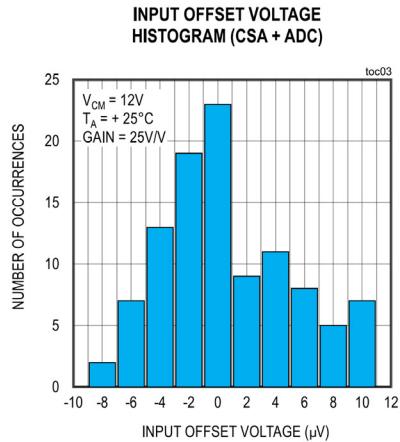

| Input Offset Voltage (CSA + ADC)               | $V_{OS}$    | $T_A = +25^\circ C$                                                                                                                                                 | 5        | 25                    |     | $\mu V$         |

|                                                |             | $-40^\circ C \leq T_A \leq +125^\circ C$                                                                                                                            | 5        | 55                    |     |                 |

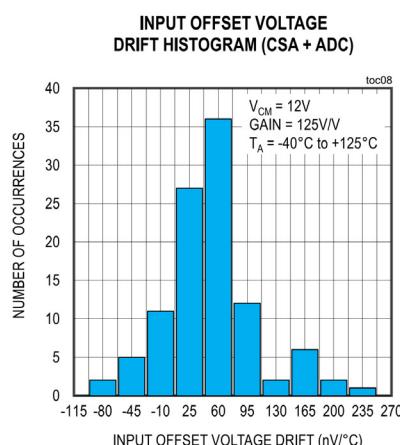

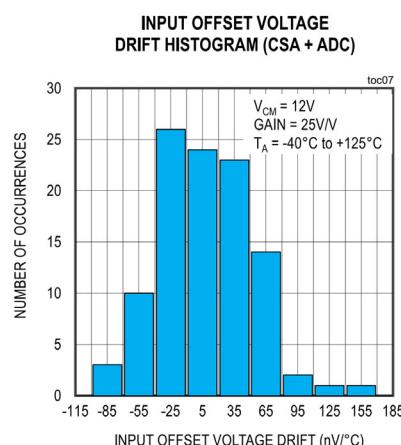

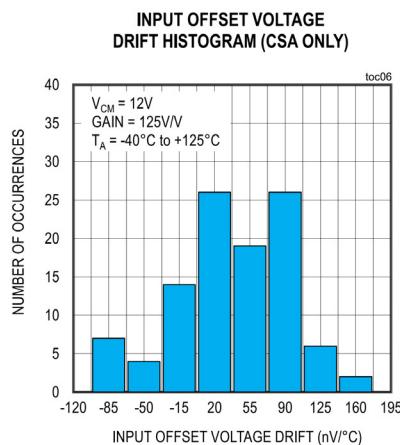

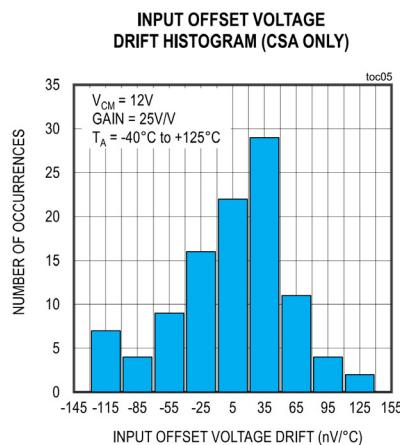

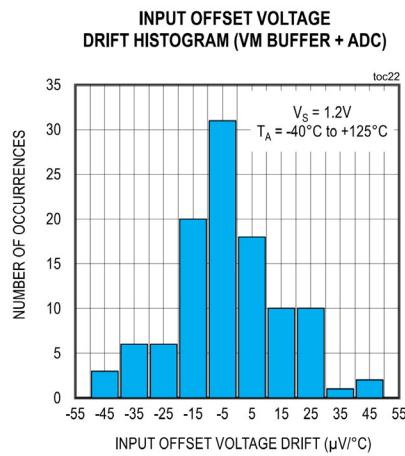

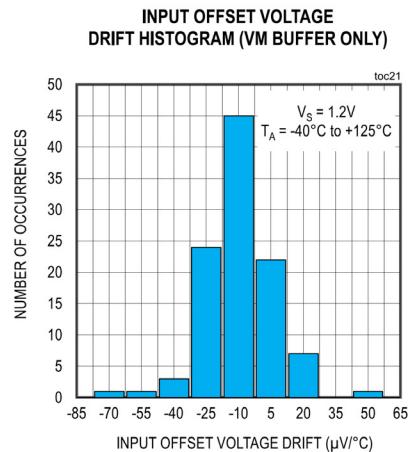

| Input Offset Drift                             | $TCV_{OS}$  |                                                                                                                                                                     |          | 50                    |     | nV/ $^\circ C$  |

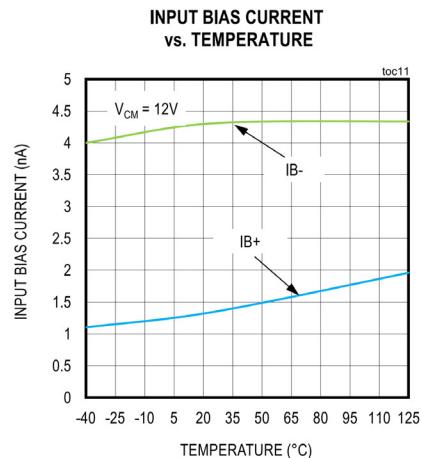

| Input Bias Current                             | $I_B$       | $-40^\circ C \leq T_A \leq +125^\circ C$                                                                                                                            | 1        | 20                    |     | nA              |

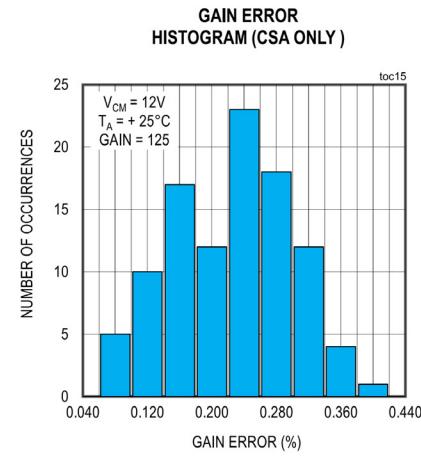

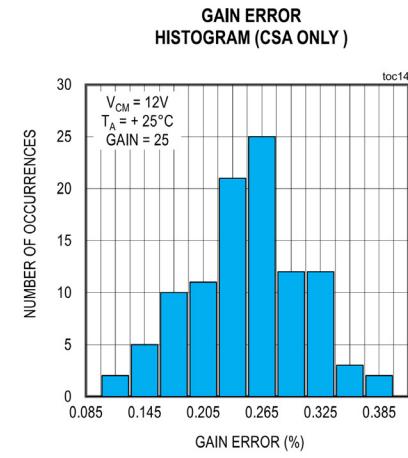

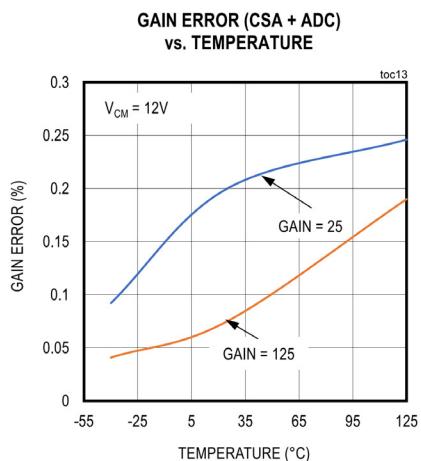

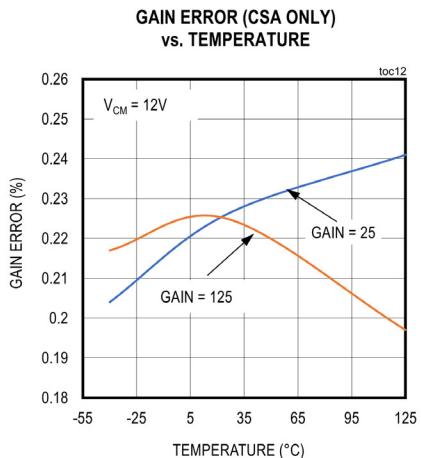

| Gain Error (CSA only)                          | GE          | $T_A = +25^\circ C$                                                                                                                                                 | 0.2      | 0.55                  |     | %               |

|                                                |             | $-40^\circ C \leq T_A \leq +125^\circ C$                                                                                                                            | 0.2      | 0.75                  |     |                 |

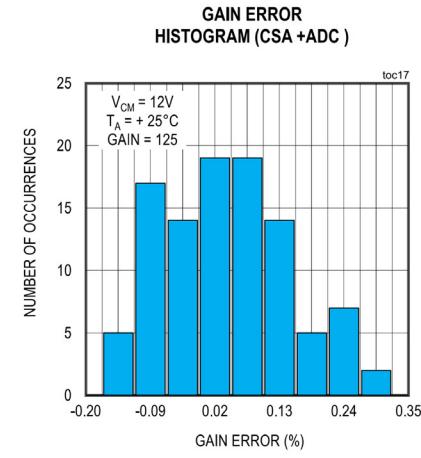

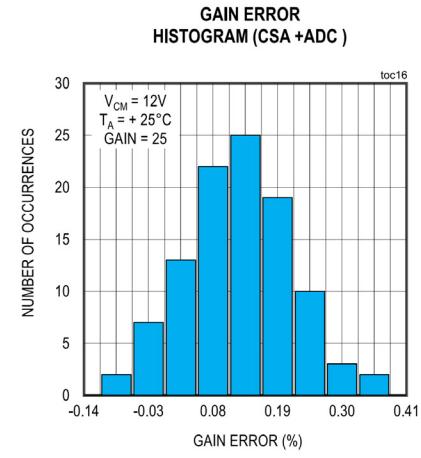

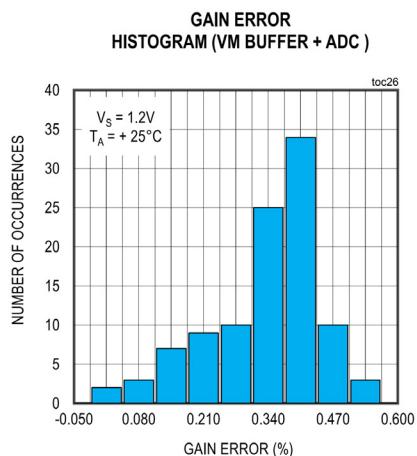

| Gain Error (CSA + ADC)                         | GE          | $T_A = +25^\circ C$                                                                                                                                                 | 0.05     | 0.5                   |     | %               |

|                                                |             | $-40^\circ C \leq T_A \leq +125^\circ C$                                                                                                                            | 0.05     | 1.05                  |     |                 |

| Common Mode Rejection Ratio (CSA only)         | CMRR        |                                                                                                                                                                     | 123      | 140                   |     | dB              |

| Common Mode Rejection Ratio (CSA + ADC)        | CMRR        |                                                                                                                                                                     | 119      | 140                   |     | dB              |

| Power Supply Rejection Ratio (CSA only)        | PSRR        |                                                                                                                                                                     | 76       | 110                   |     | dB              |

| Power Supply Rejection Ratio (CSA + ADC)       | PSRR        |                                                                                                                                                                     | 76       | 110                   |     | dB              |

| Input Voltage-Noise Density                    | $V_N$       | $V_{SENSE} = (V_{RS+} - V_{RS-}) = 50mV$                                                                                                                            | f = 1kHz | 47                    |     | nV/ $\sqrt{Hz}$ |

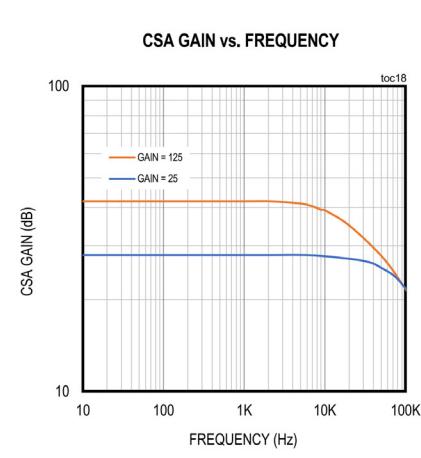

| Small Signal Bandwidth                         | BW          | $V_{SENSE} = (V_{RS+} - V_{RS-}) = \pm 50mV$                                                                                                                        |          | 50                    |     | kHz             |

|                                                |             | $V_{SENSE} = (V_{RS+} - V_{RS-}) = \pm 10mV$                                                                                                                        |          | 10                    |     |                 |

| Wake-up and Over-Current Thresholds Resolution |             | $V_{SENSE} = \pm 50mV$                                                                                                                                              |          | 0.78                  |     | mV              |

| Wake-up Response Time                          |             | Sampling Rate = 15ksps                                                                                                                                              |          | 32.7                  |     | ms              |

| Over-Current Response Time                     |             | Unfiltered ( $D4 = 0$ )<br>Filtered ( $D4 = 1$ ), Sample Rate = 15ksps<br>Filtered ( $D4 = 1$ ), Sample Rate = 60ksps<br>Filtered ( $D4 = 1$ ), Sample Rate = 1Msps |          | 31<br>294<br>88<br>35 |     | $\mu s$         |

## 電気的特性（続き）

(特に指定のない限り、 $V_{DD} = 1.8V$ 、 $V_{RS+} = V_{RS-} = +12V$ 、 $V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V$ 、 $V_S = +12V$ 、 $T_A = +25^\circ C$  での値であり、最小限界値および最大限界値は  $T_A = -40^\circ C \sim +125^\circ C$  の範囲内の値です。 (Note 1) )

| PARAMETER                                          | SYMBOL       | CONDITIONS                                                                                                                                                          | MIN | TYP                   | MAX | UNITS |

|----------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------|-----|-------|

| <b>INPUT VOLTAGE MEASUREMENT</b>                   |              |                                                                                                                                                                     |     |                       |     |       |

| Input Voltage Range                                | $V_S$        |                                                                                                                                                                     | 0   | 36                    |     | V     |

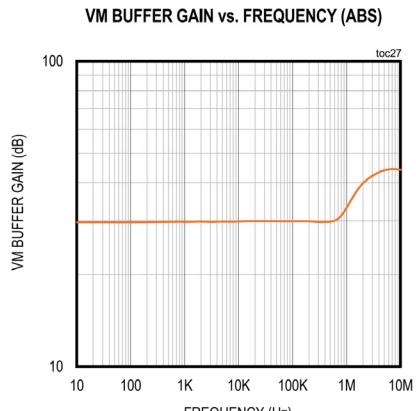

| Voltage Buffer Gain                                | G            |                                                                                                                                                                     |     | 1/30                  |     | V/V   |

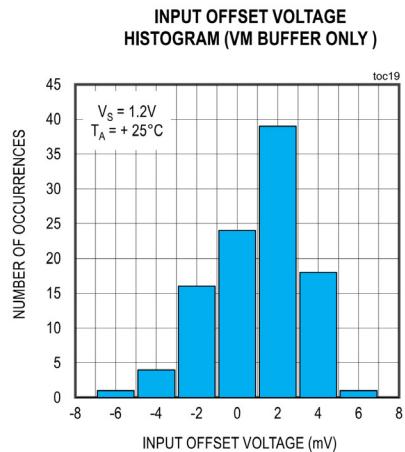

| Input Offset Voltage (Voltage Buffer only)         | $V_{OS}$     | Referred to $V_S$ , $V_S = 1.2V$                                                                                                                                    |     | 1.5                   | 21  | mV    |

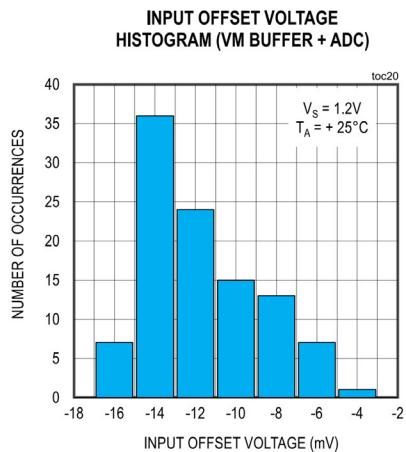

| Input Offset Voltage (Voltage Buffer + ADC)        | $V_{OS}$     | Referred to $V_S$ , $V_S = 1.2V$                                                                                                                                    |     | 1.5                   | 35  | mV    |

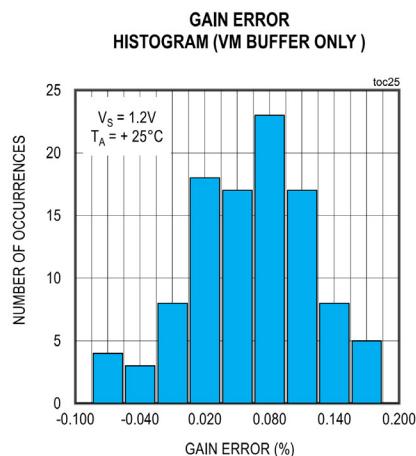

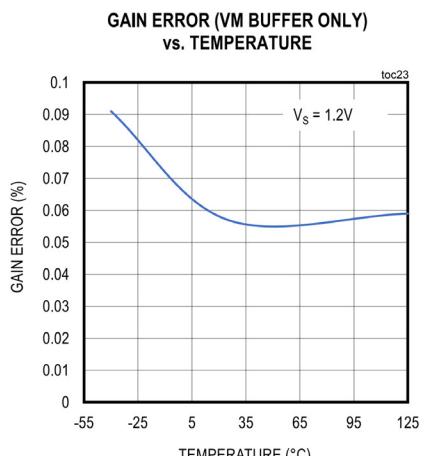

| Gain Error (Voltage Buffer only)                   | $GE$         |                                                                                                                                                                     |     | 0.05                  | 0.4 | %     |

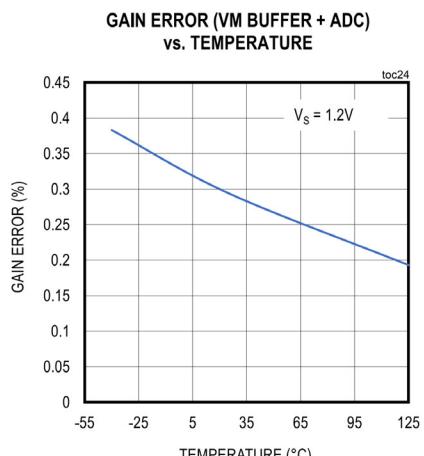

| Gain Error (Voltage Buffer + ADC)                  | $GE$         |                                                                                                                                                                     |     | 0.2                   | 1.2 | %     |

| Input Voltage Signal Bandwidth                     | BW           |                                                                                                                                                                     |     | 1                     |     | kHz   |

| Over/Under-Voltage Thresholds Resolution           |              | Referred to $V_S$                                                                                                                                                   |     | 0.586                 |     | V     |

| Input Impedance                                    | $Z_{IN}$     |                                                                                                                                                                     |     | 6.5                   |     | MΩ    |

| Over/Under-Voltage Response Time                   |              | Unfiltered ( $D4 = 0$ )<br>Filtered ( $D4 = 1$ ), Sample Rate = 15ksps<br>Filtered ( $D4 = 1$ ), Sample Rate = 60ksps<br>Filtered ( $D4 = 1$ ), Sample Rate = 1Msps |     | 31<br>294<br>88<br>35 |     | μs    |

| <b>ADC CHARACTERISTICS</b>                         |              |                                                                                                                                                                     |     |                       |     |       |

| Sample Frequency                                   | $f_S$        | Programmable through I <sup>2</sup> C                                                                                                                               | 15  | 1,000                 |     | Ksps  |

| Resolution                                         |              | (Note 2)                                                                                                                                                            |     | 12                    |     | bits  |

| Internal Reference Voltage                         | $V_{REF}$    |                                                                                                                                                                     |     | 1.25                  |     | V     |

| Switching Time                                     | $t_S$        | From current to voltage measurement or vice-versa                                                                                                                   |     | 1                     |     | ms    |

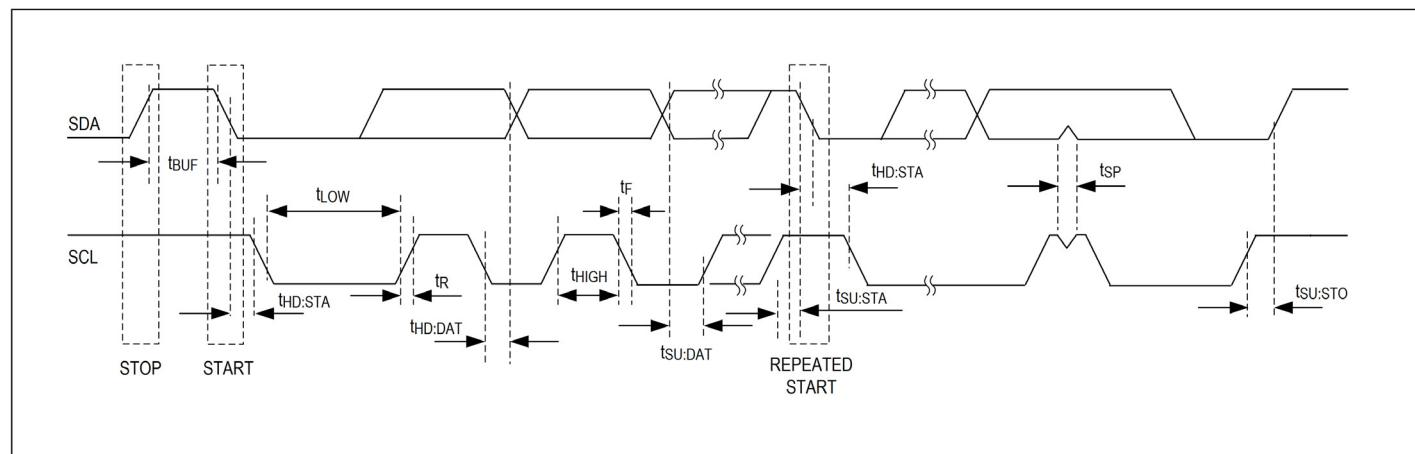

| <b>I<sup>2</sup>C TIMING (UP TO 1MHz) (Note 3)</b> |              |                                                                                                                                                                     |     |                       |     |       |

| Serial Clock Frequency                             | $f_{SCL}$    |                                                                                                                                                                     |     | 1                     |     | MHz   |

| Bus Free Time Between Start and Stop Conditions    | $t_{BUF}$    |                                                                                                                                                                     |     | 0.5                   |     | μs    |

| START Condition Hold Time                          | $t_{HD:STA}$ |                                                                                                                                                                     |     | 0.26                  |     | μs    |

| STOP Condition Setup Time                          | $t_{SU:STO}$ | 90% of SCL to 10% of SDA                                                                                                                                            |     | 0.26                  |     | μs    |

| Clock Low Period                                   | $t_{LOW}$    |                                                                                                                                                                     |     | 0.5                   |     | μs    |

| Clock High Period                                  | $t_{HIGH}$   |                                                                                                                                                                     |     | 0.26                  |     | μs    |

| START Condition Setup Time                         | $t_{SU:STA}$ | 90% of SCL to 90% of SDA                                                                                                                                            |     | 0.26                  |     | μs    |

| Data Setup Time                                    | $t_{SU:DAT}$ | 10% of SDA to 10% of SCL                                                                                                                                            |     | 50                    |     | ns    |

| Data In Hold Time                                  | $t_{HD:DAT}$ | 10% of SCL to 10% of SDA                                                                                                                                            |     | 0                     |     | μs    |

## 電気的特性（続き）

(特に指定のない限り、 $V_{DD} = 1.8V$ 、 $V_{RS+} = V_{RS-} = +12V$ 、 $V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V$ 、 $V_S = +12V$ 、 $T_A = +25^{\circ}C$  での値であり、最小限界値および最大限界値は  $T_A = -40^{\circ}C \sim +125^{\circ}C$  の範囲内の値です。 (Note 1) )

| PARAMETER                                                                 | SYMBOL       | CONDITIONS               | MIN                  | TYP | MAX | UNITS |

|---------------------------------------------------------------------------|--------------|--------------------------|----------------------|-----|-----|-------|

| Minimum Receive SCL/SDA Rise Time                                         | $t_R$        | (Note 3)                 | 20 + 0.1CB           |     |     | ns    |

| Maximum Receive SCL/SDA Rise Time                                         | $t_R$        | (Note 3)                 | 120                  |     |     | ns    |

| Minimum Receive SCL/SDA Fall Time                                         | $t_F$        | (Note 3)                 | 20 + 0.1CB           |     |     | ns    |

| Maximum Receive SCL/SDA Fall Time                                         | $t_F$        | (Note 3)                 | 120                  |     |     | ns    |

| Transmit SDA Fall Time                                                    | $t_F$        | Bus capacitance = 550pF. |                      | 120 |     | ns    |

| Maximum Pulse Width of Spikes That Must Be Suppressed by the Input Filter |              |                          |                      | 50  |     | ns    |

| Capacitive Load for Each Bus Line                                         | $C_B$        |                          | 550                  |     |     | pF    |

| <b>I<sup>2</sup>C TIMING (HS MODE UP TO 3.4MHz) (Note 3)</b>              |              |                          |                      |     |     |       |

| Serial Clock Frequency                                                    | $f_{SCL}$    |                          |                      | 3.4 |     | MHz   |

| START Condition Hold Time                                                 | $t_{HD:STA}$ |                          | 160                  |     |     | ns    |

| START Condition Setup Time                                                | $t_{SU:STA}$ | 90% of SCL to 90% of SDA | 160                  |     |     | ns    |

| Clock Low Period                                                          | $t_{LOW}$    |                          | 160                  |     |     | ns    |

| Clock High Period                                                         | $t_{HIGH}$   |                          | 60                   |     |     | ns    |

| Data Setup Time                                                           | $t_{SU:DAT}$ | 10% of SDA to 10% of SCL | 10                   |     |     | ns    |

| Data In Hold Time                                                         | $t_{HD:DAT}$ | 10% of SCL to 10% of SDA | 35                   |     |     | ns    |

| Minimum Receive SCL/SDA Rise Time                                         | $t_R$        | (Note 3)                 | 20 + 0.1CB           |     |     | ns    |

| Maximum Receive SCL/SDA Rise Time                                         | $t_R$        | (Note 3)                 | 120                  |     |     | ns    |

| Minimum Receive SCL/SDA Fall Time                                         | $t_F$        | (Note 3)                 | 20 + 0.1CB           |     |     | ns    |

| Maximum Receive SCL/SDA Fall Time                                         | $t_F$        | (Note 3)                 | 120                  |     |     | ns    |

| STOP Condition Setup Time                                                 | $t_{SU:STO}$ | 90% of SCL to 10% of SDA | 160                  |     |     | ns    |

| Capacitive Load for Each Bus Line                                         | $C_B$        |                          | 100                  |     |     | pF    |

| Maximum Pulse Width of Spikes That Must Be Suppressed by the Input Filter |              |                          | 10                   |     |     | ns    |

| <b>LOGIC (SDA, SCL, A0, ALERT_) DC CHARACTERISTICS</b>                    |              |                          |                      |     |     |       |

| Input High Voltage                                                        | $V_{IH}$     |                          | 0.7 x $V_{DD}$ + 0.3 |     |     | V     |

## 電気的特性（続き）

（特に指定のない限り、 $V_{DD} = 1.8V$ 、 $V_{RS+} = V_{RS-} = +12V$ 、 $V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V$ 、 $V_S = +12V$ 、 $T_A = +25^\circ C$  での値であり、最小限界値および最大限界値は  $T_A = -40^\circ C \sim +125^\circ C$  の範囲内の値です。 [\(Note 1\)](#) ）

| PARAMETER                                      | SYMBOL       | CONDITIONS                                                                                                                           |                                                                     | MIN  | TYP         | MAX                 | UNITS   |

|------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|-------------|---------------------|---------|

| Input Low Voltage                              | $V_{IL}$     |                                                                                                                                      |                                                                     | -0.3 |             | $0.3 \times V_{DD}$ | V       |

| Input High Leakage Current                     | $I_{IH}$     | Logic Input to $DV_{DD}$                                                                                                             |                                                                     | -1   | $\pm 0.005$ | +1                  | $\mu A$ |

| Input Low Leakage Current                      | $I_{IL}$     | Logic Input to 0V                                                                                                                    |                                                                     | -1   | $\pm 0.005$ | +1                  | $\mu A$ |

| Input Capacitance                              | $C_{IN}$     |                                                                                                                                      |                                                                     |      | 5           |                     | $pF$    |

| Output Low Voltage                             | $V_{OL}$     | $I_{OL} = 3mA$                                                                                                                       |                                                                     | 0    |             | 0.3                 | V       |

| Output High Leakage Current                    |              | $V_{OUT} = V_{DD}$                                                                                                                   |                                                                     |      | $\pm 0.005$ | 1                   | $\mu A$ |

| <b>POWER SUPPLY</b>                            |              |                                                                                                                                      |                                                                     |      |             |                     |         |

| Supply Voltage Range                           | $V_{DD}$     | Guaranteed by PSRR                                                                                                                   |                                                                     | 1.71 |             | 1.98                | V       |

| Active Power Supply Current                    | $I_{ACTIVE}$ | Active mode, $I^2C$ inactive                                                                                                         | $-40^\circ C \leq T_A \leq +125^\circ C$                            |      | 2700        | 3500                | $\mu A$ |

| Low-Power Mode Supply Current                  | $I_{LP}$     | $I^2C$ inactive, ADC is shutdown, current-sense takes one measurement every 50ms                                                     | $-40^\circ C \leq T_A \leq +125^\circ C$                            |      | 52          | 85                  | $\mu A$ |

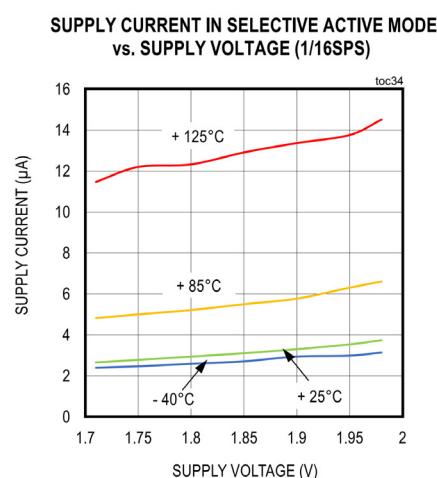

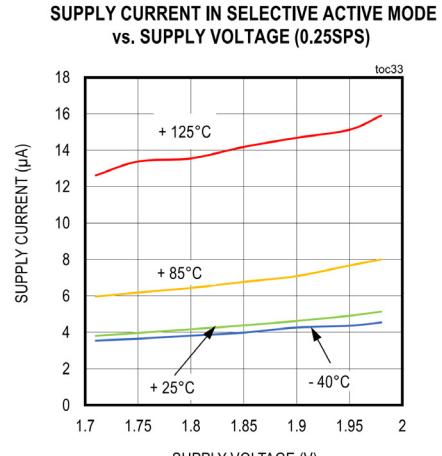

| Average Supply Current in Selected Active Mode | $I_{AVE}$    | $I^2C$ inactive, 4 conversions/s                                                                                                     | $-40^\circ C \leq T_A \leq +125^\circ C$                            |      | 41          | 65                  | $\mu A$ |

|                                                |              | $I^2C$ inactive, 1 conversions/s                                                                                                     | $-40^\circ C \leq T_A \leq +125^\circ C$ ( <a href="#">Note 3</a> ) |      | 18          | 38                  |         |

|                                                |              | $I^2C$ inactive, 0.25 conversions/s                                                                                                  | $-40^\circ C \leq T_A \leq +125^\circ C$ ( <a href="#">Note 3</a> ) |      | 14          | 27                  |         |

|                                                |              | $I^2C$ inactive, 0.0625 conversions/s                                                                                                | $-40^\circ C \leq T_A \leq +125^\circ C$ ( <a href="#">Note 3</a> ) |      | 13          | 23                  |         |

| Standby Supply Current                         | $I_{SDBY}$   | In Standby and between conversions, $I^2C$ bus inactive                                                                              | $-40^\circ C \leq T_A \leq +125^\circ C$                            |      | 2.7         | 15                  | $\mu A$ |

| Turn-On Time                                   | $t_{EN}$     | In Low-Power Mode, analog current-sense wakes up every 50ms. Measured current is below programmed value in "Wakeup Current" register |                                                                     |      | 300         |                     | $\mu s$ |

|                                                |              | From Low-Power Mode to Active Mode. From Standby to either Active Mode or Selected Active Mode or Single Measurement Mode            |                                                                     |      | 500         |                     |         |

| Power-On Time                                  | $t_{ON}$     | $V_{DD} = 0V$ to $1.8V$                                                                                                              |                                                                     |      | 100         |                     | ms      |

[Note 1](#) : すべてのデバイスは、 $T_A = +25^\circ C$  で 100% 製造テストされています。 温度制限範囲全体の仕様は、設計および特性評価によって裏付けられています。

[Note 2](#) : 12 ビットのデータに電流計測用の符号ビットが 1 ビット追加されます。

[Note 3](#) : 設計により裏付けられています。

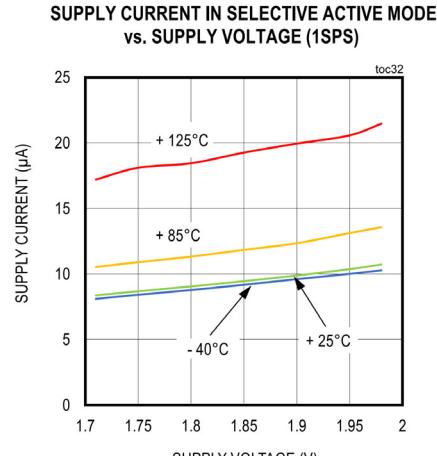

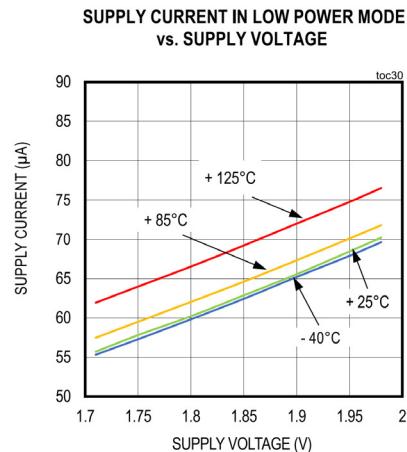

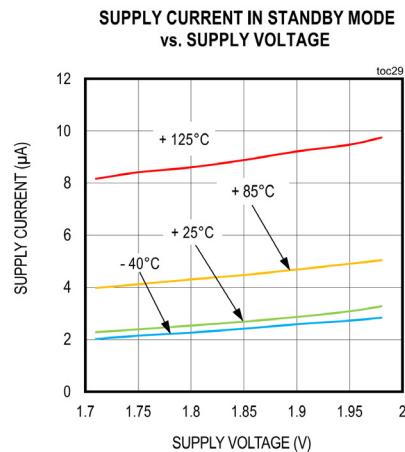

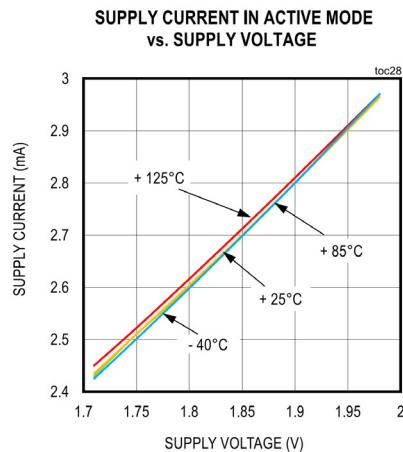

**標準動作特性**

(特に指定のない限り、 $V_{DD} = 1.8V$ 、 $V_{RS+} = V_{RS-} = +12V$ 、 $V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V$ 、 $V_S = +12V$ 、 $T_A = +25^\circ C$ での値であり、最小限界値および最大限界値は $T_A = -40^\circ C \sim +125^\circ C$ の範囲内の値です。)

## 標準動作特性（続き）

(特に指定のない限り、 $V_{DD} = 1.8V$ 、 $V_{RS+} = V_{RS-} = +12V$ 、 $V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V$ 、 $V_S = +12V$ 、 $T_A = +25^\circ C$ での値であり、最小限界値および最大限界値は $T_A = -40^\circ C \sim +125^\circ C$ の範囲内の値です。)

## 標準動作特性（続き）

(特に指定のない限り、 $V_{DD} = 1.8V$ 、 $V_{RS+} = V_{RS-} = +12V$ 、 $V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V$ 、 $V_S = +12V$ 、 $T_A = +25^\circ C$ での値であり、最小限界値および最大限界値は $T_A = -40^\circ C \sim +125^\circ C$ の範囲内の値です。)

## 標準動作特性（続き）

(特に指定のない限り、 $V_{DD} = 1.8V$ 、 $V_{RS+} = V_{RS-} = +12V$ 、 $V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V$ 、 $V_S = +12V$ 、 $T_A = +25^\circ C$ での値であり、最小限界値および最大限界値は $T_A = -40^\circ C \sim +125^\circ C$ の範囲内の値です。)

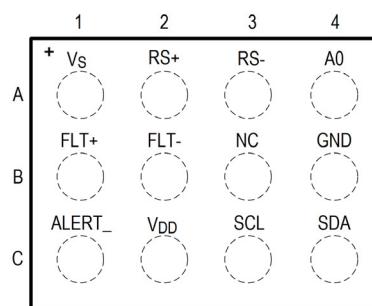

**ピン配置****WLP-12**TOP VIEW

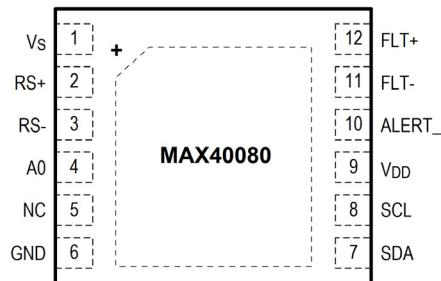

**MAX40080****12-WLP****TDFN**

TOP VIEW

**TDFN-EP**

(3mm x 3mm)

## 端子説明

| ピン     |      | 名称              | 説明                                     |

|--------|------|-----------------|----------------------------------------|

| WLP-12 | TDFN |                 |                                        |

| A1     | 1    | V <sub>S</sub>  | 入力電圧センス                                |

| A2     | 2    | RS+             | 正の電流センス入力                              |

| A3     | 3    | RS-             | 負の電流センス入力                              |

| A4     | 4    | A0              | アドレス入力。外付け抵抗に接続します。                    |

| B1     | 12   | FLT+            | FLT+と FLT-の間にコンデンサを接続して入力信号の帯域幅を制限します。 |

| B2     | 11   | FLT-            | FLT+と FLT-の間にコンデンサを接続して入力信号の帯域幅を制限します。 |

| B3     | 5    | NC              | 接続不可                                   |

| B4     | 6    | GND             | グランド                                   |

| C1     | 10   | ALERT_          | I <sup>2</sup> C 割込み／アラート出力（アクティブ・ロー）  |

| C2     | 9    | V <sub>DD</sub> | アナログ正電源電圧                              |

| C3     | 8    | SCL             | I <sup>2</sup> C クロック                  |

| C4     | 7    | SDA             | I <sup>2</sup> C データ                   |

**詳細**

MAX40080 は、電流とコモンモード電圧を計測し、そのデータをデジタル形式に変換します。変換結果へのアクセスを可能にするのが、I<sup>2</sup>C 対応の 2 線式シリアル・インターフェースです。標準的な I<sup>2</sup>C コマンドによって、データの読み出しや他の動作特性の設定が可能になります。電流/電圧レジスタを読み出している間は、計測される電流および電圧に生じるどのような変化も、読み出しが完了するまで無視されます。電流/電圧レジスタは、読み出し動作が完了すると、次の計測のために更新されます。

**I<sup>2</sup>C に適合した SMBus 対応のバス・インターフェース**

標準的な I<sup>2</sup>C に適合した 2 線式シリアル・インターフェースで、電流および電圧のレジスタから電流/電圧を読み出します。設定レジスタとの間で、制御ビットの読み出しや書き込みも行います。更にこのインターフェースは、選択可能なパケット・エラー・チェック (PEC) など、有益な SMBus 機能に対応しています。SMBus タイムアウトには対応していないため、この SMBus インターフェースは SMBus 対応であるものの、完全には適合していません。

図 1. I<sup>2</sup>C/SMBus のタイミング図

通常のトランザクションは、それぞれ 2 バイトの書き込みおよび読み出しで構成されています。しかし、レジスタによっては 1 バイトの読み出しもあり、またあるレジスタは 4 バイトの読み出しだけです。PEC が有効の場合、バイトが 1 つ追加されます。トランザクションを長くすることは推奨しません。トランザクションは常にスタート (S) 条件で始まり、その後にスレーブ・アドレスと書き込み/読み出しふィットが続きます。

2 バイトの書き込みトランザクション（ワード書き込み）は、マスターがスタート条件を発生し、MAX40080 のスレーブ・アドレス、続いて書き込みビットをそれぞれ送信することから始まります。デバイスは ACK (A) ビットでアクノリッジし、マスターがターゲット・レジスタを送信した後、MAX40080 からの別の ACK が続けます。次に、マスターは 2 つのデータ・バイトを書き込み、MAX40080 はそれに ACK で応答します。マスターは、ストップ (P) 条件を発生してトランザクションを終了します。より多くのバイトを書き込むと（推奨しませんが）、単にレジスタが上書きされます（例えば、4 バイトの書き込みでは、データ・ロー、データ・ハイ、データ・ロー、データ・ハイのように上書きされます）。

| DIRECTION | M → S | M → S         | M → S | S → M | M → S           | S → M | M → S           | S → M | M → S            | S → M | M → S |

|-----------|-------|---------------|-------|-------|-----------------|-------|-----------------|-------|------------------|-------|-------|

| BITS      | 1     | 7             | 1     | 1     | 8               | 1     | 8               | 1     | 8                | 1     | 1     |

| CONTENT   | S     | SLAVE ADDRESS | WR    | A     | REGISTER SELECT | A     | DATA BYTE [7:0] | A     | DATA BYTE [15:8] | A     | P     |

図 2.2 バイトの書き込み（ワード書き込み）

パケット・エラー・チェック (PEC) がイネーブルの場合、書き込みトランザクションは同様ですが、PEC バイト (SLAVE ADDRESS、REGISTER ADDRESS、DATA LOW、DATA HIGH を用いて計算) が、2 番目のデータ・バイトに続く ACK ビットの後に、マスターによって追加される点が異なります。

3バイトの倍数ではない書き込みを試みても、すべて無視されます。3バイトを複数セット書き込む場合、PEC バイトは上記のバイトに加えて、最初の PEC バイトと 2 番目のデータ・ローおよびデータ・ハイのバイトを用いて計算されます。ここでも、PEC が有効の 3 バイトを超える書き込みは推奨しません。

| DIRECTION | M → S | M → S         | M → S | S → M | M → S           | S → M | M → S           | S → M | M → S            | S → M | M → S    | S → M | M → S |

|-----------|-------|---------------|-------|-------|-----------------|-------|-----------------|-------|------------------|-------|----------|-------|-------|

| BITS      | 1     | 7             | 1     | 1     | 8               | 1     | 8               | 1     | 8                | 1     | 8        | 1     | 1     |

| CONTENT   | S     | SLAVE ADDRESS | WR    | A     | REGISTER SELECT | A     | DATA BYTE [7:0] | A     | DATA BYTE [15:8] | A     | PEC BYTE | A     | P     |

図 3.2 バイトの書き込み (PEC バイト有り)

2 バイトの読み出し (ワード読み出し) は書き込みより少し複雑です。マスタは、レジスタ・バイトを送信して本デバイスから ACK を受信した後、反復スタート (Sr) を発生し、アドレスと読み出しひつを書き込みます。次に本デバイスは、アドレス/バイト読み出しに ACK で応答し、2 つのデータ・バイトを送信します。マスタは、最初のデータ・バイトに ACK で応答し、2 番目のデータ・バイトに NACK で応答して、トランザクションが完了したことを通知し、次にストップ条件を発生します。

| DIRECTION | M → S | M → S         | M → S | S → M | M → S           | S → M |

|-----------|-------|---------------|-------|-------|-----------------|-------|

| BITS      | 1     | 7             | 1     | 1     | 8               | 1     |

| CONTENT   | S     | SLAVE ADDRESS | WR    | A     | REGISTER SELECT | A     |

| M → S | M → S         | M → S | S → M | S → M           | M → S | S → M            | M → S | M → S |

|-------|---------------|-------|-------|-----------------|-------|------------------|-------|-------|

| 1     | 7             | 1     | 1     | 8               | 1     | 8                | 1     | 1     |

| Sr    | SLAVE ADDRESS | Rd    | A     | DATA BYTE [7:0] | A     | DATA BYTE [15:8] | N     | P     |

図 4.2 バイトの読み出し (ワード読み出し)

パケット・エラー・チェック (PEC) が有効の場合、読み出しへトランザクションは同様ですが、2 番目のデータ・バイトに続く ACK ビットの後に、PEC バイトが本デバイスによって追加される点が異なります。

| DIRECTION | M → S | M → S         | M → S | S → M | M → S           | S → M |

|-----------|-------|---------------|-------|-------|-----------------|-------|

| BITS      | 1     | 7             | 1     | 1     | 8               | 1     |

| CONTENT   | S     | SLAVE ADDRESS | WR    | A     | REGISTER SELECT | A     |

| M → S | M → S         | M → S | S → M | S → M           | M → S | S → M            | M → S | M → S |

|-------|---------------|-------|-------|-----------------|-------|------------------|-------|-------|

| 1     | 7             | 1     | 1     | 8               | 1     | 8                | 1     | 1     |

| Sr    | SLAVE ADDRESS | Rd    | A     | DATA BYTE [7:0] | A     | DATA BYTE [15:8] | N     | P     |

図 5.2 バイトの読み出し (PEC バイト有り)

図 6 および図 7 に示すように、PEC の有無に関係なく 1 バイトの読み出しが上記のワード読み出しに似ていますが、1 バイトだけが読み出されます。

| DIRECTION | M→S | M→S           | M→S | S→M | M→S             | S→M |

|-----------|-----|---------------|-----|-----|-----------------|-----|

| BITS      | 1   | 7             | 1   | 1   | 8               | 1   |

| CONTENT   | S   | SLAVE ADDRESS | WR  | A   | REGISTER SELECT | A   |

| M→S | M→S           | M→S | S→M | S→M       | M→S | M→S |

|-----|---------------|-----|-----|-----------|-----|-----|

| 1   | 7             | 1   | 1   | 8         | 1   | 1   |

| Sr  | SLAVE ADDRESS | Rd  | A   | DATA BYTE | N   | P   |

図 6.1 バイトの読み出し

| DIRECTION | M→S | M→S           | M→S | S→M | M→S             | S→M |

|-----------|-----|---------------|-----|-----|-----------------|-----|

| BITS      | 1   | 7             | 1   | 1   | 8               | 1   |

| CONTENT   | S   | SLAVE ADDRESS | WR  | A   | REGISTER SELECT | A   |

| M→S | M→S           | M→S | S→M | S→M       | M→S | S→M      | M→S | M→S |

|-----|---------------|-----|-----|-----------|-----|----------|-----|-----|

| 1   | 7             | 1   | 1   | 8         | 1   | 8        | 1   | 1   |

| Sr  | SLAVE ADDRESS | Rd  | A   | DATA BYTE | A   | PEC BYTE | N   | P   |

図 7.1 バイトの読み出し（PEC 有り）

**Read 32 プロトコル：**Read 32 プロトコルは、最大 32 ビット（4 バイト）のデータをスレーブ・デバイスから読み出すことが必要なコマンドと共に使用されます。MAX40080 の場合、これが適用されるのはレジスタ Current\_Voltage\_Measurement だけです。

このプロトコルを使用すると 32 ビット未満でも読み出しが可能ですが、そのパケットをパディングして 32 ビットにする必要があります。データまたは意味のあるビットが下位ビットにパックされ、未使用的上位ビットはゼロで埋められます。例えば、20 ビットの値はビット[19:0]（最上位ビットはビット[19]）で送信されます。ビット[31:20]はすべてゼロです。

| DIRECTION | M→S | M→S           | M→S | S→M | M→S             | S→M |

|-----------|-----|---------------|-----|-----|-----------------|-----|

| BITS      | 1   | 7             | 1   | 1   | 8               | 1   |

| CONTENT   | S   | SLAVE ADDRESS | WR  | A   | REGISTER SELECT | A   |

| M→S | M→S           | M→S | S→M | S→M             | M→S | S→M              | M→S |

|-----|---------------|-----|-----|-----------------|-----|------------------|-----|

| 1   | 7             | 1   | 1   | 8               | 1   | 8                | 1   |

| Sr  | SLAVE ADDRESS | Rd  | A   | DATA BYTE [7:0] | A   | DATA BYTE [15:8] | A   |

| S→M               | M→S | S→M               | M→S | M→S |

|-------------------|-----|-------------------|-----|-----|

| 8                 | 1   | 8                 | 1   | 1   |

| DATA BYTE [23:16] | A   | DATA BYTE [31:24] | N   | P   |

図 8. Read 32

|                   |               |                   |       |                 |                 |                  |       |

|-------------------|---------------|-------------------|-------|-----------------|-----------------|------------------|-------|

| DIRECTION         | M → S         | M → S             | M → S | S → M           | M → S           | S → M            |       |

| BITS              | 1             | 7                 | 1     | 1               | 8               | 1                |       |

| CONTENT           | S             | SLAVE ADDRESS     | WR    | A               | REGISTER SELECT | A                | • • • |

|                   |               |                   |       |                 |                 |                  |       |

| M → S             | M → S         | M → S             | S → M | S → M           | M → S           | S → M            | M → S |

| 1                 | 7             | 1                 | 1     | 8               | 1               | 8                | 1     |

| Sr                | SLAVE ADDRESS | Rd                | A     | DATA BYTE [7:0] | A               | DATA BYTE [15:8] | A     |

|                   |               |                   |       |                 |                 |                  |       |

| S → M             | M → S         | S → M             | M → S | S → M           | M → S           | M → S            | M → S |

| 8                 | 1             | 8                 | 1     | 8               | 1               | 1                | 1     |

| DATA BYTE [23:16] | A             | DATA BYTE [31:24] | A     | PEC BYTE        | N               | P                |       |

図 9. Read 32 (PEC 有り)

## I<sup>2</sup>C スレーブ・アドレス

MAX40080 は、A0 入力ピンに接続された 1 本の抵抗に基づく独自の I<sup>2</sup>C スレーブ・アドレス選択方法を採用しています。抵抗に基づくそのような方法には多くの利点があります。例えば、コストが低くなり、サイズが小さくなることに加え、ユーザは在庫システムに 1 種類の部品だけを持ち、それを、標準的な 1% 精度の抵抗を 1 つ変えるだけで、異なる I<sup>2</sup>C アドレスを持つ複数のプロジェクトで使用できるようになります。目的の I<sup>2</sup>C アドレスを選んで抵抗値を選択します。[表 1](#) を参照してください。

5つの最下位ビットでエンコードされた 32 個のアドレスに対応する 32 通りの異なる抵抗値が示されています。アドレス・ワードの 2 つの最上位ビット (A<sub>6</sub>、A<sub>5</sub>) は固定されており、利用可能な 2 つのオプション (A<sub>6</sub>=0、A<sub>5</sub>=1 または A<sub>6</sub>=1、A<sub>5</sub>=0) が工場の最終テストで OTP を介して選ばれます。デフォルト値は、A<sub>6</sub>=0、A<sub>5</sub>=1 です。本デバイスは抵抗値を A0 ピンで常にモニタし、デバイスに電源を入れた後に抵抗値が変化した場合、I<sup>2</sup>C スレーブ・アドレスが変更されることに注意してください。

表 1. I<sup>2</sup>C スレーブ・アドレス

| RESISTOR VALUE [Ω], 1% | SLAVE ADDRESS                            |

|------------------------|------------------------------------------|

| 115,000                | A <sub>6</sub> , A <sub>5</sub> , 0_0000 |

| 100,000                | A <sub>6</sub> , A <sub>5</sub> , 0_0001 |

| 86,600                 | A <sub>6</sub> , A <sub>5</sub> , 0_0010 |

| 75,000                 | A <sub>6</sub> , A <sub>5</sub> , 0_0011 |

| 64,900                 | A <sub>6</sub> , A <sub>5</sub> , 0_0100 |

| 56,200                 | A <sub>6</sub> , A <sub>5</sub> , 0_0101 |

| 48,700                 | A <sub>6</sub> , A <sub>5</sub> , 0_0110 |

| 42,200                 | A <sub>6</sub> , A <sub>5</sub> , 0_0111 |

| 36,500                 | A <sub>6</sub> , A <sub>5</sub> , 0_1000 |

| 30,900                 | A <sub>6</sub> , A <sub>5</sub> , 0_1001 |

| 26,100                 | A <sub>6</sub> , A <sub>5</sub> , 0_1010 |

| 21,500                 | A <sub>6</sub> , A <sub>5</sub> , 0_1011 |

| 16,900                 | A <sub>6</sub> , A <sub>5</sub> , 0_1100 |

| 12,400                 | A <sub>6</sub> , A <sub>5</sub> , 0_1101 |

| 8,060                  | A <sub>6</sub> , A <sub>5</sub> , 0_1110 |

| 3,740                  | A <sub>6</sub> , A <sub>5</sub> , 0_1111 |

| 2,870                  | A <sub>6</sub> , A <sub>5</sub> , 1_0000 |

| 2,490                  | A <sub>6</sub> , A <sub>5</sub> , 1_0001 |

| 2,150                  | A <sub>6</sub> , A <sub>5</sub> , 1_0010 |

| 1,870                  | A <sub>6</sub> , A <sub>5</sub> , 1_0011 |

表 1. I<sup>2</sup>C スレーブ・アドレス（続き）

|       |                                          |

|-------|------------------------------------------|

| 1,620 | A <sub>6</sub> , A <sub>5</sub> , 1_0100 |

| 1,400 | A <sub>6</sub> , A <sub>5</sub> , 1_0101 |

| 1,210 | A <sub>6</sub> , A <sub>5</sub> , 1_0110 |

| 1,050 | A <sub>6</sub> , A <sub>5</sub> , 1_0111 |

| 909   | A <sub>6</sub> , A <sub>5</sub> , 1_1000 |

| 768   | A <sub>6</sub> , A <sub>5</sub> , 1_1001 |

| 649   | A <sub>6</sub> , A <sub>5</sub> , 1_1010 |

| 536   | A <sub>6</sub> , A <sub>5</sub> , 1_1011 |

| 422   | A <sub>6</sub> , A <sub>5</sub> , 1_1100 |

| 309   | A <sub>6</sub> , A <sub>5</sub> , 1_1101 |

| 200   | A <sub>6</sub> , A <sub>5</sub> , 1_1110 |

| 95.3  | A <sub>6</sub> , A <sub>5</sub> , 1_1111 |

## I<sup>2</sup>C 通信速度

MAX40080 は、I<sup>2</sup>C リビジョン 3.0 対応 (3.4MHz) のシリアル・インターフェースを備えています。リビジョン 3.0 I<sup>2</sup>C 対応のシリアル通信チャンネルは次のとおりです。

- 0Hz～100kHz (スタンダード・モード)

- 0Hz～400kHz (ファースト・モード)

- 0Hz～1MHz (ファースト・モード・プラス)

- 0Hz～3.4MHz (ハイスピード・モードまたは HS モード)

- I<sup>2</sup>C クロック・ストレッ칭は利用せず

スタンダード・モード、ファースト・モード、ファースト・モード・プラスの動作に、特別なプロトコルは必要ありません。この範囲全体でバス速度を変更する場合の主な考慮事項は、バス容量とプルアップ抵抗の組み合わせです。バス容量とプルアップ抵抗で作られる時定数 ( $C \times R$ ) が大きくなると、バス動作が遅くなります。したがって、バス速度を上げる場合は、適切な時定数を維持するために、プルアップ抵抗を下げる必要があります。プルアップ抵抗の選択に関する詳細な手引きについては、I<sup>2</sup>C リビジョン 3.0 仕様書の「プルアップ抵抗のサイジング」のセクションを参照してください。一般に、バス容量が 200pF の場合、100kHz のバスには 5.6kΩ、400kHz のバスには約 1.5kΩ、1MHz のバスには 680Ω のプルアップ抵抗が必要です。プルアップ抵抗は、オープン・ドainein・バスが低い場合に電力を消費することに注意してください。プルアップ抵抗の値が低いほど、消費電力 ( $V^2/R$ ) は大きくなります。

ハイスピード・モードの動作には、考慮事項がいくつか必要です。考慮事項の一覧については、I<sup>2</sup>C 3.0 仕様書を参照してください。MAX40080 に関する主な考慮事項は次のとおりです。

- I<sup>2</sup>C バス・マスタは、電流源プルアップを使用して信号の立上がり時間を短縮します。

- I<sup>2</sup>C スレーブは、SDA ラインと SCL ラインに対して異なるセットの入力フィルタを使用して、より高いバス速度に対応する必要があります。

- 通信プロトコルは、高速マスター・コードを利用する必要があります。

電源投入時および各ストップ条件の後に、MAX40080 の入力フィルタは、設定レジスタのビット 7 がハイに設定されていない限り、スタンダード・モード、ファースト・モード、またはファースト・モード・プラス (すなわち、0Hz～1MHz) に設定されます。設定レジスタのビット 7 がハイにセットされている場合、一度 HS モードに入ると、本デバイスはこのビットがセットされたままでいる限りそのモードにとどまり、その結果、ストップ条件は無視されます。

このビットがリセットされると、次のストップ条件で、MAX40080 は HS モードを終了します。

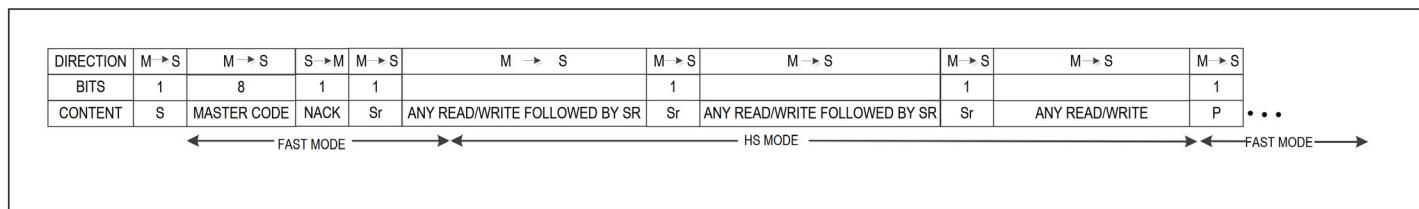

## 最大 3.4MHz の動作に向けた HS モードの稼働

図 10 は HS モード動作を稼働させるためのプロトコルを示しています。HS モード動作では、最大 3.4MHz のバス動作速度が可能です。HS モード・プロトコルの稼働は次のとおりです。

1. 1MHz 以下のバス速度で動作している間に、このプロトコルを開始します。

2. マスターはスタート・コマンド (S) を送信します。

3. マスターは 8 ビットのマスター・コード 00001xxb (xxb はドント・ケア・ビット) を送信します。

4. アドレス指定されたスレーブは、ノット・アクリソジ (NA) を発行します。

5. マスターはそのバス速度をこの時点で 3.4MHz まで上げて、読み出し／書き込み動作を発行できます。

6. マスターは、ストップ (P) を発行するまで、高速の読み出し／書き込み動作を発行し続けることができます。ストップ (P) を発行すると、バス入力フィルタは確実に 1MHz 以下の動作に設定されます。ストップ発行後は、上述したアルゴリズムのステップ 1～6 を省略しても構いません。

図 10. HS モードの稼働

I<sup>2</sup>C の HS モードは、本デバイスがアクティブ・モードで動作する場合に限り利用可能であることに注意してください。アクティブ・モードおよびその他の動作モードに関する詳細については、[設定レジスタ](#)の項目を参照してください。

## 動作モード

本デバイスは、「**設定 (Configuration)**」レジスタを通じてプログラムできる次の 5 つのモードの 1 つで動作します。

- スタンバイ・モード (Standby Mode)**：デバイスは、コマンドを受信できる I<sup>2</sup>C インタフェースを除いて、非アクティブです。

- 低消費電力モード (Low-Power Mode)**：ADC は無効ですが、電流検出は部分的にアクティブであり、50ms ごとに 1 回の電流計測を行います。計測された電流は、「Wake Up Current」レジスタに設定されたスレッショルド未満です。計測された電流がそのスレッショルドに達すると、デバイスは「**アクティブ・モード (Active Mode)**」に入ります。デバイスが低消費電力モードにとどまっている限り、電圧計測は行われません。この理由から、電流だけを FIFO に保存することを推奨します (FIFO に何を保存すべきかを決めるには [FIFO 設定レジスタ](#) のセクションを参照してください)。しかしデバイスは、低消費電力モードからアクティブ・モードへとウェイクアップすると、FIFO 設定レジスタ内の Store V\_I 設定に従って、電流計測または電圧計測のいずれかを行います。

- 単一計測モード (Single-Measurement Mode)**：デバイスは基本的にスタンバイ・モードになっていますが、SM バスの「**クイック・コマンド (Quick Command)**」に応答する場合には、ウェイクアップして電流と電圧の計測を 1 回行い、その後次の「クイック・コマンド」まで再びスタンバイ・モードに入れます。

- アクティブ・モード**：デバイスは、その機能すべてにおいてアクティブであり、計測が常に行われます。

- 選択されたアクティブ・モード (Selected Active Mode)**：デバイスは（サンプリング・レートの設定に従って）毎秒複数回の計測を自動的に行い、各計測の間はスタンバイ状態になります。

本デバイスは、「**アクティブ・モード**」または「**選択されたアクティブ・モード**」のいずれかで動作している場合、I<sup>2</sup>C バスが 1 分もの間非アクティブであれば、自動的にスタンバイ・モードに入れます。

## クイック・コマンド：

クイック・コマンドでは、スレーブ・アドレスの R/W# ビットがそのコマンドを表します。R/W# ビットは、単一計測モードの場合に限り、計測を行うのに使用されます。送受信されるデータはありません。

| DIRECTION | M→S | M→S           | M→S  | S→M | M→S |

|-----------|-----|---------------|------|-----|-----|

| BITS      | 1   | 7             | 1    | 1   | 1   |

| CONTENT   | S   | SLAVE ADDRESS | R/W# | A   | P   |

図 11. クイック・コマンド

## アラート管理

MAX40080 は、次の状況のいずれかが発生した場合に通知するオープン・ドラインの ALERT\_ 出力を特徴としています。

- 過電流

- 過電圧

- 低電圧

- FIFO オーバーフロー警告（プログラマブルなスレッショルド）

- FIFO が満杯（64 個のデータを保存）

- 変換完了（単一計測モードのみ）

- ウェイクアップ電流スレッショルドに到達

- I<sup>2</sup>C バス（非アクティブ時）で 1 分間のタイムアウト時間が経過

上記の状態はいずれも、ステータス・レジスタにも通知されます。

ALERT\_出力はラッチされ、ステータス・レジスタにおいて関連するフラグがクリアされた後に限り、デアサートされます。そのようなフラグは、ステータス・レジスタに書き込むことでクリアされます。詳細については、[ステータス・レジスタ](#)の説明を参照してください。

ALERT\_の割込み出力（SMBALERT#とも呼ぶ）は、SMBus のアラート応答アドレス（ARA）と併用されるワイヤード AND 信号です。

スレーブ専用デバイスは、SMBALERT#を通じてホストに、通信を開始したい旨を信号で通知できます。ホストはその割込みを処理し、アラート応答アドレスによってすべての SMBALERT#デバイスに同時にアクセスします。SMBALERT#をローに引き下げたデバイスだけが、アラート応答アドレスを認識します。ホストは、修正されたバイト受信動作を行います。スレーブ送信デバイスにより提供された 7 ビットのデバイス・アドレスは、そのバイトの 7 つの最上位ビットに配置されます。8 番目のビットはゼロでも 1 でも構いません。

複数のデバイスが SMBALERT#をローに引き下げた場合、優先度が最も高い（アドレスが最も低い）デバイスが、スレーブ・アドレス転送時に標準のアービトレーションによって通信の権利を獲得します。

このデバイスは、そのアドレスに応答したマスターからアクノリッジ（ACK）を受信した後に、SMBALERT#信号に対するプルダウンを停止しなければなりません。ホストは、メッセージ転送が完了したときに SMBALERT#がまだローであることを検知した場合、再び ARA を読み出す必要があると認識します。

## 内部レジスタ

ポインタ・レジスタは、表 2 に示すレジスタから選択します。ポインタ・レジスタは、I<sup>2</sup>C トランザクションごとに書込みが必要です。

レジスタ・アドレスは、読出し中および書込み中に自動インクリメントされません。最大ピーク電流レジスタは、読み出すとリセットされます。

スレーブ・アドレス・バイト、ポインタ・レジスタ・バイト（値は 00h）、データ・バイトを書き込むことにより、設定レジスタへの書込みが行われます。他のすべてのレジスタには、スレーブ・アドレス・バイト、ポインタ・レジスタ・バイト（04h または 05h など）、および 2 つのデータ・バイトが必要です。データ・バイトを 1 つだけ書き込む場合、対応するレジスタのビット D[15:8]に保存されます。データ・バイトを 3 つ以上書き込む場合、追加のデータは同じレジスタに書き込まれます。

スレーブ・アドレス・バイト（書込み）、ポインタ・バイト、反復スタート、別のスレーブ・アドレス・バイト（読出し）を発行し、データ・バイトを読み出すことによって、読出し動作を実行します。データ・バイトを 3 つ以上読み出す場合、追加の読み出しは同じレジスタから行われます。図 4 を参照してください。

表 2. レジスタ機能と POR 状態

| REGISTER NAME           | R/W | ADDRESS(HEX) | NUMBER OF BITS | POR STATE(HEX) | I2C READ TYPE |

|-------------------------|-----|--------------|----------------|----------------|---------------|

| Configuration           | R/W | 00h          | 16             | 0060h          | Read Word     |

| Status                  | R   | 02h          | 14             | 0000h          | Read Word     |

| Threshold_Over_Current  | R/W | 04h          | 7              | 30h            | Read Byte     |

| Threshold_Over_Voltage  | R/W | 05h          | 6              | 30h            | Read Byte     |

| Threshold_Under_Voltage | R/W | 06h          | 6              | 00h            | Read Byte     |

| Wake_Up_Current         | R/W | 07h          | 7              | 08h            | Read Byte     |

| Max_Peak_Current        | R   | 08h          | 14             | 0000h          | Read Word     |

| FIFO_Configuration      | R/W | 0Ah          | 16             | 3400h          | Read Word     |

| Current_Measurement     | R   | 0Ch          | 16             | 0000h          | Read Word     |

| Voltage_Measurement     | R   | 0Eh          | 16             | 0000h          | Read Word     |

表 2. レジスタ機能と POR 状態（続き）

|                             |     |     |    |            |           |

|-----------------------------|-----|-----|----|------------|-----------|

| Current_Voltage Measurement | R   | 10h | 32 | 0000 0000h | Read 32   |

| INT_EN                      | R/W | 14h | 8  | FFh        | Read Byte |

## 設定レジスタ

設定レジスタには、次に示す 16 ビットのデータが含まれます。

|          |                |                 |              |             |     |       |             |       |    |    |

|----------|----------------|-----------------|--------------|-------------|-----|-------|-------------|-------|----|----|

| D15      | D14 D13 D12    | D11 D10 D9 D8   | D7           | D6          | D5  | D4    | D3          | D2    | D1 | D0 |

| Reserved | Digital Filter | ADC Sample Rate | Stay HS Mode | Input Range | PEC | Alert | I2C Timeout | Modes |    |    |

## 動作モード

次に示すデバイス動作モードの 1 つを選択するには、ビット D2、D1、D0 を設定します。

表 3. 動作モード

| OPERATION MODE         | D2 | D1 | D0 | COMMENT                         |

|------------------------|----|----|----|---------------------------------|

| Standby Mode           | 0  | 0  | 0  | Default mode at device power up |

| Low-Power Mode         | 0  | 0  | 1  |                                 |

| Single-Conversion Mode | 0  | 1  | 0  |                                 |

| Active Mode            | 0  | 1  | 1  | Continuous measurement          |

|                        | 1  | 0  | 0  | Fixed sample rate at 4sps       |

|                        | 1  | 0  | 1  | Fixed sample rate at 1sps       |

|                        | 1  | 1  | 0  | Fixed sample rate at 0.25sps    |

| Selected Active Mode   | 1  | 1  | 1  | Fixed sample rate at 0.0625sps  |

変換が行われているときに、動作モードが変更された場合、その変換が完了してから変更が行われます。スタンバイ中も、I<sup>2</sup>C インターフェースはアクティブのままであり、すべてのレジスタはマスターにアクセス可能です。

本デバイスは、「アクティブ・モード」または「選択されたアクティブ・モード」のいずれかで動作している場合、I<sup>2</sup>C バスが 1 分もの間非アクティブであれば、自動的にスタンバイ・モードに入ります。

## I<sup>2</sup>C タイムアウト

I<sup>2</sup>C タイムアウトを無効にするには、D3 に 1 を書き込みます。

I<sup>2</sup>C タイムアウトを有効にするには、D3 に 0 を書き込みます（リセット時および電源投入時のデフォルト状態）。本デバイスは、「アクティブ・モード」または「選択されたアクティブ・モード」のいずれかで動作している場合、I<sup>2</sup>C バスが 1 分もの間非アクティブであれば、自動的にスタンバイ・モードに入ります。そのような状態が起きた場合、ALERT\_がローに引き下げられ、ステータス・レジスタにビットが設定されます。

## アラート応答時間

ビット D4 でアラート割込みの応答時間を選択します。

- D4 = 0 : フィルタリングなし。アラートは、検出されるとすぐに発行されます。

- D4 = 1 : アラートは、4 回連続の ADC クロック・サンプル内で検出された後に発行されます（遅延時間は ADC のサンプリング周波数に応じて 4μs～266.4μs の範囲で変わります）。

## PEC

パケット・エラー・チェックを有効（デフォルト）にするには、1 を書き込みます。パケット・エラー・チェックを無効にするには、0 を書き込みます。

パケット・エラー・チェック（PEC）を有効にするには、PEC ビットを設定します。有効にすると、各メッセージ転送の最後に PEC バイトが付加されます。これは、（アドレス／読み出し／書き込みバイトを含む）すべてのメッセージ・バイトに対して計算される CRC-8 バイトです。データ・バイトを送信する最後のデバイスも、PEC バイトを送信するため、マスターは、書き込みトランザクション後に PEC バイトを送信し、本デバイスは、読み出しトランザクション後に PEC バイトを送信します。

## 入力範囲

50mV (デフォルト) の範囲を選択するには D6 に 0 を書き込みます。

10mV の範囲を選択するには D6 に 1 を書き込みます。

## HS モードの維持

本デバイスに HS モードを維持させるには、D7 を 1 に設定します。HS モードを終了するには、D7 を 0 に設定します (デフォルト)。このビットが 1 に設定された場合、デバイスの I<sup>2</sup>C 速度が (最大 3.4MHz の) HS モードに設定されているならば、デバイスは HS モードを維持し、したがってストップ条件を無視します。このビットが 0 にリセットされると、次のストップ条件で、デバイスは HS モードを終了します。

## ADC のサンプリング・レート

表 4 は ADC の利用可能なすべてのサンプリング・レートを示しています。「FIFO からのデータ読み出し (Data read from FIFO)」列はアクティブ・モードに限り有効であることに注意してください。単一計測モードおよび選択されたアクティブ・モードでは、どのサンプリング・レートでも FIFO からのデータ読み出しが「電流と電圧の両方 (Both Current and Voltage)」になります。

表 4. サンプリング・レートの選択

| D11 | D10 | D9 | D8 | SAMPLE RATE (ksps) | DATA READ FROM FIFO       |

|-----|-----|----|----|--------------------|---------------------------|

| 0   | 0   | 0  | 0  | 15                 | Either Current or Voltage |

| 0   | 0   | 1  | 0  | 23.45              | Either Current or Voltage |

| 0   | 0   | 1  | 1  | 30                 | Either Current or Voltage |

| 0   | 1   | 0  | 0  | 37.5               | Either Current or Voltage |

| 0   | 1   | 0  | 1  | 47.1               | Either Current or Voltage |

| 0   | 1   | 1  | 0  | 60                 | Either Current or Voltage |

| 0   | 1   | 1  | 1  | 93.5               | Either Current or Voltage |

| 1   | 0   | 0  | 0  | 120                | Either Current or Voltage |

| 1   | 0   | 0  | 1  | 150                | Either Current or Voltage |

| 1   | 0   | 1  | 0  | 234.5              | Either Current or Voltage |

| 1   | 0   | 1  | 1  | 375                | Either Current or Voltage |

| 1   | 1   | 0  | 0  | 468.5              | Either Current or Voltage |

| 1   | 1   | 0  | 1  | 750                | Either Current or Voltage |

| 1   | 1   | 1  | 0  | 1,000              | Either Current or Voltage |

| 1   | 1   | 1  | 1  | 0.5                | Both Current and Voltage  |

I<sup>2</sup>C インタフェースは、最大速度 3.4MHz でデータを読み出します。したがって、FIFO をオーバーフローすることなく、ADC のすべてのサンプリング・レートを常に本デバイスから引き出せるわけではありません。

ADC のサンプリング・レートが高い主な目的は、デジタル・フィルタリングを用いたオーバーサンプリングのためです。I<sup>2</sup>C が FIFO をオーバーフローすることなくデータを確実に読み出せるようにするのは、ユーザの責任です。

詳細については、[アプリケーション情報](#)のセクションの「[FIFO のデータ読み出しレート](#)」を参照してください。

MAX40080 で電流もしくは電圧、またはその両方のいずれを保存すべきかを決定するには、[FIFO 設定レジスタ](#)も参照してください。MAX40080 がアクティブ・モードであり、かつ FIFO が電流と電圧の両方を保存するように設定されている場合、最も遅いサンプリング・レートの 0.5ksps のみが使用できます。本デバイスが単一計測モードおよび選択されたアクティブ・モードの場合、どのサンプリング・レートでも電流と電圧の両方が読み出し可能であることに注意してください。

## デジタル・フィルタ

このオプションでは、サンプル全体の平均値を計算します。[表 5](#) を参照してください。そのような平均値は、次に挙げる動作モードに適用されます。

- アクティブ・モード

- 選択されたアクティブ・モード

- 単一計測モード

これらのモードのそれぞれには、フィルタを何も使用しないオプションもあります。

表 5. デジタル・フィルタの選択

| D14 | D13 | D12 | FUNCTION                  |

|-----|-----|-----|---------------------------|

| 0   | 0   | 0   | No Average                |

| 0   | 0   | 1   | Average among 8 samples   |

| 0   | 1   | 0   | Average among 16 samples  |

| 0   | 1   | 1   | Average among 32 samples  |

| 1   | 0   | 0   | Average among 64 samples  |

| 1   | 0   | 1   | Average among 128 samples |

表 6 は、選択されたサンプリング周波数とフィルタ・オプションに応じた出力レートを示しています。

表 6. 出力データ・レートとサンプリング・レートの関係

| Sample Rate<br>[ksps] | Output Data Rate [ksps] |         |          |           |            |             |

|-----------------------|-------------------------|---------|----------|-----------|------------|-------------|

|                       | No Filter               | x8      | x16      | x32       | x64        | x128        |

| 15                    | 15                      | 1.875   | 0.9375   | 0.46875   | 0.234375   | 0.1171875   |

| 18.75                 | 19                      | 2.34375 | 1.171875 | 0.5859375 | 0.29296875 | 0.146484375 |

| 23.45                 | 23                      | 2.93125 | 1.465625 | 0.7328125 | 0.36640625 | 0.183203125 |

| 30                    | 30                      | 3.75    | 1.875    | 0.9375    | 0.46875    | 0.234375    |

| 37.5                  | 38                      | 4.6875  | 2.34375  | 1.171875  | 0.5859375  | 0.29296875  |

| 47.1                  | 47                      | 5.8875  | 2.94375  | 1.471875  | 0.7359375  | 0.36796875  |

| 60                    | 60                      | 7.5     | 3.75     | 1.875     | 0.9375     | 0.46875     |

| 93.5                  | 94                      | 11.6875 | 5.84375  | 2.921875  | 1.4609375  | 0.73046875  |

| 120                   | 120                     | 15      | 7.5      | 3.75      | 1.875      | 0.9375      |

| 150                   | 150                     | 18.75   | 9.375    | 4.6875    | 2.34375    | 1.171875    |

| 234.5                 | 235                     | 29.3125 | 14.65625 | 7.328125  | 3.6640625  | 1.83203125  |

| 375                   | 375                     | 46.875  | 23.4375  | 11.71875  | 5.859375   | 2.9296875   |

| 468.5                 | 469                     | 58.5625 | 29.28125 | 14.640625 | 7.3203125  | 3.66015625  |

| 750                   | 750                     | 93.75   | 46.875   | 23.4375   | 11.71875   | 5.859375    |

| 1000                  | 1000                    | 125     | 62.5     | 31.25     | 15.625     | 7.8125      |

## ステータス・レジスタ

ステータス・レジスタには、次に挙げる 6 つのフラグと 6 ビットの FIFO データ・カウントが含まれています。

| D13-8           | D7            | D6         | D5                       | D4          | D3         | D2         | D1               | D0      |

|-----------------|---------------|------------|--------------------------|-------------|------------|------------|------------------|---------|

| FIFO Data Count | FIFO Overflow | FIFO Alarm | I <sup>2</sup> C Timeout | Underflow_V | Overflow_V | Overflow_I | Conversion Ready | Wake-Up |

ビット D7～D0 にあるフラグのそれぞれをクリアするために、読み出された同じワードによるこのレジスタへの書き込みが必要になります。このフラグをクリアする場合、上位のバイトに書き込まれていることに意味はなく、このレジスタに影響を与えません。

例えば、過電流状態が発生したために過電流フラグが設定されたとします。FIFO には 4 つのデータがあるとします。

このレジスタを読み出すと、データ 0x0404 が得られます。

過電流フラグをクリアするには、このレジスタにデータ 0xXXX4 を書き込む必要があります。ここで上位バイトの X は、どの値でも構わないことを示しています。

## ウェイクアップ電流

D0 は読み出し専用のステータス・ビットで、計測された電流がレジスタ「Wake\_up\_Current」にプログラムされた値を超えていることを示しています。

「Wake\_up\_Current」これは、本デバイスが低消費電力モードに設定されている場合に限り適用されます。割込みも発生します。

## 変換完了

D1 は読み出し専用のステータス・ビットで、ADC 変換が完了していることを示しています。このビットは単一計測モードに限り使用され、そのようなモードでは割込みも発生します。

## オーバーフロー電流

D2 は読み出し専用のビットで、計測された電流がレジスタ「**Threshold\_Over\_Current**」にプログラムされた値を超えていることを示しています。そのような状態では割込みも発生します。このビットは単一変換モード、選択的アクティブ・モード、アクティブ・モードで使用され、FIFO が電圧のみを保存する場合には適用されません。FIFO が電流と電圧の両方を保存するアクティブ・モードにおいて、このビットが適用されるのは、ADC のサンプリング・レートが 0.5Ksps の場合に限ります。

## オーバーフロー電圧またはアンダーフロー電圧

D3 は読み出し専用のビットで、計測された電圧がレジスタ「**Threshold\_Over\_Voltage**」にプログラムされた値を超えていることを示しています。そのような状態では割込みも発生します。

D4 は読み出し専用のビットで、計測された電圧がレジスタ「**Threshold\_Under\_Voltage**」にプログラムされた値を下回っていることを示しています。そのような状態では割込みも発生します。

D3 と D4 の両方は、単一変換モード、選択的アクティブ・モード、アクティブ・モードで使用できます。この 2 つのビットは、FIFO が電流計測値のみを保存する場合には適用されません。アクティブ・モードにおいて FIFO が電流計測値と電圧計測値の両方を保存する場合、この 2 つのビットが適用されるのは、ADC のサンプリング・レートが 0.5Ksps の場合に限ります。

## I<sup>2</sup>C タイムアウト

D5 は読み出し専用のビットで、本デバイスは、「アクティブ・モード」または「選択されたアクティブ・モード」のいずれかで動作している場合、I<sup>2</sup>C バスが 1 分間非アクティブであれば、自動的にスタンバイ・モードに入ることを示します。そのような状態では割込みも発生します。

## FIFO アラーム

D6 は読み出し専用のステータス・ビットで、ADC の FIFO がオーバーフローする直前であることを示しています。そのような状態が起きると、割込みも発生します。

FIFO の深さは 64 であり、N 個の場所が書き込み済みで、かつまだどれも読み出されていない場合、オーバーフロー警告が発行されます。数値 N は、FIFO 設定レジスタの Overflow\_Threshold フィールドで決定されます。

## FIFO オーバーフロー

1 に設定されると、FIFO が 64 個のデータで満杯であることを示します。割込みも発行されます。データの数が 63 個以下となる他の状況ではいずれも、このビットが 0 になります。

## FIFO データ・カウント

6 ビットのカウンタで、現在 FIFO の中にあるデータの数を示します。範囲は 0~63 です。

FIFO が満杯の場合、つまり FIFO に 64 個のデータがある場合、このカウンタは 0 になりますが、オーバーフロー・ビットは 1 に設定されます。

## スレッショルド・レジスタおよびウェイクアップ電流レジスタ

表 7 は、threshold\_over\_current レジスタ、threshold\_over/under\_voltage レジスタ、wake\_up\_current レジスタのデータ形式を示しています。

表 7. スレッショルド・レジスタおよびウェイクアップ電流レジスタ

| レジスタ名                  | レジスタ・アドレス | ビット 6 | ビット 5~0                                                                   |

|------------------------|-----------|-------|---------------------------------------------------------------------------|

| Threshold_Over_Current | 0x04      | sign  | 過電流スレッショルド。計測された電流がこの値より高い場合、ALERT_ にアラートが発行され、ステータス・レジスタ・ビットが 1 つ設定されます。 |

| Threshold_Over_Voltage | 0x05      | n/a   | 過電圧スレッショルド。計測された電圧がこの値より高い場合、ALERT_ にアラートが発行され、ステータス・レジスタ・ビットが 1 つ設定されます。 |

表 7. 閾値レジスタおよびウェイクアップ電流レジスタ（続き）

|                         |      |      |                                                                                                                   |

|-------------------------|------|------|-------------------------------------------------------------------------------------------------------------------|

| Threshold_Under_Voltage | 0x06 | n/a  | 低電圧スレッショルド。計測された電圧がこの値より低い場合、ALERT_にアラートが発行され、ステータス・レジスタ・ビットが1つ設定されます。                                            |

| Wake_up_Current         | 0x07 | sign | 低消費電力モード時のウェイクアップ電流スレッショルド。計測された電流がこの値より高い場合、本デバイスはアクティブ・モードに切り替わります。更に、ALERT_にアラートが発行され、ステータス・レジスタ・ビットが1つ設定されます。 |

**MAX\_Peak\_Current**

FIFO が保存した最大電流値を表示します。

**FIFO の設定**

| BIT             | D15   | D14 | D13-8            | D7-2     | D1-0     |

|-----------------|-------|-----|------------------|----------|----------|

| <b>BIT NAME</b> | Flush | RO  | Overflow_Warning | Not_Used | Store_IV |

| <b>DEFAULT</b>  | 0     | 0   | 110100           | 000000   | 00       |

**Store IV**

この2つのビットで、本デバイスが電流もしくは電圧、またはその両方のいずれを計測して FIFO に保存するかを決定します。

- 2'b00 : 電流のみ

- 2'b01 : 電圧のみ

- 2'b10 : 電流と電圧

- 2'b11 : 不使用

FIFO の深さは 64、幅は 32 ビットです。この2つのビットで行われた選択に関わらず、電流と電圧の情報は次の表に示すデータ形式を常に使用します。

| D31-D16 | D15-D0  |

|---------|---------|

| Voltage | Current |

電流のみモード (2'b00) では、ADC は電流しか計測しないため、電圧ビット (D31~D16) は常に空になっており、意味はありません。

電圧のみモード (2'b01) では、ADC は電圧しか計測しないため、電流ビット (D15~D0) は常に空になっており、意味はありません。

電流と電圧モード (10) では、ADC は 10 回の電流計測と 1 回の電圧計測を常に交互に行います。すべてのビット (D31~D0) が書き込まれます。10 個連続した電流ビットごとに、電圧ビットが繰り返し挿入されます。このモードでは、電流または電圧の実際のサンプリング・レートは、設定レジスタに指定されている ADC サンプリング・レートを下回ります。

電流および電圧のデータは、Current\_Measurement (0x0C) 、Voltage\_Measurement (0x0E) 、Current\_Voltage\_Measurement (0x10) の各レジスタを介して FIFO から読み出されます。動作モードを常時監視するのはユーザの責任です。例えば、これらのビットが電流のみ (2'b00) に設定された場合、意味あるデータを提供するのはレジスタ Current\_Measurement (0x0C) だけです。

すべてのデータは 2 の補数です。

**Overflow\_Threshold**

これは 6 ビットのプログラマブルなスレッショルドで、これによりユーザは FIFO 内のどのデータ・カウントでオーバーフロー警告割込みを発行すべきかを設定できるようになります。

範囲は 0x00~0x3F です。

デフォルト値は 0x34 です (FIFO の 80% が満たされています)。

**RO**

RO (ロールオーバー) :

これによって、FIFO が満杯のときのロールオーバー動作が定義されます。RO がローに設定されている場合、FIFO が満杯のときは、新しいデータ・サンプルが FIFO に書き込まれずに失われます。RO がハイに設定されている場合、FIFO は先頭の場所にロールオーバーし、新しいデータ・サンプルが FIFO に書き込まれ、古いデータ・サンプルを上書きします。

**フラッシュ**

1に設定されている場合、FIFO内のデータ内容全体がリセットされます。

**FIFOからの電流および電圧の読み出し**

電流と電圧のデータは、次のレジスタを通じて FIFOから読み出されます。

FIFO 設定レジスタ（ビット Store V\_I）によって、ユーザが電流のみもしくは電圧のみ、または両方のいずれを読み出したいのかを指定します。読み出しポインタは、読み出すごとにインクリメントされます。

すべてのデータは2の補数です。

FIFOからの読み出しが可能なレジスタは次のとおりです。

FIFO 設定レジスタ：ビット Store IV：

- 2'b00：電流のみ（2バイト、読み出し専用）

| REGISTER NAME       | REGISTER ADDRESS | D15        | D14–D13                | D12          | D11–D0            |

|---------------------|------------------|------------|------------------------|--------------|-------------------|

| Current_Measurement | 0x0C             | Data Valid | Current Sign Extension | Current Sign | Current Magnitude |

- 2'b01：電圧のみ（2バイト、読み出し専用）

| REGISTER NAME       | REGISTER ADDRESS | D15        | D14–D13                | D12          | D11–D0            |

|---------------------|------------------|------------|------------------------|--------------|-------------------|

| Voltage_Measurement | 0x0E             | Data Valid | Voltage Sign Extension | Voltage Sign | Voltage Magnitude |

- 2'b10：電流と電圧（4バイト、読み出し専用）

| REGISTER NAME               | REGISTER ADDRESS | D31        | D30–D28                       | D27–D16              | D15      | D14–D12                       | D11–D0               |

|-----------------------------|------------------|------------|-------------------------------|----------------------|----------|-------------------------------|----------------------|

| Current_Voltage_Measurement | 0x10             | Data Valid | Voltage Sign<br>(repeated 3x) | Voltage<br>Magnitude | Reserved | Current Sign<br>(repeated 3x) | Current<br>Magnitude |

- 11：不使用

Data Valid = 0 : FIFO は空になっており、データに意味はありません。

Data Valid = 1 : FIFO は空になっていないので、データ是有効です。

電圧符号は、電圧計測値が常に正であるため、常に 0 でなくてはなりません。

**INT\_EN**

このレジスタは、ステータス・レジスタのマスクです。つまり、各ビットがステータス・レジスタからの割込み発生を有効／無効にします。これらのビットは、ステータス・レジスタにおいて報告されているビットと同じ順序です。

1 = 割込み発生が有効（デフォルト）

0 = 割込み発生が無効

| BIT         | D7                         | D6                      | D5                                      | D4                         | D3                        | D2                           | D1                                 | D0                        |