## 4.5V~36V、2.2MHz、0.6A/1.2A、 H ブリッジ内蔵の昇降圧コンバータ

MAX26039/MAX26040

### 概要

MAX26039/MAX26040 は、ハイサイド・スイッチとローサイド・スイッチを内蔵した小型の同期整流式昇降圧コンバータ・ファミリです。MAX26040 は、4.5V~36V の入力電圧で最大 1.2A を供給するように設計されており、無負荷時の自己消費電流はわずか 52 $\mu$ A です。これらの IC の出力電圧精度は $\pm 2\%$ です。電圧品質は、パワーグッド (PGOOD) 信号を観察することで監視可能です。

MAX26039/MAX26040 は、5V の固定出力電圧、または 4.0V~15V のプログラマブルな出力電圧を提供します。詳細については、[型番](#)の表を参照してください。周波数を 220kHz~2.2MHz の範囲で調整できるため、外付け部品の小型化と出力リップルの低減が可能です。MAX26040B および MAX26040D では、低自己消費電流 (52 $\mu$ A) のスキップ・モードを利用できます。これらの IC は、スペクトラム拡散周波数変調で動作することで、変調周波数による電磁干渉 (EMI) 放射を最小限に抑えることができます。

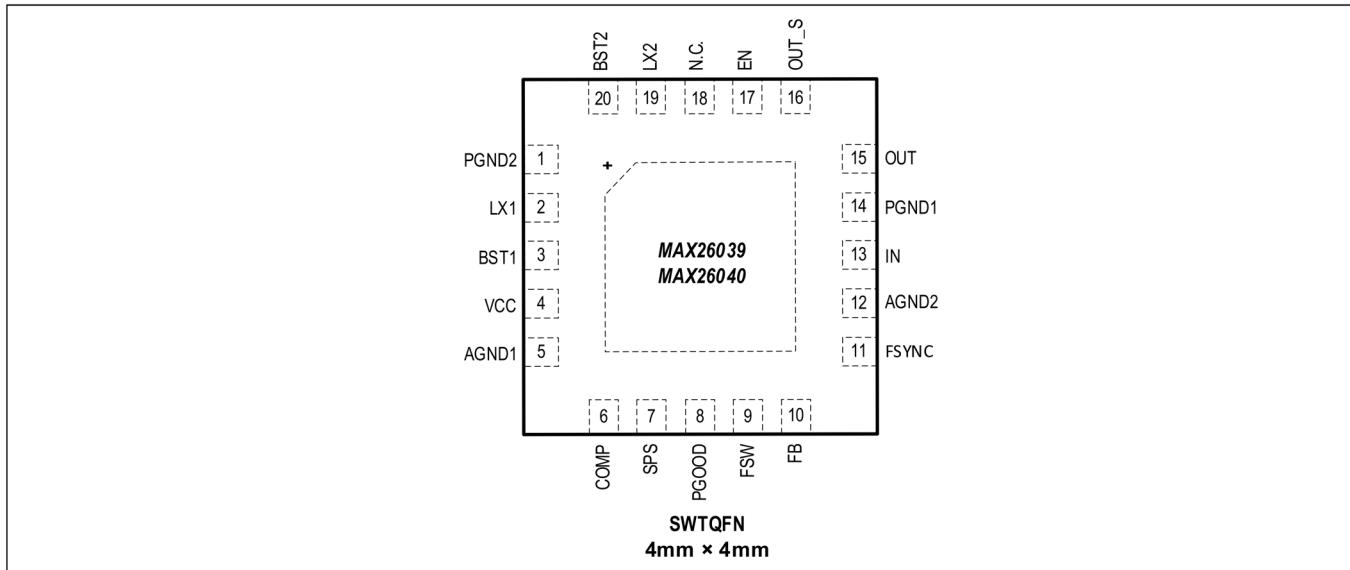

MAX26039/MAX26040 は、小型 (4mm × 4mm) の 20 ピン、TQFN 側面濡れ性パッケージで提供され、使用する外付け部品はごくわずかです。

### アプリケーション

- テレコム、サーバー、ネットワーク機器

- 12V/24V 産業用アプリケーション

- ポイントオブロード (POL) 電源

### 機能と利点

- 高電圧、高効率、低消費電力

- 動作電源電圧 : 4.5V~36V

- 最大 40V の入力トランジメントに対応可能

- EN ピン互換 : 3.3V~40V

- 出力電流 (MAX26039) : 0.6A (最大値)

- 出力電流 (MAX26040) : 1.2A (最大値)

- 温度範囲 : -40°C~+125°C

- 効率性を向上、および部品表 (BOM) コストと基板スペースを削減

- 電界効果トランジスタ (FET) H ブリッジ・アーキテクチャを内蔵

- 固定出力電圧

- 20 ピン SWTQFN パッケージ

- 低自己消費電流により、委託メーカー (OEM) の厳しい電流要件に対応可能

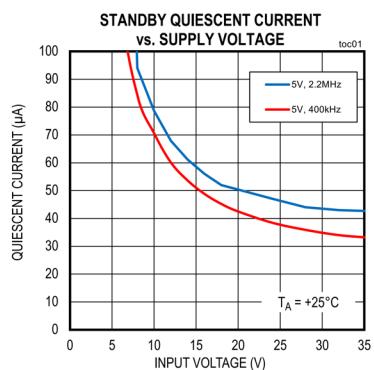

- スタンバイ・モード時の自己消費電流 : 52 $\mu$ A

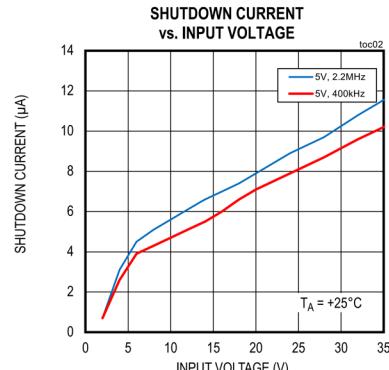

- シャットダウン・モード時の自己消費電流 : 10 $\mu$ A (最大値)

- 高いスイッチング周波数により、小型の外付け部品を使用可能

- 動作周波数 : 200kHz~2.2MHz

- スキップ・モードによる効率的な低消費電力動作が可能

- 固定周波数パルス幅変調 (PWM) モード

- 外部周波数同期

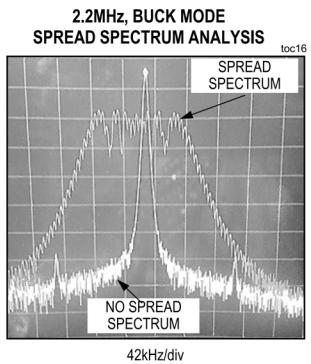

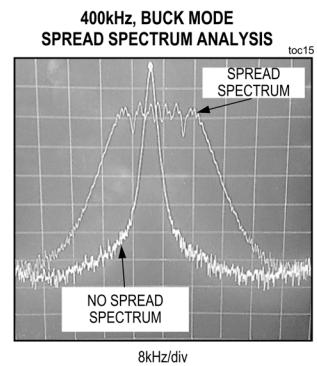

- スイッチング周波数での EMI 放射を低減

- スペクトラム拡散の有効化／無効化が可能

[型番](#)は、データシートの末尾に記載しています。

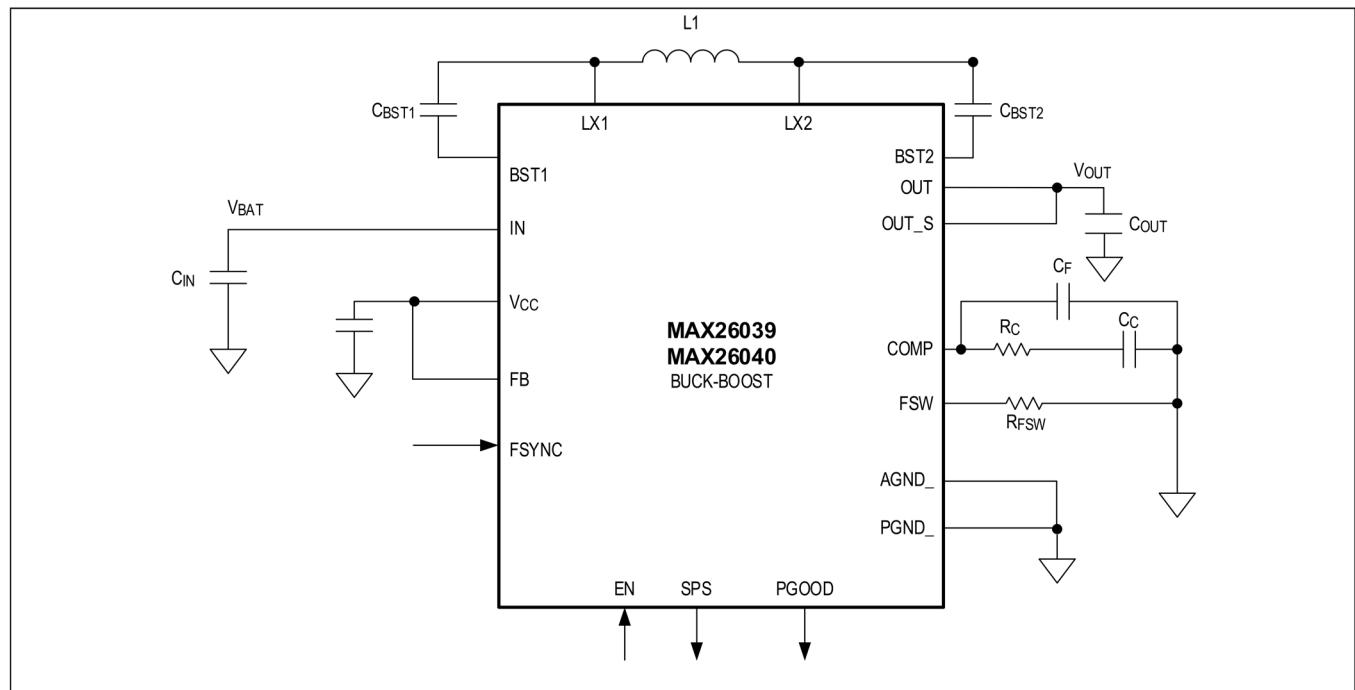

## 標準動作回路

## 絶対最大定格

|                                  |       |                               |

|----------------------------------|-------|-------------------------------|

| IN                               | ..... | -0.3V~+40V                    |

| EN、LX1 (Note 1)                  | ..... | -0.3V~V <sub>IN</sub> + 0.3V  |

| LX2、OUT_S (Note 1)               | ..... | -0.3V~V <sub>OUT</sub> + 0.3V |

| OUT                              | ..... | -0.3V~+18V                    |

| BST1~LX1、BST2~LX2 (Note 2)       | ..... | -0.3V~+5V                     |

| V <sub>CC</sub> 、PGOOD、SPS、FSYNC | ..... | -0.3V~+6V                     |

| COMP、FB、FSW                      | ..... | -0.3V~V <sub>CC</sub> + 0.3V  |

| PGND_                            | ..... | -0.3V~+0.3V                   |

|                                                                                        |              |

|----------------------------------------------------------------------------------------|--------------|

| 連続消費電力 (4層基板) 20 ピン SWTQFN、T <sub>A</sub> = +70°C<br>(+70°C を超えると 30.3mW/°C でディレーティング) | 2424mW       |

| 動作温度範囲                                                                                 | -40°C~+125°C |

| ジャンクション温度                                                                              | +150°C       |

| 保管温度範囲                                                                                 | -65°C~+150°C |

| はんだ処理温度 (リフロー)                                                                         | +260°C       |

| リード温度 (はんだ処理、10 秒)                                                                     | +300°C       |

**Note 1 :** 通常の動作状況で最大定格出力電流を上限とする負荷条件下においては、これらの上限値を超える 50ns 以内のトランジエント電圧に対する自己保護機能を備えています。

**Note 2 :** 内部で 5V にクランプされています。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作中に記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## 推奨動作条件

| PARAMETER                 | SYMBOL         | CONDITION | TYPICAL RANGE | UNIT |

|---------------------------|----------------|-----------|---------------|------|

| Ambient Temperature Range | T <sub>A</sub> |           | -40 to +125   | °C   |

注：これらの条件範囲は保証値ではありません。

## パッケージ情報

## SWTQFN-EP

|                                             |                           |

|---------------------------------------------|---------------------------|

| Package Code                                | T2044Y+4C                 |

| Outline Number                              | <a href="#">21-100068</a> |

| Land Pattern Number                         | <a href="#">90-0409</a>   |

| <b>THERMAL RESISTANCE, FOUR-LAYER BOARD</b> |                           |

| Junction to Ambient ( $\theta_{JA}$ )       | 33°C/W                    |

| Junction to Case ( $\theta_{JC}$ )          | 2°C/W                     |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、[www.analog.com/packages](#) で確認してください。パッケージ・コードの「+」、「#」、「-」は RoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面は RoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、[www.analog.com/thermal-tutorial](#) を参照してください。

## 電気的特性

（特に指定のない限り、 $V_{IN} = V_{EN} = 14V$ 、 $T_A = -40^{\circ}C \sim +125^{\circ}C$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$ 、 $C_{OUT} = 22\mu F$ 、 $C_{VCC} = 2.2\mu F$  ([Note 3](#))。）

| PARAMETER                            | SYMBOL             | CONDITIONS                                                                     | MIN  | TYP  | MAX  | UNITS    |

|--------------------------------------|--------------------|--------------------------------------------------------------------------------|------|------|------|----------|

| Input Voltage Range                  | $V_{IN}$           | Normal operation ( <a href="#">Note 4</a> )                                    | 4.5  |      | 36   | V        |

| Shutdown Supply Current              | $I_{IN\_SHUTDOWN}$ | $V_{EN} = 0V$                                                                  |      | 3    | 10   | $\mu A$  |

| Standby Supply Current               | $I_{IN\_STANDBY}$  | $V_{OUT} = 5V$ , no load, $V_{FSYNC} = 0V$ ,<br>MAX26039ATPAY+, MAX26040ATPAY+ | 52   | 85   |      | $\mu A$  |

| Undervoltage Lockout                 | $UVLO_{IN\_RISE}$  | $V_{IN}$ rising                                                                |      | 4.2  | 4.45 | V        |

|                                      | $UVLO_{IN\_FALL}$  | $V_{IN}$ falling, output enabled                                               |      |      | 1.95 |          |

| <b><math>V_{CC}</math> REGULATOR</b> |                    |                                                                                |      |      |      |          |

| Output Voltage                       | $V_{CC}$           | $V_{IN} > 6V$ , $I_{VCC} = 1mA$ to $20mA$                                      | 4.4  | 4.6  | 4.7  | V        |

| Dropout Voltage                      | $V_{CCDROP}$       | $V_{IN} = 3.5V$ , $I_{VCC} = 20mA$                                             |      | 0.15 | 0.4  | V        |

| Undervoltage Lockout                 | $UVLO_{VCC}$       | $V_{CC}$ rising                                                                |      | 3.5  | 3.9  | V        |

|                                      | $UVLO_{VCCFAL}$    | $V_{CC}$ voltage falling                                                       |      | 3.2  | 3.65 |          |

| Short-Circuit Current Limit          | $I_{VCCSC}$        | $V_{CC}$ shorted to AGND, after startup                                        |      | 50   | 85   | mA       |

| <b>BUCK-BOOST CONVERTER</b>          |                    |                                                                                |      |      |      |          |

| Fixed Output Voltage                 | $V_{OUT\_5V}$      | $V_{FB} = V_{CC}$                                                              | 4.91 | 5    | 5.08 | V        |

| Output-Voltage Adjustable Range      | $V_{OUT\_ADJ}$     |                                                                                | 4    |      | 12   | V        |

| Soft-Start Ramp Time                 | $t_{START}$        | $V_{OUT}$ from 10% to 90%                                                      | 4    | 7    | 10   | ms       |

| Autoretry                            | $t_{AUTO}$         | Autoretry time after a fault condition has been detected                       |      | 26   |      | ms       |

| Minimum On-Time                      | $t_{ON\_MIN}$      |                                                                                |      | 85   |      | ns       |

| Minimum Off-Time                     | $t_{OFF\_MIN}$     | Buck mode, $f_{SW} = 400kHz$                                                   |      | 300  |      | ns       |

| Dead Time                            | $DT$               | Rising and falling edges ( <a href="#">Note 5</a> )                            |      | 15   |      | ns       |

| LX1, LX2 Rise Time                   | $t_{LX\_RISE}$     | <a href="#">Note 5</a>                                                         |      | 5    |      | ns       |

| BST1 Switch On-Resistance            | $R_{ON\_BST1}$     | $V_{LX1} = 0V$ , $I_{BST1} = 10mA$                                             |      | 3.8  | 7.5  | $\Omega$ |

(特に指定のない限り、 $V_{IN} = V_{EN} = 14V$ 、 $T_A = -40^{\circ}C \sim +125^{\circ}C$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$ 、 $C_{OUT} = 22\mu F$ 、 $C_{VCC} = 2.2\mu F$  ([Note 3](#))。)

| PARAMETER                                     | SYMBOL              | CONDITIONS                                                                       | MIN   | TYP              | MAX   | UNITS     |

|-----------------------------------------------|---------------------|----------------------------------------------------------------------------------|-------|------------------|-------|-----------|

| BST2 Switch On-Resistance                     | $R_{ON\_BST2}$      | $V_{LX2} = 0V$ , $I_{BST2} = 10mA$                                               |       | 5                | 10    | $\Omega$  |

| <b>POWER MOSFET</b>                           |                     |                                                                                  |       |                  |       |           |

| DMOS_ Resistance                              | $R_{DS(ON)\_DMO S}$ | $V_{CC} = 4.5V$ , $I_{DS(ON)} = 0.2A$                                            |       | 70               | 150   | $m\Omega$ |

| LX1 Leakage Current                           | $I_{LX1\_LKG}$      | $V_{EN} = 0V$ , $V_{IN} = V_{LX1} = 36V$ , $T_A = +25^{\circ}C$                  |       | 1.0              |       | $\mu A$   |

| LX2 Leakage Current                           | $I_{LX2\_LKG}$      | $V_{EN} = 0V$ , $V_{LX2} = 12V$ , $T_A = +25^{\circ}C$                           |       | 1.0              |       | $\mu A$   |

| <b>CURRENT SENSE (<a href="#">Note 6</a>)</b> |                     |                                                                                  |       |                  |       |           |

| Current Limit Threshold                       | $I_{LIMIT1}$        | $V_{FB} = V_{CC}$ , $V_{OUT} = 5V$ (MAX26040)                                    | 1.9   | 2.15             | 2.5   | A         |

|                                               | $I_{LIMIT2}$        | $V_{FB} = V_{CC}$ , $V_{OUT} = 5V$ (MAX26039)                                    | 0.9   | 1.1              | 1.25  |           |

| <b>ERROR AMPLIFIER</b>                        |                     |                                                                                  |       |                  |       |           |

| Regulated Feedback Voltage                    | $V_{FB}$            |                                                                                  | 1.234 | 1.25             | 1.266 | V         |

| FB Leakage Current                            | $I_{FB\_LKG}$       | $V_{FB\_LKG} = V_{CC}$ , $T_A = +25^{\circ}C$                                    |       | 1                |       | $\mu A$   |

| FB Line-Regulation Error                      | $R_{EGFB}$          | $V_{IN} = 2V$ to $36V$ , $V_{FB} = 1.25V$                                        |       | 0.01             |       | %/V       |

| Transconductance (from FB to COMP)            | $gm$                | $V_{FB} = 1.25V$ , $V_{CC} = 4.5V$                                               | 450   | 750              | 1000  | $\mu S$   |

| <b>SWITCHING FREQUENCY</b>                    |                     |                                                                                  |       |                  |       |           |

| FSW Voltage                                   | $V_{FSW}$           | $I_{FSW} = 10\mu A$                                                              | 1.21  | 1.26             |       | V         |

| PWM Switching Frequency                       | $f_{SW1}$           | $R_{FSW} = 12k\Omega$                                                            | 2.00  | 2.20             | 2.35  | MHz       |

|                                               | $f_{SW2}$           | $R_{FSW} = 73.2k\Omega$                                                          | 380   | 415              | 450   | KHz       |

| PWM Switching-Frequency Range                 | $f_{RNG}$           |                                                                                  | 0.200 | 2.2              |       | MHz       |

| FSYNC External Clock Input                    | $f_{SYNC1}$         | Minimum sync pulse of 100ns, $R_{FOSC} = 12k\Omega$ ( <a href="#">Note 7</a> )   |       | 2.2              |       | MHz       |

|                                               | $f_{SYNC2}$         | Minimum sync pulse of 100ns, $R_{FOSC} = 73.2k\Omega$ ( <a href="#">Note 7</a> ) |       | 440              |       | KHz       |

| Spread Spectrum                               | SPS                 | Spread spectrum enabled ( <a href="#">Note 5</a> )                               |       | $f_{SW\_ \pm 3}$ |       | %         |

| <b>OUTPUT MONITORS</b>                        |                     |                                                                                  |       |                  |       |           |

| Output Overvoltage Threshold                  | $V_{OUT\_OVP\_R}$   | Detected with respect to $V_{FB}$ rising                                         | 105.5 | 108              | 110.8 | %         |

|                                               | $V_{OUT\_OVP\_F}$   | Detected with respect to $V_{FB}$ falling                                        | 102.5 | 105              | 107.8 |           |

| PGOOD Threshold Rising                        | $P_{GOOD\_R}$       | % of $V_{OUT}$ , rising                                                          | 94    | 96               | 98.3  | %         |

| PGOOD Threshold Falling                       | $P_{GOOD\_F}$       | % of $V_{OUT}$ , falling                                                         | 91    | 93               | 95.6  | %         |

| PGOOD Output Low Voltage                      | $V_{PGOODL}$        | $I_{SINK} = 1mA$                                                                 |       | 0.3              |       | V         |

| PGOOD Leakage Current                         | $I_{PGOOD\_LEAK}$   | $V_{PGOOD} = V_{CC}$ , $T_A = +25^{\circ}C$                                      |       | 1                |       | $\mu A$   |

| PGOOD Debounce Time                           | $t_{PGOOD}$         | Fault detection, rising                                                          |       | 60               |       | $\mu s$   |

|                                               |                     | Fault detection, falling                                                         |       | 4                |       |           |

| <b>LOGIC INPUTS (EN, FSYNC, SPS)</b>          |                     |                                                                                  |       |                  |       |           |

| Input High Level                              |                     | $V\_rising$                                                                      | 2.1   |                  |       | V         |

| Input Low Level                               |                     | $V\_falling$                                                                     |       | 0.8              |       | V         |

(特に指定のない限り、 $V_{IN} = V_{EN} = 14V$ 、 $T_A = -40^{\circ}C \sim +125^{\circ}C$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$ 、 $C_{OUT} = 22\mu F$ 、 $C_{VCC} = 2.2\mu F$  (Note 3)。)

| PARAMETER                     | SYMBOL         | CONDITIONS                            | MIN | TYP | MAX | UNITS       |

|-------------------------------|----------------|---------------------------------------|-----|-----|-----|-------------|

| EN, SPS Input Leakage Current | $I_{IN\_LEAK}$ | $V_- = V_{CC}$ , $T_A = +25^{\circ}C$ |     | 1   |     | $\mu A$     |

| FSYNC Pull-Down Resistance    | $R_{FSYNC-PD}$ |                                       |     | 1   |     | $M\Omega$   |

| <b>THERMAL SHUTDOWN</b>       |                |                                       |     |     |     |             |

| Thermal-Shutdown Threshold    | $T_{SHUTDOWN}$ |                                       | 166 |     |     | $^{\circ}C$ |

| Thermal-Shutdown Hysteresis   | $T_{HYS}$      |                                       | 18  |     |     | $^{\circ}C$ |

**Note 3 :** すべての限界値は $+25^{\circ}C$ で100%テストされています。動作温度範囲および対応する電源電圧範囲にわたる限界値は、設計と特性評価によって裏付けられています。代表値は $T_A = +25^{\circ}C$ で規定しています。

**Note 4 :** 入力電圧範囲は出力電圧に応じて異なります (型番の表を参照)。

**Note 5 :** 製品テストは行っていませんが、設計により裏付けられています。

**Note 6 :** 電流の測定は、デバイスがスイッチングしていないときに行われています。コンバレータの伝搬遅延のため、動作時に測定される電流制限値はこれより高い値になります。

**Note 7 :** FSYNCピンに印加する外部クロック周波数は、FSWピンに接続された抵抗で設定される公称スイッチング周波数の-10%~0%の範囲内の周波数にしてください。

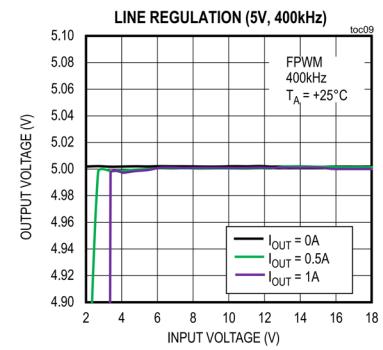

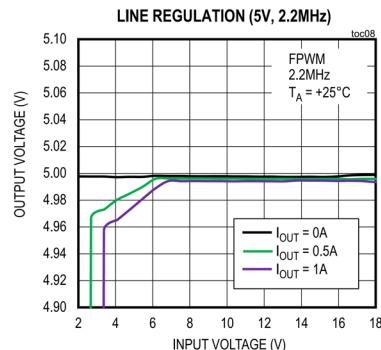

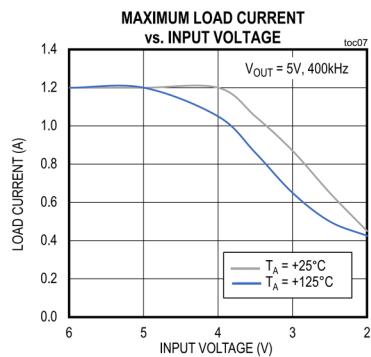

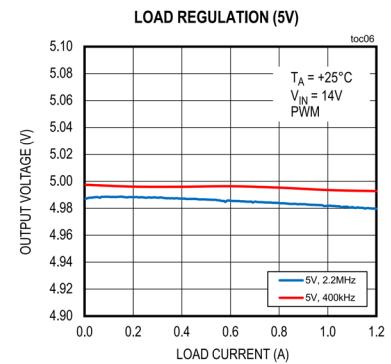

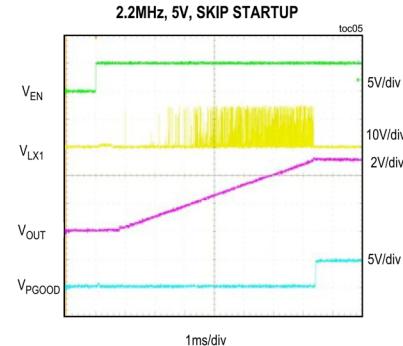

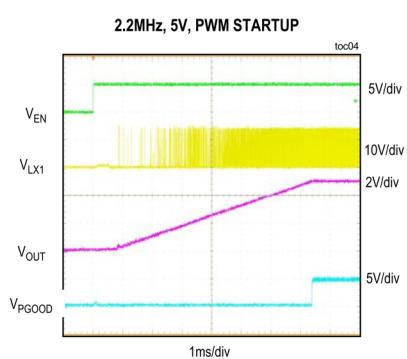

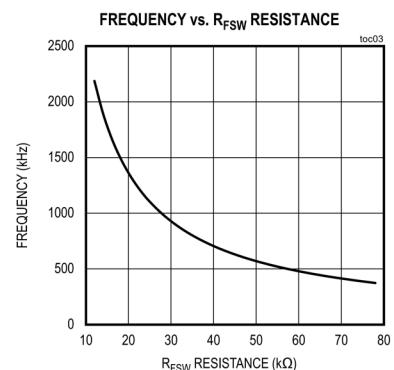

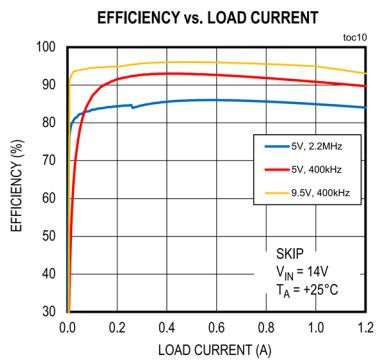

## 標準動作特性

(特に指定のない限り、 $T_A = +25^\circ\text{C}$ )

(特に指定のない限り、 $T_A = +25^\circ\text{C}$ )

## ピン配置

## 端子説明

| ピン番号 | 名称              | 機能                                                                                                                                                 |

|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | PGND2           | 昇圧側の内蔵ローサイドFET用グランド・リファレンス。                                                                                                                        |

| 2    | LX1             | INとPGNDの間のスイッチング・ノード。                                                                                                                              |

| 3    | BST1            | LX1ノードのハイサイド・ドライバ用ブーストストラップ・コンデンサ。BST1とLX1の間には100nFのコンデンサを接続します。                                                                                   |

| 4    | V <sub>CC</sub> | リニア・レギュレータ出力。V <sub>CC</sub> から内部回路に電力が供給されます。2.2μFのセラミック・コンデンサでAGNDにバイパスします。                                                                      |

| 5    | AGND1           | ICのアナログ・グランド。PCBのリファレンス用グランド・プレーンに接続します。                                                                                                           |

| 6    | COMP            | 外部補償。ループの外部補償ネットワークに接続します。                                                                                                                         |

| 7    | SPS             | スペクトラム拡散の有効化／無効化ピン。スペクトラム拡散をオンにする場合はハイに、オフにする場合はローにします。                                                                                            |

| 8    | PGOOD           | オープン・ドレイン出力、アクティブ・ハイのパワーグッド・インジケータ。V <sub>OUT</sub> がレギュレーション・ポイントの96%を超えると、PGOODがアサートされます。V <sub>OUT</sub> がレギュレーション・ポイントの93%を下回ると、PGOODはローになります。 |

| 9    | FSW             | スイッチング周波数設定用の内部発振器ピン。グランドとの間に抵抗を接続して、目的の周波数を設定します。                                                                                                 |

| 10   | FB              | 帰還アナログ入力。外部抵抗分圧器をOUTからFBおよびAGNDに接続して、目的の出力電圧を設定します。V <sub>CC</sub> に接続すると、出力電圧は5Vに設定されます。                                                          |

| 11   | FSYNC           | 同期入力。軽負荷での動作時にスキップ・モードを有効にするには、AGNDに接続します。軽負荷での動作時に強制PWMモードにするには、V <sub>CC</sub> に接続します。FSYNCは1MΩのプルダウン抵抗を内蔵しています。                                 |

| 12   | AGND2           | アナログ・グランド・リファレンス。                                                                                                                                  |

| 13   | IN              | 電源電圧入力。INから内部電圧レギュレータに電力が供給されます。INは4.7μF(最小値)のセラミック・コンデンサでPGNDにバイパスしてください。                                                                         |

| 14   | PGND1           | 降圧側の内蔵ローサイドFET用グランド・リファレンス。                                                                                                                        |

| 15   | OUT             | スイッチング・レギュレータ電圧出力。                                                                                                                                 |

| 16   | OUT_S           | レギュレータの電圧検出入力。                                                                                                                                     |

| 17   | EN              | 高電圧イネーブル入力。                                                                                                                                        |

| 18   | N.C.            | 接続なし。内部ではどの回路にも接続されていません。                                                                                                                          |

|    |      |                                                                       |

|----|------|-----------------------------------------------------------------------|

| 19 | LX2  | OUT と PGND の間のスイッチング出力ノード。                                            |

| 20 | BST2 | LX2 ノードのハイサイド・ドライバ用ブートストラップ・コンデンサ。BST2 と LX2 の間には 100nF のコンデンサを接続します。 |

| —  | EP   | 露出パッド。                                                                |

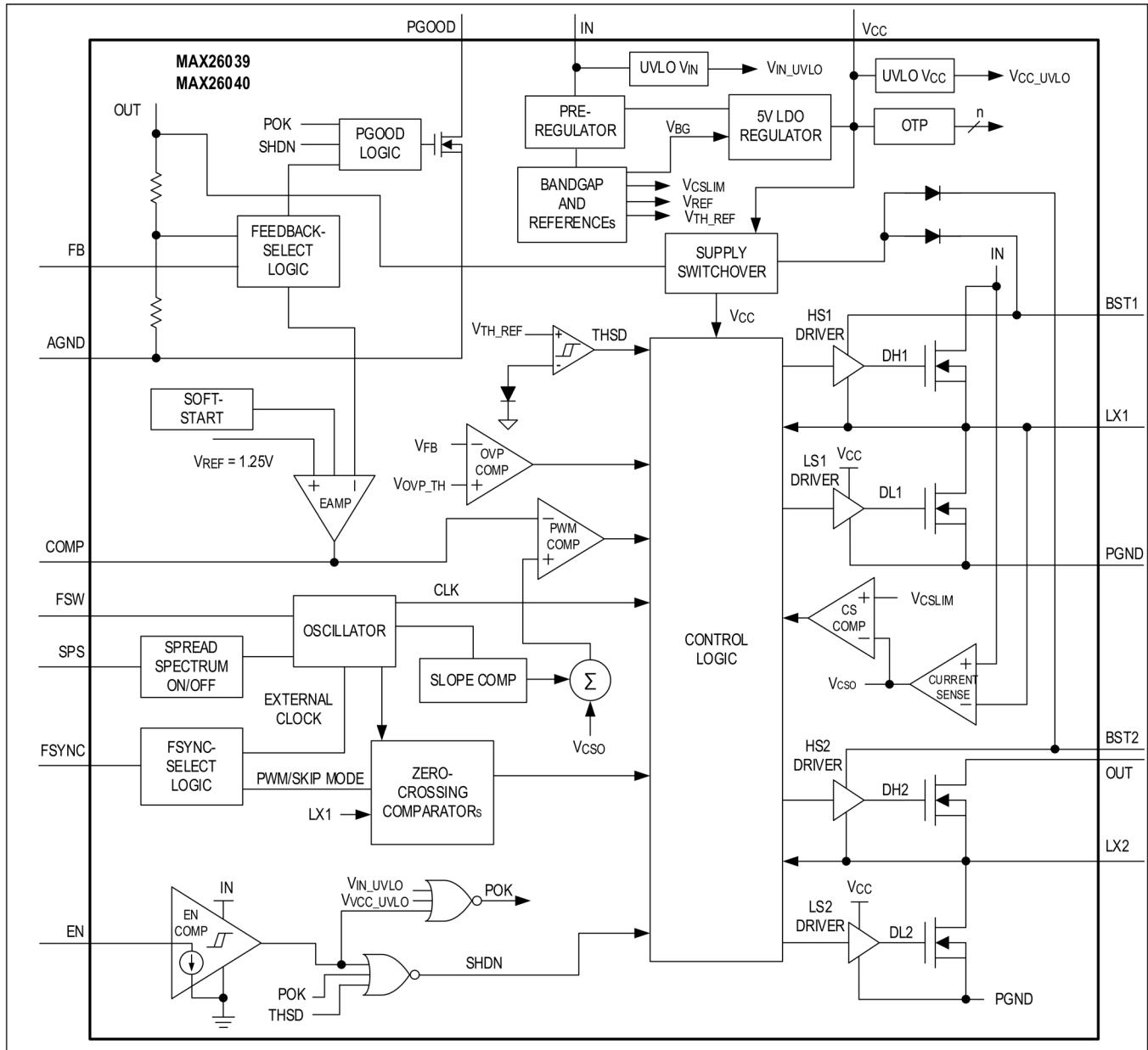

## 機能図

## 詳細説明

MAX26039/MAX26040 は、H ブリッジ・アーキテクチャを内蔵した 0.6A/1.2A の電流モード昇降圧コンバータです。3.5V~36V の入力電圧で動作し、無負荷時の自己消費電流はわずか  $52\mu\text{A}$  です。ひとたび起動条件を満足すると、デバイスは 2V~36V の広い入力電圧範囲で動作します。スイッチング周波数は 200kHz~2.2MHz の範囲で抵抗によってプログラム可能です。また、外部クロックに同期させることができます。デバイスは、5V 固定として、または 4V~15V の範囲で調整して電圧を出力できます。入力電圧範囲が広く、また、低入力トランジエント時に出力電圧を一定に保つことができます。軽負荷アプリケーションでは、ロジック入力 (FSYNC) によりスキップ・モードで消費電流を低減したり、固定周波数の強制 PWM モードで周波数変動を無くし EMI を最小限に抑えたりできます。保護機能としては、サイクル単位の電流制限と自動回復機能を備えたサーマル・シャットダウンがあります。

## リニア・レギュレータ出力

このコンバータには、内部回路ブロックに給電する 4.6V のリニア・レギュレータ ( $V_{CC}$ ) が内蔵されています。 $V_{CC}$  と AGND の間に  $2.2\mu\text{F}$  のセラミック・コンデンサを接続します。起動シーケンスが完了すると、OUT ピンによって  $V_{CC}$  が駆動され、IN が 2V まで低下しても動作できるようになります。

## 広い入力電圧範囲

このデバイスは、3.5V~36V の広い入力電圧範囲に対して仕様規定された電源入力 (IN) を備えています。最初の起動条件を満足すると ( $BIAS > UVLO$  および  $IN > 3.5V$ ) 、デバイスは 2V~36V の拡張入力範囲で動作します。IN ピンは、内部 BIAS 電源と、4 つの H ブリッジ金属酸化膜半導体電界効果トランジスタ (MOSFET) に給電します。出力電圧が 3.2V を超え、スイッチング・レギュレータの起動が完了すると、BIAS 電圧は OUT ピンによって駆動されます。このデバイスは、H ブリッジの昇降圧アーキテクチャにより、最初のパワーアップが完了した後、2V の入力で動作することができます。

## 同期入力

同期入力 (FSYNC) は、動作モードの選択および周波数の制御に使用するロジックレベル入力です。FSYNC を BIAS または外部クロックに接続すると、固定周波数の強制 PWM 動作が有効になります。FSYNC を AGND に接続すると、スキップ・モード動作が有効になります。FSYNC の外部クロックは内部クロックより 10% 低い周波数でできます。このデバイスは、2 周期内で外部クロックに同期します。2 クロック周期を過ぎても FSYNC に外部クロック信号が現れない場合、デバイスは内部クロックを使用します。

## パワーグッド出力

このデバイスは、オープン・ドレインのパワーグッド (PGOOD) 出力を備えています。PGOOD は、 $V_{OUT}$  がレギュレーション電圧の 96% を超えるとアサートされ、レギュレーション電圧の 93% を下回るとアサート解除されます。PGOOD は、 $10\text{k}\Omega$  の抵抗を使用して BIAS に接続します。

## スペクトラム拡散オプション

このデバイスでは SPS ピンを使用することでスペクトラム拡散を有効化できます。SPS をハイにするとスペクトラム拡散が有効化され、動作周波数は  $f_{osc}$  を中心に  $\pm 3\%$  の範囲で変動します。変調信号は 2.1MHz 時に周期が  $110\mu\text{s}$  の三角波です。したがって、 $f_{osc}$  は  $110\mu\text{s}$  の間に 3% 低下して 2.2MHz になり、更に  $110\mu\text{s}$  かけて 3% 上昇して 2.1MHz に戻ります。そしてこのサイクルが繰り返し続けられます。 $f_{osc}$  が 2.1MHz 以外の周波数で動作する場合、変調信号は比例して変化します（例えば、400kHz の場合、 $110\mu\text{s}$  の変調周期は  $110\mu\text{s} \times 2.2\text{MHz}/0.4\text{MHz} = 550\mu\text{s}$  に増加します）。デバイスが外部クロックに同期している場合、内部のスペクトラム拡散は無効化されますが、デバイスは FSYNC ピンの入力クロックをフィルタリングしないため、駆動外部クロックに存在する変調は（スペクトラム拡散のものを含め）そのまま通過します。

## 内部発振器 (FSW)

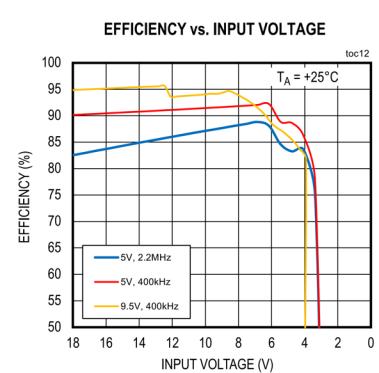

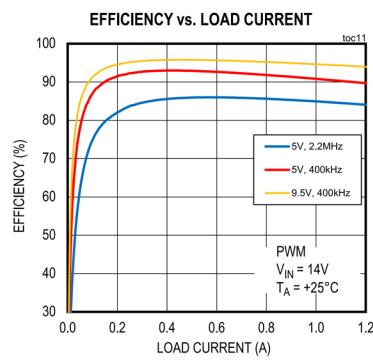

スイッチング周波数は、FSW ピンと AGND の間に接続される抵抗 ( $R_{FSW}$ ) によって設定されます（例えば、 $R_{FSW} = 73.2\text{k}\Omega$  で 400kHz のスイッチング周波数に設定されます）。周波数を高くすると、インダクタの値を低くし、出力容量を小さくできます。その結果、高いスイッチング周波数ではピーク電流と  $I^2R$  損失は低くなりますが、コア損失、ゲート・チャージ電流、スイッチング損失は増加します。

## 過熱保護

熱過負荷保護機能により、コンバータの総消費電力が制限されます。ジャンクション温度が  $+166^\circ\text{C}$  (代表値) を超えると、内部サーマル・センサーが内部バイアス・レギュレータと降圧コンバータをシャットダウンし、デバイスを冷却します。ジャンクション温度が  $18^\circ\text{C}$  低下すると、サーマル・センサーは再びデバイスをオンにします。

## 軽負荷時の動作

軽負荷時には、FSYNC が AGND に接続されデバイスが降圧領域に入った場合、サイクルのスキップを開始して高効率を維持します。インダクタ電流のゼロ交差を 32 回連続で検出すると、デバイスはパルス周波数変調 (PFM) モードに入ります。PFM モードでは、ピーク・インダクタ電流制限値は約 480mA に変化し (0.6A MAX26039 の場合は約 240mA)、インダクタ電流が負の値になるのを防ぎます。これにより、出力電圧の上昇が起こります。出力電圧がレギュレーション値の 103% を超えると、デバイスはスイッチングを停止します。出力電圧がレギュレーション値の 101% を下回ると、スイッチングを再開します。デバイスが PFM モードに入るとときの負荷電流は、使用するインダクタとインダクタ電流によって異なります。

## ソフトスタート

固定周波数の補助発振器によってデバイスのソフトスタート時間が決められています。これにより、すべての出力電圧と周波数には、7ms (代表値) のソフトスタート時間があります。

## 過電圧保護

このデバイスは、サイクルごとに過電圧保護を行います。専用の内部コンパレータが、固定のスレッショルドで出力電圧を監視します。出力電圧がレギュレーション値の 108% (代表値) より高くなると、降圧側のハイサイド・スイッチ (DH1) と昇圧側のローサイド・スイッチ (DL2) がオフになります。スイッチングは、出力電圧がレギュレーション値の 105% (代表値) を下回るまでオフになります。

## 短絡保護

迅速で堅牢な短絡保護を行うため、デバイスは常に DH1 電流を監視しています。入力電流が 16 回連続でピーク電流制限値に達し、出力電圧がレギュレーション値の 60%未満になると、デバイスはスイッチングを停止して、ヒップ・モードに入ります。ヒップ・モードでの自動リトライ時間は 26ms (代表値) です。

## アプリケーション情報

### インダクタの選択

インダクタの設計は、サイズ、効率、制御、帯域幅、コンバータの安定性などの兼ね合いで決まります。昇降圧アプリケーションでは、昇圧モードと昇降圧モードに右半平面（RHP）ゼロが存在するため、正しい値のインダクタを選択することが一層重要になります。インダクタンス値を大きくすると、MOSFETの実効値電流損失、およびインダクタのコア損失と巻線損失が低減します。一方で、大きなインダクタンス値は制御ループの速度を低下させ、RHPゼロの周波数を低くします。これにより、安定性に懸念が生じる場合があります。

インダクタの選択は、インダクタの電流リップルに基づいて始めます。ここで、インダクタの電流リップルは降圧モードと昇圧モードでの最大インダクタ電流のパーセント値として表され、式1と式2を使用します。通常、最大インダクタ電流の40%のリップルが速度と効率の間でバランスのとれた妥協点です。

式1

$$L_{BUCK} > \frac{(V_{IN_{MAX}} - V_{OUT}) \times V_{OUT}}{f_{SW} \times I_{LMAX} \times \% \Delta I_{RIPPLE} \times V_{IN_{MAX}}}$$

両方の動作領域におけるリップルとRHPゼロを考慮してインダクタンスの最終値を選択します。インダクタンスの最終値を選択したら、ピーク・インダクタ電流を計算し、飽和電流がピーク・インダクタ電流より20%以上大きく低DC抵抗（DCR）のインダクタを選択します。

### ピーク・インダクタ電流

インダクタの定格は最大飽和電流によって決定します。インダクタ電流の最大値は、最大負荷電流にピークtoピーク・リップル電流の半分を加えたものです。選択したインダクタンス値に対して、実際のピーク値は式2に示すように計算できます。

式2

$$I_{LPEAK} = \frac{V_{OUT} \times I_{OUT}}{V_{IN_{MIN}}} + \frac{V_{IN_{MIN}} \times \left(1 - \frac{V_{IN_{MIN}}}{V_{OUT}}\right)}{L \times f_{SW} \times 2}$$

### 入力コンデンサの設計

入力コンデンサは、電源から流れるピーク電流を低減すると共に、回路のスイッチングによって生じる入力のノイズと電圧リップルを低減します。降圧モードの動作では、入力コンデンサに不連続な入力電流が流れることになるので、式3で得られる入力実効値電流に対応できるよう設計する必要があります。

式3

$$I_{RMS} = \frac{I_{LOAD} \times \sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}}{V_{IN}}$$

最大入力実効値電流は  $V_{IN} = 2 \times V_{OUT}$  のときに発生し、式4で得られます。

式4

$$I_{RMS} = \frac{I_{LOAD}}{2}$$

### 出力コンデンサの設計

高昇圧モード ( $V_{IN-MIN}$  および重負荷電流) での最も厳しい条件における出力容量の最小値を計算するには、式5を使用します。

式5

$$C_{OUT-MIN} \geq \frac{I_{OUT_{MAX}} \times D_{MAX}}{f_{SW} \times \Delta V_{OUT}}$$

ここで、 $D_{MAX} = 0.98A$ 。高昇圧モード状態で動作していない場合には、もっと小さい出力容量を使用できます。

出力フィルタ・コンデンサは、出力リップルと負荷過渡応答の要求を満たすため、等価直列抵抗 (ESR) が十分に低い値でなければなりません。出力電圧リップルの許容値、および負荷ステップ電流時における出力電圧の最大偏差によって、出力容量とその ESR が決まります。出力リップルは、 $\Delta V_0$  (コンデンサの放電によるもの) と  $\Delta V_{ESR}$  (出力コンデンサの ESR によるもの) で構成されています。出力容量は、過電圧フォルト保護機能をトリップさせることなく、全負荷条件から無負荷条件に遷移するときのインダクタのエネルギーを吸収できるだけの大きな値が必要です。出力には、ESR が低いセラミックまたはアルミニウムの電解コンデンサを使用します。高容量で低 ESR のコンデンサを使用する場合、フィルタ・コンデンサの ESR が出力電圧リップルに対して支配的になります。このため、出力コンデンサのサイズは、出力電圧リップル ( $V_{RIPPLE(P-P)}$ ) の仕様を満足するために必要な最大 ESR によって決まります。

式 6

$$V_{RIPPLE(P-P)} = ESR \times I_{OUTMAX} \times LIR$$

ここで、 $LIR = 0.4$  ( $LIR$  は最大インダクタ電流での P-P リップル電流の比です。40%、すなわち 0.4 がこのパラメータの想定値として妥当な値です)。必要となる実容量値は、低 ESR の実現に必要な物理的サイズやコンデンサ技術の特性と関連します。したがって、通常は容量の値よりも ESR と電圧の定格値を基準に選択します。アルミニウムの電解コンデンサの場合、出力リップル全体が  $\Delta V_{ESR}$  によるもので、セラミック・コンデンサを使用する場合、ESR とコンデンサの放電による出力リップル電圧への寄与分は等しいと仮定します。セラミック・コンデンサなどの低容量のフィルタ・コンデンサを使用する場合、そのサイズは通常、電圧の低下や上昇が負荷過渡応答時に問題を生じないような容量として決定します。一般的には、オーバーシュートの条件を満たすために十分な容量が追加されていれば、負荷の立上がりエッジでのアンダーシュートの問題は生じません。しかし、低容量のフィルタ・コンデンサは一般的にゼロでの ESR が高く、総合的安定性を損なうことがあります。

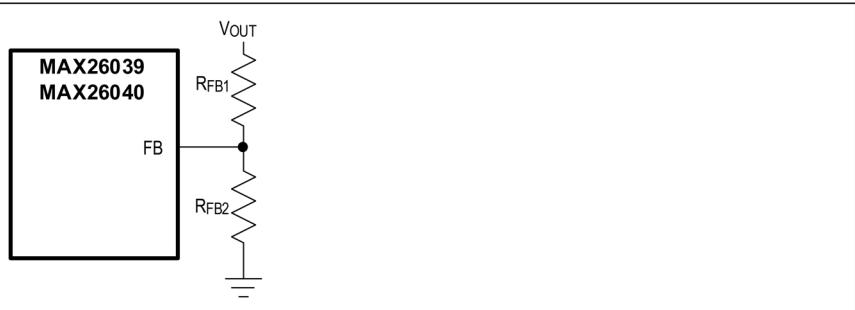

## 出力電圧の設定

FB を  $V_{CC}$  に接続すると、帰還ピン (FB) と AGND の間に接続された内蔵プリセット抵抗分圧器によって固定の出力電圧 (5V) が有効となります。出力電圧を 4V~15V に外部調整するには、出力 (OUT) と FB および AGND の間に抵抗分圧器を接続します。 $R_{FB1}$  と  $R_{FB2}$  の値は式 7 を使用して計算します。

式 7

$$R_{FB1} = R_{FB2} \left[ \left( \frac{V_{OUT}}{V_{FB}} \right) - 1 \right]$$

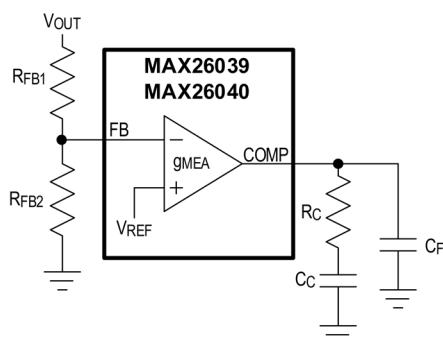

ここで、 $V_{FB} = 1.25V$  (代表値) 、 $R_{FB2}$  は  $50k\Omega$  未満で、通常  $10k\Omega$  に設定します。図 1 を参照してください。

図 1. 出力電圧の設定

## MAX26040 におけるエラー・アンプ補償の設計

MAX26040 コンバータは、内部トランジスタコンダクタンス・アンプの入力端子と出力端子を反転して使用することで、外部の周波数補償を利用することができます (図 2 参照)。

図2.補償ネットワーク

コントローラはピーク電流モード制御のアーキテクチャを使用しています。このアーキテクチャは、外付けインダクタを通じて必要な電流を流すことにより出力電圧を安定化します。電流モード制御は、インダクタと出力コンデンサによってできる帰還ループの双極を、2つの单極に分割します。極のうちの1つは、コンバータの代表的な帯域幅を超える高い周波数に移動するため、单極のシステムになります。これにより、ループの補償に必要となるのはタイプIIのみで、補償が容易になります。昇圧モードでは、電源段によって新たなる右半平面(RHP)が加わるため、制御ループに位相遅延が追加されます。コンバータの安定性にこのRHPゼロによる影響が出るのを避けるため、帯域幅が最も厳しい場合のRHPゼロ周波数の約4分の1になるように補償を設計します。

外部補償の設計は、最適な設計に達するまで何回か繰り返す必要があります。高昇圧モード、および重負荷( $V_{IN-MIN}$ )で動作する場合、RHPゼロ周波数は減少するため、補償の設計には注意が必要です。

降圧モードと昇圧モードのどちらに対しても補償を設計できる便利な方法は最小入力電圧と重負荷(高昇圧モード)で補償を設計することです。この動作条件では、RHPゼロはその最小周波数になります。そのRHPゼロ周波数の5分の1以下の帯域幅になるように補償を設計します。コンバータのクローズド・ループ・ゲインは、コンバータのパワーワンのゲインとエラー・アンプのゲインの組み合わせになります。ここで、コンバータの周波数は以下のようになります。

式8

$$f_{p\text{BOOST}} = \frac{2}{2\pi \times R_{\text{LOAD}} \times C_{\text{OUT}}}$$

$$f_{z\text{MOD}} = \frac{1}{2\pi \times \text{ESR} \times C_{\text{OUT}}}$$

$$f_{z\text{RHP}} = \frac{R_{\text{LOAD}} \times (1 - D)^2}{2\pi \times L}$$

ここで、エラー・アンプの周波数は以下のようになります。

式9

$$f_{pd\text{EA}} = \frac{1}{2\pi \times (R_{O_{\text{EA}}} || R_C) \times C_C}$$

ここで、

$R_{O_{\text{EA}}}$ はエラー・アンプの出力インピーダンスで、 $18\text{M}\Omega$ (代表値)です。 $R_{O_{\text{EA}}}$ と $R_C$ の並列抵抗は、支配的な因子である $RC$ になります。これにより、以下のように簡略化した式が得られます。

$$f_{pd\text{EA}} = \frac{1}{2\pi \times R_C \times C_C}$$

式 10

$$f_{zEA} = \frac{1}{2\pi \times R_C \times C_C}$$

$$f_{pEA} \cong \frac{1}{2\pi \times R_C \times C_F}$$

if  $C_F \ll C_C$

安定性を得るには、以下の指示に従って適切な設計を行ってください（設計例については、[表 1](#)を参照）。

- 必要なインダクタンス（L）の最小値を計算します。

- 昇圧コンバータが持つ右半平面ゼロ（ $f_{zRHP}$ ）を計算します。

- $f_{zRHP}$ の5分の1以下になるようにクロスオーバー周波数（ $f_C$ ）を設定します。

- パワー一段の残りの要素（ $f_{pBOOST}$ と $f_{zMOD}$ ）を計算します。

- 帯域幅をRHPの5分の1以下に設定します： $f_{BW} = f_{zRHP}/5$ 。

- エラー・アンプの補償は、以下のように選択します。

- $f_{zEA}$ は $f_C$ の3分の1です。

- エラー・アンプのゼロを算出したら、 $f_{pdEA}$ を計算します。

- $f_{pEA}$ は、降圧モードの周波数応答と干渉しないよう、十分高い値に設定します。昇圧のみのモードでは、 $f_{pEA}$ は $f_{zMOD}$ と $f_{zRHP}$ のどちらか低い周波数に設定することができます。

まず、コントローラの出力電圧とスイッチング周波数の設定から設計を始めます。8Vの出力電圧では、 $R_{FB2} = 10\text{k}\Omega$ を選択することで式7から $R_{FB1} = 54.2\text{k}\Omega$ が得られます。 $R_{FSW}$ とAGNDの間に $73.2\text{k}\Omega$ を接続することで、スイッチング周波数は400kHzに設定されます。

表 1. 設計例

| PARAMETERS | VALUE      |

|------------|------------|

| $V_{OUT}$  | 8V         |

| $f_{SW}$   | 400kHz     |

| $V_{SUP}$  | 3V to 18V  |

| $I_{OUT}$  | 1.2A (max) |

## インダクタの設計

インダクタの選択は、降圧モードの電流リップルを40%と仮定して始めます。式11と式12を用いて最小インダクタンスを求めます。

式 11

$$L_{BUCK} > \frac{(V_{IN_{MAX}} - V_{OUT}) \times V_{out}}{f_{SW} \times I_{L_{MAX}} \times \% \Delta I_{RIPPLE} \times V_{IN_{MAX}}} = 23\mu\text{H}$$

この計算値から、最も近い標準値の 22 $\mu$ Hを選択します。

式 12

$$I_{L_{\text{PEAK}}} = \frac{V_{\text{OUT}} \times I_{\text{OUT}}}{V_{\text{IN}_{\text{MIN}}}} + \frac{V_{\text{IN}_{\text{MIN}}} \times \left(1 - \frac{V_{\text{IN}_{\text{MIN}}}}{V_{\text{OUT}}}\right)}{L \times f_{\text{SW}} \times 2} = 3.31A$$

飽和電流 (Isat) がピーク・インダクタ電流より 20%以上高いインダクタを選択します。

コンバータが昇圧モードで動作する場合、インダクタの選択によって右半平面周波数が決まり、それにより高昇圧モードでのコンバータの安定性が決まります。式 13 に示すように、計算したインダクタ値を使用して高昇圧モードでの RHP ゼロ周波数を計算します。

式 13

$$f_{zRHP} = \frac{R_{\text{LOAD}} \times (1 - D)^2}{2\pi \times L} = 6.6\text{kHz}$$

RHP ゼロが 6.6kHz の場合、高昇圧モードで安定した動作を得るには、ループのクロスオーバー周波数 (fc) を RHP ゼロ周波数の 5 分の 1 以下にする必要があります。

## 出力コンデンサの設計

最大デューティ・サイクルが 0.98、かつ最も厳しい条件下 (低 V<sub>IN</sub>、重負荷電流) で、最小出力容量を式 14 のように計算します。

式 14

$$C_{\text{OUT}_{\text{MIN}}} = \frac{I_{\text{OUT}_{\text{MAX}}} \times D_{\text{MAX}}}{f_{\text{SW}} \times \Delta V_{\text{OUT}}} = 118\mu\text{F}$$

## エラー・アンプ補償の設計

補償の設計は、昇圧パワ一段で重要な周波数を最低入力電圧と最大負荷で計算することから始めます (式 15 を参照)。

式 15

$$f_{p\text{BOOST}} = \frac{2}{2\pi \times R_{\text{LOAD}} \times C_{\text{OUT}}} = 415\text{Hz}$$

$$f_{z\text{MOD}} = \frac{1}{2\pi \times ESR \times C_{\text{OUT}}} = 337\text{kHz}$$

6.6kHz の RHP ゼロでは、安定した動作を得るためにクローズド・ループのコンバータの目標帯域幅 (fc) を 1.32kHz (RHP の 5 分の 1) 以下にする必要があります。エラー・アンプのゼロは、クロスオーバー周波数で十分な位相ブーストを得るために、この帯域幅より十分に低い値にする必要があります。通常、このゼロは低周波数の極に近い値に設定します。この場合、補償の抵抗 R<sub>C</sub> は式 16 を用いて計算できます。

式 16

$$R_C = 2\pi \times f_C \times \frac{R_{CB} \times C_{\text{OUT}}}{g_m \times (1 - D_{\text{BOOST}})} \times \frac{(R_{FB2} + R_{FB1})}{R_{FB2}} = 13.92\text{k}\Omega$$

ここで、R<sub>CS</sub> = 0.6 $\Omega$ 、g<sub>m</sub> = 712 $\mu$ S (代表値)、(または、電気的特性の表から 750 $\mu$ S (代表値) を使用することもできます)。

f<sub>C</sub> = 1.32kHz を選択し、f<sub>zEA</sub> を 440Hz (f<sub>C</sub> の 3 分の 1) に設定すると、結果は式 17 のようになります。

式 17

$$C_C = \frac{1}{2\pi \times R_C \times f_{zEA}} = 26\text{nF}$$

$C_F$  は、高周波数の極の位置を決定します。高周波数の極の位置は降圧モードの帯域幅より高くしてください。それにより、位相マージンに影響を与えないと共に、あらゆる高周波数ノイズの減衰を可能にします。 $f_{pEA}$  は通常、100kHz に設定すれば十分です。

式 17

$$C_F = \frac{1}{2\pi \times R_C \times f_{pEA}} = 114\text{pF}$$

このアプリケーションでは、エラー・アンプの補償には  $R_C = 15\text{k}\Omega$ 、 $C_C = 22\text{nF}$ 、 $C_F = 100\text{pF}$ （最も近い標準値で概算）を選択します。

### PCB レイアウト時のガイドライン

低スイッ칭損失とノイズのない安定した動作を実現するには、慎重な PCB レイアウトが欠かせません。ノイズ耐性と消費電力の改善には可能な限り多層基板を使用します。優れた PCB レイアウトを作成するには次のガイドラインに従ってください。

1. デバイスのパッケージ下面には連続的な広い銅箔プレーンを使用します。すべての放熱部品には、十分な冷却性能を持ったものを使用してください。効率的に放熱し、デバイスのフル・パワーを得られるよう、デバイス底面のパッドはこの銅箔プレーンにハンダ付けしてください。このプレーンに複数のビア、または 1 つの大きなビアを使用することで放熱してください。

2. 電源部品と大電流経路はノイズに敏感なアナログ回路から絶縁します。これは、アナログ信号にノイズをカッピングさせないために極めて重要です。

3. 大電流経路は、特にグランド端子では短くします。この方法は、安定したジッタのない動作に必須のものです。大電流経路は、入力コンデンサ、ハイサイド FET、インダクタ、出力コンデンサから構成され、できるだけ短くする必要があります。

4. 電源パターンと負荷の接続配線は短くします。この方法は、高い効率を得るために必須のものです。銅層の厚い（1 オンスよりは 2 オンス）PCB を使用することで、全負荷時の効率を改善できます。

5. アナログ信号ラインは、高周波数プレーンから離して配線してください。これにより、デバイスにフィードバックされる敏感な信号の完全性を確保します。

6. アナログ部分と電源部分のグランド接続はデバイスの近くで行ってください。これにより、グランドの電流ループを最小限に抑えます。グランドを 1 つしか使用しない場合、アナログ・リターン信号と高電力信号の間の絶縁を十分に保ってください。

## 型番

| PART           | PIN-PACKAGE   | V <sub>OUT</sub><br>(ADJUSTABLE) | f <sub>SW</sub>        | V <sub>IN</sub><br>(V) | V <sub>OUT</sub><br>(DEFAULT) | CURRENT<br>(A) | I <sub>LIM</sub> (A)<br>(min) | MODE            |

|----------------|---------------|----------------------------------|------------------------|------------------------|-------------------------------|----------------|-------------------------------|-----------------|

| MAX26039ATPAY+ | 20 SWTQFN-EP* | 4 to 12                          | 200kHz<br>to<br>2.2MHz | 2 to 36                | 5                             | 0.6            | 0.9                           | SKIP or<br>FPWM |

| MAX26040ATPAY+ | 20 SWTQFN-EP* | 4 to 12                          | 200kHz<br>to<br>2.2MHz | 2 to 36                | 5                             | 1.2            | 1.9                           | SKIP or<br>FPWM |

注：全てのデバイスは-40°C～+125°Cの温度範囲で動作します。

\*は鉛 (Pb) フリー／RoHS 準拠のパッケージであることを示します。

SW = 側面濡れ性パッケージ。

\*EP = 露出パッド。

## 改訂履歴

| 版数 | 改訂日   | 説明   | 改訂ページ |

|----|-------|------|-------|

| 0  | 10/24 | 初版発行 | -     |