MAX22516

## トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

### 概要

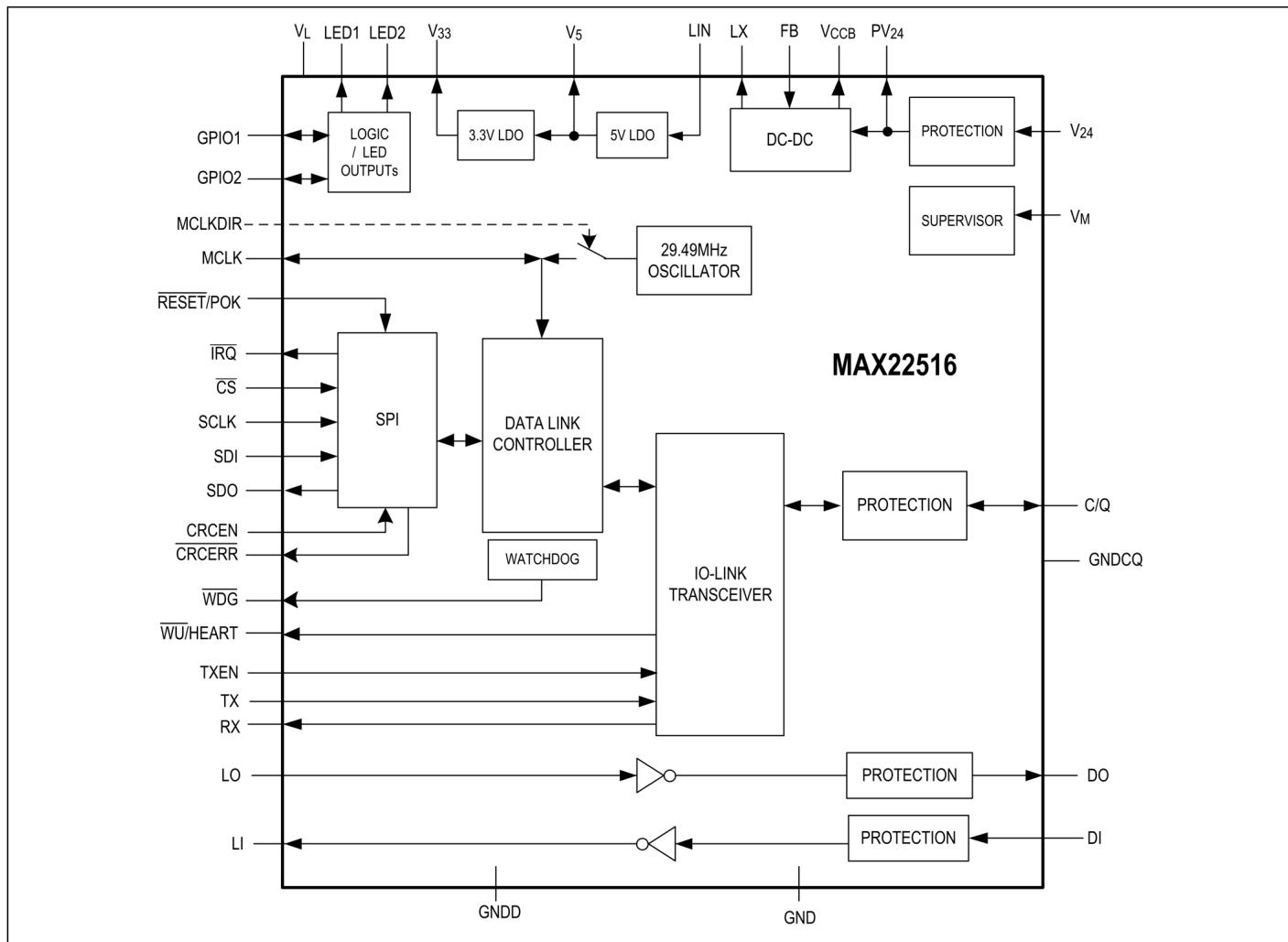

MAX22516 IO-Link データ・リンク・コントローラには、24V C/Q トランシーバー、補助デジタル入出力、内蔵リニア・レギュレータ (DC/DC、5V、3.3V)、フル機能の IO-Link データ・リンク・コントローラが統合されています。

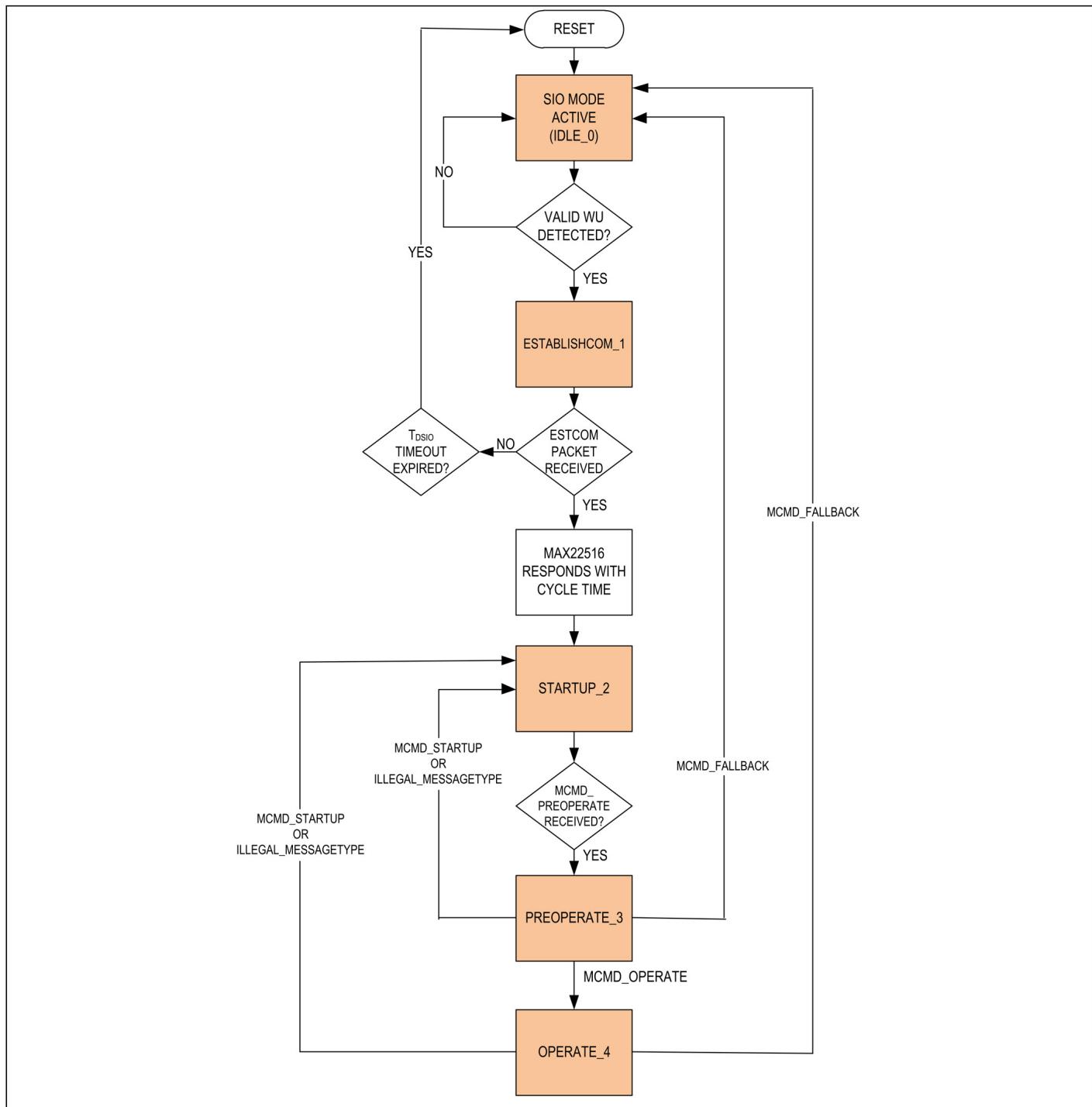

設定された状態では、MAX22516 データ・リンク・コントローラが IO-Link トランシーバーを動作させ、通常動作中は外部のマイクロコントローラからの介入を必要としません。また、IO-Link トランシーバーは、UART インターフェース (TXEN, TX, RX) による直接制御や、シリアル・ペリフェラル・インターフェース (SPI) を介した制御も可能です。データ・リンク・コントローラには、IO-Link 通信用の送受信バッファが組み込まれています。最大サイズのプロセス・データ、ISDU イベント、ページ・データ用のバッファを備えているため、時間の制約があるマイクロコントローラの介入の必要がなく、マイクロコントローラはアプリケーション・レイヤのタスクに集中できます。

MAX22516 は豊富な組み込み保護機能を備えており、過酷な産業環境でロバストな通信が確保されます。IO-Link インターフェースの端子 ( $V_{24}$ 、C/Q、DO、DI、GND) は全て、逆電圧保護、短絡保護、組み込みの $\pm 1kV/500\Omega$  サージ保護の機能を備えています。

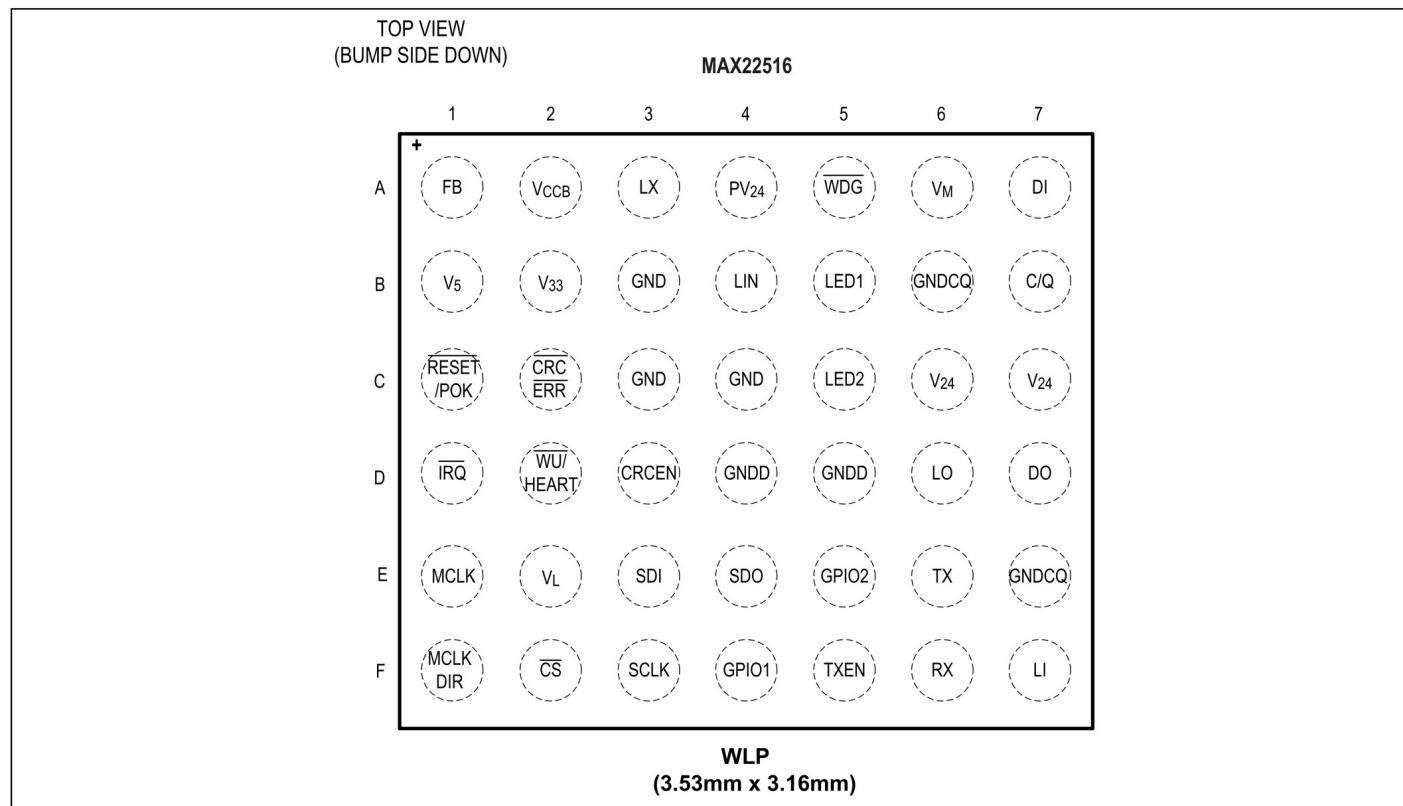

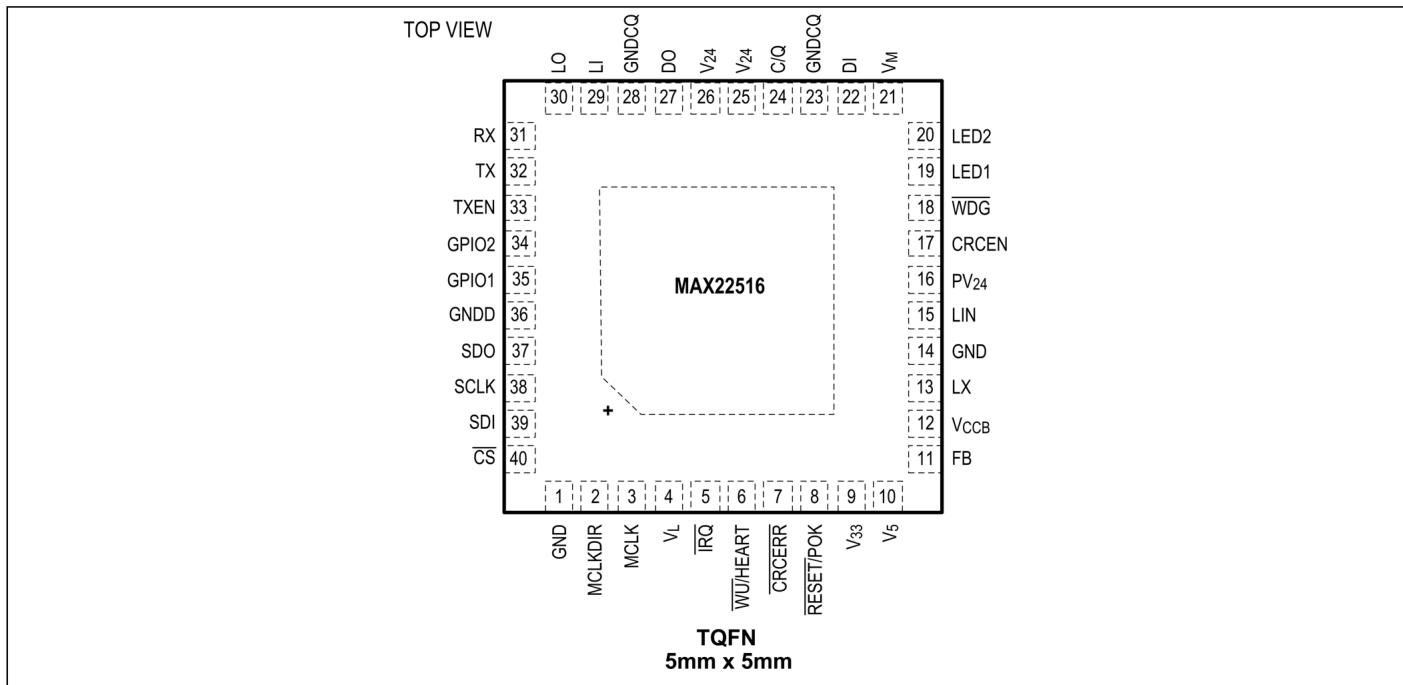

MAX22516 は小型の WLP パッケージ (3.53mm × 3.16mm) または 40 ピン TQFN-EP パッケージ (5mm × 5mm) で提供され、-40°C～+125°C の周囲温度範囲で動作します。

### 主なアプリケーション

- IO-Link のセンサーおよびアクチュエータ・デバイス

- 工業用センサー

### 利点および特長

- IO-Link 通信を容易に改善可能

- COM3 : 400μs (最小値) のサイクル時間をサポート

- データ・リンク・コントローラが自律的に全てのマスター・メッセージの要求に応答

- 確定的なデバイス応答遅延

- 高集積化ソリューション

- 以下を含むフル機能のデータ・リンク・レイヤ

- メッセージ・ハンドラ

- ISDU ハンドラ

- ページ・ハンドラ

- イベント・ハンドラ

- モード・ハンドラ

- スタートアップ・ハンドラ

- バースト・モード動作が可能な 15MHz SPI

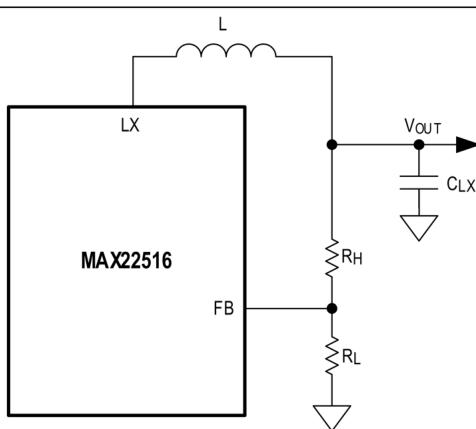

- 高効率 200mA DC/DC (出力調整可)

- 3.3V と 5V の高精度リニア・レギュレータ

- 柔軟なアプリケーション

- トランスペアレントなモード・オプション (TX、RX、TXEN)

- LED ドライバ (シーケンスのプログラムが可能)

- COM1、COM2、COM3 のデータレート

- ロバストで信頼性が高いデザイン

- $\pm 1kV/500\Omega$  のサージ保護機能内蔵

- 小型センサー設計に合わせて最適化

- 小型の WLP (3.53mm × 3.16mm) および 40 ピン TQFN-EP (5mm × 5mm) パッケージを採用

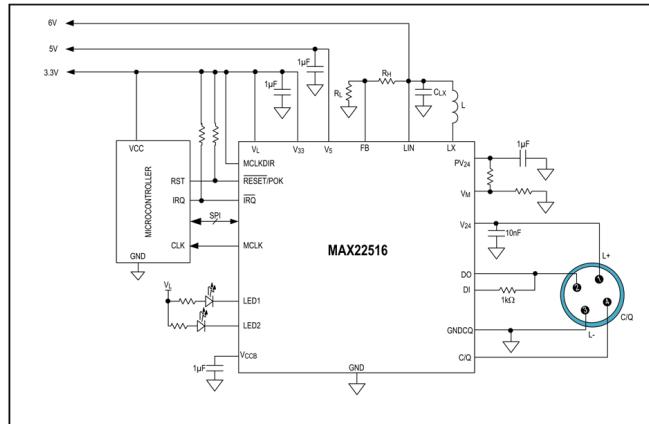

### 簡略アプリケーション回路図

型番はデータシート末尾に記載されています。

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

©2024 Analog Devices, Inc. All rights reserved. 商標および登録商標は各社の所有に属します。

本社／〒105-7323 東京都港区東新橋 1-9-1 東京汐留ビルディング 23F

大阪営業所／〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F

19-101758; Rev 2; 3/24

## 絶対最大定格

特に指定のない限り、全ての電圧は GND 基準です。

### 電源

|                                                                     |                                                                      |

|---------------------------------------------------------------------|----------------------------------------------------------------------|

| V <sub>24</sub> (連続)                                                | -36V～+36V                                                            |

| V <sub>24</sub> (ピーク、100μs)                                         | -52V～+65V                                                            |

| PV <sub>24</sub> (連続)                                               | -0.3V～+36V                                                           |

| PV <sub>24</sub> (ピーク、100μs)                                        | MAX(-0.3V、V <sub>24</sub> - 52V)～<br>MIN(+52V、V <sub>24</sub> + 52V) |

| V <sub>5</sub> 、V <sub>L</sub> 、V <sub>M</sub> 、FB、V <sub>CCB</sub> | -0.3V～+6V                                                            |

| V <sub>33</sub>                                                     | -0.3V～(V <sub>5</sub> + 0.3V)                                        |

| LX                                                                  | -0.3V～(PV <sub>24</sub> + 0.3V)                                      |

| LIN (連続)                                                            | MAX(-0.3V、V <sub>5</sub> - 0.3V)～+36V                                |

| LIN (ピーク、100μs)                                                     | MAX(-0.3V、V <sub>5</sub> - 0.3V)～+52V                                |

| 24V I/O                                                             |                                                                      |

| C/Q、DO (連続)                                                         | MAX(-36V、V <sub>24</sub> - 36V)～<br>MIN(+36V、V <sub>24</sub> + 36V)  |

| C/Q、DO (ピーク、100μs)                                                  | MAX(-52V、V <sub>24</sub> - 60V)～<br>MIN(+52V、V <sub>24</sub> + 60V)  |

| CQGND                                                               | -0.3V～+0.3V                                                          |

| DI (連続)                                                             | -36V～+36V                                                            |

| DI (ピーク、100μs)                                                      | -52V～+52V                                                            |

| ロジック入力                                                              |                                                                      |

| CS、SCLK、SDI、TX、TXEN、LO、CRCEN、<br>MCLKDIR                            | -0.3V～(V <sub>L</sub> + 0.3V)                                        |

### ロジック出力

|                                                 |                               |

|-------------------------------------------------|-------------------------------|

| SDO、RX、MCLK、LI                                  | -0.3V～(V <sub>L</sub> + 0.3V) |

| IRQ、WU/HEART、LED1、LED2、CRCERR、WDG、<br>RESET/POK | -0.3V～+ 6V                    |

| GPIO1、GPIO2                                     | -0.3V～(V <sub>L</sub> + 0.3V) |

### 電流

|                                      |        |

|--------------------------------------|--------|

| V <sub>24</sub> 、LX、GND、GNDCQ への連続電流 | ±1A    |

| PV <sub>24</sub> への連続電流              | ±200mA |

| PV <sub>24</sub> へのピーク電流 (100μs)     | ±1A    |

| C/Q への連続電流                           | ±500mA |

| その他全てのピンへの連続電流                       | ±50mA  |

### 連続消費電力

|                                                                          |        |

|--------------------------------------------------------------------------|--------|

| 40 ピン TQFN-EP (T <sub>A</sub> = +70°C、+70°C を超えると 28mW/°C で<br>ディレーティング) | 2857mW |

| 42 パンプ WLP (T <sub>A</sub> = +70°C、+70°C を超えると 27.5mW/°C で<br>ディレーティング)  | 1510mW |

### 温度

|                      |              |

|----------------------|--------------|

| 動作温度範囲               | -40°C～+125°C |

| 最大ジャンクション範囲          | +150°C       |

| 保存温度範囲               | -40°C～+150°C |

| はんだ付け温度 (リフロー)       |              |

| (TQFN のみ、はんだ処理 10 秒) | +300°C       |

| パンプ・リフロー温度           | +260°C       |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## パッケージ情報

### 40 TQFN-EP

|                                                       |                         |

|-------------------------------------------------------|-------------------------|

| Package Code                                          | T4055+1C                |

| Outline Number                                        | <a href="#">21-0140</a> |

| Land Pattern Number                                   | <a href="#">90-0016</a> |

| <b>Thermal Resistance, Single Layer Board:</b>        |                         |

| Junction-to-Ambient ( $\theta_{JA}$ )                 | 45°C/W                  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 2°C/W                   |

| <b>Thermal Resistance, Four Layer Board:</b>          |                         |

| Junction-to-Ambient ( $\theta_{JA}$ )                 | 28°C/W                  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 2°C/W                   |

### 42 WLP

|                                              |                                                                                      |

|----------------------------------------------|--------------------------------------------------------------------------------------|

| Package Code                                 | W423H3+1                                                                             |

| Outline Number                               | <a href="#">21-100631</a>                                                            |

| Land Pattern Number                          | Refer to the Application Note 1891: Wafer-Level Packaging (WLP) and Its Applications |

| <b>Thermal Resistance, Four Layer Board:</b> |                                                                                      |

| Junction-to-Ambient ( $\theta_{JA}$ )        | 36.38°C/W                                                                            |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、[www.maximintegrated.com/packages](http://www.maximintegrated.com/packages) で確認してください。パッケージ・コードの「+」、「#」、「-」はRoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面はRoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、[www.maximintegrated.com/thermal-tutorial](http://www.maximintegrated.com/thermal-tutorial) を参照してください。

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

## 電気的特性

(特に指定のない限り、 $V_{24} = 7V \sim 36V$ 、 $V_5 = 4.85V \sim 5.5V$ 、 $V_L = 2.5V \sim 5.5V$ 、 $V_{GNDQ} = V_{GND} = 0V$ 、全ロジック入力は  $V_L$  または  $GND$ 、代表値は  $V_{24} = 24V$ 、 $V_5 = 5V$ 、 $V_L = 3.3V$ 、 $T_A = +25^\circ C$  における値 (Note 1) )

| PARAMETER                                          | SYMBOL                | CONDITIONS                                                                                                            |                                               | MIN    | TYP   | MAX    | UNITS   |  |  |

|----------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------|-------|--------|---------|--|--|

| <b>DC CHARACTERISTICS</b>                          |                       |                                                                                                                       |                                               |        |       |        |         |  |  |

| <b>POWER SUPPLY</b>                                |                       |                                                                                                                       |                                               |        |       |        |         |  |  |

| $V_{24}$ Supply Voltage                            | $V_{24}$              |                                                                                                                       |                                               | 8      |       | 36     | V       |  |  |

| $V_{24}$ Undervoltage Lockout Threshold            | $V_{24UVLO}$          | $V_{24}$ rising                                                                                                       |                                               | 7      | 7.5   | 8      | V       |  |  |

|                                                    |                       | $V_{24}$ falling                                                                                                      |                                               | 6.3    | 6.9   | 7.5    |         |  |  |

| $V_{24}$ Undervoltage Lockout Threshold Hysteresis | $V_{24UVLO\_HYS}$     |                                                                                                                       |                                               | 530    |       |        | mV      |  |  |

| $V_{24}$ Supply Current                            | $I_{24}$              | No load on C/Q, DO, $V_5$ powered externally, DC-DC disabled, MCLK disabled                                           | C/Q, DO disabled, $V_{33}$ enabled            | 0.01   | 0.05  | 0.10   | mA      |  |  |

|                                                    |                       |                                                                                                                       |                                               | 0.42   | 0.6   | 0.75   |         |  |  |

|                                                    |                       | $V_5$ powered externally, DC-DC enabled, MCLK enabled                                                                 | C/Q, DO in push-pull and is high or low       | 0.60   | 0.75  | 0.95   |         |  |  |

| $V_5$ Supply Voltage                               | $V_5$                 | $V_5$ supplied externally                                                                                             |                                               | 4.85   |       | 5.5    | V       |  |  |

| $V_5$ Undervoltage Lockout Threshold               | $V_{5UVLO}$           | $V_5$ rising                                                                                                          |                                               | 3.15   | 3.27  | 3.40   | V       |  |  |

|                                                    |                       | $V_5$ falling                                                                                                         |                                               | 3.10   | 3.22  | 3.35   |         |  |  |

| $V_5$ Supply Current                               | $I_5$                 | V <sub>5</sub> powered externally, DC-DC disabled, MCLK disabled, $V_{33}$ enabled, no load on $V_{33}$               | C/Q, DO disabled                              | 1.5    | 2.4   | 3.0    | mA      |  |  |

|                                                    |                       |                                                                                                                       | C/Q, DO in push-pull mode, no load on C/Q, DO | 2.1    | 3     | 3.7    |         |  |  |

|                                                    |                       | $V_5$ powered externally, DC-DC enabled, MCLK enabled and set to 29.48MHz, C/Q in push-pull and is high or low        |                                               | 2.9    | 4     | 5      |         |  |  |

| $V_L$ Logic Level Supply Voltage                   | $V_L$                 |                                                                                                                       |                                               | 2.5    |       | 5.5    | V       |  |  |

| $V_L$ Undervoltage Threshold                       | $V_{LUVLO}$           | $V_L$ rising                                                                                                          |                                               |        | 1.35  |        | V       |  |  |

|                                                    |                       | $V_L$ falling                                                                                                         |                                               |        | 0.45  |        |         |  |  |

| $V_L$ Logic Level Supply Current                   | $I_L$                 | All logic inputs at GND or $V_L$ , no load on any logic outputs, MCLK disabled                                        |                                               | 10     |       |        | $\mu A$ |  |  |

| <b>DC-DC SWITCHING REGULATOR</b>                   |                       |                                                                                                                       |                                               |        |       |        |         |  |  |

| Input Voltage Range                                | $V_{24\_DC}$          | $V_{24}$ is the input to the DC-DC                                                                                    |                                               | 7      |       | 36     | V       |  |  |

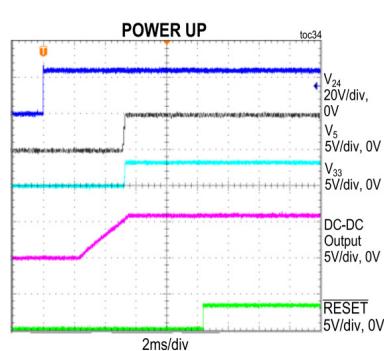

| DC-DC Turn-on Delay                                | $t_{DC\_ON}$          | Delay from $V_{24}$ crossing $V_{24UVLO}$ threshold until the DC-DC regulator finishes soft-start and RESET/POK rises |                                               | 2.22   |       |        | ms      |  |  |

| Switching Frequency                                | $f_{DC\_H}$           | BuckSS = 0                                                                                                            |                                               | 1.140  | 1.229 | 1.330  | MHz     |  |  |

|                                                    | $f_{DC\_HSPRD}$       | BuckSS = 1                                                                                                            |                                               | 1.229  |       |        |         |  |  |

| Spread Spectrum                                    | $\Delta f_{DC\_SPRD}$ | BuckSS = 1                                                                                                            |                                               | -11.5  |       | +13.5  | %       |  |  |

| Feedback (FB) Regulation Voltage                   | $V_{DC\_FB}$          |                                                                                                                       |                                               | 0.8865 | 0.9   | 0.9135 | V       |  |  |

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

(特に指定のない限り、 $V_{24} = 7V \sim 36V$ 、 $V_5 = 4.85V \sim 5.5V$ 、 $V_L = 2.5V \sim 5.5V$ 、 $V_{GNDQ} = V_{GND} = 0V$ 、全ロジック入力は  $V_L$  または  $GND$ 、代表値は  $V_{24} = 24V$ 、 $V_5 = 5V$ 、 $V_L = 3.3V$ 、 $T_A = +25^\circ C$  における値 (Note 1) )

| PARAMETER                                                           | SYMBOL              | CONDITIONS                                                 | MIN  | TYP  | MAX  | UNITS           |

|---------------------------------------------------------------------|---------------------|------------------------------------------------------------|------|------|------|-----------------|

| Output Voltage Accuracy                                             | $ACC_{DCFB}$        |                                                            | -1.5 | 0    | +1.5 | %               |

| Feedback (FB) OK Threshold                                          | $V_{DC\_FBOK}$      |                                                            | 92   | 95   | 98   | $\%V_{DC\_F_B}$ |

| Feedback (FB) Low Threshold                                         | $V_{DC\_FBTHLO_W}$  |                                                            | 61   | 65   | 70   | $\%V_{DC\_F_B}$ |

| LX On-Resistance (High Side)                                        | $R_{DC\_HS}$        | From $V_{24}$ to LX, LX is sinking current (Note 2)        |      | 2.2  | 3.9  | $\Omega$        |

| LX On-Resistance (Low Side)                                         | $R_{DC\_LS}$        | From LX to GND (Note 2)                                    |      | 1.3  | 2.8  | $\Omega$        |

| Active Diode On-Resistance                                          | $R_{DC\_ACT}$       | DC current (Note 2)                                        |      | 3.0  | 5.5  | $\Omega$        |

| Maximum Peak Current into Active Diode                              | $I_{DC\_ACTMAX}$    |                                                            | 300  |      |      | mA              |

| Maximum LX Current Ripple                                           | $\Delta I_{DC\_LX}$ |                                                            |      | 100  |      | %               |

| High-Side Peak Current Limit                                        | $I_{DC\_HSLIM}$     |                                                            | +350 | +390 | +440 | mA              |

| Low-Side Current Limit                                              | $I_{DC\_LSMAX}$     |                                                            | -240 | -190 | -150 | mA              |

| DC-DC Autoretry Period                                              | $t_{DCRETRY}$       |                                                            |      | 22   |      | ms              |

| External Capacitance on $PV_{24}$                                   | $C_{DC\_PV24}$      |                                                            |      | 1    |      | $\mu F$         |

| LX Leakage Current                                                  | $I_{LX\_LKG}$       | $0V < V_{LX} < 36V$                                        | -1   |      | +1   | $\mu A$         |

| FB Input Bias Current                                               | $I_{FB\_LKG}$       | $0 \leq V_{FB} \leq 1V$ , $T_A = 25^\circ C$               | -100 |      | +100 | nA              |

| FB Threshold for POK Assertion                                      | $V_{FBOK\_F}$       | $V_{FB}$ falling                                           | 89   | 92   | 95   | $\%V_{FB}$      |

|                                                                     |                     | $V_{FB}$ rising                                            | 92   | 95   | 98   |                 |

| FB Undervoltage Trip Threshold                                      | $V_{FB\_LOW}$       |                                                            | 61   | 64.5 | 70   | $\%V_{FB}$      |

| LX Minimum On-Time                                                  | $t_{LX\_MINON}$     | (Note 2)                                                   |      | 64   | 92   | ns              |

| LX Minimum Off-Time                                                 | $t_{LX\_MINOFF}$    | (Note 2)                                                   |      | 32   | 60   | ns              |

| <b><math>V_{CCB}</math> LINEAR REGULATOR (<math>V_{CCB}</math>)</b> |                     |                                                            |      |      |      |                 |

| $V_{CCB}$ Output Voltage                                            | $V_{CCB}$           | $8V \leq V_{PV24} \leq 36V$ , $0mA \leq I_{LOAD} \leq 5mA$ | 4.85 | 5    | 5.15 | V               |

| $V_{CCB}$ Current Limit                                             | $I_{CCB\_MAX}$      | $V_{PV24} = 8V$                                            | 10   |      |      | mA              |

| <b>5V LINEAR REGULATOR (<math>V_5</math>)</b>                       |                     |                                                            |      |      |      |                 |

| $V_5$ Input Supply Voltage                                          | $V_{LIN}$           |                                                            | 6    |      | 36   | V               |

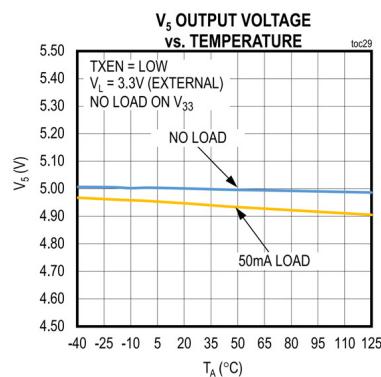

| $V_5$ Output Voltage                                                | $V_5$               | $6V \leq V_{LIN} \leq 36V$ , no load on $V_5$              | 4.85 | 5    | 5.15 | V               |

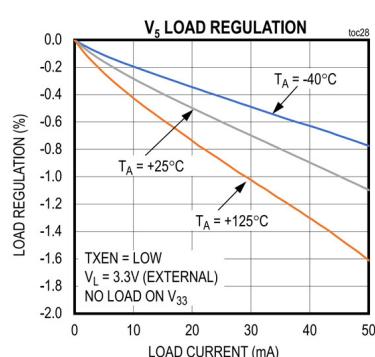

| $V_5$ Load Regulation                                               | $\Delta V_{5LDR}$   | $V_{LIN} = 24V$ , $1mA \leq I_{LOAD} \leq 50mA$            |      | 0.6  | 2.0  | %               |

| $V_5$ Line Regulation                                               | $\Delta V_{5LNR}$   | $6V \leq V_{LIN} \leq 36V$ , $I_{LOAD} = 1mA$              |      | 0.05 | 0.2  | mV/V            |

| $V_5$ Load Capacitance                                              | $C_{V5}$            | External capacitance on $V_5$                              |      | 1    |      | $\mu F$         |

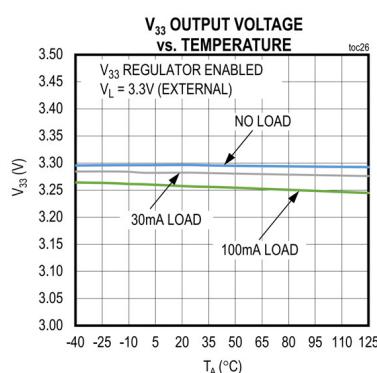

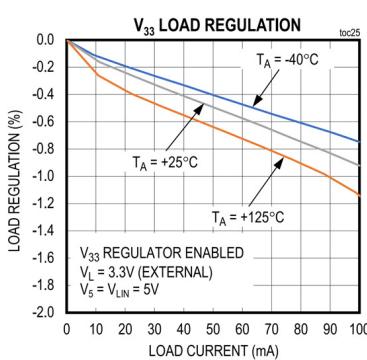

| <b>3.3V LINEAR REGULATOR (<math>V_{33}</math>)</b>                  |                     |                                                            |      |      |      |                 |

| $V_{33}$ Output Voltage                                             | $V_{33}$            | No load                                                    | 3.15 | 3.3  | 3.45 | V               |

| $V_{33}$ Load Regulation                                            | $\Delta V_{33\_LR}$ | $1mA \leq I_{LOAD} \leq 100mA$                             |      | 0    | 0.9  | 3               |

| $V_{33}$ Load Capacitance                                           | $C_{V33}$           | External capacitance on $V_{33}$                           |      | 1    |      | $\mu F$         |

| <b>C/Q, DO DRIVERS</b>                                              |                     |                                                            |      |      |      |                 |

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

(特に指定のない限り、 $V_{24} = 7V \sim 36V$ 、 $V_5 = 4.85V \sim 5.5V$ 、 $V_L = 2.5V \sim 5.5V$ 、 $V_{GNDQ} = V_{GND} = 0V$ 、全ロジック入力は  $V_L$  または  $GND$ 、代表値は  $V_{24} = 24V$ 、 $V_5 = 5V$ 、 $V_L = 3.3V$ 、 $T_A = +25^\circ C$  における値 (Note 1) )

| PARAMETER                              | SYMBOL         | CONDITIONS                                                                                                                                    | MIN                                 | TYP            | MAX  | UNITS      |         |

|----------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------|------|------------|---------|

| C/Q, DO Driver High-Side On-Resistance | $R_{CQOH}$     | High-side enabled, $CQ\_CL[1:0]$ or $DO\_CL[1:0] = 01$ , $I_{LOAD} = +150mA$ (Note 2)                                                         |                                     | 2.4            | 4.4  | $\Omega$   |         |

| C/Q, DO Driver Low-Side On-Resistance  | $R_{CQLO}$     | Low-side enabled, $CQ\_CL[1:0]$ or $DO\_CL[1:0] = 01$ , $I_{LOAD} = -150mA$ (Note 2)                                                          |                                     | 2.0            | 4.0  | $\Omega$   |         |

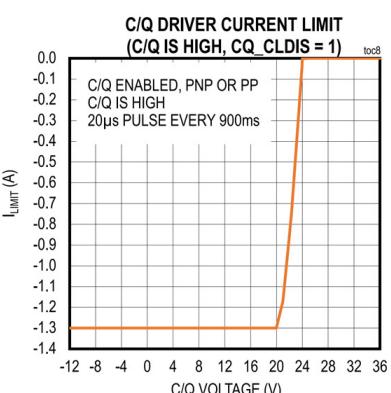

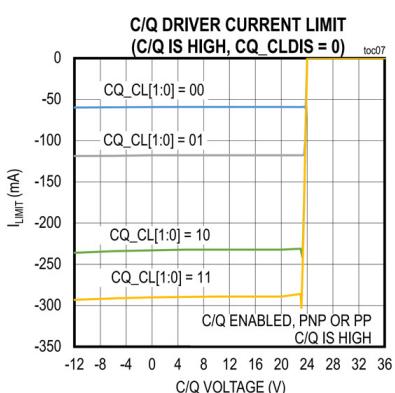

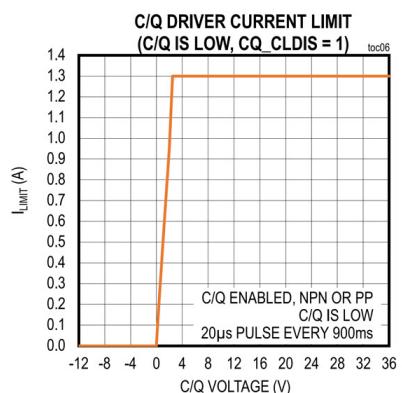

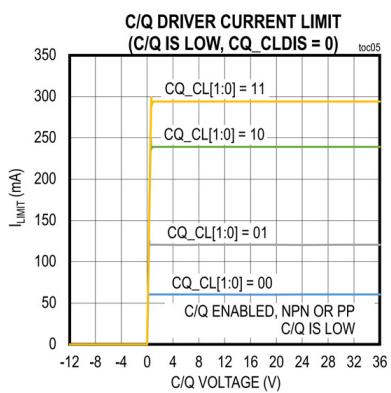

| C/Q, DO Driver Current Limit           | $I_{CL}$       | $V_{DROP} = 3V$ (Note 3)                                                                                                                      | $CQ\_CL[1:0]$ or $DO\_CL[1:0] = 00$ | 50             | 60   | 70         |         |

|                                        |                |                                                                                                                                               | $CQ\_CL[1:0]$ or $DO\_CL[1:0] = 01$ | 100            | 120  | 140        |         |

|                                        |                |                                                                                                                                               | $CQ\_CL[1:0]$ or $DO\_CL[1:0] = 10$ | 200            | 230  | 260        |         |

|                                        |                |                                                                                                                                               | $CQ\_CL[1:0]$ or $DO\_CL[1:0] = 11$ | 250            | 289  | 330        |         |

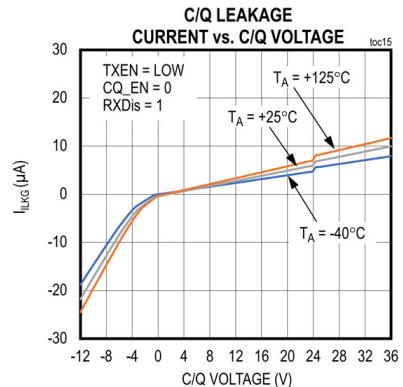

| C/Q Leakage Current                    | $I_{LEAK\_CQ}$ | $V_{24} = 24V$ , ( $V_{24} - 36V$ ) $\leq V_{C/Q, DO} \leq 36V$ , Driver disabled, C/Q receiver disabled                                      | C/Q driver                          | -32            | +40  | $\mu A$    |         |

| DO Leakage Current                     | $I_{LEAK\_DO}$ | $V_{24} = 24V$ , ( $V_{24} - 36V$ ) $\leq V_{DO} \leq 36V$ , Driver disabled                                                                  | DO driver                           | -22            | +4   | $\mu A$    |         |

| C/Q, DO Output Reverse Current         | $I_{REV\_CQ}$  | Driver enabled and in push-pull, $V_{C/Q, DO} = (V_{24} + 5V)$ or $(V_{GND} - 5V)$                                                            |                                     | -90            | +375 | $\mu A$    |         |

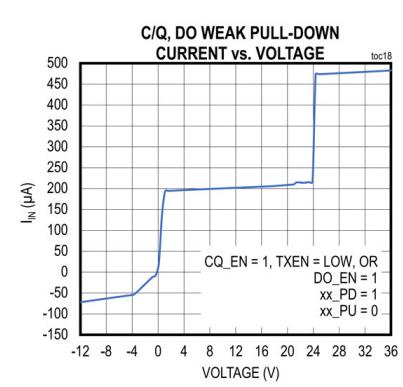

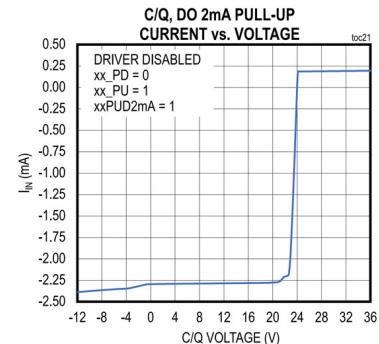

| C/Q, DO Weak Pull-Down Current         | $I_{CQPD}$     | Driver disabled, $V_{C/Q, DO} > 5V$ , $CQ\_PD = 1$ or $DO\_PD = 1$ , $CQ\_PU = 0$ or $DO\_PU = 0$ , $CQPu2mA = 0$ or $DOPu2mA = 0$            |                                     | -220           | -193 | -160       | $\mu A$ |

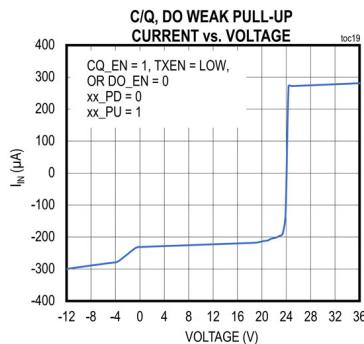

| C/Q, DO Weak Pull-Up Current           | $I_{CQPU}$     | Driver disabled, $V_{C/Q, DO} = (V_{24} - 5V)$ , $CQ\_PD = 0$ or $DO\_PD = 0$ , $CQ\_PU = 1$ or $DO\_PD = 1$ , $CQPu2mA = 0$ or $DOPu2mA = 0$ |                                     | +160           | +200 | +260       | $\mu A$ |

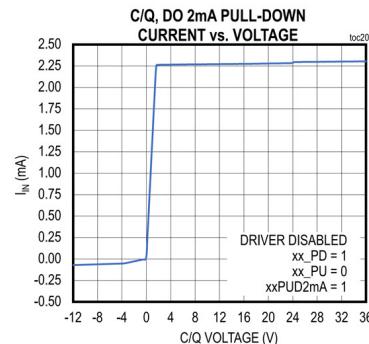

| C/Q, DO 2mA Pull-Down Current          | $I_{CQPD2}$    | Driver disabled, $V_{C/Q, DO} > 5V$ , $CQ\_PD = 1$ or $DO\_PD = 1$ , $CQ\_PU = 0$ or $DO\_PU = 0$ , $CQPu2mA = 1$ or $DOPu2mA = 1$            |                                     | -2.5           | -2.2 | -2.0       | $mA$    |

| C/Q, DO 2mA Pull-Up Current            | $I_{CQPU2}$    | Driver disabled, $V_{C/Q, DO} = (V_{24} - 5V)$ , $CQ\_PD = 0$ or $DO\_PD = 0$ , $CQ\_PU = 1$ or $DO\_PU = 1$ , $CQPu2mA = 1$ or $DOPu2mA = 1$ |                                     | 2.0            | 2.2  | 2.5        | $mA$    |

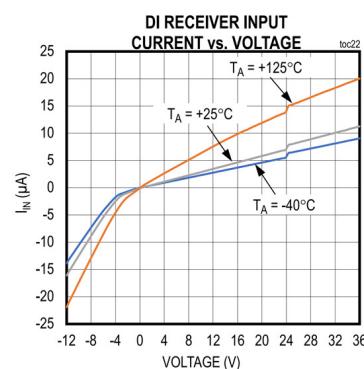

| <b>C/Q, DI RECEIVERS</b>               |                |                                                                                                                                               |                                     |                |      |            |         |

| Input Voltage Range                    | $V_{RIN}$      | For valid RX /LI logic                                                                                                                        |                                     | $V_{24} - 36V$ | 36   | $V$        |         |

| Input Threshold High                   | $V_{THR}$      | Receiver enabled                                                                                                                              | $V_{24} \geq 18V$                   | 11             | 12.5 | $V$        |         |

|                                        |                |                                                                                                                                               | $V_{24} < 18V$                      | 54             | 80   | $\%V_{24}$ |         |

| Input Threshold Low                    | $V_{TLR}$      | Receiver enabled                                                                                                                              | $V_{24} \geq 18V$                   | 9              | 10.5 | $V$        |         |

|                                        |                |                                                                                                                                               | $V_{24} < 18V$                      | 45             | 68.1 | $\%V_{24}$ |         |

| Input Hysteresis                       | $V_{HYSR}$     | Receiver enabled                                                                                                                              | $V_{24} \geq 18V$                   | 2              |      | $V$        |         |

|                                        |                |                                                                                                                                               | $V_{24} < 18V$                      | 11             |      | $\%V_{24}$ |         |

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

(特に指定のない限り、 $V_{24} = 7V \sim 36V$ 、 $V_5 = 4.85V \sim 5.5V$ 、 $V_L = 2.5V \sim 5.5V$ 、 $V_{GNDQ} = V_{GND} = 0V$ 、全ロジック入力は  $V_L$  または  $GND$ 、代表値は  $V_{24} = 24V$ 、 $V_5 = 5V$ 、 $V_L = 3.3V$ 、 $T_A = +25^\circ C$  における値 (Note 1) )

| PARAMETER                                                                                                     | SYMBOL         | CONDITIONS                                         | MIN               | TYP           | MAX               | UNITS      |

|---------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------|-------------------|---------------|-------------------|------------|

| C/Q Input Threshold High (TTL Mode)                                                                           | $V_{TH\_TTL}$  | C/Q driver disabled, RX TTL = 1                    | 2.10              |               | 3.45              | V          |

| C/Q Input Threshold Low (TTL Mode)                                                                            | $V_{TL\_TTL}$  | C/Q driver disabled, RX TTL = 1                    | 1.1               |               | 1.8               | V          |

| Input Hysteresis (TTL Mode)                                                                                   | $V_{HYSTTL}$   | Driver disabled, RX TTL = 1                        |                   | 1.38          |                   | V          |

| C/Q Receiver Input Capacitance                                                                                | $C_{IN\_CQ}$   | Driver disabled, CQ_PD = 0, CQ_PU = 0, f = 100kHz  |                   | 35            |                   | pF         |

| DI Receiver Input Capacitance                                                                                 | $C_{IN\_DI}$   |                                                    |                   | 2             |                   | pF         |

| <b>VOLTAGE MONITOR INPUT</b>                                                                                  |                |                                                    |                   |               |                   |            |

| $V_M$ Voltage Range                                                                                           | $V_M$          |                                                    | 0                 |               | 5.5               | V          |

| $V_M$ Threshold Voltage                                                                                       | $V_{M\_R}$     | Rising                                             | 0.87              | 0.9           | 0.93              | V          |

|                                                                                                               | $V_{M\_F}$     | Falling                                            | 0.83              | 0.86          | 0.89              |            |

| $V_M$ Threshold Hysteresis                                                                                    | $V_{M\_HYS}$   |                                                    |                   | 0.04          |                   | V          |

| $V_M$ Input Current                                                                                           | $I_M$          |                                                    | -1                |               | +1                | $\mu A$    |

| <b>RESET/POWER OK (RESET/POK)</b>                                                                             |                |                                                    |                   |               |                   |            |

| RESET/POK Input Voltage Low                                                                                   | $V_{RSTIL}$    |                                                    | 0.4               |               |                   | V          |

| RESET/POK Input Voltage High                                                                                  | $V_{RSTIH}$    |                                                    |                   | 1.3           |                   | V          |

| RESET/POK Output Voltage Low                                                                                  | $V_{POKLOW}$   | $I_{LOAD} = -5mA$                                  |                   |               | +0.12             | V          |

| RESET/POK High Impedance Leakage Current                                                                      | $I_{RST\_OD}$  | RESET/POK not asserted                             | -1                |               | +1                | $\mu A$    |

| <b>LOGIC INPUTS (<math>\overline{CS}</math>, SCLK, SDI, TX, TXEN, LO, GPIO1, GPIO2, MCLK, MCLKDIR, CRCEN)</b> |                |                                                    |                   |               |                   |            |

| Logic Input Voltage Low Threshold                                                                             | $V_{IL}$       |                                                    |                   |               | $0.31 \times V_L$ | V          |

| Logic Input Voltage High Threshold                                                                            | $V_{IH}$       |                                                    |                   | 0.68 $\times$ | $V_L$             | V          |

| Logic Input Leakage Current                                                                                   | $I_{LEAK}$     | Logic input = GND or $V_L$                         | -1                |               | +1                | $\mu A$    |

| GPIO_Pull-Up Resistance                                                                                       | $R_{GPIO\_UP}$ |                                                    | 200               | 330           | 460               | k $\Omega$ |

| GPIO_Pull-Down Resistance                                                                                     | $R_{GPIO\_DN}$ |                                                    | 200               | 330           | 460               | k $\Omega$ |

| <b>LOGIC OUTPUTS (WU/HEART, IRQ, SDO, RX, LI, MCLK, GPIO1, GPIO2, LED1, LED2, CRCERR, WDG)</b>                |                |                                                    |                   |               |                   |            |

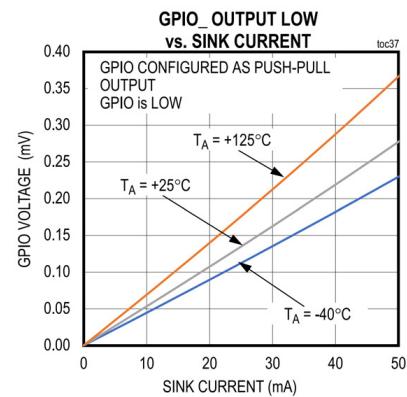

| Logic Output Voltage Low                                                                                      | $V_{OL}$       | $I_{LOAD} = -5mA$                                  |                   |               | 0.4               | V          |

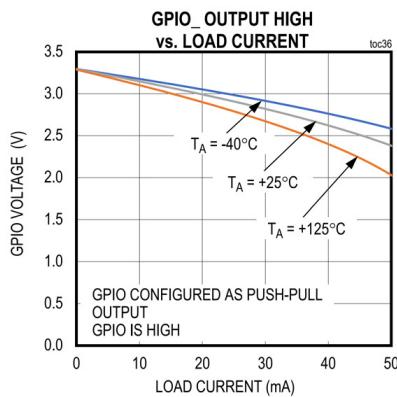

| Logic Output Voltage High                                                                                     | $V_{OH}$       | SDO, RX, LI, MCLK, GPIO1, GPIO2                    | $I_{LOAD} = +5mA$ | $V_L - 0.4$   |                   | V          |

| Open-Drain High Impedance Leakage Current                                                                     | $I_{LK\_OD}$   | IRQ, WU/HEART, CRCERR, LED1 and LED2, not asserted |                   | -1            | +1                | $\mu A$    |

| SDO Leakage Current                                                                                           | $I_{LK\_SDO}$  | $\overline{CS}$ = high                             |                   | -1            | +1                | $\mu A$    |

| RX Leakage Current                                                                                            | $I_{LK\_RX}$   | $RX = GND$ or $V_L$                                |                   | -1            | +1                | $\mu A$    |

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

(特に指定のない限り、 $V_{24} = 7V \sim 36V$ 、 $V_5 = 4.85V \sim 5.5V$ 、 $V_L = 2.5V \sim 5.5V$ 、 $V_{GNDQ} = V_{GND} = 0V$ 、全ロジック入力は  $V_L$  または  $GND$ 、代表値は  $V_{24} = 24V$ 、 $V_5 = 5V$ 、 $V_L = 3.3V$ 、 $T_A = +25^\circ C$  における値 (Note 1) )

| PARAMETER                                    | SYMBOL                  | CONDITIONS                                                                     | MIN                                             | TYP  | MAX  | UNITS |

|----------------------------------------------|-------------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|-------|

| <b>INTERNAL THERMAL SENSOR</b>               |                         |                                                                                |                                                 |      |      |       |

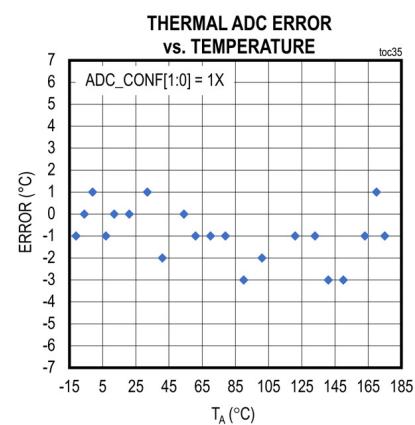

| Programmable Thermal Warning Threshold Range | $T_{WRN\_RNG}$          | Typical range                                                                  | -15                                             |      | +174 | °C    |

| Programmable Thermal Warning Threshold Step  | $T_{WRN\_LSB}$          | 1 LSB                                                                          |                                                 | 3    |      | °C    |

| Thermal ADC Resolution                       | $T_{WRN\_RES}$          |                                                                                |                                                 | 6    |      | bit   |

| Thermal ADC Accuracy                         | $\Delta T_{PREC\_25C}$  | $T_J = 25^\circ C$ (Note 2)                                                    | -8                                              | 0    | +8   | °C    |

|                                              | $\Delta T_{PREC\_125C}$ | $T_J = 125^\circ C$ (Note 2)                                                   | -7                                              | 3    | +12  |       |

| Thermal ADC Conversion Time                  | $t_{ADC\_CONV}$         |                                                                                |                                                 | 450  |      | μs    |

| <b>THERMAL PROTECTION</b>                    |                         |                                                                                |                                                 |      |      |       |

| C/Q, DO Driver Shutdown Temperature          | $T_{SHUT\_DRV}$         | Driver temperature rising, driver fault bit is set and driver is disabled      |                                                 | +165 |      | °C    |

| C/Q, DO Driver Shutdown Hysteresis           | $T_{SHUT\_DHYS}$        | Driver temperature falling, driver is automatically re-enabled, $TSHOFFEN = 0$ |                                                 | 9    |      | °C    |

| IC Thermal Warning Threshold                 | $T_{WRN}$               | Die temperature rising, ThW and ThWInt bits are set                            |                                                 | +135 |      | °C    |

| IC Thermal Warning Threshold Hysteresis      | $T_{WRN\_HYS}$          | Die temperature falling, ThW bit is cleared                                    |                                                 | 9    |      | °C    |

| IC Thermal Shutdown Threshold                | $T_{SHUT\_IC}$          | Die temperature rising, ThShd bit set                                          |                                                 | +175 |      | °C    |

| IC Thermal Shutdown Hysteresis               | $T_{SHUT\_ICHYS}$       | Die temperature falling, ThShd bit is cleared                                  |                                                 | 26   |      | °C    |

| <b>AC ELECTRICAL CHARACTERISTICS</b>         |                         |                                                                                |                                                 |      |      |       |

| <b>C/Q, DO DRIVERS</b>                       |                         |                                                                                |                                                 |      |      |       |

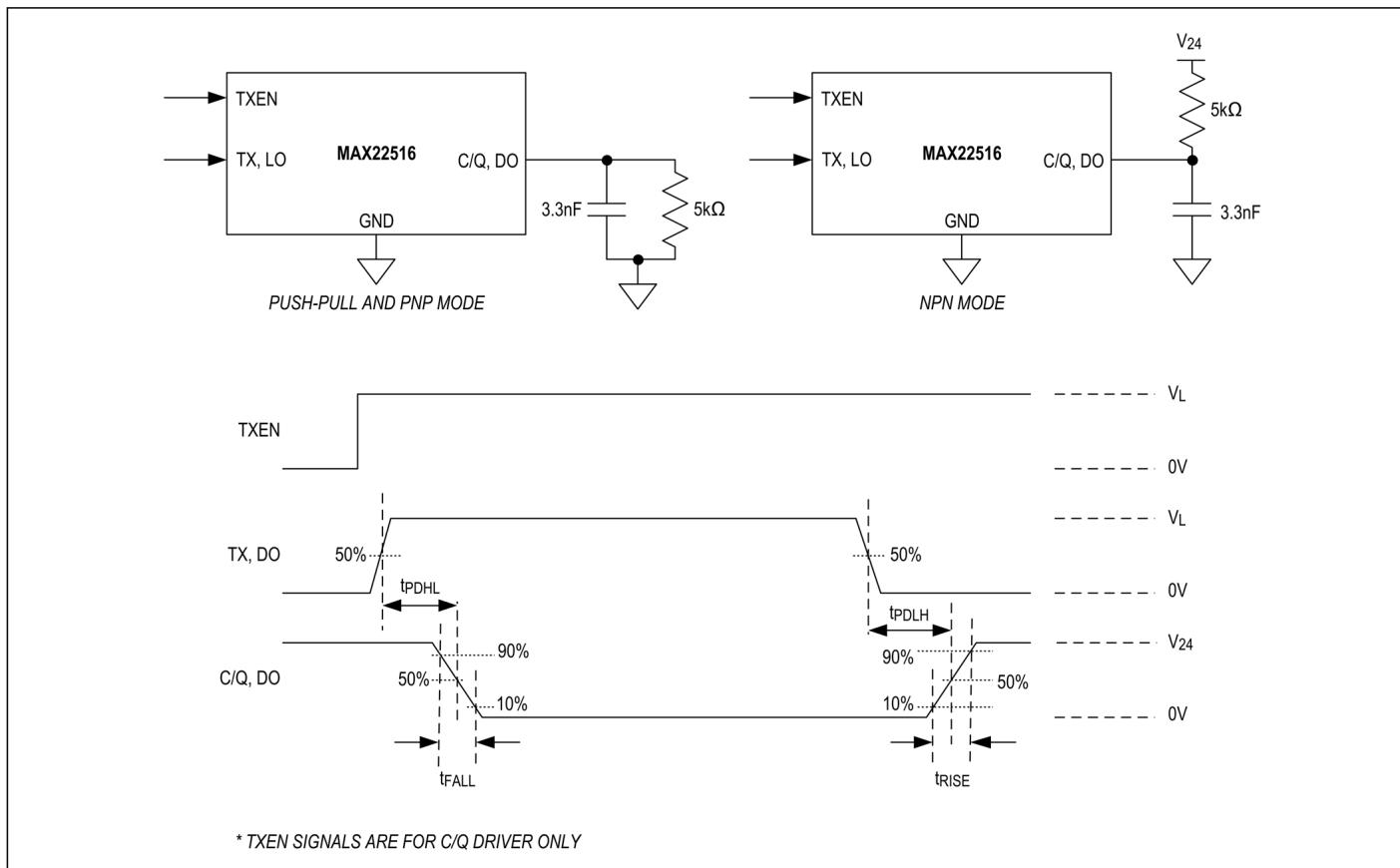

| C/Q, DO Driver Low-to-High Propagation Delay | $t_{PDLH\_PP}$          | $CQ\_SLEW[1:0] = 00$ or<br>$DO\_SLEW[1:0] = 00$ , Figure 1                     | Push-pull or PNP mode                           | 0.32 | 0.61 | 0.90  |

|                                              | $t_{PDLH\_OC}$          | $CQ\_SLEW[1:0] = 00$ or<br>$DO\_SLEW[1:0] = 00$ , Figure 1                     | NPN mode                                        |      | 1    | μs    |

| C/Q, DO Driver High-to-Low Propagation Delay | $t_{PDHL\_PP}$          | $CQ\_SLEW[1:0] = 00$ or<br>$DO\_SLEW[1:0] = 00$ , Figure 1                     | Push-pull or NPN mode                           | 0.41 | 0.65 | 0.92  |

|                                              | $t_{PDHL\_OC}$          | $CQ\_SLEW[1:0] = 00$ or<br>$DO\_SLEW[1:0] = 00$ , Figure 1                     | PNP mode                                        |      | 1    | μs    |

| C/Q, DO Driver Skew                          | $t_{SKEW}$              | $ t_{PDLH} - t_{PDHL} $ , $CQ\_SLEW[1:0] = 00$ or<br>$DO\_SLEW[1:0] = 00$      |                                                 | -0.2 | +0.2 | μs    |

| C/Q, DO Driver Rise Time                     | $t_{RISE}$              | Push-pull or PNP mode, $V_{24(max)} = 30V$ , Figure 1                          | $CQ\_SLEW[1:0] = 00$ or<br>$DO\_SLEW[1:0] = 00$ | 0.2  | 0.36 | 0.56  |

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

(特に指定のない限り、 $V_{24} = 7V \sim 36V$ 、 $V_5 = 4.85V \sim 5.5V$ 、 $V_L = 2.5V \sim 5.5V$ 、 $V_{GNDQ} = V_{GND} = 0V$ 、全ロジック入力は  $V_L$  または  $GND$ 、代表値は  $V_{24} = 24V$ 、 $V_5 = 5V$ 、 $V_L = 3.3V$ 、 $T_A = +25^\circ C$  における値 (Note 1) )

| PARAMETER                                           | SYMBOL | CONDITIONS                                                            | MIN                                       | TYP  | MAX  | UNITS   |         |

|-----------------------------------------------------|--------|-----------------------------------------------------------------------|-------------------------------------------|------|------|---------|---------|

| C/Q, DO Driver Fall Time                            | tFALL  | Push-pull or PNP mode, $V_{24(max)} = 30V$ , <a href="#">Figure 1</a> | CQ_SLEW[1:0] = 01 or<br>DO_SLEW[1:0] = 01 | 0.38 | 0.69 | 1.04    | $\mu s$ |

|                                                     |        |                                                                       | CQ_SLEW[1:0] = 10 or<br>DO_SLEW[1:0] = 10 | 0.80 | 1.63 | 2.65    |         |

|                                                     |        |                                                                       | CQ_SLEW[1:0] = 11 or<br>DO_SLEW[1:0] = 11 | 2.2  | 6.3  | 11.5    |         |

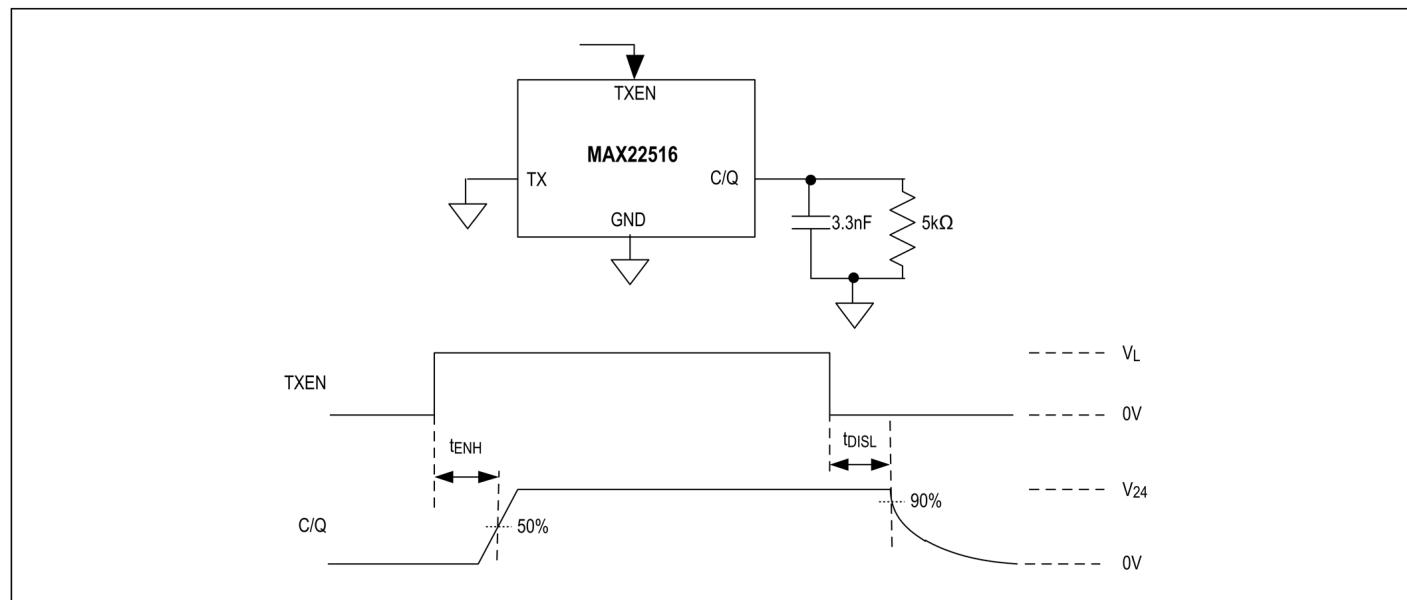

| C/Q, DO Driver Enable Time High                     | tENH   | Push-pull or NPN mode, $V_{24(max)} = 30V$ , <a href="#">Figure 1</a> | CQ_SLEW[1:0] = 00 or<br>DO_SLEW[1:0] = 00 | 0.18 | 0.32 | 0.50    | $\mu s$ |

|                                                     |        |                                                                       | CQ_SLEW[1:0] = 01 or<br>DO_SLEW[1:0] = 01 | 0.38 | 0.63 | 1.00    |         |

|                                                     |        | Push-pull or NPN mode, $V_{24(max)} = 30V$ , <a href="#">Figure 1</a> | CQ_SLEW[1:0] = 10 or<br>DO_SLEW[1:0] = 10 | 1    | 1.56 | 2.5     |         |

|                                                     |        |                                                                       | CQ_SLEW[1:0] = 11 or<br>DO_SLEW[1:0] = 11 | 4    | 7.32 | 12      |         |

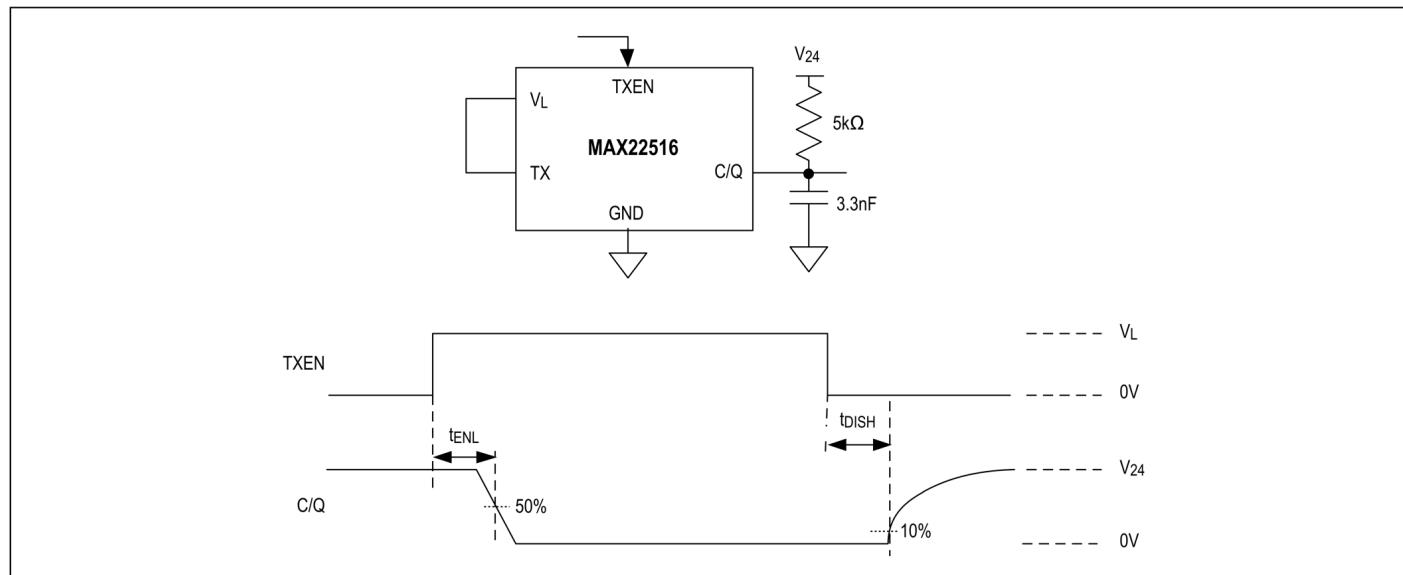

| C/Q, DO Driver Disable Time Low                     | tENL   | Push-pull or NPN mode, <a href="#">Figure 2</a>                       | 0.27                                      | 0.43 | 0.67 | $\mu s$ |         |

| C/Q, DO Driver Disable Time High                    | tDISH  | Push-pull or PNP mode, <a href="#">Figure 3</a>                       | 1.2                                       | 1.8  | 2.4  | $\mu s$ |         |

| C/Q, DO Driver Disable Time Low                     | tDISL  | Push-pull or NPN mode, <a href="#">Figure 2</a>                       | 1.2                                       | 1.93 | 2.6  | $\mu s$ |         |

| <b>C/Q, DI RECEIVERS</b>                            |        |                                                                       |                                           |      |      |         |         |

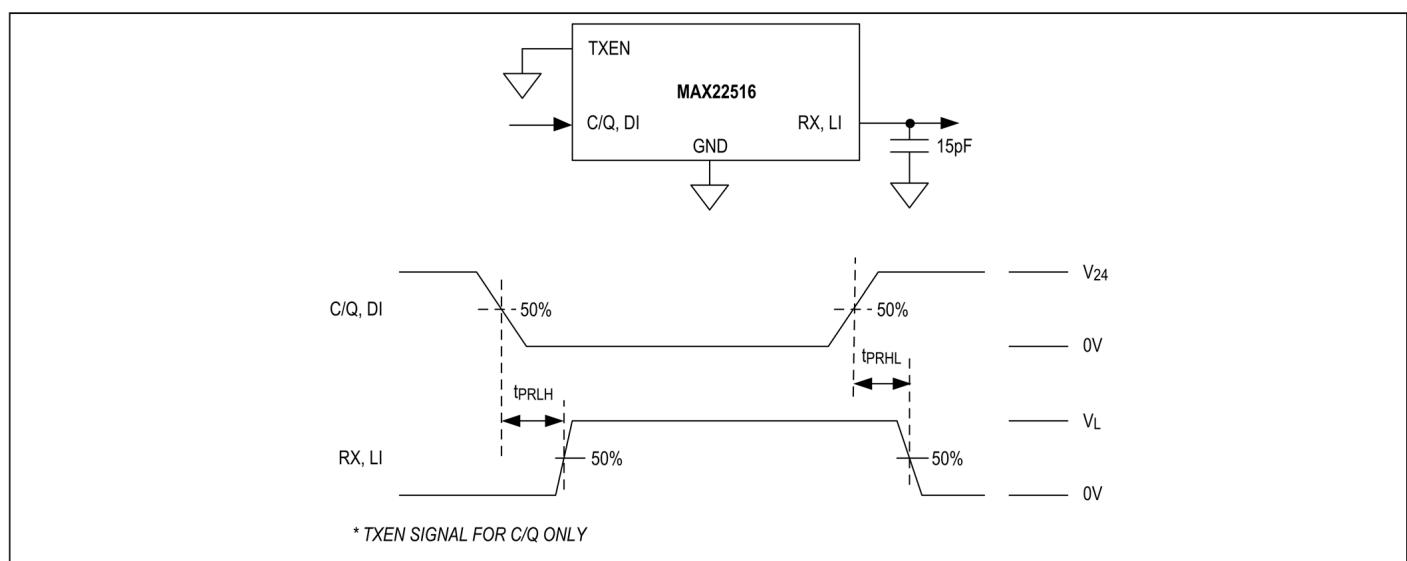

| C/Q Receiver Low-to-High Propagation Delay          | tPRLH  | <a href="#">Figure 4</a>                                              | RXFilter = 1                              | 0.83 | 1.28 | 1.8     | $\mu s$ |

|                                                     |        |                                                                       | RXFilter = 0                              | 0.27 | 0.39 | 0.51    |         |

| C/Q Receiver High-to-Low Propagation Delay          | tPRHL  | <a href="#">Figure 4</a>                                              | RXFilter = 1                              | 0.75 | 1.16 | 1.7     | $\mu s$ |

|                                                     |        |                                                                       | RXFilter = 0                              | 0.18 | 0.28 | 0.38    |         |

| DI Receiver Low-to-High Propagation Delay           | tPRLH  | <a href="#">Figure 4</a>                                              | RXFilter = 1                              | 0.97 | 2.30 | 2.30    | $\mu s$ |

|                                                     |        |                                                                       | RXFilter = 0                              | 0.45 |      | 1.05    |         |

| DI Receiver High-to-Low Propagation Delay           | tPRHL  | <a href="#">Figure 4</a>                                              | RXFilter = 1                              | 0.85 | 2.05 | 2.05    | $\mu s$ |

|                                                     |        |                                                                       | RXFilter = 0                              | 0.35 |      | 0.78    |         |

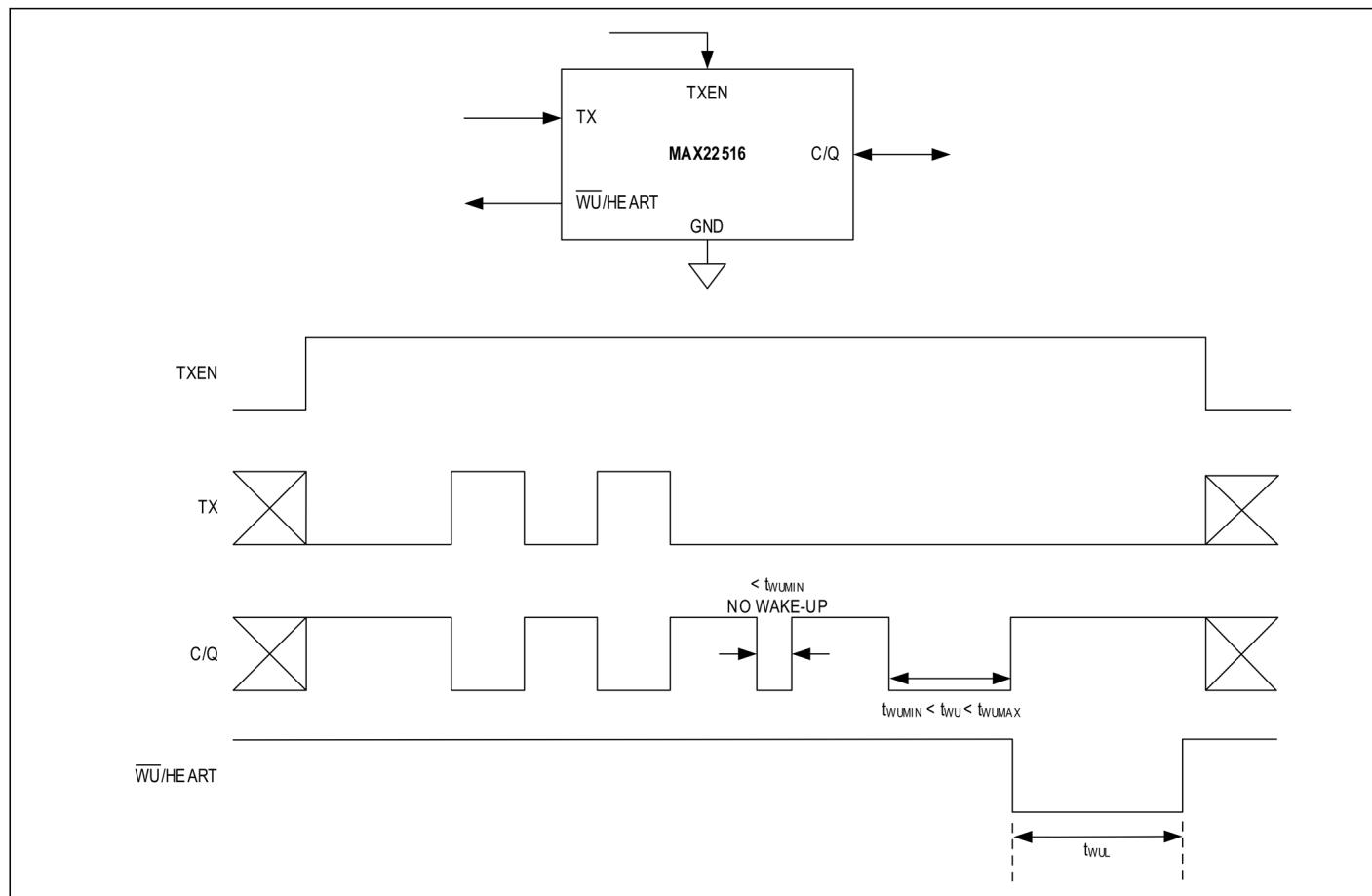

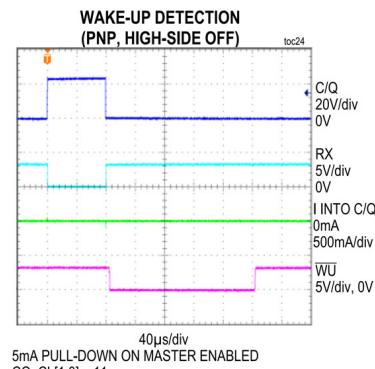

| <b>WAKE-UP DETECTION (<a href="#">Figure 5</a>)</b> |        |                                                                       |                                           |      |      |         |         |

| Wake-Up Input Minimum Pulse Width                   | tWUMIN | C/Q load capacitance = 3nF                                            | 60                                        | 66   | 70   | $\mu s$ |         |

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

(特に指定のない限り、 $V_{24} = 7V \sim 36V$ 、 $V_5 = 4.85V \sim 5.5V$ 、 $V_L = 2.5V \sim 5.5V$ 、 $V_{GNDQ} = V_{GND} = 0V$ 、全ロジック入力は  $V_L$  または  $GND$ 、代表値は  $V_{24} = 24V$ 、 $V_5 = 5V$ 、 $V_L = 3.3V$ 、 $T_A = +25^\circ C$  における値 (Note 1) )

| PARAMETER                                                                 | SYMBOL         | CONDITIONS                                                               | MIN                | TYP  | MAX   | UNITS |

|---------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------|--------------------|------|-------|-------|

| Wake-Up Input Maximum Pulse Width                                         | $t_{WUMAX}$    |                                                                          | 85                 | 95   | 110   | μs    |

| WU/HEART Output Low Time                                                  | $t_{WUL}$      | Valid wake-up condition on C/Q,<br>WU/HEART configured as Wake-up output | 150                | 200  | 250   | μs    |

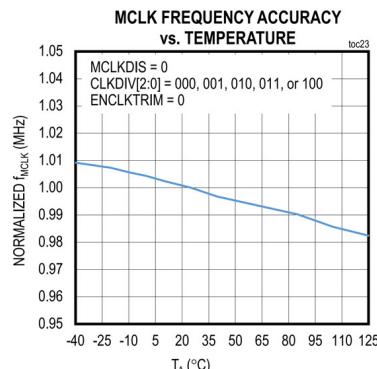

| <b>MCLK CLOCK</b>                                                         |                |                                                                          |                    |      |       |       |

| MCLK Output Frequency                                                     | $f_{MCLK}$     | MCLKDIR = high                                                           | ClkDiv[2:0] = 000  | 3.55 | 3.684 | 3.81  |

|                                                                           |                |                                                                          | ClkDiv [2:0] = 001 | 7.10 | 7.37  | 7.62  |

|                                                                           |                |                                                                          | ClkDiv [2:0] = 010 | 14.1 | 14.71 | 15.3  |

|                                                                           |                |                                                                          | ClkDiv [2:0] = 011 | 28   | 29.4  | 31    |

|                                                                           |                |                                                                          | ClkDiv [2:0] = 100 | 1.78 | 1.843 | 1.91  |

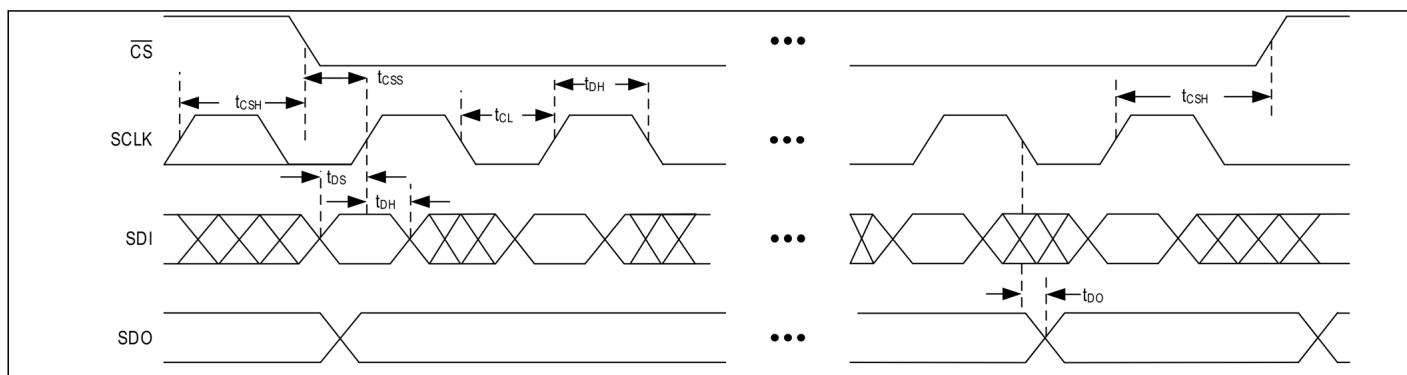

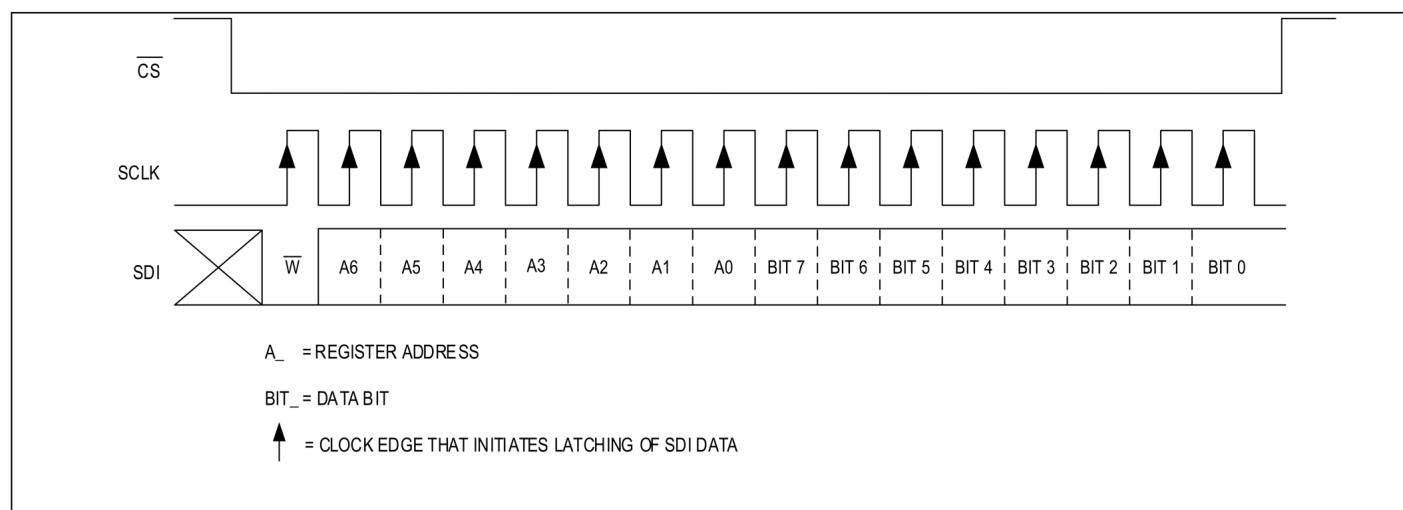

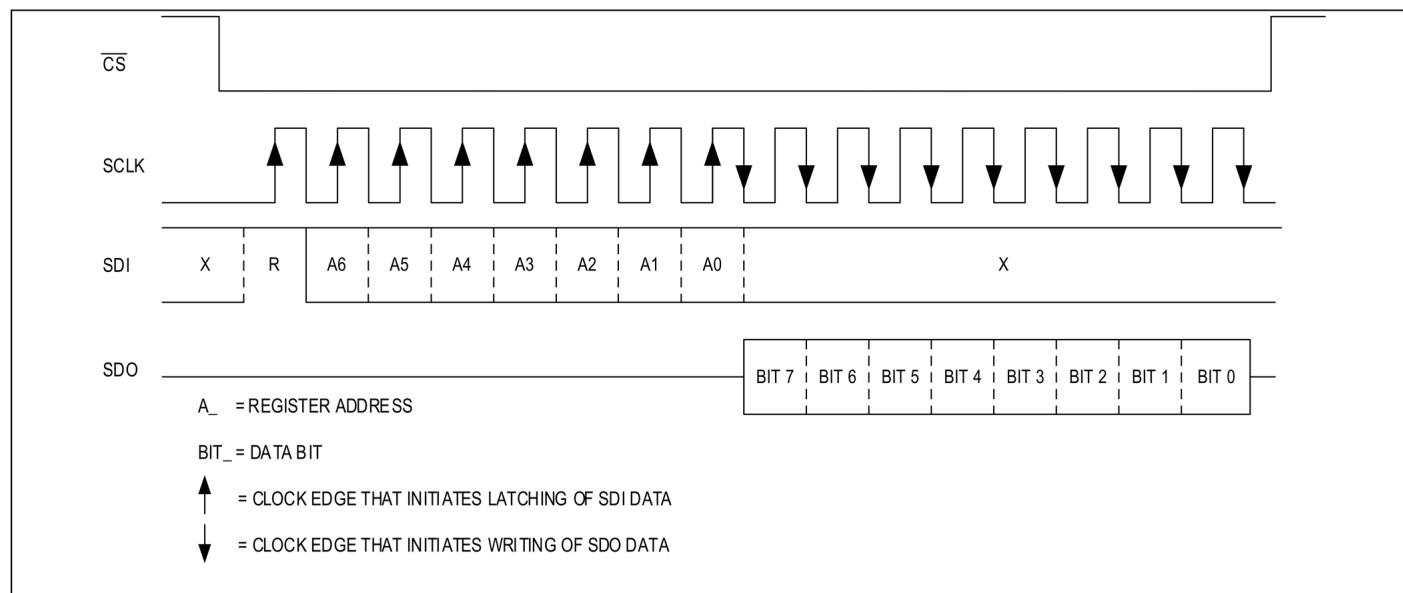

| <b>SPI TIMING (<math>\overline{CS}</math>, SCLK, SDI, SDO) (Figure 6)</b> |                |                                                                          |                    |      |       |       |

| Maximum SCLK Frequency                                                    | $f_{SPI\_MAX}$ | With 50% duty cycle on SCLK                                              |                    |      | 15    | MHz   |

| SCLK Clock Period                                                         | $t_{CH+CL}$    |                                                                          | 40                 |      |       | ns    |

| SCLK Pulse Width High                                                     | $t_{CH}$       |                                                                          | 8                  |      |       | ns    |

| SCLK Pulse Width Low                                                      | $t_{CL}$       |                                                                          | 32                 |      |       | ns    |

| CS Fall to SCLK Rise Time                                                 | $t_{CSS}$      |                                                                          | 9                  |      |       | ns    |

| SCLK Rise to $\overline{CS}$ Rise Hold Time                               | $t_{CSH}$      |                                                                          | 11                 |      |       | ns    |

| SDI Hold Time                                                             | $t_{DH}$       |                                                                          | 6                  |      |       | ns    |

| SDI Setup Time                                                            | $t_{DS}$       |                                                                          | 8                  |      |       | ns    |

| SDO Output Data Propagation Delay                                         | $t_{DO}$       |                                                                          |                    | 20   |       | ns    |

| SDO Rise and Fall Times                                                   | $t_{FT}$       |                                                                          | 0.5                | 4    |       | ns    |

| Minimum $\overline{CS}$ Pulse                                             | $t_{CSW}$      |                                                                          | 20                 |      |       | ns    |

| <b>EMC TOLERANCE</b>                                                      |                |                                                                          |                    |      |       |       |

| ESD Protection ( $V_{24}$ , C/Q, DO, DI Pins to GND)                      |                | IEC 61000-4-2 contact discharge                                          |                    | ±3   |       | kV    |

| ESD Protection (All Other Pins)                                           |                | Human body model                                                         |                    | ±2   |       | kV    |

| Surge Protection ( $V_{24}$ , C/Q, DO, DI Pins)                           | $V_{SRG}$      | 500Ω 8/20μs surge to ground                                              |                    | ±1.2 |       | kV    |

**Note 1:** 全てのデバイスは、 $T_A = 25^\circ C$  で 100% 製品テストされています。動作温度範囲における制限値は、設計により確保されています。

**Note 2:** 製品テストの対象外です。設計により性能を確保しています。

**Note 3:**  $V_{DROP}$  は、ローサイド・ドライバの電流制限値を計測するときはドライバ出力の  $GND$  に対する電圧 ( $V_{DRIVER} - V_{GND}$ ) で、ハイサイドの電流制限値を計測するときは ( $V_{24} - V_{DRIVER}$ ) として測定します。

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

## タイミング図

図 1. C/Q ドライバの伝搬遅延

図 2. C/Q ドライバのイネーブル・ロー（ローになるとイネーブル）、ディスエーブル・ハイ（ハイになるとディスエーブル）のタイミング

図 3. C/Q ドライバのイネーブル・ハイ、ディスエーブル・ローのタイミング

図 4. C/Q レシーバのタイミング

図 5. ウェイクアップ検出

図 6. SPI タイミング図

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

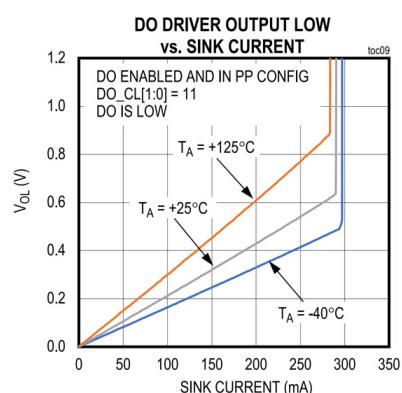

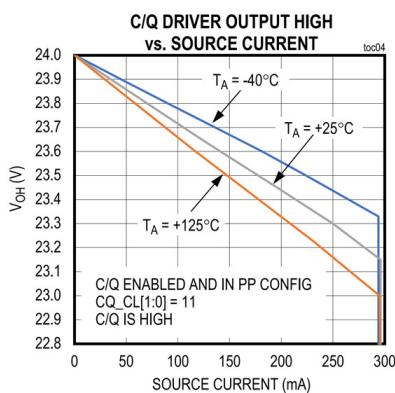

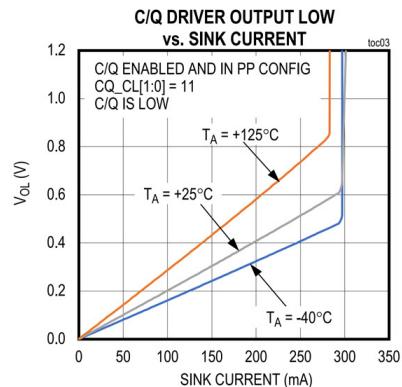

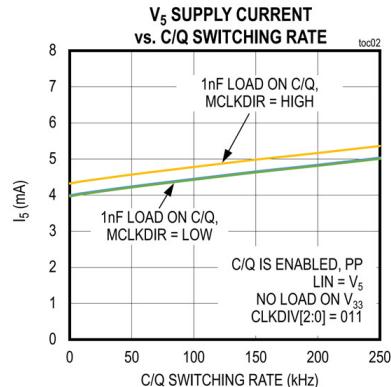

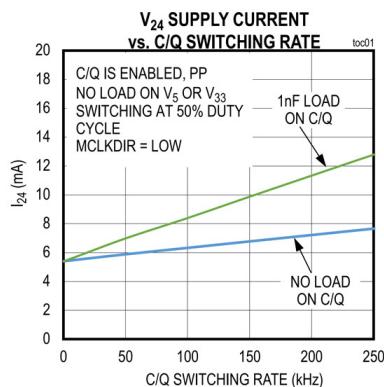

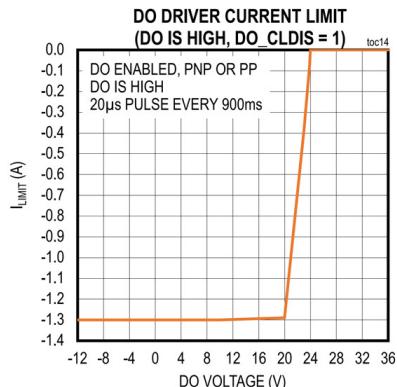

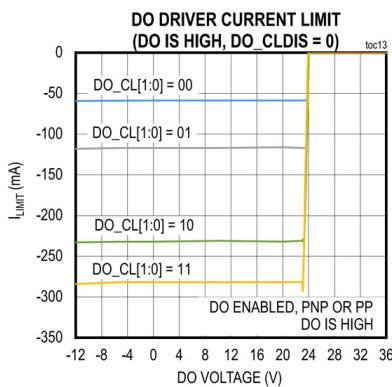

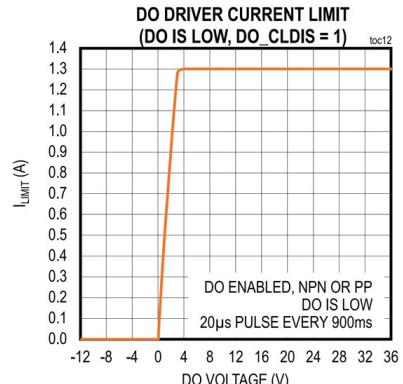

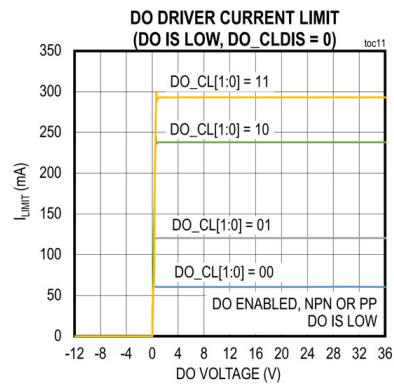

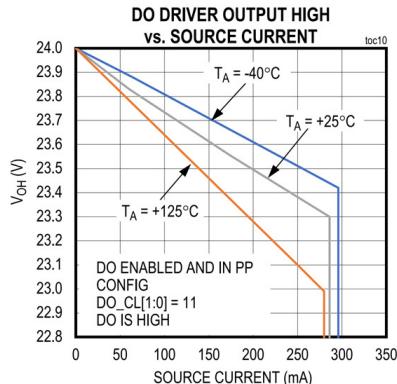

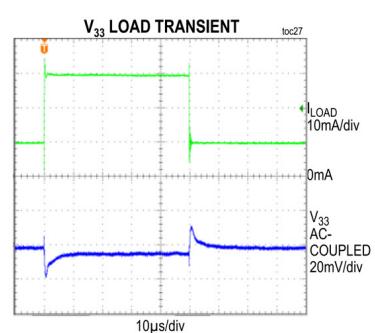

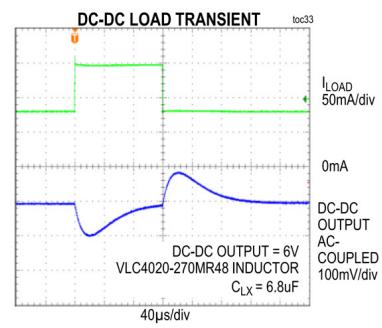

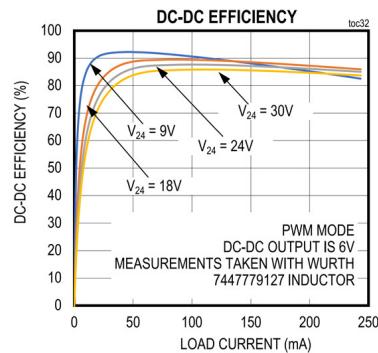

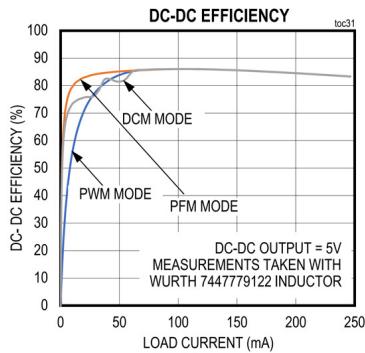

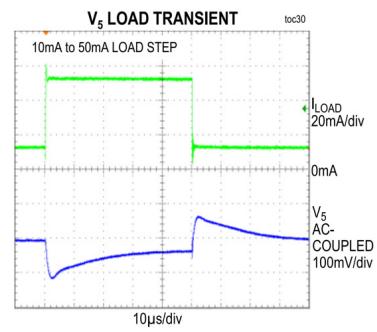

## 標準動作特性

特に指定のない限り、 $V_{24} = 24V$ 、 $LIN = DC/DC$  出力 = 6V、 $V_L = V_{33}$ 、 $T_A = 25^\circ C$ 。

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

特に指定のない限り、 $V_{24} = 24V$ 、LIN = DC/DC 出力 = 6V、 $V_L = V_{33}$ 、 $T_A = 25^\circ C$ 。

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

特に指定のない限り、 $V_{24} = 24V$ 、 $LIN = DC/DC$  出力 = 6V、 $V_L = V_{33}$ 、 $T_A = 25^\circ C$ 。

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

特に指定のない限り、 $V_{24} = 24V$ 、LIN = DC/DC 出力 = 6V、 $V_L = V_{33}$ 、 $T_A = 25^\circ C$ 。

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

特に指定のない限り、 $V_{24} = 24V$ 、 $LIN = DC/DC$  出力 = 6V、 $V_L = V_{33}$ 、 $T_A = 25^\circ C$ 。

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

## ピン配置

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

## 端子説明

| ピン                            |            | 名称               | 説明                                                                                                                                                                                                                                                                             |

|-------------------------------|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN                          | WLP        |                  |                                                                                                                                                                                                                                                                                |

| <b>電源</b>                     |            |                  |                                                                                                                                                                                                                                                                                |

| 12                            | A2         | V <sub>CCB</sub> | 内蔵 5V 電源レギュレータの出力。1μF のコンデンサをできるだけデバイスの近くに配置して、V <sub>CCB</sub> を GND にバイパスします。V <sub>CCB</sub> は最大 5mA の外部負荷に電源を供給できます。                                                                                                                                                       |

| 16                            | A4         | PV <sub>24</sub> | アクティブ・ダイオードの出力、DC/DC の入力。外付けの 1μF コンデンサをできるだけデバイスの近くに配置して、PV <sub>24</sub> をバイパスします。                                                                                                                                                                                           |

| 15                            | B4         | LIN              | 5V リニア・レギュレータ入力。DC/DC 回路の出力、PV <sub>24</sub> 電源、6V～36V の外部電源のいずれかに LIN を接続します。LIN は 1μF のコンデンサで GND にバイパスします。LIN を V <sub>5</sub> に接続すると、5V リニア・レギュレータがディスエーブルされます。                                                                                                            |

| 10                            | B1         | V <sub>5</sub>   | 5V リニア・レギュレータ出力／電源入力。V <sub>5</sub> は内蔵 5V リニア・レギュレータの出力です。1μF のコンデンサをできるだけデバイスの近くに配置して、V <sub>5</sub> を GND にバイパスします。5V リニア・レギュレータをディスエーブルするには、LIN を V <sub>5</sub> に接続します。<br>通常動作のためには、V <sub>5</sub> に 5V の供給が必要です。5V レギュレータをディスエーブルする場合は、外部 5V 電源を V <sub>5</sub> に供給します。 |

| 25, 26                        | C6, C7     | V <sub>24</sub>  | 電源電圧入力。全ての V <sub>24</sub> ピンを相互に接続します。V <sub>24</sub> は IO-Link コネクタの L+端子に接続するか、外部電源に接続します。10nF のコンデンサをできるだけデバイスの近くに配置して、V <sub>24</sub> を GND にバイパスします。                                                                                                                     |

| 23, 28                        | B6, E7     | GNDCQ            | C/Q ドライバと IO-Link のグランド。GNDCQ は IO-Link コネクタの L-端子および GND に接続します。詳細については、 <a href="#">レイアウトとグランド接続配線</a> のセクションを参照してください。                                                                                                                                                      |

| 4                             | E2         | V <sub>L</sub>   | ロジック IO 電源入力。1μF のコンデンサをできるだけデバイスの近くに配置して、V <sub>L</sub> を GND にバイパスします。V <sub>L</sub> は全ロジック信号のロジック・レベルを設定します。V <sub>33</sub> 、V <sub>5</sub> 、2.5V～5.5V の外部電圧のいずれかに V <sub>L</sub> を接続します。                                                                                   |

| 1, 14                         | B3, C3, C4 | GND              | グランド。GND は GNDCQ に接続します。<br>全ての GND ピンを接続する必要があります。詳細については、 <a href="#">レイアウトとグランド接続配線</a> のセクションを参照してください。                                                                                                                                                                    |

| 36                            | D4, D5     | GNDD             | デジタル・グランド。GNDD は GND に接続します。<br>全ての GND ピンを接続する必要があります。詳細については、 <a href="#">レイアウトとグランド接続配線</a> のセクションを参照してください。                                                                                                                                                                |

| 9                             | B2         | V <sub>33</sub>  | 3.3V リニア・レギュレータ出力。1μF のコンデンサをできるだけデバイスの近くに配置して、V <sub>33</sub> を GND にバイパスします。V <sub>33</sub> をディスエーブルするアプリケーションではバイパス・コンデンサは必要ありません。                                                                                                                                          |

| EP                            | -          | EP               | 露出パッド。EP は GND に接続します。詳細については、 <a href="#">レイアウトとグランド接続配線</a> のセクションを参照してください。                                                                                                                                                                                                 |

| <b>DC/DC レギュレータ</b>           |            |                  |                                                                                                                                                                                                                                                                                |

| 13                            | A3         | LX               | 内蔵 DC/DC コンバータのスイッチング出力。DC/DC 回路による電圧を生成するために、LX と出力コンデンサの間にインダクタを接続します。詳細については、 <a href="#">内蔵 DC/DC レギュレータ</a> のセクションを参照してください。                                                                                                                                              |

| 11                            | A1         | FB               | DC/DC 降圧レギュレータの帰還入力。DC/DC の出力と GND の間の抵抗分圧器のタップに FB を接続します。詳細については、 <a href="#">内蔵 DC/DC レギュレータ</a> のセクションを参照してください。<br>DC/DC を使用しない場合は、FB を V <sub>CCB</sub> に接続します。                                                                                                          |

| <b>24V I/O ライン・インターフェース</b>   |            |                  |                                                                                                                                                                                                                                                                                |

| 24                            | B7         | C/Q              | C/Q IO-Link トランシーバー入力／出力。TXEN をハイにドライブし、CQ_EN = 1 にセットすると、C/Q ドライバがイネーブルされます。C/Q のロジックは、デフォルトでは TX と RX の信号の論理反転になります。                                                                                                                                                         |

| 27                            | D7         | DO               | DO 補助ドライバ出力。DO_EN = 1 にセットすると、DO ドライバ出力がイネーブルされます。DO は LO 入力の論理反転です。DO_EN = 0 のとき、DO は高インピーダンスになります。                                                                                                                                                                           |

| 22                            | A7         | DI               | 補助デジタル入力。LI は DI 入力の信号の論理反転です。DI レシーバは常時イネーブルされています。信号と DI ピンの間に 1kΩ の抵抗を直列に接続します。                                                                                                                                                                                             |

| <b>補助 DI/DO ロジック・インターフェース</b> |            |                  |                                                                                                                                                                                                                                                                                |

| 30                            | D6         | LO               | DO ドライバ・ロジック入力。DO は、イネーブルされているときは、LO 入力の信号の論理反転です。                                                                                                                                                                                                                             |

# トランシーバーおよび内蔵 DC/DC レギュレータを備えた IO-Link データ・リンク・コントローラ

MAX22516

|                              |    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------|----|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29                           | F7 | LI                     | DI レシーバ・ロジック出力。LI は DI 入力の信号の論理反転です。LI は常時イネーブルされています。                                                                                                                                                                                                                                                                                                                                                                           |

| <b>SPI インターフェース</b>          |    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 37                           | E4 | SDO                    | シリアル・データ出力。MAX22516 の SDO を SPI ホスト・コントローラのシリアル・データ入力に接続します。 $\overline{CS}$ がハイのとき、SDO は高インピーダンスになります。                                                                                                                                                                                                                                                                                                                          |

| 38                           | F3 | SCLK                   | シリアル・クロック入力。                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 39                           | E3 | SDI                    | シリアル・データ入力。MAX22516 の SDI を SPI ホスト・コントローラのシリアル・データ出力に接続します。                                                                                                                                                                                                                                                                                                                                                                     |

| 40                           | F2 | $\overline{CS}$        | SPI チップ・セレクト入力。 $\overline{CS}$ をローにドライブすると読み出し／書き込みサイクルを開始します。このサイクルは $\overline{CS}$ をハイにドライブすると終了します。                                                                                                                                                                                                                                                                                                                         |

| 17                           | D3 | CRCEN                  | SPI インターフェース用 CRC イネーブル。CRCEN を $V_L$ に接続すると、SPI インターフェースの CRC が有効になります。                                                                                                                                                                                                                                                                                                                                                         |

| 7                            | C2 | $\overline{CRCERR}$    | オープン・ドレインの SPI CRC エラー出力。最後の SPI 通信で CRC エラーが検出されている場合、 $\overline{CRCERR}$ はローにアサートされます。                                                                                                                                                                                                                                                                                                                                        |

| <b>電圧モニタ</b>                 |    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

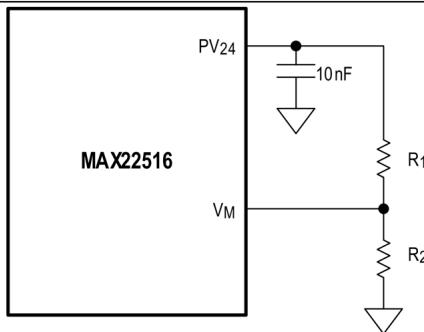

| 21                           | A6 | $V_M$                  | 電圧モニタ入力。モニタする電源（例えば $PV_{24}$ ）と GND の間に抵抗分圧器を接続し、モニタする電圧のパワーOK スレッショルドを規定します。詳細については、 <a href="#">電圧モニタ入力</a> のセクションを参照してください。                                                                                                                                                                                                                                                                                                  |

| <b>割込みとインジケータ</b>            |    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5                            | D1 | $\overline{IRQ}$       | アクティブ・ロー、オープン・ドレインの割込み要求出力。 $\overline{IRQ}$ は、イネーブルされている場合、IOLInt、DEVInt、ISDULint のビットのいずれかがセットされたときにローにアサートされます。                                                                                                                                                                                                                                                                                                               |

| 6                            | D2 | $\overline{WU/HEART}$  | オープン・ドレインの IO-Link ウエイクアップ要求／ハート出力。MISC_CTRL レジスタの HEART_WU ビットの設定により、 $\overline{WU/HEART}$ ピンの機能をプログラムします。                                                                                                                                                                                                                                                                                                                     |

| 8                            | C1 | $\overline{RESET/POK}$ | アクティブ・ロー・リセット入力とパワーOK (POK) 出力のデュアル機能のオープン・ドレイン端子。 $\overline{RESET/POK}$ をローにドライブすると MAX22516 がリセット・モードに設定されます。 $V_{24}$ 、 $V_5$ 、DC/DC 出力のいずれかの電圧が各々の低電圧ロックアウト (UVLO) スレッショルドを下回ったとき、MAX22516 は $\overline{RESET/POK}$ をローにアサートします。通常動作時は、 $\overline{RESET/POK}$ を $V_{CCB}$ または $V_L$ に $10\text{k}\Omega$ (代表値) の抵抗で接続します。<br>詳細については、 <a href="#">リセット入力／パワーOK 出力 (<math>\overline{RESET/POK}</math>)</a> のセクションを参照してください。 |

| 18                           | A5 | $\overline{WDG}$       | オープン・ドレインのウォッチドッグ・タイムアウト出力。 $\overline{WDG}$ は、ウォッチドッグ・タイマのカウンタが制限値に達したときにローにアサートされます。                                                                                                                                                                                                                                                                                                                                           |

| <b>IO-Link UART インターフェース</b> |    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 31                           | F6 | RX                     | C/Q レシーバのロジック出力。デフォルトでは RX は C/Q の論理反転です。                                                                                                                                                                                                                                                                                                                                                                                        |

| 33                           | F5 | TXEN                   | C/Q ドライバ・イネーブルのロジック入力。                                                                                                                                                                                                                                                                                                                                                                                                           |

| 32                           | E6 | TX                     | C/Q ドライバのロジック入力。                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>クロック入力／出力</b>             |    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2                            | F1 | MCLKDIR                | MCLK の入力／出力方向選択。MCLKDIR をハイにドライブすると、UART 用に内部発振器を使用し、MCLK がクロック源となります。<br>MCLKDIR をローにドライブすると内部クロックがディスエーブルされます。MCLKDIR をローにしたときには、UART 通信用の外部クロックを MCLK に接続します。                                                                                                                                                                                                                                                                 |

| 3                            | E1 | MCLK                   | マイクロコントローラ・クロック入力／出力。MCLK をクロック源として使用するには MCLKDIR をハイにドライブします。MCLK をクロック入力ピンとして使用するには MCLKDIR をローにドライブします。MCLKDIR がローのときには MCLK に外部クロック源を接続します。                                                                                                                                                                                                                                                                                  |

| <b>汎用 I/O と LED 出力</b>       |    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                  |