## 工場出荷時キャリブレーション済みの 設定可能な12チャンネル工業用アナログ入力

#### 概要

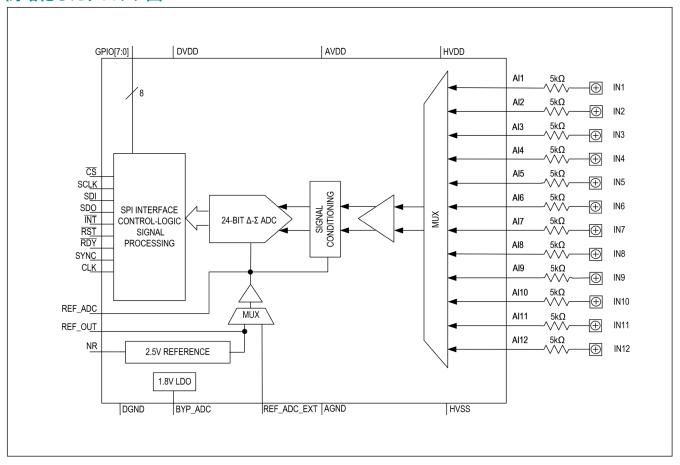

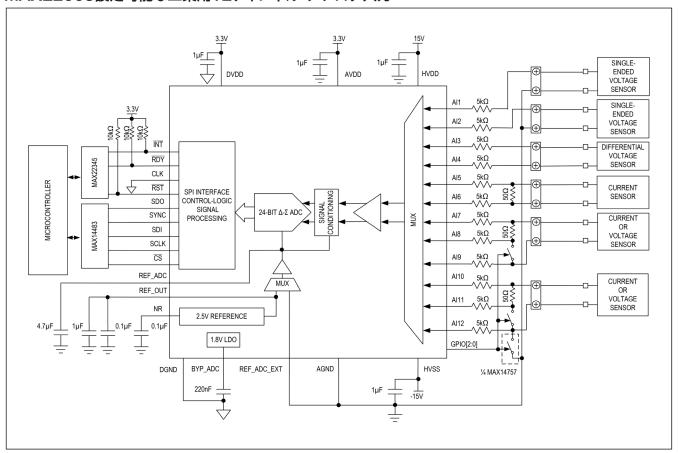

MAX22005は、工業グレードの12チャンネル・アナログ入力電圧モード・デバイスです。各チャンネルに外付けの高精度抵抗を追加することで、アナログ入力電流モード・デバイスとしても構成できます。また、各チャンネルに外付けの高精度抵抗と低コストのスイッチを組み合わせることで、設定可能なアナログ入力として動作させることもできます。入力チャンネルは、12個のシングルエンド入力、6個の差動入力、または最大8個のマルチチャンネル設定可能な差動入力として使用できます。このデバイスは、合計で最大26種類の設定に対応しています。

MAX22005は、全チャンネルで共有される24ビットのデルタシグマADCを内蔵しています。このADCは、内蔵5ppm/Cの高精度リファレンス、または外部リファレンスのどちらでも使用できます。標準的な工業用アナログ入力電圧範囲は、高電圧対応のゼロ・ドリフト入力アンプを使用して、ADCの入力電圧範囲に変換されます。すべての入力ポートは、Transient Voltage Suppressor(TVS)ダイオードを使用することなく、最大±36Vの逆極性および最大±2kVのサージ・パルスに対し、堅牢に保護されています。

8つの汎用デジタルI/O(GPIO)ポートは、一般的な用途に使用できる他、設定可能な入力用の外部スイッチを制御するために使用することもできます。

MAX22005は、出荷時にキャリブレーションされており、温度 範囲全域にわたり、総合未調整誤差(TUE)が0.05%FSR未満 というクラス最高のシステム性能を実現しています。

ホストは、すべての設定および情報管理に加え、変換結果の取得のために、30MHzの高速SPIバスを介してMAX22005と通信します。オプションの8ビットCRCを用いると、SPIインターフェースの信頼性が高まり、すべての8ビット・バーストおよびすべてのダブルビット・エラーから保護できます。

MAX22005は、2.7V~3.6Vのアナログ電源およびデジタル電源、更に最大±24Vの高電圧電源で動作します。

MAX22005は、48ピンLGAパッケージを採用しており、-40°C~+125°Cの工業用温度範囲で動作します。

#### アプリケーション

- プログラマブル・ロジック・コントローラ(PLC)

- プログラマブル・オートメーション・コントローラ(PAC)

- 分散制御システム(DCS)

#### 利点と特長

- より堅牢で高信頼性のシステムが可能

- ・全入力ポートに対する高電圧保護:±36V

- ・ 全ピンのHBM ESD保護:2kV

- サージ保護:±2kV(外部5kΩ抵抗使用)

- · CRC検出による堅牢なシリアル通信

- ・ ウォッチドッグ・タイマ

- ソフトウェアによる設定可能性

- ・ ±12.5Vのアナログ入力電圧モード

- 外部センス抵抗による±25mAのアナログ入力電流 モード

- ・ 外部センス抵抗および低コストのスイッチを使用した 設定可能な入力

- クラス最高のシステム精度

- ・ 工場出荷時キャリブレーション済み:0.02%FSR(25℃)

- 25°Cの工場出荷時キャリブレーション温度から ±50°Cの範囲内:0.05%FSR

- ・ 最大入力リーク電流:30nA

- 内部リファレンス:5ppm/°C

- その他の機能

- · 内部または外部ADCリファレンス

- ・8つのGPIOポート

- ・ ±5V電源使用時に48.5mWの低消費電力

- 30MHzのSPI/QSPI/DSP対応シリアル・インターフェース

- 動作温度範囲:-40℃~+125℃

- 7.5mm × 7mmの48ピンLGAパッケージ

型番はデータシートの末尾に記載されています。

## 簡略化したブロック図

## 目次

| 概要                               | 1  |

|----------------------------------|----|

| アプリケーション                         |    |

| 利点と特長                            |    |

| 簡略化したブロック図                       | 2  |

| 絶対最大定格                           | 7  |

| パッケージ情報                          | 7  |

| 48-PIN LGA                       | 7  |

| 電気的特性                            | 7  |

| 標準動作特性                           | 12 |

| ピン配置                             | 14 |

| MAX22005                         | 14 |

| 端子説明                             | 14 |

| 詳細                               | 17 |

| 動作モード                            | 18 |

| 入力レンジ設定                          | 19 |

| 差動入力同相電圧範囲                       | 19 |

| 入力電圧定格                           | 19 |

| 電源電圧および電源投入シーケンス                 | 20 |

| パワーオン・リセット                       | 20 |

| SPIインターフェース                      | 20 |

| ウォッチドッグ・タイマ                      | 21 |

| 製品追跡                             | 21 |

| アナログ入力ADC                        | 21 |

| アナログ入力のオフセット誤差およびゲイン誤差のキャリブレーション | 25 |

| システム・キャリブレーション                   | 25 |

| ADCソフトウェア・リセット                   | 28 |

| ADC RDY (データ・レディ)出力              | 28 |

| SYNCピンを用いたADC変換の同期               | 28 |

| ハードウェア・リセット                      | 29 |

| レジスタ・マップ                         | 30 |

| MAX22005のレジスタ・マップ                | 30 |

| レジスタの詳細                          | 31 |

| アプリケーション情報                       | 45 |

| 電源のヘッドルーム要件                      | 45 |

| 電源投入シーケンス                        | 45 |

| 基板レイアウト                          | 45 |

| サージ保護                            | 45 |

| 標準アプリケーション回路                     |    |

| MAX22005設定可能な工業用12チャンネル・アナログ入力   | 46 |

# 工場出荷時キャリブレーション済みの 設定可能な12チャンネル工業用アナログ入力

| 目次(続き) |  |  |

|--------|--|--|

|        |  |  |

| 型番   | 46 |

|------|----|

| 改訂履歴 | 47 |

# 工場出荷時キャリブレーション済みの 設定可能な12チャンネル工業用アナログ入力

## 図一覧

| 図1. SPI書込みタイミング(CRC無効時はN = 24、CRC有効時はN = 32)                                             |                                                              |    |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------|----|

| 図2. SPI読出しタイミング(CRC無効時はN = 24、CRC有効時はN = 32)                                             | 図1. SPI書込みタイミング(CRC無効時はN = 24、CRC有効時はN = 32)                 | 11 |

| 図4. 入力ポートのペア                                                                             |                                                              |    |

| 図5. 入力保護20<br>図6. 2点システム・キャリブレーション                                                       | 図3. 入力ポートのトリプレット                                             | 17 |

| 図6. 2点システム・キャリブレーション26<br>図7. RDYの出力タイミング、a) シングルサイクル・モード、b) 連続シングルサイクル・モード、c) 連続変換モード28 | 図4. 入力ポートのペア                                                 | 18 |

| 図7. RDYの出力タイミング、a) シングルサイクル・モード、b) 連続シングルサイクル・モード、c) 連続変換モード28                           | 図5. 入力保護                                                     | 20 |

|                                                                                          | 図6. 2点システム・キャリブレーション                                         | 26 |

| 図8. SYNC入力タイミング29                                                                        | 図7. RDYの出力タイミング、a) シングルサイクル・モード、b) 連続シングルサイクル・モード、c) 連続変換モード | 28 |

|                                                                                          | 図8. SYNC入力タイミング                                              | 29 |

# 工場出荷時キャリブレーション済みの 設定可能な12チャンネル工業用アナログ入力

## 表一覧

| 表1. 入力レンジ                     |    |

|-------------------------------|----|

| 表2. CRC有効時のSPIトランザクション        | 20 |

| 表3. CRC無効時のSPIトランザクション        | 21 |

| 表4. 製品ID                      | 21 |

| 表5. 入力チャンネル設定の選択              | 22 |

| 表6. 入力チャンネルの制限値およびコード         | 22 |

| 表7. 連続変換におけるデータレートの選択         | 24 |

| 表8. シングルサイクル変換におけるデータレートの選択   | 24 |

| 表9. シングルサイクル連続変換におけるデータレートの選択 | 25 |

| 表10. 入力チャンネルのフルスケール・レンジ       | 26 |

### **Absolute Maximum Ratings**

| AVDD to AGND -0.3V to +3.9V                                                           | AI_ to HVSS0.3V to the lower of (+52V or (V <sub>HVDD</sub> - V <sub>HVSS</sub> ) + |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| DVDD to DGND                                                                          | 0.3V)  INT to DGND                                                                  |

| REF_ADC, REF_ADC_EXT, NR, REF_OUT to AGND0.3V to the lower of (+3.9V or VAVDD + 0.3V) | Soldering Temperature (reflow)+260°C                                                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 48-PIN LGA

| Package Code                                           | L487A7M+1 |  |  |

|--------------------------------------------------------|-----------|--|--|

| Outline Number                                         | 21-100448 |  |  |

| Land Pattern Number 90-100160                          |           |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                   |           |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 51.25°C/W |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 23.46°C/W |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/jp/packages">www.maximintegrated.com/jp/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/jp/thermal-tutorial">www.maximintegrated.com/jp/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{AVDD} = V_{DVDD} = 3.3V, V_{HVDD} = +15V, V_{HVSS} = -15V, Reference Source = Internal Reference, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 1)$

| PARAMETER           | SYMBOL              | CONDITIONS                                                                       | MIN   | TYP   | MAX   | UNITS |

|---------------------|---------------------|----------------------------------------------------------------------------------|-------|-------|-------|-------|

| ANALOG INPUT-VOLTA  | GE MODE—SIN         | GLE-ENDED                                                                        |       |       |       |       |

| Headroom            |                     | From V <sub>HVSS</sub>                                                           | 2.5   |       |       | V     |

| Headroom            |                     | From V <sub>HVDD</sub>                                                           | 2.5   |       |       | V     |

|                     |                     | ADC full-scale range                                                             |       | ±12.5 |       |       |

| Input-Voltage Range | V <sub>IN</sub>     | Linear range V <sub>HVSS</sub> = -5V, V <sub>HVDD</sub> = +5V ( <u>Note 2</u> )  | -2.5  |       | +2.5  | V     |

|                     |                     | Linear range (Note 2)                                                            | -10.5 |       | +10.5 |       |

| Offset Error        | V <sub>OFFSET</sub> | T <sub>A</sub> = +25°C                                                           |       | ±0.1  | ±1.3  | mV    |

| Offset Drift        |                     | $T_A = +25^{\circ}C \pm 50^{\circ}C$ , with internal reference ( <i>Note 3</i> ) |       |       | ±13.6 | μV/°C |

| Gain Error          |                     | T <sub>A</sub> = +25°C                                                           | ·     | ±200  | ±450  | ppm   |

## **Electrical Characteristics (continued)**

$(V_{AVDD} = V_{DVDD} = 3.3V, V_{HVDD} = +15V, V_{HVSS} = -15V,$  Reference Source = Internal Reference,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                      | SYMBOL             | CONDITIONS                                                                                                                                                | MIN | TYP  | MAX   | UNITS             |

|--------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|-------------------|

| Gain Drift                     |                    | $T_A = +25^{\circ}C \pm 50^{\circ}C$ , with internal reference ( <i>Note 3</i> )                                                                          |     |      | ±3.4  | ppm/°C            |

| INL Error                      | INL                | T <sub>A</sub> = +25°C                                                                                                                                    |     |      | ±600  | μV                |

| INL Drift                      |                    | T <sub>A</sub> = +25°C ± 50°C ( <i>Note 3</i> )                                                                                                           |     |      | ±4.0  | μV/°C             |

| Total Upadiustad Error         | TUE                | T <sub>A</sub> = +25°C ( <u>Note 4</u> )                                                                                                                  |     |      | ±0.02 | % FSR             |

| Total Unadjusted Error         | TOE                | $T_A = +25^{\circ}C \pm 50^{\circ}C (\underline{Note \ 3} \text{ and } \underline{Note \ 4})$                                                             |     |      | ±0.05 | /0 F3K            |

| Input-Voltage Noise            | V <sub>NOISE</sub> | ADC sample rate is 11.52ksps, ADC mode is Continuous Single-Cycle.                                                                                        |     | 138  |       | μV <sub>RMS</sub> |

| Input Current                  |                    |                                                                                                                                                           |     |      | ±30   | nA                |

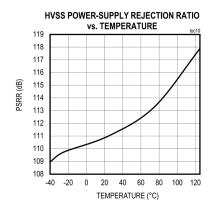

| Supply-Rejection Ratio         | PSRR               | DC, V <sub>HVDD</sub> = +5V to +24V                                                                                                                       |     | 100  |       | dB                |

| Supply-Rejection Ratio         | FORK               | DC, V <sub>HVSS</sub> = -24V to -5V                                                                                                                       |     | 100  |       | ub                |

| Open Detector                  |                    | From AI_ to V <sub>HVDD</sub>                                                                                                                             |     | 2    |       | ΜΩ                |

| Resistance                     |                    | From AI_ to AGND                                                                                                                                          |     | 2    |       | IVIZZ             |

| 50Hz/60Hz Normal-              |                    | DCHNL_RATE[3:0] = 0b0010, 0b0011, 0b0100, 0b0101                                                                                                          | 87  |      |       | dB                |

| Mode Rejection                 |                    | DCHNL_RATE[3:0] = 0b0000, 0b0001                                                                                                                          | 75  |      |       |                   |

| Settling Time                  |                    | V <sub>IN</sub> changes from 0V to -10.5V or 0V to +10.5V, digital output reaches 1% of final value. ADC sample rate is 57.6ksps, ADC mode is Continuous. |     |      | 0.2   | ms                |

| ANALOG INPUT VOLTA             | GE MODE—DIF        | FERENTIAL                                                                                                                                                 |     |      |       |                   |

| Input-Voltage Range            | V                  | ADC full-scale range                                                                                                                                      |     | ±25  |       | V                 |

| input-voitage Kange            | V <sub>IN</sub>    | linear range (Note 2)                                                                                                                                     | -21 |      | +21   | V                 |

| Offset Error                   | Voffset            | T <sub>A</sub> = +25°C                                                                                                                                    |     | ±0.2 | ±2.6  | mV                |

| Offset Drift                   |                    | $T_A = +25^{\circ}C \pm 50^{\circ}C$ , with internal reference ( <i>Note 3</i> )                                                                          |     |      | ±23.1 | μV/°C             |

| Gain Error                     |                    | T <sub>A</sub> = +25°C                                                                                                                                    |     | ±200 | ±450  | ppm               |

| Gain Drift                     |                    | $T_A = +25^{\circ}C \pm 50^{\circ}C$ , with internal reference ( <i>Note 3</i> )                                                                          |     |      | ±4.8  | ppm/°C            |

| INL Error                      | INL                | T <sub>A</sub> = +25°C                                                                                                                                    |     |      | ±1.2  | mV                |

| INL Drift                      |                    | T <sub>A</sub> = +25°C ± 50°C ( <i>Note 3</i> )                                                                                                           |     |      | ±5.0  | μV/°C             |

| Total Unadjusted Error         | TUE                | T <sub>A</sub> = +25°C ( <u>Note 4</u> )                                                                                                                  |     |      | ±0.02 | % FSR             |

| Total Unadjusted Error         | IOE                | T <sub>A</sub> = +25°C ± 50°C ( <i>Note 3</i> and <i>Note 4</i> )                                                                                         |     |      | ±0.05 | 70 F3K            |

| Input-Voltage Noise            | V <sub>NOISE</sub> | ADC sample rate is 11.52ksps, ADC mode is Continuous Single-Cycle.                                                                                        |     | 275  |       | μV <sub>RMS</sub> |

| Common-Mode<br>Rejection Ratio | CMRR               | V <sub>CM</sub> = -10V to +10V. Differential input is 0V                                                                                                  | 72  |      |       | dB                |

| Supply Bajaction Batic         | DODD               | DC, V <sub>HVDD</sub> = +5V to +24V                                                                                                                       |     | 100  |       | dB                |

| Supply-Rejection Ratio         | PSRR               | DC, V <sub>HVSS</sub> = -24V to -5V                                                                                                                       |     | 100  |       |                   |

| Input Current                  | I <sub>IN</sub>    |                                                                                                                                                           |     |      | ±30   | nA                |

## **Electrical Characteristics (continued)**

$(V_{AVDD} = V_{DVDD} = 3.3V, V_{HVDD} = +15V, V_{HVSS} = -15V, Reference Source = Internal Reference, T_A = T_{MIN} to T_{MAX}$ , unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 1)

| PARAMETER                                              | SYMBOL               | CONDITIONS                                                                                                                                                | MIN                        | TYP | MAX                        | UNITS  |

|--------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|----------------------------|--------|

| 50Hz/60Hz Normal-                                      |                      | DCHNL_RATE[3:0] = 0b0010, 0b0011, 0b0100, 0b0101                                                                                                          | 87                         |     |                            | dB     |

| Mode Rejection                                         |                      | DCHNL_RATE[3:0] = 0b0000, 0b0001                                                                                                                          | 75                         |     |                            |        |

| Open-Detector                                          |                      | From AI_ to V <sub>HVDD</sub>                                                                                                                             |                            | 2   |                            | MO     |

| Resistance                                             |                      | From AI_ to AGND                                                                                                                                          |                            | 2   |                            | ΜΩ     |

| Settling Time                                          |                      | V <sub>IN</sub> changes from 0V to -10.5V or 0V to +10.5V, digital output reaches 1% of final value. ADC sample rate is 57.6ksps; ADC mode is Continuous. |                            |     | 0.2                        | ms     |

| ADC REFERENCE (REF_                                    | ADC)                 |                                                                                                                                                           |                            |     |                            |        |

| REF_ADC Output<br>Voltage                              | V <sub>REF_ADC</sub> | Internal reference                                                                                                                                        |                            | 2.5 |                            | V      |

| Output-Voltage<br>Accuracy                             |                      | Referred to V <sub>REF_ADC</sub> , T <sub>A</sub> = +25°C                                                                                                 | -0.2                       |     | +0.2                       | %      |

| Output-Voltage<br>Temperature Coefficient              |                      | T <sub>A</sub> = -40°C to +125°C ( <u>Note 3</u> )                                                                                                        |                            | 1   | 5                          | ppm/°C |

| Line Regulation                                        |                      | 2.7V ≤ V <sub>AVDD</sub> ≤ 3.6V                                                                                                                           |                            |     | 130                        | μV/V   |

| REF_ADC Bypass<br>Capacitor                            |                      |                                                                                                                                                           |                            | 4.7 |                            | μF     |

| V <sub>REF_ADC_EXT</sub> Input<br>Range                |                      | External Reference                                                                                                                                        |                            | 2.5 |                            | V      |

| DIGITAL INPUTS                                         |                      |                                                                                                                                                           |                            |     |                            |        |

| Input Logic-Low Voltage                                | $V_{IL}$             |                                                                                                                                                           |                            |     | 0.3 ×<br>V <sub>DVDD</sub> | V      |

| Input Logic-High Voltage                               | $V_{IH}$             |                                                                                                                                                           | 0.7 ×<br>V <sub>DVDD</sub> |     |                            | V      |

| Input Hysteresis                                       | V <sub>HYS</sub>     |                                                                                                                                                           |                            | 200 |                            | mV     |

| Input Leakage Current                                  | I <sub>IN</sub>      |                                                                                                                                                           | -1                         |     | +1                         | μΑ     |

| Input Capacitance                                      | C <sub>IN</sub>      |                                                                                                                                                           |                            | 10  |                            | pF     |

| DIGITAL OUTPUTS                                        |                      |                                                                                                                                                           |                            |     |                            |        |

| Output Logic-Low<br>Voltage                            | $V_{OL}$             | I <sub>OL</sub> = 4mA                                                                                                                                     |                            |     | 0.4                        | V      |

| Output Logic-High<br>Voltage (SDO, RDYB,<br>GPIO[7:0]) | $V_{OH}$             | I <sub>OH</sub> = 4mA                                                                                                                                     | 0.9 ×<br>V <sub>DVDD</sub> |     |                            | V      |

| Three-State Leakage<br>Current                         |                      |                                                                                                                                                           | -10                        |     | +10                        | μΑ     |

| Three-State Output<br>Capacitance                      |                      |                                                                                                                                                           |                            | 10  |                            | pF     |

| SUPPLIES                                               |                      |                                                                                                                                                           |                            |     |                            |        |

| Analog Supply Voltage                                  | V <sub>AVDD</sub>    |                                                                                                                                                           | 2.7                        | 3.3 | 3.6                        | V      |

| Digital Supply Voltage                                 | V <sub>DVDD</sub>    |                                                                                                                                                           | 2.7                        | 3.3 | 3.6                        | V      |

## **Electrical Characteristics (continued)**

$(V_{AVDD} = V_{DVDD} = 3.3V, V_{HVDD} = +15V, V_{HVSS} = -15V,$ Reference Source = Internal Reference,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                           | SYMBOL                | CONDITIONS                                                                                       | MIN | TYP  | MAX | UNITS |

|-------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Positive High-Voltage<br>Supply     | V <sub>HVDD</sub>     |                                                                                                  | 5   |      | 24  | V     |

| Negative High-Voltage<br>Supply     | V <sub>HVSS</sub>     |                                                                                                  | -24 |      | -5  | V     |

| High-Voltage Supply                 | V <sub>HV</sub>       | V <sub>HVDD</sub> - V <sub>HVSS</sub>                                                            | 10  |      | 48  | V     |

| DVDD POR Threshold                  | V <sub>DVDD_POR</sub> | Voltage rising                                                                                   |     | 1.5  |     | V     |

| HVDD-HVSS<br>Undervoltage Threshold |                       | Voltage rising                                                                                   |     | 1.5  |     | V     |

| Analog Supply Current               | I <sub>AVDD</sub>     | ADC sample rate is 11.52ksps, ADC mode is Continuous Single-Cycle. Single-ended AI1–AI12 at AGND |     | 4.5  |     | mA    |

| Digital Supply Current              | I <sub>DVDD</sub>     | ADC sample rate is 11.52ksps, ADC mode is Continuous Single-Cycle. Single-ended AI1–AI12 at AGND |     | 1.8  |     | mA    |

| High-Voltage Supply<br>Current      | I <sub>HV</sub>       | ADC sample rate is 11.52ksps, ADC mode is Continuous Single-Cycle. Single-ended AI1–AI12 at AGND |     | 2.5  |     | mA    |

| Total Power                         |                       | ADC sample rate is 11.52ksps, ADC mode is Continuous Single-Cycle. Single-ended AI1–AI12 at AGND |     | 95.8 |     | mW    |

|                                     |                       | Al1–Al12 at AGND, V <sub>HVDD</sub> = 5V and V <sub>HVSS</sub> = -5V, all inputs are on          |     | 45.8 |     |       |

| TIMING CHARACTERIST                 | rics                  |                                                                                                  |     |      |     |       |

| SCLK Frequency                      | fsclk                 | All SPI transactions                                                                             |     |      | 30  | MHz   |

| SCLK Clock Period                   | t <sub>CP</sub>       | All SPI transactions                                                                             | 33  |      |     | ns    |

| SCLK Pulse-Width High               | t <sub>CH</sub>       | All SPI transactions                                                                             | 13  |      |     | ns    |

| SCLK Pulse-Width Low                | t <sub>CL</sub>       | All SPI transactions                                                                             | 13  |      |     | ns    |

| CS Fall Setup Time                  | t <sub>CSS0</sub>     | CS falling edge to 1st SCLK rising edge setup time                                               | 7   |      |     | ns    |

| CS Fall Hold Time                   | t <sub>CSH0</sub>     | SCLK rising edge to $\overline{\text{CS}}$ falling edge hold time                                | 0   |      |     | ns    |

| CS Rise Hold Time                   | t <sub>CSH1</sub>     | SCLK falling edge to $\overline{\text{CS}}$ rising edge hold time                                | 3   |      |     | ns    |

| CS Pulse-Width High                 | tcsw                  | Minimum CS pulse-width high                                                                      | 150 |      |     | ns    |

| SDI Setup Time                      | t <sub>DS</sub>       | SDI setup time to SCLK rising edge                                                               | 5   |      |     | ns    |

| SDI Hold Time                       | t <sub>DH</sub>       | SDI hold time after SCLK rising edge                                                             | 5   |      |     | ns    |

| SDO Transition Time                 | <sup>t</sup> DOT      | SDO transition valid after SCLK falling edge                                                     |     |      | 20  | ns    |

| SDO Hold Time                       | t <sub>DOH</sub>      | Output remains valid after falling edge of SCLK                                                  | 2   |      |     | ns    |

| SDO Disable Time                    | t <sub>DOD</sub>      | CS rising edge to SDO disable, C <sub>LOAD</sub> = 20pF                                          |     |      | 25  | ns    |

Note 1: Limits are 100% tested at  $T_A$  = +25°C, unless otherwise noted. Limits over the operating temperature range and relevant supply-voltage range are guaranteed by design and characterization.

- **Note 2:** Offset error, gain error, INL error, TUE, and settling times are only guaranteed in the linear range. The minimum and maximum specification of the linear range are guaranteed through offset, gain, INL error, and TUE.

- Note 3: Guaranteed by design and characterization. Not tested in production.

- Note 4: FSR stands for full-scale range. It is 25V in single-ended mode and 50V in differential mode.

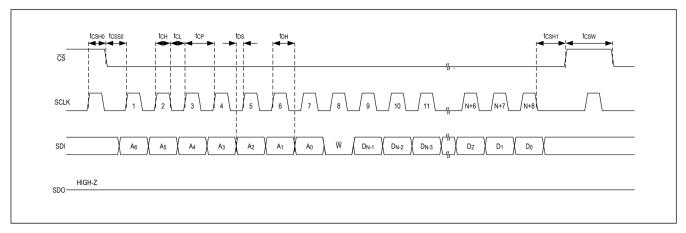

#### 図1. SPI書込みタイミング(CRC無効時はN = 24、CRC有効時はN = 32)

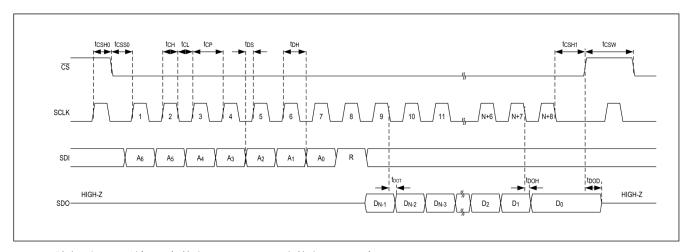

図2. SPI読出しタイミング(CRC無効時はN = 24、CRC有効時はN = 32)

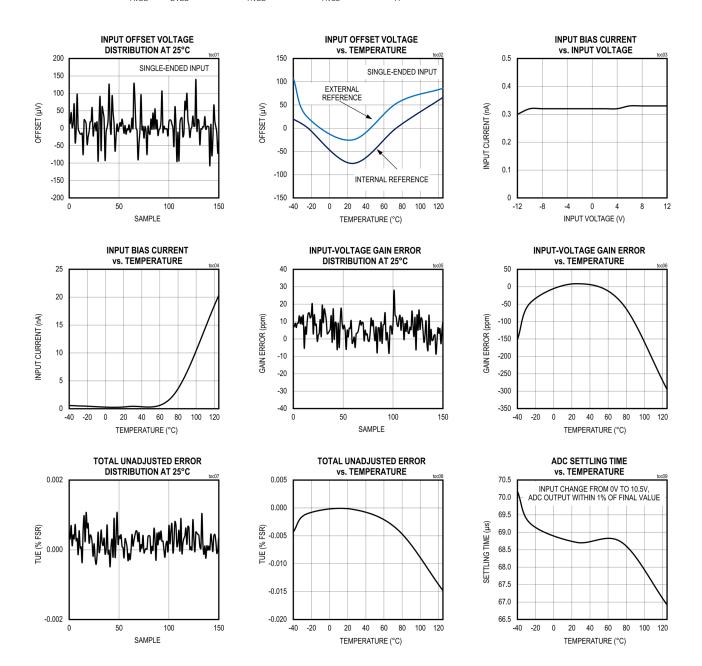

## 標準動作特性

(特に指定のない限り、 $V_{AVDD} = V_{DVDD} = +3.3V$ 、 $V_{HVDD} = +15V$ 、 $V_{HVSS} = -15V$ 、 $V_{A} = +25$ °C。)

## 標準動作特性(続き)

(特に指定のない限り、 $V_{AVDD} = V_{DVDD} = +3.3V$ 、 $V_{HVDD} = +15V$ 、 $V_{HVSS} = -15V$ 、 $V_{A} = +25$ °C。)

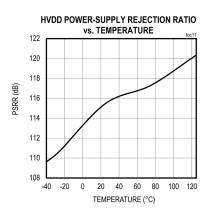

## ピン配置

#### MAX22005

## 端子説明

| 端子     | 名称  | 説明      |

|--------|-----|---------|

| アナログ入力 |     |         |

| 1      | Al8 | アナログ入力8 |

| 2      | AI7 | アナログ入力7 |

| 3      | Al6 | アナログ入力6 |

## 端子説明(続き)

| 端子             | 名称              | 説明                                                                                                                                    |

|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 4              | Al5             | アナログ入力5                                                                                                                               |

| 5              | Al4             | アナログ入力4                                                                                                                               |

| 6              | Al3             | アナログ入力3                                                                                                                               |

| 7              | Al2             | アナログ入力2                                                                                                                               |

| 8              | Al1             | アナログ入力1                                                                                                                               |

| 45             | Al12            | アナログ入力12                                                                                                                              |

| 46             | Al11            | アナログ入力11                                                                                                                              |

| 47             | Al10            | アナログ入力10                                                                                                                              |

| 48             | Al9             | アナログ入力9                                                                                                                               |

| 電源             |                 |                                                                                                                                       |

| 9              | HVDD            | 入力パス用の正側高電圧電源、+5V~+24V。HVDDは、1µFのコンデンサを介してAGNDにバイパスします。                                                                               |

| 10             | HVSS            | 入力パス用の負側高電圧電源、-5V~-24V。HVSSは1µFのコンデンサを介してAGNDにバイパスします。                                                                                |

| 11, 13, 29     | AGND            | アナログ・グランド。すべてのAGNDピンを相互に接続します。                                                                                                        |

| 12, 30         | AVDD            | アナログ電源、2.7V~3.6V。すべてのAVDDを相互に接続します。各AVDDは、 $1\mu$ Fのセラミック・コンデンサを介してAGNDにバイパスします。                                                      |

| 21, 31         | DVDD            | デジタル電源、2.7V~3.6V。すべてのDVDDを相互に接続します。各DVDDピンは、1µFのセラミック・コンデンサを介してDGNDにバイパスします。                                                          |

| 24             | DGND            | デジタル・グランド                                                                                                                             |

| リファレンスおよ       | びインターフェ         | ース                                                                                                                                    |

| 14             | NR              | 電圧リファレンスのノイズ除去。広帯域ノイズを抑制するには、NRを1µFのセラミック・コンデンサを介してAGNDにバイパスします。                                                                      |

| 15, 16, 27, 28 | I.C.            | 内部で接続。適切な使い方のためにはAGNDに接続します。                                                                                                          |

| 17             | REF_<br>ADC_EXT | ADCの外部電圧リファレンス入力。使用しない場合はAGNDに接続します。                                                                                                  |

| 18             | REF_OUT         | 電圧リファレンス出力。REF_OUTは、(0.1µF    1µF)のセラミック・コンデンサを介してAGNDにバイパ<br>スします。                                                                   |

| 19             | REF_ADC         | ADCの電圧リファレンス・バッファ付き出力。REF_ADCは、4.7µFのセラミック・コンデンサを介して<br>AGNDにバイパスします。                                                                 |

| 20             | SYNC            | ADC同期入力。SYNCはADCのモジュレータおよびデジタル・フィルタをリセットします。複数の<br>MAX22005のSYNCを並列に接続すると、それらのADCを外部トリガおよび外部クロックに同期でき<br>ます。SYNCを使用しない場合は、DGNDに接続します。 |

| 22             | BYP_ADC         | 1.8Vのサブレギュレータ出力。BYP_ADCは、220nF以上のコンデンサを介してDGNDにバイパスします。                                                                               |

| 23             | RST             | アクティブ・ローのリセット入力。通常動作では、RSTをハイに保持します。                                                                                                  |

| 25             | CLK             | 外部クロック入力。使用しない場合はDGNDに接続します。                                                                                                          |

| 26             | RDY             | アクティブ・ローのデータ・レディ出力。新たなADC変換結果がデータ・レジスタで利用可能になると、RDYはローになります。1つの出力ワードの読出し動作がすべて完了すると、RDYはハイに戻ります。RDYは常に駆動されています。                       |

| 32             | CS              | アクティブ・ローのSPIチップ・セレクト入力                                                                                                                |

| 33             | SCLK            | SPIシリアル・クロック入力                                                                                                                        |

| 34             | SDO             | SPIシリアル・データ出力                                                                                                                         |

| 35             | SDI             | SPIシリアル・データ入力                                                                                                                         |

| 36             | ĪNT             | 割込み出力。INTはオープン・ドレインのアクティブ・ロー出力です。                                                                                                     |

# 端子説明(続き)

| 端子      | 名称    | 説明      |

|---------|-------|---------|

| GPIOポート |       |         |

| 37      | GPIO0 | 汎用I/O 0 |

| 38      | GPIO1 | 汎用I/O 1 |

| 39      | GPIO2 | 汎用I/O 2 |

| 40      | GPIO3 | 汎用I/O 3 |

| 41      | GPIO4 | 汎用I/O 4 |

| 42      | GPIO5 | 汎用I/O 5 |

| 43      | GPIO6 | 汎用I/O 6 |

| 44      | GPIO7 | 汎用I/O 7 |

#### 詳細

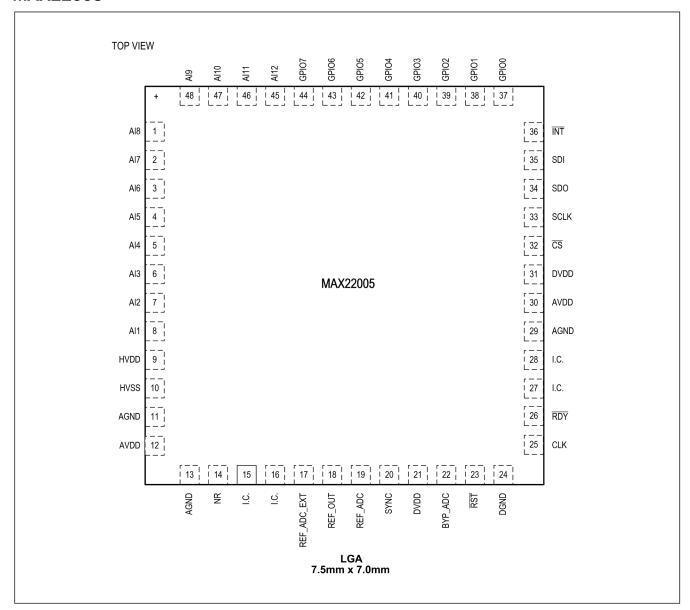

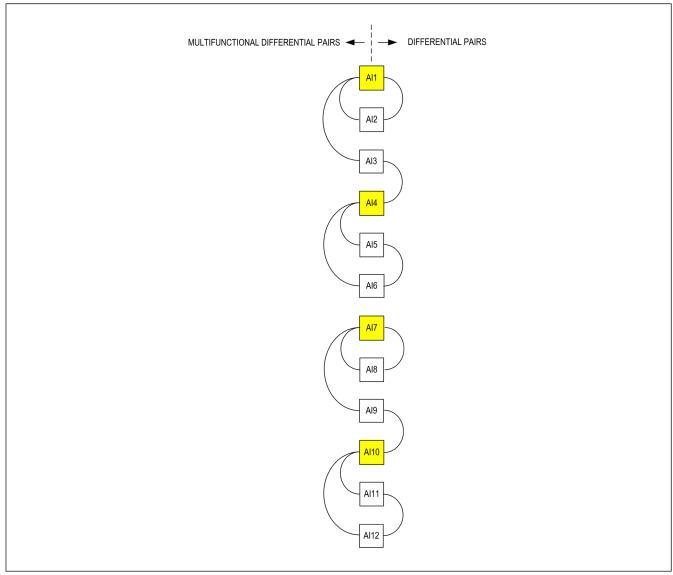

MAX22005は、工業用グレードの設定可能なアナログ入力ソリューションです。MAX22005では、12個のシングルエンド入力、6ペアの隣接した差動入力、あるいは4つの入力トリプレットを基準に定義される8個の多機能差動ペアとして利用できます。入力トリプレットを図3に示します。ポートINAが「コモン」入力となり、INCと中間ポートのINBが、入力トリプレットを定義するその他の2つのポートとなります。

ポートのペアリング方法を図4に図解します。黄色で強調表示された入力がコモン入力(COM)です。

MAX22005は、受信パス内に高性能24ビット・デルタシグマADCを備えています。ADCの後段にある高性能デシメーション・フィルタは、選択されたADCデータレートにおいて、50Hz/60Hzを87dB以上で除去します。このデバイスには、5ppm/°C(最大)の高性能電圧リファレンスが内蔵されています。しかし、外部リファレンスを用いることもできます。

図3. 入力ポートのトリプレット

図4. 入力ポートのペア

#### 動作モード

MAX22005には以下の動作モードがあります。

- 12個のシングルエンド・アナログ入力

- 6個の差動アナログ入力

- 8個の多機能差動アナログ入力

これらのモードを切り替える際に、プリント基板を変更する必要はありません。入力は、アナログ入力電圧モード (AIVM) またはアナログ入力電流モード (AICM) に設定できます。MAX22005による電流測定では、外付けの高精度抵抗を利用して電流を電圧に変換します。電流測定を行う場合は、任意の奇数チャンネル入力と対応するセンス・ポートを使用できます。内蔵のGPIOポートは、外部アナログ・スイッチを制御し、電流センス抵抗を電気的に接続または切断できます(図3参照)。電流測定は差動で行われるため、外部スイッチに高い精度は必要ありません。 $2.5\Omega$ の低電圧CMOSスイッチを推奨します。

MAX22005は、すべてのシングルエンド入力および差動入力に対して、2線式構成をサポートしています。また、多機能差動入力では3線式構成をサポートしており、これは例えば測温抵抗体(RTD)の接続に使用できます。その他の構成オプションについてはAN7413を参照してください。

#### 入力レンジ設定

最高精度を維持するため、MAX22005は入力に対して複数の電圧レンジを備えています。

表1に使用可能なレンジをまとめています。公称レンジは、対象アプリケーションに応じたレンジを仕様規定します。リニア・レンジは公称レンジを含み、ゲイン誤差、オフセット誤差、INL、PSRR、CMRRなどの性能仕様が確保されています。更に広いフルスケール・レンジは、データ・コンバータの変換制限値を設定します。この拡張レンジは、ADCにクリッピングが生じることなく変換できる入力電圧の上限を定義します。

MAX22005では、リニア・レンジを公称レンジの105%、フルスケール・レンジを公称レンジの125%に設定しています。例えば、公称レンジが±10Vの場合、MAX22005のリニア・レンジは±10.5V、フルスケール・レンジは±12.5Vとなります。

#### 表1. 入力レンジ

| MODE | SETTING | NOMINAL | LINEAR | FULL SCALE |

|------|---------|---------|--------|------------|

| AIVM | ±12.5V  | ±10V    | ±10.5V | ±12.5V     |

| AICM | ±25mA   | ±20mA   | ±21mA  | ±25mA      |

#### 差動入力同相電圧範囲

信号の振幅が入力のフルスケール・レンジ未満の場合、MAX22005はより大きな入力同相電圧範囲を許容します。 許容される最大入力同相電圧範囲は、次式で計算できます。

$V_{CM} = 25 - V_{DIFF}$

ここで、

V<sub>CM</sub> = 最大入力同相電圧範囲

$V_{DIFF} = ピークtoピーク入力電圧$

#### 入力電圧定格

すべての高電圧アナログ入力は、AGNDを基準として±36Vの耐性があります。一般的なアナログ入力での挙動は<u>図5</u>に図示します。すべてのアナログ入力は、5kΩの保護抵抗を直列接続する必要があります。HVSSおよびHVDDでの電源電圧がアクティブに駆動されている限り、MAX22005の入力ピン電圧は、HVDDをダイオード電圧降下分だけ上回ることも、HVSSをダイオード電圧降下分だけ下回ることもありません。直列抵抗が電流を制限するため、ダイオードの電圧降下はわずかです。

DC/DCコンバータの1つが正常に機能せず、電流のシンクもソースもできなくなった場合でも、そのDC/DCコンバータ周辺の抵抗性帰還回路を用いることで、MAX22005の入力ピンを効果的に保護できます。エンジニアは、MAX22005のアナログ入力ピン電圧が定格を超えないように、電流経路の総抵抗R<sub>PATH</sub>を設計する責任があります。

図5. 入力保護

#### 電源電圧および電源投入シーケンス

MAX22005には3つの独立した電源があります。低電圧アナログ電源 (AVDD、AGND)、低電圧デジタル電源 (DVDD、DGND) (どちらも2.7V~3.6Vで仕様規定されています)、およびアナログ・バイポーラ高電圧電源 (入力AFE用の HVDD、HVSS) です。高電圧AFEが適切に動作するためには、 $V_{HVSS}$ 電源は-5V未満、 $V_{HVDD}$ 電源は5V以上である必要があります。±12Vの入力の場合、少なくとも、 $V_{HVSS}$ =-15V、かつ $V_{HVDD}$ =15Vが必要です。3つの電源ペア (AVDD/AGND、DVDD/DGND、HVDD/HVSS) は任意の順序でパワーアップできます。

#### パワーオン・リセット

AVDD電源とDVDD電源は、パワーオン・リセット回路でモニタされています。MAX22005は、AVDD電源およびDVDD電源が、データを失うことなく安全に動作できる特定のスレッショルドに達するまで、リセット状態に保持されます。ひとたびこのスレッショルドを超えると、SPIインターフェースおよび低電圧回路が完全に動作します。高電圧電源も常にモニタされています。MAX22005がSPIインターフェースを介して通信するために必要なのは、AVDD電源とDVDD電源のみです。AVDDおよびDVDDに給電されている状態で高電圧電源が失われた場合、その状態は、GEN\_INTレジスタのHVDD\_INTビットを通じてレポートされます。

#### SPIインターフェース

SPIインターフェースを用いると、マイクロプロセッサとMAX22005の間であらゆる重要な情報を通信できます。オプションの CRCを使うと、MAX22005との間でやりとりされるデータの信頼性が向上します。この機能は、ハードウェア・リセット後やパワーアップ後はデフォルトで無効化されていますが(ただしソフトウェア・リセット後は除く)、SPIインターフェースを通じていつでも有効化や無効化ができます。

CRCが有効化されている場合、 $\underline{82}$ に示すように、SPIトランザクションは40ビット長です。CRCが無効化されている場合、 $\underline{83}$ に示すようにSPIトランザクションは32ビット長です。

#### 表2. CRC有効時のSPIトランザクション

| BITS 39:33       | BIT 32 | BITS 31:8      | BITS 7:0 |

|------------------|--------|----------------|----------|

| Register Address | R/W    | 24-bit Payload | CRC      |

#### 表3. CRC無効時のSPIトランザクション

| BITS 31:25       | BIT 24           | BITS 23:0      |

|------------------|------------------|----------------|

| Register Address | $R/\overline{W}$ | 24-bit Payload |

MAX22005は、0x31多項式( $x^8 + x^5 + x^4 + x^0$ )を用いたCRC-8アルゴリズムを実装しています。この多項式は、アナログ・デバイセズの1-wire\*製品で用いられているものと同じです。このCRCアルゴリズムは、反射入力バイトと反射出力バイトを用います(つまり、バイト単位でMSBファーストではなくLSBファーストで処理します。入力シーケンスのバイト順は変更されません)。初期値は0x00で、出力はXOR処理を行わずにそのままレポートされます。

このCRCは以下のタイプのエラーを検出できます。

- 32ビット内の任意の奇数個のエラー

- 32ビット内のすべてのダブルビット・エラー

- 8ビットのウィンドウ内に含まれる可能性のあるエラーのクラスタ(1ビット~8ビットが誤り)

- 大きなエラー・クラスタの大半

書込みトランザクションの場合、CRCは直前の32ビットに対して計算されます。つまり、7ビットのレジスタ・アドレス、1ビットの読出しまたは書込み制御、24ビットのペイロードです。

書込み動作の2つの例を以下に示します。

OxOO OFOOをGEN CHNL CTRLレジスタに書き込む: 0xO6 000F 0011

0x34\_0000をCHNL\_CMDレジスタに書き込む:0x40 3400 00A0

読出しトランザクションでは、MAX22005がホストに返すCRCは、ホストから送られた8ビット・ヘッダ(レジスタ・アドレスおよび読出し制御)と24ビットのペイロードで構成される32ビットに基づいて計算されます。

読出し動作の2つの例を以下に示します。

デフォルト値をGEN CNFGレジスタから読み出す:0x05 1000 00CB

デフォルト値をDCHNL STAレジスタから読み出す:0x43 0000 08AA

CRCはデフォルトでは無効化されています。詳細については、AN27を参照してください。

#### ウォッチドッグ・タイマ

MAX22005は、ホスト・コントローラとの通信が途絶した場合の安全性を高めるため、ウォッチドッグ・タイマ機能を備えています。ウォッチドッグを有効化するには、GEN\_CNFG(0x02)のTMOUT\_ENビットをセットし、TMOUT\_CNFGビットとTMOUT\_SEL[3:0]ビットに必要な割込み動作とタイムアウト時間を設定します。正しくフォーマットされた2つのSPIトランザクション間の時間がタイムアウト時間を超えると、INTピンおよびGEN\_INTレジスタ(0x07)のTMOUT\_INTビットに割込みがアサートされます。正しくフォーマットされたトランザクションとは、32ビット以上(CRCが無効化されている場合)、または40ビット以上(CRCが有効化されている場合)のトランザクションです。トランザクションが正しくフォーマットされているかどうかは、常にトランザクションの最後で判断されます。詳細については、レジスタ・マップの説明を参照してください。

#### 製品追跡

MAX22005には、32ビット幅の固有のシリアル番号があり、デバイス追跡に使用できます(GEN\_PRODレジスタおよびGEN\_REVレジスタのSERIAL[32:0])。

更に、工業用I/Oファミリの他の製品と区別するための8ビットの製品IDもあります(GEN\_PRODレジスタのPROD\_ID[7:0])。 製品IDは以下のようにデコードできます。

#### 表4. 製品ID

| BIT 7                     | 6 | 5 | 4 | 3            | 2           | 1 | 0              |

|---------------------------|---|---|---|--------------|-------------|---|----------------|

| Number of output Channels |   |   | ١ | Number of In | put Channel | S | RTD/TC Support |

MAX22005は、最大12入力チャンネルに対応しており、製品IDは0x18です。

シリコンのリビジョンは、8ビットのリビジョンID(GEN\_REVレジスタのREV\_ID[7:0])に反映されます。

#### アナログ入力ADC

アナログ入力チャンネルは、1つの高性能24ビット・デルタシグマ・アナログ・デジタル・コンバータ(ADC)を共有しています。 データレートは、1sps(サンプル/秒)~115.2kspsの範囲でプログラマブルです。ADCは、2.5Vの内部リファレンスまたは

外部リファレンスを利用できます。ADCは、合計26の入力設定が可能であり、これらはGEN\_CHNL\_CTRLのAI\_DCHNL\_SEL[4:0]ビットで選択できます。 $\underline{85}$ に、チャンネル選択オプションをまとめます。

#### 表5. 入力チャンネル設定の選択

| AI_DCHNL_SEL[4:0] | INPUT CONFIGURATION                                                                 |

|-------------------|-------------------------------------------------------------------------------------|

| 00000             | Input AI1 in single-ended mode (-12.5V to +12.5V range)                             |

| 00001             | Input Al2 in single-ended mode (-12.5V to +12.5V range)                             |

| 00010             | Input Al3 in single-ended mode (-12.5V to +12.5V range)                             |

| 00011             | Input Al4 in single-ended mode (-12.5V to +12.5V range)                             |

| 00100             | Input AI5 in single-ended mode (-12.5V to +12.5V range)                             |

| 00101             | Input Al6 in single-ended mode (-12.5V to +12.5V range)                             |

| 00110             | Input AI7 in single-ended mode (-12.5V to +12.5V range)                             |

| 00111             | Input Al8 in single-ended mode (-12.5V to +12.5V range)                             |

| 01000             | Input Al9 in single-ended mode (-12.5V to +12.5V range)                             |

| 01001             | Input AI10 in single-ended mode (-12.5V to +12.5V range)                            |

| 01010             | Input AI11 in single-ended mode (-12.5V to +12.5V range)                            |

| 01011             | Input AI12 in single-ended mode (-12.5V to +12.5V range)                            |

| 01100             | Inputs Al1–Al2 in differential mode (-25.0V to +25.0V range)                        |

| 01101             | Inputs Al3–Al4 in differential mode (-25.0V to +25.0V range)                        |

| 01110             | Inputs Al5–Al6 in differential mode (-25.0V to +25.0V range)                        |

| 01111             | Inputs AI7–AI8 in differential mode (-25.0V to +25.0V range)                        |

| 10000             | Inputs Al9–Al10 in differential mode (-25.0V to +25.0V range)                       |

| 10001             | Inputs Al11–Al12 in differential mode (-25.0V to +25.0V range)                      |

| 10010             | Inputs Al1(COM)–Al2 in multifunctional differential mode (-25.0V to +25.0V range)   |

| 10011             | Inputs Al1(COM)–Al3 in multifunctional differential mode (-25.0V to +25.0V range)   |

| 10100             | Inputs Al4(COM)–Al5 in multifunctional differential mode (-25.0V to +25.0V range)   |

| 10101             | Inputs Al4(COM)–Al6 in multifunctional differential mode (-25.0V to +25.0V range)   |

| 10110             | Inputs AI7(COM)–AI8 in multifunctional differential mode (-25.0V to +25.0V range)   |

| 10111             | Inputs AI7(COM)–AI9 in multifunctional differential mode (-25.0V to +25.0V range)   |

| 11000             | Inputs Al10(COM)–Al11 in multifunctional differential mode (-25.0V to +25.0V range) |

| 11001             | Inputs Al10(COM)–Al12 in multifunctional differential mode (-25.0V to +25.0V range) |

ADCの結果は、DCHNL\_DATAレジスタに2の補数フォーマットで格納されます。 $\underline{86}$ に、ADCの出力コードと対応する入力電圧をまとめています。

## 表6. 入力チャンネルの制限値およびコード

| AI_DCHNL_SEL[4:0] | INPUT CHANNEL    | ADC CODE<br>0x800000<br>(-8388608) (V) | ADC CODE<br>0x000000<br>(0) (V) | ADC CODE<br>0x7FFFFF<br>(+8388607) (V) |

|-------------------|------------------|----------------------------------------|---------------------------------|----------------------------------------|

| 00000             | Al1 single-ended | -12.5                                  | 0                               | +12.5                                  |

| 00001             | Al2 single-ended | -12.5                                  | 0                               | +12.5                                  |

| 00010             | Al3 single-ended | -12.5                                  | 0                               | +12.5                                  |

| 00011             | Al4 single-ended | -12.5                                  | 0                               | +12.5                                  |

| 00100             | AI5 single-ended | -12.5                                  | 0                               | +12.5                                  |

| 00101             | Al6 single-ended | -12.5                                  | 0                               | +12.5                                  |

| 00110             | AI7 single-ended | -12.5                                  | 0                               | +12.5                                  |

#### 表6. 入力チャンネルの制限値およびコード(続き)

| AI_DCHNL_SEL[4:0] | INPUT CHANNEL                               | ADC CODE<br>0x800000<br>(-8388608) (V) | ADC CODE<br>0x000000<br>(0) (V) | ADC CODE<br>0x7FFFFF<br>(+8388607) (V) |

|-------------------|---------------------------------------------|----------------------------------------|---------------------------------|----------------------------------------|

| 00111             | Al8 single-ended                            | -12.5                                  | 0                               | +12.5                                  |

| 01000             | Al9 single-ended                            | -12.5                                  | 0                               | +12.5                                  |

| 01001             | Al10 single-ended                           | -12.5                                  | 0                               | +12.5                                  |

| 01010             | Al11 single-ended                           | -12.5                                  | 0                               | +12.5                                  |

| 01011             | Al12 single-ended                           | -12.5                                  | 0                               | +12.5                                  |

| 01100             | AI1–AI2 differential                        | -25.0                                  | 0                               | +25.0                                  |

| 01101             | Al3–Al4 differential                        | -25.0                                  | 0                               | +25.0                                  |

| 01110             | Al5–Al6 differential                        | -25.0                                  | 0                               | +25.0                                  |

| 01111             | AI7–AI8 differential                        | -25.0                                  | 0                               | +25.0                                  |

| 10000             | Al9-Al10 differential                       | -25.0                                  | 0                               | +25.0                                  |

| 10001             | AI11–AI12 differential                      | -25.0                                  | 0                               | +25.0                                  |

| 10010             | AI1(COM)–AI2 multifunctional differential   | -25.0                                  | 0                               | +25.0                                  |

| 10011             | AI1(COM)–AI3 multifunctional differential   | -25.0                                  | 0                               | +25.0                                  |

| 10100             | Al4(COM)–Al5 multifunctional differential   | -25.0                                  | 0                               | +25.0                                  |

| 10101             | Al4(COM)–Al6 multifunctional differential   | -25.0                                  | 0                               | +25.0                                  |

| 10110             | AI7(COM)–AI8 multifunctional differential   | -25.0                                  | 0                               | +25.0                                  |

| 10111             | AI7(COM)-AI9 multifunctional differential   | -25.0                                  | 0                               | +25.0                                  |

| 11000             | AI10(COM)–AI11 multifunctional differential | -25.0                                  | 0                               | +25.0                                  |

| 11001             | AI10(COM)–AI12 multifunctional differential | -25.0                                  | 0                               | +25.0                                  |

動作モードは、DCHNL\_CMDレジスタのDCHNL\_MODE[1:0]ビットを用いて選択できます。デフォルトでは、ADCはスタンバイ・モードになっており、全体の消費電力を低減します。

デルタシグマ・モジュレータの次段には高性能デジタル・フィルタが続き、これは、選択したデータレートに応じて、5次のSINCフィルタ、平均化フィルタ、4次のSINCフィルタで構成されます。一部のデータレートでは、50Hzまたは60Hzを75dB以上抑圧できます。

ADCは、連続モード、シングルサイクル・モード、連続シングルサイクル・モードの3つの変換動作モードが可能です。

連続モードでは、ADCは、選択したサンプル・レートで連続的に動作します。データレートに応じて、デジタル・フィルタが安定するまで、最大5つの出力サンプルが必要です。このモードを使用するのは、単一チャンネルからデータを収集し、高サンプル・レートが必要な場合です。

**シングルサイクル・モード**は、レイテンシのない変換をシングルサイクルで実行し、その後ADCはスタンバイ・モードに戻ります。 このモードを使用するのは、複数のチャンネルで単発測定を行い、中程度のサンプル・レートが必要な場合です。

連続シングルサイクル・モードでは、ADCは選択したレートでレイテンシのない変換を連続的に実行します。このモードを使用するのは、1チャンネルを連続的にモニタリングする必要があるものの、デジタル・フィルタのセトリングをマスクしたい場合です。これは、入力の変化後に高速セトリングが必要ながらも、連続モードのようにデータレートを増やす必要がない場合に有用です。

動作モードは、DCHNL\_CTRL1レジスタのSCYCLEビットおよびCONTSCビットで選択できます。連続モードおよび連続シングルサイクル・モードは、DCHNL\_CMDレジスタのDCHNL\_MODE[1:0]ビットをスタンバイ・モードに変更すると終了します。 更に、入力チャンネルの選択を変更すると(GEN\_CHNL\_CTRLレジスタのAI\_DCHNL\_SEL[4:0]ビット)、ADCのコントロール・レジスタ(DCHNL\_CTRL1、DCHNL\_CTRL2)も進行中の連続変換をアボートし、ADCをスタンバイ・モードに戻します。

使用可能なデータレートは、DCHNL\_CMDレジスタのDCHNL\_RATE[3:0]ビットを設定することで選択できます。<u>表7</u>に、連続モードで使用可能なデータレートをまとめています。太字のデータレートは、50Hz/60Hz抑圧特性が75dBを超えています。なお、最大データレートではシステム・キャリブレーションによる補正は選択できません。

表7. 連続変換におけるデータレートの選択

| DCHNL_RATE[3:0] | DATA RATE (SPS) | EFFECTIVE NUMBER OF BITS |

|-----------------|-----------------|--------------------------|

| 0000            | 5               | 21                       |

| 0001            | 10              | 21                       |

| 0010            | 15              | 21                       |

| 0011            | 30              | 20                       |

| 0100            | 50              | 20                       |

| 0101            | 60              | 20                       |

| 0110            | 225             | 19                       |

| 0111            | 450             | 19                       |

| 1000            | 900             | 19                       |

| 1001            | 1800            | 18                       |

| 1010            | 3600            | 18                       |

| 1011            | 7200            | 18                       |

| 1100            | 14400           | 17                       |

| 1101            | 28800           | 17                       |

| 1110            | 57600           | 17                       |

| 1111            | 115200 (Note)   | 16                       |

注:最大データレートでは、システム・キャリブレーションはサポートされていません。

表8に、シングルサイクル・モードで使用可能なデータレートを示します。シングルサイクル・モードでの動作では、ADCのアナログ・フロントエンドが安定できるように、変換開始時にオーバーヘッドが必要です。加えて、生のモジュレータ出力を処理する時間も必要です。表8に示す公称データレートは、入力信号のサンプリング周期を示す目安となります。実際のデータレートは、システム・キャリブレーションを用いるかどうかによって異なります。これは、計算のオーバーヘッドがこの2つの場合で異なるためです。太字のデータレートは、50Hz/60Hz抑圧特性が75dBを超えています。

表8. シングルサイクル変換におけるデータレートの選択

| DCHNL_RATE[3:0] | NOMINAL DATA<br>RATE (sps) | ACTUAL DATA<br>RATE (sps) | ACTUAL DATA RATE PLUS SYSTEM CALIBRATION (sps) | EFFECTIVE<br>NUMBER OF BITS |

|-----------------|----------------------------|---------------------------|------------------------------------------------|-----------------------------|

| 0000            | 1 (0.9955)                 | 1 (0.9955)                | 1 (0.9955)                                     | 21                          |

| 0001            | 2.5                        | 2.5                       | 2.5                                            | 21                          |

| 0010            | 5                          | 5                         | 5                                              | 21                          |

| 0011            | 10                         | 10                        | 10                                             | 20                          |

| 0100            | 12.5                       | 12.5                      | 12.5                                           | 20                          |

| 0101            | 15                         | 15                        | 15                                             | 20                          |

| 0110            | 50                         | 50                        | 50                                             | 19                          |

| 0111            | 60                         | 60                        | 60                                             | 19                          |

| 1000            | 150                        | 150                       | 150                                            | 19                          |

| 1001            | 300                        | 299                       | 298                                            | 18                          |

| 1010            | 900                        | 891                       | 886                                            | 18                          |

| 1011            | 1800                       | 1772                      | 1752                                           | 18                          |

| 1100            | 2880                       | 2810                      | 2759                                           | 17                          |

| 1101            | 5760                       | 5486                      | 5297                                           | 17                          |

| 1110            | 11520                      | 10473                     | 9804                                           | 17                          |

| 1111            | 23040                      | 19200                     | 17067                                          | 16                          |

表9に、シングルサイクル連続モードで使用可能なデータレートを示します。シングルサイクル連続モードの動作は、シングルサイクル・モードと類似していますが、オーバーヘッドがわずかに異なるため、実際のデータレートもわずかに異なります。太字で示したデータレートは、50Hz/60Hzに対して75dBを超える抑圧特性を有します。

#### 表9. シングルサイクル連続変換におけるデータレートの選択

| DCHNL_RATE[3:0] | NOMINAL DATA<br>RATE (sps) | ACTUAL DATA<br>RATE (sps) | ACTUAL DATA RATE PLUS SYSTEM CALIBRATION (sps) | EFFECTIVE<br>NUMBER OF BITS |

|-----------------|----------------------------|---------------------------|------------------------------------------------|-----------------------------|

| 0000            | 1 (0.9955)                 | 1 (0.9955)                | 1 (0.9955)                                     | 21                          |

| 0001            | 2.5                        | 2.5                       | 2.5                                            | 21                          |

| 0010            | 5                          | 5                         | 5                                              | 21                          |

| 0011            | 10                         | 10                        | 10                                             | 20                          |

| 0100            | 12.5                       | 12.5                      | 12.5                                           | 20                          |

| 0101            | 15                         | 15                        | 15                                             | 20                          |

| 0110            | 50                         | 50                        | 50                                             | 19                          |

| 0111            | 60                         | 60                        | 60                                             | 19                          |

| 1000            | 150                        | 150                       | 150                                            | 19                          |

| 1001            | 300                        | 299                       | 299                                            | 18                          |

| 1010            | 900                        | 892                       | 887                                            | 18                          |

| 1011            | 1800                       | 1776                      | 1755                                           | 18                          |

| 1100            | 2880                       | 2818                      | 2768                                           | 17                          |

| 1101            | 5760                       | 5519                      | 5327                                           | 17                          |

| 1110            | 11520                      | 10593                     | 9910                                           | 17                          |

| 1111            | 23040                      | 19609                     | 17389                                          | 16                          |

ADCは、オーバーレンジ状態を通知するステータス・ビットを備えています。デジタル・フィルタの出力がオーバーフローすると、DCHNL\_STAレジスタのDORビットがロジック・ハイに設定されます。このときデジタル出力は、正のオーバーフローの場合は0x7FFFFF、負のオーバーフローの場合は0x800000に設定されます。

#### アナログ入力のオフセット誤差およびゲイン誤差のキャリブレーション

#### システム・キャリブレーション

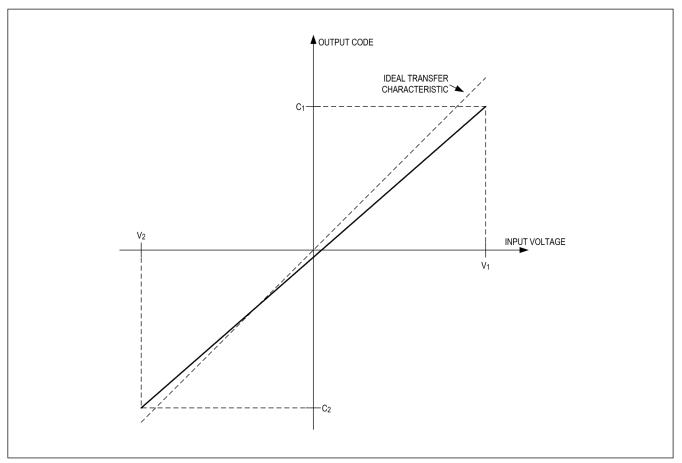

MAX22005は、そのTUE仕様を満たすように、工場出荷時にキャリブレーションされています。ただし、ユーザが独自のシステム・レベル・キャリブレーションを行えば、ボード・レベルの部品を含むアナログ入力シグナル・チェーン全体のゲイン誤差およびオフセット誤差を補正できます。2点測定アルゴリズムを使用することで、システム・レベルのオフセット誤差とゲイン誤差を計算し、補正できます。MAX22005では、26通りの入力設定それぞれに対し、オフセット補正レジスタとゲイン補正レジスタのペアが個別に用意されています。ゲイン係数とオフセット係数を計算するための2点キャリブレーションを図6に示します。詳細については、AN7449「MAX22005 User Calibration Guide」を参照してください。

ユーザ/システム・キャリブレーションを行う前に、各チャンネルのオフセット・キャリブレーション・レジスタ(DCHNL\_N\_SOC)を0x00\_0000に、ゲイン・キャリブレーション・レジスタ(DCHNL\_N\_SGC)を0xC0\_0000に設定する必要があります。

次に、アプリケーションのフルスケール・レンジに近い2つの入力電圧 $V_1$ および $V_2$ を印加し、それぞれに対応するデジタル出力コード $C_1$ および $C_2$ を記録します。

図6. 2点システム・キャリブレーション

入力チャンネルのゲインAは次式で計算できます。

$$A = \frac{(\frac{C_1 - C_2}{2^{24}}) \times V_{FSR}}{(V_1 - V_2)}$$

ここで、 $V_{FSR}$ は、選択した入力チャンネルのフルスケール・レンジを表します。各チャンネルのフルスケール・レンジを $\underline{810}$ に示します。

## 表10. 入力チャンネルのフルスケール・レンジ

| AI_DCHNL_SEL[4:0] | INPUT CHANNEL    | FULL_SCALE<br>RANGE V <sub>FSR</sub><br>(V) | DIGITAL GAIN<br>A <sub>DIG</sub> | DIGITAL SIGN<br>S <sub>DIG</sub> |

|-------------------|------------------|---------------------------------------------|----------------------------------|----------------------------------|

| 00000             | Al1 single-ended | 25                                          | 2                                | +1                               |

| 00001             | Al2 single-ended | 25                                          | 2                                | -1                               |

| 00010             | Al3 single-ended | 25                                          | 2                                | -1                               |

| 00011             | Al4 single-ended | 25                                          | 2                                | +1                               |

| 00100             | Al5 single-ended | 25                                          | 2                                | +1                               |

| 00101             | Al6 single-ended | 25                                          | 2                                | -1                               |

#### 表10. 入力チャンネルのフルスケール・レンジ(続き)

| 00110 | AI7 single-ended                            | 25 | 2 | +1 |

|-------|---------------------------------------------|----|---|----|

| 00111 | Al8 single-ended                            | 25 | 2 | -1 |

| 01000 | Al9 single-ended                            | 25 | 2 | -1 |

| 01001 | Al10 single-ended                           | 25 | 2 | +1 |

| 01010 | Al11 single-ended                           | 25 | 2 | +1 |

| 01011 | Al12 single-ended                           | 25 | 2 | -1 |

| 01100 | Al1–Al2 differential                        | 50 | 2 | +1 |

| 01101 | Al3–Al4 differential                        | 50 | 2 | -1 |

| 01110 | AI5-AI6 differential                        | 50 | 2 | +1 |

| 01111 | AI7-AI8 differential                        | 50 | 2 | +1 |

| 10000 | Al9–Al10 differential                       | 50 | 2 | -1 |

| 10001 | AI11-AI12 differential                      | 50 | 2 | +1 |

| 10010 | AI1(COM)–AI2 multifunctional differential   | 50 | 2 | +1 |

| 10011 | AI1(COM)–AI3 multifunctional differential   | 50 | 2 | +1 |

| 10100 | AI4(COM)–AI5 multifunctional differential   | 50 | 2 | +1 |

| 10101 | Al4(COM)–Al6 multifunctional differential   | 50 | 2 | +1 |

| 10110 | AI7(COM)–AI8 multifunctional differential   | 50 | 2 | +1 |

| 10111 | AI7(COM)–AI9 multifunctional differential   | 50 | 2 | +1 |

| 11000 | Al10(COM)–Al11 multifunctional differential | 50 | 2 | +1 |

| 11001 | Al10(COM)–Al12 multifunctional differential | 50 | 2 | +1 |

ゲイン・キャリブレーション係数は、デフォルトのゲイン・キャリブレーション係数を、計算で求めたゲインで割ることで算出できます。

ゲイン・キャリブレーション係数 = 1.5/A

この結果は、23ビットのフラクション長を持つ符号なし2進数フォーマットで表現され、対応するDCHNL\_N\_SGCレジスタにロードされます。

入力換算オフセットは次のように計算できます。

$$V_{\mathsf{OFFSET}} = \frac{C_1 \times V_{\mathsf{FSR}}}{2^{24}} - A \times V_1$$

オフセット・キャリブレーション係数を計算する際には、シグナル・チェーンのデジタル・ゲイン $A_{DIG}$ と符号 $S_{DIG}$ を考慮する必要があります。ゲインおよび符号の両方を表9にまとめています。この情報を基に、オフセット・キャリブレーション係数DCHNL\_N\_SOCは次のように計算できます。

DCHNL\_N\_SOC =

$$\left(C_1 - A \times \frac{V_1}{V_{\text{FSR}}} \times 2^{24}\right) \times \frac{S_{\text{DIG}}}{1.5 \times A_{\text{DIG}}}$$

その結果得られたDCHNL\_N\_SOCの値は、2の補数フォーマットで表す必要があります。

計算したキャリブレーション係数は、それぞれオフセット用はDCHNL\_N\_SOCレジスタ、ゲイン用はDCHNL\_N\_SGCに格納されます。これらのレジスタは、間接アドレス指定によって選択できます(DCHNL\_N\_SELレジスタを参照)。

デフォルトでは、生のADC出力データは、システムのゲインおよびオフセット・キャリブレーション係数を用いて補正されます。しかし、この補正は、DCHNL\_CTRL2レジスタのNOSYSGビットとNOSYSOビットを用いて無効化できます。

#### ADCソフトウェア・リセット

ホストは、ソフトウェア・リセットを実行してADCをデフォルト状態に復元できます。ソフトウェア・リセットでは、DCHNL\_レジスタがそれぞれデフォルト状態に戻され、内部のステート・マシンもリセットされます。ただし、ソフトウェア・リセットは、完全なパワーオン・リセットやハードウェア・リセットのシーケンスを実行するものではありません。したがって、例えばSPIインターフェースが応答しない場合などにはソフトウェア・リセットは有効ではありません。

ソフトウェア・リセットを発行するには2回のSPIトランザクションが必要です。まず、DCHNL\_CTRL1レジスタのDCHNL\_PD ビットをロジック・ハイ (リセット) にセットします。次に、DCHNL\_CMDレジスタに対して書込みトランザクションを発行し、DCHNL\_MODE[1:0]を「01」に設定します。

リセット動作の完了を確認するには、DCHNL\_STAレジスタのPDSTAT[1:0]ビットをモニタします。ADCがリセット・フェーズ中は、PDSTAT[1:0]が「11」(リセット)に設定されています。リセット動作が完了すると、PDSTAT[1:0]は「10」(スタンバイ)に設定されます。通常はリセット(「11」)状態をモニタする必要はありません。スタンバイ・モード(「10」)をポーリングするだけで十分です。

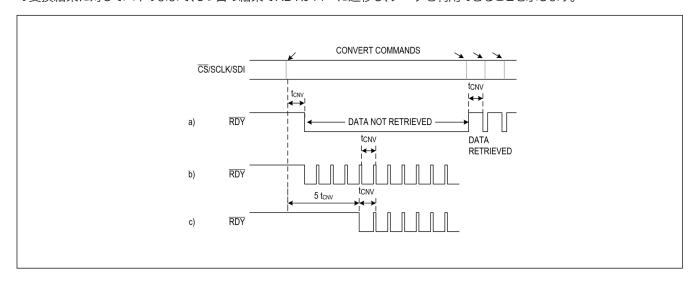

#### ADC RDY (データ・レディ)出力

RDYは、ADCの変換ステータスを示し、変換結果を利用可能かどうかを示します。RDYがローの場合、変換結果を利用できます。RDYがハイの場合は変換が進行中で、その変換はまだ利用できません。DCHNL\_DATAレジスタの読出しが完了すると、RDYはハイに駆動されます。各サンプルが利用可能になるたびにデータを読み出す場合、RDYは出力データレートに合わせてハイからローに遷移します。以前のデータが読み出されていない場合、RDYはローからハイに遷移し、その約0.5µs後に新しいデータが利用可能になります。その後、RDYの立下がりエッジが新しいデータを利用できることを示します。連続モードでは、RDYは最初の4つの変換結果に対してハイのままで、5つ目の結果でRDYがローに遷移し、データを利用できることを示します。

図7. RDYの出力タイミング、a) シングルサイクル・モード、b) 連続シングルサイクル・モード、c) 連続変換モード

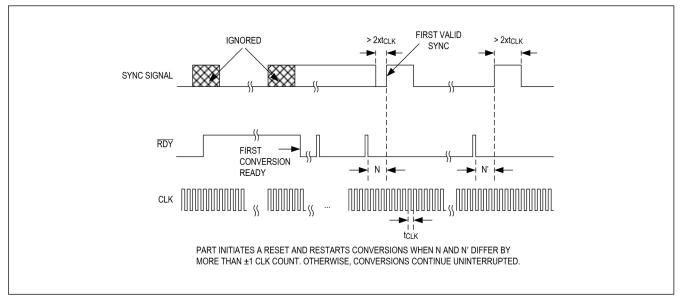

#### SYNCピンを用いたADC変換の同期

MAX22005は、高安定の内部発振器を内蔵しており、公称7.3728MHz (8.192MHz × 0.9)のシステム・クロックを生成し、アナログ・タイミングとデジタル・タイミングの両方に供給します。必要に応じて、高安定の外部クロックを用いることもできます。SYNCピンは、理想的には外部クロックと併用され、これを用いてデータ変換を外部イベントに同期させることができます。この同期方法は内部クロックでも機能しますが、局部発振器の周波数精度に限界があるため、必然的に再同期が必要です。複数のMAX22005で高安定の外部クロックを共用すれば、再同期を行う必要がなく、はるかに長いタイム・インターバルが可能となります。

DCHNL\_CTRL2レジスタのSYNC\_MODEビットをロジック・ハイにセットすると、外部同期モードを有効化できます。また、SYNC\_MODEは、連続変換モードでのみ動作するため、DCHNL\_CTRL1レジスタのSCYCLEをロジック・ゼロにセットする必要があります。必要に応じて、DCHNL\_CTRL2レジスタのEXTCLKビットをロジック・ハイにセットし、高精度の外部クロック信号を用いることもできます。

この同期モードは、現在の変換がデータレートより長い周期の連続パルス信号に同期しているかどうかを検出するために使用されます。同期パルスの立上がりエッジのみがタイミング・リファレンスとして用いられるため、同期信号のパルス幅は重要ではありません。ただし、パルス幅は内部クロック・ソースを用いる場合は300nsより長く、外部クロック・ソースを用いる場合は200nsより長くする必要があります。更に、連続するSYNCパルスの間のSYNC信号のロー時間も、内部クロック・ソースを用いる場合は300nsより長く、外部クロック・ソースを用いる場合はクロック周期の2倍より長くする必要があります。理想的には、同期信号の周波数は変換レートの整数倍です。同期モードは、RDYの立下がりエッジから次のSYNCパルスの立上がりエッジまでのADCクロック・サイクル数を記録します。その後のSYNCパルスにおいて、RDYの立下がりエッジからSYNCパルスの立上がりエッジまでのADCクロック・サイクル数が再度評価され、記録された値と比較されます。新しいADCクロック・サイクル数が、記録された値と比べて1を超えて異なる場合、進行中の変換は停止され、デジタル・フィルタの内容がリセットされて新しい変換が開始されます。デジタル・フィルタがリセットされるため、有効な結果が利用可能となるまでには、デジタル・フィルタの全レイテンシ分の時間が必要です。新しいADCクロック・カウントが±1のカウント制限内に収まっている場合は、変換は中断されずに継続されます。

図8に、MAX22005のADCクロックとSYNC信号のタイミング関係を示します。スタートアップ遅延のため、RDYの最初の立下がりエッジより前のSYNCパルスは無視されます。RDYの立下がりエッジの後に続く最初のSYNCピンの立上がりエッジによって、SYNC信号と変換タイミングの関係が確立します。

図8. SYNC入力タイミング

#### ハードウェア・リセット

MAX22005は、ハードウェア・リセットを実行するためのアクティブ・ローのRSTピンを備えています。RSTピンをローにプルダウンすると、すべてのレジスタがパワーオン・リセット状態に再設定されます。アナログ入力は切断されます。進行中のADC変換は停止され、デジタル・フィルタもリセットされます。RSTがロジック「1」に戻ると、デバイスは電源が最初に投入されたときと同じ動作をします。

## レジスタ・マップ

## MAX22005のレジスタ・マップ

| ADDRESS    | NAME                                | MSB            |                 |                |                   |            |                |                 | LSB           |

|------------|-------------------------------------|----------------|-----------------|----------------|-------------------|------------|----------------|-----------------|---------------|

| GEN Regist | ters                                |                |                 |                |                   |            |                |                 |               |

|            | GEN_PROD[23:16]                     |                |                 |                | PROD              | _ID[7:0]   |                |                 |               |

| 0x00       | GEN_PROD[15:8]                      |                |                 |                | SERIAL_I          | MSB[15:8]  |                |                 |               |

|            | GEN_PROD[7:0]                       |                | SERIAL_MSB[7:0] |                |                   |            |                |                 |               |

|            | GEN_REV[23:16]                      |                |                 |                | REV_              | ID[7:0]    |                |                 |               |

| 0x01       | GEN_REV[15:8]                       |                |                 |                | SERIAL_           | LSB[15:8]  |                |                 |               |

|            | GEN_REV[7:0]                        |                |                 |                | SERIAL_           | _LSB[7:0]  |                |                 |               |

|            | GEN_CNFG[23:16]                     | CRC_EN         | _               | ADCREF<br>_SEL | _                 | _          | -              | _               | -             |

| 0x02       | <u>GEN_CNFG[15:8]</u>               | -              | _               | _              | -                 | _          | _              | _               | -             |

|            | GEN_CNFG[7:0]                       | -              | _               | TMOUT_<br>EN   | TMOUT_<br>CNFG    |            | TMOUT_         | _SEL[3:0]       |               |

|            | GEN_CHNL_CTRL[23:1<br>6]            | AIP_TE         | ST[1:0]         | AIN_TE         | EST[1:0]          | _          | _              | _               | _             |

| 0x03       | 0x03 GEN_CHNL_CTRL[15:8             |                | _               |                | AI_DCHNL_SEL[4:0] |            |                |                 |               |

|            | GEN_CHNL_CTRL[7:0]                  | -              | _               | _              | _                 | _          | _              | _               | _             |

|            | <u>GEN_GPIO_CTRL[23:1</u> <u>6]</u> |                |                 |                | GPIO_             | EN[7:0]    |                |                 |               |

| 0x04       | GEN_GPIO_CTRL[15:8]                 | GPIO_DIR[7:0]  |                 |                |                   |            |                |                 |               |

|            | GEN_GPIO_CTRL[7:0]                  |                |                 |                | GPO_D             | ATA[7:0]   |                |                 |               |

|            | GEN_GPI_INT[23:16]                  |                |                 | G              | PI_POS_E          | DGE_INT[7: | 0]             |                 |               |

| 0x05       | GEN_GPI_INT[15:8]                   |                |                 | G              | PI_NEG_EI         | DGE_INT[7: | 0]             |                 |               |

|            | GEN_GPI_INT[7:0]                    | -              | _               | _              | _                 | _          | _              | _               | _             |

|            | GEN_GPI_DATA[23:16]                 |                |                 |                |                   | E_INT_STA  |                |                 |               |

| 0x06       | GEN_GPI_DATA[15:8]                  |                |                 | GPI_           |                   | E_INT_STA  | [7:0]          |                 |               |

|            | GEN_GPI_DATA[7:0]                   |                |                 |                | GPI_DA            | ATA[7:0]   |                |                 |               |

|            | GEN_INT[23:16]                      | _              | _               | _              | _                 | _          | _              | _               | _             |

| 0x07       | <u>GEN_INT[15:8]</u>                | _              | _               | _              | _                 | -          | _              | TMOUT_<br>INT   | -             |

|            | GEN_INT[7:0]                        | HVDD_I<br>NT   | _               | _              | _                 | _          | CNFG_I<br>NT   | CRC_IN<br>T     | GPI_INT       |

|            | GEN_INTEN[23:16]                    | _              | _               | _              | _                 | _          | -              | _               | ı             |

| 0x08       | GEN_INTEN[15:8]                     | _              | _               | _              | _                 | _          | _              | TMOUT_<br>INTEN | -             |

|            | GEN_INTEN[7:0]                      | HVDD_I<br>NTEN | _               | _              | _                 | _          | CNFG_I<br>NTEN | CRC_IN<br>TEN   | GPI_INT<br>EN |

| 0.00       | GEN_PWR_CTRL[23:1<br>6]             | _              | _               | _              | _                 | GEN_PD     | _              | GEN_RS<br>T     | _             |

| 0x09       | GEN_PWR_CTRL[15:8]                  | -              | _               | -              | _                 | _          | -              | -               | _             |

|            | GEN_PWR_CTRL[7:0]                   | _              | _               | _              | _                 | _          | _              | _               | _             |

| ADDRESS   | NAME               | MSB              |        |                       |              |            |            |               | LSB        |  |