### MAX17851

# SPI-UART安全監視ブリッジ

#### 概要

MAX17851SPI-UART安全監視ブリッジは、SPIフォーマットから、アナログ・デバイセズのバッテリ管理データ・アクイジション・システムとのインターフェース用に特別に設計されたユニバーサル非同期レシーバ/トランスミッタ(UART)フォーマットに通信を変換します。安全監視ブリッジは、シングルおよびデュアル・デイジーチェーン・システム・アーキテクチャにおいて、最大4Mbpsのボー・レートで堅牢な通信を可能にします。高スループットのデュアルUARTシステムは、96セルのバッテリ電圧を1173us以内に読み取ることができます。

UARTは、組み込みUART通信ロックステップ安全対策ステート・マシン(LSSM)を介した、メッセージの破損、遅延、喪失、挿入の検出を行う自動車安全水準(ASIL)Dシステム向けのISO26262に適合しています。MAX17851は、ホスト・マイクロコントローラでのソフトウェア開発を簡素化するために、メッセージ・ペイロード内の全ての通信を自己検証します。

更に、MAX17851はホスト・マイクロコントローラの通信を監視し、あらゆる障害を検出します。ホストとの通信に障害が発生した場合、MAX17851は最初に自動的に通信の回復を試みます。失敗した場合、制御を行います。その場合、MAX17851は、オプションでデイジーチェーン・ネットワークを再設定し、バッテリの状態を監視し続けることができます。これにより、安全なシステム運転を継続できます。最後に、MAX17851は、バッテリの状態が事前に設定された範囲から外れた場合、コンタクタに信号を発するため、システム全体がフェールセーフ状態になります。

### アプリケーション

- バッテリ管理システム(BMS)

- 電気自動車およびハイブリッド電気自動車(EV/HEV)

- エネルギー貯蔵システム(ESS)

### 利点と特長

- アナログ・デバイセズのバッテリ管理UARTプロトコル に対応

- ASIL D機能安全要件に対応

- ・ 簡素化されたホスト・レポート機能を備える、自動化 されたオン・チップ通信検証

- フォルトの種類および位置に対する常時オンのデイジーチェーン・フォルト・ポーリング

- 冗長デイジーチェーン・コントローラを備える内蔵システム・ウォッチドッグ

- プログラマブルなシステム回復

- ・ デイジーチェーン構成用のプログラマブルなメモリ

- プログラマブルなコンタクタ制御

- マイクロコントローラがスリープ・モード時のセル・バランシング機能を内蔵

- プログラマブルな割込み機能を備えた安全な長期バランシング・モニタリング

- 最大4Mbpsまで設定可能なUARTボー・レート

- 最大10MHzのSPIインターフェース

- 1.71V~5.5Vで動作

- 超低自己消費電流

- 動作温度範囲:-40°C~+125°C(AEC-Q100)

型番はデータシートの最後に記載されています。

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

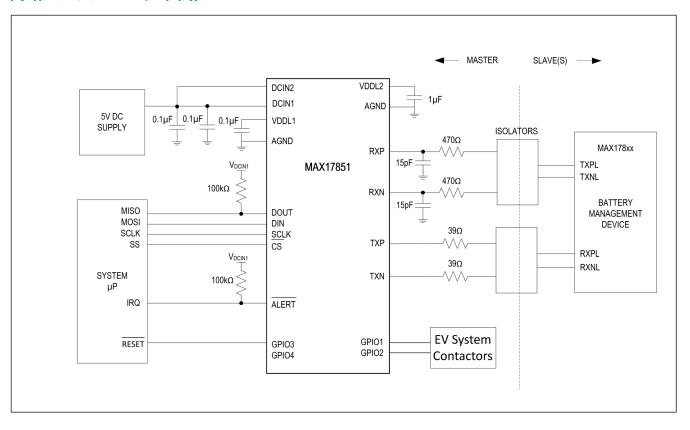

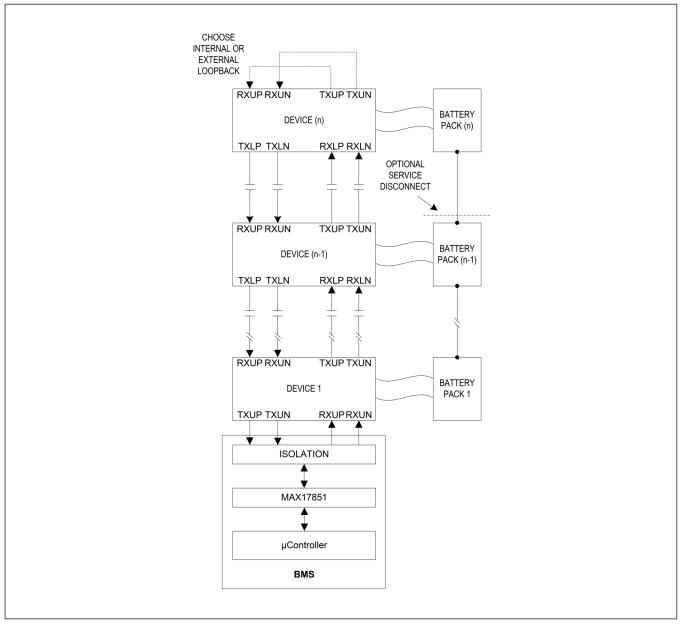

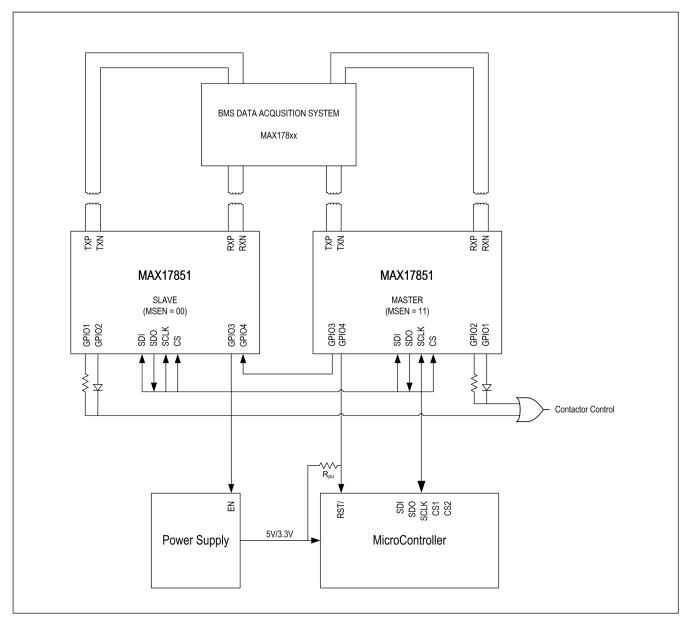

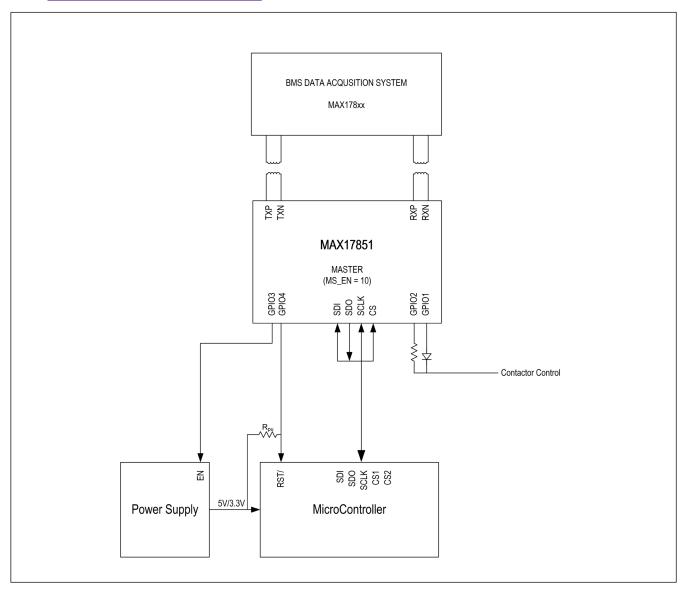

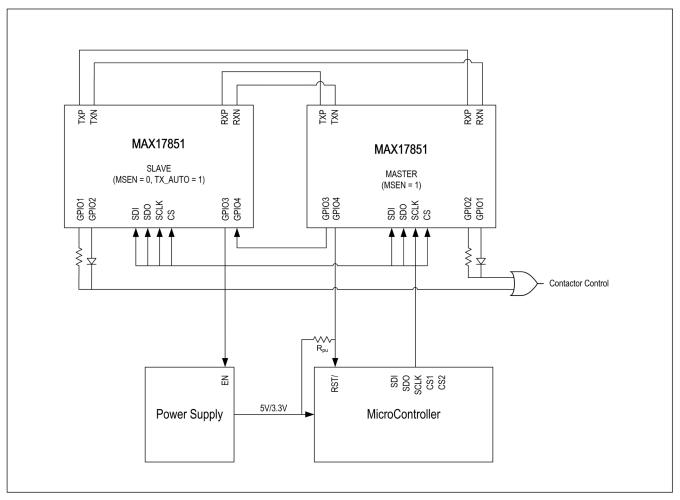

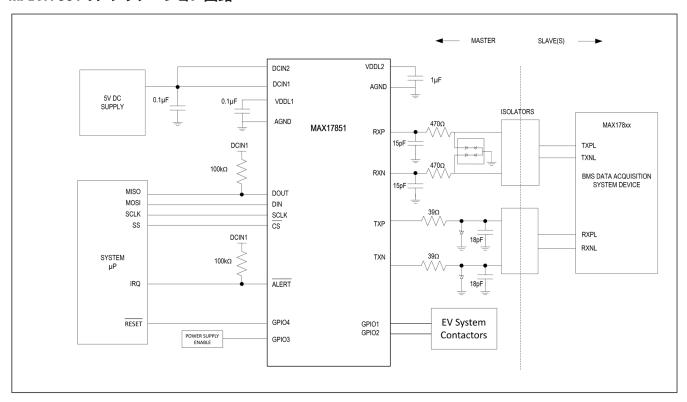

# 簡略アプリケーション回路

# 目次

| 概要                             | 1  |

|--------------------------------|----|

| アプリケーション                       |    |

| 利点と特長                          |    |

| 簡略アプリケーション回路図                  | 2  |

| 絶対最大定格                         | 8  |

| パッケージ情報                        | 8  |

| TSSOP                          | 8  |

| 電気的特性                          | 8  |

| 標準動作特性                         | 16 |

| ピン配置                           | 16 |

| MAX17851A                      | 16 |

| 端子説明                           | 17 |

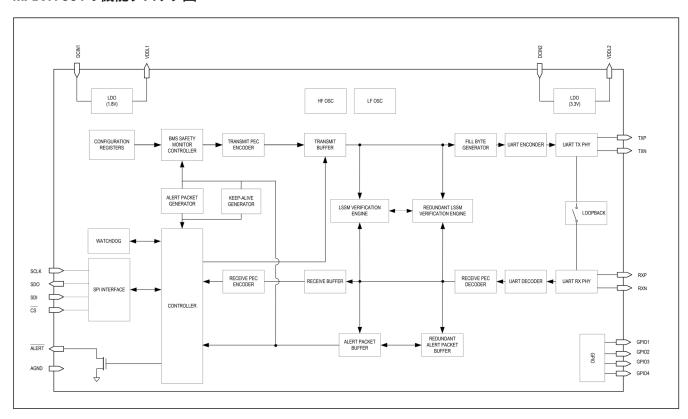

| 機能図                            | 18 |

| MAX17851の機能ブロック図               | 18 |

| 詳細説明                           | 20 |

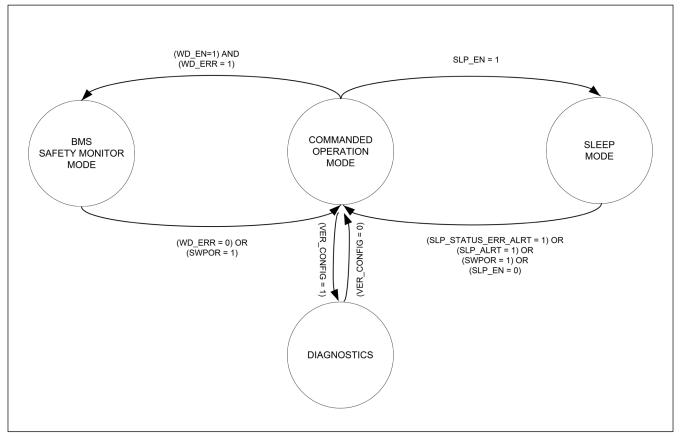

| 動作モード                          | 20 |

| コマンド動作モード                      | 21 |

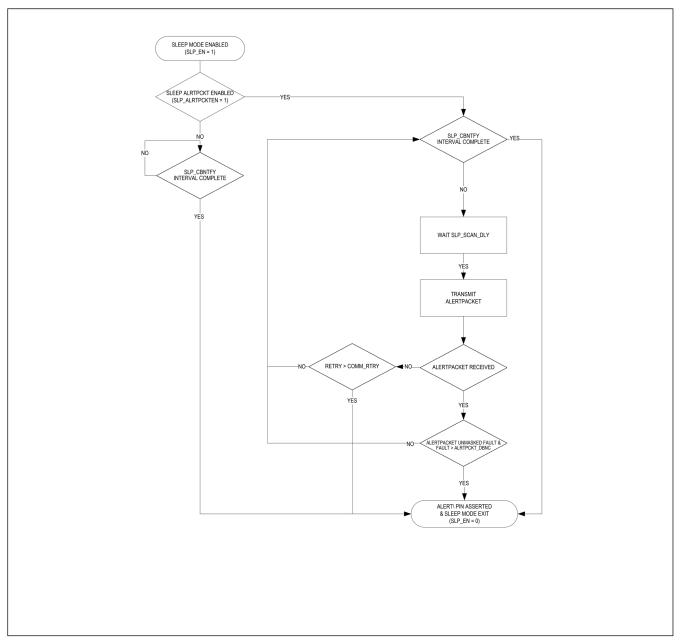

| スリープ・モード                       | 21 |

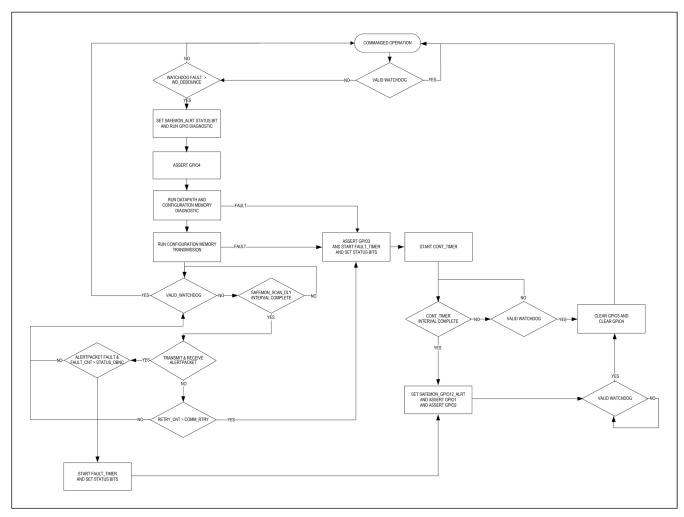

| BMS安全モニタリング・モード                | 23 |

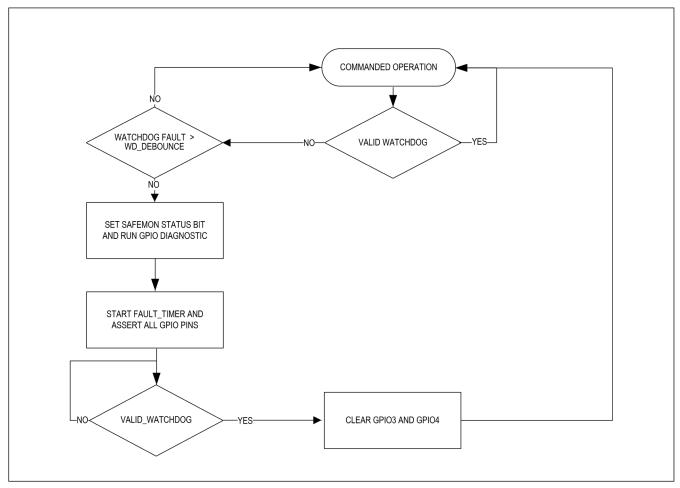

| BMS安全モニタリング・モードおよび安全対策診断状態への移行 | 24 |

| マイクロコントローラおよび電源の回復             | 25 |

| BMS安全モニタリング動作                  | 26 |

| ALERTPACKETを用いたフォルト・ポーリング      | 27 |

| BMS安全モニタリング・モードの終了             | 28 |

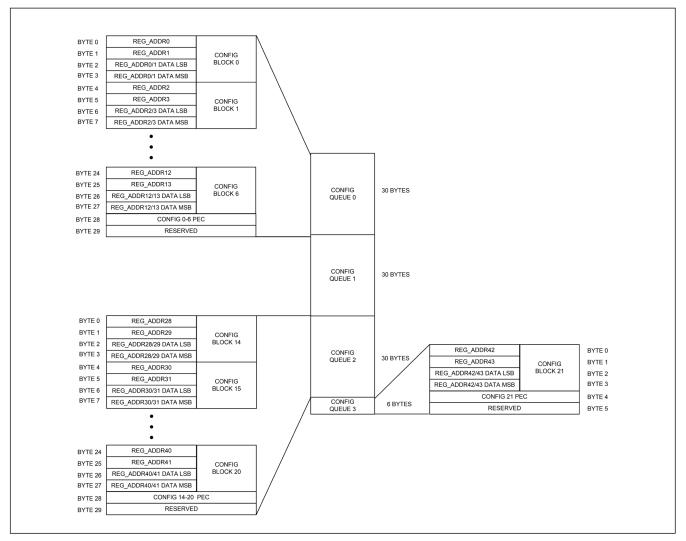

| 設定メモリ                          | 28 |

| データパスおよび設定メモリの検証               | 29 |

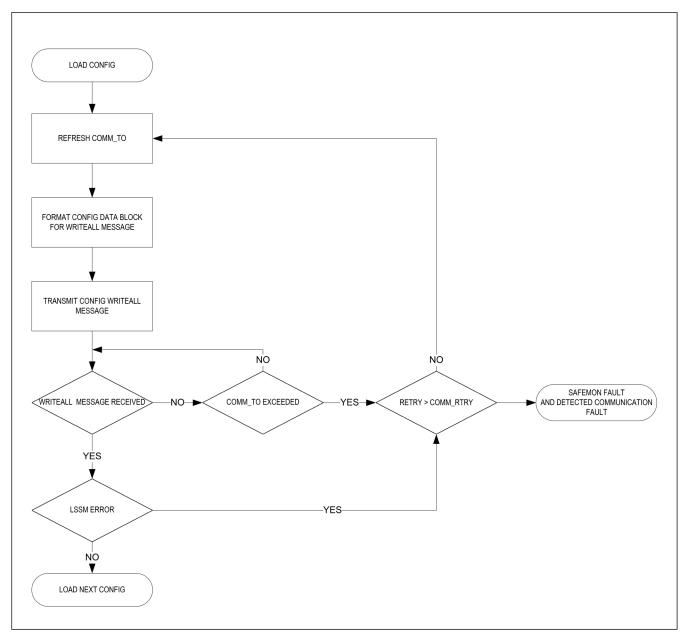

| 設定メモリの伝送                       | 30 |

| 設定メモリのセットアップ                   | 31 |

| マスタ/スレーブのデバイス設定                | 32 |

| BMS安全モニタリング・モードにおけるマスタ         | 32 |

| BMS安全モニタリング・モードにおけるスレーブ        | 32 |

| コマンド動作モードのスレーブ                 | 32 |

| スリープ・モードのスレーブ                  | 33 |

| 診断および動作の検証                     | 33 |

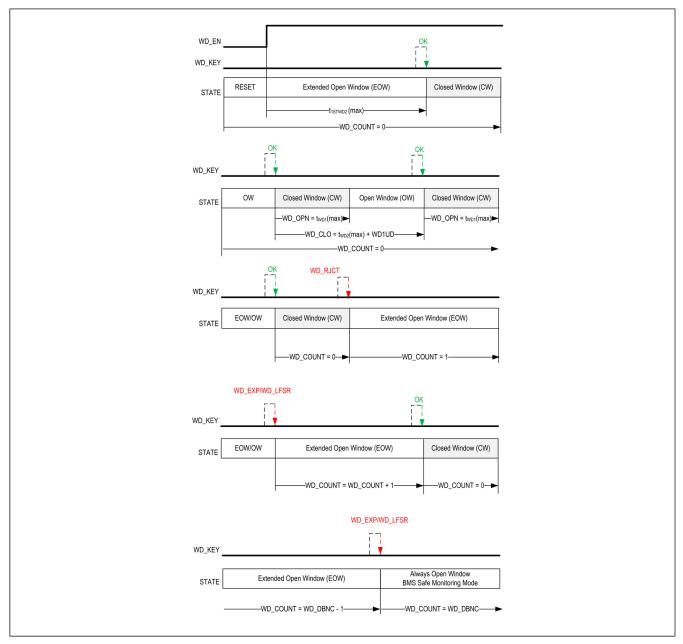

| ウォッチドッグ                        | 34 |

| チャレンジ/応答モード                    | 36 |

| 単純なウィンドウ・モード                   | 36 |

| LFSR/CRCコードの例                  | 37 |

| GPIO制御                         | 37 |

# 目次(続き)

| シリアル・ペリフェラル・インターフェース (SPI) | 38 |

|----------------------------|----|

| SPIトランザクション                | 38 |

| SPIのタイミング                  | 39 |

| SPIでの読出しと書込みに対する制限         | 40 |

| UARTインターフェース               | 40 |

| バッテリ管理UARTプロトコル            | 41 |

| UARTメッセージ                  | 42 |

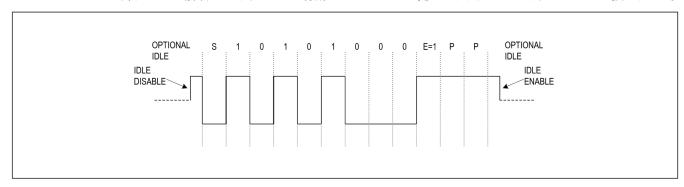

| プリアンブル・キャラクタ               | 42 |

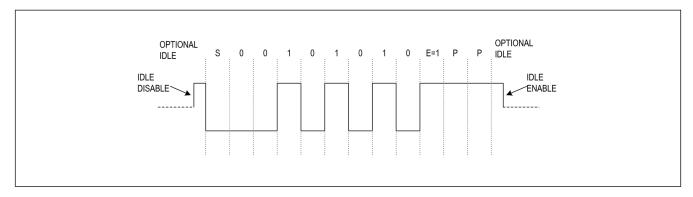

| ストップ・キャラクタ                 | 43 |

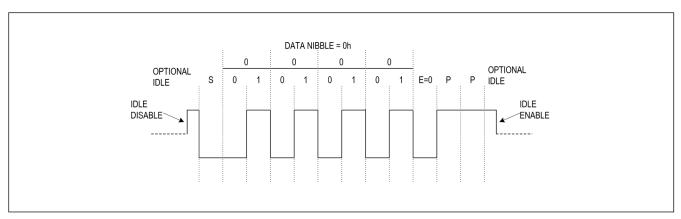

| マンチェスター・エンコーディング           | 43 |

| データ・タイプ                    | 43 |

| スレーブ・デバイス・アドレスの割り当て        | 43 |

| UARTのメッセージ・データ・タイプ         | 44 |

| 一般的なUARTコマンド               | 44 |

| UARTの動作                    | 44 |

| UARTの動作モード                 | 45 |

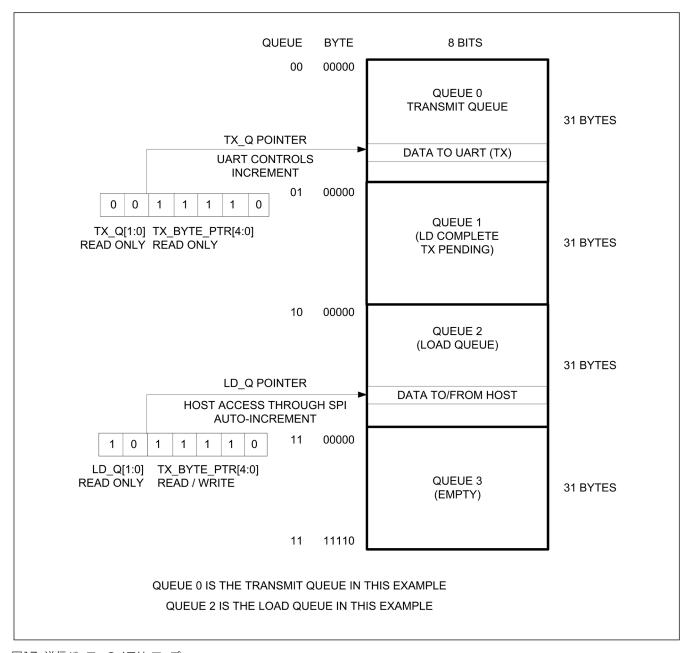

| 送信バッファ                     | 46 |

| 送信バッファのキュー                 | 47 |

| 送信バッファのクリア                 | 48 |

| メッセージ長                     | 48 |

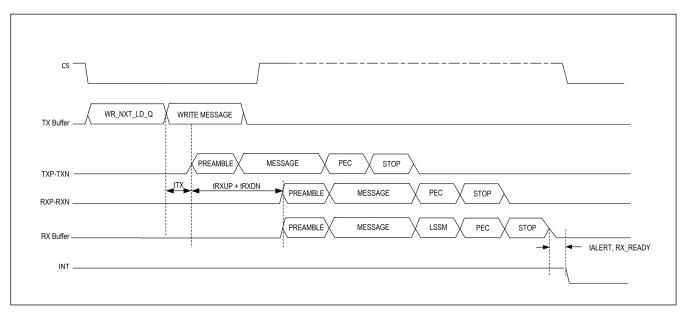

| ロード・キューの書込み                | 48 |

| 送信バッファのフィル                 | 49 |

| メッセージの送信                   | 49 |

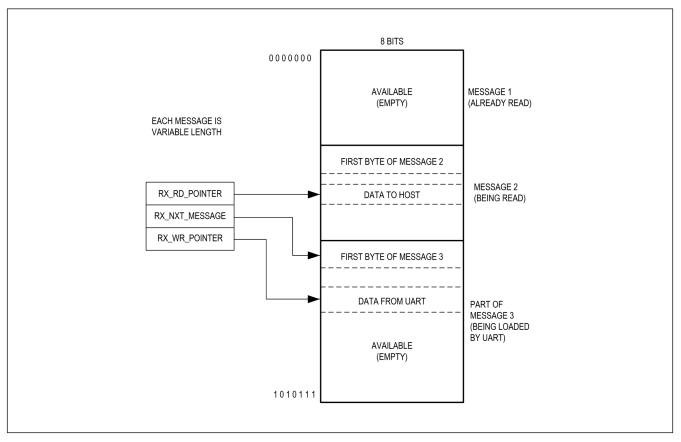

| 受信バッファ                     | 49 |

| 受信バッファのクリア                 | 50 |

| メッセージの受信                   | 51 |

| メッセージの例外                   | 51 |

| メッセージの読出し                  | 52 |

| アラート・パケット・バッファ             | 52 |

| 自動およびユーザ指定アライブ・カウンタ        | 53 |

| データチェック・パーサ                | 54 |

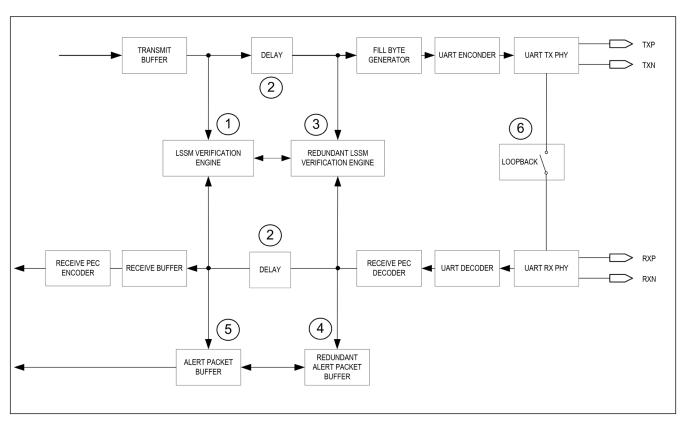

| ロックステップ安全対策の検証             | 55 |

| デュアル・ロックステップ・データパス処理       | 56 |

| アラートおよびフォルト                | 57 |

| ALERTピン、ステータス、アラート・フラグの動作  | 57 |

| フォルト・タイマー                  | 58 |

| ハードウェア・フォルトの検出             | 58 |

| レジスタ・フォルトの検出               | 58 |

| MAX17851ユーザ・レジスタ・マップ       | 58 |

# 目次(続き)

| レジスタの詳細                              | 63  |

|--------------------------------------|-----|

| アプリケーション情報                           | 120 |

| システム構成                               | 120 |

| デュアルUART動作                           | 120 |

| デュアルUART MAX17851の初期化                | 121 |

| デュアルUARTのBMSデータ・アクイジション・システムの初期化     | 124 |

| 最終的なMAX17851設定                       | 126 |

| シングルUART動作                           | 126 |

| シングルUARTのMAX17851の初期化                | 127 |

| シングルUARTのBMSデータ・アクイジション・システムの初期化     | 129 |

| 最終的なMAX17851設定                       | 130 |

| デイジーチェーン設定用の設定メモリ・シーケンス              | 131 |

| ウォッチドッグ設定                            | 135 |

| UART書込みおよび読出しのためのトランザクション・シーケンス      | 136 |

| 補助的なエラー・チェック機能                       | 137 |

| 破損したプリアンブル・キャラクタ                     | 137 |

| 破損メッセージの内容                           | 138 |

| ストップ・キャラクタの破損または喪失                   | 138 |

| 意図しないプリアンブル                          | 138 |

| 意図しないストップ・キャラクタ                      | 138 |

| フォルト処理のガイドライン                        | 138 |

| スリープ・モードの設定                          | 142 |

| TX_AUTO機能を用いたハードウェア・イン・ザ・ループ(HIL)テスト | 142 |

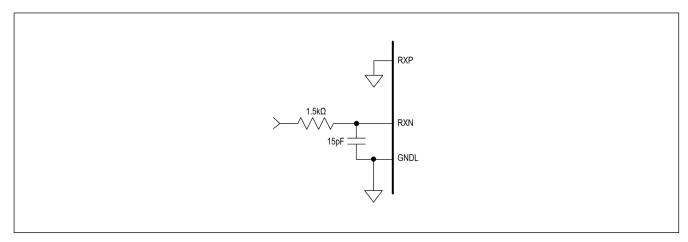

| UARTの物理レイヤ                           | 145 |

| UARTのシングルエンド・モード動作                   | 145 |

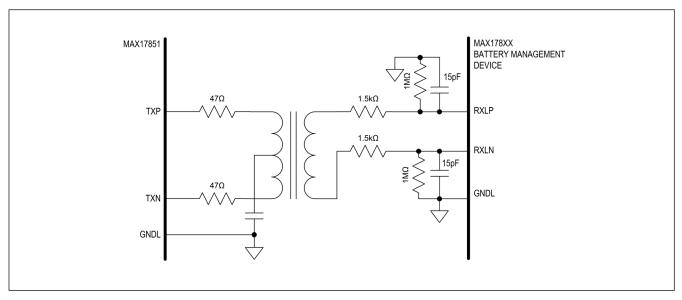

| UARTのトランス・カップリング                     | 145 |

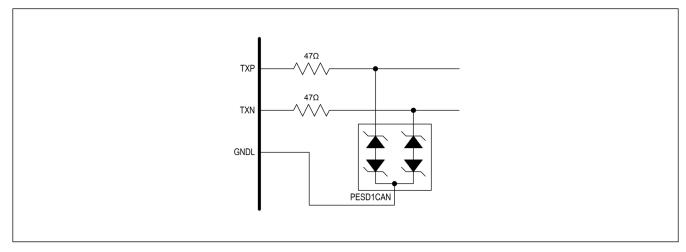

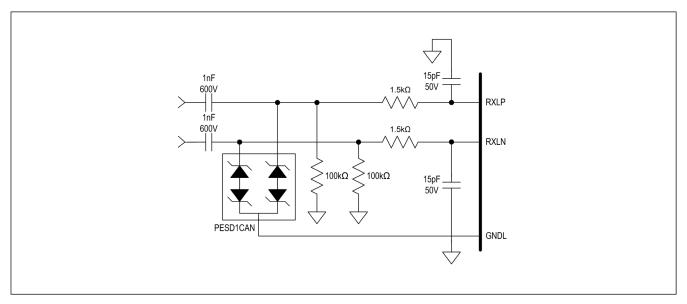

| UARTの補足的ESD保護                        | 146 |

| 電源に関する考慮事項                           | 147 |

| PCBレイアウトに関する推奨事項                     | 148 |

| レイアウト例(シルクスクリーン)                     | 149 |

| レイアウト例(金属)                           | 150 |

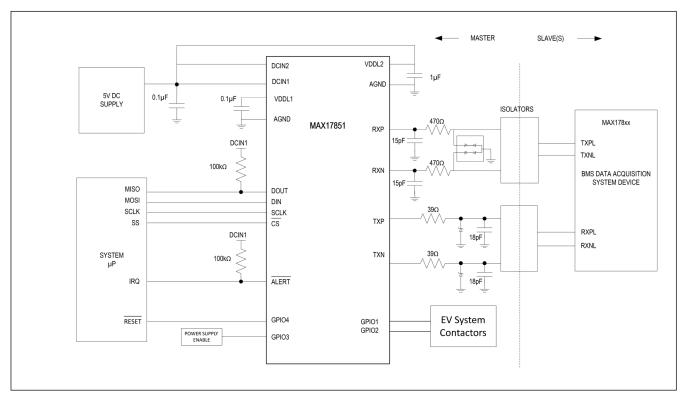

| 標準アプリケーション回路                         | 151 |

| MAX17851のアプリケーション回路                  | 151 |

| 型番                                   |     |

| 改訂履歴                                 | 152 |

|                                      |     |

# 図一覧

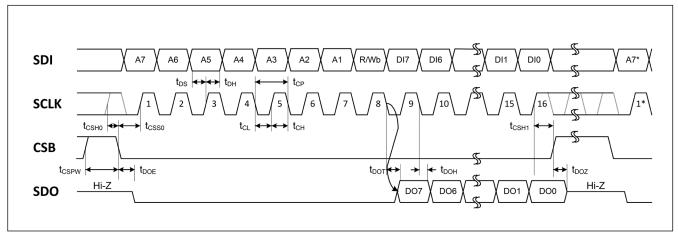

| 図1. SPIタイミング図                               | 14  |

|---------------------------------------------|-----|

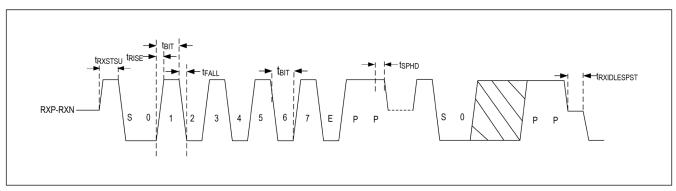

| 図2. 受信UARTのタイミング                            | 14  |

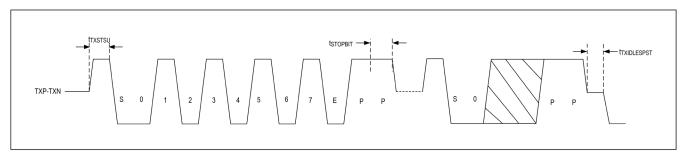

| 図3. 送信UARTのタイミング                            | 14  |

| 図4. TXバッファの書込みおよび読出し                        | 15  |

| 図5. 動作モード                                   | 21  |

| 図6. スリープ・モードの状態遷移図                          | 23  |

| 図7. BMS安全モニタリング・モードのフロー・チャート                | 24  |

| 図8. BMS安全モニタリング(NOMON)モードのフロー・チャート          | 27  |

| 図9. 設定メモリ                                   | 29  |

| 図10. 設定メモリ・データの伝送                           | 31  |

| 図11. ウォッチドッグ動作                              | 36  |

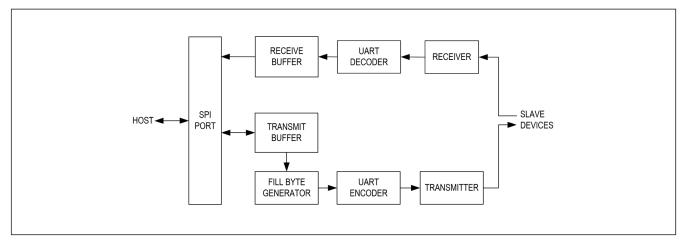

| 図12. システムのデータ・フロー                           | 41  |

| 図13. UARTでのプリアンブルのタイミング                     | 42  |

| 図14. UARTでのストップ・キャラクタのタイミング                 |     |

| 図15. UARTでのマンチェスター・エンコーディング・データ・ニブルOhのタイミング | 43  |

| 図16. UARTのデータ・フロー                           | 45  |

| 図17. 送信バッファのメモリ・マップ                         | 47  |

| 図18. 受信バッファのメモリ・マップ                         | 50  |

| 図19. LSSMのデータパス                             | 57  |

| 図20. デュアルUART                               | 121 |

| 図21. シングルUART                               | 127 |

| 図22. ハードウェア・イン・ザ・ループのテスト・セットアップ             | 143 |

| 図23. シングルエンド・モード                            | 145 |

| 図24. UART信号のトランス・カップリング                     | 146 |

| 図25. UARTトランスミットの補足的ESD保護                   | 146 |

| 図26. UARTレシーバの補足的ESD保護(容量性カップリングと共に表示)      |     |

| 図27. 電源に関する考慮事項                             | 148 |

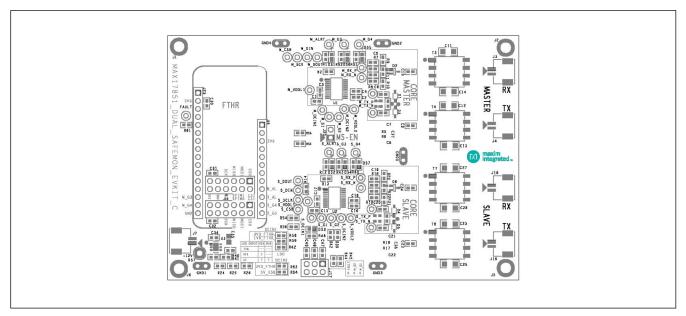

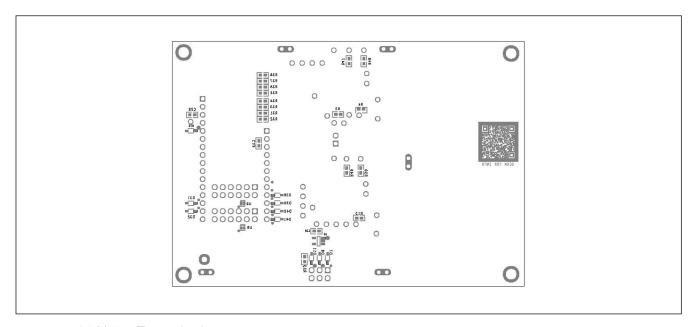

| 図28. レイアウト例:最上層のシルクスクリーン                    | 149 |

| 図29. レイアウト例:最下層のシルクスクリーン                    | 149 |

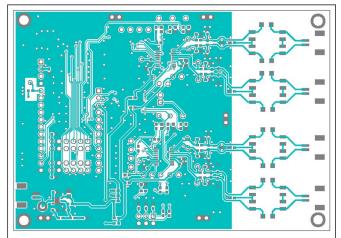

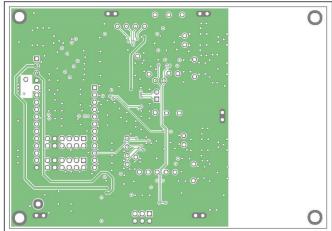

| 図30. レイアウト例:最上層の金属                          | 150 |

| 図31. レイアウト例: 2層目の金属                         | 150 |

| 図32. レイアウト例:最下層の金属                          | 150 |

| 図33 1、イアウト例:3層日の全尾                          | 150 |

# 表一覧

| 表1. MAX17851の機能ブロックに対する電力分配                       | 1.8 |

|---------------------------------------------------|-----|

| 表2. データパスおよび設定メモリの実行時間                            |     |

| 表3. 設定メモリからのWRITEALLコマンド・シーケンス                    |     |

| 表4. デュアルUART下り経路でのREADALLコマンドのシーケンス(zはデバイス数)      |     |

| 表5. GPIO制御                                        |     |

| 表6. SPIレジスタの一覧                                    |     |

| 表7. SPI通信の概要                                      |     |

| 表 7. SPI 通信の                                      |     |

|                                                   |     |

| 表9. UARTのメッセージ・データ・タイプ                            |     |

| 表10. 一般的なUARTコマンド                                 |     |

| 表11. UARTの動作モード                                   |     |

| 表12. キューのメモリ・マップ                                  |     |

| 表13. HELLOALLメッセージでロードされるキューの例                    |     |

| 表14. ユーザ指定アライブ・カウンタを伴うコマンドの伝搬(ALIVECOUNT_EN = 10) |     |

| 表15. 自動アライブ・カウンタを伴うコマンドの伝搬(ALIVECOUNT_EN = 11)    |     |

| 表16. LSSMステータス・バイトのエラー・マッピング                      | 55  |

| 表17. マスタ/スレーブ・デバイスの設定シーケンス                        | 122 |

| 表18. マスタ/スレーブのBMSデイジーチェーンの初期化シーケンス                | 124 |

| 表19. マスタ/スレーブのUARTアラート・パケット設定                     | 126 |

| 表20. シングルUARTデバイス設定シーケンス                          | 128 |

| 表21. シングルUARTのBMSデイジーチェーンの初期化シーケンス                | 129 |

| 表22. アラート・パケット設定                                  | 131 |

| 表23. 設定メモリのシーケンス                                  | 131 |

| 表24. ウォッチドッグ設定                                    | 135 |

| 表25. UART書込みおよび読出しのためのトランザクション・シーケンス              |     |

| 表26. フォルト処理のガイドライン                                |     |

| 表27 ハードウェア・イン・ザ・ループのテスト・シーケンス                     |     |

# **Absolute Maximum Ratings**

| RXP, RXN to AGND                                                         |

|--------------------------------------------------------------------------|

| Maximum Continuous Current into Any Pin20mA                              |

| Continuous Power Dissipation (Multilayer Board) (T <sub>A</sub> = +70°C) |

| 20 TSSOP (derate 11.1mW/°C above +70°C)887mW                             |

| Operating Temperature Range40°C to +125°C                                |

| Storage Temperature Range–55°C to +150°C                                 |

| Junction Temperature (Continous) +150°C                                  |

| Soldering Lead Temperature (10s)+300°C                                   |

|                                                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### **TSSOP**

| Package Code                            | U20+7C         |

|-----------------------------------------|----------------|

| Outline Number                          | <u>21-0066</u> |

| Land Pattern Number                     | 90-0116        |

| Thermal Resistance, Single-Layer Board: |                |

| Junction to Ambient (θ <sub>JA</sub> )  | 91°C/W         |

| Junction to Case (θ <sub>JC</sub> )     | 20°C/W         |

| Thermal Resistance, Four-Layer Board:   |                |

| Junction to Ambient (θ <sub>JA</sub> )  | 73.8 °C/W      |

| Junction to Case (θ <sub>JC</sub> )     | 20°C/W         |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/jp/packages">www.maximintegrated.com/jp/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/jp/thermal-tutorial">www.maximintegrated.com/jp/thermal-tutorial</a>.

### **Electrical Characteristics**

$(V_{DCIN1} > = V_{DDL1}, V_{DCIN1} < 5.5V, V_{DCIN2} > = V_{DDL2}, V_{DCIN2} < 5.5V, V_{DDL1} = 1.8V, V_{DDL2} = 3.3V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, where  $T_{MIN} = -40^{\circ}C$  and  $T_{MAX} = +125^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ . Operation is with the recommended application circuit.)

| PARAMETER                                            | SYMBOL                  | CONDITIONS                                                                                      | MIN   | TYP | MAX  | UNITS |

|------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------|-------|-----|------|-------|

| POWER REQUIREMENTS                                   |                         |                                                                                                 |       |     |      |       |

| DCIN1 Supply Voltage                                 | V=                      | V <sub>DDL1</sub> = 1.8V                                                                        | 2.375 |     | 5.5  | V     |

| DOINT Supply Voltage                                 | V <sub>DCIN1</sub>      | V <sub>DCIN1</sub> = V <sub>DDL1</sub>                                                          | 1.71  | 1.8 | 1.89 |       |

| DCIN2 Supply Voltage                                 | V=                      | V <sub>DDL2</sub> = 3.3V nominal                                                                | 4.5   |     | 5.5  | V     |

| DCINZ Supply Voltage                                 | V <sub>DCIN2</sub>      | V <sub>DCIN2</sub> = V <sub>DDL2</sub>                                                          | 3.2   |     | 5.5  |       |

| DCIN1 Static Supply<br>Current                       | IDCIN1_STATIC           | f <sub>SCLK</sub> = 0, SDO not loaded                                                           |       | 920 |      | uA    |

| Incremental DCIN1<br>Communication Supply<br>Current | I <sub>DCIN1_COMM</sub> | Continuous SPI Reads, f <sub>SCLK</sub> = 10MHz,<br>SDO loaded 20pF, <i>Note: DCIN1 Current</i> |       | 310 |      | uA    |

| DCIN2 Static Supply<br>Current                       | IDCIN2_STATIC           | UART Baud Rate = 2MHz, TXIDLEHIZ,<br>TX not active with 200pF load                              |       | 10  | 20   | uA    |

$(V_{DCIN1}>=V_{DDL1},\,V_{DCIN1}<5.5V,\,V_{DCIN2}>=V_{DDL2},\,V_{DCIN2}<5.5V,\,V_{DDL1}=1.8V,\,V_{DDL2}=3.3V,\,T_A=T_{MIN}\,\,to\,\,T_{MAX},\,\,unless\,\,otherwise\,\,noted,\,\,where\,\,T_{MIN}=-40\,^{\circ}C\,\,and\,\,T_{MAX}=+125\,^{\circ}C.\,\,Typical\,\,values\,\,are\,\,at\,\,T_A=+25\,^{\circ}C.\,\,Operation\,\,is\,\,with\,\,the\,\,recommended\,\,application\,\,circuit.)$

| PARAMETER                                            | SYMBOL                        | CONDITIONS                                                               | MIN                         | TYP | MAX                         | UNITS    |

|------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------|-----------------------------|-----|-----------------------------|----------|

| Incremental DCIN2<br>Communication Supply<br>Current | IDCIN2_COMM                   | UART Baud Rate = 2MHz, TXIDLEHIZ,<br>TXL not active with 200pF           |                             | 880 | 910                         | uA       |

| V <sub>DDL1</sub> REGULATOR                          |                               |                                                                          |                             |     |                             |          |

| Output Voltage                                       | V <sub>DDL1</sub>             | 0mA < I <sub>VDDL1</sub> < 10mA, 2.375V < V <sub>DCIN1</sub> < 5.5V      | 1.71                        | 1.8 | 1.89                        | V        |

| Short-Circuit Current                                | I <sub>DDL1_SC</sub>          | V <sub>DDL1</sub> = AGND                                                 | 5                           |     | 50                          | mA       |

| POR Threshold                                        | V <sub>DDL1_PORRI</sub><br>SE | V <sub>DDL1</sub> rising                                                 | 1.3                         | 1.5 | 1.65                        | V        |

| POR Hysteresis                                       | V <sub>DDL1_PORHY</sub><br>S  |                                                                          | 20                          | 50  |                             | mV       |

| V <sub>DDL2</sub> REGULATOR                          |                               |                                                                          |                             |     |                             |          |

| Output Voltage                                       | V <sub>DDL2</sub>             | 0mA < I <sub>VDDL2</sub> < 10mA, 4.5V < V <sub>DCIN2</sub> < 5.5V        | 3.2                         | 3.3 | 3.4                         | V        |

| Short-Circuit Current                                | I <sub>DDL2_SC</sub>          | V <sub>DDL2</sub> = AGND                                                 | 13                          |     |                             | mA       |

| LOGIC INPUTS (CS, DIN                                | , SCLK)                       |                                                                          |                             |     |                             |          |

| Input High Voltage                                   | VIH                           | V <sub>DCIN1</sub> > 2.375V                                              | 0.7 x<br>V <sub>DCIN1</sub> |     |                             | V        |

| mput riigir võitage                                  | VIH                           | 1.71V < V <sub>DCIN1</sub> < 1.89V                                       | 0.8 x<br>V <sub>DCIN1</sub> |     |                             |          |

| Input Low Voltage                                    | V <sub>IL</sub>               | V <sub>DCIN1</sub> > 2.375V                                              |                             |     | 0.3 x<br>V <sub>DCIN1</sub> | V        |

| mput Low Voltage                                     | VIL.                          | 1.71V < V <sub>DCIN1</sub> < 1.89V                                       |                             |     | 0.2 x<br>V <sub>DCIN1</sub> | V        |

| Input Leakage Current                                | I <sub>IN</sub>               | Vin = 0V or V <sub>DCIN1</sub><br>(Note 12)                              |                             |     | ±1                          | μΑ       |

| Internal Impedance                                   | R <sub>PD</sub>               | DIN, SCLK pull down to GND (Notes 13, 14)                                | 40                          | 100 | 160                         | kΩ       |

| mternal impedance                                    | R <sub>PU</sub>               | CS pull up to V <sub>DCIN1</sub> (Notes 13, 14)                          | 40                          | 100 | 160                         | KS2      |

| Input Capacitance                                    | C <sub>IN</sub>               |                                                                          |                             | 10  |                             | pF       |

| Hysteresis Voltage                                   | V <sub>H</sub>                |                                                                          |                             | 250 |                             | mV       |

| LOGIC OUTPUTS (DOUT                                  | Γ, ALERT)                     |                                                                          |                             |     |                             |          |

| Output High Voltage                                  | V <sub>OH</sub>               | V <sub>DCIN1</sub> >2.375V, I <sub>SOURCE</sub> = 4mA, Note 10           | V <sub>DCIN1</sub><br>-0.2  |     |                             |          |

| Calput Flight Voltage                                | VOH                           | 1.71V < V <sub>DCIN1</sub> < 1.89V, I <sub>SOURCE</sub> = 1.5mA, Note 10 | V <sub>DCIN1</sub><br>-0.2  |     | "                           | <b>v</b> |

| Output Low Voltage                                   | Var                           | V <sub>DCIN1</sub> >2.375V, I <sub>SINK</sub> = 4mA                      |                             |     | 0.2                         | V        |

| Output Low Voltage                                   | V <sub>OL</sub>               | 1.71V < V <sub>DCIN1</sub> < 1.89V, I <sub>SINK</sub> = 1.5mA            |                             |     | 0.2                         | V        |

| Output Tristate Leakage                              | loz                           | V <sub>DOUT</sub> = 0 and 5V, V <sub>ALERT</sub> = 5V                    |                             |     | ±1                          | μΑ       |

| Output Tristate<br>Capacitance                       | C <sub>OZ</sub>               |                                                                          |                             | 10  |                             | pF       |

$(V_{DCIN1}>=V_{DDL1},\,V_{DCIN1}<5.5V,\,V_{DCIN2}>=V_{DDL2},\,V_{DCIN2}<5.5V,\,V_{DDL1}=1.8V,\,V_{DDL2}=3.3V,\,T_A=T_{MIN}\,\,to\,\,T_{MAX},\,\,unless\,\,otherwise\,\,noted,\,\,where\,\,T_{MIN}=-40\,^{\circ}C\,\,and\,\,T_{MAX}=+125\,^{\circ}C.\,\,Typical\,\,values\,\,are\,\,at\,\,T_A=+25\,^{\circ}C.\,\,Operation\,\,is\,\,with\,\,the\,\,recommended\,\,application\,\,circuit.)$

| PARAMETER                                      | SYMBOL                        | CONDITIONS                                                       | MIN                                  | TYP                  | MAX                                  | UNITS |

|------------------------------------------------|-------------------------------|------------------------------------------------------------------|--------------------------------------|----------------------|--------------------------------------|-------|

| GENERAL PURPOSE IN                             | PUTS/OUTPUTS                  | (GPIO1, GPIO2, GPIO3, GPIO4)                                     | •                                    |                      |                                      |       |

| Output Leakage Current                         | I <sub>GPO_LKG</sub>          | V <sub>GPIOn</sub> = 0 and 5V, GPIO disabled                     | -1                                   |                      | 1                                    | μΑ    |

| Outset High Maltage                            | .,                            | V <sub>DCIN1</sub> > 2.375V, I <sub>SOURCE</sub> = 4mA           | V <sub>DCIN1</sub> - 0.2             |                      |                                      |       |

| Output High Voltage                            | V <sub>ОН</sub>               | 1.71V < V <sub>DCIN1</sub> < 1.89V, I <sub>SOURCE</sub> = 1.5mA  | V <sub>DCIN1</sub> - 0.2             |                      |                                      | V     |

| Outrot Law Valtage                             |                               | V <sub>DCIN1</sub> > 2.375V, I <sub>SINK</sub> = 4mA             |                                      |                      | 0.2                                  |       |

| Output Low Voltage                             | V <sub>OL</sub>               | 1.71V < V <sub>DCIN1</sub> < 1.89V, I <sub>SINK</sub> = 1.5mA    |                                      |                      | 0.2                                  | V     |

| Innut High Voltage                             | V                             | V <sub>DCIN1</sub> > 2.375V                                      | 0.7 x<br>V <sub>DCIN1</sub>          |                      |                                      | V     |

| Input High Voltage                             | V <sub>IH</sub>               | 1.71V < V <sub>DCIN1</sub> < 1.89V                               | 0.8 x<br>V <sub>DCIN1</sub>          |                      |                                      | V     |

| Innut I am Valtaga                             | V                             | V <sub>DCIN1</sub> > 2.375V                                      |                                      |                      | 0.3 x<br>V <sub>DCIN1</sub>          |       |

| Input Low Voltage                              | V <sub>IL</sub>               | 1.71V < V <sub>DCIN1</sub> < 1.89V                               |                                      |                      | 0.2 x<br>V <sub>DCIN1</sub>          | V     |

| Pulldown Resistance                            | R <sub>GPIO</sub>             | GPIOn_CFG configured as input                                    |                                      | 2M                   |                                      | Ω     |

| Output Short Circuit<br>Current                | loss                          | I <sub>SINK</sub> , V <sub>GPIOn</sub> = V <sub>DCIN1</sub> = 5V |                                      |                      | 50                                   | mA    |

| POWER AND GROUND                               | FAULT DETECTI                 | ON                                                               | •                                    |                      |                                      |       |

| Open Detection Voltage (V <sub>DDL1</sub> )    | V <sub>ALRTVDDL1</sub>        |                                                                  | 1.62                                 | 1.65                 | 1.68                                 | V     |

| Open Detection Voltage (V <sub>DDL2</sub> )    | V <sub>ALRTVDDL2</sub>        |                                                                  | 2.90                                 | 3.00                 | 3.10                                 | V     |

| Over Voltage Detection (VDCIN1)                | V <sub>ALRTOV_DCI</sub>       |                                                                  | 5.6                                  | 5.7                  | 5.8                                  | V     |

| Overvoltage Detection<br>Hysteresis (VDCIN1)   | VDCIN1OV_HY                   |                                                                  | 100                                  |                      | 150                                  | mV    |

| Over Voltage Detection (VDCIN2)                | V <sub>ALRTOV_DCI</sub><br>N2 |                                                                  | 5.6                                  | 5.7                  | 5.8                                  | V     |

| Overvoltage Detection<br>Hysteresis (VDCIN2)   | V <sub>DCIN2OV</sub> HY       |                                                                  | 100                                  |                      | 150                                  | mV    |

| OSCILLATORS                                    |                               |                                                                  | •                                    |                      |                                      |       |

| LF Oscillator Frequency                        | fLFOSC                        |                                                                  | 32.11                                | 32.768               | 33.42                                | kHz   |

| HF Oscillator Frequency                        | fHFOSC                        |                                                                  | 62.72                                | 64                   | 65.28                                | MHz   |

| UART INPUTS (RXP, RX                           | N)                            |                                                                  |                                      |                      |                                      |       |

| Differential Input High<br>Threshold           | V <sub>TH</sub>               | Note 1                                                           | V <sub>DDL1</sub> /2<br>- 400mV      | V <sub>DDL1</sub> /2 | V <sub>DDL1</sub> /2<br>+ 400mV      | V     |

| Differential Input Zero-<br>Crossing Threshold | V <sub>ZC</sub>               | Note 1                                                           | -400                                 | 0                    | 400                                  | mV    |

| Differential Input Low<br>Threshold            | V <sub>TL</sub>               | Note 1                                                           | -V <sub>DDL1</sub> /<br>2 -<br>400mV | -V <sub>DDL1</sub> / | -V <sub>DDL1</sub> /<br>2 +<br>400mV | V     |

$(V_{DCIN1}>=V_{DDL1},\,V_{DCIN1}<5.5V,\,V_{DCIN2}>=V_{DDL2},\,V_{DCIN2}<5.5V,\,V_{DDL1}=1.8V,\,V_{DDL2}=3.3V,\,T_A=T_{MIN}\,\,to\,\,T_{MAX},\,\,unless\,\,otherwise\,\,noted,\,\,where\,\,T_{MIN}=-40\,^{\circ}C\,\,and\,\,T_{MAX}=+125\,^{\circ}C.\,\,Typical\,\,values\,\,are\,\,at\,\,T_A=+25\,^{\circ}C.\,\,Operation\,\,is\,\,with\,\,the\,\,recommended\,\,application\,\,circuit.)$

| PARAMETER                                                 | SYMBOL                  | CONDITIONS                                                      | MIN                     | TYP                  | MAX                                                                             | UNITS                |

|-----------------------------------------------------------|-------------------------|-----------------------------------------------------------------|-------------------------|----------------------|---------------------------------------------------------------------------------|----------------------|

| Differential Input<br>Hysteresis                          | V <sub>HYST</sub>       | Note 1                                                          | 30                      | 80                   | 160                                                                             | mV                   |

| Common-Mode Voltage<br>Bias                               | V <sub>CM</sub>         |                                                                 |                         | V <sub>DDL1</sub> /2 |                                                                                 | V                    |

| Input Capacitance                                         | C <sub>IN</sub>         |                                                                 |                         | 2                    |                                                                                 | pF                   |

| Leakage Current                                           | l <sub>LKG_RX</sub>     | V <sub>RX</sub> = 0.9V                                          |                         | ±1.0                 |                                                                                 | μA                   |

| Input Resistance to Common Mode Voltage                   | R <sub>RXIN</sub>       |                                                                 |                         | 8.0                  |                                                                                 | ΜΩ                   |

| UART OUTPUTS (TXP, T                                      | XN)                     |                                                                 |                         |                      |                                                                                 |                      |

| Output Low Voltage                                        | V <sub>OL</sub>         | I <sub>OL</sub> = -20mA                                         |                         |                      | V <sub>AGND</sub><br>+ 0.4                                                      | V                    |

| Output High Voltage                                       | V <sub>OH</sub>         | I <sub>OH</sub> = 20mA                                          | V <sub>DDL2</sub> - 0.4 |                      |                                                                                 | V                    |

| UART TIMING                                               |                         |                                                                 |                         |                      |                                                                                 |                      |

| Bit Period Except for Second STOP Bit                     | t <sub>BIT</sub>        | f <sub>UART</sub> = 4Mbps,<br>( <u>Note 2</u> , <u>Note 3</u> ) |                         | 16                   |                                                                                 | 1/f <sub>HFOSC</sub> |

| D'' D : 15 16                                             |                         | f <sub>UART</sub> = 2Mbps ( <i>Note 3</i> , <i>Note 4</i> )     |                         | 32                   |                                                                                 |                      |

| Bit Period Except for<br>Second STOP Bit                  | t <sub>BIT</sub>        | f <sub>UART</sub> = 1Mbps ( <u>Note 3</u> , <u>Note 4</u> )     |                         | 64                   |                                                                                 | 1/f <sub>HFOSC</sub> |

| Second 6 / 6 / 5 /                                        |                         | f <sub>UART</sub> = 0.5Mbps ( <u>Note 3</u> , <u>Note 4</u> )   |                         | 128                  |                                                                                 | ]                    |

| Second STOP Bit<br>Period                                 | <sup>t</sup> STOPBIT    | Note 2, Note 3                                                  |                         | 1.125                |                                                                                 | t <sub>BIT</sub>     |

| Tx Idle to START Setup<br>Time                            | <sup>t</sup> TXSTSU     | Note 2, Note 3, Note 4                                          |                         | 0.5                  |                                                                                 | t <sub>BIT</sub>     |

| STOP Hold Time to Idle                                    | tsphd                   | Note 2, Note 3                                                  |                         |                      | 0.5                                                                             | t <sub>BIT</sub>     |

| Rx Minimum Idle Time<br>(STOP Bit to START Bit)           | <sup>t</sup> RXIDLESPST | (Note 2, Note 3)                                                | 1                       |                      |                                                                                 | t <sub>BIT</sub>     |

| Tx Idle Time                                              | tTXIDLESPST             | ( <u>Note 1</u> , <u>Note 2</u> )                               |                         | 0.5                  |                                                                                 | t <sub>BIT</sub>     |

| Rx Fall Time                                              | tFALL                   | Note 2, Note 3, Note 4                                          |                         |                      | 0.5                                                                             | t <sub>BIT</sub>     |

| Rx Rise Time                                              | <sup>t</sup> RISE       | ( <u>Note 2</u> , <u>Note 3</u> , <u>Note 4</u> )               |                         |                      | 0.5                                                                             | t <sub>BIT</sub>     |

| UART MESSAGE TIMING                                       | <b>;</b>                |                                                                 |                         |                      |                                                                                 |                      |

| SPI Command to Tx<br>Valid Propagation Delay              | t <sub>TX</sub>         | ( <u>Note 5</u> )                                               | 125                     |                      | 250                                                                             | ns                   |

| Tx Valid to Rx Valid Up<br>Stack Delay                    | t <sub>RXUP</sub>       | (Note 6)                                                        |                         |                      | n x<br>t <sub>PROP</sub>                                                        |                      |

| Tx Valid to Rx Valid<br>Down Stack Delay                  | t <sub>RXDN</sub>       | (Note 6)                                                        |                         |                      | n x<br>t <sub>PROP</sub>                                                        |                      |

| End of STOP Character to RX_STOP_ALRT Flag True           | <sup>t</sup> ALERT      | ( <u>Note 7</u> )                                               |                         |                      | 2                                                                               | t <sub>BIT</sub>     |

| SPI START to UART<br>Slave Device Register<br>Write Delay | <sup>‡</sup> REGWR      | ( <u>Note 8, Note 9</u> )                                       |                         |                      | 8 / f <sub>SCLK</sub><br>+ 130 x<br>t <sub>BIT</sub> + n<br>x t <sub>PROP</sub> |                      |

$(V_{DCIN1} > = V_{DDL1}, V_{DCIN1} < 5.5V, V_{DCIN2} > = V_{DDL2}, V_{DCIN2} < 5.5V, V_{DDL1} = 1.8V, V_{DDL2} = 3.3V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, where  $T_{MIN} = -40$ °C and  $T_{MAX} = +125$ °C., Typical values are at  $T_A = +25$ °C. Operation is with the recommended application circuit.)

| PARAMETER                           | SYMBOL            | CONDITIONS                                            | MIN | TYP | MAX | UNITS |

|-------------------------------------|-------------------|-------------------------------------------------------|-----|-----|-----|-------|

| SPI TIMING                          |                   |                                                       |     |     |     | •     |

| SCLK Frequency                      | fsclk             | V <sub>DCIN1</sub> > 2.375V ( <u>Note 15</u> )        |     |     | 10  | MHz   |

| SCLK Period                         | t <sub>CP</sub>   |                                                       | 100 |     |     | ns    |

| SCLK Pulse Width High               | t <sub>CH</sub>   |                                                       | 40  |     |     | ns    |

| SCLK Pulse Width Low                | t <sub>CL</sub>   |                                                       | 40  |     |     | ns    |

| CSB Fall to SCLK Rise<br>Setup Time | tcsso             | To first SCLK rising edge (RE).                       | 40  |     |     | ns    |

| CSB Fall to SCLK Rise<br>Hold Time  | t <sub>CSH0</sub> | Applies to inactive RE preceding first RE.            | 25  |     |     | ns    |

| SCLK Rise to CSB Rise<br>Hold Time  | t <sub>CSH1</sub> | Applies to 8+8*n RE.                                  | 25  |     |     | ns    |

| CSB Pulse Width High                | t <sub>CSPW</sub> |                                                       | 400 |     |     | ns    |

| CSB Pulse Width High<br>After SWPOR | tcspwsp           | Applies after an accepted/executed SWPOR command.     | 100 |     |     | us    |

| SDI to SCLK Rise Setup<br>Time      | t <sub>DS</sub>   |                                                       | 10  |     |     | ns    |

| SDI to SCLK Rise Hold<br>Time       | t <sub>DH</sub>   |                                                       | 10  |     |     | ns    |

| SCLK Fall to SDO<br>Transition      | t <sub>DOT</sub>  | V <sub>DCIN1</sub> > 2.375V, C <sub>LOAD</sub> = 20pf |     |     | 40  | ns    |

| SCLK Fall to SDO Hold               | t <sub>DOH</sub>  | C <sub>LOAD</sub> = 0pf                               | 2   |     |     | ns    |

| CSB Fall to SDO<br>Transition       | t <sub>DOE</sub>  | V <sub>DCIN1</sub> > 2.375V, C <sub>LOAD</sub> = 20pf |     |     | 40  | ns    |

| CSB Rise to SDO Hi-Z                | t <sub>DOZ</sub>  | VDCIN1 > 2.375V, Output disable time                  |     |     | 40  | ns    |

- Note 1: Differential signal  $(V_{RXP} V_{RXN})$  where  $V_{RXP}$ ,  $V_{RXN}$  do not exceed a common-mode voltage range of  $\pm 25V$ .

- Note 2: All parameters measured based on differential signal.

- Note 3: Guaranteed by design and not production tested.

- **Note 4:** Fall time measured 90% to 10%, rise time measured 10% to 90%.

- Note 5: Measured from falling edge of 8th SCLK cycle of the WR NXT LD Q SPI command byte (B0h).

- **Note 6:** t<sub>PROP</sub> is the maximum propagation delay through a slave device in a given direction. Refer to the UART slave device data sheet for the actual delay. The number of UART slave devices is denoted by n.

- Note 7: Measured from end of 10th bit of stop character.

- Note 8: Parameter t<sub>REGWR</sub> is the minimum amount of time needed to write a register in the nth slave device of the daisy-chain. It is measured from the start of the SPI transaction WR\_NXT\_LD\_Q (B0h) that initiates transmission of a WRITEALL mesage to when the nth device receives a valid WRITEALL message. For example, for 4MHz SPI frequency, 2Mbps UART baud rate, n = 10 and t<sub>PROP</sub> = 3 × t<sub>BIT</sub>, t<sub>REGWR</sub> = 2µs + 65µs + 15µs = 82µs.

- Note 9: Computation of t<sub>REGWR</sub> consists of three terms: 1) duration of the SPI transaction, 2) partial duration of the UART message, and 3) propagation delay of the UART message. The first term equals the number of bits in the SPI transaction (8) × the SPI bit time (1 / f<sub>SCLK</sub>). The second term equals the time from the start of the WRITEALL message to the first STOP bit of the last PEC nibble. The last PEC nibble is the 11th character in the message. With each character lasting 12 UART bit times, there are 11 × 12 = 132 bit times from the start of the message to the end of the last PEC nibble. Since the write occurs just before the two STOP bits of the 11th character, the term is actually 130 × t<sub>BIT</sub>. The third term is the propagation delay required for the WRITEALL message to get to the nth device.

- Note 10: V<sub>OH</sub> specification for ALERT is determined by the external pullup resistor and leakage current of the network.

- **Note 11:** Static logic inputs with  $V_{IL}$  = AGND and  $V_{IH}$  =  $V_{DCIN1}$ . CSB =  $V_{IH}$  (if pullup is active).

# SPI-UART安全監視ブリッジ

## MAX17851

- Note 12: No internal safety pullup/pulldown impedances active. Input buffers only.

- Note 13: Internal safety pullup/pulldown impedances available with enable function.

- Note 14: If pullup is supported, note CSB connection and diode to  $V_{\text{DDL1}}$ . This diode is present regardless of enable mode.

- Note 15: Applications must afford time for the device to drive data on the SDO bus and meet the  $\mu$ C setup time prior to the  $\mu$ C latching in the result on the following SCLK rising edge. In practice, this can be determined by loading and  $\mu$ C characteristics, and the relevant  $t_{DOT}/t_{DOE}$ .

図1. SPIタイミング図

図2. 受信UARTのタイミング

図3. 送信UARTのタイミング

図4. TXバッファの書込みおよび読出し

注:DCIN1の電流: DCIN1の総電流は、IDCIN1\_STATICとIDCIN1\_COMMの和です。IDCIN1\_COMMは、SPIの動作周波数、SDOの出

カデータ、DCIN1の電圧、各通信ラインの合計容量に依存します。使用したデータ・パターンは、5VのDCIN1を用いた

平均50%の遷移のデータ・パターンを仮定しています。

注:DCIN2の電流: DCIN2の総電流は、IDCIN2\_STATICとIDCIN2\_COMMの和です。IDCIN2\_COMMは、UARTのボー・レート、UART

の出力データ、DCIN2の電圧、各通信ラインの合計容量に依存します。使用したデータ・パターンは、3.3VのDCIN2を

用いた平均67%の遷移のデータ・パターンを仮定しています。

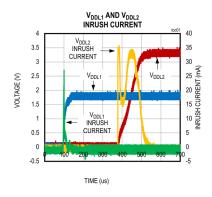

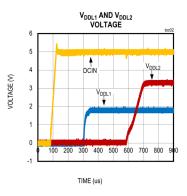

# 標準動作特性

(特に指定にない限り、DCIN1 = 3.3V、DCIN2 = 5.0V、 $T_A = +25$ °C。)

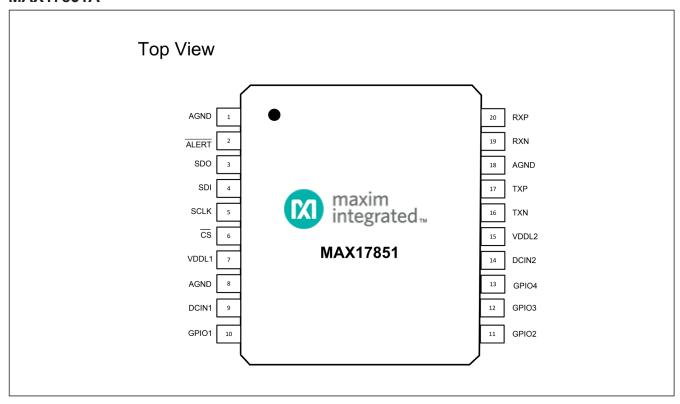

# ピン配置

### MAX17851A

# 端子説明

| ピン | 名称                | 説明                                                                                                                                      | タイプ          |

|----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1  | AGND              | アナログ・グランド。電源グランドに接続します。                                                                                                                 | Ground       |

| 2  | ALERT             | アクティブ・ロー、オープン・ドレインの割込み出力。アプリケーションの要件に従って<br>このピンにプルアップ抵抗を接続します。何らかの割込みフラグがセットされた場合、<br>このピンがアサートされます。                                   | Output       |

| 3  | SDO               | SPIデータ出力。SPIマスタのSDI/MISO入力に接続します。 $\overline{CS}$ がデアサートされるとこの出力はトライステートになります。 $\overline{CS}$ がアサートされると、このピンは、DCIN1電源とAGND電源の間で駆動されます。 | Output       |

| 4  | SDI               | SPIデータ入力。SPIマスタのSDO/MOSI出力に接続します。5Vに対応可能です。                                                                                             | Input        |

| 5  | SCLK              | SPIクロック入力。SPIマスタのSCLK出力に接続します。5Vに対応可能です。                                                                                                | Input        |

| 6  | <del>CS</del>     | アクティブ・ローのSPIチップ・セレクト入力。SPIマスタのスレーブ・セレクト出力に接続します。これをアサートするとSPIポートが有効化されます。5Vに対応可能です。                                                     | Input        |

| 7  | V <sub>DDL1</sub> | 1.8V LDOの電源出力および内部発振器とロジック用の電源出力。直接給電するには、DCIN1に接続します。アプリケーション回路に従ってデカップリングします。                                                         | Power        |

| 8  | AGND              | アナログ・グランド。電源グランドに接続します。                                                                                                                 | Ground       |

| 9  | DCIN1             | 1.8V LDOレギュレータ用の電源入力。アプリケーション回路に従ってデカップリングします。                                                                                          | Power        |

| 10 | GPIO1             | 汎用I/O。デフォルト設定は汎用入力です。ハードウェアの冗長性を確保するために、このピンはGPIO2と並列に用いることができます。                                                                       | Input/Output |

|    |                   | 使用しない場合、ピンは無接続のままにすることができます。詳細については、GPIO<br>制御のセクションを参照してください。                                                                          |              |

| 11 | GPIO2             | 汎用I/O。デフォルト設定は汎用入力です。ハードウェアの冗長性を確保するために、このピンはGPIO1と並列に用いることができます。                                                                       | Input/Output |

|    |                   | 使用しない場合、ピンは無接続のままにすることができます。詳細については、 <u>GPIO</u><br>制御のセクションを参照してください。                                                                  |              |

| 12 | GPIO3             | 汎用I/O。デフォルト設定は汎用入力です。<br>使用しない場合、ピンは無接続のままにすることができます。詳細については、 <u>GPIO</u><br>制御のセクションを参照してください。                                         | Input/Output |

| 13 | GPIO4             | 汎用I/O。デフォルト設定は汎用入力です。 使用しない場合、ピンは無接続のままにすることができます。詳細については、GPIO制御のセクションを参照してください。                                                        | Input/Output |

| 14 | DCIN2             | 3.3V LDOレギュレータ用の電源入力。アプリケーション回路に従ってデカップリン<br>グします。                                                                                      | Power        |

| 15 | $V_{DDL2}$        | 3.3V LDOの電源出力およびUART用の電源出力。直接給電するには、DCIN2に接続します。アプリケーション回路に従ってデカップリングします。                                                               | Power        |

| 16 | TXN               | UARTトランスミッタ負出力。アプリケーション回路に従ってUARTスレーブ・デバイ                                                                                               |              |

| 17 | TXP               | UARTトランスミッタ正出力。アプリケーション回路に従ってUARTスレーブ・デバイスのRXPポートに接続します。このピンは、VDDL2電源とAGND電源の間で駆動されます。                                                  | Output       |

| 18 | AGND              | アナログ・グランド。電源グランドに接続します。                                                                                                                 | Ground       |

| 19 | RXN               | UARTレシーバ負入力。アプリケーション回路に従ってUARTスレーブ・デバイスの<br>TXNポートに接続します。                                                                               | Input        |

| 20 | RXP               | UARTレシーバ正入力。アプリケーション回路に従ってUARTスレーブ・デバイスの<br>TXPポートに接続します。                                                                               | Input        |

# 機能図

### MAX17851の機能ブロック図

# 表1. MAX17851の機能ブロックに対する電力分配

| BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SUPPLY            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Decillators Second Seco |                   |

| Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>DDL1</sub> |

| BMS Safety Monitor Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| Transmit PEC Encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| Alert Packet Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| Keep Alive Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| Watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| Digital Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| Transmit Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| Fill Byte Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

| UART Encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| LSSM/Redundant LSSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |