# OV/サージ、UV、逆極性、接地喪失に対する 保護機能を備えた 3V~80V、7A 電力リミッタ

MAX17617/MAX17617A

## 製品のハイライト

- 堅牢な保護機能によりシステムのダウンタイムを低減

- 広い入力電源範囲 : +3V~+80V (逆電流保護無効時)

- 広い入力電源範囲 : +3V~+75V (逆電流保護有効時)

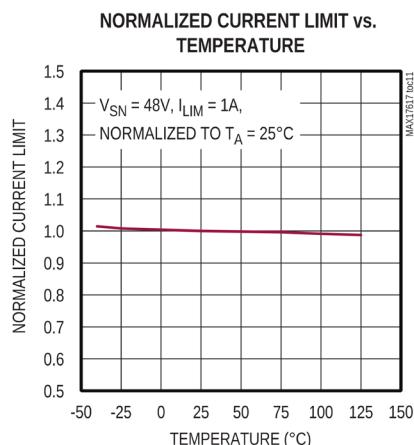

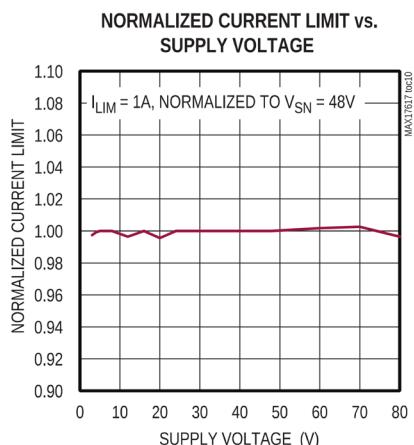

- プログラマブルな電流制限の精度 (3A~7A、全温度範囲) :  $\pm 3\%$

- プログラマブルな電流制限の精度 (2A~3A、全温度範囲) :  $\pm 4\%$

- プログラマブルな電流制限の精度 (0.7A~2A、全温度範囲) :  $\pm 7\%$

- クラス 2 のアプリケーション向け 100W、24V の電力制限精度 :  $\pm 6\%$

- 入力電圧逆極性保護 (外付け nFET 使用)

- 応答時間が 100ns の高速な 2 段階逆電流保護 (外付け nFET 使用)

- 低  $R_{ON}$  の内部 nFET (代表値 20m $\Omega$ )

- 出力電圧逆極性耐性

- 接地喪失保護

- 許容短期的過負荷 : 200%

- プログラマブルな過電圧サージ保護 (MAX17617A)

- 再利用性を最大限に高め再適格性確認の必要性を最小限に抑える柔軟な設計

- 調整可能な UVLO および OVLO/OVFB スレッショルド

- $\pm 2\%$  の精度の電流モニタリング読出し、IMON (3A~7A、+85°C まで)

- プログラマブルな起動時突入電流制限値

- プログラマブルな電流制限フォルト応答: 連続モード、自動再試行モード、ラッチオフ・モード

- ロジック・レベルのイネーブル入力 (EN)

- 外付け n 型電界効果トランジスタ (nFET) の保護付きゲート駆動

- オープン・ドレイン・フォルト・インジケータ (FLAG)

- パワー・グッド出力 (PGOOD)

- プログラマブルな出力低電圧検出 (OUTUV)

- ジャンクション温度のモニタリング ( $T_J$ )

- サーマル・フォールドバック電流制限

## ソリューションの実装面積を縮小

- 4.5mm × 5.75mm、23 ピン FCQFN パッケージ

- 一般的の使用条件での保護要件に対応する内蔵 nFET

## 主なアプリケーション

- 入力電圧と出力過電流に対する保護 :

MAX17617/MAX17617A は、入力電圧フォルト時と出力過電流フォルト時には、負荷電流を遮断し、出力を入力から切り離します。

- 接地喪失保護 :

グランド・バス上にある単一フォルト安全ヒューズが切れた場合など、接地喪失イベントが生じた場合には、MAX17617/MAX17617A は負荷電流を遮断し、出力を入力から切り離します。

- サージ保護 :

MAX17617A は、入力電圧に過渡的なサージが発生している間は出力電圧制限レギュレーションを行い、接続されている負荷を短期的な入力電圧サージ・イベントから保護します。

- UL1310 クラス 2 電力リミッタ :

MAX17617/MAX17617A が備える 3A~7A で精度  $\pm 3\%$  の電流制限および精度  $\pm 6\%$  の電力制限は、UL1310 クラス 2 電源アプリケーションに厳格な保護境界を提供し、負荷への最大限の電力供給を可能にします。

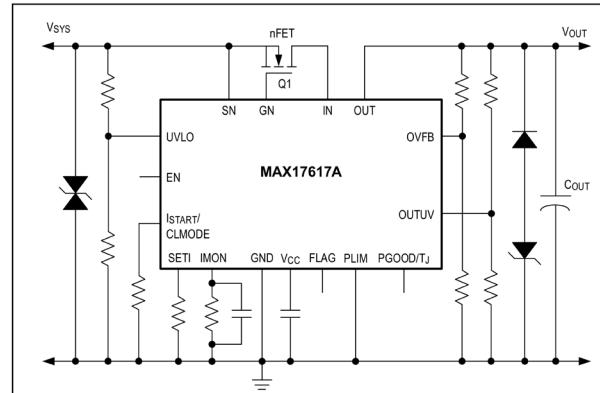

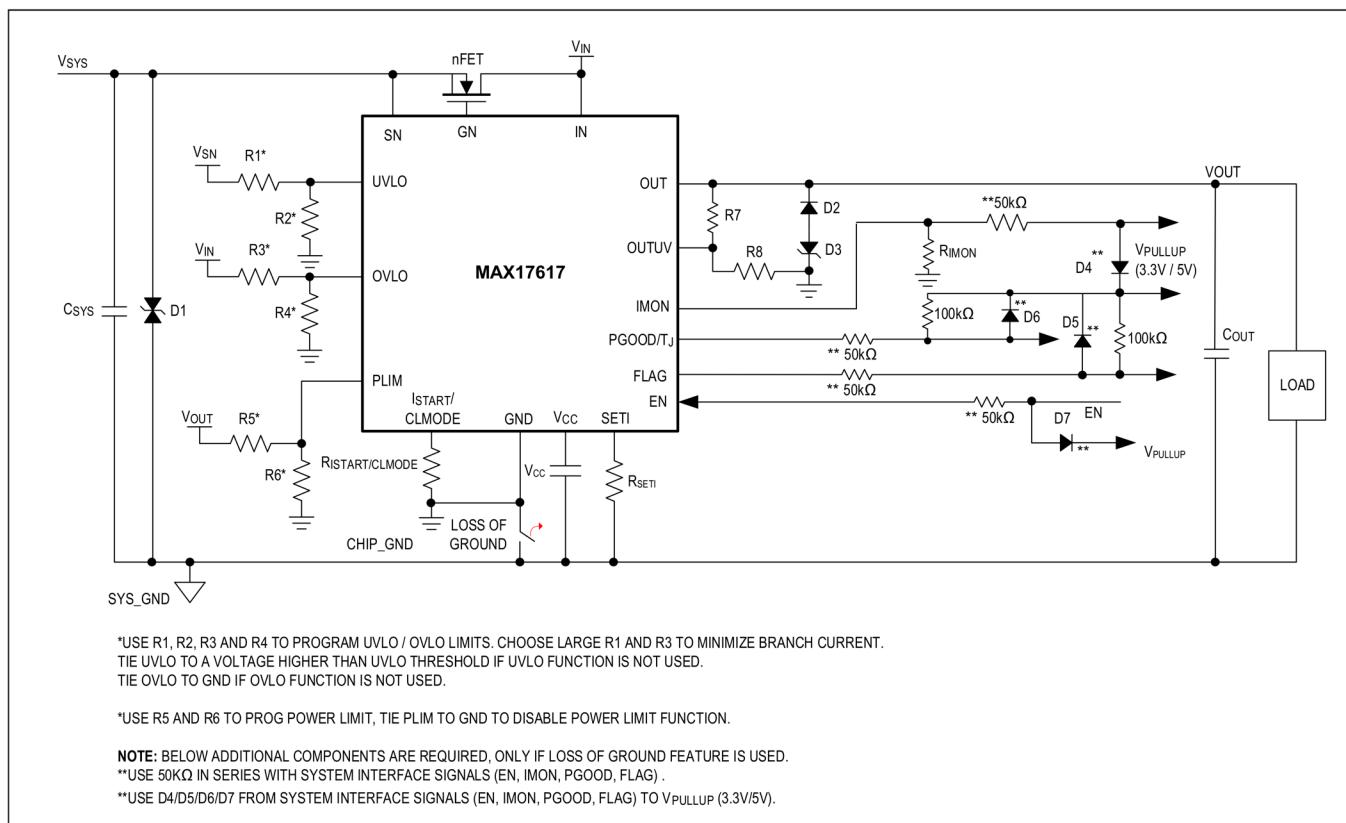

## 簡略アプリケーション回路図

型番は、データシートの末尾に記載しています。

## 目次

|                                               |    |

|-----------------------------------------------|----|

| 製品のハイライト .....                                | 1  |

| 主なアプリケーション .....                              | 1  |

| 簡略アプリケーション回路図 .....                           | 1  |

| 絶対最大定格 .....                                  | 4  |

| パッケージ情報 .....                                 | 4  |

| 電気的特性 .....                                   | 5  |

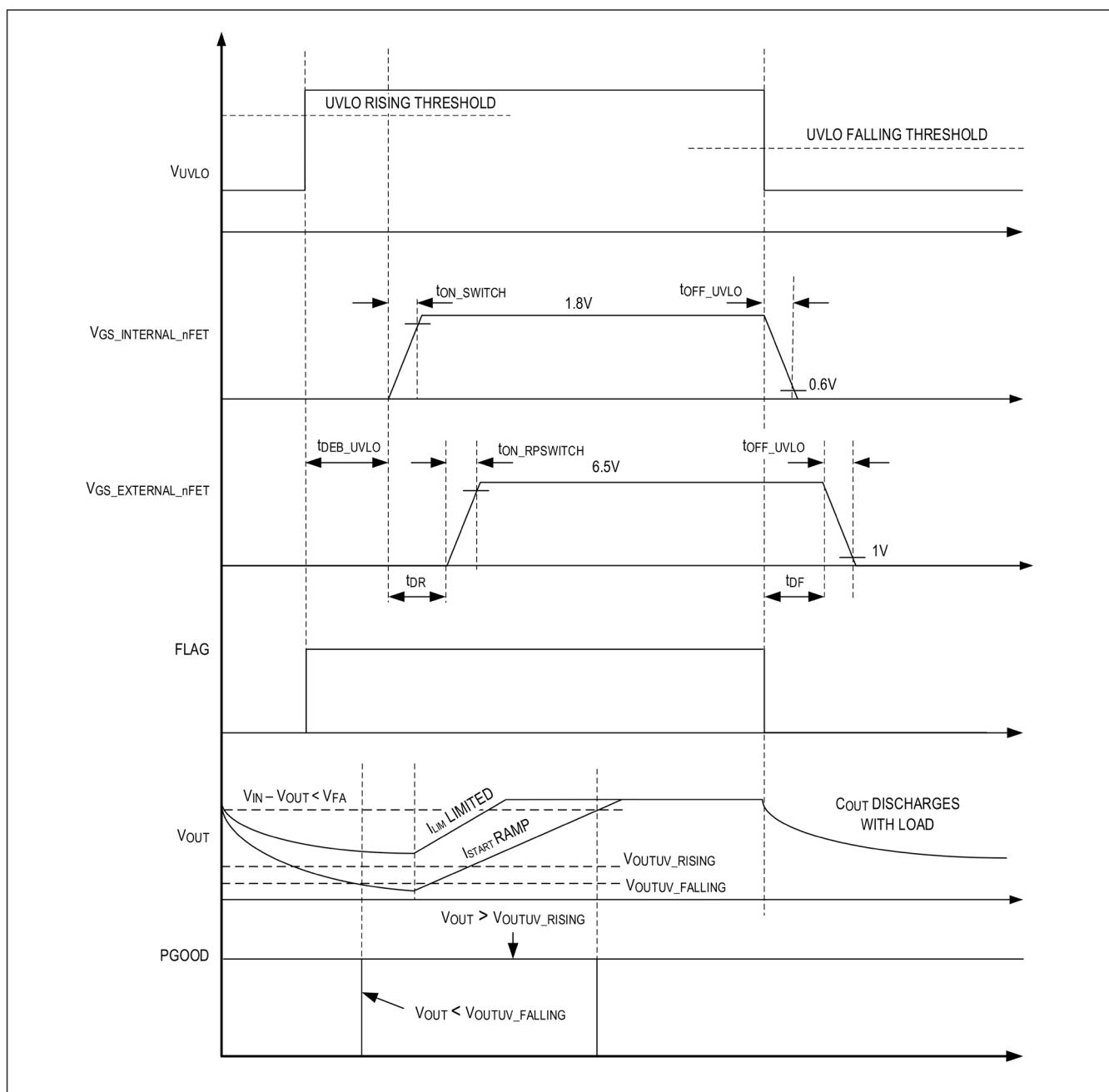

| タイミング図 .....                                  | 9  |

| 標準動作特性 .....                                  | 10 |

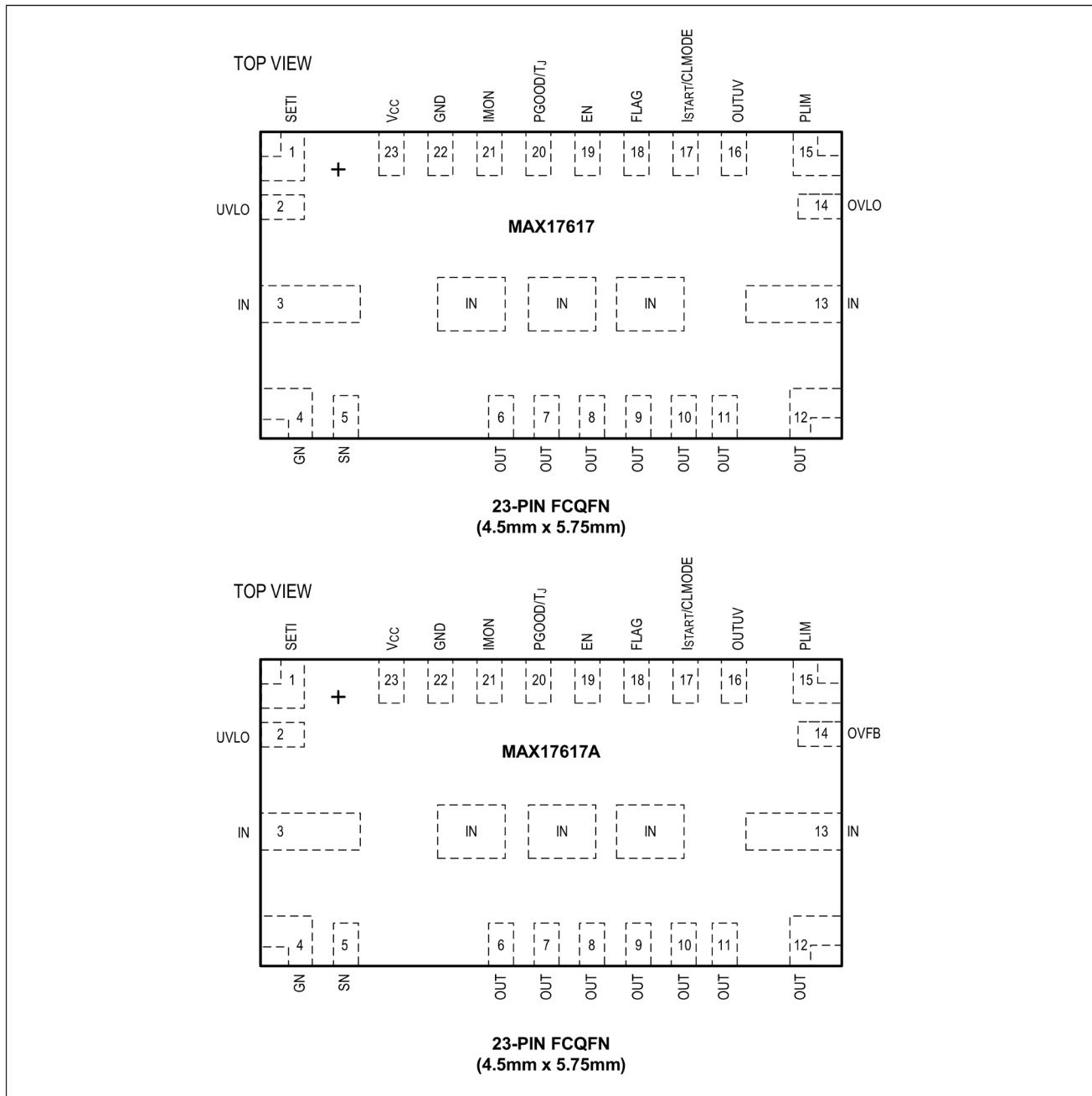

| ピン配置 .....                                    | 15 |

| 端子説明 .....                                    | 16 |

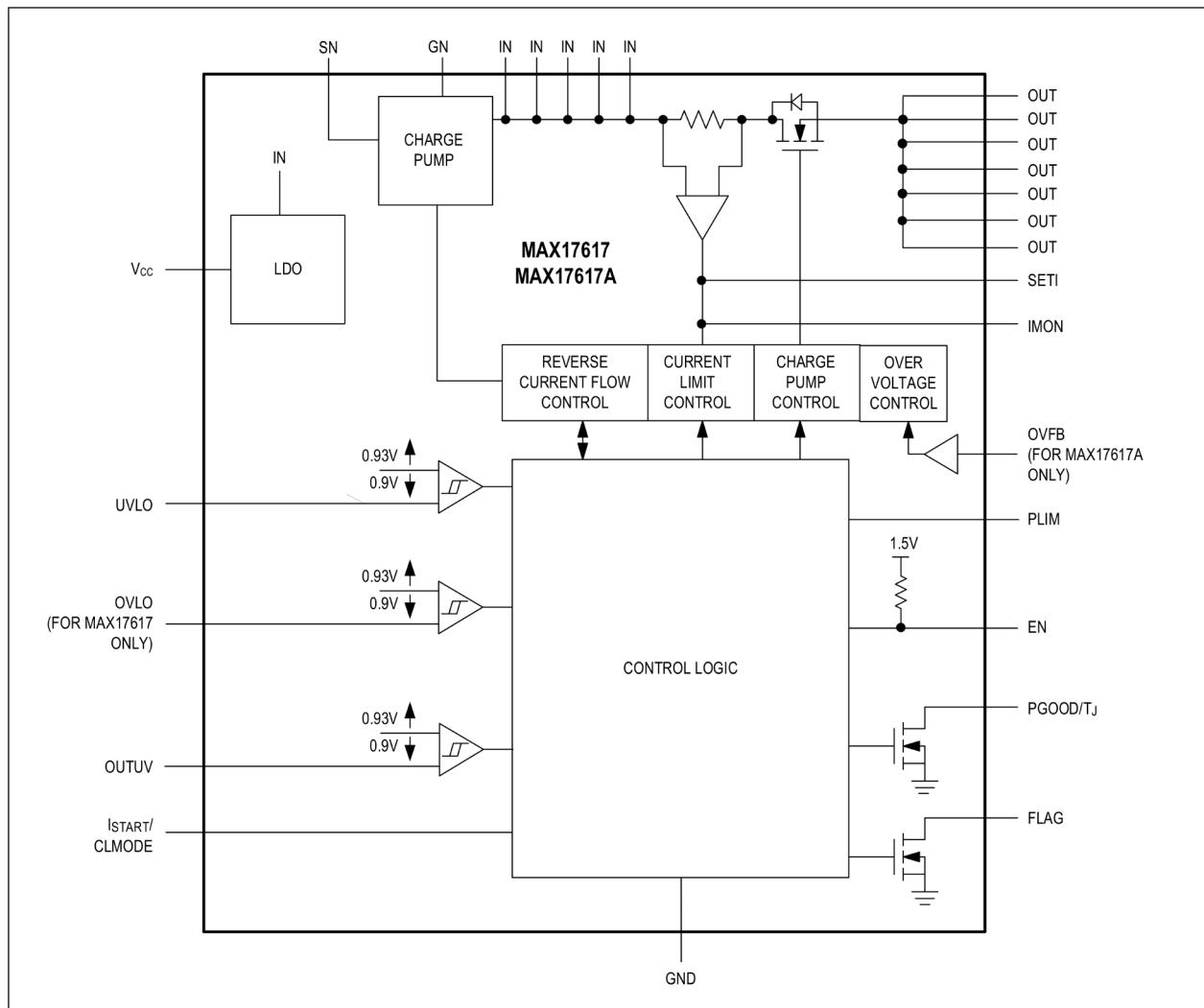

| 機能図 .....                                     | 17 |

| 詳細説明 .....                                    | 18 |

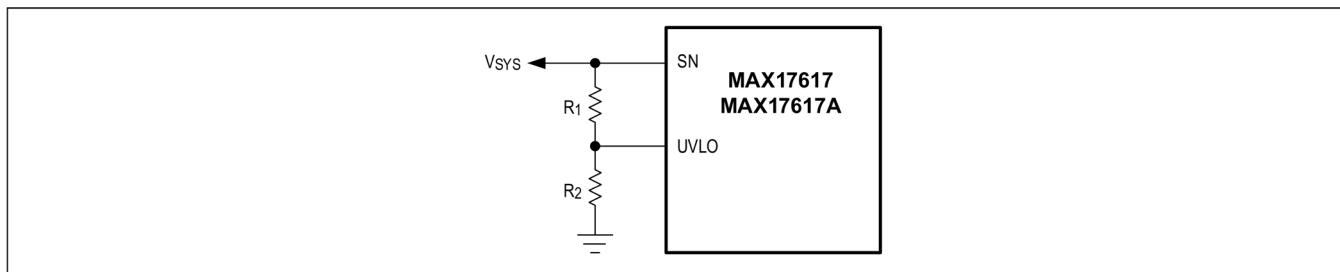

| 入力低電圧ロックアウト (UVLO) .....                      | 19 |

| 入力過電圧ロックアウト (OVLO) .....                      | 21 |

| 入力デバウンス保護 .....                               | 23 |

| イネーブル .....                                   | 24 |

| 起動時突入電流制限 (I <sub>START</sub> ) .....         | 24 |

| 電流制限スレッショルドの設定 (I <sub>LIM</sub> ) .....      | 26 |

| 電流モニタリング (IMON) .....                         | 27 |

| 電流制限機能と短期過電流対応機能 .....                        | 27 |

| 電流制限タイプの選択 .....                              | 28 |

| 連続電流制限 .....                                  | 29 |

| 自動再試行電流制限 .....                               | 30 |

| ラッチオフ電流制限 .....                               | 31 |

| 短絡保護 .....                                    | 31 |

| 逆電流保護 .....                                   | 32 |

| 入力電圧のサージ除去と出力過電圧フィードバック・レギュレーション (OVFB) ..... | 33 |

| 入力逆極性保護 .....                                 | 35 |

| 出力逆極性保護 .....                                 | 35 |

| 接地喪失保護 .....                                  | 36 |

| 出力低電圧検出 (OUTUV) .....                         | 37 |

| パワー・グッド出力 (PGOOD/T <sub>J</sub> ) .....       | 37 |

| フォルト出力 (FLAG) .....                           | 37 |

| リニア・レギュレータ (V <sub>CC</sub> ) .....           | 38 |

| 逆保護用外付け nFET のゲート・ドライバ .....                  | 38 |

| ダイ温度のモニタリング (PGOOD/T <sub>J</sub> ) .....     | 39 |

|                                     |    |

|-------------------------------------|----|

| サーマル・シャットダウン保護 .....                | 39 |

| 電力制限 .....                          | 39 |

| アプリケーション情報 .....                    | 41 |

| IN コンデンサ .....                      | 41 |

| IN 端子のホット・プラグイン .....               | 41 |

| 入力ハード地絡 .....                       | 41 |

| 瞬時電圧低下応答 .....                      | 41 |

| OUT コンデンサ .....                     | 41 |

| OUT 端子のホット・プラグイン .....              | 42 |

| 誘導性ハード地絡に備える OUT クランピング・ダイオード ..... | 42 |

| レイアウトと放熱 .....                      | 42 |

| ESD 保護 .....                        | 42 |

| 標準アプリケーション回路 .....                  | 43 |

| 型番 .....                            | 44 |

**絶対最大定格**

|                                                                       |                                |

|-----------------------------------------------------------------------|--------------------------------|

| IN～GND                                                                | −0.3V～+85V                     |

| SN～GND (逆電流保護なし)                                                      | −85V～+78V                      |

| SN～GND (逆電流保護なし)                                                      | −85V～+85V                      |

| OUT～GND                                                               | −85V～+85V                      |

| IN～OUT (DC)                                                           | −0.3V～+85V                     |

| UVLO、OVLO、OVFB、OUTUV～GND                                              | −0.3V～+33V                     |

| EN、PGOOD/T <sub>J</sub> 、I <sub>START</sub> /CLMODE、PLIM、<br>FLAG～GND | −0.3V～+6V                      |

| V <sub>CC</sub> ～GND                                                  | −0.3V～+2V                      |

| SETI、IMON～GND                                                         | −0.3V～(V <sub>CC</sub> + 0.3)V |

|                                                                   |              |

|-------------------------------------------------------------------|--------------|

| GN～SN                                                             | −0.3V～+10V   |

| GN～GND                                                            | −85V～+85V    |

| IN～SN                                                             | −1V～+85V     |

| IN 電流 (DC)                                                        | 8A           |

| 連続消費電力 (T <sub>A</sub> = +70°C、+70°C を超えると<br>36.5mW/C でディレーティング) | 3469.7mW     |

| 動作温度範囲                                                            | −40°C～+125°C |

| ジャンクション温度 (Note 1)                                                | −40°C～+150°C |

| 保管温度                                                              | −65°C～+150°C |

| リード温度 (はんだ処理、10 秒)                                                | +300°C       |

| はんだ処理温度 (リフロー)                                                    | +260°C       |

**Note 1 :** ジャンクション温度が+125°Cを超えると、動作寿命が短くなります。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作のセクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

**パッケージ情報**

|                                                        |                           |

|--------------------------------------------------------|---------------------------|

| Package Code                                           | F234A5F+1F                |

| Outline Number                                         | <a href="#">21-100606</a> |

| Land Pattern Number                                    | <a href="#">90-100213</a> |

| <b>THERMAL RESISTANCE, FOUR-LAYER BOARD</b>            |                           |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 27.38°C/W                 |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 1.81°C/W                  |

最新のパッケージ外形図とランド・パターン (フットプリント) に関しては、<https://www.analog.com/en/design-center/packaging-quality-symbols-footprints/package-index.html> で確認してください。パッケージ・コードの「+」、「#」、「-」はRoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面は RoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、<https://www.analog.com/en/technical-articles/thermal-characterization-of-ic-packages.html> を参照してください。

## 電気的特性

(特に指定のない限り、 $V_{IN} = V_{SN} = 3V \sim 80V$ 、 $GN = \text{オープン}$ 、UVLO、OVLO/OVFB、EN、IMON、PGOOD/T<sub>J</sub>、OUTUV、I<sub>START/CLMODE</sub>、FLAG、PLIM =  $\text{オープン}$ 、 $R_{SETI} = 2.13\text{k}\Omega$ 、 $V_{CC} = 2.2\mu\text{F}$ をGNDとの間に接続、 $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 。代表値は $V_{IN} = 48V$ 、 $T_A = +25^\circ\text{C}$ での値 (Note 2を参照)。)

| PARAMETER                                         | SYMBOL           | CONDITIONS                                                    | MIN   | TYP  | MAX   | UNITS         |

|---------------------------------------------------|------------------|---------------------------------------------------------------|-------|------|-------|---------------|

| <b>Input Section</b>                              |                  |                                                               |       |      |       |               |

| IN Voltage Range                                  | $V_{IN}$         | Without Reverse Current Protection                            | 3     | 80   |       | V             |

|                                                   |                  | With Reverse Current Protection                               | 3     | 75   |       |               |

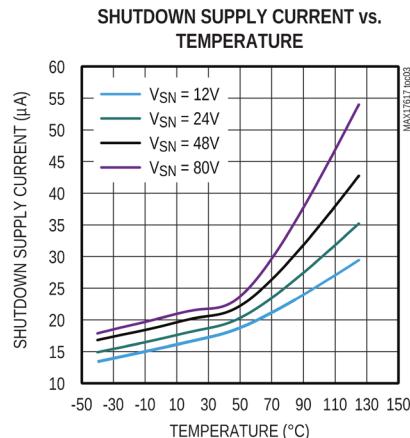

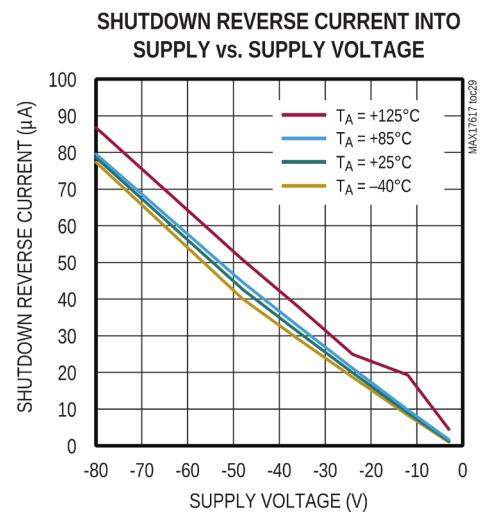

| Shutdown IN Current                               | $I_{INSHDN}$     | $V_{EN} = 0V, V_{OUT} = \text{GND}, T_A = +125^\circ\text{C}$ | 20    | 80   |       | $\mu\text{A}$ |

|                                                   |                  | $V_{EN} = 0V, V_{OUT} = \text{GND}, T_A = +85^\circ\text{C}$  | 20    | 50   |       |               |

| Shutdown SN Current                               |                  | $V_{EN} = 0V, V_{SN} = -80V$                                  | -53   | -105 |       | $\mu\text{A}$ |

| Shutdown IN to OUT Current                        |                  | $V_{EN} = 0V, V_{IN} - V_{OUT} = 80V$                         | 30    | 110  |       | $\mu\text{A}$ |

| Shutdown IN, GN, SN shorted                       |                  | $V_{EN} = 0V, V_{OUT} = \text{GND}, T_A = +125^\circ\text{C}$ | 30    | 90   |       | $\mu\text{A}$ |

|                                                   |                  | $V_{EN} = 0V, V_{OUT} = \text{GND}, T_A = +85^\circ\text{C}$  | 30    | 60   |       |               |

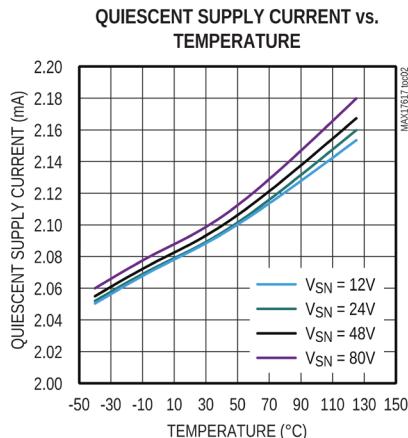

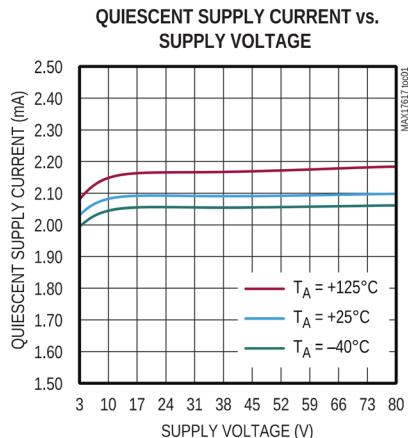

| Supply Current                                    | $I_{IN}$         |                                                               | 2     | 3    |       | $\text{mA}$   |

| Internal IN Undervoltage Trip level               | $V_{INUVLOR}$    | $V_{IN}$ Rising                                               | 2.74  | 2.80 | 2.86  | V             |

|                                                   | $V_{INUVLOF}$    | $V_{IN}$ Falling                                              | 2.64  | 2.70 | 2.76  |               |

| <b>Enable (EN)</b>                                |                  |                                                               |       |      |       |               |

| EN Input-Logic High                               | $V_{ENH}$        |                                                               | 1.4   |      |       | V             |

| EN Input-Logic Low                                | $V_{ENL}$        |                                                               |       | 0.4  |       | V             |

| EN Internal Pullup Voltage                        |                  | $3V < V_{IN} < 80V$                                           | 1.3   | 2.05 |       | V             |

| EN Input Current                                  |                  | $V_{EN} = 5V$                                                 |       | 20   |       | $\mu\text{A}$ |

| EN Pullup Current                                 |                  | $V_{EN} = 0V$                                                 | 2.74  | 5    | 9.56  | $\mu\text{A}$ |

| <b><math>V_{CC}</math> (LDO)</b>                  |                  |                                                               |       |      |       |               |

| $V_{CC}$ Output Voltage Range                     | $V_{CC}$         | $1\text{mA} < I_{VCC} < 10\text{mA}$                          | 1.7   | 1.8  | 1.86  | V             |

| $V_{CC}$ UVLO                                     | $V_{CC\_UVR}$    | $V_{CC}$ rising                                               | 1.62  | 1.66 | 1.7   | V             |

|                                                   | $V_{CC\_UVF}$    | $V_{CC}$ falling                                              | 1.54  | 1.58 | 1.62  |               |

| $V_{CC}$ current limit                            | $I_{VCC}$        |                                                               | 15    | 29   | 48    | $\text{mA}$   |

| <b>Undervoltage Lockout (UVLO)</b>                |                  |                                                               |       |      |       |               |

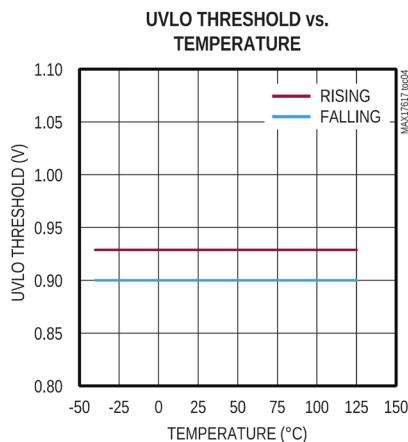

| UVLO Threshold                                    |                  | UVLO Rising                                                   | 0.911 | 0.93 | 0.948 | V             |

|                                                   |                  | UVLO Falling                                                  | 0.882 | 0.90 | 0.918 |               |

| UVLO Leakage Current                              | $I_{UVLO\_LEAK}$ | $V_{UVLO} = 1V, T_A = +25^\circ\text{C}$                      | -100  |      | +100  | nA            |

| <b>Overvoltage Lockout (OVLO) (MAX17617 only)</b> |                  |                                                               |       |      |       |               |

| OVLO Threshold                                    |                  | OVLO Rising                                                   | 0.911 | 0.93 | 0.948 | V             |

|                                                   |                  | OVLO Falling                                                  | 0.882 | 0.90 | 0.918 |               |

| OVLO Leakage Current                              | $I_{OVLO\_LEAK}$ | $V_{OVLO} = 1V, T_A = +25^\circ\text{C}$                      | -100  |      | +100  | nA            |

(特に指定のない限り、 $V_{IN} = V_{SN} = 3V \sim 80V$ 、 $GN = \text{オープン}$ 、UVLO、OVLO/OVFB、EN、IMON、PGOOD/T<sub>J</sub>、OUTUV、I<sub>START</sub>/CLMODE、FLAG、PLIM = オープン、 $R_{SETI} = 2.13k\Omega$ 、 $V_{CC} = 2.2\mu F$ をGNDとの間に接続、 $T_A = -40^\circ C \sim +125^\circ C$ 。代表値は $V_{IN} = 48V$ 、 $T_A = +25^\circ C$ での値 (Note 2を参照)。)

| PARAMETER                                               | SYMBOL         | CONDITIONS                                                                                             |                                                                | MIN                | TYP   | MAX       | UNITS |  |

|---------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------|-------|-----------|-------|--|

| <b>Output Overvoltage Clamp (OVFB) (MAX17617A only)</b> |                |                                                                                                        |                                                                |                    |       |           |       |  |

| Overvoltage Clamp Reference                             | $OVFB_{REF}$   |                                                                                                        |                                                                | 0.784              | 0.800 | 0.816     | V     |  |

| Overshoot on OVFB                                       |                | IN Slew Rate < 0.1V/ $\mu s$                                                                           | $C_{LOAD} = 4.7\mu F$ ,<br>$I_{LIM} = 7A$ ,<br>$I_{LOAD} = 1A$ | 0                  |       | mV        |       |  |

|                                                         |                | IN Slew Rate < 1V/ $\mu s$                                                                             | $C_{LOAD} = 4.7\mu F$ ,<br>$I_{LIM} = 7A$ ,<br>$I_{LOAD} = 1A$ | 0                  |       |           |       |  |

| <b>Current Limit and Monitoring (SETI and IMON)</b>     |                |                                                                                                        |                                                                |                    |       |           |       |  |

| Current Limit Adjustment Range                          | $I_{LIM}$      |                                                                                                        |                                                                | 0.7                | 7.0   | 7.0       | A     |  |

| Current Limit Threshold Accuracy                        | $I_{LIM\_ACC}$ | $0.7A < I_{LIM} < 2A$                                                                                  |                                                                | -7                 | +7    | %         |       |  |

|                                                         |                | $2A \leq I_{LIM} < 3A$                                                                                 |                                                                | -4                 | +4    |           |       |  |

|                                                         |                | $3A \leq I_{LIM} \leq 7A$                                                                              |                                                                | -3                 | +3    |           |       |  |

| Overcurrent Response Time                               | $t_{SOC}$      | $I_{LIM} = 1A$ , $I_{OUT}$ step from 0.5A to 3A, Time to regulate $I_{OUT}$ to Current Limit           |                                                                | 20                 |       | $\mu s$   |       |  |

| Short-Term Over Current Limit                           | $I_{STLIM}$    |                                                                                                        |                                                                | $2 \times I_{LIM}$ |       | A         |       |  |

| Short-Term Over Current Limit Blanking Time             | $t_{STOC}$     |                                                                                                        |                                                                | 400                |       | $\mu s$   |       |  |

| Overcurrent Protection Threshold                        | $I_{OCP}$      | (See Figure 16 in the <a href="#">Short Circuit Protection</a> Section)                                | (See Note 3)                                                   | 22                 | 30    | 36        | A     |  |

| Overcurrent Protection Response Time                    | $t_{OCP}$      | $I_{LIM} = 7A$ , $I_{OUT}$ step from 3.5A to 40A, Time to turn off the switch once $I_{OUT} > I_{OCP}$ | (See Note 3)                                                   | 1                  |       | $\mu s$   |       |  |

| IMON Accuracy                                           | $I_{MON\_ACC}$ | $0.7A < I_{LIM} < 2A$                                                                                  | $I_{OUT} < I_{LIM}$                                            | -6                 | +6    | %         |       |  |

|                                                         |                | $2A \leq I_{LIM} < 3A$                                                                                 | $I_{OUT} < I_{LIM}$                                            | -3                 | +3    |           |       |  |

|                                                         |                | $3A \leq I_{LIM} \leq 7A$                                                                              | $I_{OUT} < I_{LIM}$ , $T_A = +125^\circ C$                     | -2.5               | +2.5  |           |       |  |

|                                                         |                |                                                                                                        | $I_{OUT} < I_{LIM}$ , $T_A = +85^\circ C$                      | -2                 | +2    |           |       |  |

| IMON Range                                              |                |                                                                                                        |                                                                | 0                  | 1.25  | 1.25      | V     |  |

| SETI/IMON Current Ratio                                 |                |                                                                                                        |                                                                | 21300              |       | A/A       |       |  |

| SETI Clamp                                              |                |                                                                                                        |                                                                | 1.59               | 1.81  | 1.81      | V     |  |

| IMON Clamp                                              |                |                                                                                                        |                                                                | 1.49               | 1.69  | 1.69      | V     |  |

| SETI Fault                                              |                |                                                                                                        |                                                                | 400                |       | $mV$      |       |  |

| SETI Resistance                                         |                | $I_{LIM} = 7A$                                                                                         |                                                                | 2.13               |       | $k\Omega$ |       |  |

| SETI Regulation Voltage                                 |                |                                                                                                        |                                                                | 0.7                |       | V         |       |  |

| SETI Range                                              |                |                                                                                                        |                                                                | 0                  | 1.4   | 1.4       | V     |  |

(特に指定のない限り、 $V_{IN} = V_{SN} = 3V \sim 80V$ 、 $GN =$  オープン、UVLO、OVLO/OVFB、EN、IMON、PGOOD/T<sub>J</sub>、OUTUV、I<sub>START</sub>/CLMODE、FLAG、PLIM = オープン、 $R_{SETI} = 2.13k\Omega$ 、 $V_{CC} = 2.2\mu F$  を GND との間に接続、 $T_A = -40^\circ C \sim +125^\circ C$ 。代表値は  $V_{IN} = 48V$ 、 $T_A = +25^\circ C$  での値 (Note 2 を参照)。)

| PARAMETER                                                    | SYMBOL            | CONDITIONS                                                | MIN               | TYP                     | MAX   | UNITS |

|--------------------------------------------------------------|-------------------|-----------------------------------------------------------|-------------------|-------------------------|-------|-------|

| <b>Reverse Current Protection</b>                            |                   |                                                           |                   |                         |       |       |

| Slow Reverse Current Blocking Threshold                      | $V_{RIB\_SLOW}$   | $(V_{IN} - V_{OUT})$ falling                              | -1                | -5                      | -10   | mV    |

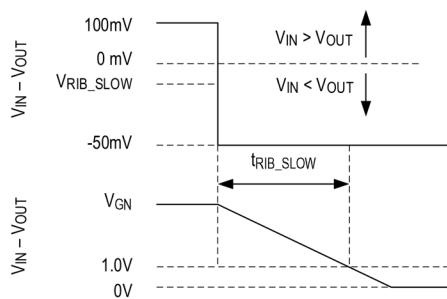

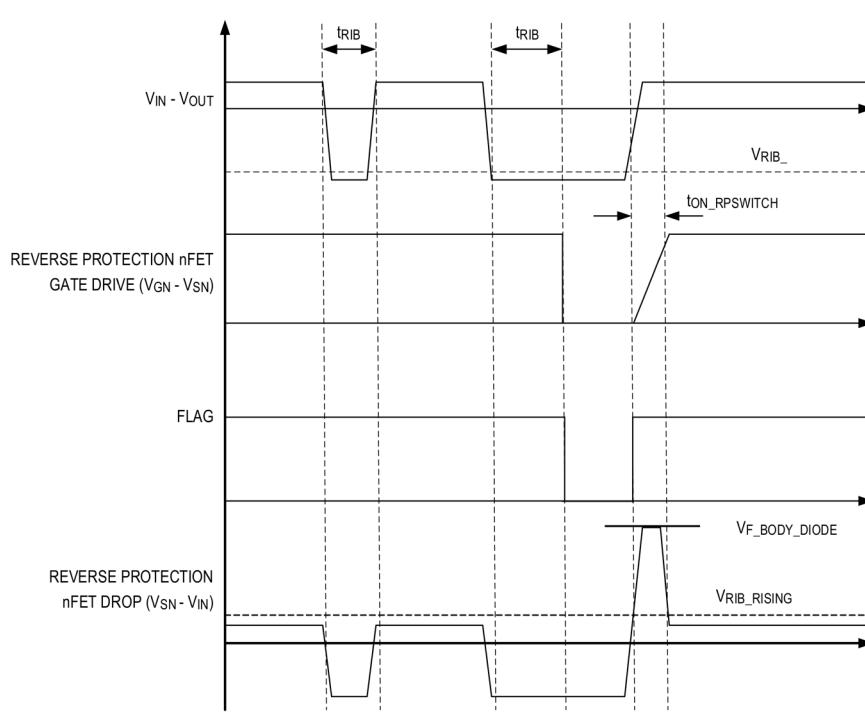

| Slow Reverse Current Blocking Response Time                  | $t_{RIB\_SLOW}$   | (See <a href="#">Figure 1</a> ), CGN-SN = 20nF            |                   | 20                      | 30    | μs    |

| Fast Reverse Current Blocking Threshold                      | $V_{RIB\_FAST}$   | $(V_{IN} - V_{OUT})$ falling                              | -70               | -100                    | -130  | mV    |

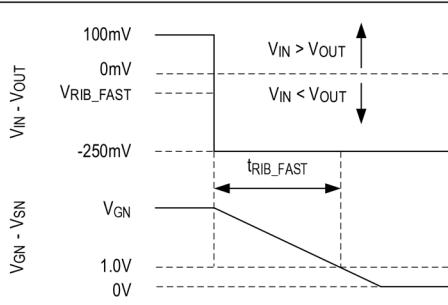

| Fast Reverse Current Blocking Response Time                  | $t_{RIB\_FAST}$   | (See <a href="#">Figure 2</a> ), CGN-SN = 20nF            |                   | 100                     | 160   | ns    |

| Reverse Current Blocking Rising Threshold Voltage            | $V_{RIB\_RISING}$ | $(V_{SN} - V_{OUT})$ Rising                               | 70                | 100                     | 130   | mV    |

| Reverse Output Current drawn from OUT                        | $I_{OUT\_REV}$    | $V_{SN} = 0V$ , $V_{OUT} = 48V$ , IN = OPEN               |                   | 9                       |       | mA    |

| <b>Power Limit</b>                                           |                   |                                                           |                   |                         |       |       |

| PLIM Threshold                                               | $V_{PLIM\_TH}$    |                                                           | 0.3               |                         |       | V     |

| PLIM Operating Range                                         |                   |                                                           | $V_{PLIM\_TH}$    | $3 \times V_{PLIM\_TH}$ |       | V     |

| <b>Gate Drive (GN, SN)</b>                                   |                   |                                                           |                   |                         |       |       |

| External Reverse Protection nFET Gate Drive Voltage          | $V_{GN\_SN}$      | EN = High, No-Fault Condition                             | $V_{IN} \geq 10V$ | 6                       | 6.5   | 7     |

| Gate Active Pullup Current                                   |                   | EN = High, $V_{GN} = V_{SN}$ , No Reverse Fault Condition | 80                | 100                     | 120   | μA    |

| Gate Pulldown Resistance                                     |                   | EN = High, External nFET OFF                              | 60                | 120                     |       | Ω     |

|                                                              |                   | Always present                                            | 3                 |                         |       | MΩ    |

| <b>Internal FET</b>                                          |                   |                                                           |                   |                         |       |       |

| Internal nFET ON Resistance                                  | $R_{ON}$          | $I_{LOAD} = 100mA$                                        | 20                | 40                      |       | mΩ    |

| <b>FLAG Output</b>                                           |                   |                                                           |                   |                         |       |       |

| Logic-Low Voltage                                            |                   | $I_{SINK} = 1mA$                                          |                   | 0.4                     |       | V     |

| Leakage Current                                              |                   | $V_{PULLUP} = 5V$ , PGOOD/T <sub>J</sub> Open-Drain OFF   |                   | 1                       |       | μA    |

| <b>Power Good Output (PGOOD/T<sub>J</sub>)</b>               |                   |                                                           |                   |                         |       |       |

| Logic-Low Voltage                                            |                   | $I_{SINK} = 1mA$                                          |                   | 0.4                     |       | V     |

| Leakage Current                                              |                   | $V_{PULLUP} = 5V$ , PGOOD/T <sub>J</sub> Open-Drain OFF   |                   | 1                       |       | μA    |

| <b>Output Under Voltage Sensing (OUTUV)</b>                  |                   |                                                           |                   |                         |       |       |

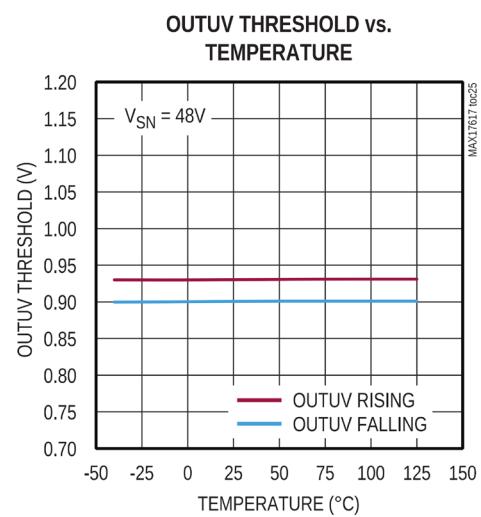

| OUTUV Threshold                                              |                   | OUTUV Rising                                              | 0.911             | 0.93                    | 0.948 | V     |

|                                                              |                   | OUTUV Falling                                             | 0.882             | 0.90                    | 0.918 |       |

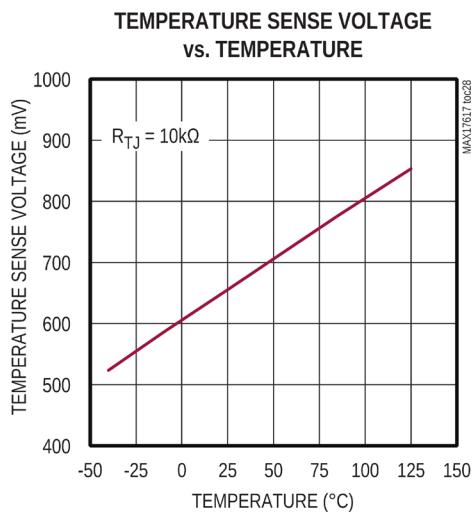

| <b>Junction Temperature Monitoring (PGOOD/T<sub>J</sub>)</b> |                   |                                                           |                   |                         |       |       |

| Accuracy                                                     |                   | $T_A = +25^\circ C$                                       | -9                | 9                       |       | °C    |

(特に指定のない限り、 $V_{IN} = V_{SN} = 3V \sim 80V$ 、 $GN = \text{オープン}$ 、UVLO、OVLO/OVFB、EN、IMON、PGOOD/T<sub>J</sub>、OUTUV、I<sub>START</sub>/CLMODE、FLAG、PLIM =  $\text{オープン}$ 、 $R_{SETI} = 2.13k\Omega$ 、 $V_{CC} = 2.2\mu F$ をGNDとの間に接続、 $T_A = -40^\circ C \sim +125^\circ C$ 。代表値は $V_{IN} = 48V$ 、 $T_A = +25^\circ C$ での値 (Note 2を参照)。)

| PARAMETER                                                           | SYMBOL                   | CONDITIONS                                                                                | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------|------|------|------|-------|

| T <sub>J</sub> voltage                                              |                          | T <sub>A</sub> = +25°C, R <sub>TJ</sub> = 10kΩ to GND                                     |      | 652  |      | mV    |

|                                                                     |                          | T <sub>A</sub> = +125°C, R <sub>TJ</sub> = 10kΩ to GND                                    |      | 854  |      |       |

| dV/dTemp                                                            |                          | T <sub>A</sub> = +25°C to +125°C                                                          |      | 2    |      | mV/°C |

| T <sub>J</sub> Current Limit                                        |                          |                                                                                           | 100  |      | 600  | μA    |

| <b>Timing characteristics</b>                                       |                          |                                                                                           |      |      |      |       |

| IN Debounce Time                                                    | t <sub>DEB</sub>         | Time from $V_{IN} > V_{UVLO\_R}$ and Internal FET turn-on starts                          | 0.9  | 1    | 1.1  | ms    |

| INUVLO Blanking Time                                                | t <sub>INUVLOBLANK</sub> | Power-up FLAG assertion blanking time                                                     |      | 0.5  |      | ms    |

| EN Turn-On Time                                                     |                          | Delay from EN = 1 for the part to turn on Internal FET (provided $V_{IN} > V_{UVLO\_R}$ ) |      | 2.5  |      | ms    |

| Internal nFET Turn-On Time                                          | t <sub>ON_SWITCH</sub>   | From No Fault to $I_{OUT} = 1A$                                                           |      | 150  |      | μs    |

| Delay between Internal nFET Turn-On and External nFET Turn-On       | t <sub>DR</sub>          |                                                                                           | 90   | 100  | 110  | μs    |

| The delay between Internal nFET Turn-Off and External nFET Turn-Off | t <sub>DF</sub>          |                                                                                           | 90   | 100  | 110  | μs    |

| Undervoltage Lock Out Turn OFF Time                                 | t <sub>OFF_UVLO</sub>    | $V_{UVLO}$ falling from 1V to 0.8V                                                        |      | 1    |      | μs    |

| Oversupply Lock Out Turn OFF Time                                   | t <sub>OFF_OVLO</sub>    | $V_{OVLO}$ rising from 0.8V to 1V                                                         |      | 1    |      | μs    |

| Undervoltage Lock Out Rising Edge Debounce Time                     | t <sub>DEB_UVLO</sub>    | $V_{IN}$ rising                                                                           |      | 10   |      | μs    |

| Oversupply Lock Out Falling Edge Debounce Time                      | t <sub>DEB_OVLO</sub>    | $V_{IN}$ falling                                                                          |      | 10   |      | μs    |

| Auto Retry Time                                                     | t <sub>RETRY</sub>       |                                                                                           |      | 800  |      | ms    |

| Blanking Time                                                       | t <sub>BLANK</sub>       |                                                                                           | 21.8 | 24.0 | 26.4 | ms    |

| Startup Timeout                                                     | t <sub>STO</sub>         |                                                                                           | 1080 | 1200 | 1320 | ms    |

| Loss of Ground Switch Turn OFF Time                                 |                          | $C_{VCC} = 2.2\mu F$                                                                      |      | 100  |      | ms    |

| <b>Thermal Protection</b>                                           |                          |                                                                                           |      |      |      |       |

| Thermal Foldback                                                    | T <sub>J(FB)</sub>       |                                                                                           |      | 150  |      | °C    |

| Thermal Shutdown                                                    | T <sub>J</sub>           |                                                                                           |      | 165  |      | °C    |

| Thermal Shutdown Hysteresis                                         | T <sub>J(HYS)</sub>      |                                                                                           |      | 20   |      | °C    |

**Note 2 :** すべてのデバイスは $T_A = +25^\circ C$ で100%製品テストしています。動作温度範囲を超える制限値は設計により裏付けられており、製品テストは行っておりません。

**Note 3 :** 設計により裏付けられていますが、製品テストは行っていません。

## タイミング図

図1. 低速逆電流ブロッキング応答時間

図2. 高速逆電流ブロッキング応答時間

## 標準動作特性

## CURRENT LIMIT RESPONSE

## OUTPUT SHORT-CIRCUIT RESPONSE

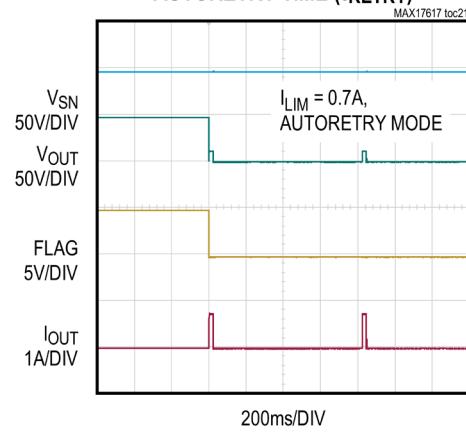

THERMAL FOLDBACK DUE TO

OUTPUT SHORT-CIRCUITAUTORETRY TIME ( $t_{RETRY}$ )

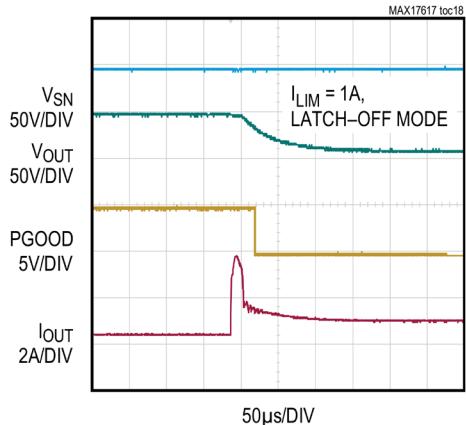

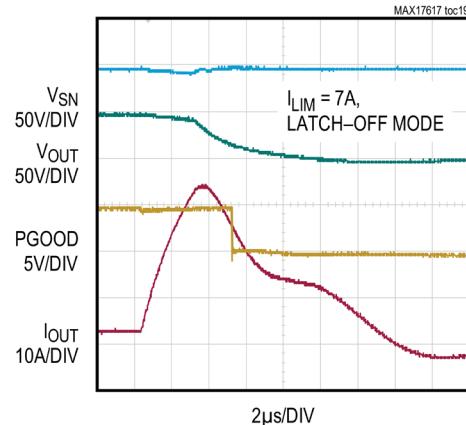

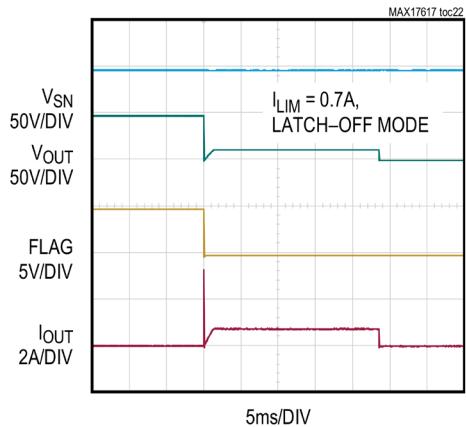

## LATCH-OFF CURRENT LIMIT

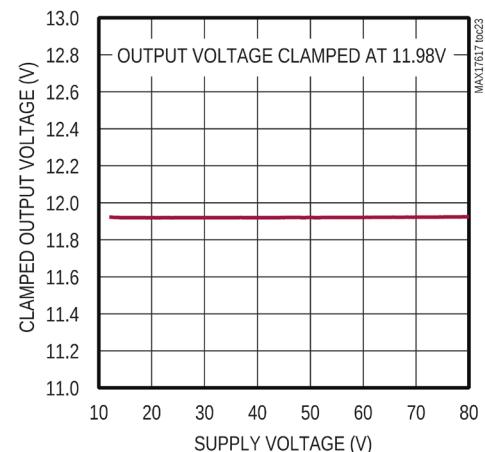

CLAMPED OUTPUT VOLTAGE VS.

SUPPLY VOLTAGE

## ピン配置

## 端子説明

| 端子       |           | 名称                         | 機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-----------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX17617 | MAX17617A |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1        | 1         | SETI                       | 電流制限調整ピン。SETIとGNDの間に抵抗を接続して電流制限値を設定します。 <a href="#">電流制限スレッショルドの設定</a> のセクションを参照してください。SETIには30pFを超えるコンデンサは接続しないでください。                                                                                                                                                                                                                                                                                                                                                                                                |

| 2        | 2         | UVLO                       | 入力低電圧ロックアウト(UVLO)調整ピン。SN/INとGNDの間に抵抗分圧器を接続して、UVLOスレッショルドを設定します。UVLO機能を使用しない場合は、UVLOスレッショルドより高い電圧にUVLOを接続します。                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3, 13    | 3, 13     | IN                         | 入力ピン。ホット・プラグイン・アプリケーションについては <a href="#">アプリケーション情報</a> のセクションを参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4        | 4         | GN                         | 外付け逆保護nFETのゲート・ドライバ出力。外付けnFETを使用しない場合は、SN端子とGN端子をINに接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5        | 5         | SN                         | 外付け逆保護nFETのリターンおよび入力電圧検出ピン。標準アプリケーション回路に示すように、外付けnFETのソースに接続します。外付けnFETを使用しない場合は、SN端子とGN端子をINに接続します。                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6-12     | 6-12      | OUT                        | 出力ピン。出力ケーブルが長い場合、または誘導性負荷の場合は、 <a href="#">アプリケーション情報</a> のセクションを参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14       | -         | OVLO                       | OVLO調整ピン。SN/INとGNDの間に抵抗分圧器を接続して、OVLOスレッショルドを設定します。OVLOをGNDに接続すると、OVLO機能が無効化されます。                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -        | 14        | OVFB                       | 出力電圧クランプ機能用の出力電圧フィードバック・ピン。OUTとGNDの間に抵抗分圧器を接続して、出力電圧クランプ・スレッショルドを設定します。使用しない場合はOVFBをGNDに接続します。 <a href="#">入力電圧のサージ除去と出力過電圧フィードバック・レギュレーション(OVFB)</a> のセクションを参照してください。                                                                                                                                                                                                                                                                                                                                                |

| 15       | 15        | PLIM                       | 電力制限調整ピン。PLIMを外付け抵抗分圧器に接続すると、電力制限機能が起動するスレッショルドを定義し、電流制限スレッショルドを低下させることができます。この機能を無効化し、SETIに配置された抵抗のみで電流制限を設定する場合は、PLIMをGNDに接続します。                                                                                                                                                                                                                                                                                                                                                                                    |

| 16       | 16        | OUTUV                      | PGOODコンパレータ入力の出力低電圧検出。OUTピンとGNDピンの間に抵抗分圧器を接続して、OUTUVスレッショルドを設定します。                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17       | 17        | I <sub>START</sub> /CLMODE | 起動時突入電流制限／電流制限モードの選択および逆保護nFET有無プログラミング・ピン。I <sub>START</sub> /CLMODEピンとGNDの間に抵抗を接続して、起動時電流制限および電流制限モードを設定します。 <a href="#">起動時突入電流制限(I<sub>START</sub>)</a> のセクションを参照してください。                                                                                                                                                                                                                                                                                                                                          |

| 18       | 18        | FLAG                       | オープン・ドレインのフォルト・インジケータ出力。FLAG機能を使用する場合は、FLAGを外部バイアス電圧にプルアップします。FLAG機能については <a href="#">フォルト出力(FLAG)</a> のセクションを参照してください。                                                                                                                                                                                                                                                                                                                                                                                               |

| 19       | 19        | EN                         | アクティブ・ハイのイネーブル入力。内部で1.5Vにプルアップされています。無接続のままにすると常時オン動作します。                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20       | 20        | PGOOD/ T <sub>J</sub>      | オープン・ドレインのパワー・グッド出力またはダイ温度モニタ出力。PGOOD機能を使用する場合は、PGOOD/T <sub>J</sub> を外部バイアス電圧にプルアップします。PGOODは次の条件でハイにプルアップされます。 <ul style="list-style-type: none"><li>V<sub>OUT</sub>がOUTUVの立上がりスレッショルドを超過し、(V<sub>IN</sub> - V<sub>OUT</sub>) &lt; V<sub>FA</sub>の条件が満たされる場合。PGOODは次の条件でローにプルダウンされます。</li><li>V<sub>OUT</sub>がOUTUVの立下がりスレッショルドより低下した場合。</li></ul> このピンは、ダイ温度のモニタリングにも使用できます。PGOOD/T <sub>J</sub> とGNDの間に10kΩ～20kΩの抵抗を接続して、デバイスの温度を計測します。詳細については、 <a href="#">ダイ温度のモニタリング(PGOOD/T<sub>J</sub>)</a> のセクションを参照してください。 |

| 21       | 21        | IMON                       | 電流モニタリングの出力ピン。IMONとGNDの間に抵抗を接続して、電流モニタの読み出しを設定します。 <a href="#">電流モニタリング(IMON)</a> のセクションを参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 22       | 22        | GND                        | グランド・ピン。すべての制御信号に対するリファレンス・ピン。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 23       | 23        | V <sub>cc</sub>            | 内部LDOの出力。最小2.2μF/0603の低ESRセラミック・コンデンサをV <sub>cc</sub> とGNDの間に接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## 機能図

## 詳細説明

MAX17617/MAX17617A は、入力電圧フォルトおよび出力過電流フォルトからシステムを保護するための、極めて汎用的かつプログラマブルな保護領域を備えています。また、MAX17617/MAX17617A には、プログラマブルな電力制限機能も備わっています。オン抵抗が低い（代表値 20mΩ）内蔵 nFET により、（正極性）入力電圧フォルトに対し、最大+80V（逆電流保護なし）／+75V（逆電流保護あり）まで保護します。このデバイスは、外付けの分圧器によって設定可能な低電圧ロックアウト（UVLO）スレッショルドを備えています。MAX17617 はプログラマブルな過電圧ロックアウト（OVLO）機能を備えています。MAX17617A は OVFB ピンによって設定可能な出力電圧クランプ機能を備えており、入力のトランジエント・サージ発生時に出力電圧を制限するレギュレーションを行います。入力低電圧保護機能と過電圧保護機能（MAX17617）／出力電圧クランプ機能（MAX17617A）は 3V～80V の動作範囲全域で設定できます。

入力の逆極性保護は、デバイスが制御する外付け nFET を使用して行います。逆極性電圧保護の能力は、動作中の負荷バス電圧（V<sub>out</sub>）と外付け nFET の電圧ブロック能力に依存します。例えば、V<sub>out</sub>=30V で-55V の入力電圧範囲まで保護する場合、定格 85V の外付け nFET が必要となります。外付け nFET は、オプションの逆電流保護にも必要となります。逆保護用の外付け nFET（Q1）を使用する場合、デバイスは Q1 をオフにすることによって負荷から電源への逆電流の発生を防止します。逆電流スレッショルドと逆電流保護機能の順方向バイアスの特性は、ORing（OR 結合）や電力マルチプレクサのアプリケーションに適した理想ダイオード機能を示すように調整します。逆極性保護と逆電流保護が不要な場合は、SN ピンと GN ピンを IN に接続する必要があります。このデバイスは、出力端子間の誤配線によって出力に逆極性が印加されてしまった場合でも耐性があります。

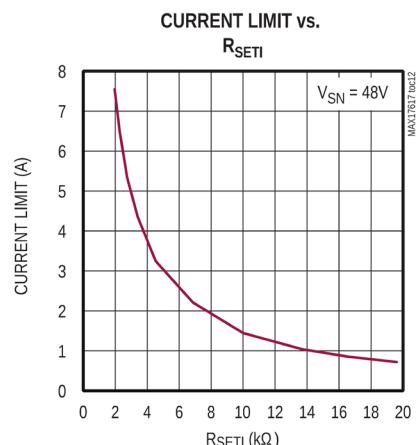

このデバイスの電流制限は、SETI ピンと GND の間に抵抗を接続することによって設定します。電流制限は 0.7A～7.0A の範囲でプログラミできます。デバイスを通過する電流が、設定した電流制限値以上になると、内部 nFET の抵抗が変化して電流が制限されます。このデバイスには、連続モード、自動再試行モード、ラッチオフ・モードの 3 つの電流制限動作モードがあります。更に、このデバイスにはプログラマブルな起動時の突入電流制限機能があり、容量性もしくは負性インピーダンスの出力負荷に電源から突入電流が流れるのを防止します。

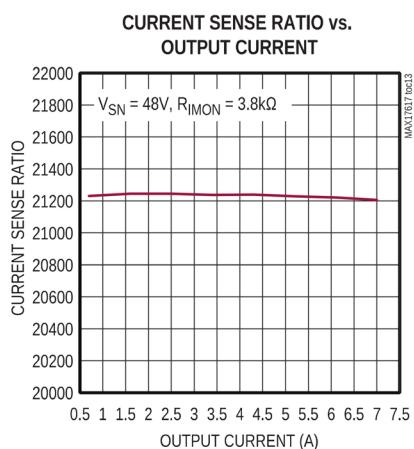

IMON ピンには、通常動作時にデバイス電流に比例する電流が発生します。IMON 抵抗を（IMON と GND の間に）配置すると、IMON ピンの電圧はデバイス電流に比例した電圧になります。この電圧をモニタリング・システムによって読み出すことで、デバイスの瞬時電流を記録することができます。測定電流の帯域幅を制限するには、オプションで IMON と GND の間に 100nF のセラミック・コンデンサを配置します。

デバイスは、コントローラの監視システムによるイネーブル入力 EN を制御することでオンまたはオフに動作を変更できます。これによってコントローラの監視システムは、接続された負荷への電力供給をオンまたはオフに変更できます。

このデバイスは接地喪失保護機能を備えており、接地喪失フォルト・イベントが発生した場合、例えば、冗長安全アプリケーションで安全接地用ヒューズが切れた場合、デバイスの動作を安全にオフにできます。

デバイスは、動作やフォルトに関する信号を示すステータス通知信号（FLAG）を備えています。また、パワー・グッド信号（PGOOD/T<sub>j</sub>）も備えており、監視システムが下流の負荷を有効化／無効化するために使用できます。FLAG および PGOOD/T<sub>j</sub> はオープン・ドレイン・ピンであり、適切なシステム・インターフェースへの外付けプルアップ抵抗が必要です。

このデバイスには、プログラマブルな出力低電圧検出スレッショルドがあり、出力電圧が OUTUV を下回った後、立上がりスレッショルドを再び超えたときの再起動の応答を制御します。このデバイスは、消費電力が過剰になることを防ぐ内部サーマル・シャットダウン保護機能も備えています。

### 入力低電圧ロックアウト (UVLO)

このデバイスのUVLO調整範囲は3V～79Vです。UVLOスレッショルド電圧を調整するには、UVLOピンに外付けの抵抗分圧器を図3に示すように接続します。次式を用いてUVLO電圧を調整できます。バッテリ電源など低バイアス電流のアプリケーションでは、R1の推奨値は2.2MΩです。

$$V_{UVLO} = V_{UVLO\_RISING} \times \left( 1 + \frac{R_1}{R_2} \right)$$

図3. 調整可能な入力UVLO

UVLOピンには30mV(代表値)のヒステリシスが存在するため、低電圧状態への出入りが決定論的に行われます。UVLOピンの電圧が0.9V(代表値)より低くなると、内蔵のnFETがオフになります。外付けのnFETを使用している場合は、100μsの遅延時間( $t_{DF}$ )後にnFETがオフになります。低電圧条件が解除され、UVLOピンの電圧が0.93V(代表値)より高くなると、デバイスは低電圧ロックアウトからの立上がり(ロックからの解除)エッジ・デバウンス時間( $t_{DEB\_UVLO}$ )だけ待った後にスイッチをオンにするプロセスを開始します。先に内蔵のnFETがオンになり、100μsの遅延時間( $t_{DR}$ )が経過した後に、外付けのnFETがオンになります。また、FLAGのアサートが解除されます。UVLOピンは無接続のままにしないでください。

UVLOピンが立上がりスレッショルドより高い電圧に上昇した場合と、立下がりスレッショルドより低い電圧に低下した場合の、低電圧による代表的なオン・シーケンスとオフ・シーケンスを示します。詳細は図4を参照してください。

図4. 入力低電圧フォルトのタイミング図

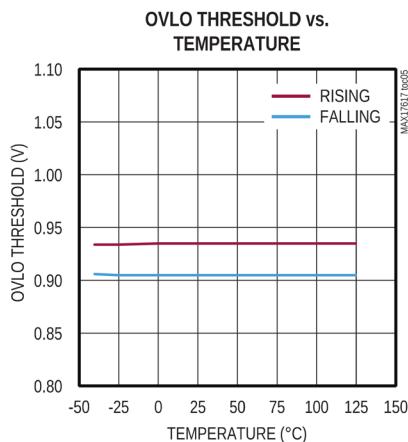

### 入力過電圧ロックアウト (OVLO)

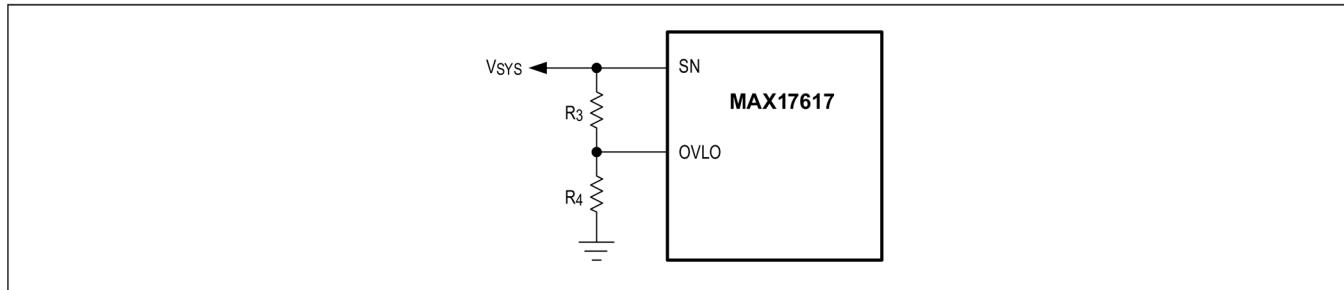

MAX17617 の OVLO 調整範囲は 3.5V～80V です。OVLO スレッショルド電圧を調整するには、OVLO ピンに外付けの抵抗分圧器を図 5 に示すように接続します。次式を用いて OVLO 電圧を調整できます。バッテリ電源など低バイアス電流のアプリケーションでは、R3 の推奨値は 2.2MΩ です。

$$V_{OVLO} = V_{OVLO\_RISING} \times \left( 1 + \frac{R_3}{R_4} \right)$$

図 5. 調整可能な入力 OVLO

OVLO ピンには 30mV (代表値) のヒステリシスが存在するため、過電圧状態への出入りが決定論的に行われます。OVLO ピンの電圧が 0.93V (代表値) より高くなると、内蔵の nFET がオフになり、FLAG がローにアサートされます。外付けの nFET を使用している場合は、100μs の遅延時間 (t<sub>DF</sub>) 後に nFET がオフになります。過電圧条件が解除され、OVLO ピンの電圧が 0.9V (代表値) より低下すると、MAX17617 は過電圧ロックアウトからの立上がり (ロックからの解除) エッジ・デバウンス時間 (t<sub>DEB\_OVLO</sub>) だけ待った後にスイッチをオンにするプロセスを開始します。先に内蔵の nFET がオンになり、100μs の遅延時間 (t<sub>DR</sub>) が経過した後に、外付けの nFET がオンになります。また、FLAG のアサートが解除されます。OVLO 機能を使用しない場合、OVLO ピンは GND に接続する必要があります。OVLO ピンは無接続のままにしないでください。

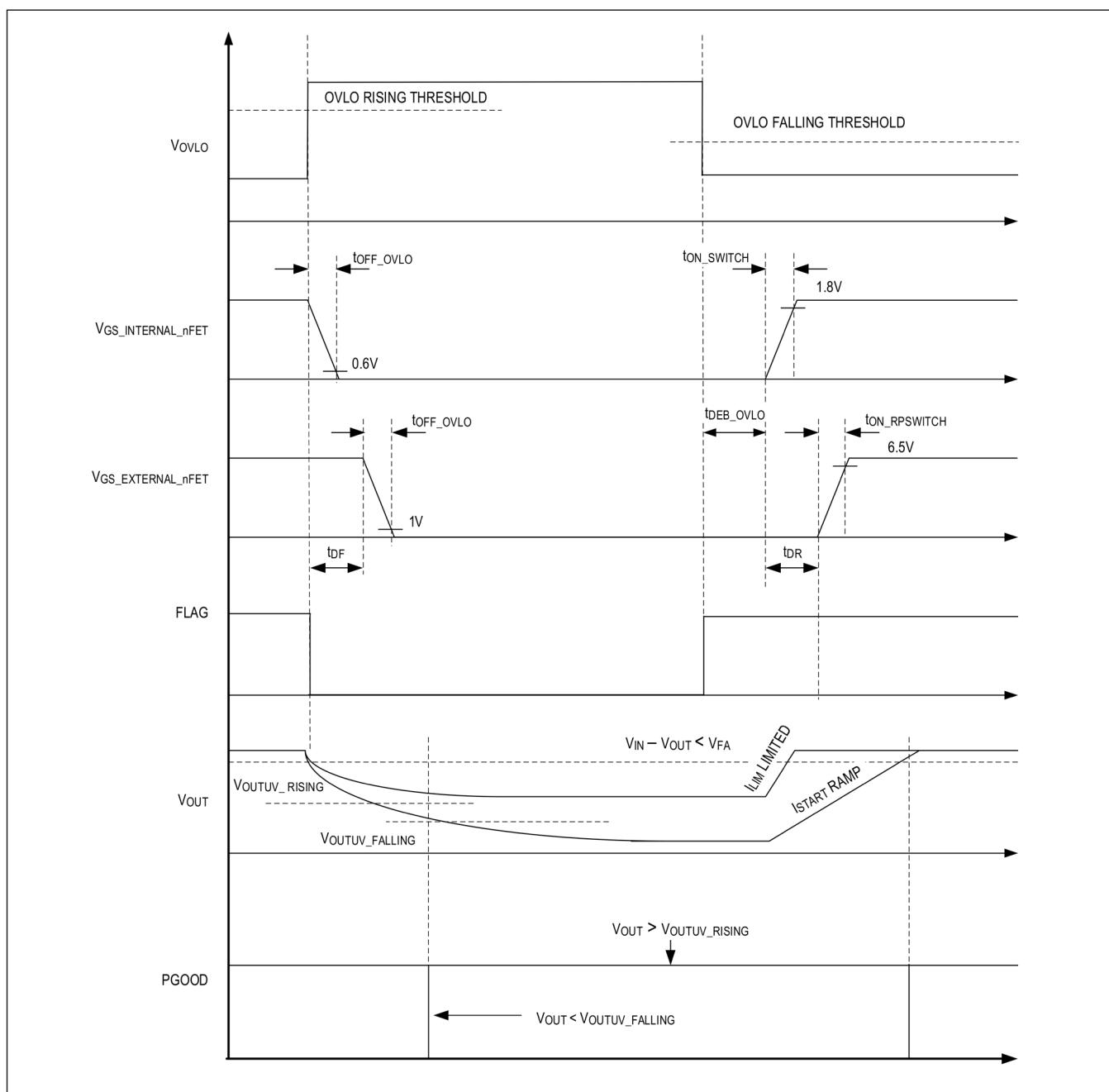

OVLO ピンの電圧が立上がりスレッショルドより高く上昇し、立下がりスレッショルドより低下したときの、過電圧による代表的なオフ・シーケンスとオン・シーケンスを図 6 に示します。

図6. 入力過電圧フォルトのタイミング図

## 入力デバウンス保護

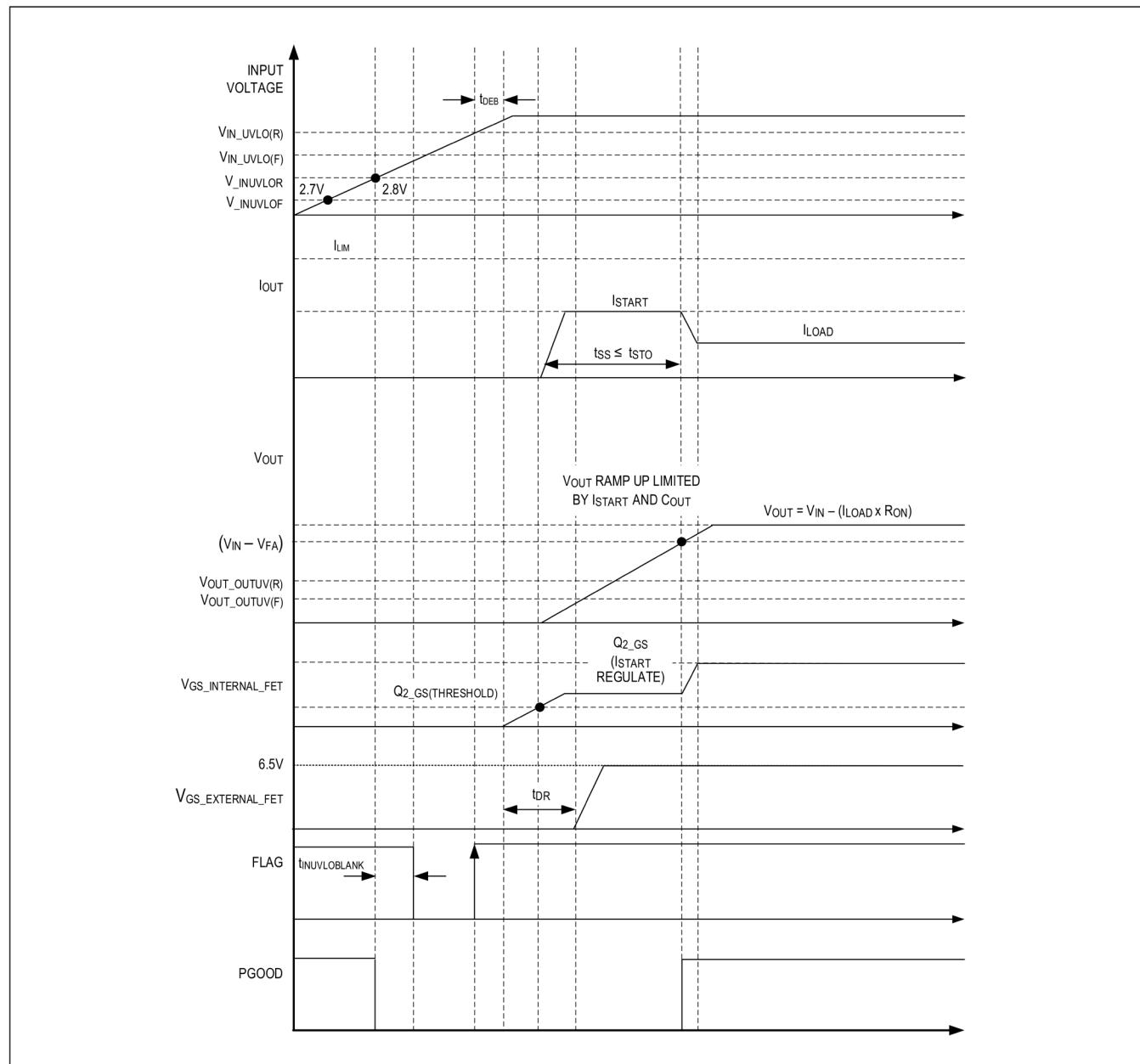

このデバイスには入力デバウンス保護機能があります。デバウンス時間 ( $t_{DEB}$ ) より長い時間、IN ピンの電圧が立上がりスレッショルド  $V_{IN\_UVLO(R)}$  より高くなった場合のみ、デバイスは動作を開始 (nFET をオン) します。 $t_{DEB}$  が経過する前に、IN ピンの電圧が立下がりスレッショルド  $V_{IN\_UVLO(F)}$  より低下すると、デバイスはオフのままになります。デバイスが EN によってオンになっている場合は、 $t_{DEB} + EN$  オン時間が常に存在します。代表的な入力パワーアップのタイミング・シーケンスを図 7 に示します。

初期パワーアップ中は (ホット・プラグイン、制御された入力電圧スルーレートなどいずれの場合も)、入力電圧が  $V_{INUVLOR}$  (最大 2.86V) を交差した後、 $t_{INUVLOBLANK} = 500\mu s$  (代表値) まで入力電圧が UVLO ピンで設定された電圧に達しなければ、デバイスは FLAG をローにアサートして UVLO フォルトを通知します。

図 7. 入力パワーアップのタイミング図

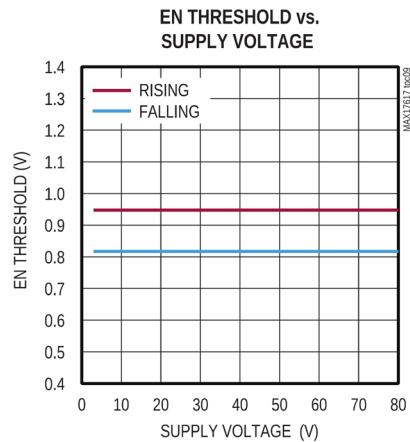

## イネーブル

MAX17617/MAX17617A は、イネーブル入力ピン (EN) を使用してオンやオフを行い、接続された負荷への給電を制御することができます。ラッチオフ・モードにおいて、フォルト状態をリセットし、デバイスの動作を再開するためには、EN ピンを  $10\mu\text{s}$  以上  $0.4\text{V}$  未満にプルダウンすることが必要です。EN 端子は内部で  $1.5\text{V}$  にプルアップされていて、オープンにしておくと常時オン・オプションになります。

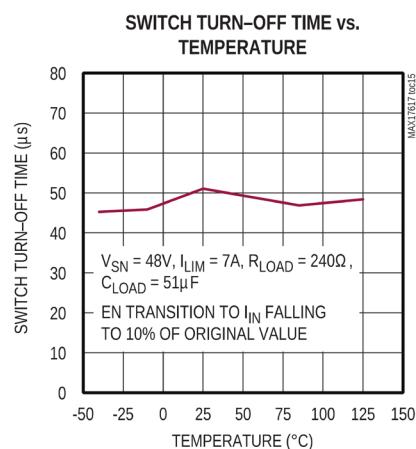

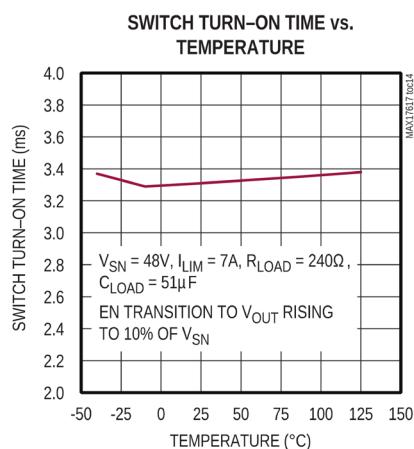

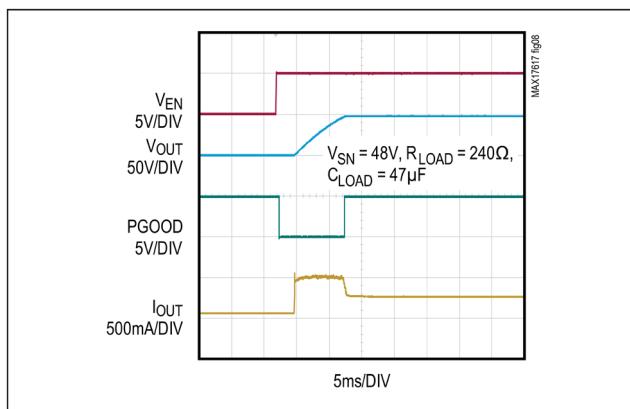

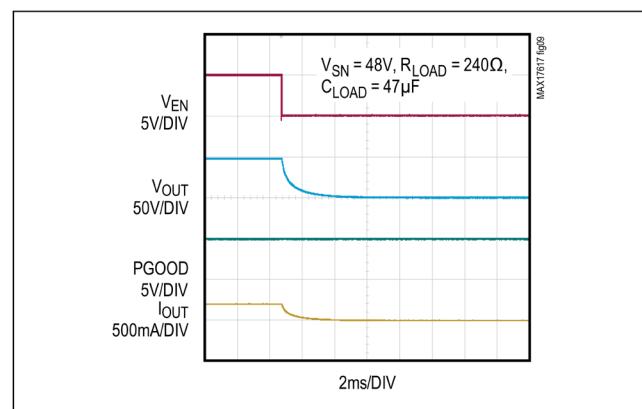

図 8 および図 9 に、EN を用いたターンオン制御とターンオフ制御を示します。

図 8. EN ピンによるターンオン制御

図 9. EN ピンによるターンオフ制御

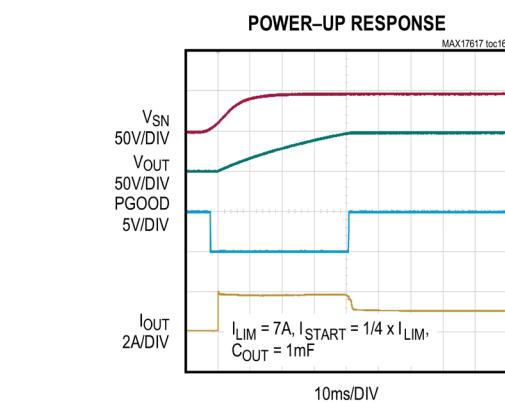

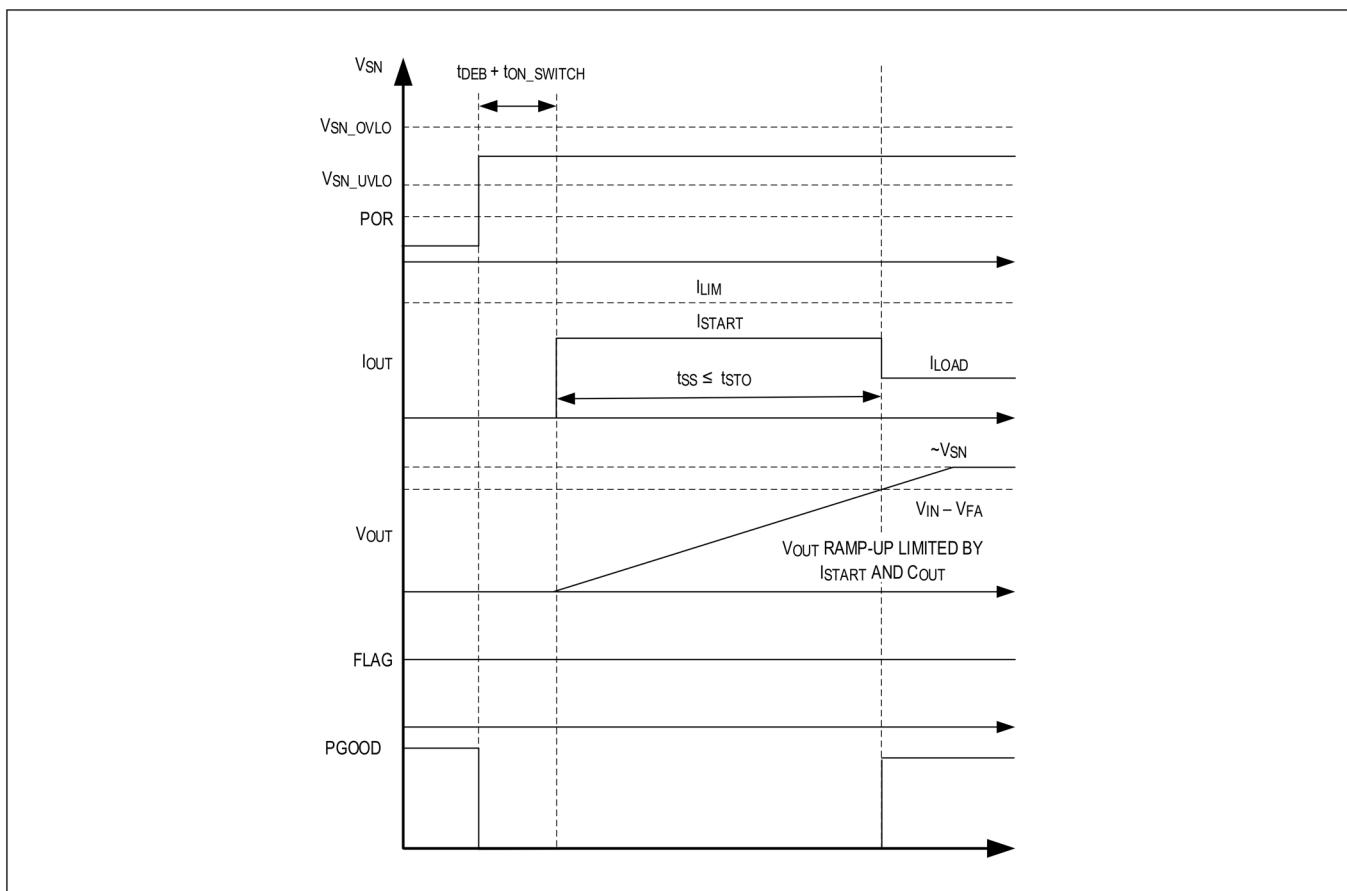

## 起動時突入電流制限 (I<sub>START</sub>)

このデバイスにはプログラマブルな起動時の突入電流制限機能があり、大きな容量性の負荷に電源から突入電流が流れるのを防止します。起動タイムアウト時間中 ( $t_{STO}$ )、 $V_{OUT} < V_{IN} - V_{FA}$  である間は、出力に供給される電流は  $I_{START}$  に制限されます。タイムアウト時間  $t_{STO}$  は、POR、EN、UVLO、OVLO のいずれかによってターンオフ・イベント後に再起動が行われる場合に適用されます。 $t_{STO}$  の間に出力が  $(V_{IN} - V_{FA})$  のレベルまで充電されなかった場合は、デバイスはオフになります、通常動作を再開するためには、選択されている CLMODE にかかわらず IN または EN をトグルする必要があります。

$I_{START}$  は、 $I_{START}/CLMODE$  ピンと GND の間に抵抗を接続することで設定されます。POR 後に直ちに  $R_{START/CLMODE}$  が読み出され、 $I_{START\_RATIO}$  ( $I_{START}/I_{LIM}$ ) がプログラムされます。 $I_{START\_RATIO} = (1/16, 1/8, 1/4, 1/2, 1)$  を設定するには、表 1 から  $R_{START/CLMODE}$  の値を選択します。 $I_{START}/CLMODE$  ピンは、電流制限モードおよび逆保護機能を設定する場合にも用いられます。

表 1.  $I_{START}/CLMODE$  の設定

| $R_{START/CLMODE}$ ( $\Omega$ ) | $I_{START}/I_{LIM}$ ( $I_{START\_RATIO}$ ) | CLMODE     | PRESENCE OF EXTERNAL nFET/<br>REVERSE PROTECTION FEATURE |

|---------------------------------|--------------------------------------------|------------|----------------------------------------------------------|

| 24.3                            | 1                                          | Auto-retry | No                                                       |

| 78.7                            | 1                                          | Continuous | No                                                       |

| 147.0                           | 1                                          | Latch-off  | No                                                       |

| 226.0                           | 1                                          | Auto-retry | Yes                                                      |

| 309.0                           | 1                                          | Continuous | Yes                                                      |

| 402.0                           | 1                                          | Latch-off  | Yes                                                      |

| 499.0                           | 0.5                                        | Auto-retry | No                                                       |

| 604.0                           | 0.5                                        | Continuous | No                                                       |

| 732.0                           | 0.5                                        | Latch-off  | No                                                       |

| R <sub>ISTART/CLMODE</sub> (Ω) | I <sub>START</sub> /I <sub>LIM</sub><br>(I <sub>START_RATIO</sub> ) | CLMODE     | PRESENCE OF EXTERNAL nFET/<br>REVERSE PROTECTION FEATURE |

|--------------------------------|---------------------------------------------------------------------|------------|----------------------------------------------------------|

| 866.0                          | 0.5                                                                 | Auto-retry | Yes                                                      |

| 1000                           | 0.5                                                                 | Continuous | Yes                                                      |

| 1210                           | 0.5                                                                 | Latch-off  | Yes                                                      |

| 1400                           | 0.25                                                                | Auto-retry | No                                                       |

| 1620                           | 0.25                                                                | Continuous | No                                                       |

| 1870                           | 0.25                                                                | Latch-off  | No                                                       |

| 3160                           | 0.25                                                                | Auto-retry | Yes                                                      |

| 5760                           | 0.25                                                                | Continuous | Yes                                                      |

| 9090                           | 0.25                                                                | Latch-off  | Yes                                                      |

| 12400                          | 0.125                                                               | Auto-retry | No                                                       |

| 16200                          | 0.125                                                               | Continuous | No                                                       |

| 20000                          | 0.125                                                               | Latch-off  | No                                                       |

| 24300                          | 0.125                                                               | Auto-retry | Yes                                                      |

| 28700                          | 0.125                                                               | Continuous | Yes                                                      |

| 34800                          | 0.125                                                               | Latch-off  | Yes                                                      |

| 41200                          | 0.0625                                                              | Auto-retry | No                                                       |

| 48700                          | 0.0625                                                              | Continuous | No                                                       |

| 56200                          | 0.0625                                                              | Latch-off  | No                                                       |

| 64900                          | 0.0625                                                              | Auto-retry | Yes                                                      |

| 75000                          | 0.0625                                                              | Continuous | Yes                                                      |

| 86600                          | 0.0625                                                              | Latch-off  | Yes                                                      |

大きい容量性負荷に対する起動時間は、次の式を使用して計算できます。

$$t_{SS} = \frac{V_{IN} \times C_{OUT}}{I_{START}}$$

ここで、t<sub>SS</sub>は必要な起動充電時間（単位：秒）です。

図10は、パワーアップ中の代表的な起動タイミング・シーケンスを示しています。

図 10. I<sub>START</sub> のタイミング図

ソフトスタート期間中、PGOOD はローにアサートされたままになります。出力電圧の上昇中に、内蔵 nFET 両端の電圧降下 (IN ピンと OUT ピンの間で計測) が内部スレッショルドの V<sub>FA</sub> より低くなると、PGOOD のアサートが解除されます。

### 電流制限スレッショルドの設定 (I<sub>LIM</sub>)

デバイスに電流制限スレッショルドを設定するには、SETI と GND の間に抵抗を接続します。電流設定抵抗を計算するには次の式を用います。

$$R_{SETI}(\text{k}\Omega) = \frac{14910}{I_{LIM}(\text{mA})}$$

ここで、I<sub>LIM</sub>は目的の電流制限値で単位は mA です。

1.86kΩ未満の R<sub>SETI</sub>は使用しないでください。表 2 には様々な抵抗値に対する電流制限スレッショルドを示しています。

表 2. 電流制限スレッショルドとの抵抗値の関係

| R <sub>SETI</sub> (kΩ) | CURRENT LIMIT I <sub>LIM</sub> (A) |

|------------------------|------------------------------------|

| 21.0                   | 0.7                                |

| 14.7                   | 1                                  |

| 7.32                   | 2                                  |

| 4.87                   | 3                                  |

| 3.65                   | 4                                  |

| 2.94                   | 5                                  |

| 2.43                   | 6                                  |

| 2.10                   | 7                                  |

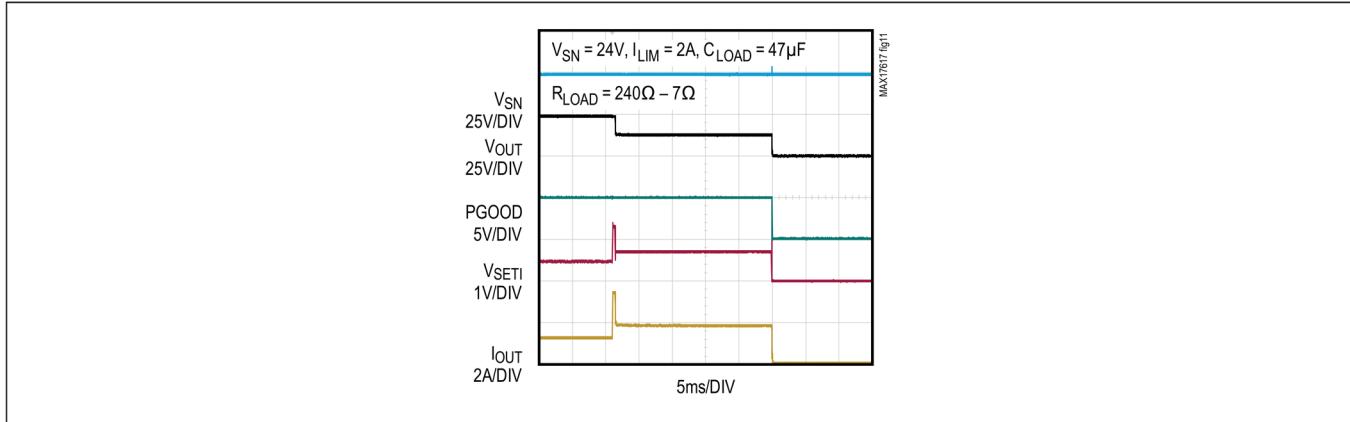

SETIが無接続のままである場合、 $V_{SETI} \geq 1.5V$ となり、電流レギュレータには全く電流が流れません。デバイスは、いつシャットダウン状態が終了するかをSETIピンでチェックします。SETIピンに配置された抵抗が $1k\Omega$ 未満の場合、スイッチはオフのままになりFLAGがアサートされます。図11に、負荷ステップ・イベント時のSETIの応答を示します。

図11. 負荷ステップ・イベント時のSETIの応答

## 電流モニタリング (IMON)

このデバイスは、内蔵nFETを流れる負荷電流をモニタするための専用のIMONピンを備えています。

IMONとGNDの間に抵抗( $R_{IMON}$ )を接続して、デバイス電流をモニタします。次式を使用して、モニタ用抵抗 $R_{IMON}$ を計算します。

$$R_{IMON} = \frac{26625}{I_{LIM}(mA)}$$

ここで、 $R_{IMON}$ はIMONとGNDの間の抵抗(単位： $k\Omega$ )です。

測定電流の帯域幅を制限するために、オプションでIMONピンとGNDの間にセラミック・コンデンサを使用できます。

必要なコンデンサを選択するには次式を用います。

$$C_{IMON} = \frac{1}{2\pi \times R_{IMON} \times f_{CIMON}}$$

ここで、 $f_{CIMON}$ は、必要な電流モニタ帯域幅(Hz)、 $C_{IMON}$ は、必要な容量(F)です。

IMONピンの電圧( $V_{IMON}$ )は、次の式を使用して計算できます。

$$V_{IMON} = \frac{I_{nFET}}{21300} \times R_{IMON}$$

ここで、InFETは内蔵FETを流れる負荷電流です。

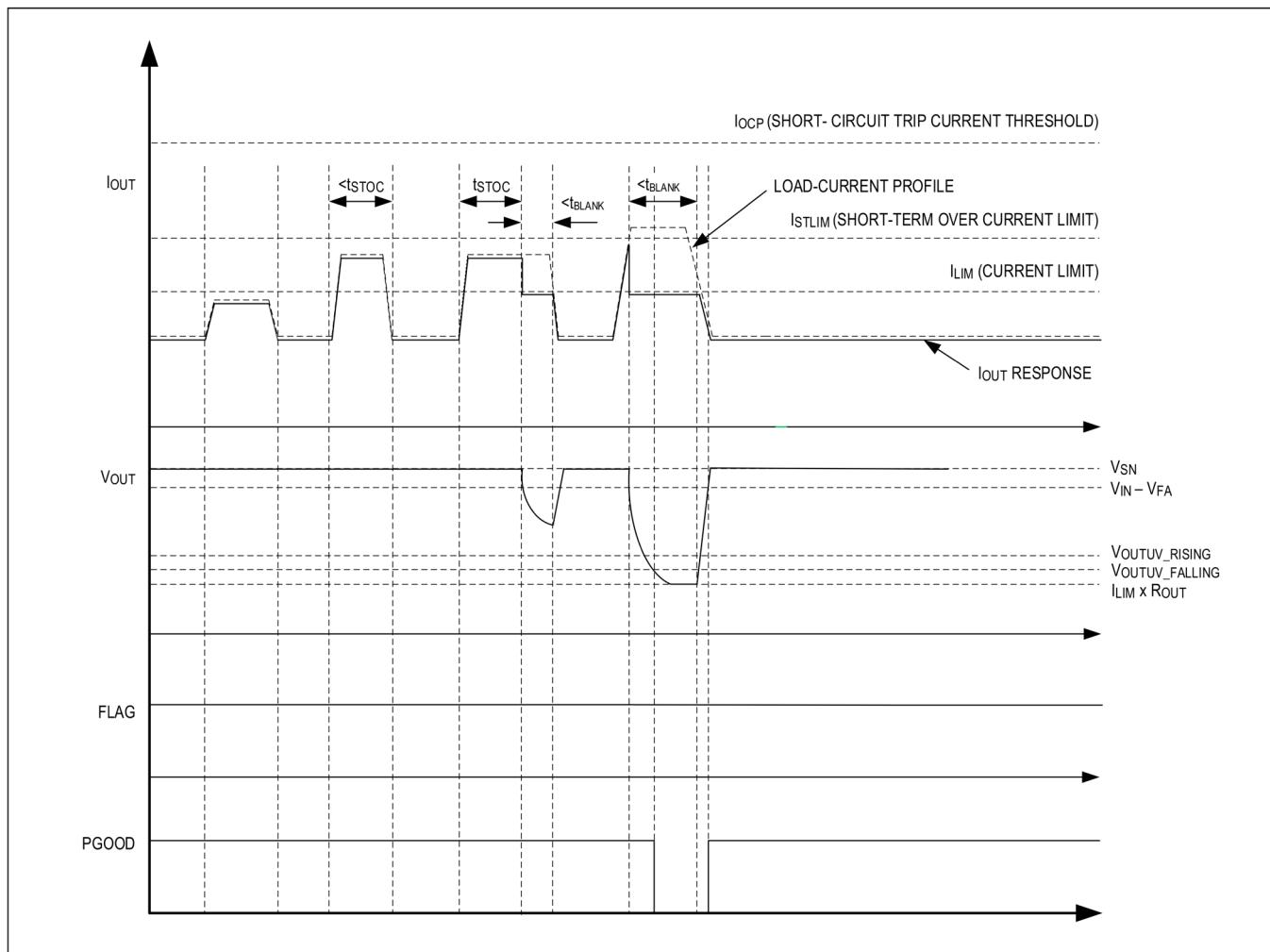

## 電流制限機能と短期過電流対応機能

このデバイスは短期過電流許容能力( $I_{STLIM}$ )を備えており、通常動作中の短期的な過負荷電流のある負荷電流プロファイルに対応できます。 $I_{STLIM}$ は、SETIピンでの電流制限の設定値( $I_{LIM}$ )の2倍に設定されており、短期過電流時間( $t_{STOC}$ )は $400\mu s$ に設定されています。

- 1) 負荷電流が $t_{STOC}$ 未満の時間、 $I_{LIM}$ を超過しても、 $I_{STLIM}$ より低くとどまつていれば、デバイスは電流を制限せず、通常動作を継続します。

- 2) 負荷電流が $I_{LIM}$ を超過し、 $I_{STLIM}$ より低い状態が $t_{STOC}$ より長い時間継続した場合、あるいは負荷電流が $I_{STLIM}$ を超過し、 $I_{OCP}$ より低い場合には、デバイスは約 $100\mu s$ 以内に電流を設定された電流制限値( $I_{LIM}$ )に制限します。

デバイスが電流制限 (ILIM) 状態になると、デバイスの動作は [電流制限タイプの選択](#) のセクションに記載の電流制限モードによって決まります。

図12は、電流制限と短期過電流のタイミング図です。

図12. 電流制限と短期過電流のタイミング図

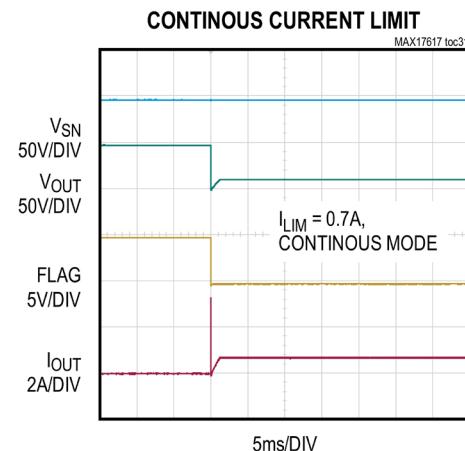

## 電流制限タイプの選択

MAX17617/MAX17617Aでは、連続モード、自動再試行モード、ラッチオフ・モードの3種類の電流制限モードが選択できます。電流制限モードは、[表1](#)に示すように、 $I_{START}/CLMODE$ ピンを通じてプログラムできます。 $(V_{IN} - V_{OUT} < V_{FA})$ の条件が  $t_{STO}$ 以内に成立しなければ、選択されている  $CLMODE$ にかかわらずデバイスはラッチオフ状態に入ります。

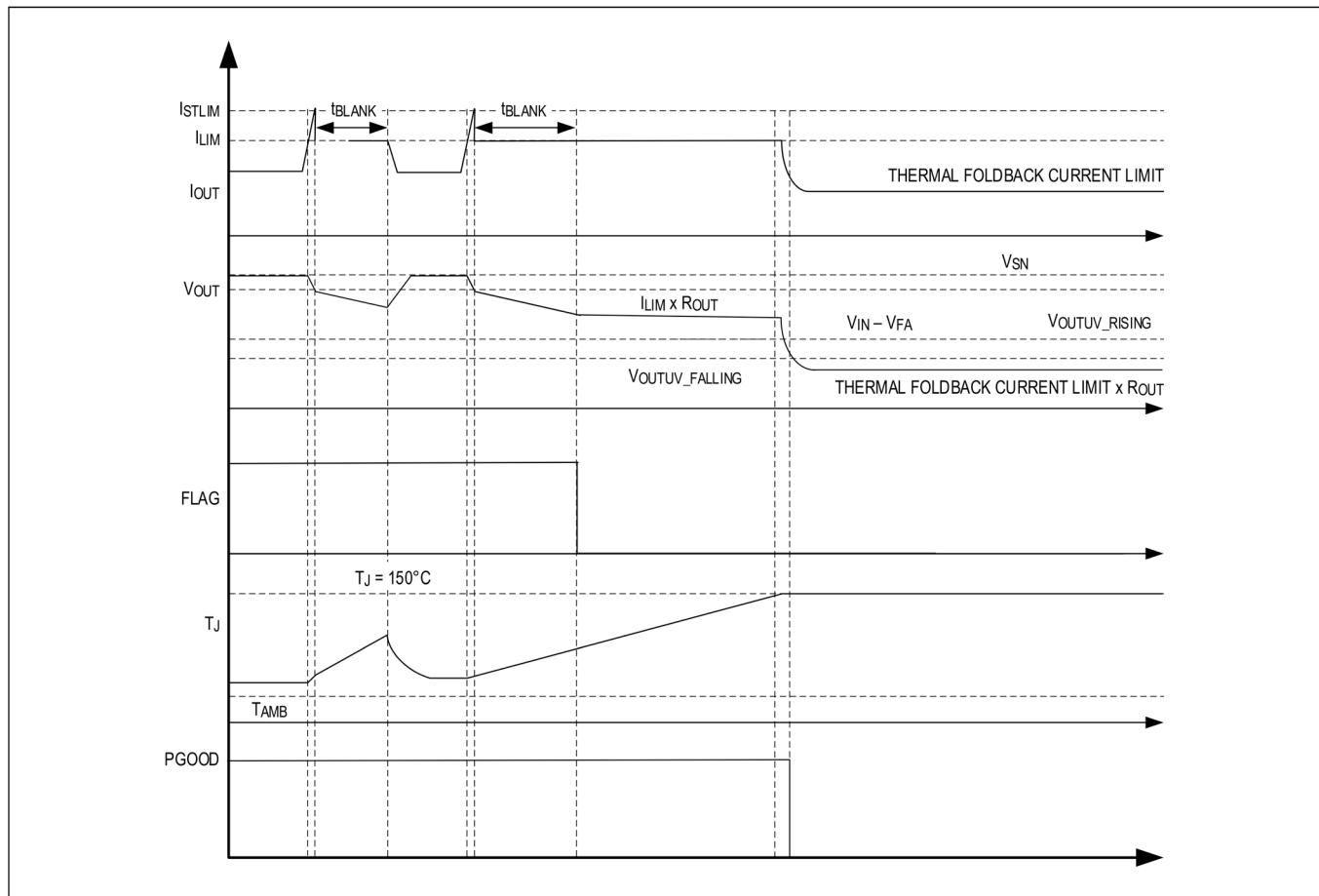

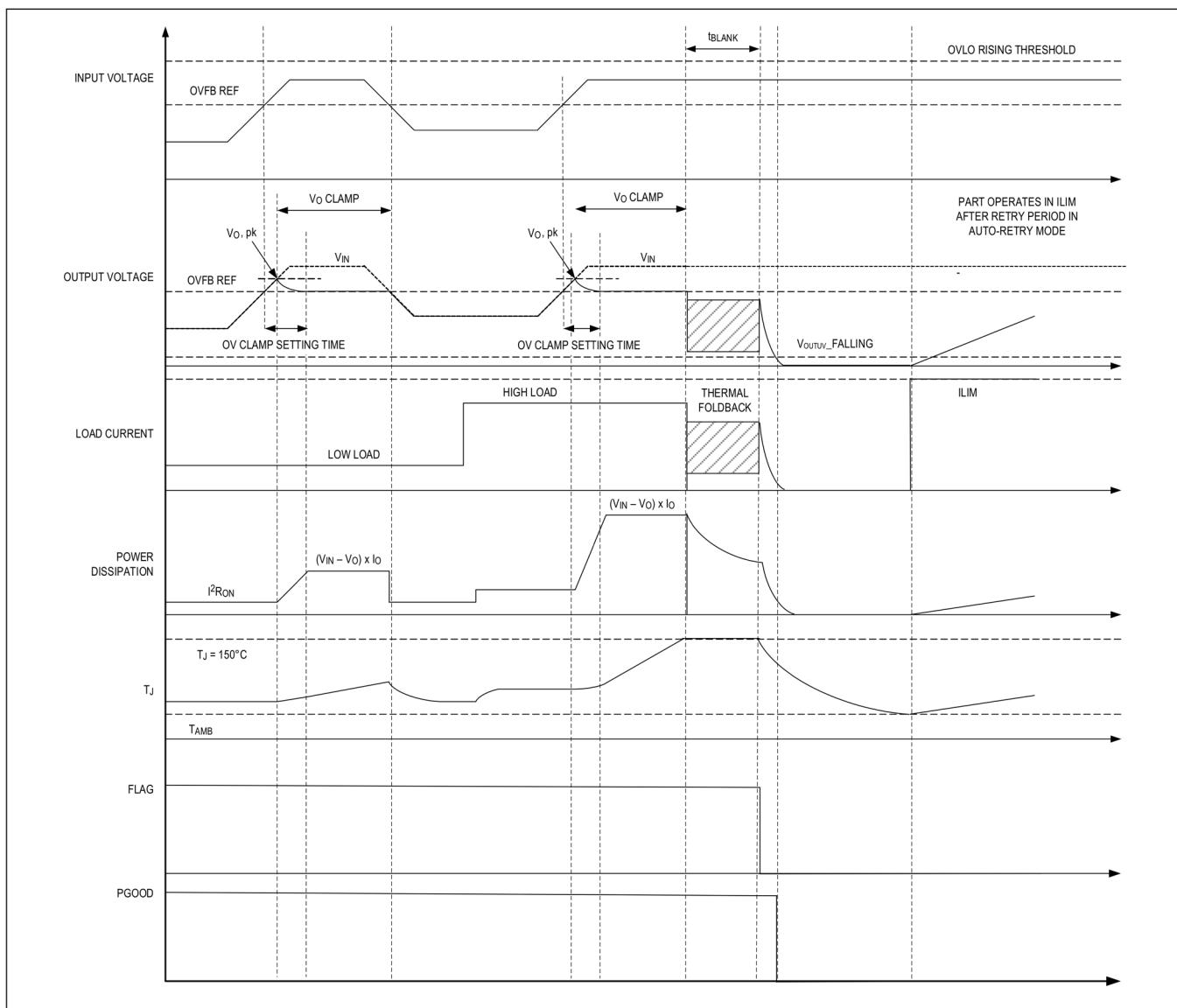

### 連続電流制限

連続電流制限モードでは、デバイスは連続的に電流を制限します。電流制限が  $t_{BLANK}$  時間より長く続くと、FLAG ピンがアサートされ、内部スイッチでの電圧降下が  $V_{FA}$  より低くなるとデアサートされます。図 13 に連続電流制限モードの代表的な動作を示します。

図 13. 連続モード時のフォルト・タイミング図

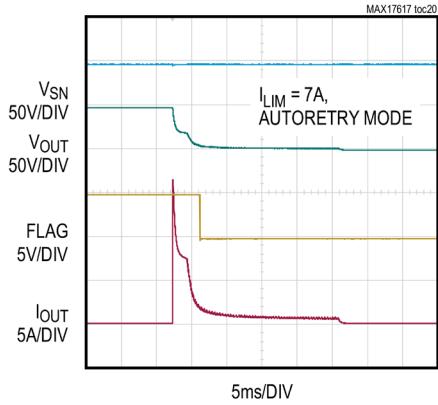

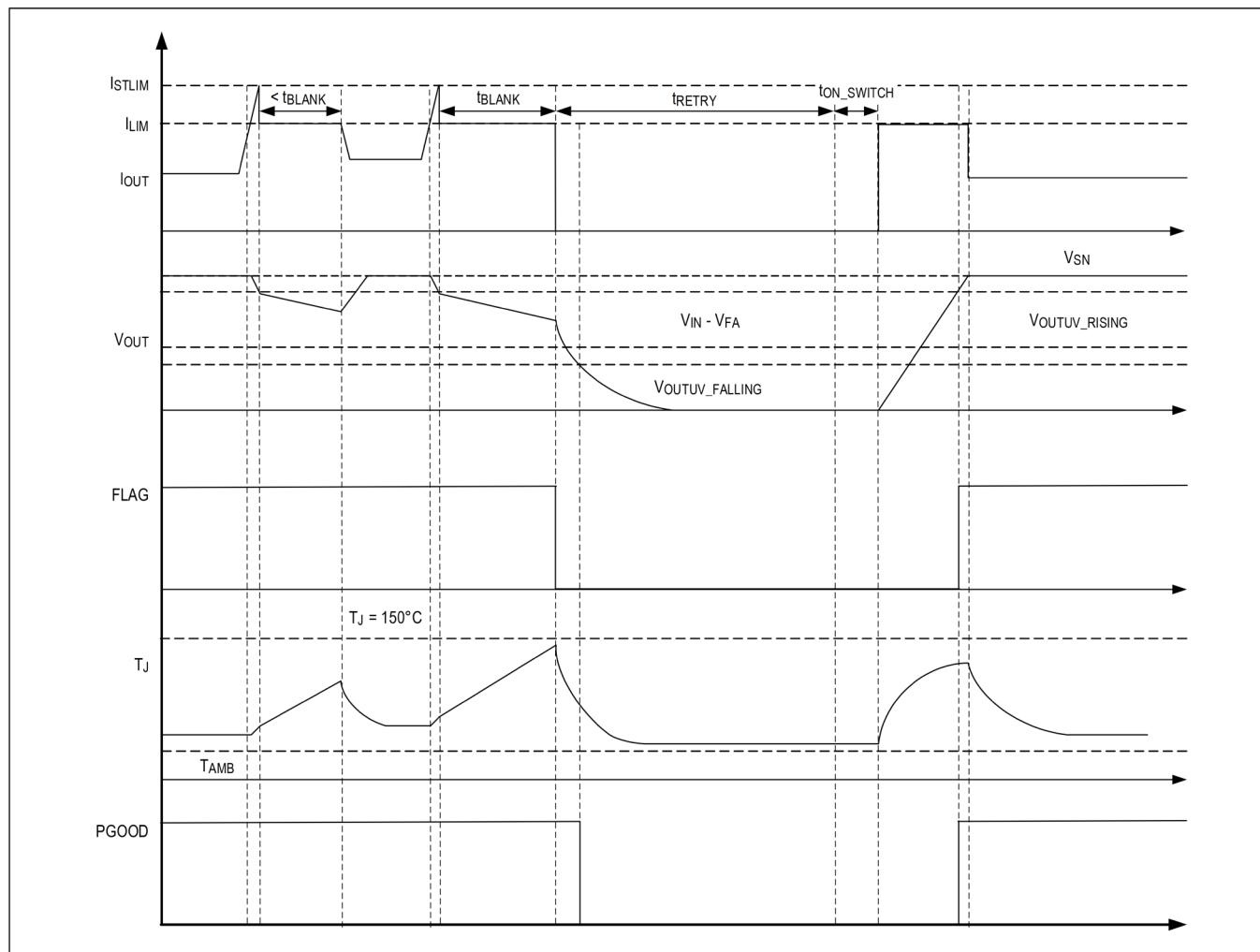

## 自動再試行電流制限

自動再試行電流制限モードでは、内部で固定されている自動再試行時間 ( $t_{RETRY}$ ) 後に再起動を試みます。ブランкиング・タイマー時間 ( $t_{BLANK}$ ) が経過しても過電流条件が継続していれば、内蔵の自動再試行タイマーが起動されます。 $t_{BLANK}$  が経過する前に過電流状態が解消していれば、ブランкиング・タイマーはリセットします。 $t_{RETRY}$  の間、スイッチはオフのままです。 $t_{RETRY}$  が経過すると、デバイスは  $I_{LIM}$  で動作を再開します。�ルトが存在している場合、このサイクルが繰り返され、FLAG ピンはアサートされたままになります。過電流状態が終了すると、スイッチはオン状態を続けます。電流制限が  $t_{BLANK}$  時間より長く続くと、FLAG ピンがアサートされ、内部スイッチでの電圧降下が  $V_{FA}$  より低くなるとデアサートされます。

自動再試行機能により、過電流状態または短絡状態の場合のシステム電力を削減できます。 $t_{BLANK}$  の間スイッチがオンである場合、電源電流は電流制限値に維持されます。 $t_{RETRY}$  の間は、スイッチに電流は流れません。したがって、平均出力電流は、設定された電流制限値に比べてはるかに小さくなります。平均出力電流は次の式で計算できます。

$$I_{LOAD} = I_{LIM} \times \frac{t_{BLANK}}{t_{RETRY} + t_{BLANK}}$$

24ms (代表値) の  $t_{BLANK}$  と 800ms (代表値) の  $t_{RETRY}$  を仮定すると、デューティ・サイクルは 2.9%になり、全時間スイッチがオンであった場合と比較して 97.1%の電力削減となります。図 14 に自動再試行電流制限モードの代表的な動作を示します。

図 14. 自動再試行モード時の�ルト・タイミング図

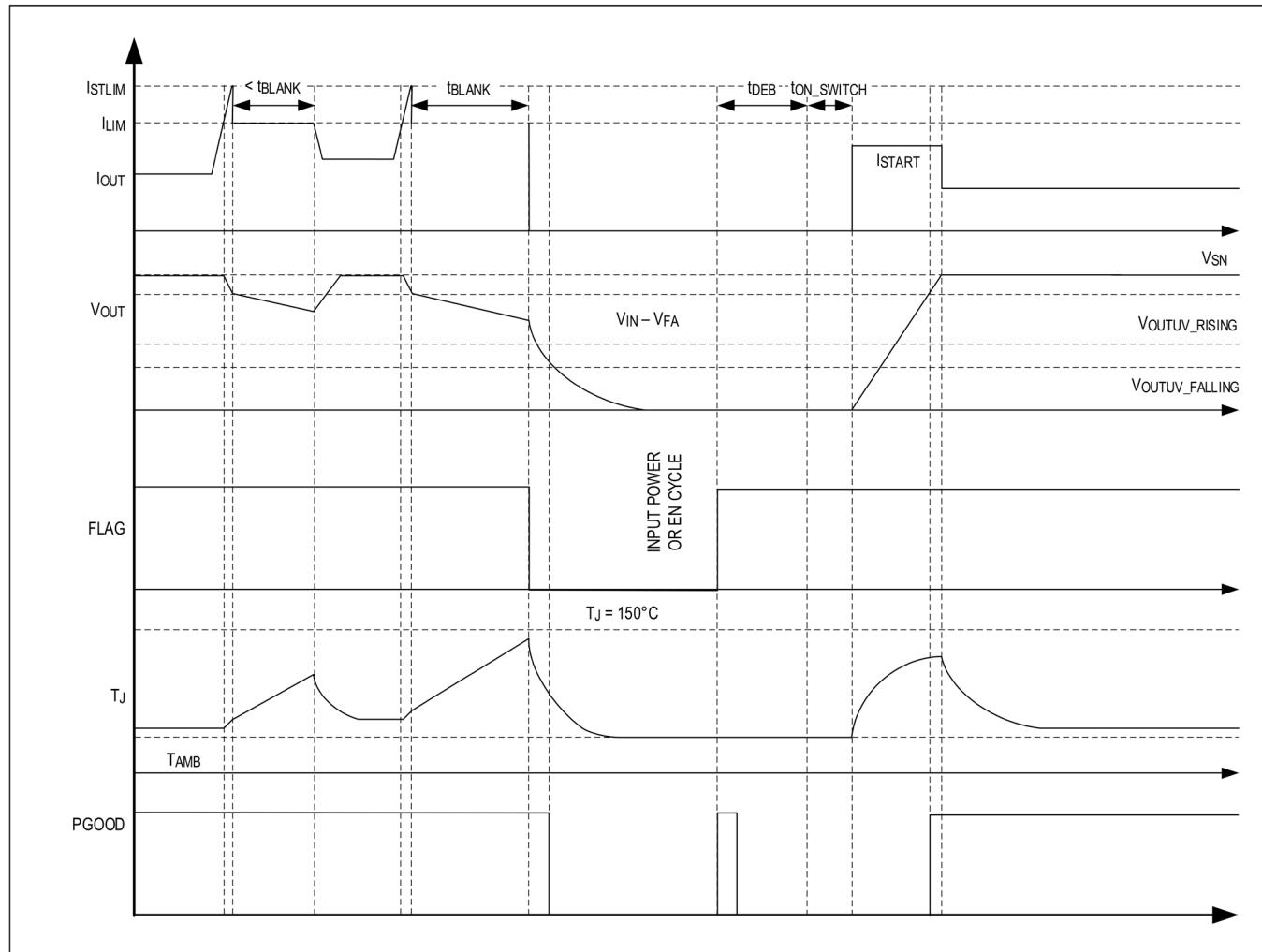

## ラッチオフ電流制限

ラッチオフ電流制限モードでは、過電流イベントがブランкиング・タイマー時間 ( $t_{BLANK}$ ) より長く続くと、デバイスはラッチされオフのままになります。 $t_{BLANK}$  が経過する前に過電流状態が解消していれば、ブランкиング・タイマーはリセットします。スイッチをリセットするには、コントロール・ロジック (EN) を  $10\mu\text{s}$  (代表値) 以上の間ローに維持するか、入力電力の投入を繰り返します。

図 15 にラッチオフ電流制限モードの代表的な動作を示します。

図 15. ラッチオフ・モード時のフォルト・タイミング図

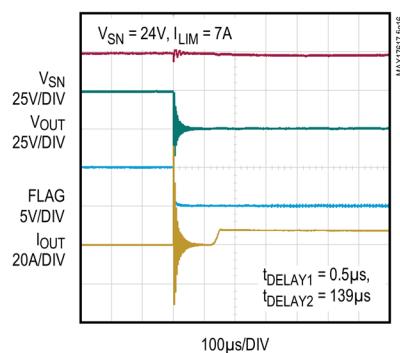

## 短絡保護

出力短絡イベントの間、デバイスを流れる電流は極めて急速に増加します。このデバイスは高速トリップ電流コンパレータを備えており、出力短絡時のピーク電流を制限できます。この高速トリップ電流コンパレータは、内蔵 nFET を流れる電流が  $I_{OCP}$  を超過すると、 $1\mu\text{s}$  ( $t_{DELAY1}$ ) 以内に内蔵 nFET をオフにします。 $I_{OCP}$  は  $30\text{A}$  (代表値) に内部設定されています。 $200\mu\text{s}$  ( $t_{DELAY2}$ ) の遅延時間後、デバイスはオン状態に戻り、出力電流を設定された電流制限値に制限し、上述の電流制限モードの各セクションで説明したように動作します。図 16 には、電流が  $I_{OCP}$  スレッショルドを超過したときのシステム挙動を図示しています。

図 16. 短絡応答

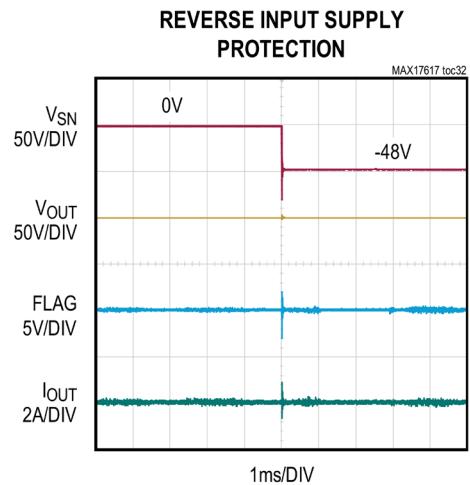

## 逆電流保護

逆電流保護機能は、外付け nFET を用いる場合に有効化されます。デバイスは、OUT ピンから IN ピンへの逆電流の流れを防止します。

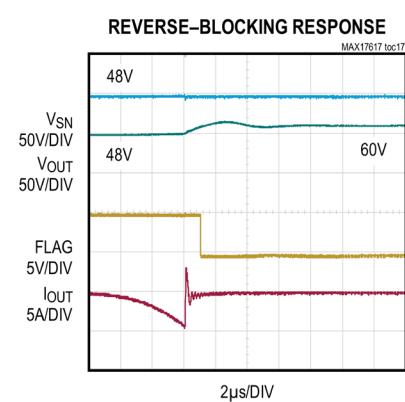

逆電流状態が検出された場合 ( $(V_{IN} - V_{OUT}) < V_{RIB\_}$ ) 、外付け nFET はオフになります。逆電流状態が解消されると ( $(V_{IN} - V_{OUT}) > V_{RIB\_RISING}$ ) 、外付け nFET は  $t_{on\_RPSWITCH}$  の経過後にオンに戻ります。逆電流状態が唯一のフォルトである場合 (UVLO、OVLO、サーマル・フォルト、順方向過電流フォルトのいずれも存在しない場合) は、内部 nFET はオン状態を維持します。それ以外の場合は、内部 nFET もオフになります。図 17 に、低速または高速逆電流状態の代表的な動作を示します。

デバイスには、逆電流保護用に、低速（代表値20μs）と高速（代表値100ns）の応答時間を持つ2つの逆電流スレッショルドがあります。低速逆電圧のスレッショルドは-5mV（代表値）で、高速側の値は-100mV（代表値）です。この機能により、ノイズの多い環境でも安定した動作が実現できると同時に、入力短絡やOUTピンでのホット・プラグインなどの厳しいフォルトに対する高速保護が可能です。逆電流状態時には、FLAGピンがアサートされます。

図 17. 逆電流フォルトのタイミング図

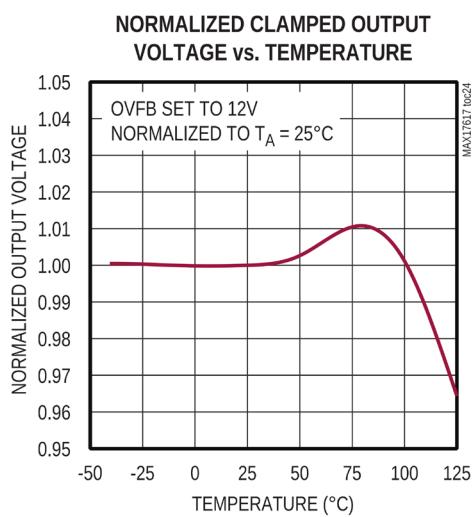

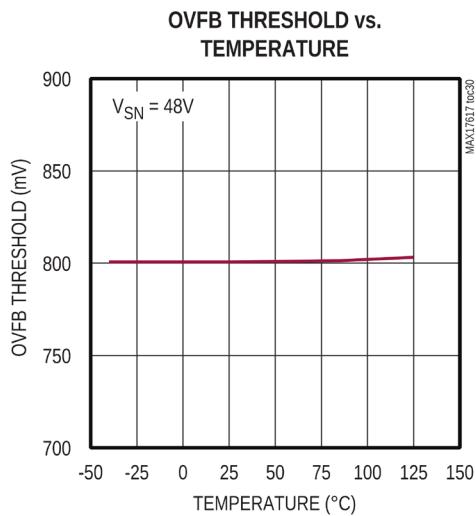

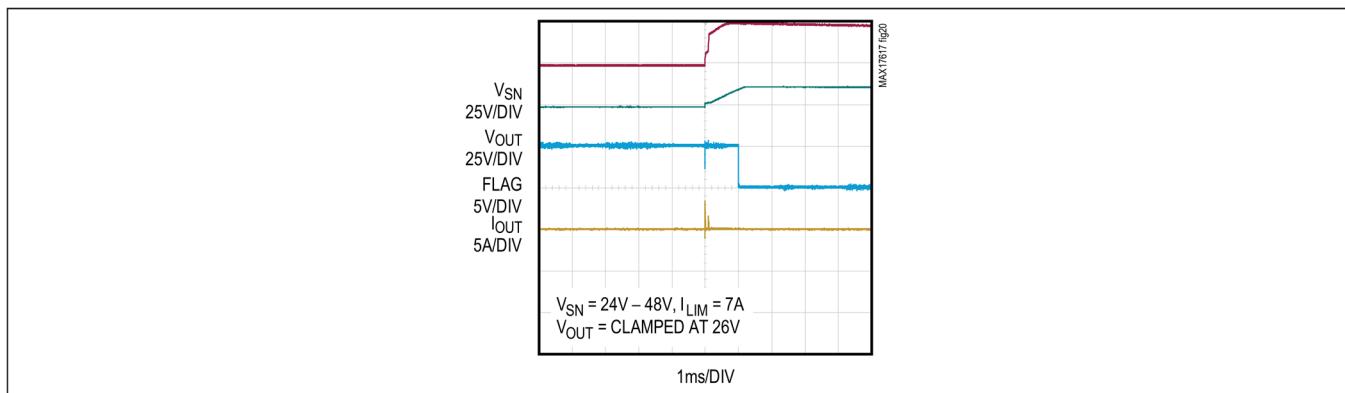

## 入力電圧のサージ除去と出力過電圧フィードバック・レギュレーション(OVFB)

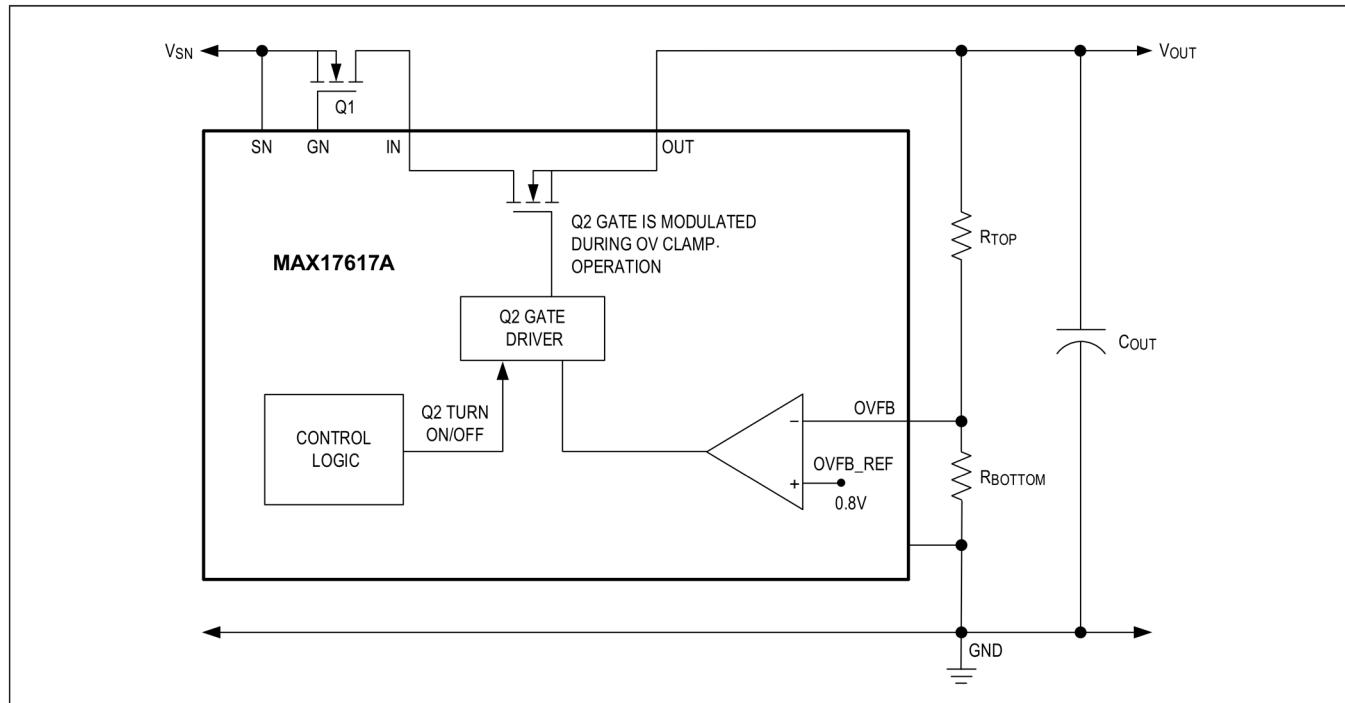

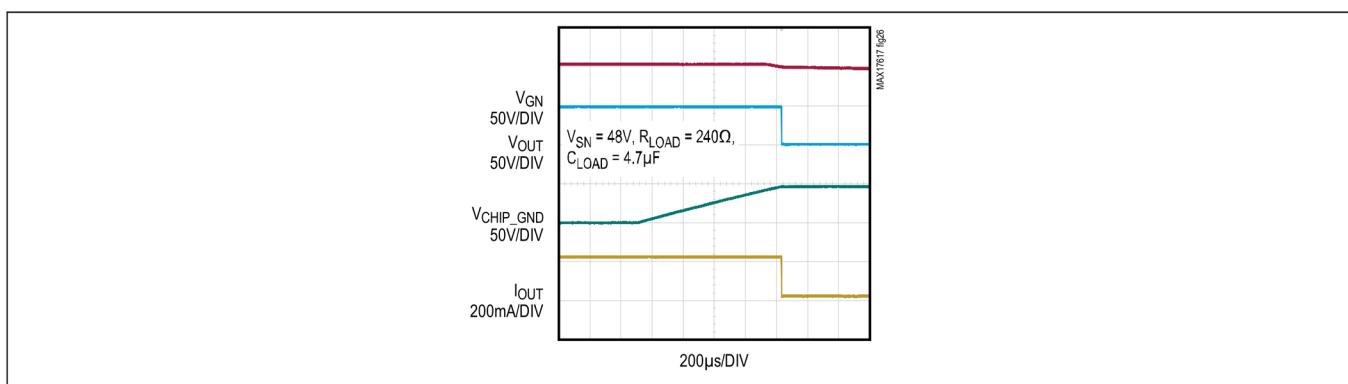

MAX17617A はサージ保護機能を備えており、入力電圧のサージ・イベント中に出力電圧を設定された電圧に制限します。入力電圧のサージがスレッショルドを超えると、出力過電圧フィードバック・ループ(OVFB)が内蔵制御 nFET のドレイン-ソース間抵抗を調整して出力電圧を制限します。過電圧クランプ機能の簡略化した内部ブロック図を図 18 に示します。

OVFB 状態用のタイマーはありません。負荷条件に応じて、無期限に OUT を IN より低く安定化します。

- 他の条件(過電流やサーマル・フォールドバックなど)が発生しない限り、デバイスは OVFB モードで動作します。このことは、 $(V_{IN} - V_{OUT})$  が  $V_{FA}$  を超過した場合でも、OVFB 状態のみが存在する限りは成立します。この場合、FLAG ピンはアサートされません。

- OVFB 状態は  $t_{BLANK}$  をトリガする可能性があり(結果的にサーマル・フィードバック状態が発生した場合)、 $t_{BLANK}$  経過後にデバイスは設定された CLMODE に従って動作します。FLAG ピンは  $t_{BLANK}$  時間の終了時にアサートされます。

図 18. OVFB による過電圧クランプ

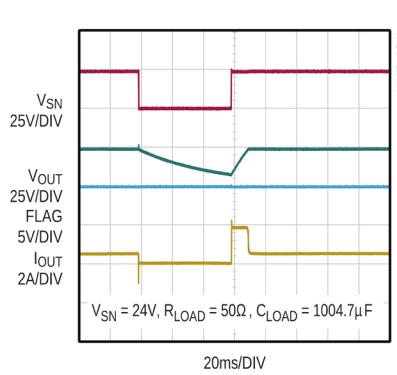

代表的な過電圧クランプ動作とリカバリ・シーケンスを図 19 に示します。また、図 20 は、入力サージ・イベント中の MAX17617A の過電圧クランプ応答を示しています。

図 19. 過電圧 クランプ動作とリカバリ

図 20. 過電圧 クランプ応答

## 入力逆極性保護

入力の逆極性保護は、MAX17617/MAX17617Aが制御する外付けnFETを使用して実現されます。入力電源端子への配線の誤りにより、デバイスの入力ピンに負の電圧が印加されてしまう場合があります。標準アプリケーション回路に示すように、外付けnFET (Q1) のソースをSNピンに、ドレインをINピンに、ゲートをGNピンに接続してください。入力逆極性電圧�ルトが発生すると、この外付けnFETがオフになって負荷を保護します。外付けnFETは、オプションの逆電流保護にも必要となります。逆極性保護と逆電流保護が不要な場合は、SNピンとGNピンをINピンに接続する必要があります。

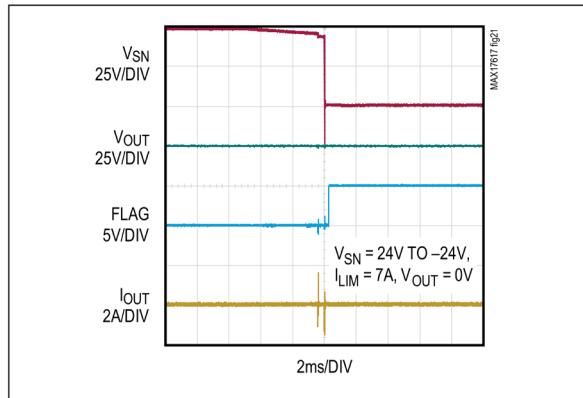

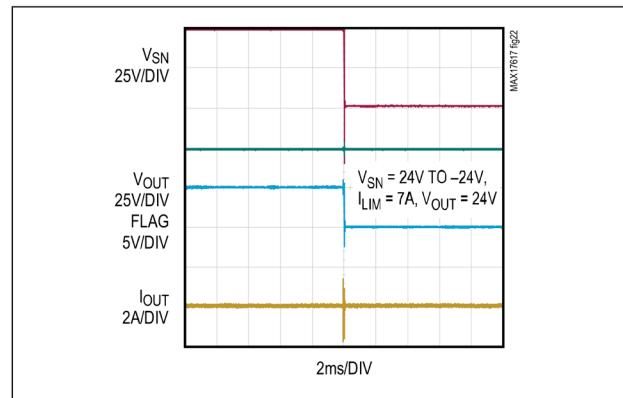

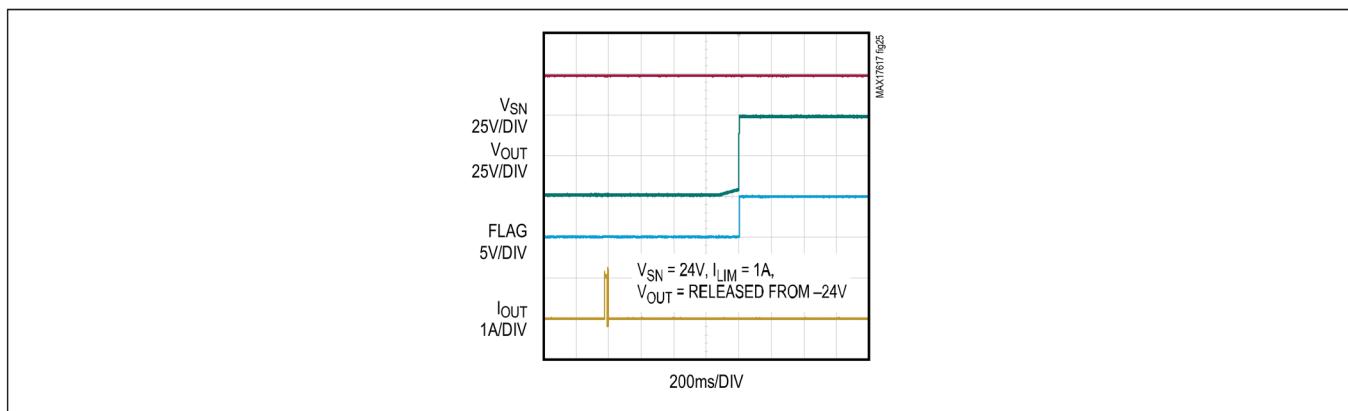

逆極性電圧保護の能力は、動作中の負荷バス電圧 ( $V_{OUT}$ ) と外付けnFETの電圧ブロック能力に依存します。例えば、 $V_{OUT} = 30V$  で  $-55V$  の入力電圧まで保護する場合、定格  $85V$  の外付けnFETが必要となります。デバイスは、ゲート・ドライブ (GN) に  $6.5V$  (代表値) を供給します。図21に、 $V_{OUT} = 0V$  および  $V_{SN} = -24V$  でのMAX17617の逆極性保護を示します。図22に、 $V_{OUT} = +24V$  および  $V_{SN} = -24V$  でのMAX17617の逆極性保護を示します。

図21.  $V_{OUT} = 0V$  および  $V_{SN} = -24V$  での入力逆極性保護

図22.  $V_{OUT} = +24V$  および  $V_{SN} = -24V$  での入力逆極性保護

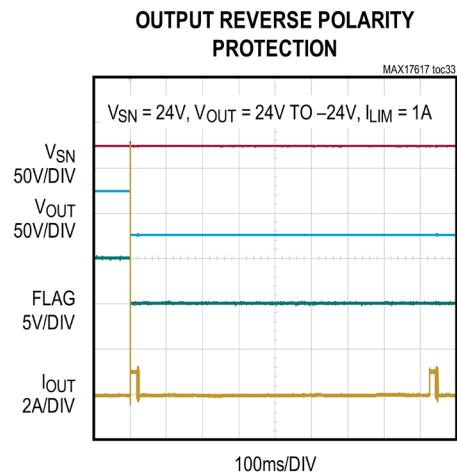

## 出力逆極性保護

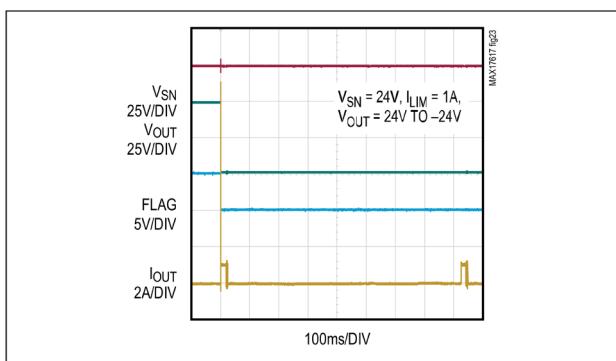

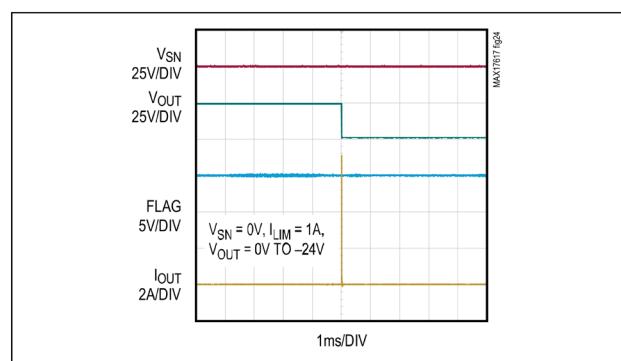

MAX17617/MAX17617Aはデバイス自体と入力電力接続を、偶発的な逆極性接続による逆出力電圧から保護します。逆出力電圧は、誘導性負荷により、あるいは出力端子間の活線負荷の誤配線により、OUTピンとGNDピンの間に生じる可能性があります。

図23に  $V_{OUT} = -24V$  および  $V_{SN} = 24V$  でのMAX17617の出力逆極性保護を、図24に  $V_{OUT} = -24V$  および  $V_{SN} = 0V$  での応答を示します。デバイスは、 $-(85 - V_{IN})V$  までの回路の負出力電圧に対して保護が可能です。図25に出力逆極性�ルト状態からの回復特性を示します。

図 23.  $V_{OUT} = -24V$  および  $V_{SN} = 24V$  での自動再試行モード時の

出力逆極性保護

図 24.  $V_{OUT} = -24V$  および  $V_{SN} = 0V$  での自動再試行モード時の

出力逆極性保護

図 25.  $V_{OUT} = -24V$  の初期条件および  $V_{SN} = 24V$  での出力逆極性フォルトからの回復特性

## 接地喪失保護

このデバイスは、接地喪失イベント時に、内部nFETおよび外付けnFETをオフにして負荷を保護します。接地喪失イベントは、システム制御のグランド・リファレンスと MAX17617/MAX17617A周辺のICグランド・ネットワークの間の断線が原因で発生する場合があります。この機能があることで、接地喪失イベントから保護するための外部回路を追加する必要がなくなります。標準アプリケーション回路に示すように、信号ピン(EN、IMON、FLAG、PGOOD)の保護には追加部品が必要です。図26に接地喪失イベント時の代表的な動作を示します。

図 26. 接地喪失時の負荷電流の瞬時低下

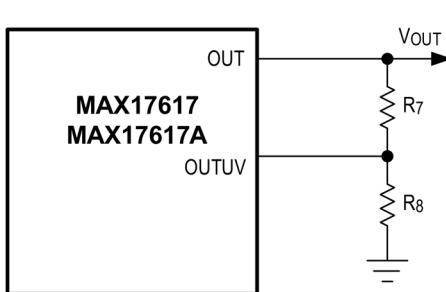

## 出力低電圧検出 (OUTUV)

このデバイスは、プログラマブルな出力低電圧検出スレッショルド (OUTUV) を備えています。OUT ピンの電圧が何らかのフォルト状態によって OUTUV の立下がりスレッショルド未満に低下すると、内部制御ロジックはソフトスタート動作で再起動サイクルを実行します。何らかのフォルト状態の間、出力電圧が OUTUV 立下がりスレッショルドより低くならなければ、再起動サイクルはソフトスタート動作なしで実行されます。これは、設定された OUTUV スレッショルド未満には出力電圧が放電されないような過渡的な入力電源のフォルト状態において特に有用で、この場合デバイスはソフトスタート・サイクルを経ずに回復します。

OUTUV スレッショルド電圧を調整するには、OUTUV ピンに外付けの抵抗分圧器を図 27 に示すように接続します。次式を用いて OUTUV 電圧を調整できます。バッテリ電源など低バイアス電流のアプリケーションでは、R7 の推奨値は  $2.2\text{M}\Omega$  です。

$$V_{OUTUV} = V_{OUTUV\_RISING} \times (1 + R7/R8)$$

図 27. 調整可能な出力低電圧検出

## パワー・グッド出力 (PGOOD/T<sub>J</sub>)

このデバイスは PGOOD コンバレータを備えており、下流の負荷の有効化／無効化のために出力電圧の状態をモニタします。このオープン・ドレインのパワー・グッド出力には、外付けのプルアップ抵抗とバイアス電源が必要です。PGOOD は以下の説明のように機能します。

- 1) PGOOD は、出力電圧が OUTUV 立上がりスレッショルドより高くなり、 $(V_{IN} - V_{OUT}) < V_{FA}$  の条件が満たされるとハイになります。

- 2) PGOOD は、出力電圧が OUTUV の立下がり閾値を下回るとローになります。

- 3) システムのパワーアップ時には、PGOOD は  $V_{OUT} > V_{OUTUV}$ かつ $(V_{IN} - V_{OUT}) < V_{FA}$  であればハイになり、それ以外の条件ではローになります。

## フォルト出力 (FLAG)

このデバイスには、オープン・ドレインのフォルト信号 FLAG があります。このフォルト信号には、外付けのプルアップ抵抗とバイアス電源が必要です。FLAG ピンは、次に示すフォルト状態のときにローにアサートされます。

- ソフトスタート時に、 $t_{STO}$  の終了時点で  $(V_{IN} - V_{OUT}) > V_{FA}$  である場合。

- 過電流状態と短絡状態で、電流制限超過が  $t_{BLANK}$  期間を超えた場合。

- 逆電流条件で、逆保護用の外付け nFET がオフになった場合。

- サーマル・シャットダウン。

- 入力 UVLO。

- 入力 OVLO。

デバイスが検出した上記のフォルト条件がクリアされると、FLAG はデアサートされます。

表 3 に、様々な動作条件における nFET の状態とフォルト信号の状態を示します。

表3. フォルト時のFETの状態

| CONDITION                                                               | EXTERNAL nFET STATUS | INTERNAL nFET STATUS | FLAG STATUS                                                             |

|-------------------------------------------------------------------------|----------------------|----------------------|-------------------------------------------------------------------------|

| EN Disabled                                                             | OFF                  | OFF                  | High                                                                    |

| Normal Operation<br>(No Fault)                                          | ON                   | ON                   | High                                                                    |

| Input UVLO                                                              | OFF                  | OFF                  | Low                                                                     |

| Input OVLO                                                              | OFF                  | OFF                  | Low                                                                     |

| Soft Start<br>(During $t_{START}/t_{STO}$ period)                       | ON                   | ON                   | High                                                                    |

| Output Overcurrent                                                      | ON                   | Regulate             | Low<br>(After $t_{BLANK}$ )                                             |

| Short Circuit                                                           | OFF                  | OFF                  | Low                                                                     |

| Reverse current with No Other Fault                                     | OFF                  | ON                   | Low                                                                     |

| Over Voltage Clamp                                                      | ON                   | Regulate             | High                                                                    |

| Power Limit                                                             | ON                   | Regulate             | High<br>(Automatically low after $t_{BLANK}$ due to current regulation) |

| Loss of Ground                                                          | OFF                  | OFF                  | High                                                                    |

| Output Undervoltage                                                     | ON                   | ON                   | High                                                                    |

| Thermal Regulation                                                      | ON                   | Regulate             | High<br>(Automatically low after $t_{BLANK}$ due to current regulation) |

| Thermal Shutdown                                                        | OFF                  | OFF                  | Low                                                                     |

| SETI Grounded (First Power ON)                                          | OFF                  | OFF                  | Low                                                                     |

| $(V_{IN}-V_{OUT}) > V_{FA}$ at the end of $t_{STO}$<br>(during startup) | OFF                  | OFF                  | Low                                                                     |

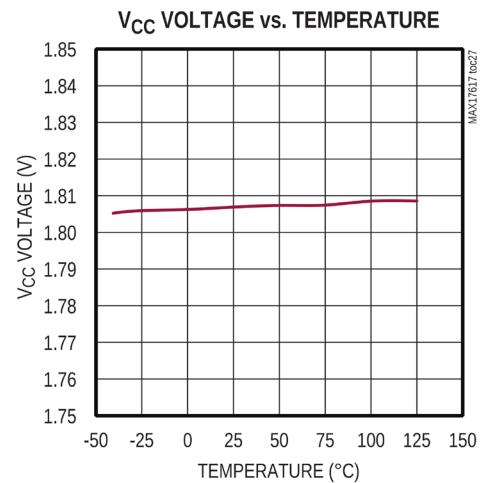

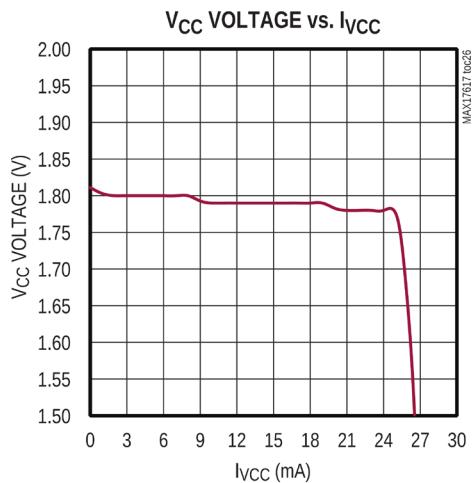

### リニア・レギュレータ ( $V_{CC}$ )

MAX17617/MAX17617Aには、 $V_{IN}$ から $V_{CC}$ に電力を供給する低ドロップアウト(LDO)レギュレータが内蔵されています。このLDOは、パワーアップ時またはENがトグルされたときに動作します。代表的な $V_{CC}$ の出力電圧は1.8Vです。 $V_{CC}$ は、2.2 $\mu$ Fの低ESRセラミック・コンデンサを使用してGNDにバイパスしてください。

### 逆保護用外付けnFETのゲート・ドライバ

このデバイスは、逆保護用外付けnFETを駆動するゲート・ドライバ回路を内蔵しています。ゲート・ドライバは、ゲート端子とソース端子の間の偶発的な短絡から内部で保護されています。 $t_{START}/CLM$  MODEピンとGNDの間に抵抗を接続すると、外付けnFETの有無に関する情報が提供されます。デバイスは、ゲート・ドライバ(GN)に6.5V(代表値)を供給します。ENピンのデアサートによってデバイスの動作が無効化されたとき、ゲート・ドライバは外付けnFETのゲート端子とソース端子の間で受動的な抵抗として機能します。

逆保護機能を使用せず外付けnFETを実装しない場合には、SN端子とGN端子をINピンに接続します。

### ダイ温度のモニタリング (PGOOD/T<sub>J</sub>)

このデバイスにはダイ温度モニタリングの機能があります。PGOOD/T<sub>J</sub>とGNDの間に10kΩ～20kΩの抵抗を接続して、内部ダイ温度をPGOOD/T<sub>J</sub>ピンでモニタします。

PGOOD/T<sub>J</sub>ピンは、ダイ（ホットスポット）温度が25°Cで652mV、+125°Cで854mVの電圧を示し、温度勾配は2mV/°Cです。ダイ（ホットスポット）温度は次の式を使用して表現されます。

$$V_{TJ} = (T_{DIE} - 25^{\circ}\text{C}) \times 2\text{mV} + 652\text{mV}$$

$$T_{DIE} = \frac{V_{TJ} - 652\text{mV}}{2\text{mV}} + 25^{\circ}\text{C}$$

ここで、

T<sub>DIE</sub>はダイ温度、

V<sub>TJ</sub>はPGOOD/T<sub>J</sub>ピンの電圧です。

### サーマル・シャットダウン保護

このデバイスには、過熱から保護するためのサーマル・シャットダウン機能と、サーマル・フォールドバック電流制限御機能があります。ジャンクション温度が150°C（代表値）に達すると、電流制限値が内部で低下し、これによって内部nFETの消費電力を低減させ、ジャンクション温度を約150°Cに安定化します。ジャンクション温度が+165°C（代表値）を超える過酷な状況の場合は、デバイスがオフになります。FLAGピンをアサートします。ジャンクション温度が20°C（代表値）低下するとデバイスはサーマル・シャットダウンを終了し通常動作を再開します。ただし、ラッチオフ・モードの場合は、デバイスはラッチオフ状態を継続します。

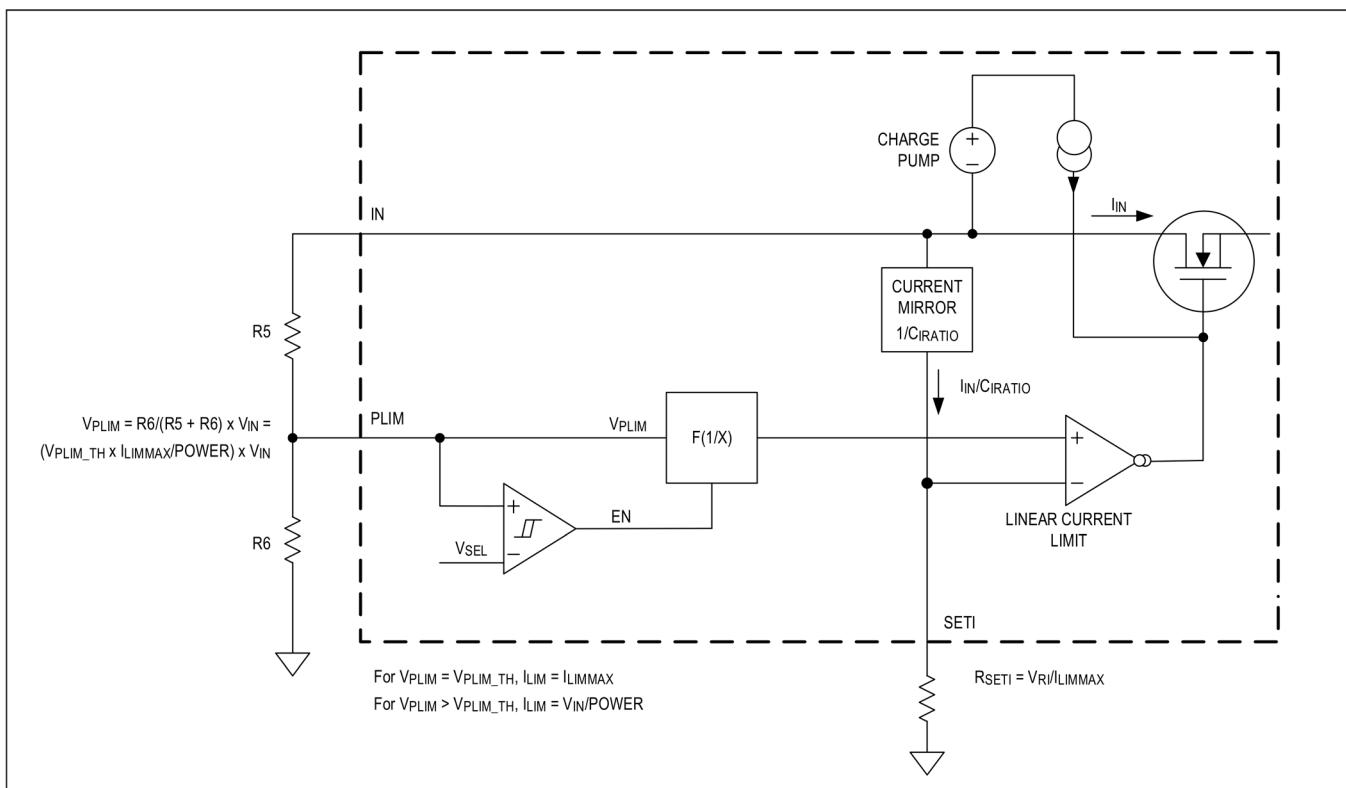

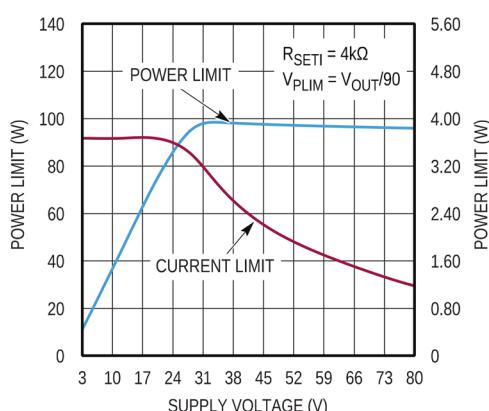

### 電力制限

デバイスには独自の電力制限機能があり、これを利用すると設定した電流制限値を外部電圧（V<sub>EXT</sub>）に応じて自動的に変更できます。デバイスは、この外部電圧の一部を、V<sub>EXT</sub>とGNDの間に接続された分圧器を通じてPLIMピンでモニタし、次の関係に基づき電流制限値を自動的に調整します。

V<sub>PLIM</sub> ≤ V<sub>PLIMTH</sub>の場合、出力電流は、R<sub>SET1</sub>で設定されたI<sub>LIM</sub>値に制限されます。

V<sub>PLIM</sub> > V<sub>PLIMTH</sub>の場合、出力電流制限値は  $\frac{I_{LIM} \times V_{PLIMTH}}{V_{PLIM}}$  に制限されます。

標準アプリケーション回路のR5およびR6で形成される、比がKの外付け分圧器の場合、外部電圧から供給される電力は、次式で与えられます。

$$V_{PLIM} = V_{EXT} \times K$$

$$P = \frac{V_{EXT} \times I_{LIM} \times V_{PLIMTH}}{V_{PLIM}}$$

$$\text{Hence, } P = \frac{I_{LIM} \times V_{PLIMTH}}{K}$$

ここで、I<sub>LIM</sub>、K、V<sub>PLIMTH</sub>は本質的には一定ですが、設計によって決まる許容誤差が含まれます。

デバイスは、V<sub>PLIMTH</sub> < V<sub>PLIM</sub> < 3 × V<sub>PLIMTH</sub>の範囲で±6%の電力制限精度を持っています。この電圧範囲は、外部電圧（V<sub>EXT</sub>）の変動幅の3倍に対応します。

設計に必要な条件は、出力電力制限値（P）が100W、電流制限値が4Aであると仮定します。

抵抗分圧比kは次のように計算されます：  $k = \frac{R_6}{R_6 + R_5} = \frac{I_{LIM} \times V_{PLIMTH}}{P}$

ここで、V<sub>PLIMTH</sub> = 0.3です。R6が10kΩとすると、R5の計算値は825kΩとなります。

入力電力を制限するアプリケーションでは、V<sub>SN</sub>はV<sub>EXT</sub>に等しく、PLIMの抵抗分圧器は電流制限値が減少し始める入力電圧を決定するよう設定されます。この電圧を設定し、最大電流制限値を設定することで、そのアプリケーションの最大「入力電力制限」が設定されます。電流制限値は、V<sub>EXT</sub>に等しいV<sub>OUT</sub>を用いることで出力電圧に応じて動的に変更することもできます。この機能には出力電力制限機能が備わっており、この機能によって、過剰な電力消費による熱的な制限がない限り、より大きな出力電流を供給し、「給電停止」後に入力電力が回復した後に生じる低出力電圧状態での出力リザーバ・コンデンサを充電することができます。この電力制限機能は、PLIMピンをGNDに接続することで無効化できます。PLIMの簡略化したブロック図を図28に示します。図29に100Wクラス2の出力電力制限応答を示します。

図 28. 電力制限回路

図 29. 100W クラス 2 出力電力制限

## アプリケーション情報

### IN コンデンサ

負荷電流の突然の変動時に入力電圧を維持するために、INピンとGNDの間に1μFのコンデンサを接続することを推奨します。

### IN端子のホット・プラグイン

多くの電力アプリケーションでは、放射エミッションを低減しESD能力を強化するために入力フィルタリング・コンデンサが必要です。ホット・プラグイン・アプリケーションでは、ケーブルの寄生容量と入力コンデンサによって、活線状態の電源ケーブルが入力端子に接続されたときにオーバーシュートやリンギングを引き起こします。

この作用により、供給電圧の2倍もの電圧が保護デバイスにかかります。工業用アプリケーションでは、システムをこうした状況から保護するために、トランジエント電圧サプレッサ(TVS)がよく使用されます。保護能力を高めるには、サージ電圧を最大80Vまでに制限できるTVSを入力端子の近くに配置する必要があります。

### 入力ハード地絡

多くのシステム・アプリケーションでは入力短絡保護が必要です。このデバイスは、逆方向電流がOUTピンに流入しINピンから流出するのを検知し、外付けnFETをオフにします。逆方向電流の大きさは、入力回路のインダクタンスとINピン近くに配置された容量に依存します。

### 瞬時電圧低下応答

MAX17617/MAX17617Aには、入力電源ブラウンアウト・テスト時の瞬時電圧低下からの高速回復機能があります。ブラウンアウト・フォルトからの回復時、デバイスは、内部nFETをオンにするのに150μs(代表値)、外付けnFETをオンにするのに100μs(代表値)を要します。図30に、瞬時電圧低下と回復応答の特性を示します。

図30. 瞬時電圧低下応答

### OUTコンデンサ

接続可能な最大容量性負荷( $C_{MAX}$ )は、電流制限設定値( $I_{LIM}$ (A))、起動タイムアウト( $t_{STO}$ (ms))、入力電圧( $V_{SN}$ )の関数です。 $C_{MAX}$ は次の式を用いて計算できます。

$$C_{MAX} (\text{mF}) = \frac{I_{LIM} \times t_{STO}}{V_{SN}}$$

例えば、 $V_{SN} = 24V$ 、 $t_{STO}$ (代表値) = 1200ms、 $I_{LIM} = 1A$ の場合、 $C_{MAX}$ は50mFです。

出力コンデンサ値が $C_{MAX}$ を超えると、過電流状態を誤ってトリガする可能性があります。なお、上の式では、OUTピンからは負荷電流が流れていないと前提としている点に注意してください。負荷電流が流れると、コンデンサの充電電流がオフセットされることにより充電時間が長くなり、それによって過電流状態と誤判定する可能性が生じます。

実際のアプリケーションでは、 $C_{MAX}$ の値はプリント基板(PCB)の熱性能によって制限されます。熱設計が不十分な場合、デバイスのサーマル・フォールドバック電流制限が必要以上に早く開始され、充電可能な最大容量が更に制限されることになる可能性があります。そのため、大きなコンデンサ・バンクを充電するにはPCBの良好な熱設計が必須です。

## OUT端子のホット・プラグイン

一部のアプリケーションでは、入力電圧の有無によらず、デバイスのOUT端子に外部から電圧が供給される場合があります。こうした条件下では、デバイスは、逆方向電流がOUTピンに流入しINピンから流出するのを検知し、外付けnFETをオフにします。ケーブルの寄生インダクタンスと出入力コンデンサによって、外部から電圧がOUT端子にかかるときにオーバーシュートやリンギングが発生します。これにより、供給電圧の2倍の電圧が保護デバイスにかかり、デバイスの損傷につながる可能性があります。過電圧状態でも、端子での電圧が絶対最大定格を超過しないように維持することを推奨します。

## 誘導性ハード地絡に備えるOUTクランピング・ダイオード

誘導性負荷や長いケーブルがあり、突然の地絡からの保護を要するアプリケーションには、出力クランプを推奨します。このクランプは、標準アプリケーション回路に示すように、TVSとダイオードで実現できます。これは、出力短絡イベント時の誘導性キックバックによるOUTピンの負方向のスパイクを、安全動作領域にクランプするために必要なものです。VINMAXの最大入力電圧に対するTVSの負の最大クランピング電圧は、INピンとOUTピンの間の電圧が80Vを超えることのないようにするために、 $(80 - V_{INMAX})V$ に制限されます。

## レイアウトと放熱

出入力コンデンサはデバイスのできるだけ近くに配置します。IN端子とOUT端子は、短く幅の広いパターンで電源バスに接続する必要があります。通常動作中は、消費電力は小さくパッケージの温度変化はわずかです。

定常的な通常動作時の消費電力は次のように計算できます。

$$P_{SS} = I_{OUT}^2 \times R_{ON}$$

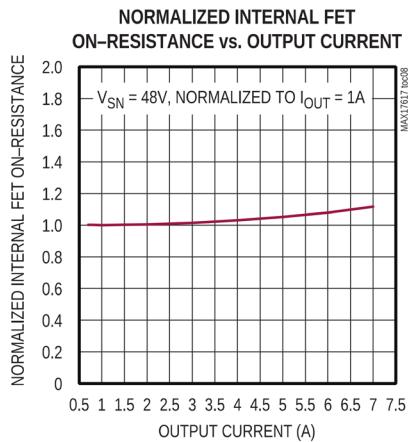

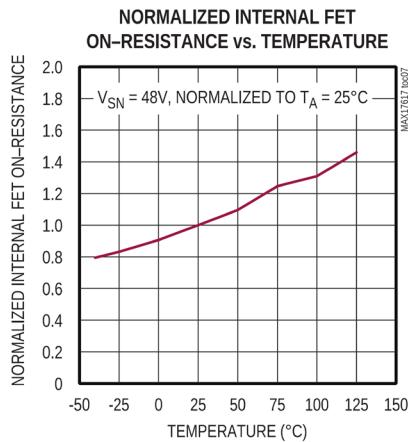

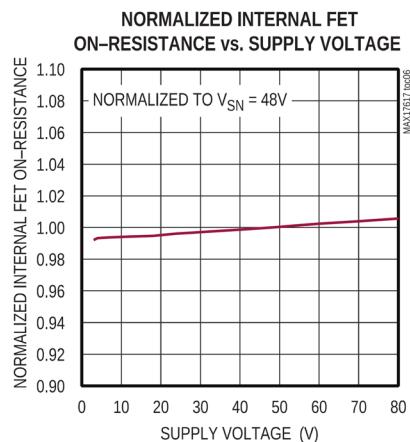

様々な動作温度での $R_{ON}$ の値については、電気的特性の表と標準動作特性を参照してください。内層のグランド・プレーンに適切に放熱するため、露出パッドとグランド・プレーンの間にサーマル・ピアを使用します。

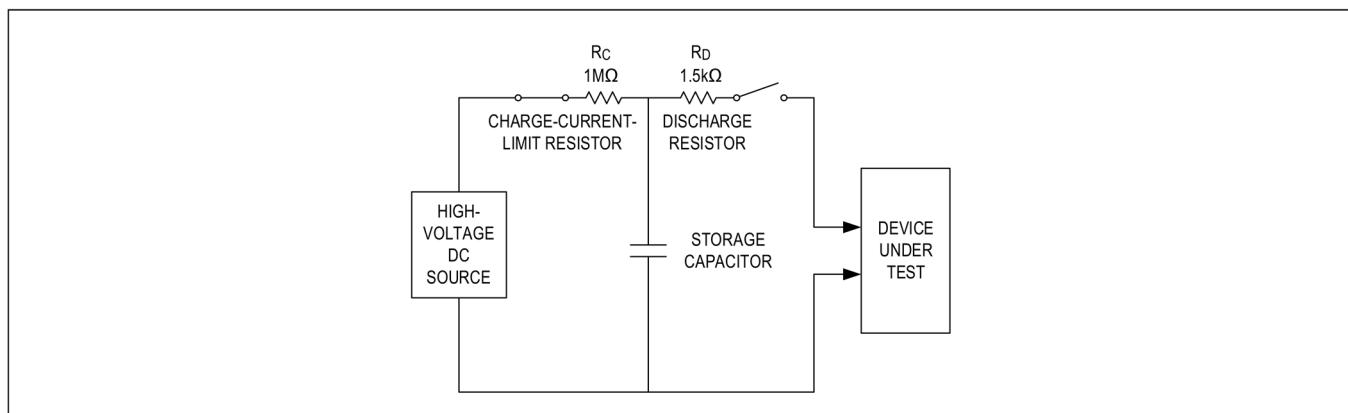

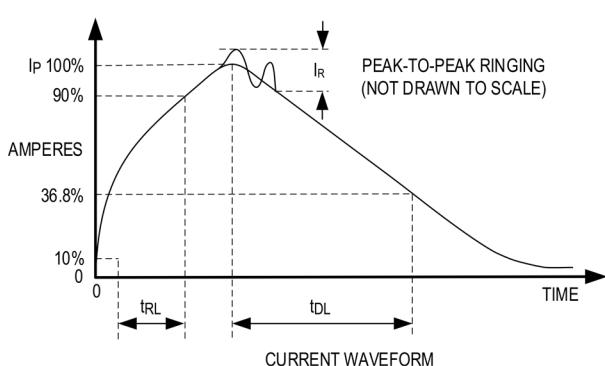

## ESD保護

INでの±2kV（代表値）（HBM）ESDにはコンデンサは不要です。すべてのピンに±2kV（HBM）ESDの保護があります。外付けnFETを用いるアプリケーションでは、INコンデンサのセクションを参照してください。

図31は人体モデル、図32はこれが低いインピーダンスに向けて放電する際に発生する電流波形を示しています。このモデルは対象とするESD電圧まで充電された100pFのコンデンサで構成され、1.5kΩの抵抗を介してデバイスに放電されます。

図31. 人体モデルによるESD試験モデル

図32. 人体モデルの電流波形

## 標準アプリケーション回路

## MAX17617 のアプリケーション回路

## 型番

| PART NUMBER    | TEMP RANGE      | PIN-PACKAGE  | FEATURES |

|----------------|-----------------|--------------|----------|

| MAX17617AFD+   | -40°C to +125°C | 23-Pin FCQFN | OVLO     |

| MAX17617AFD+T  | -40°C to +125°C | 23-Pin FCQFN | OVLO     |

| MAX17617AAFD+  | -40°C to +125°C | 23-Pin FCQFN | OVFB     |

| MAX17617AAFD+T | -40°C to +125°C | 23-Pin FCQFN | OVFB     |

+ は鉛 (Pb) フリー／RoHS 準拠パッケージを表します。

T = テープ&リール。

## 改訂履歴

| 版数 | 改訂日  | 説明   | 改訂ページ |

|----|------|------|-------|

| 0  | 1/25 | 初版発行 | -     |