# **MAX17615**

# 過電圧/低電圧/逆電圧保護機能を内蔵した 4.25V~60V 250mA の電流リミッタ

## 製品のハイライト

- 堅牢な保護機能によりシステムのダウンタイムを低減

- 広い入力電源範囲:+4.25V~+60V

- ホット・プラグイン耐性があり、35V の入力電源まで Transient Voltage Suppressor (TVS) が不要

- 負入力耐性:-65V

- 負出力耐性: -(65 V<sub>IN</sub>)V

- 低 R<sub>ON</sub>: 1.42Ω(代表値)

- ・ 逆電流ブロック保護

- 熱過負荷保護

- -40°C~+125°C の拡張温度範囲

- 最大限の再利用と最小限の適格性再評価を実現する柔軟な設計

- 調整可能な OVLO および UVLO スレッショルド

- プログラマブルな順方向電流制限:全温度範囲にわたり 10mA~20mA 範囲で±6%、20mA~250mA 範囲で±5%の 精度

- プログラマブルな過電流フォルト応答:自動リトライ・ モード、ラッチオフ・モード、および連続モード

- スムーズな電流遷移

- ソリューションの実装面積を削減

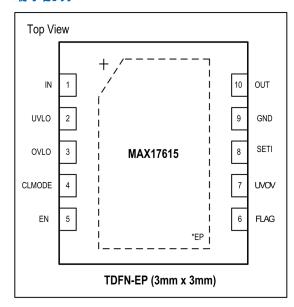

- 10 端子の 3mm × 3mm TDFN パッケージ

- 内蔵 FET

## 主なアプリケーション

小さいトータル・ソリューション・サイズ(センサー・システム)

ファクトリ・オートメーションやビルディング・オートメーションなどのアプリケーションでは、より小さいフォーム・ファクタに、より多くの機能を組み込むという需要が高まっており、電源回路や保護回路に使用できるボード・スペースは制限されています。MAX17615は、順方向 MOSFETと逆方向 MOSFET、電流検出、入出力逆極性保護、順方向および逆方向過電流保護、UVLO/OVLO などの回路を全て1つのチップにまとめているので、ディスクリート・コンポーネントを使用したソリューションと比較して、同じ保護機能を実装するのに必要なトータル・ソリューション・サイズをわずか1/8に抑えることができます。

• 高い電流制限精度(状態監視、バッテリ駆動モジュール) バッテリ駆動の電子機器やバッテリ・チャージャでは、過電 流フォルトからの保護のために高精度の電流制限が必要で す。MAX17615 は±5%の高い電流制限精度を備えているの で、こうしたアプリケーションにおいて安定した過電流保護 を実現できます。

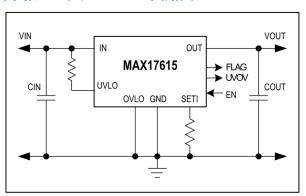

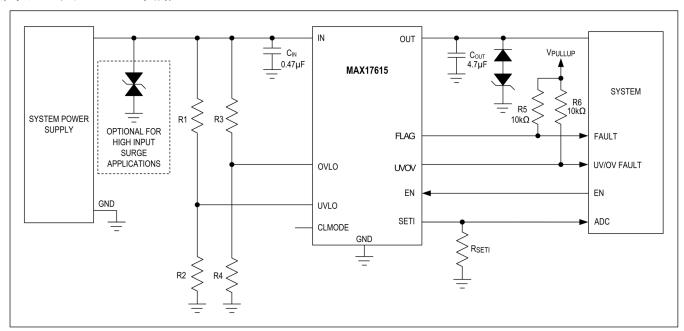

## 簡略アプリケーション回路図

## 端子説明

出力逆極性保護(プロセス計測器、PLC、ネットワーク・モジュール)

離れた場所にある機器に 24V 出力を供給するファクトリ・オートメーション・アプリケーションでは、ケーブル配線のミスによって出力端子に逆極性の電圧が加わるおそれがあります。 MAX17615 はこのようなシナリオに対する信頼性の高い保護機能を備えており、費用のかさむ機器の故障やサービス・コストの発生を防ぎます。

詳細についてはデバイス用途例を参照してください。

型番は、データシートの末尾に記載しています。

## 絶対最大定格

| $N\sim$ GND65 $V\sim$ +65 $V$                                                   | $IN\sim GN$  |

|---------------------------------------------------------------------------------|--------------|

| N~OUT −65V~+65V                                                                 | IN~OU        |

| OUT~GND65V~+65V                                                                 | $OUT \sim C$ |

| VLO, OVLO $\sim$ GND0.3V $\sim$ MAX(V <sub>IN</sub> , V <sub>OUT</sub> ) + 0.3V | UVLO,        |

| $\overline{\text{VOV}}$ , $\overline{\text{FLAG}}$ , EN, CLMODE~GND0.3V~+ 6.0V  | UVOV,        |

| N 電流(DC)262.5mA                                                                 | IN 電流        |

| ETI~GND0.3V~1.6V                                                                | SETI~        |

連続消費電力 (10 端子 TDFN EP (T<sub>A</sub> = +70°C、+70°C を超える 温度では 24.4mW/°C でディレーティング) ) .......1951.2mW 動作温度範囲 ...... -40°C∼+125°C ジャンクション温度範囲 ..... -40°C∼+150°C 保管温度範囲 ..... -65°C∼+150°C リード温度 (はんだ付け処理、10 秒) .....+300°C

Note 1: SETI 端子は内部でクランプされています。この端子に5mAを超える電流をかけると、デバイスが損傷する可能性があります。

Note 2: ジャンクション温度が+125℃を超えると、動作寿命が短くなります。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作のセクションに記載す る規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

# パッケージ情報

# パッケージ・タイプ: 10 TDFN

| Package Code                                           | T1033+1C       |  |

|--------------------------------------------------------|----------------|--|

| Outline Number                                         | <u>21-0137</u> |  |

| Land Pattern Number                                    | 90-0003        |  |

| Thermal Resistance, Four-Layer Board:                  |                |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 41°C/W         |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 9°C/W          |  |

最新のパッケージ外形図とランド・パターン(フットプリント)に関しては、www.maximintegrated.com/packages で確認してください。パッケージ・コードの「+」、「#」、「-」は RoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面は RoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、www.maximintegrated.com/thermal-tutorialを参照してください。

#### 電気的特性

(特に指定のない限り、V<sub>IN</sub> = +4.25~+60V、T<sub>A</sub>= -40℃~+125℃。代表値は V<sub>IN</sub> = +24V、T<sub>A</sub>= +25℃、R<sub>SETI</sub> = 1.2kΩ での値。(Note 3))

| PARAMETER                                | SYMBOL              | CONDITIONS                                                                                     | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|---------------------|------------------------------------------------------------------------------------------------|------|------|------|-------|

| IN Voltage Range                         | V <sub>IN</sub>     |                                                                                                | 4.25 |      | 60   | V     |

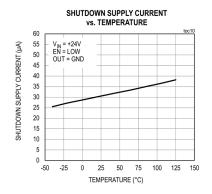

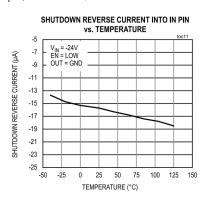

| Shutdown Input Current into IN pin       | I <sub>SHDN</sub>   | V <sub>EN</sub> = 0V                                                                           |      | 37   | 82   | μA    |

| Shutdown Output                          | l                   | $V_{EN} = 0V$ , $V_{OUT} = 0V$                                                                 |      |      | -5   |       |

| Current into OUT pin                     | l <sub>OFF</sub>    | V <sub>EN</sub> = 0V, V <sub>OUT</sub> = -60V, V <sub>IN</sub> = 0V                            |      |      | -27  | μΑ    |

| Reverse Input Current into IN pin        | I <sub>IN_RVS</sub> | V <sub>IN</sub> = -60V, V <sub>OUT</sub> = 0V                                                  | -85  | -50  |      | μA    |

| Reverse Shutdown<br>Current into OUT pin | lout_Rvs            | V <sub>IN</sub> = 0V, V <sub>OUT</sub> = +24V, V <sub>EN</sub> = 0V                            |      | 170  | 400  | μA    |

| Reverse Shutdown<br>Current into IN pin  |                     | V <sub>IN</sub> = 0V, V <sub>OUT</sub> = +24V, V <sub>EN</sub> = 0V, T <sub>A</sub> =<br>+25°C |      |      | -0.4 | μA    |

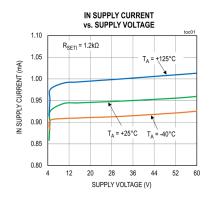

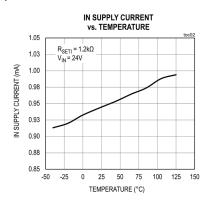

| Supply Current                           | I <sub>IN</sub>     | V <sub>IN</sub> = +24V, V <sub>EN</sub> = 5V                                                   |      | 0.94 | 1.30 | mA    |

(特に指定のない限り、 $V_{IN}$  = +4.25~+60V、 $T_A$ = -40°C~+125°C。 代表値は  $V_{IN}$  = +24V、 $T_A$ = +25°C、 $R_{SETI}$  = 1.2 $k\Omega$  での値。 (Note 3) )

| PARAMETER                                             | SYMBOL               | CONDITIONS                                                                                     | MIN      | TYP   | MAX   | UNITS                                 |

|-------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------|----------|-------|-------|---------------------------------------|

| Internal Undervoltage-                                | V                    | V <sub>IN</sub> rising                                                                         | 4.080    | 4.160 | 4.225 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Trip Level                                            | V <sub>INTUVLO</sub> | V <sub>IN</sub> falling                                                                        | 3.950    | 4.000 | 4.100 | V                                     |

| Undervoltage Threshold                                | V <sub>UVLOR</sub>   | V <sub>UVLO</sub> rising                                                                       | 1.47     | 1.50  | 1.53  | .,                                    |

| Level                                                 | V <sub>UVLOF</sub>   | V <sub>UVLO</sub> falling                                                                      | 1.42     | 1.45  | 1.48  | V                                     |

| Overvoltage Threshold                                 | V <sub>OVLOR</sub>   | V <sub>OVLO</sub> rising                                                                       | 1.47     | 1.50  | 1.53  |                                       |

| Level                                                 | V <sub>OVLOF</sub>   | V <sub>OVLO</sub> falling                                                                      | 1.42     | 1.45  | 1.48  | V                                     |

| UVLO and OVLO<br>Leakage Current                      | I <sub>LEAK</sub>    | V <sub>UVLO</sub> = V <sub>OVLO</sub> = 0 to 2V, T <sub>A</sub> = +25°C                        | -100     |       | 100   | nA                                    |

| UVLO Adjustment<br>Range                              |                      | ( <u>Note 4</u> )                                                                              | 4.25     |       | 59    | V                                     |

| OVLO Adjustment<br>Range                              |                      | ( <u>Note 4</u> )                                                                              | 5.50     |       | 60    | V                                     |

| lata and DOD                                          | $V_{PORR}$           | V <sub>IN</sub> rising                                                                         | 3.3      | 3.7   | 4.0   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Internal POR                                          | V <sub>PORF</sub>    | V <sub>IN</sub> falling                                                                        | 3.1      | 3.5   | 3.8   | V                                     |

| INTERNAL FET                                          |                      |                                                                                                |          |       |       |                                       |

| Internal FET On-<br>Resistance                        | R <sub>ON</sub>      | I <sub>LOAD</sub> = 100mA, V <sub>IN</sub> > 8V                                                |          | 1.42  | 2.70  | Ω                                     |

| Current Limit Adjustment Range                        | I <sub>LIM</sub>     | ( <u>Note 5</u> )                                                                              | 10       |       | 250   | mA                                    |

|                                                       |                      | 10mA < I <sub>LIM</sub> < 20mA                                                                 | -6       |       | +6    | 0,                                    |

| Current Limit Accuracy                                |                      | 20mA ≤ I <sub>LIM</sub> ≤ 250mA                                                                | -5       |       | +5    | %                                     |

| FLAG Assertion Drop-<br>Voltage Threshold             | $V_{FA}$             | Increase (V <sub>IN</sub> - V <sub>OUT</sub> ) drop until FLAG asserts, V <sub>IN</sub> = +24V | 430      | 500   | 570   | mV                                    |

| Reverse Current Blocking Slow- Threshold              | $V_{RIBS}$           | (V <sub>OUT</sub> - V <sub>IN</sub> ), VIN = +24V                                              | 2        | 11    | 20    | mV                                    |

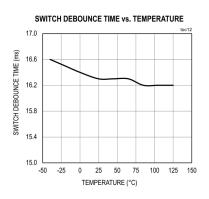

| Reverse Current Blocking Debounce Blanking Time       | <sup>t</sup> DEBRIB  | V <sub>IN</sub> = +24V                                                                         | 100      | 140   | 180   | μs                                    |

| Reverse Current-<br>Blocking Powerup<br>Blanking Time | <sup>t</sup> BLKRIB  |                                                                                                | 14.4     | 16.0  | 17.6  | ms                                    |

| Reverse Current-<br>Blocking Fast Threshold           | $V_{RIBF}$           | (V <sub>OUT</sub> - V <sub>IN</sub> ), V <sub>IN</sub> = +24V                                  | 70       | 105   | 140   | mV                                    |

| Reverse Current-<br>Blocking Fast Response<br>Time    | t <sub>RIB</sub>     | I <sub>REVERSE</sub> = 2.5A ( <u>Note 6</u> )                                                  |          | 150   | 230   | ns                                    |

| Reverse-Blocking<br>Supply Current                    | I <sub>RBL</sub>     | Current into OUT when (V <sub>OUT</sub> - V <sub>IN</sub> ) > 130mV                            |          | 1.00  | 1.35  | mA                                    |

| SETI                                                  |                      |                                                                                                | <u> </u> |       |       | ı                                     |

| R <sub>SETI</sub> x I <sub>LIM</sub>                  | V <sub>RI</sub>      |                                                                                                |          | 1.5   |       | V                                     |

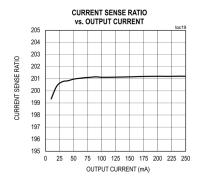

| Current-Mirror Output                                 | C <sub>IRATIO</sub>  | 10mA ≤ I <sub>OUT</sub> ≤ 20mA                                                                 | 190      | 200   | 210   | A/A                                   |

| Ratio                                                 | · IIVATIO            | 20mA ≤ I <sub>OUT</sub> ≤ 250mA                                                                | 193      | 200   | 207   | , , , ,                               |

| Internal SETI Clamp                                   |                      | 5mA into SETI                                                                                  | 1.6      |       | 2.2   | V                                     |

| SETI Leakage Current                                  |                      | V <sub>SETI</sub> = 1.6V, T <sub>A</sub> = +25°C                                               | -0.1     |       | +0.1  | μA                                    |

| LOGIC INPUT                                           |                      |                                                                                                |          |       |       |                                       |

(特に指定のない限り、 $V_{IN}$  = +4.25~+60V、 $T_A$ = -40°C~+125°C。代表値は $V_{IN}$  = +24V、 $T_A$ = +25°C、 $R_{SETI}$  = 1.2k $\Omega$  での値。(Note 3))

| PARAMETER                              | SYMBOL               | CONDITIONS                                                                                                                            | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| EN Input-Logic High                    | V <sub>IH</sub>      |                                                                                                                                       | 1.4  |      |      | V     |

| EN Input-Logic Low                     | V <sub>IL</sub>      |                                                                                                                                       |      |      | 0.4  | V     |

| EN Pullup Voltage                      |                      | EN pin unconnected. V <sub>IN</sub> = 60V                                                                                             |      | 1.6  | 2.0  | V     |

| EN Input Current                       |                      | V <sub>EN</sub> = 5.5V                                                                                                                |      | 17   | 30   | μΑ    |

| EN Pullup Current                      |                      | V <sub>EN</sub> = 0.4V                                                                                                                | 1.0  | 3.0  | 8.0  | μΑ    |

| CLMODE Input-Logic<br>High             |                      |                                                                                                                                       | 2.0  | 3.8  | 4.9  | V     |

| CLMODE Input-Logic Low                 |                      |                                                                                                                                       | 0.15 | 0.60 | 0.95 | V     |

| CLMODE Pullup Input<br>Current         |                      |                                                                                                                                       | 8    | 10   | 12   | μA    |

| FLAG, UVOV OUTPUT                      |                      |                                                                                                                                       |      |      |      |       |

| FLAG, UVOV Output<br>Logic-Low Voltage |                      | I <sub>SINK</sub> = 1mA                                                                                                               |      |      | 0.4  | V     |

| FLAG, UVOV Output<br>Leakage Current   |                      | $V_{IN} = V_{\overline{FLAG}} = V_{\overline{UVOV}} = 5.5V. \overline{FLAG}$ and $\overline{UVOV}$ pins are deasserted, $T_A$ = +25°C |      |      | 0.1  | μA    |

| TIMING CHARACTERIS                     | TICS                 |                                                                                                                                       |      |      |      |       |

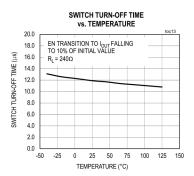

| Switch Turn-On Time                    | ton_switch           | $R_{LOAD} = 1k\Omega$ , $C_{LOAD} = 0pF$ , $V_{IN} = +24V$                                                                            |      | 230  | 450  | μs    |

| Overvoltage Switch Turn-Off Time       | toff_ovp             | $V_{OVLO}$ exceeds $V_{OVLOR}$ as a step;<br>$R_{LOAD} = 1k\Omega$ , $V_{IN} = +24V$                                                  |      | 1.0  | 1.3  | μs    |

| Overvoltage Falling Edge Debounce Time | t <sub>DEB_OVP</sub> |                                                                                                                                       |      | 20   |      | μs    |

| IN Debounce Time                       | t <sub>DEB</sub>     | From $(V_{IN\_UVLO} < V_{IN} < V_{IN\_OVLO})$ and EN = High, to $V_{OUT}$ = 10% of $V_{IN}$ . Elapses only at power-up.               | 14.4 | 16.0 | 17.6 | ms    |

| Current Limit Blanking<br>Time         | t <sub>BLANK</sub>   | ( <u>Note 7</u> )                                                                                                                     | 144  | 160  | 176  | ms    |

| Current Limit Autoretry<br>Time        | t <sub>RETRY</sub>   | After blanking time from I <sub>OUT</sub> > I <sub>LIM</sub> to FLAG deasserted. ( <i>Note 8</i> )                                    | 1.08 | 1.20 | 1.32 | s     |

| THERMAL PROTECTION                     | N                    |                                                                                                                                       |      |      |      |       |

| Thermal Shutdown Threshold             | TJ                   |                                                                                                                                       |      | 160  |      | °C    |

| Thermal Shutdown<br>Hysteresis         | T <sub>J(HYS)</sub>  |                                                                                                                                       |      | 28   |      | °C    |

**Note 3:** 全てのデバイスは  $T_A = +25$ °C で 100%出荷テストしています。動作温度範囲を超える制限値は設計により裏付けられており、出荷テストは行っておりません。

Note 4: ユーザ設定可能。方法については過電圧ロックアウト (OVLO) および低電圧ロックアウト (UVLO) のセクションを参照してください。

Note 5: 精度は低下しますが、電流制限値を10mA未満とすることも可能です。

Note 6: 出荷テストは行っていませんが、設計により裏付けられています。

Note 7: 過負荷や短絡の条件下では、デバイスの消費電力が増加します。ジャンクション温度がサーマル・シャットダウン・スレッショルド (T<sub>I</sub>) を超過すると、デバイスはサーマル・シャットダウン保護に入ります。

Note 8: 自動リトライ時間とブランキング時間の比は 7.5 に固定されています。

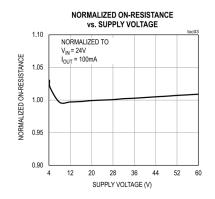

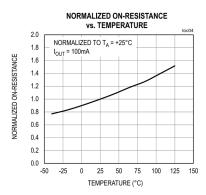

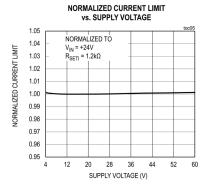

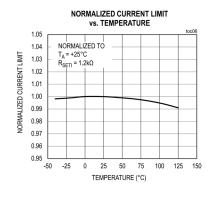

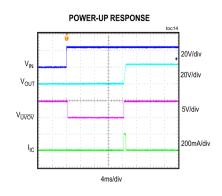

# 標準動作特性

(特に指定のない限り、 $C_{IN} = 0.47 \mu F$ 、 $C_{OUT} = 4.7 \mu F$ 、 $T_A = +25 ^{\circ} C$ )

(特に指定のない限り、 $C_{IN}=0.47\mu F$ 、 $C_{OUT}=4.7\mu F$ 、 $T_A=+25$ °C)

(特に指定のない限り、 $C_{IN}=0.47\mu F$ 、 $C_{OUT}=4.7\mu F$ 、 $T_A=+25$ °C)

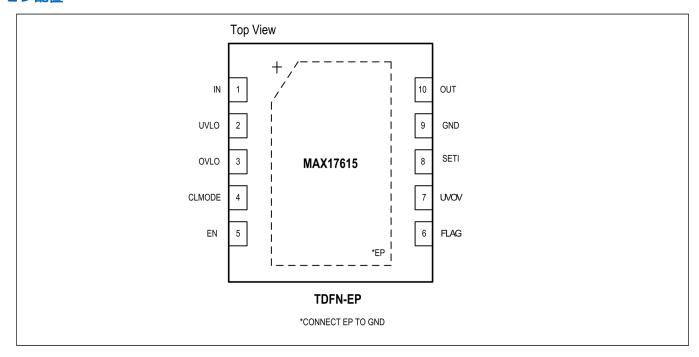

# ピン配置

# 端子説明

| 端子 | 名称     | 機能                                                                                                                                                         |

|----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | IN     | 入力端子。GND との間に低 ESR のセラミック・コンデンサを接続します。ホット・プラグイン・アプリケーションについてはアプリケーション情報のセクションを参照してください。                                                                    |

| 2  | UVLO   | UVLO 調整。IN と GND の間に抵抗分圧器を接続して UVLO スレッショルドを設定します。                                                                                                         |

| 3  | OVLO   | OVLO 調整。IN と GND の間に抵抗分圧器を接続して OVLO スレッショルドを設定します。                                                                                                         |

| 4  | CLMODE | 電流制限モード選択。CLMODE を GND に接続すると連続モードになります。ラッチオフ・モードの場合は、CLMODE と GND の間に 150k $\Omega$ の抵抗を接続します。CLMODE を未接続の状態にすると自動リトライ・モードになります。                          |

| 5  | EN     | アクティブ・ハイのイネーブル入力。内部で 1.6V にプルアップされています。                                                                                                                    |

| 6  | FLAG   | オープンドレインのフォルト表示出力。FLAGは以下の条件でローになります。     過電流時間がブランキング時間を超えた。     逆電流が検出された。     R <sub>SETI</sub> が 1kΩ (最大値) 未満。     IN 端子の電圧は正常だが OUT 端子に逆極性の電圧が加わっている。 |

| 7  | ŪVOV   | オープンドレインのフォルト表示出力。UVOVは以下の条件でローになります。  ◆ 入力電圧が UVLO の立下がりスレッショルド未満に低下。  ◆ 入力電圧が OVLO の立上がりスレッショルドを超えて上昇。                                                   |

| 8  | SETI   | 過電流制限調整端子および電流モニタ出力。過電流制限を設定するには、SETIと GND の間に抵抗を接続します。電流制限/スレッショルドの設定のセクションを参照してください。SETIには 10pF を超えるコンデンサは接続しないでください。                                    |

| 9  | GND    | グラウンド。                                                                                                                                                     |

| 10 | OUT    | 出力端子。出力ケーブルが長い場合や誘導性負荷がある場合は、アプリケーション情報のセクションを参<br>照してください。                                                                                                |

| _  | EP     | 露出パッド。熱性能を最適化するために、数個のサーマル・ビアを使用して、EP を面積の広い GND プレーンに接続します。リファレンスのレイアウト設計については、MAX17615 の評価キットのデータシートを参照してください。                                           |

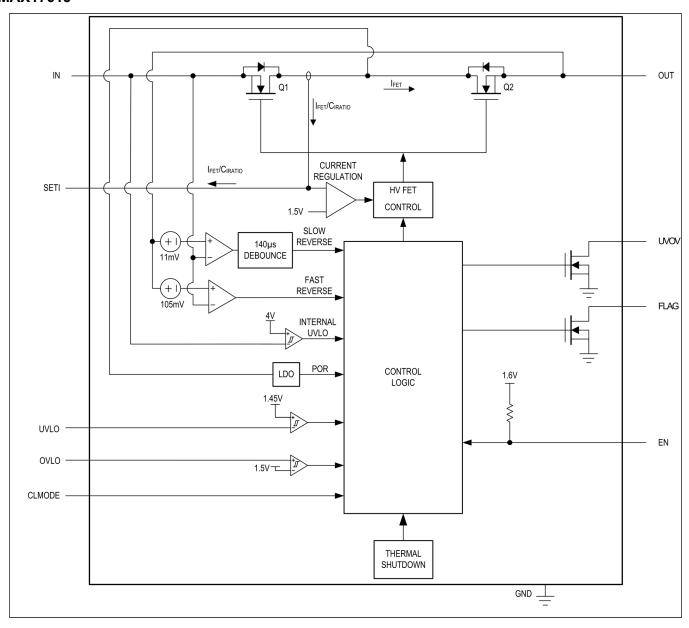

# 機能図

# **MAX17615**

#### 詳細説明

MAX17615 過電圧および過電流保護デバイスを使用すれば、正負の入力電圧フォルトについては最大+ $60V\sim-65V$ 、出力負荷電流については最大 250mA までの範囲で、調整可能な保護限度をシステムに設定できます。このデバイスは直列に接続された 2 つの内部 MOSFET を備えており、その合計  $R_{ON}$  は  $1.42\Omega$ (代表値)という低い値です。このデバイスは、負の入力電圧を完全に遮断します。このデバイスは、誤って逆極性の出力電圧が接続された場合でも、その大きさが $-(65-V_{IN})V$  以下であれば耐えることができます。また、入力低電圧保護は  $4.25V\sim59V$  の範囲内、過電圧保護は  $5.5V\sim60V$  の範囲内に設定できます。更に、このデバイスには、4V(代表値)の内部低電圧ロックアウト立下がりスレッショルドが設定されています。

このデバイスは、マスタ管理システムにより、EN 端子を通じてイネーブルまたはディスエーブルされます。これによりスイッチが動作し、接続された負荷への電力供給をオンまたはオフに切り替えます。

デバイス内を流れる電流は電流制限を設定することにより制限されますが、この設定は SETI と GND の間に接続した抵抗によって行います。電流制限値は 10mA~250mA の範囲で設定可能です。デバイスの電流が設定された電流制限値に達するか超過すると、内蔵 FET のオン抵抗を調整することによって電流が設定値に制限されます。電流制限の下で動作している場合、このデバイスには 3 つの異なる動作モードがあります。すなわち、自動リトライ・モード、連続モード、ラッチオフ・モードです。また、SETI 端子の電圧は GND 基準で、通常動作時の値はデバイスの電流に比例します。SETI 端子に現れる電圧をモニタリング・システムの ADC で読み取ると、デバイスの瞬時電流を記録できます。

MAX17615 にはFLAGとUVOVの状態表示信号があり、様々な動作状態やフォルトの信号を表示します。状態表示信号端子自体はオープンドレインであり、外付け抵抗で適切なシステム・インターフェース電圧にプルアップする必要があります。

MAX17615 は、OUT 端子から IN 端子への逆電流をブロックします。過度な電力消費に対してはサーマル・シャットダウン保護機能を内蔵しています。

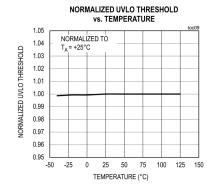

## 低電圧ロックアウト(UVLO)

UVLO 立上がりスレッショルドを調整するには、標準動作回路のセクションに示すように、UVLO 端子に抵抗分圧器を外付けします。次式を用いて UVLO 電圧を調整できます。R1 の推奨値は  $2.2M\Omega$  です。

$$V_{UVLO} = V_{UVLOR} \times \left[1 + \frac{R_1}{R_2}\right]$$

ここで、

V<sub>UVLOR</sub>は UVLO 立上がりスレッショルド、

VuvLo は、デバイスが UVLO 状態を終了する入力電源電圧です。

UVLO 端子の電圧が  $V_{UVLOR}$ を超えると、MAX17615 は低電圧ロックアウト (UVLO) 状態を終了してオンになります。UVLO 端子の電圧が  $V_{UVLOF}$ 未満に低下すると、デバイスは UVLO 状態に入ってオフになります。このデバイスには、4.16V (代表値) の UVLO 立上がりスレッショルドもあります。外部抵抗分圧器ベースの UVLO 設定値は、この内部 UVLO 立上がりスレッショルド未満に設定しないでください。

MAX17615 は、Q1 FET と Q2 FET の中間で検出される内部パワーオン・リセット(POR)機能を備えています。このデバイスは、IN 端子の電圧が 3.5V(代表値)の内部 POR 立下がりスレッショルド未満に低下すると、内蔵 FET Q1 と Q2 をオフにします。これにより $\overline{\text{UVOV}}$  端子がハイにアサートされて、SETI 端子は非アクティブになります。IN 端子の電圧が 3.7V(代表値)の内部 POR 立上がりスレッショルドを超えると、 $\overline{\text{UVOV}}$ 端子がローにアサートされて SETI 端子はアクティブになります。内蔵 FET Q1 と Q2 はオフのままです。このデバイスは、IN 端子で検出する内部 UVLO も実装しています。IN 電圧が 4.16V(代表値)の内部 UVLO 立上がりスレッショルドを超えると、Q1 FET がオンになります。Q2 FET は、瞬時 IN 電圧がユーザの定義した外部 UVLO 電圧立上がりスレッショルドを超えて $\overline{\text{UVOV}}$ 端子がハイにアサートされてから、16ms( $\overline{\text{toeb}}$ )後にオンになります。

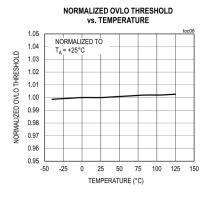

## 過電圧ロックアウト(OVLO)

OVLO 立上がりスレッショルドを調整するには、標準動作回路のセクションに示すように、OVLO 端子に抵抗分圧器を外付けします。次式を用いて OVLO 電圧を調整できます。R3 の推奨値は 2.2M $\Omega$  です。

$$V_{\text{OVLO}} = V_{\text{OVLOR}} \times \left[1 + \frac{R_3}{R_4}\right]$$

ここで、VovLoR は OVLO 立上がりスレッショルドです。

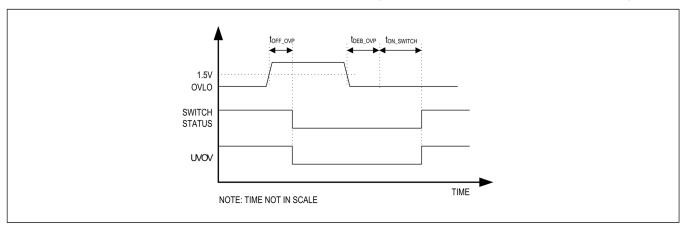

OVLO 端子の電圧が Vovlor を超え、その状態にある時間が過電圧スイッチオフ時間( $toff_OVP$ )に達すると、MAX17615 は過電圧ロックアウト(OVLO)状態に入ってオフになり、 $\overline{UVOV}$ ローをアサートします。このデバイスは、OVLO 条件がなくなると、過電圧立下がりデバウンス時間( $t_{DEB_OVP}$ )が経過するのを待ってからスイッチ・ターンオン手順を開始します。スイッチ・ターンオン時間( $t_{ON_SWITCH}$ )が経過して $\overline{UVOV}$ がハイにアサートされると、スイッチは再びオンになります。過電圧状態での代表的な動作を図1に示します。

図 1. 過電圧フォルト時のタイミング図

## 入力電圧逆極性保護

MAX17615 は、入力電圧が誤って逆極性状態になってしまった場合でも、MAX17615 自体と下流側の負荷回路を保護します。入力電圧逆極性状態時は内蔵 FET がオフのままになります。

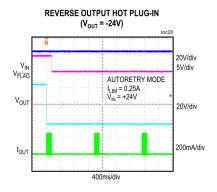

# 出力電圧逆極性保護

MAX17615 は、出力電圧が誤って逆極性状態になってしまった場合でも、MAX17615 自体と入力電源接続を保護します。逆極性出力電圧は、出力端子間の活線負荷の誤配線により OUT 端子と GND 端子の間に生じる可能性があります。デバイスがイネーブルされると( $V_{EN} > V_{IH}$ )、 $R_{SETI}$  抵抗によって設定される電流制限に従って OUT 端子の電流が制限されます。デバイスがシャットダウン・モードのときは( $V_{EN} < V_{IL}$ )、OUT 電流が  $27\mu A$ (最大)に制限されます。

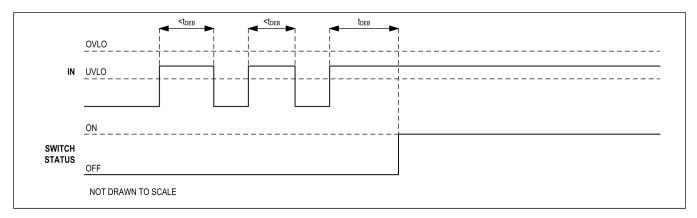

## 入力デバウンス保護

このデバイスには入力デバウンス保護機能があります。デバイスは、入力電圧が UVLO スレッショルドより高い状態がデバウンス時間 (tdeb) より長く続いた場合のみ、動作を開始(内蔵 FET をオン) します。tdeb はデバイスの起動時のみカウントされます。この機能は、電源供給のランプアップ時に EN 信号が有効になっているアプリケーションで使用することを意図したものです。図 2 にデバウンスの代表的なタイミング図を示します。

# 過電圧/低電圧/逆電圧保護機能を内蔵した

# 4.25V~60V 250mA の電流リミッタ

図 2. デバウンスのタイミング図

# イネーブル

MAX17615 は、EN 端子を EN スレッショルド電圧より高くすることによってイネーブルし、低くすることによってディスエーブルします。したがってこのデバイスでは、EN 端子を使って接続負荷への電力供給をオン/オフできます。ラッチオフ・モードでは、EN 端子を  $15\mu s$  以上かけてトグルすると、フォルト状態がリセットされてデバイスが動作を再開します。EN 端子は内部で 1.6V にプルアップされていて、オープンにしておくと常時オン・オプションになります。デバイスが EN 端子でオンにされたときには、入力デバウンス時間( $t_{DEB}$ )が有効です。

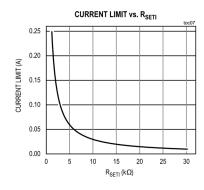

# 電流制限/スレッショルドの設定

デバイスに電流制限スレッショルドを設定するには、SETI と GND の間に抵抗を接続します。電流制限設定抵抗の値は、次式を使用して計算します。

$$R_{SETI}(k\Omega) = \frac{300}{I_{LIM}(mA)}$$

ここで、ILIMは目的の電流制限値で単位は mA です。

$1.2k\Omega$  未満の  $R_{SEII}$ は使用しないでください。表 1 には様々な抵抗値に対する電流制限スレッショルドを示しています。

このデバイスは、IN 端子に流れ込む電流を読み出すことができます。 $C_{IRATIO}$ の比を持つ電流ミラーが、電流検出オートゼロ・オペアンプを使用して実装されています。ミラーリングされた電流は、SETI 端子から外付け電流制限抵抗に流れます。SETI 端子の電圧は、次の関係式により IN 電流に関する情報を提供します。

$$I_{\text{IN-OUT}}(A) = \frac{V_{\text{SETI}}(V)}{R_{\text{SETI}}(k\Omega)}$$

SETI を無接続のままにした場合は  $V_{SETI} \ge 1.5V$  です。Q2 FET がターンオフして、流れる電流は内部回路による数  $\mu A$  だけになります。起動時はこれによってスイッチがオフのままになり、 $t_{BLANK}$  の経過後に $\overline{FLAG}$ がアサートされます。起動時に  $R_{SETI}$  が  $350\Omega$  より低ければ、スイッチがオフのままで $\overline{FLAG}$ がアサートされます。測定の減衰特性を最適にするため、SETI 端子の容量は 10pF までに制限します。

表 1. 電流制限スレッショルドとの抵抗値の関係

| R <sub>SETI</sub> (kΩ) | CURRENT LIMIT (mA) |

|------------------------|--------------------|

| 30                     | 10                 |

| 12                     | 25                 |

| 6                      | 50                 |

| 3                      | 100                |

| 2                      | 150                |

| 1.5                    | 200                |

| 1.2                    | 250                |

# 過電圧/低電圧/逆電圧保護機能を内蔵した

# 4.25V~60V 250mA の電流リミッタ

## 電流制限タイプの選択

CLMODE 端子は、デバイスの過電流応答を次の 3 つのモードの 1 つに設定するために使われます。すなわち、自動リトライ・モード (CLMODE 端子は未接続のまま)、連続モード (CLMODE 端子を GND に接続)、そしてラッチオフ・モード (CLMODE と GND の間に 150k $\Omega$  の抵抗を接続)です。

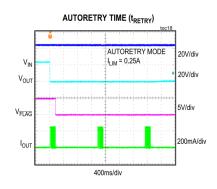

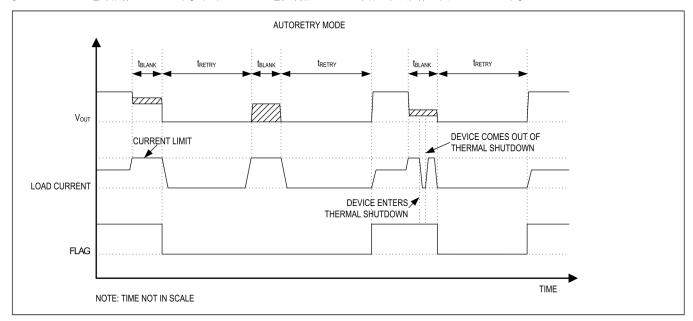

# 自動リトライ電流制限

自動リトライ電流制限モードでは、デバイスを流れる電流が電流制限スレッショルドに達すると、 $t_{BLANK}$  タイマーがカウントを開始します。過電流状態の時間が  $t_{BLANK}$  を超えると、 $\overline{FLAG}$ 端子がアサートされます。 $t_{BLANK}$  が経過する前に過電流状態が解消されると、タイマーはリセットされます。デバイスがサーマル・シャットダウン・モードに入ると出力 Q2 FET がターンオフし、ジャンクション温度が  $T_{I(HYS)}$  低下すると再びターンオンします。この熱サイクルは、経過時間が  $t_{BLANK}$ に達するまで続きます。 $t_{BLANK}$ が経過すると、直ちにリトライ時間遅延( $t_{RETRY}$ )のカウントが始まります。 $t_{RETRY}$ の間スイッチはオフのままで、 $t_{RETRY}$ が経過するとスイッチがオンに戻ります。フォルトが依然として存在する場合はこのサイクルが繰り返され、 $\overline{FLAG}$ 端子はアサートされたままになります。過電流状態が解消されると、スイッチはオンのままになります。

この自動リトライ機能により、過電流状態または短絡状態時のシステム電力を削減できます。 $t_{BLANK}$ の間スイッチがオンの場合、電源電流は電流制限値に維持されます。 $t_{RETRY}$ の間は、スイッチに電流は流れません。したがって、平均出力電流は、設定された電流制限値に比べてはるかに小さくなります。平均出力電流は次式で計算できます。

$$I_{LOAD} = I_{LIM} \left[ \frac{t_{BLANK}}{t_{RETRY} + t_{BLANK}} \right]$$

$t_{BLANK}$ が 160ms(代表値)、 $t_{RETRY}$ が 1200ms(代表値)とすると、デューティ・サイクルは 11.8%となり、全時間スイッチがオンの場合と比較して 88.2%の電力削減となります。自動リトライ電流制限モードの代表的な動作を図 3 に示します。

図 3. 自動リトライ・モード時のフォルト・タイミング図

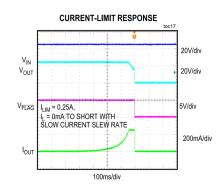

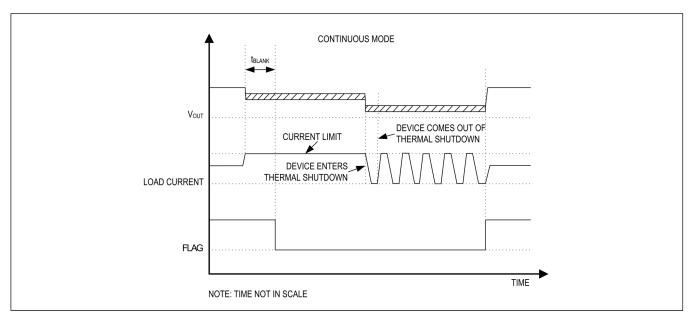

## 連続電流制限

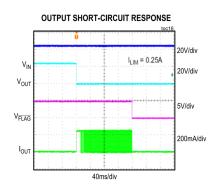

連続電流制限モードでは、デバイスを流れる電流が電流制限スレッショルドに達すると、デバイスが出力電流を設定済みの電流制限値に制限します。デバイスがサーマル・シャットダウン・モードに入ると出力 Q2 FET がターンオフし、ジャンクション温度が  $T_{J(HYS)}$ 低下すると再びターンオンします。過電流状態の時間が  $t_{BLANK}$ を超えると $\overline{FLAG}$ 端子がアサートされ、過電流状態が解消されるとデアサートされます。連続電流制限モードの代表的な動作を図 4 に示します。

図4. 連続モード時のフォルト・タイミング図

# ラッチオフ電流制限

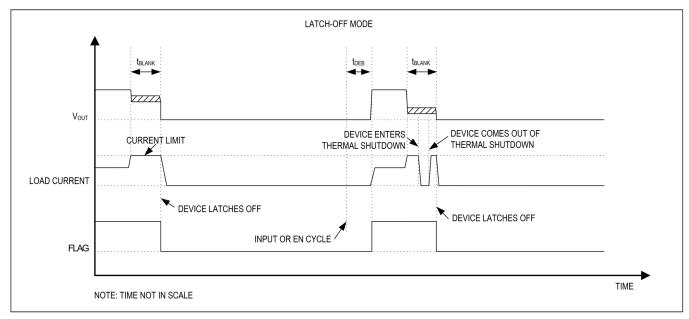

ラッチオフ電流制限モードでは、デバイスを流れる電流が電流制限スレッショルドに達すると、 $t_{BLANK}$  タイマーがカウントを開始します。過電流状態の時間が  $t_{BLANK}$  を超えると、 $\overline{FLAG}$ 端子がアサートされます。 $t_{BLANK}$  が経過する前に過電流状態が解消されると、タイマーはリセットされます。デバイスがサーマル・シャットダウン・モードに入ると出力 Q2 FET がターンオフし、ジャンクション温度が  $T_{I(HYS)}$ 低下すると再びターンオンします。過電流状態が  $t_{BLANK}$  を超えて続くとデバイスはオフになり、そのままオフの状態を維持します。デバイスをリセットするには、制御ロジック(EN)をトグルするか、入力電圧を一度オフにしてから再びオンにします。ラッチオフ電流制限モードの代表的な動作を図 5 に示します。

図 5. ラッチオフ・モード時のフォルト・タイミング図

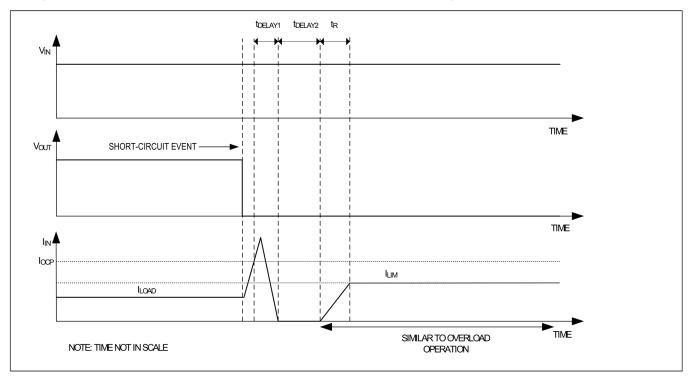

#### 短絡保護

ハード出力短絡の発生時は、デバイスを流れる電流が急激に増加します。このデバイスは高速トリップ電流コンパレータを備えており、出力短絡時のピーク電流を制限できます。この高速トリップ電流コンパレータは、FET を流れる電流が  $I_{OCP}$  を超えると、 $I_{\mu S}$  ( $I_{DELAY1}$ ) 以内に内蔵の Q2 FET だけをオフにします。 $I_{OCP}$  は、設定電流制限値より  $I_{OCP}$  るの個本 高い値に内部で設定されています。 $I_{OCP}$  は、設定電流制限値に制限して、上述の電流制限モードの各セクションで説明したように動作します。  $I_{OCP}$  スレッショルドを超過したときのシステム挙動を示します。

図 6. 高速過電流トリップのタイミング図

## 逆電流保護

MAX17615 は、OUT 端子から IN 端子へ逆電流が流れるのを防止します。逆電流の性質には2種類があります。

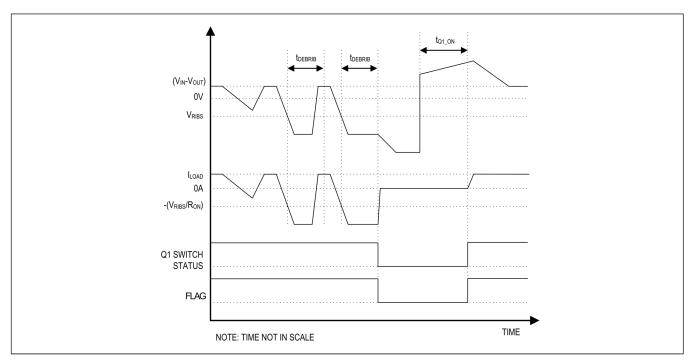

逆電流ブロック・デバウンス・ブランキング時間(tdebrib)の間に( $V_{IN}$  –  $V_{OUT}$ ) <  $V_{RIBS}$  の状態になると、低速逆電流状態が検出されます。 入力 Q1 FET だけがターンオフしてFLAG端子がアサートされ、出力 Q2 FET はオンに維持されます。この期間およびその後に、デバイスは OUT 端子と IN 端子の電圧差をモニタして、逆電流状態が続いているかどうかを判定します。逆電流状態が解消されると、Q1 FET が再びターンオンしてFLAG端子がデアサートされます。 Q1 FET のターンオンにかかる時間は  $t_{Q1}$  ON (約  $100\mu$ s) です。低速逆電流状態の代表的な動作を図 7 に示します。

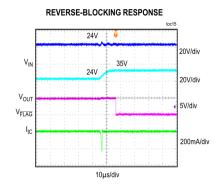

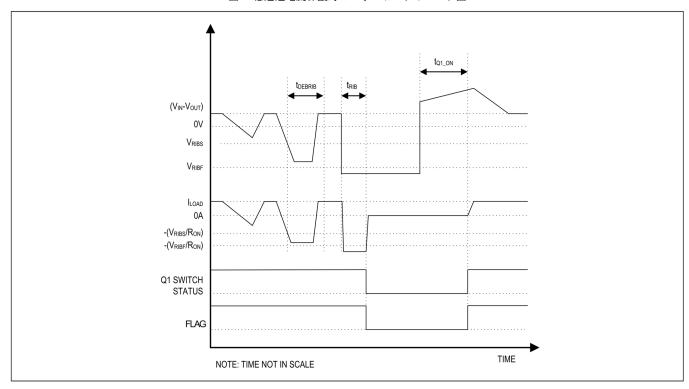

逆電流ブロック高速応答時間( $t_{RIB}$ )の間に( $V_{IN}$  –  $V_{OUT}$ ) <  $V_{RIBF}$  の状態になると、高速逆電流状態が検出されます。入力 Q1 FET だけがターンオフして $\overline{FLAG}$ 端子がアサートされ、出力 Q2 FET はオンに維持されます。この期間およびその後に、デバイスは OUT 端子と IN 端子の電圧差をモニタして、逆電流状態が続いているかどうかを判定します。逆電流状態が解消されると、Q1 FET が再びターンオンして $\overline{FLAG}$ 端子がデアサートされます。Q1 FET のターンオンにかかる時間は  $t_{QLON}$ (約  $100\mu s$ )です。高速逆電流状態の代表的な動作を図 8 に示します。

このデバイスには、逆電流保護用に、低速(<140μs)と高速(<150ns)の応答時間を持つ 2 つの逆電流スレッショルドが設定されています。低速逆電流保護用のスレッショルドは 11mV(代表値)で、高速逆電流保護用は 105mV(代表値)です。この機能により、ノイズの多い環境でも確実な動作が実現される一方で、入力短絡や出力端子のホット・プラグインといった厳しいフォルト状態下でも迅速な保護を実現します。

図 7. 低速逆電流保護時のフォルト・タイミング図

図 8. 高速逆電流保護時のフォルト・タイミング図

#### フォルト出力

このデバイスには $\overline{FLAG}$ と $\overline{UVOV}$ という 2 つのオープンドレイン・フォルト出力があり、これらの出力と  $\overline{DC}$  電源との間には外付けのプルアップ抵抗を接続する必要があります。下記の条件のいずれか 1 つが満たされると、 $\overline{FLAG}$ 端子がローになります。

- 過電流状態の時間がブランキング時間を超える

- 逆電流が検出される

- R<sub>SETI</sub>が 1kΩ (最大値) 未満になる

- IN 端子の電圧が設定された UVLO~OVLO の範囲内で有効なときに、OUT 端子の極性が逆になる

また、下記の条件のいずれか1つが満たされると、UVOVフォルト出力がローになります。

- 入力電圧が UVLO の立下がりスレッショルド未満に低下する

- 入力電圧が OVLO の立上がりスレッショルドを超えて上昇する

起動時、 $\overline{\text{UVOV}}$ 端子は、入力電圧が UVLO 立上がりスレッショルドを超えてから 16ms のデバウンス時間が経過した後に、デアサートされます。

## サーマル・シャットダウン保護

このデバイスは過熱に対する保護のためにサーマル・シャットダウン機能を備えており、ジャンクション温度が+160°C(代表値)を超えるとターンオフします。ジャンクション温度が 28°C(代表値)低下すると、デバイスはサーマル・シャットダウン状態を終了して通常動作を再開します。

# 過電圧/低電圧/逆電圧保護機能を内蔵した

# 4.25V~60V 250mA の電流リミッタ

## アプリケーション情報

# IN コンデンサ

負荷電流が突然変動しても入力電圧を一定に維持できるように、IN 端子と GND の間には  $0.47\mu F$  のコンデンサを接続することを推奨します。

## IN 端子のホット・プラグイン

システム電源アプリケーションの多くは、放射エミッションを減少させて ESD 耐性を高めるために、入力フィルタ・コンデンサを必要とします。ホット・プラグイン・アプリケーションでは、ケーブルの寄生インダクタンスと入力コンデンサによって、電源ケーブルを入力端子に接続したときにオーバーシュートやリンギングが発生します。この作用により、保護デバイスには供給電圧のほぼ 2 倍の電圧がかかります。工業用アプリケーションでは、システムをこうした状況から保護するために、トランジェント電圧サプレッサ(TVS)がよく使用されます。保護性能を改善するには、サージ電圧を最大で 60V に制限できる TVS を入力端子の近くに配置する必要があります。IN端子の最大許容スルー・レートは  $100V/\mu s$ です。

## 入力ハード地絡

多くのシステム・アプリケーションには入力短絡保護が必要です。このデバイスは、OUT 端子に流入して IN 端子から流出する逆方向電流を検知して、内蔵 FET をターンオフします。逆方向電流の大きさは、入力回路のインダクタンスと IN 端子近くに配置された容量によって異なります。

$V_{IN}$ が「 $(V_{OUT} - V_{IN}) > 60V$ 」という条件を満たすような負の値となった場合は、デバイスが損傷する可能性があります。

#### OUT コンデンサ

接続可能な最大容量性負荷( $C_{MAX}$ 、 $\mu F$ )は、電流制限設定値( $I_{LIM}$ 、mA)、ブランキング時間( $t_{BLANK}$ 、ms)、入力電圧( $V_{IN}$ 、V)、および予め設定された電流制限モードの関数です。

自動リトライ・モードとラッチオフ電流制限モードの場合、CMAXは以下の関係を使って計算します。

$$C_{MAX}(\mu F) = \frac{I_{LIM}(mA) \times t_{BLANK(TYP)}(ms)}{V_{IN}(V)}$$

例えば、 $V_{IN} = 24V$ 、 $t_{BLANK}$ (代表値) = 160ms、 $I_{LIM} = 250$ mA の場合、 $C_{MAX}$ は 1667 $\mu F$  です。

自動リトライおよびラッチオフ電流制限モードでは、出力コンデンサの値が  $C_{MAX}$ を超えると、誤って過電流状態がトリガされる可能性があります。なお、上の式は負荷電流が流れていないことを前提としています。負荷電流が流れると、コンデンサの充電電流がオフセットされることによって充電時間が長くなり、そのために誤って過電流状態と判定されてしまう可能性があります。また、アプリケーション PCB の動作温度と熱抵抗特性によっては、ジャンクション温度がサーマル・シャットダウン・スレッショルド  $(T_I)$  に達する可能性があります。その場合はデバイスが出力 Q2 FET をターンオフして、ジャンクション温度が  $T_{I(HYS)}$ 低下した後に再びターンオンします。自動リトライ・モードでは、 $t_{BLANK}$  が経過するまでこの熱サイクルが続きます。 $t_{BLANK}$  の経過後は、直ちに  $t_{RETRY}$  のカウントが開始されます。 $t_{RETRY}$  の間は、スイッチがオフのままになります。 $t_{RETRY}$  が経過するとスイッチが再びオンに戻り、出力容量の充電を続けます。ラッチオフ電流制限モードでは、 $t_{BLANK}$  が経過するまで熱サイクルが続きます。デバイスはターンオフし、 $t_{BLANK}$  が経過するまで熱サイクルが続きます。

連続電流制限モードでは、より大きい出力コンデンサを充電できます。アプリケーション PCB の動作温度と熱抵抗特性によっては、ジャンクション温度がサーマル・シャットダウン・スレッショルド  $(T_I)$  に達して、動作ジャンクション温度が 2 つのサーマル・シャットダウン・ヒステリシス制限値の間にある場合は、デバイスが周期的な動作をします。したがって、連続動作時はより大きい出力コンデンサを充電できます。

## OUT 端子のホット・プラグイン

アプリケーションによっては、入力電圧の有無に関わらず、デバイスの OUT 端子に正電圧または負電圧が加わる可能性があります。こうした状況では、OUT 端子に流れ込んで IN 端子から流れ出す逆電流をデバイスが検知して、内蔵 FET をオフにします。OUT 端子に外部から電圧を加えると、ケーブルの寄生インダクタンスと入出力コンデンサによってオーバーシュートやリンギングが発生します。これによりデバイスには最大 2 倍の電圧が加わることになるので、デバイスが損傷する可能性があります。したがって、過電圧状態でも端子の電圧が絶対最大定格を超過しないように、電圧クランプを使用することを推奨します。OUT 端子の最大許容スルー・レートは 100V/μs です。

## 誘導性ハード地絡に備える OUT クランピング・ダイオード

誘導性負荷や長いケーブルがあり、突然の地絡からの保護を要するアプリケーションには、出力クランプを推奨します。このクランプは、標準アプリケーション回路に示すように、TVS とダイオードで実現できます。このクランプは、出力短絡イベント時の誘導性キックバックによる OUT 端子の負電圧スパイクを制限するために必要です。

# レイアウトと放熱

短絡状態を出力するためのスイッチ応答時間を最適化するには、全ての配線パターンをできるだけ短くして、望ましくない寄生インダクタンスの影響を減らすことが非常に重要です。入力コンデンサと出力コンデンサを、デバイスのできるだけ近く(5mm 以下)に配置してください。IN と OUT は、短くて幅の広いパターンで電源バスに接続する必要があります。通常動作時は消費電力が小さく、パッケージの温度変化もわずかです。

定常状態での通常動作時消費電力は次式で計算できます。

$$P_{(SS)} = I_{OUT}^2 \times R_{ON}$$

様々な動作温度での Ronの値については、電気的特性の表と標準動作特性を参照してください。

出力が継続的にグランドに短絡されている場合、消費電力は次式で計算できます。

$$P = I_{OIIT} \times V_{IN}$$

短絡フォルト状態時は、その消費電力によってデバイスがサーマル・シャットダウン・スレッショルドに達する可能性があるので、注意 が必要です。システムの熱容量を大きくすると共に周囲への熱抵抗を減らすために、露出パッドからグランド・プレーンへのサーマル・ ビアを設けることが強く推奨されます。

自動リトライ電流制限モードでは、t<sub>RETRY</sub> の期間はデバイスがターンオフするので、デバイス内の平均消費電力は減少します。デバイスの消費電力は次式で計算します。

$$P_{(AVG)} = \frac{v_{IN} \times I_{OUT} \times t_{BLANK}}{t_{RETRY} + t_{BLANK}}$$

## ESD 保護

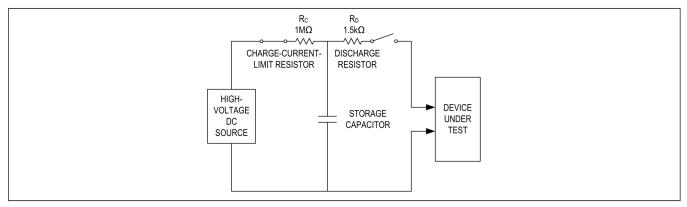

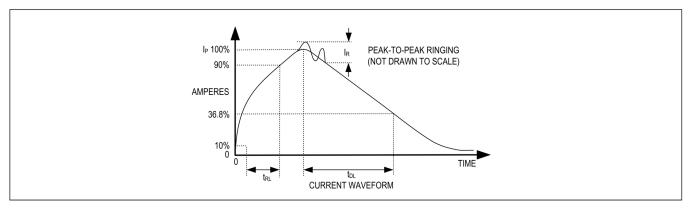

このデバイスは、IN が  $0.47\mu F$  の低 ESR セラミック・コンデンサでグランドにバイパスされた状態で、IN 端子の ESD を $\pm 15kV$  (人体モデル (HBM) による静電放電 (ESD) モデル) として仕様規定されています。IN 端子の ESD が $\pm 2kV$  (HBM、代表値) の場合、コンデンサは必要ありません。全ての端子は代表値 $\pm 2kV$  (HBM) の ESD 保護を備えています。② 9 は HBM を、② 10 はこのモデルが低インピーダンス経路に放電する際に発生する電流波形を示しています。このモデルは対象とする ESD 電圧まで充電された 100pF のコンデンサで構成され、 $1.5k\Omega$  の抵抗を介してデバイスに放電されます。

図 9. 人体モデルによる ESD 試験モデル

図 10. 人体モデルの電流波形

# 標準アプリケーション回路

# 型番

| PART          | TEMP RANGE      | PIN PACKAGE |

|---------------|-----------------|-------------|

| MAX17615ATB+  | -40°C to +125°C | 10 TDFN-EP* |

| MAX17615ATB+T | -40°C to +125°C | 10 TDFN-EP* |

+は鉛 (Pb) フリー/RoHS 準拠パッケージを表します。

T= テープ&リール

\*EP = 露出パッド

MAX17615

# 改訂履歴

| 版数 | 改訂日  | 説明           | 改訂ページ |

|----|------|--------------|-------|

| 0  | 8/22 | 市場投入のためのリリース | -     |